## MINISTERO DELLO SVILUPPO ECONOMICO DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE UFFICIO ITALIANO BREVETTI E MARCHI

| DOMANDA DI INVENZIONE NUMERO | 102012902110785 |

|------------------------------|-----------------|

| Data Deposito                | 14/12/2012      |

| Data Pubblicazione           | 14/06/2014      |

Classifiche IPC

Titolo

COMPONENTE ELETTRONICO DI POTENZA NORMALMENTE SPENTO

## DESCRIZIONE

del brevetto per invenzione industriale dal titolo: "COMPONENTE ELETTRONICO DI POTENZA NORMALMENTE SPENTO" di STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI, 2

AGRATE BRIANZA (MB)

Inventori: SANTANGELO Antonello, GIUFFRIDA Marcello Francesco Salvatore

\*\*\* \*\*\*\* \*\*\*

La presente invenzione è relativa a un componente elettronico di potenza normalmente spento.

Per realizzare strutture a ponte e semiponte nei circuiti a commutazione ad alta tensione, si diffondendo l'impiego di transistori a effetto di campo di potenza con elevate prestazioni, come ad esempio JFET di alta tensione in substrati SiC o MOSFET in substrati GaN ad elevata mobilità di elettroni (HEMT, High Electron Mobility Transistors). Transistori di questo genere, seppure estremamente efficienti e adatti a operare con tensioni ad esempio dell'ordine di 600-1.200 V, hanno però 10 svantaggio di essere normalmente accesi (normally on). In altre parole, se non viene applicata una specifica tensione di spegnimento sui terminali di controllo, i dispositivi normalmente accesi permettono il passaggio di corrente in presenza di una differenza di potenziale fra i terminali di conduzione. Date le alte tensioni in gioco, si possono così creare condizioni rischiose, ad esempio quando i circuiti di pilotaggio che alimentano i terminali di controllo sono soggetti a malfunzionamenti o disturbi che impediscono di operare correttamente, anche solo per periodi di tempo limitati.

Per evitare questi inconvenienti, i transistori alta tensione normalmente accesi vengono spesso utilizzati in combinazione con un transistore di bassa tensione normalmente spento (normally off), che impedisce passaggio di corrente in assenza di controllo. I transistori accoppiati l'uno all'altro in sono configurazione cascode e sono incorporati in una stessa struttura di incapsulamento (package) per formare un unico componente di potenza discreto. Facendo per semplicità riferimento a transistori a effetto di campo a canale N, il transistore di bassa tensione normalmente spento terminale di sorgente collegato a una linea a potenziale di riferimento (massa) e terminale di pozzo collegato a un terminale di sorgente del transistore di alta tensione normalmente acceso. Il terminale di porta del transistore normalmente spento riceve un segnale di controllo da un circuito di pilotaggio, mentre il terminale di porta del transistore normalmente acceso è collegato a massa.

assenza del segnale di controllo, il transistore normalmente spento, che è collegato in serie al transistore normalmente acceso, impedisce il passaggio di corrente e forza lo spegnimento dell'intero componente discreto.

Il transistore normalmente acceso e il transistore normalmente spento sono di regola realizzati in chip separati e incorporati in una singola struttura di incapsulamento, provvista di terminali di connessione. Il transistore normalmente spento e il transistore normalmente acceso sono portati su una stessa lamina conduttrice incorporata nella struttura di incapsulamento e sono collegati fra loro, alla lamina conduttrice e ai terminali di connessione mediante connessioni a filo.

Le soluzioni note sono però piuttosto complesse, sia per la necessità di isolare almeno il transistore normalmente spento dalla lamina conduttrice, sia per il numero di connessioni a filo. Inoltre, le connessioni a filo hanno associate induttanze parassite non trascurabili.

C'è quindi un interesse a semplificare la struttura del componente di potenza, in modo da ridurre sia le connessioni a filo sia, di conseguenza, le induttanze parassite.

Scopo della presente invenzione è fornire un componente elettronico di potenza che permetta di superare le limitazioni descritte.

Secondo la presente invenzione viene fornito un componente elettronico di potenza come definito nella rivendicazione 1.

Per una migliore comprensione dell'invenzione, ne verranno ora descritte alcune forme di realizzazione, a puro titolo di esempio non limitativo e con riferimento ai disegni allegati, nei quali:

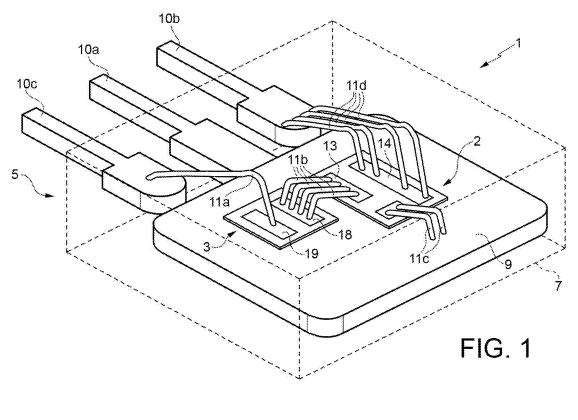

- la figura 1 è una vista prospettica semplificata, con parti asportate per chiarezza, di un componente elettronico di potenza in accordo a una forma di realizzazione della presente invenzione;

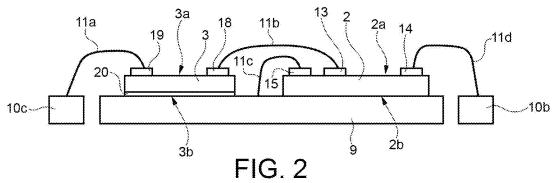

- la figura 2 è una vista laterale semplificata del componente elettronico di potenza di figura 1;

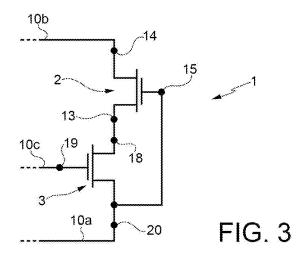

- la figura 3 è uno schema elettrico relativo al componente di figura 1;

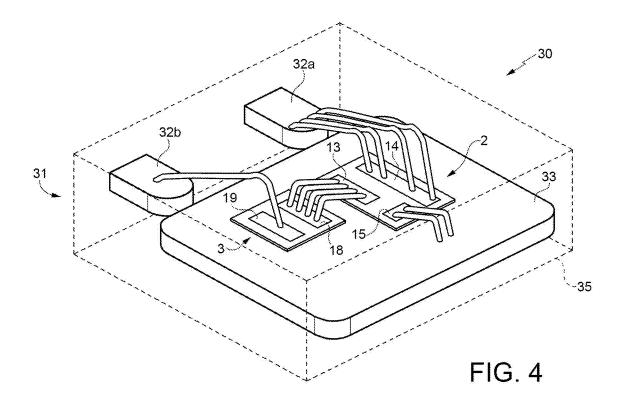

- la figura 4 è una vista prospettica semplificata, con parti asportate per chiarezza, di un componente elettronico di potenza in accordo a una diversa di realizzazione della presente invenzione;

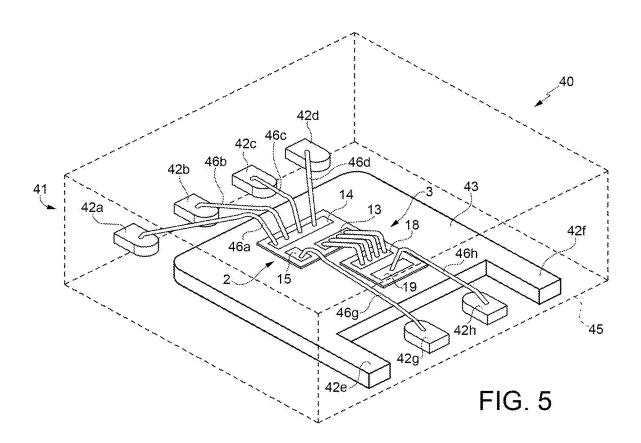

- la figura 5 è una vista prospettica semplificata, con parti asportate per chiarezza, di un componente elettronico di potenza in accordo a un'ulteriore diversa di realizzazione della presente invenzione;

- la figura 6 è uno schema elettrico relativo al componente di figura 5;

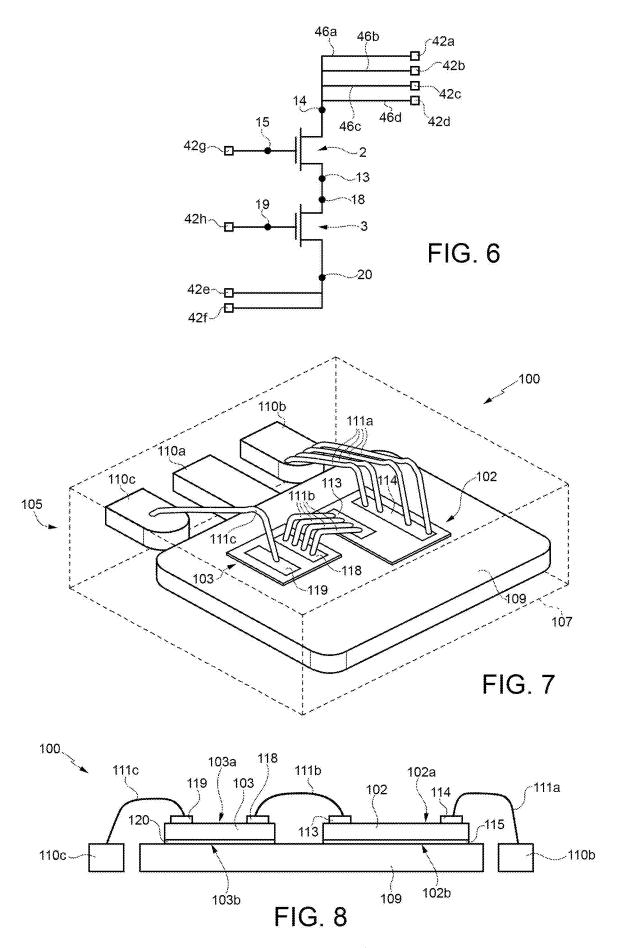

- la figura 7 è una vista prospettica semplificata, con parti asportate per chiarezza, di un componente elettronico di potenza in accordo a un'ulteriore diversa di realizzazione della presente invenzione;

- la figura 8 è una vista laterale semplificata del componente elettronico di potenza di figura 7;

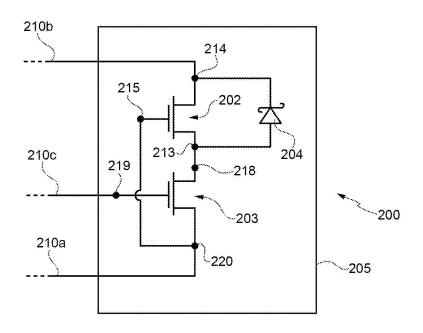

- la figura 9 è uno schema elettrico relativo a un componente elettronico di potenza in accordo a un'ulteriore diversa di realizzazione della presente invenzione;

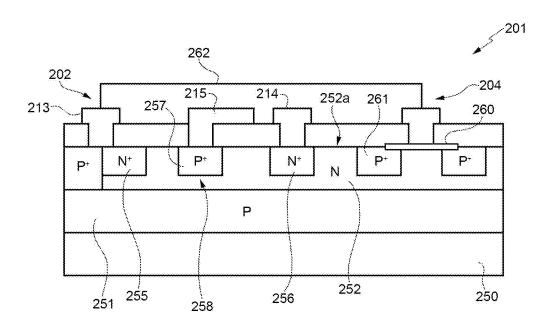

- la figura 10 è una sezione trasversale attraverso un chip incorporante una porzione del componente elettronico di potenza di figura 9;

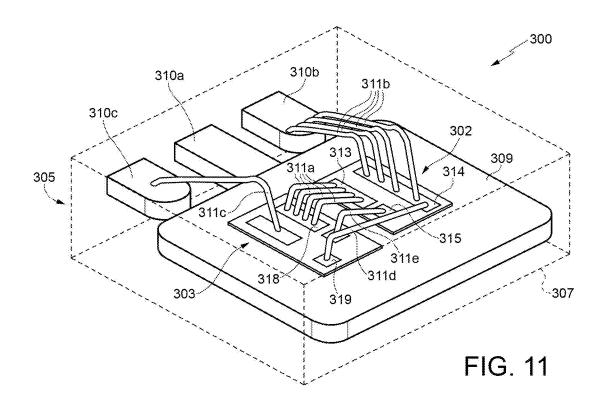

- la figura 11 è una vista prospettica semplificata, con parti asportate per chiarezza, di un componente elettronico di potenza in accordo a un'ulteriore diversa di realizzazione della presente invenzione;

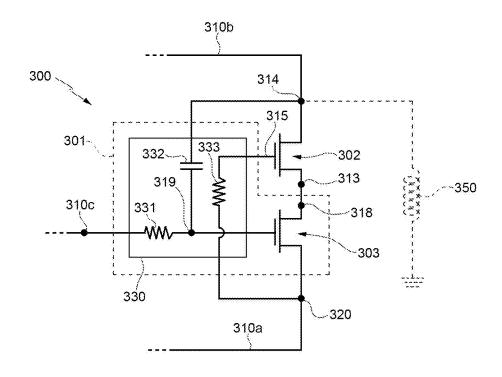

- la figura 12 è uno schema elettrico relativo al componente di figura 11;

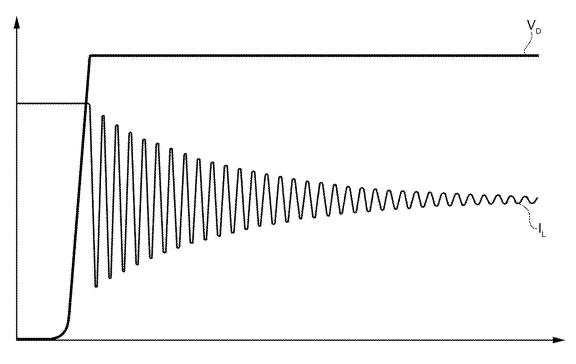

- la figura 13 è un grafico che mostra grandezze relative al componente elettronico di potenza noto; e

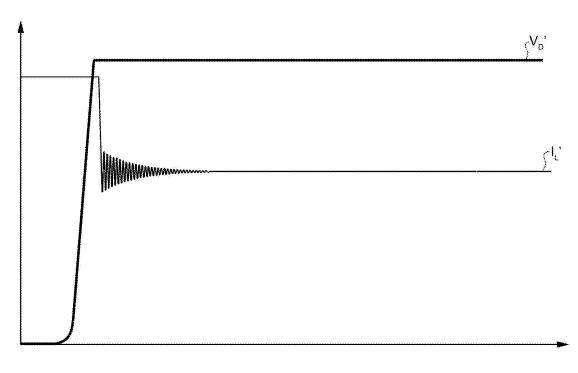

- la figura 14 è un grafico che mostra grandezze relative al componente elettronico di potenza di figura 12.

Con riferimento alle figure 1 e 2, un componente di potenza discreto normalmente spento, indicato nel suo complesso con il numero 1, comprende un transistore

normalmente acceso 2 e un transistore normalmente spento 3, incorporati in una stessa struttura di incapsulamento (package) 5. A sua volta, la struttura di incapsulamento 5 comprende un involucro 7, indicato in modo semplificato con linea a tratteggio, una piastrina (plate) metallica 9 contenuta nell'involucro 7 e una pluralità di reofori 10 che si estendono al di fuori dell'involucro 7. In una forma di realizzazione, sono presenti tre reofori 10a, 10b, 10c, uno dei quali (10a) è realizzato di pezzo con la piastrina metallica 9.

Il transistore normalmente acceso 2 e il transistore normalmente spento 3 sono realizzati in chip distinti e sono disposti entrambi sulla piastrina metallica 9. Il collegamento del transistore normalmente acceso 2 e del transistore normalmente spento 3 fra loro, alla piastrina metallica 9 e ai reofori 10 è ottenuto mediante connessioni a filo 11a-11d realizzate mediante wire bonding.

Il transistore normalmente acceso 2 è un transistore di alta tensione ed è in grado di sopportare tensioni ad esempio fino a 1.200 V. In una forma di realizzazione, il transistore normalmente acceso 2 è un transistore GaN HEMT a svuotamento (depletion) e presenta un terminale di sorgente 13, terminale di pozzo 14 e terminale di porta 15 tutti su una prima faccia (fronte) 2a del rispettivo chip opposta alla piastrina metallica 9. Una seconda faccia

(retro) 2b opposta alla prima faccia 2a è adiacente alla piastrina metallica 9.

Il transistore normalmente spento 3 è del tipo Bottom Source di bassa tensione. In particolare, il transistore normalmente spento 3 ha terminale di pozzo 18 e terminale di porta 19 su una prima faccia 3a del rispettivo chip e terminale di sorgente 20 su una seconda faccia 3b opposta alla prima faccia 3a. In una forma di realizzazione, il transistore normalmente spento 3 è un transistore LDMOS. La seconda faccia 3b del transistore normalmente spento 3 è unita alla piastrina metallica 9 mediante un giunto conduttivo. Pertanto, il terminale di sorgente 20 del transistore normalmente spento 3 e la piastrina metallica 9 sono in elettricamente collegati sostanzialmente in modo diretto.

Il transistore normalmente acceso 2 e il transistore normalmente spento 3 sono collegati fra loro configurazione cascode, come mostrato in figura 3. pratica, il terminale di porta 19 del transistore normalmente spento 3 è collegato al reoforo 10c tramite le connessioni a filo 11a e il terminale di pozzo 18 è collegato al terminale di sorgente 13 del transistore normalmente acceso 2 tramite le connessioni a filo 11b. Il terminale di sorgente 20 del transistore normalmente spento 3 è invece collegato, tramite la piastrina metallica 9, al reoforo 10a.

Il transistore normalmente acceso 2 ha terminale di porta 15 collegato al terminale di sorgente 20 del transistore normalmente spento 3 (tramite le connessioni a filo 11c e la piastrina metallica 9). Il terminale di pozzo 14 del transistore normalmente acceso 2 è collegato al reoforo 10b tramite le connessioni a filo 11d.

L'impiego di un transistore Bottom Source (in pratica con il terminale di sorgente sul retro del chip) come transistore normalmente spento permette di superare il problema dell'isolamento del terminale di pozzo dalla piastrina metallica 9 e, allo stesso tempo, di ridurre il numero di connessioni a filo e le induttanze parassite. Contrariamente a quanto accade nei componenti di potenza discreti normalmente spenti convenzionali, nel transistore normalmente spento 3 la seconda faccia 3b rivolta verso la piastrina definisce il terminale di sorgente 20 (e non il terminale di pozzo). Il terminale di pozzo 18 si trova invece sulla prima faccia 3a, opposta alla piastrina metallica 9, e quindi non c'è necessità di prevedere un apposito isolamento. Inoltre, dato che tra il terminale di sorgente 20 del transistore normalmente spento 3 e la piastrina metallica 9 deve essere realizzata connessione elettrica diretta, è sufficiente prevedere un giunto di connessione conduttivo. Non occorre

realizzare una connessione a filo dedicata, ottenendo un beneficio anche in termini di riduzione dell'induttanza parassita.

Nella forma di realizzazione di figura 4, il normalmente acceso 2. е. il. transistore transistore normalmente spento 3 di un componente di potenza 30 normalmente spento sono alloggiati in una struttura di incapsulamento 31 avente due reofori 32a, 32b. Τn particolare, il transistore normalmente acceso iltransistore normalmente spento 3 sono posti su piastrina metallica 33 incorporata in un involucro 35 della struttura di incapsulamento 31.

Nella forma di realizzazione di figura 5, il 2 il transistore normalmente acceso е transistore normalmente spento 3 di un componente di potenza 40 sono alloggiati in una struttura di incapsulamento circuiti integrati che comprende un involucro 45, piastrina metallica 43 e una pluralità di piedini (pin) di connessione 42a-42h (otto nell'esempio illustrato). I piedini (pin) di connessione 42a-42h sono disposti in ugual numero su lati opposti della piastrina metallica 43 e dell'involucro 45. In una forma di realizzazione, i piedini di connessione 42a-42d che si trovano su un primo lato della piastrina metallica 43 sono collegati al terminale di pozzo 14 del transistore normalmente acceso 2 mediante

rispettive connessioni a filo 46a-46d. Due piedini connessione 42e, 42f su un secondo lato della piastrina metallica 43 sono realizzati di pezzo con quest'ultima. Gli altri due piedini di connessione 42q, 42h rispettivamente collegati al terminale di porta 15 del transistore normalmente acceso 2 mediante connessioni a filo 46g e al terminale di porta 19 del transistore normalmente spento 3 mediante connessioni a filo 46g, come mostrato in figura 6. In questo modo, i terminali di porta 15, 19 del transistore normalmente acceso 2 transistore normalmente spento 3 sono indipendentemente accessibili dall'esterno.

Nelle figure 7 e 8 è illustrata un'ulteriore forma di realizzazione dell'invenzione. Ιn questo caso, componente di potenza 100 normalmente spento comprende un transistore normalmente acceso 102 е un transistore normalmente acceso 103 incorporati in una stessa struttura di incapsulamento 105. A sua volta, la struttura di incapsulamento 105 comprende un involucro 107, una piastrina metallica 109 contenuta nell'involucro 107 e una pluralità di reofori 110 (tre nell'esempio illustrato) che si estendono al di fuori dell'involucro 107. Uno dei reofori (110a) è realizzato di pezzo con la piastrina metallica 109.

Il transistore normalmente acceso 102 è un JFET di

potenza di tipo bottom gate orizzontale. In particolare, il transistore normalmente acceso 102 ha terminale di sorgente 113 e terminale di pozzo 114 su una prima faccia 102a (figura 8), opposta alla piastrina metallica 109, e terminale di porta 115 su una seconda faccia 102b, opposta alla prima faccia 102a e adiacente alla piastrina metallica 109. Inoltre, il terminale di porta 115 è collegato elettricamente alla piastrina metallica 109 attraverso un giunto conduttivo (non mostrato).

Il transistore normalmente spento 103 è un transistore LDMOS Bottom Source di bassa tensione, come già descritto.

Il transistore normalmente acceso 102 e il transistore normalmente spento 103 sono collegati in configurazione cascode, analogamente a quanto mostrato in figura 3. In questo caso, tuttavia, il terminale di porta 115 del transistore normalmente acceso 102 è collegato direttamente alla piastrina 109 e, attraverso questa, al terminale di sorgente 120 del transistore normalmente spento 103. Non è quindi richiesta connessione a filo fra il terminale di porta 115 del transistore normalmente acceso 102 e il terminale di sorgente 120 del transistore normalmente spento 103. Per il resto, il transistore normalmente acceso 102 ha terminale di pozzo 114 collegato al reoforo 110b attraverso connessioni a filo 111a e terminale di sorgente

113 collegato al terminale di pozzo 118 del transistore normalmente spento 103 attraverso connessioni a filo 111b. Inoltre, il transistore normalmente spento 103 ha terminale di porta 119 collegato al reoforo 110c attraverso connessioni a filo 111c.

La configurazione descritta permette quindi di risparmiare un'ulteriore connessione a filo.

Nella forma di realizzazione illustrata nelle figure 9 e 10, un componente di potenza 200 normalmente spento comprende un transistore normalmente acceso 202 e transistore normalmente spento 203 in configurazione cascode, realizzati in chip separati e incorporati in una stessa struttura di incapsulamento 205 dotata di reofori 210a, 210b, 210c (qui illustrata solo schematicamente). In particolare, il transistore normalmente acceso 202 terminale di sorgente 213, terminale di pozzo 214 terminale di porta 215 rispettivamente collegati a terminale di pozzo 218 del transistore normalmente spento 203, al reoforo 210b e al reoforo 210a. Il transistore normalmente spento 203 ha, inoltre, terminale di porta 219 e terminale di sorgente 220 rispettivamente collegati al reoforo 210c e al reoforo 210a.

Il transistore normalmente acceso 202 è un JFET di potenza laterale e ha integrato nello stesso chip 201 (figura 10) un diodo Schottky 204. In particolare, il diodo

Schottky 204 ha anodo e catodo rispettivamente collegati al terminale di sorgente 213 e al terminale di pozzo 214 del transistore normalmente acceso 202.

In dettaglio, il chip 201 in cui è integrato il transistore normalmente acceso 202 comprende un substrato semiisolante 250, su cui sono disposti, nell'ordine, uno strato conduttivo di tipo P 251 e uno strato di deriva 252 di tipo N.

Una regione di sorgente 255, una regione di pozzo 256 e una regione di porta 257 sono realizzate nello strato di deriva 252 e affiorano a una sua superficie 252a. Una regione di canale 258 è definita nello strato di deriva 252 fra la regione di sorgente 255 e la regione di pozzo 256, entrambe di tipo N+. La regione di porta 257, di tipo P+, anch'essa disposta fra la regione di sorgente 255 e la regione di pozzo 256, si estende fra la superficie 252a dello strato di deriva 252 e la regione di canale 258.

Nel chip 201 è integrato anche il diodo Schottky 204, che comprende un terminale di anodo 260 metallico, formato sullo strato di deriva 252 e contornato da un guard ring 261 di tipo P+. Il terminale di anodo 260 è collegato al terminale di sorgente 213 del transistore normalmente acceso 202 attraverso una linea di connessione 262 sul chip 201 (rappresentata solo schematicamente in figura 10). Il terminale di catodo del diodo

Schottky 204 è definito dal terminale di pozzo 214 del transistore normalmente acceso 202.

Il diodo Schottky 204 può essere facilmente integrato nel chip 201 del transistore normalmente acceso 202 e permette di utilizzare in maniera ottimale il dispositivo nel terzo quadrante, riducendo la tensione sul diodo risultante nello stato di conduzione. Regioni di sorgente e di porta del transistore normalmente acceso 202 formano infatti un diodo PN che si trova in parallelo al diodo Schottky.

Le figure 11 e 12 illustrano un'ulteriore forma di realizzazione dell'invenzione. Un componente di potenza 300 normalmente spento comprende un transistore normalmente acceso 302 e un transistore normalmente acceso 303 in configurazione cascode, realizzati in chip separati e incorporati in una stessa struttura di incapsulamento 305 dotata di reofori 310a, 310b, 310c (qui illustrata solo schematicamente).

La struttura di incapsulamento 305 comprende n involucro 307 e una piastrina metallica 309 su cui sono disposti i chip del transistore normalmente acceso 302 e del transistore normalmente acceso 303.

Il transistore normalmente acceso 302 è un transistore di alta tensione, ad esempio un transistore GaN HEMT a svuotamento, mentre il transistore normalmente spento 303 è

del tipo Bottom Source di bassa tensione, in particolare un transistore LDMOS.

Come accennato, il transistore normalmente acceso 302 e il transistore normalmente spento 303 sono collegati fra loro in configurazione cascode. In pratica, un terminale di pozzo 318 del transistore normalmente spento 303 è collegato un terminale di sorgente 313 del transistore normalmente acceso 302 tramite connessioni a filo 311a. Un terminale di sorgente 320 del transistore normalmente spento 303 è invece collegato, tramite la piastrina metallica 309, al reoforo 310a.

Il transistore normalmente acceso 302 ha terminale pozzo 314 collegato al reoforo 310b tramite connessioni a filo 311b.

Come mostrato più in dettaglio in figura 12, nel chip (qui indicato con 301) che alloggia il transistore normalmente spento 303 è integrato anche un circuito di controllo 330. Il circuito di controllo 330 è accoppiato al transistore normalmente acceso 302 e al transistore normalmente spento 303 ed è configurato per rallentare il trasferimento di carica verso la capacità porta-sorgente del transistore normalmente spento 303 durante la fase di accensione e per rallentare la rimozione di carica dalla capacità porta-sorgente del transistore normalmente acceso 302 durante la fase di spegnimento.

realizzazione, il circuito una forma di controllo 330 comprende un primo resistore 331. un condensatore 332 e un secondo resistore 333. Il primo resistore 331 e il condensatore 332 collegano il terminale 319 del transistore normalmente spento di porta rispettivamente al reoforo 310c, tramite connessioni a filo al terminale di pozzo 314 del transistore 311c, е normalmente acceso 302 (e quindi al reoforo 310b), tramite connessioni a filo 311d. Il secondo resistore 333 è collegato fra il terminale di porta 315 del transistore normalmente acceso 302 e il terminale di sorgente 318 del transistore normalmente spento 303, tramite connessioni a filo 311e (dato che il terminale di sorgente 318 è sulla faccia del chip alloggiante il transistore normalmente spento 303 in contatto con la piastrina metallica 309, il collegamento viene realizzato su una faccia libera del chip stesso e completato con un contatto profondo, qui non mostrato).

In molte applicazioni, commutazioni eccessivamente veloci fra gli stati di acceso e spento possono causare problemi, anche in considerazione delle elevate tensioni in gioco. Principalmente, fronti troppo ripidi possono innescare oscillazioni in presenza di carichi induttivi (350 in figura 12), accensione di componenti parassiti e, in generale, disturbi elettromagnetici significativi

nell'ambiente. La figura 13 mostra a titolo di esempio oscillazioni della corrente ( $I_{\rm L}$ ) su un carico induttivo in risposta a uno spegnimento rapido del componente di potenza 300 (rampa di salita della tensione  $V_{\rm D}$  sul terminale di pozzo 314 del transistore normalmente acceso 302).

Il circuito di controllo 330, rallentando l'iniezione e il prelievo di carica dalle capacità porta-sorgente del transistore normalmente acceso 302 e del transistore normalmente spento 303, permette di ottenere transizioni meno rapide e quindi di ridurre in modo significativo i potenziali effetti negativi.

In particolare, nell'esempio illustrato in figura 12, il resistore 331 e il condensatore 332 controllano la rampa di salita e di discesa dv/dt della tensione di uscita. In aggiunta, se si considera un secondo resistore 333 si ha un ulteriore diminuzione delle oscillazioni di corrente. Selezionando i valori di resistenza del primo resistore 331 e del secondo resistore 333 e il valore di capacità del condensatore 332, è quindi possibile eliminare o ridurre in modo sostanziale possibili effetti indesiderati legati alla commutazione del componenti di potenza 300, come mostrato in figura 14 (dove la corrente sul carico e la tensione sul terminale di pozzo 314 del transistore normalmente acceso 302 sono indicate rispettivamente con  $I_L'$  e  $V_D'$ ). In particolare, studi hanno mostrato che è possibile ottenere un significativo rallentamento dei fronti di accensione e spegnimento e la sostanziale eliminazione delle oscillazioni della corrente sul carico con valori di resistenza di circa 50  $\Omega$  e una capacità di circa 4 pF (con escursioni di circa 300 V della tensione sul terminale di pozzo del transistore normalmente acceso).

Il circuito di controllo 330 ha altresì il vantaggio di essere molto semplice e facilmente integrabile nel chip 301 del transistore normalmente spento 303. Si intende tuttavia che la soluzione descritta e illustrata rappresenta un esempio non limitativo e che il circuito di controllo potrebbe essere realizzato in modo diverso.

Al componente elettronico di potenza descritto possono essere apportate modifiche e varianti, senza uscire dall'ambito della presente invenzione, come definito nelle rivendicazioni allegate.

## RIVENDICAZIONI

1. Componente elettronico di potenza comprendente:

un transistore normalmente acceso (2; 102; 202; 302) di alta tensione; e

un transistore normalmente spento (3; 103; 203; 303) di bassa tensione;

in cui:

il transistore normalmente acceso (2; 102; 202; 302) e il transistore normalmente spento (3; 103; 203; 303) sono accoppiati in configurazione cascode e sono alloggiati in un'unica struttura di incapsulamento (5; 31; 41; 105; 205; 305); e

il transistore normalmente spento (3; 103; 203; 303) è del tipo Bottom Source.

- 2. Componente secondo la rivendicazione 1, in cui il transistore normalmente acceso (2; 102; 202; 302) e il transistore normalmente spento (3; 103; 203; 303) sono alloggiati in rispettivi chip distinti e il transistore normalmente spento (3; 103; 203; 303) ha terminale di pozzo (18; 318) e terminale di porta (19; 319) su una prima faccia (3a; 103a) del rispettivo chip (301) e terminale di sorgente (20; 120; 220; 320) su una seconda faccia (3b; 103b) del rispettivo chip (301) opposta alla prima faccia (3a; 103a).

- 3. Componente secondo la rivendicazione 2, in cui la struttura di incapsulamento (5; 31; 41; 105; 205; 305)

comprende una piastrina conduttiva (9; 33; 43; 109; 309), su cui sono collocati il transistore normalmente acceso (2; 102; 202; 302) e il transistore normalmente spento (3; 103; 203; 303); e in cui il la seconda faccia (3b; 103b) del chip (301) alloggiante il transistore normalmente spento (3; 103; 203; 303) è unita alla piastrina conduttiva (9; 33; 43; 109; 309).

- 4. Componente secondo la rivendicazione 3, in cui il terminale di sorgente (20; 120; 220; 320) è elettricamente collegato alla piastrina conduttiva (9; 33; 43; 109; 309).

- 5. Componente secondo una qualsiasi delle rivendicazioni da 2 a 4, in cui il transistore normalmente spento (3; 103; 303) è un transistore LDMOS.

- 6. Componente secondo la rivendicazione 5, comprendente un circuito di controllo (330) integrato nel chip (301) che alloggia il transistore normalmente spento (303).

- 7. Componente secondo la rivendicazione 6, in cui il circuito di controllo (330) è accoppiato al transistore normalmente acceso (302) e al transistore normalmente spento (303) ed è configurato per rallentare il trasferimento di carica verso una capacità porta-sorgente del transistore normalmente spento (303) durante una fase di accensione e per rallentare la rimozione di carica da una capacità porta-sorgente del transistore normalmente acceso (302) durante una fase di spegnimento.

- 8. Componente secondo la rivendicazione 7, avente un primo terminale di connessione (310c) e un secondo terminale di connessione (310b); in cui

- il circuito di controllo (330) comprende un primo resistore (331), un condensatore (332) e un secondo resistore (333);

- il primo resistore (331) è collegato fra un terminale di controllo (319) del transistore normalmente spento (302) e il primo terminale di connessione (310c);

- il condensatore (332) è collegato fra il terminale di controllo (319) del transistore normalmente spento (302) e a un terminale di pozzo (314) del transistore normalmente acceso (302); e

- il secondo resistore (333) è collegato fra un terminale di controllo (315) del transistore normalmente acceso (302) e un terminale di sorgente (320) del transistore normalmente spento (303).

- 9. Componente secondo una qualsiasi delle rivendicazioni precedenti, in cui il transistore normalmente acceso (2; 302) è un transistore GaN HEMT.

- 10. Componente secondo una qualsiasi delle rivendicazioni da 1 a 5, in cui il transistore normalmente acceso (102) è un transistore JFET Bottom Gate orizzontale.

- 11. Componente secondo una qualsiasi delle rivendicazioni da 2 a 8, in cui il transistore normalmente

acceso (202) un transistore JFET laterale.

- 12. Componente secondo la rivendicazione 11, comprendente un diodo Schottky (204) integrato nel chip (201) del transistore normalmente acceso (203).

- 13. Componente secondo la rivendicazione 12, in cui:

- il chip (201) del transistore normalmente acceso (202) comprende uno strato di deriva (252);

- il transistore normalmente acceso (202) comprende una regione di sorgente (255), una regione di pozzo (256), una regione di porta (257) e una regione di canale (258), alloggiate nello strato di deriva (252) e affioranti a una superficie (252a) dello strato di deriva (252);

un terminale di anodo (260) del diodo Schottky (204) è disposto sullo strato di deriva (252) a distanza dal transistore normalmente acceso (202); e

un terminale di catodo del diodo Schottky (204) è definito dal terminale di pozzo (214) del transistore normalmente acceso (202).

14. Componente secondo la rivendicazione 13, in cui il terminale di anodo (260) del diodo Schottky (204) è collegato a un terminale di sorgente (213) del transistore normalmente acceso (202).

p.i.: STMICROELECTRONICS S.R.L.

Elena CERBARO

p.i.: STMICROELECTRONICS S.R.L.

Elena CERBARO (Iscrizione Albo nr. 426/BM)

p.i.: STMICROELECTRONICS S.R.L.

p.i.: STMICROELECTRONICS S.R.L.

Elena CERBARO (Iscrizione Albo nr. 426/BM)

FIG. 9

FIG. 10

FIG. 12

p.i.: STMICROELECTRONICS S.R.L.

FIG. 13

FIG. 14