(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-533137

(P2007-533137A)

(43) 公表日 平成19年11月15日(2007.11.15)

| (51) Int.C1.                 | F 1                          | テーマコード (参考)                                                                      |

|------------------------------|------------------------------|----------------------------------------------------------------------------------|

| <b>HO1L 29/786 (2006.01)</b> | HO1L 29/78                   | 626C 5FO48                                                                       |

| <b>HO1L 21/336 (2006.01)</b> | HO1L 29/78                   | 618A 5F110                                                                       |

| <b>HO1L 27/12 (2006.01)</b>  | HO1L 29/78                   | 618B 5F152                                                                       |

| <b>HO1L 21/02 (2006.01)</b>  | HO1L 29/78                   | 613A                                                                             |

| <b>HO1L 21/20 (2006.01)</b>  | HO1L 29/78                   | 616V                                                                             |

|                              | 審査請求 未請求                     | 予備審査請求 有 (全 19 頁) 最終頁に続く                                                         |

| (21) 出願番号                    | 特願2007-507361 (P2007-507361) | (71) 出願人 591016172                                                               |

| (86) (22) 出願日                | 平成17年3月28日 (2005.3.28)       | アドバンスト・マイクロ・ディバイシズ・<br>インコーポレイテッド                                                |

| (85) 翻訳文提出日                  | 平成18年12月5日 (2006.12.5)       | ADVANCED MICRO DEVI<br>CES INCORPORATED                                          |

| (86) 國際出願番号                  | PCT/US2005/010574            | アメリカ合衆国、94088-3453                                                               |

| (87) 國際公開番号                  | W02005/101521                | カリフォルニア州、サンディベイル、ビィ・<br>オウ・ボックス・3453、ワン・エイ・<br>エム・ディ・プレイス、メイル・ストップ<br>・68 (番地なし) |

| (87) 國際公開日                   | 平成17年10月27日 (2005.10.27)     | (74) 代理人 100099324                                                               |

| (31) 優先権主張番号                 | 10/819,441                   | 弁理士 鈴木 正剛                                                                        |

| (32) 優先日                     | 平成16年4月7日 (2004.4.7)         | (74) 代理人 100111615                                                               |

| (33) 優先権主張国                  | 米国(US)                       | 弁理士 佐野 良太                                                                        |

最終頁に続く

(54) 【発明の名称】 SOI (semiconductor on insulator) 基板、およびこの基板から形成されるデバイス

## (57) 【要約】

レアアース・スカンデートのようなペロブスカイト格子構造を有する絶縁材料の層を含むSOI (semiconductor on insulator) デバイスである。この絶縁材料(52)は、この絶縁材料(52)のすぐ上にダイヤモンド格子を有する半導体材料(54)を成長させることができる、有効な格子定数を有するように選択される。レアアース・スカンデート絶縁体の例としては、ガドリニウム・スカンデート( $GdScO_3$ )、ジスプロシウム・スカンデート( $DyScO_3$ )、およびガドリニウムとジスプロシウム・スカンデートの合金( $Gd_{1-x}Dy_xScO_3$ )が含まれる。

## 【特許請求の範囲】

## 【請求項 1】

ペロブスカイト格子を有する絶縁材料の層(52)を含む基板と、前記絶縁層上に形成される半導体材料の層(54)と、そのチャネル領域中に半導体材料の層が組み入れられるMOSFETと、を含む、SOI(semiconductor on insulator)デバイス。

## 【請求項 2】

前記ペロブスカイト格子を有する絶縁材料(52)は、レアアース・スカンデートである、請求項1記載のデバイス。

## 【請求項 3】

前記レアアース・スカンデートは、ガドリニウム・スカンデート( $GdScO_3$ )、ジスプロシウム・スカンデート( $DyScO_3$ )、およびガドリニウムとジスプロシウム・スカンデートとの合金( $Gd_{1-x}Dy_xScO_3$ )のうちのいずれか1つである、請求項2記載のデバイス。

## 【請求項 4】

前記半導体材料の層(54)は、前記ペロブスカイト格子によって引張歪みが与えられるシリコン層である、請求項1記載のデバイス。

## 【請求項 5】

前記半導体材料の層(54)は、前記ペロブスカイト格子によって圧縮歪みが与えられるシリコンゲルマニウム層である、請求項1記載のデバイス。

## 【請求項 6】

前記半導体材料の層(54)は、ダイヤモンド型格子を有する化合物半導体材料である、請求項1記載のデバイス。

## 【請求項 7】

ペロブスカイト格子を有する絶縁材料の層(52)を含む基板を形成し、前記絶縁材料(52)の前記ペロブスカイト格子の(001)面上に、ダイヤモンド型格子を有する半導体材料の層(54)を成長させ、そのチャネル領域中に、前記半導体材料(54)を組み入れたMOSFETを形成する、

SOI(semiconductor on insulator)MOSFETデバイス上に半導体を形成する方法。

## 【請求項 8】

ペロブスカイト格子を有する絶縁材料の層(52)を含む基板と、前記絶縁層(52)上に形成される第1半導体材料(72)の領域であって、前記絶縁層(52)により引っ張り歪みが与えられる第1半導体材料(72)の領域と、

前記第1半導体材料(72)の領域中に形成され、そのチャネル領域中に、前記第1半導体材料を組み入れる、第1MOSFET(70)と、

前記絶縁材料の層(52)上に形成される第2半導体材料(76)の領域であって、前記絶縁層により圧縮歪みが与えられる第1半導体材料(76)の領域と、

前記第2半導体材料(76)の領域中に形成され、そのチャネル領域中に、前記第2半導体材料を組み入れる、第2MOSFET(74)と、を含む、

SOI(semiconductor on insulator)デバイス。

## 【請求項 9】

前記絶縁層(52)は、レアアース・スカンデートである、請求項8記載のデバイス。

## 【請求項 10】

前記第1半導体材料(72)は、前記絶縁材料(52)の有効な格子定数より少ない格子定数を有するシリコンゲルマニウム合金であり、

前記第2半導体材料(76)は、前記絶縁材料(52)の有効な格子定数より大きい格子定数を有するシリコンゲルマニウム合金である、請求項8記載のデバイス。

## 【発明の詳細な説明】

## 【技術分野】

10

20

30

40

50

## 【0001】

本発明は概して、絶縁ゲート型電界効果トランジスタ(MOSFET)の製造、より詳しくは、絶縁基板上に形成されるMOSFETに関する。

## 【背景技術】

## 【0002】

MOSFETは、集積回路(IC)の一般的な構成素子である。

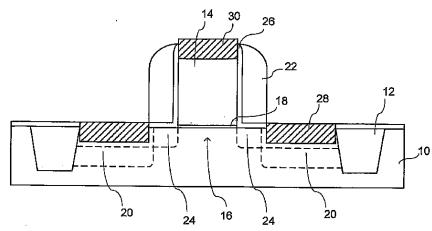

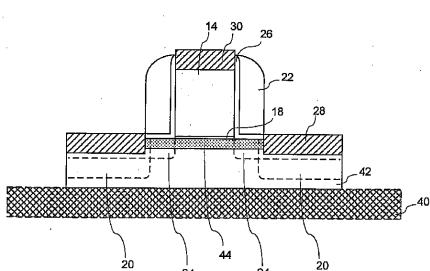

図1は、従来のMOSFETデバイスを示している。

このMOSFETは、バルクシリコン基板10上の活性領域内に形成されており、この活性領域は、基板10上に製造される他のIC素子からMOSFETの活性領域を電気的に絶縁するシャロートレンチ分離領域12に囲まれている。

MOSFETは、シリコン酸化物またはシリコン酸化窒化物のような薄いゲート絶縁体18によって分離される、ゲート14およびチャネル領域16を含んでいる。ゲート14は一般的に、ポリシリコンのような高濃度にドープした半導体材料から形成される。

MOSFETのソースおよびドレイン領域は、チャネル領域16の両側に形成される浅いソースおよびドレイン領域24と、深いソース領域およびドレイン領域18とを含んでいる。

基板上の保護材料26の形成後、浅いソースおよびドレイン領域24が注入される。それからゲート14の周りにスペーサ22を形成した後、深いソースおよびドレイン領域20がイオン注入によって形成される。

ソース・シリサイドおよびドレイン・シリサイド28は、オーミックコンタクトを提供するとともに接触抵抗を減少させるべく、深いソース領域およびドレイン領域20上に形成される。

シリサイド28は、基板半導体材料およびコバルト(Co)またはニッケル(Ni)のような金属を含んでいる。シリサイド30も、ゲート14の上面に形成される。

## 【0003】

バルク半導体基板上のデバイスの形成に変わるものとして、SOI(semiconductor on insulator)構造がある。

SOI構造において、MOSFETは、MOSFET活性領域の下にある絶縁層を含んだ基板上に形成される。

SOIデバイスは、バルク半導体基板中に形成されるデバイスに比較して多くの利点を有する。例えば、デバイス間のより良い絶縁性、リーク電流の減少、CMOS素子間のラッチアップの減少、チップキャパシタンスの減少、およびソース・ドレイン領域間の短チャネル結合の減少または除去である。

図2は、完全空乏型の一般的なSOI・MOSFETの一例を示す図である。

SOI・MOSFETは、シリコン層32および絶縁層34により構成されるSOI基板上に形成される。

MOSFET構造は、シリコン層の分離領域36上に形成される。このシリコン層は、個々のデバイスが形成される個々のアイランドを定義するようにエッチングされている。

薄い非ドープ・チャネル領域16は、シリコン層36の中心に位置する。

ソースおよびドレイン拡張部24は、ゲート絶縁体18上に形成されたゲート14の両側におけるシリコン層36中に注入される。

次にスペーサ22を形成し、高いソースおよびドレイン領域38をシリコン層36上に成長させ、それから、シリサイド・ソースおよびドレインコンタクト28と、シリサイド・ゲートコンタクト30を形成する。

## 【0004】

MOSFETの性能を向上させるための1つの選択肢として、抵抗と電力消費を減少させ、駆動電流、周波数応答および動作速度を向上させるために、MOSFET半導体材料のキャリア移動度を上げることがある。最近注目を集めているキャリア移動度を増加させる方法として、引張歪みが加えられたシリコン材料を使用する方法がある。

引っ張り歪みシリコンは、シリコンゲルマニウム基板上に半導体のエピタキシャル層を

成長させることによって形成することができる。

シリコンゲルマニウム格子は、格子内に大きなゲルマニウム原子が存在するため、純粋シリコン格子よりもわずかに大きい格子定数を有している。

エピタキシャル成長させたシリコンが、シリコンゲルマニウム格子に合わせて並ぶため、シリコン格子に引張歪みが生じる。

適度な引張歪みは電子移動度を増加させ、より大きな引張歪みは正孔移動度を増加させる。引張歪みの量は、シリコンゲルマニウム格子中のゲルマニウムの割合につれて増加する。また、適度な圧縮歪みが正孔移動度を改善することも知られている。

#### 【0005】

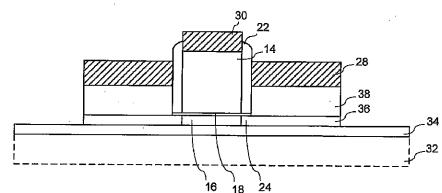

引張歪みシリコン層を有するMOSFETの一例を、図3に示す。

10

このMOSFETは、シリコン層10上に成長するシリコンゲルマニウム層32を含んだ基板上に形成される。

シリコンゲルマニウム層は一般的に、所望する歪み量によりゲルマニウム量が0から10%~40%に徐々に増加する、傾斜層(graded layer)である。

シリコンゲルマニウム層32上に歪みシリコン34のエピタキシャル層を成長させる。

MOSFETは、深いソースおよびドレイン領域20、浅いソースおよびドレイン拡張部24、ゲート酸化層18、保護材料26に囲まれたゲート14、スペーサ22、ソースおよびドレインシリサイド28、ゲートシリサイド30、およびシャロートレンチ分離12を含む従来のMOSFET構造を使用する。

チャネル領域16中の歪みシリコン材料は、ソースおよびドレインの間のキャリア移動度を高める。

20

#### 【0006】

歪みシリコンはまた、SOI基板上に形成されるMOSFETに組み入れられてもよい。

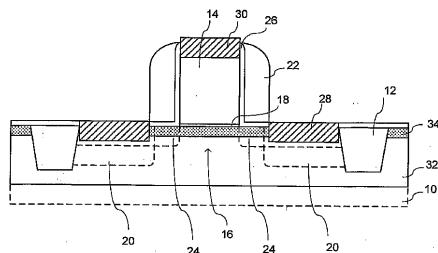

図4は、歪みシリコンSOIMOSFETの一例を示す図である。

このデバイスでは、MOSFETは、絶縁層40に重なるシリコンゲルマニウム層を含むSOI基板上に形成される。

シリコンゲルマニウム層をパターン化し、その上に個々のMOSFETが形成される分離領域42を定義する。

歪みシリコン層44を、シリコンゲルマニウム領域42上に成長させる。

30

その後、図3の従来の歪みシリコンデバイスの形成方法に類する方法で、MOSFETを形成する。

#### 【0007】

歪みシリコンチャネルを組み入れた完全空乏型のSOIデバイスを形成するのは難しい。

短チャネル効果を制御するために、完全空乏型のSOI・MOSFETの厚さは、チャネル領域がチャネル長の約3分の1を超えない厚さとすることが好ましい。

しかしながら、歪みシリコンチャネルの下のシリコンゲルマニウムに支持層を提供する必要があるため、全体のチャネル厚さはチャネル長に対する制限となる。または、歪みシリコンの厚さは移動度をかなり高めるためには十分ではない。

40

#### 【0008】

他の条件は一般的に、SOIデバイスの小型化に対するさらなる障害となる。

従来の完全空乏型のSOIデバイスでは、半導体の所望の厚さになるまで基板上の化学的機械的研磨(CMP)を実行することにより、非常に薄いチャネル層を製造することが一般的である。

しかしながら、CMPにより、その厚さに100程度の間のばらつきを有し得る、均一でない表面が製造される。

クリティカルディメンションが減少されるにつれて、このような厚さのばらつきは許容できないものとなる。例えば、45nmのデバイスについては、チャネル領域の厚さは約150であることが望ましい。

50

研磨した層の厚さにはらつきがあれば、これらのディメンションにおいて正確な厚さを有しているチャネル層を確実に製造するのは非常に難しい。

#### 【0009】

実質的にチャネル領域の厚さを一定にするために、絶縁材料上に半導体の層を成長させることは望ましいであろう。

しかしながら、従来の半導体デバイス製造技術は、さらなる結晶質の成長におけるテンプレートとして結晶格子を使用する。

例えば、シリコンウェーハは、規則的な結晶格子を提供するように、結晶面のうちの1つに沿ってカットされる単結晶シリコンから構成される。

この格子は、たい積されるシリコンの原子に対してのテンプレートとして役立つ。または、同じ格子構造を有している他の元素は、たい積において整列するであろう。このように、さらなる単結晶材料を形成する。

このようなテンプレートがない状態でたい積されたシリコンは、多結晶シリコンまたはアモルファス・シリコンの形態をとる。これは、周囲の粒子に関してランダムに方向付けられた結晶格子をそれぞれ有する個々の粒子から形成される。

シリコンのこれらの形態は、単結晶シリコンと比較して低い導電率を呈する。したがって、これらをMOSFETの活性領域において使用することは望ましくない。

このように、現在のところ、他の材料、特に、実質的にアモルファスであるか、シリコン格子と一致しない構造を有する酸化シリコンやシリコン酸化窒化物のような従来の絶縁体上に単結晶シリコンを成長させることは、一般的に可能ではなかった。

#### 【0010】

したがって、絶縁デバイス上に半導体を製造するための従来の技術は、小さなクリティカルディメンションを有するデバイスや、歪みシリコンが組み入れられたデバイスを製造するには十分ではない。

#### 【発明の開示】

#### 【0011】

本発明の実施形態は、その上に半導体層を直接成長させることができる絶縁層を含む、SOI (semiconductor on insulator) デバイスを提供する。

絶縁層が半導体材料に引張歪みまたは圧縮歪みを与えるように、絶縁層の特性および半導体層の特性を選ぶことができる。

#### 【0012】

本発明のさらなる実施形態は、上述のようなデバイスを形成する方法を提供する。

本発明の好ましい一実施形態は、ペロブスカイト (perovskite) 格子構造を有する絶縁材料の層を利用する。このペロブスカイト格子は、ダイヤモンド格子半導体を成長させるのに適したテンプレートを提供することができる。

ペロブスカイト格子構造を有している絶縁体の例には、ガドリニウム・スカンデート ( $GdScO_3$ )、ジスプロシウム・スカンデート ( $DyScO_3$ ) のようなレアアース・スカンデート (rare earth scandate) や、ガドリニウムとジスプロシウム・スカンデートの合金 ( $Gd_{1-x}Dy_xScO_3$ ) が含まれる。

レアアース・スカンデートに互換性を有する (compatible) ダイヤモンド格子構造を有している半導体の例には、シリコン、ゲルマニウム、シリコンとゲルマニウムの合金、および砒化ガリウムのようなIII-V型半導体が含まれる。

レアアース・スカンデートと半導体材料の化学量論組成は、レアアース・スカンデートがその上に成長させた半導体材料に引張歪みまたは圧縮歪みを与えるように、設計することができる。

このような絶縁材料は、SOI・MOSFET中の絶縁層として使用することができ、薄い半導体層を絶縁層上に直接成長させることができる。

#### 【発明を実施するための最良の形態】

#### 【0013】

本発明の実施形態によれば、ダイヤモンド格子を有する単結晶半導体材料を、ペロブス

10

20

20

30

40

40

50

カイト格子を有する絶縁層上に成長させることができる。

ダイヤモンド格子を有する半導体は、シリコン、ゲルマニウムおよびシリコンゲルマニウム合金を含んでいる。

閃亜鉛鉱 (zinc blende) 格子と呼ばれることがある一種のダイヤモンド格子を有している化合物半導体はまた、ペロブスカイト格子上に成長させることができ、この出願においてはダイヤモンド格子を有すると考えられるであろう。

このような化合物半導体の一例は、あるII-VIタイプの半導体と同様に、砒化ガリウム (GaAs) のようなIII-Vタイプの半導体を含んでいる。

ペロブスカイト格子構造を有している絶縁体の例には、ガドリニウム・スカンデート ( $GdScO_3$ )、ジスプロシウム・スカンデート ( $DyScO_3$ )、およびガドリニウムおよびジスプロシウム・スカンデート ( $Gd_{1-x}Dy_xScO_3$ ) の合金のような、レアアース・スカンデート化合物が含まれる。

レアアース・スカンデートと半導体材料の化学量論組成は、レアアース・スカンデートがその上に成長させた半導体材料に引張歪みまたは圧縮歪みを与えるように、設計することができる。

#### 【0014】

ある実施形態の一例においては、レアアース・スカンデート・ガドリニウム・スカンデート ( $GdScO_3$ ) の層は、引張り歪みシリコンまたはシリコンゲルマニウム層の成長のための絶縁層および支持層として使用される。

単結晶ガドリニウム・スカンデートは、22から35の誘電率を有しているので、SOI用の優れた絶縁材料である。

#### 【0015】

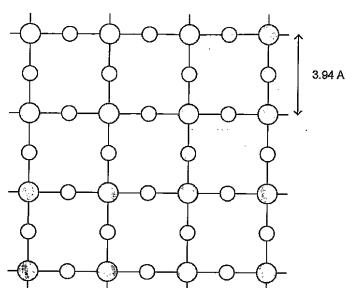

図5aは、ガドリニウム・スカンデート ( $GdScO_3$ ) のペロブスカイト格子中の単位胞 (単位格子) の(001)面 (フェース) を示している。

その理想的な形状において、ペロブスカイト格子は、Pm3m対称性 (Pm3m symmetry) を有している。換言すると、格子の単位胞は、立方体の中心にカチオンのうちの一方 (例えば、Gd) があり、各端部にカチオンのうちの他方 (例えば、Sc) があり、各端部に沿った中心にアニオン (O) を有する立方体である。

ほとんどのペロブスカイト格子において、格子は、格子中における特定の原子により、完全な立方体の形状から多少歪められるが、全体的な構造は同じままである。したがって単位格子の面は、面心原子がなく、実質的に正方形である。

#### 【0016】

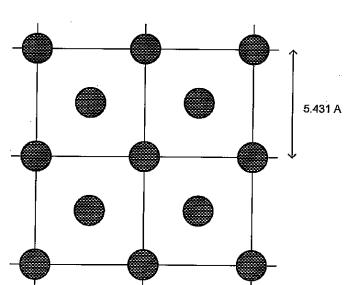

図5bは、シリコンのダイヤモンド格子中の単位胞の(001)面を示している。

ダイヤモンド格子は実質的に、2つの互いに貫入する (interpenetrating) 面心立方格子で構成されており、これらの格子はそれぞれ、3つの空間軸のそれぞれの軸に沿った格子定数の長さの4分の1だけ、他の格子からずれて (オフセットされて) いる。

#### 【0017】

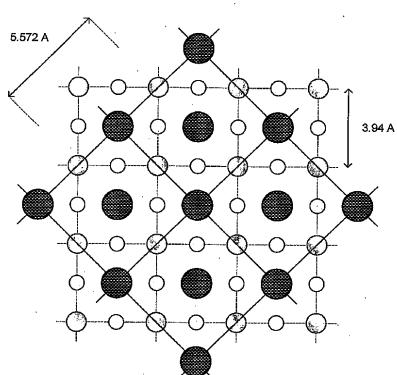

ダイヤモンド格子は、ペロブスカイト格子と構造上異なるが、この2つの格子は、各格子中の原子の間隔に基づきエピタキシャル成長させるという目的において互換性を有する。

図5cに示すように、ガドリニウム・スカンデート格子の(001)平面に対して、シリコン格子の(001)平面を、45°回転させる場合、シリコン・ダイヤモンド格子の面の原子は、ガドリニウム・スカンデート・ペロブスカイト格子の空いている面に沿って並ぶ。

このように、ガドリニウム・スカンデート格子は、シリコンを成長させるためのテンプレートとして役立つことができる。

#### 【0018】

図5aに示すように、ガドリニウム・スカンデート格子の(001)面の格子定数は、3.94である。また、図5bに示すように、緩和シリコン格子の(001)面の格子定数は、5.431である。

しかしながら、ガドリニウム・スカンデート格子中の面の中心部分の間の対角線の距離は、5.572である。これは、純粋な緩和シリコンの格子定数である5.431よりも約2.7%大きい。

比較のため、純粋な緩和ゲルマニウムは、5.657のゲルマニウム格子定数を有している。これはシリコンの格子定数よりも約4.2%大きい。

従来の歪みシリコンデバイスは、シリコンとゲルマニウムの2つ格子定数の値の間にあるとともに格子中のゲルマニウムの量に依存する格子定数を有する、シリコンゲルマニウム $Si_{1-x}Ge_x$ の支持層を使用する。

従来の歪みシリコンデバイスにおいては、ゲルマニウムの比率は一般的に約10%から40%の間にあり、シリコンの格子定数よりも実際上0.9%から1.7%大きい格子定数を有する格子となってしまう。

#### 【0019】

ペロブスカイト格子とダイヤモンド格子の間の格子不整合を特徴づけるべく、本願においては、ペロブスカイト格子の「有効な格子定数」と呼ばれる量を利用する。

実質的に立方体の単位胞を有するペロブスカイト格子では、有効な格子定数は、対角線上に方向付けられる単位胞の面の中心部分の間の距離として定義することができる。

立方体の形状からいくらくら歪められ、このように異なる長さの対角線を備えるダイヤモンド形状の単位胞面を有しているペロブスカイト格子においては、面の中心部分間の対角線の距離は、測定する方向に依存するであろう。

このような場合、有効な格子定数は、面の中心部分間の2つの対角線の距離の平均として定義することができる。

しかしながら、この特性が活用される実施形態においては、他方向の長さと比較して一方向の長さの方を長くする方法で、重なる半導体格子に歪みを与えることが所望される実施例のように、有効な格子定数は、より大きな距離またはより少ない距離の方向において対角線の面の中心部分の間の距離として定義することができる。

#### 【0020】

上述の測定の一例は、 $GdScO_3$ に特有のものである。また、異なる有効な格子定数を備えた他のレアアース・スカンデートは、エピタキシャル半導体格子についてずれの程度を所望のものとするように形成することができる。

例えば、ジスプロシウム・スカンデート( $DyScO_3$ )を代わりに使用することができる。 $DyScO_3$ は、約5.6の有効な格子定数を有している。

さらに他の例では、 $Gd_{1-x}Dy_xScO_3$ のようなレアアース・スカンデート合金を、所望の有効な格子定数を提供するように選択されたガドリニウムおよびジスプロシウムの化学量論比で設計することができる。

一般に、レアアース・スカンデート絶縁体上に引張り歪みシリコンを成長させることを含む使用状況については、レアアース・スカンデートの有効な格子定数は、緩和シリコンの格子定数(5.431)よりも大きいことが好ましく、緩和ゲルマニウムの格子定数(5.657)未満であることが好ましく、40%のゲルマニウムからなる緩和シリコンゲルマニウム合金の格子定数(5.519)未満であることがさらに好ましい。

#### 【0021】

レアアース・スカンデートのようなペロブスカイト格子構造を有する絶縁層の使用することにより、シリコン、ゲルマニウム、シリコンゲルマニウム合金、または化合物半導体材料を絶縁材料上に直接成長させることができる。

シリコンゲルマニウム合金中のシリコンおよびゲルマニウムの比率は、様々な効果を生成するように、絶縁基板の有効な格子定数に関して選択することができる。

例えば、絶縁材料の有効な格子定数よりも小さい格子定数を有するように、シリコンゲルマニウム合金を形成することができ、その結果、シリコンゲルマニウム合金中に所望の量の引張歪みを与えることになるようにしてもよい。

他の例においては、絶縁材料の有効な格子定数よりも大きな格子定数を有するように、シリコンゲルマニウム合金を形成することができ、その結果、シリコンゲルマニウム合金

10

20

30

40

50

上に所望の量の圧縮歪みを与えることになるようにしてよい。

圧縮歪みゲルマニウムはまた、レアアース・スカンデート絶縁体上に成長させることができる。

さらに、所与の有効な格子定数を備えたレアアース・スカンデートの層を有する基板が与えられた場合、引張りおよび圧縮歪み半導体が共存している領域を提供するように、異なる理論混合比を有するシリコンおよびシリコンゲルマニウム合金を、基板上の選択された場所で成長させることができる。

これらは例えば、高い電子移動度を提供する引張り歪みチャネルを有するN M O S デバイスおよび高い正孔移動度を提供する圧縮歪みチャネルを有するP M O S デバイスを含むC M O S デバイスを製造するのに使用することができる。

#### 【0022】

ガドリニウム・スカンデート絶縁層または他のレアアース・スカンデート絶縁層を含むS O I 基板は、多くの方法により製造することができる。

ガドリニウム・スカンデートは、分子線エピタキシーによってたい積することができる。本質的な構成元素のそれぞれのビーム線は、超高真空によって、化学量論の量においてそれらが化学結合する基板部分に向けられる。

また、他の例においては、ガドリニウム・スカンデート・ターゲットを紫外線レーザによって蒸発させ、基板面上に再結晶させる、パルスレーザたい積を使用してよい。

パルスレーザたい積は、より早く成長させることができるために、分子線エピタキシーよりも好みしいものとなり得る。また、化学蒸着法が使用されてもよい。

これらの方法が比較的平坦な表面を有する絶縁層を形成することに注目すべきである。

絶縁層上にその後成長させた半導体層は、研磨により薄くなつた層よりも実質的に厚さのばらつきが少ない。

#### 【0023】

一般的に、レアアース・スカンデート層は、その表面にシリコンゲルマニウム層を有している基板上に形成される。

このシリコンゲルマニウム層は一般的に、ゲルマニウムの含有率が0%から所望の%まで徐々に増加する段階的な方法で、シリコンウェーハ上に成長させられる。この方法は、所望の格子定数を有する緩和シリコンゲルマニウム層を成長できるようにする。

その後、レアアース・スカンデートを、例えば上述した技術のうちの1つによって、シリコンゲルマニウム層上に形成する。

実装によっては、シリコンゲルマニウム層は、レアアース・スカンデートの有効な格子定数と一致するように形成されてもよいし、または、レアアース・スカンデート格子を圧縮するとともにその有効な格子定数を減少させるべく、シリコンゲルマニウム層は、レアアース・スカンデートの有効な格子定数よりも小さい格子定数を有するように形成されてもよい。

#### 【0024】

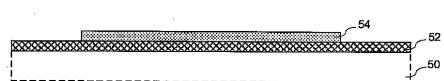

図6aないし図6fは、本発明の実施例の一例による、引張り歪みS O I ・M O S F E T の製造中に形成される構造を示す図である。

図6aは、シリコンゲルマニウム層50含むS O I 基板を示す。上述したように、シリコンゲルマニウム層50は一般的に、シリコンウェーハ上に成長させられ、所望の格子定数を提供する、表面におけるゲルマニウムの含有率を有する傾斜組成を有している。

例えば、ある実施形態の一例においては、シリコンゲルマニウム層の表面は、約20%のゲルマニウムにより構成された緩和シリコンゲルマニウム合金とすることができます。

#### 【0025】

ペロブスカイト格子を有する材料の絶縁層52は、シリコンゲルマニウム層50上に形成される。ある実施形態の一例においては、この絶縁材料は、ガドリニウム・スカンデートのようなレアアース・スカンデートである。

絶縁層52は、分子線エピタキシー、パルスレーザたい積、または化学蒸着法のような様々な技術によって形成することができる。

ある実施形態の一例においては、ガドリニウム・スカンデート層は、100から200の間の厚さに形成される。

【0026】

半導体層54は、絶縁層52上に成長させられる。この半導体層54は、単結晶層であり、シリコン、ゲルマニウム、シリコンゲルマニウム合金、III-VまたはII-VIタイプのような化合物半導体、またはダイヤモンド格子を有する別の半導体から形成することができる。

半導体層の厚さは、特定の実施形態により選択され得る。ある実施形態の一例においては、半導体層は、約200の厚さを有するシリコン層である。

完全空乏型のSOIデバイスでは、半導体層54は一般的にドープされていないが、ドーピングは、特定の実施形態に従って実行されてもよい。

【0027】

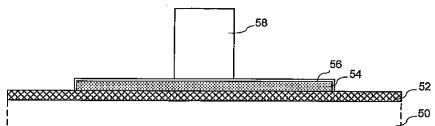

図6bは、その上に個々のデバイスが形成されることになる半導体材料の分離アイランドを形成するように、半導体層54を選択エッチングした後の図6aの構造を示す図である。

【0028】

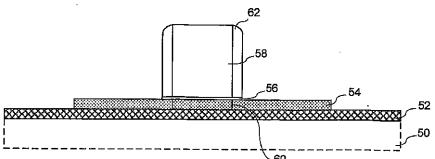

図6cは、半導体層54上にゲート絶縁層56を形成し、ゲート絶縁層56上にポリシリコン・ゲート58をたい積した後の図6bの構造を示す図である。

ゲート絶縁層56は、半導体層54を熱酸化させるか、絶縁材料をたい積することによって成長させることができる。

ポリシリコン・ゲートは、ポリシリコン層を全体的にたい積した後、ポリシリコン層をパターニングすることによって形成してよい。

【0029】

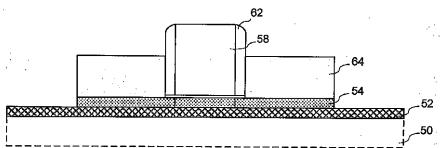

図6dは、ゲート58の両側における半導体層54中にソースおよびドレイン拡張部60を形成すべく、イオン注入によってドーパントを注入し、その後ゲート58の周りにスペーサ62を形成した後の、図6cの構造を示す図である。

ゲート58は、ソースおよびドレイン拡張部60の注入の間、チャネル領域を被覆する。

スペーサ62は、酸化シリコンを全体的にたい積した後、水平面から酸化物を除去するように、方向性のあるエッチバックプロセスを実行することによって形成することができる。

【0030】

図6eは、ゲート58の両側の隣接部分に、半導体層54に接する高いソースおよびドレイン領域64を形成した後の図6dの構造を示す図である。

高いソースおよびドレイン領域64は、シリコンの選択エピタキシャル成長によって成長させることができる。

一般的に、半導体層54上のシリコンの成長率は、周囲の露出した絶縁層52上のシリコンの成長率よりもずっと大きい。さらに、成長室中の雰囲気は一般的に、HClを含んでいる。このHClにより、たい積されたシリコンのエッチングの程度が決まる。

たい積パラメータの制御を通じて、エピタキシャル成長プロセスは、絶縁層52の露出部分上に、実質的に成長量0のシリコンを製造するのに最適化することができる。

他の例では、絶縁層52上に蓄積したシリコンをすべて除去するように、高いソースおよびドレイン領域64を形成した後、短いエッチ・バックを実行してよい。

このソースおよびドレイン領域64は、その場（インサイチュー）で、または注入プロセスによってドープされ得る。

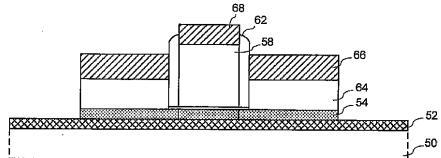

【0031】

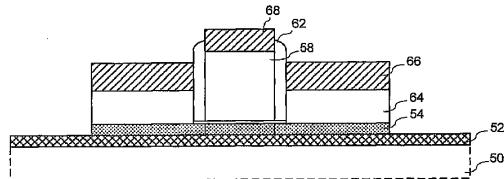

図6fは、ソースおよびドレイン・シリサイド66およびゲート・シリサイド68を形成した後の、図6eの構造を示す図である。

シリサイド66および68は、ゲート58、ソースおよびドレイン領域64のシリコン材料と、コバルト(Co)またはニッケル(Ni)のような金属と、を含む化合物から形成さ

れる。

シリサイド 6 6 および 6 8 は、構造全体の上に金属の薄い共形層をたい積し、金属と下にある半導体材料との間の接点においてシリサイド形成を促進するようにアニーリングし、その後、余った金属を除去することにより形成される。

ソースおよびドレイン領域とゲートのシリサイドが形成されることになっている部分から酸化物と保護材料を除去するパターニング・ステップは、一般的にシリサイドを形成する前に実行される。

#### 【 0 0 3 2 】

図 6 a ないし図 6 f のプロセスは、シリコンゲルマニウムの層上に形成されるレアアース・スカンデートの層からなる SOI 基板を使用している MOSFET 形成の一例を示している。しかしながら、様々な他の MOSFET 構造を形成してもよい。

概略的には、本発明の実施形態による電子デバイスは、ペロブスカイト格子を有する絶縁材料の層を含んでいる基板と、ペロブスカイト材料の層上に形成される単結晶半導体材料の層とを含む。

そのチャネル領域中に半導体を組み入れる MOSFET を、基板上に形成してよい。

MOSFET は、本明細書に記載した方法または他の様々な方法により形成することができる。

半導体材料中に所望の量の引張り歪みまたは圧縮歪みのいずれかを引き起こすように、絶縁材料と半導体材料を設計することができ、この歪みは、絶縁材料中の単位胞の面の形に従って方向づけることができる。

#### 【 0 0 3 3 】

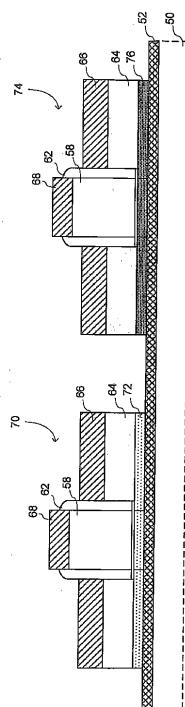

図 7 は、本発明の実施形態により形成された第 1 SOI・MOSFET と第 2 SOI・MOSFET からなる CMOS デバイスの素子の一例を示す図である。

この構造では、n 型 MOSFET デバイス 7 0 に、基板の絶縁層 5 2 上に形成される半導体領域 7 2 が組み入れられている。この半導体領域 7 2 は、絶縁層 5 2 の有効な格子定数よりも低い格子定数を有しており、半導体領域 7 2 に引張歪みを与えるとともに n 型 MOSFET 中の電子の移動度を増加させることになる、第 1 シリコンゲルマニウム合金からできている。

この構造はさらに、基板の絶縁層 5 2 上に形成される半導体領域 7 6 を組み入れられた p 型の MOSFET デバイス 7 4 を含んでいる。

この半導体領域 7 6 は、絶縁層 5 2 の有効な格子定数よりも大きい格子定数を有しており、半導体領域 7 6 に圧縮歪みを与えるとともに p 型 MOSFET 中のホールの移動度を増加させることになる、第 2 シリコンゲルマニウム合金からできている。

n 型 MOSFET および p 型 MOSFET は、絶縁層によって、これらに異なる種類の歪みが与えられる、異なるシリコンゲルマニウム合金を使用することにより、各デバイスのキャリア移動度が増加するという利点を得ることができる、CMOS デバイスを形成するように接続することができる。

#### 【 0 0 3 4 】

図 7 の構造は、様々な方法により製造することができる。

例えば、p 型デバイスおよび n 型デバイスのそれぞれについての、異なる格子定数を有する半導体領域を成長させるのに、2 つの独立した成長ステップを実行することができる。

これらの領域は、デバイス中で利用されるであろう形状に成長させてもよいし、またはこれらの領域を正確な寸法にパターン化してもよい。

他の実施形態においては、合金のうちの 1 つの層をウェーハにわたり成長させることができる。その後、シリコンまたはゲルマニウムを選択した領域に注入してこれらの領域の理論混合比を変更し、第 2 合金を形成してもよい。

#### 【 0 0 3 5 】

図 7 の構造は、n MOS および p MOS デバイスについて異なる種類の歪みを生成すべく、2 つの異なるシリコンゲルマニウム合金を利用しているが、他の実施例においては、

10

20

30

40

40

50

適当な格子定数を有する異なる種類の半導体材料が利用され得る。

さらに、絶縁材料の格子特性は、歪みを方向づけるように形成されてよい。

MOSFETは、図7に示す方法または他の様々な方法で形成することができる。

### 【0036】

上記のプロセスにおいて記載したタスクは、他のタスクを除外するものではない。また、形成されるべき特定の構造により、上述のプロセスにさらなるタスクが組み入れられ得る。例えば、処理タスク間における不動態層または保護材料の形成または除去、フォトレジストマスクおよび他のマスキング層の形成または除去のような中間の処理タスク、ドーピングおよびカウンタドーピング、クリーニング、プレーナ化、および他のタスクを、特に上述したタスクと共に実行することができる。さらに、ウェーハ全体のような基板全面上においてここで記載したプロセスを実行する必要がないが、その代わりに基板の部分上で選択的に実行することができる。さらに、例示のため、ここに記載した構造の製造の間、ある特定の順番にタスクを実行するように記載したが、実施形態によっては、プロセスの目的を達成する他の順番でタスクを実行することができる。このように、図示した上述の実施形態が現在の好ましい一例である一方、これらの実施形態は単なる例示としての記載であることを理解すべきである。本発明は特定の実施形態に制限されず、請求の範囲およびこの等価物の範囲内の、様々な変形例、組合せおよび置換に及ぶ。

10

20

30

40

### 【図面の簡単な説明】

#### 【0037】

【図1】従来の方法により形成された従来のMOSFETを示す図。

【図2】従来のSOI・MOSFETを示す図。

【図3】従来の歪みシリコンMOSFETを示す図。

【図4】従来の技術を使用してSOI基板上に形成された歪みシリコンMOSFETを示す図。

【図5a】ペロブスカイトおよびダイヤモンド格子を示すとともに、これらの格子が互換性を有する手法を示す図。

【図5b】ペロブスカイトおよびダイヤモンド格子を示すとともに、これらの格子が互換性を有する手法を示す図。

【図5c】ペロブスカイトおよびダイヤモンド格子を示すとともに、これらの格子が互換性を有する手法を示す図。

【図6a】本発明の例示的な実施形態の一例により、引張りシリコンSOI・MOSFETを製造する間に形成される構造を示す図。

【図6b】本発明の例示的な実施形態の一例により、引張りシリコンSOI・MOSFETを製造する間に形成される構造を示す図。

【図6c】本発明の例示的な実施形態の一例により、引張りシリコンSOI・MOSFETを製造する間に形成される構造を示す図。

【図6d】本発明の例示的な実施形態の一例により、引張りシリコンSOI・MOSFETを製造する間に形成される構造を示す図。

【図6e】本発明の例示的な実施形態の一例により、引張りシリコンSOI・MOSFETを製造する間に形成される構造を示す図。

【図6f】本発明の例示的な実施形態の一例により、引張りシリコンSOI・MOSFETを製造する間に形成される構造を示す図。

【図7】実施形態の一例による、CMOSデバイスの素子を示す図。

【図1】

Figure 1

Prior Art

【図2】

Figure 2

Prior Art

【図3】

Figure 3

Prior Art

【図4】

Figure 4

Prior Art

【図5a】

Figure 5a

【図5b】

Figure 5b

【図5c】

Figure 5c

【図6a】

Figure 6a

【図 6 b】

Figure 6b

【図 6 e】

Figure 6e

【図 6 c】

Figure 6c

【図 6 f】

Figure 6f

【図 6 d】

Figure 6d

【図 7】

Figure 7

**【手続補正書】**

【提出日】平成17年12月27日(2005.12.27)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】****【特許請求の範囲】****【請求項1】**

ペロブスカイト格子を有する絶縁材料の層(52)を含む基板と、

前記絶縁層上に形成される半導体材料の層(54)と、

そのチャネル領域中に半導体材料の層が組み入れられるMOSFETと、を含み、

前記ペロブスカイト格子を有する絶縁材料(52)は、ガドリニウム・スカンデート(

$GdScO_3$ )、ジスプロシウム・スカンデート( $DyScO_3$ )、およびガドリニウムとジスプロシ

ウム・スカンデートとの合金( $Gd_{1-x}Dy_xScO_3$ )のうちのいずれか1つであるレアアース・

スカンデートである、

SOI (semiconductor on insulator) デバイス。

**【請求項2】**

前記半導体材料の層(54)は、前記ペロブスカイト格子によって引張歪みが与えられるシリコン層である、請求項1記載のデバイス。

**【請求項3】**

前記半導体材料の層(54)は、前記ペロブスカイト格子によって圧縮歪みが与えられるシリコンゲルマニウム層である、請求項1記載のデバイス。

**【請求項4】**

前記半導体材料の層(54)は、ダイヤモンド型格子を有する化合物半導体材料である、請求項1記載のデバイス。

**【請求項5】**

ガドリニウム・スカンデート( $GdScO_3$ )、ジスプロシウム・スカンデート( $DyScO_3$ )、

およびガドリニウムとジスプロシウム・スカンデートとの合金( $Gd_{1-x}Dy_xScO_3$ )のうちの

いずれか1つであるレアアース・スカンデートであるペロブスカイト格子を有する絶縁材

料の層(52)を含む基板を形成し、

前記絶縁材料(52)の前記ペロブスカイト格子の(001)面上に、ダイヤモンド型

格子を有する半導体材料の層(54)を成長させ、

そのチャネル領域中に、前記半導体材料(54)を組み入れたMOSFETを形成する、

SOI (semiconductor on insulator) MOSFETデバイス上に半導体を形成する方法。

**【請求項6】**

ペロブスカイト格子を有する絶縁材料の層(52)を含む基板と、

前記絶縁層(52)上に形成される第1半導体材料(72)の領域であって、前記絶縁層(52)

により引っ張り歪みが与えられる第1半導体材料(72)の領域と、

前記第1半導体材料(72)の領域中に形成され、そのチャネル領域中に、前記第1半

導体材料を組み入れる、第1MOSFET(70)と、

前記絶縁材料の層(52)上に形成される第2半導体材料(76)の領域であって、前記

絶縁層により圧縮歪みが与えられる第1半導体材料(76)の領域と、

前記第2半導体材料(76)の領域中に形成され、そのチャネル領域中に、前記第2半

導体材料を組み入れる、第2MOSFET(74)と、を含む、

SOI (semiconductor on insulator) デバイス。

**【請求項7】**

前記絶縁層(52)は、レアアース・スカンデートである、請求項6記載のデバイス。

**【請求項 8】**

前記第1半導体材料(72)は、前記絶縁材料(52)の有効な格子定数より少ない格子定数を有するシリコンゲルマニウム合金であり、

前記第2半導体材料(76)は、前記絶縁材料(52)の有効な格子定数より大きい格子定数を有するシリコンゲルマニウム合金である、請求項6記載のデバイス。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 | International Application No<br>PCT/US2005/010574                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC 7 H01L29/786                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 |                                                                                |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |                                                                                |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>IPC 7 H01L                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                 |                                                                                |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                                                                                |

| Electronic data base consulted during the international search (name of data base and, where practical, search terms used)<br>EPO-Internal, PAJ, WPI Data, COMPENDEX, INSPEC                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                 |                                                                                |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                                                                                |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Citation of document, with indication, where appropriate, of the relevant passages                              | Relevant to claim No.                                                          |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | US 2003/008521 A1 (BOJARCZUK NESTOR<br>ALEXANDER ET AL)<br>9 January 2003 (2003-01-09)<br>the whole document    | 1-7                                                                            |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | US 2003/047785 A1 (KAWASAKI MASASHI ET AL)<br>13 March 2003 (2003-03-13)<br>page 5, paragraph 67 – paragraph 69 | 1-3, 6, 7                                                                      |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | US 2003/027408 A1 (CURLESS JAY A)<br>6 February 2003 (2003-02-06)<br>the whole document                         | 1-7                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —/—                                                                                                             |                                                                                |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 | <input checked="" type="checkbox"/> Patent family members are listed in annex. |

| * Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier document but published on or after the International filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed |                                                                                                                 |                                                                                |

| Date of the actual completion of the International search<br><br>21 June 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 | Date of mailing of the international search report<br><br>29/06/2005           |

| Name and mailing address of the ISA<br>European Patent Office, P.B. 5018 Patenttaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 661 epo nl<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                 | Authorized officer<br><br>Hoffmann, N                                          |

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US2005/010574

| C.(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category                                             | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                            | Relevant to claim No. |

| X                                                    | US 2002/195599 A1 (YU ZHIYI ET AL)<br>26 December 2002 (2002-12-26)<br>page 1, paragraph 19 – page 2, paragraph 25<br>page 6, paragraph 52<br>page 11, paragraph 91                                                                                                                                                                                                                                                                                           | 1-7                   |

| Y                                                    | US 2002/140031 A1 (RIM KERN)<br>3 October 2002 (2002-10-03)<br>page 2, paragraph 14                                                                                                                                                                                                                                                                                                                                                                           | 1-7                   |

| Y                                                    | LUCOVSKY G ET AL: "Electronic structure of high-k transition metal oxides and their silicate and aluminate alloys" JOURNAL OF VACUUM SCIENCE AND TECHNOLOGY. B, MICROELECTRONICS AND NANOMETER STRUCTURES PROCESSING, MEASUREMENT AND PHENOMENA, AMERICAN INSTITUTE OF PHYSICS, NEW YORK, NY, US, vol. 20, no. 4, July 2002 (2002-07), pages 1739-1747, XP012009458<br>ISSN: 1071-1023<br>page 1741, column 2, paragraph 2 – page 1742, column 1, paragraph 1 | 1-7                   |

| P, X                                                 | WO 2004/061920 A (ADVANCED MICRO DEVICES, INC) 22 July 2004 (2004-07-22)<br>page 8, line 10 – line 17                                                                                                                                                                                                                                                                                                                                                         | 1-6                   |

| P, X                                                 | WO 2004/068585 A (ADVANCED MICRO DEVICES, INC; DAKSHINA-MURTHY, SRIKANTESWARA; AN, JUDY,) 12 August 2004 (2004-08-12)<br>page 4, paragraph 22 – paragraph 28                                                                                                                                                                                                                                                                                                  | 1-10                  |

| A                                                    | LIM SEUNG-GU ET AL: "Dielectric functions and optical bandgaps of high-K dielectrics for metal-oxide-semiconductor field-effect transistors by far ultraviolet spectroscopic ellipsometry" JOURNAL OF APPLIED PHYSICS, AMERICAN INSTITUTE OF PHYSICS. NEW YORK, US, vol. 91, no. 7, 1 April 2002 (2002-04-01), pages 4500-4505, XP012056135<br>ISSN: 0021-8979<br>page 4500, column 2, paragraph 2                                                            | 1-10                  |

| A                                                    | SCHUBERT J ET AL: "Structural and optical properties of epitaxial BaTiO <sub>3</sub> thin films grown on GdScO <sub>3</sub> (110)" APPLIED PHYSICS LETTERS, AMERICAN INSTITUTE OF PHYSICS. NEW YORK, US, vol. 82, no. 20, 19 May 2003 (2003-05-19), pages 3460-3462, XP012034126<br>ISSN: 0003-6951<br>table 1                                                                                                                                                | 1-10                  |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No

PCT/US2005/010574

| Patent document cited in search report |    | Publication date |    | Patent family member(s) |  | Publication date |

|----------------------------------------|----|------------------|----|-------------------------|--|------------------|

| US 2003008521                          | A1 | 09-01-2003       | US | 2003008520 A1           |  | 09-01-2003       |

|                                        |    |                  | US | 2005095815 A1           |  | 05-05-2005       |

| US 2003047785                          | A1 | 13-03-2003       | JP | 2003086808 A            |  | 20-03-2003       |

|                                        |    |                  | CN | 1405898 A               |  | 26-03-2003       |

|                                        |    |                  | TW | 552718 B                |  | 11-09-2003       |

| US 2003027408                          | A1 | 06-02-2003       | WO | 03015141 A1             |  | 20-02-2003       |

| US 2002195599                          | A1 | 26-12-2002       | TW | 527631 B                |  | 11-04-2003       |

|                                        |    |                  | WO | 03001564 A2             |  | 03-01-2003       |

| US 2002140031                          | A1 | 03-10-2002       | CA | 2501580 A1              |  | 10-10-2002       |

|                                        |    |                  | CN | 1500288 A               |  | 26-05-2004       |

|                                        |    |                  | EP | 1410428 A1              |  | 21-04-2004       |

|                                        |    |                  | JP | 2005510039 T            |  | 14-04-2005       |

|                                        |    |                  | TW | 222098 B                |  | 11-10-2004       |

|                                        |    |                  | WO | 02080241 A1             |  | 10-10-2002       |

| WO 2004061920                          | A  | 22-07-2004       | US | 6730576 B1              |  | 04-05-2004       |

|                                        |    |                  | AU | 2003286810 A1           |  | 29-07-2004       |

|                                        |    |                  | WO | 2004061920 A2           |  | 22-07-2004       |

| WO 2004068585                          | A  | 12-08-2004       | US | 2004145019 A1           |  | 29-07-2004       |

|                                        |    |                  | US | 2004195627 A1           |  | 07-10-2004       |

|                                        |    |                  | WO | 2004068585 A1           |  | 12-08-2004       |

## フロントページの続き

| (51)Int.Cl.                     | F I          | テーマコード(参考) |

|---------------------------------|--------------|------------|

| <b>H 01 L 21/8238 (2006.01)</b> | H 01 L 27/12 | D          |

| <b>H 01 L 27/092 (2006.01)</b>  | H 01 L 27/12 | E          |

| <b>H 01 L 27/08 (2006.01)</b>   | H 01 L 21/20 |            |

|                                 | H 01 L 27/08 | 3 2 1 B    |

|                                 | H 01 L 27/08 | 3 3 1 E    |

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,L,U,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SM,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(74)代理人 100108604

弁理士 村松 義人

(72)発明者 キ シャン

アメリカ合衆国、カリフォルニア州 9 5 1 2 9、サン ノゼ、テムズ ドライブ 1 1 1 9

F ターム(参考) 5F048 AC04 BA10 BA14 BA15 BA16 BB05 BB08 BB12 BC01 BC06

BC15 BC16 BD01 BD09 BF06 BF16 DA25

5F110 AA30 BB04 CC02 DD05 DD12 EE09 EE32 GG01 GG02 GG03

GG04 GG06 GG12 GG25 GG42 HJ13 HK05 HK09 HK13 HK21

HK32 HK40 HM02

5F152 LN07 LN08 LN19 MM04 MM19 NN04 NP11 NQ03 NQ05 NQ10