## (19) 대한민국특허청(KR)

## (12) 특허공보(B1)

(51) Int. Cl.<sup>5</sup>

H01L 23/48

(45) 공고일자 1995년01월11일

(11) 공고번호 95-000205

---

|           |               |           |               |

|-----------|---------------|-----------|---------------|

| (21) 출원번호 | 특1986-0007396 | (65) 공개번호 | 특1987-0004509 |

| (22) 출원일자 | 1986년09월04일   | (43) 공개일자 | 1987년05월11일   |

---

|            |                                                                                                                         |

|------------|-------------------------------------------------------------------------------------------------------------------------|

| (30) 우선권주장 | 60-221832 1985년10월07일 일본(JP)                                                                                            |

| (71) 출원인   | 가부시기이사 히다찌세이사꾸쇼 미다 가쓰시게<br>일본국 도오교도 지요다구 간다 스루가다이 4-6히다찌 마이크로컴퓨터엔<br>지니어링 가부시기이사 가모시다 겐이찌<br>일본국 도오교도 고다이라시 죠스이촌 1479번지 |

|          |                                                 |

|----------|-------------------------------------------------|

| (72) 발명자 | 하기와라 야스히사<br>일본국 도오교도 미다가시무레 1-5-14<br>마스다 마사지가 |

| (74) 대리인 | 일본국 도오교도 고다이라시 나가마찌 489-1 202<br>백남기            |

심사관 : 김정국 (책자공보 제3843호)

---

(54) 리이드 프레임 및 이를 사용한 반도체 장치

---

**요약**

내용 없음.

**대표도****도1****영세서**

[발명의 명칭]

리이드 프레임 및 이를 사용한 반도체 장치

[도면의 간단한 설명]

제 1 도는 본 발명의 실시예 1인 리이드 프레임에 펠릿 와이어 본딩이 실시된 것을 도시한 확대부분 평면도.

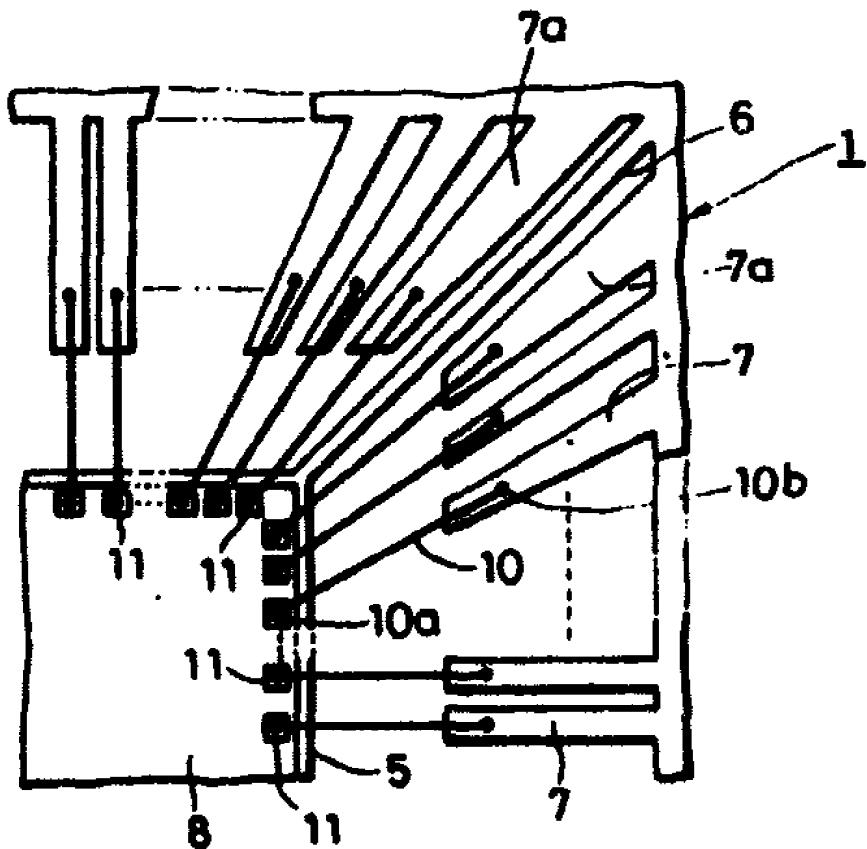

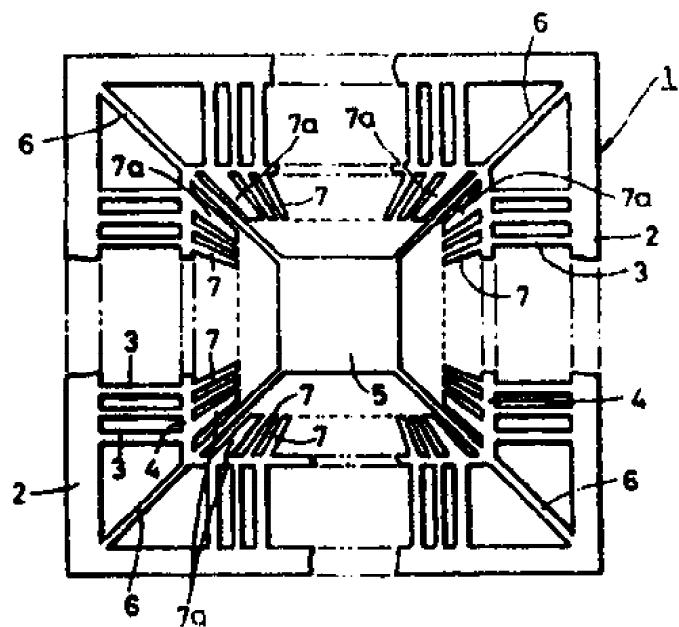

제 2 도는 실시예 1의 리이드 프레임의 전체를 도시한 평면도.

제 3 도는 실시예 1의 리이드 프레임을 사용한 반도체 장치를 도시한 전체 단면도.

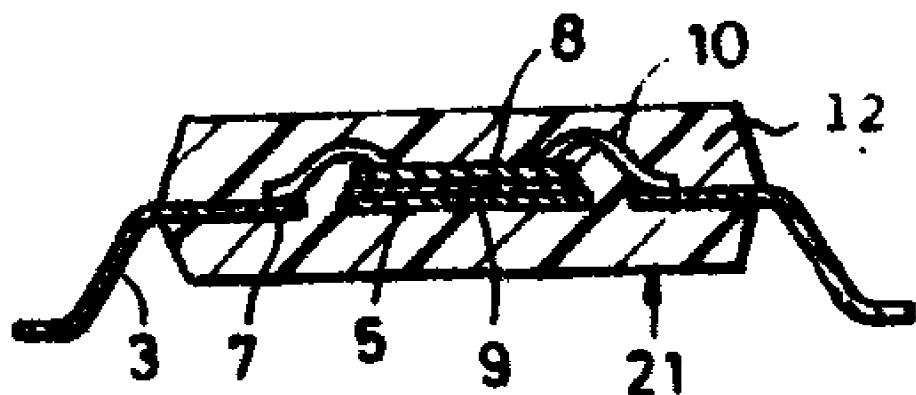

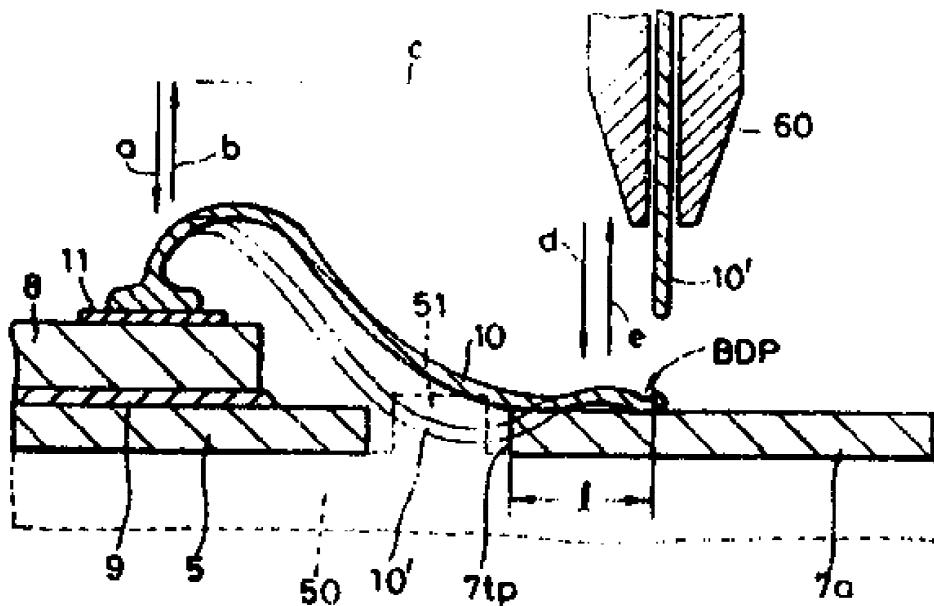

제 4 도는 본딩시의 리이드 프레임 및 그 주변의 단면도.

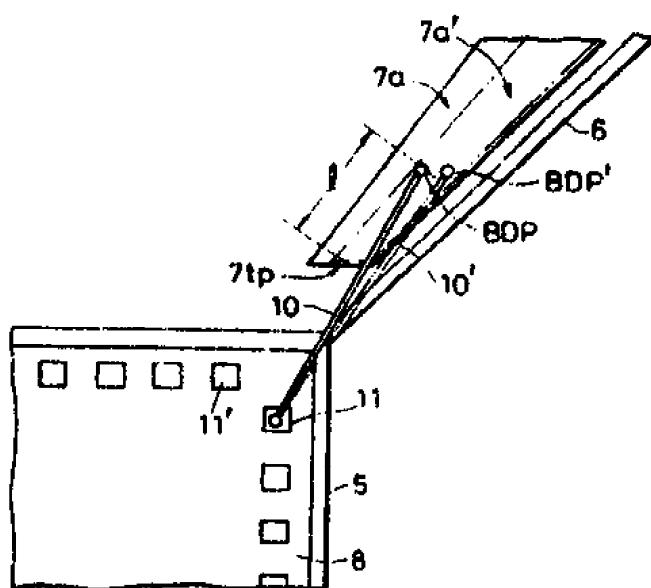

제 5 도는 본딩시의 리이프 프레임의 평면도.

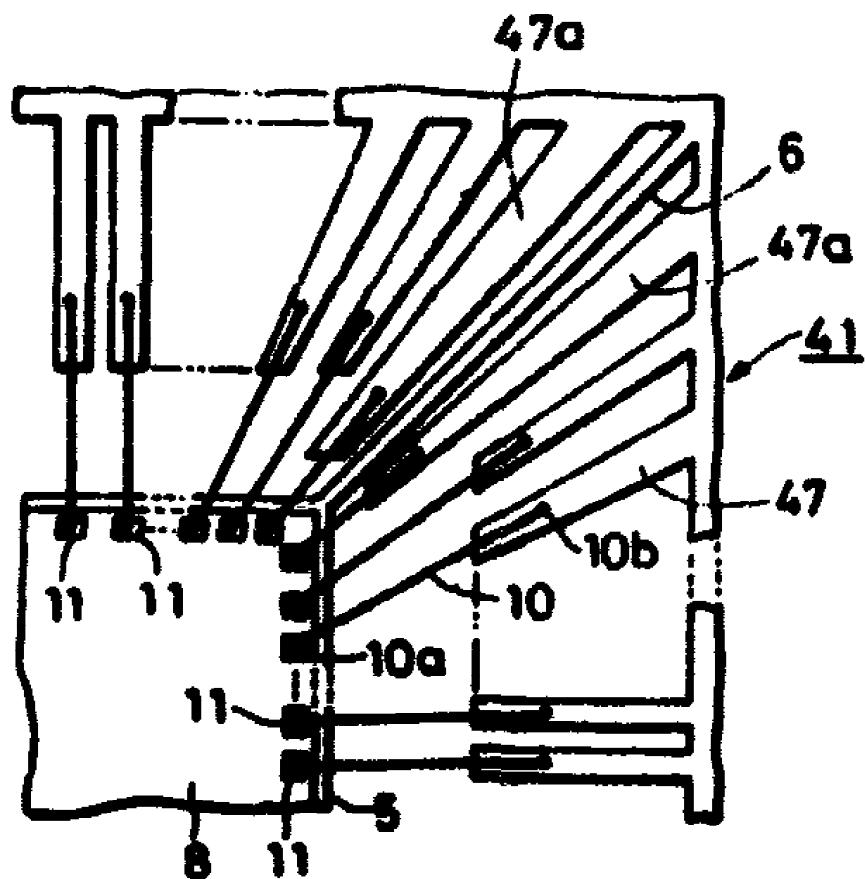

제 6 도는 본 발명의 실시예 2인 리이드 프레임에 펠릿 본딩, 와이어 본딩이 실시된 것을 도시한 확대부분 평면도.

[발명의 상세한 설명]

본 발명은 리이드 프레임 및 이를 사용한 반도체 장치에 관한 것으로, 특히 반도체 장치의 제조공정에 있어서의 와이어 본딩의 높은 신뢰성 및 작업성 향상이 도모되는 유효한 기술에 관한 것이다.

펠릿과 내부 리이드의 전기적 도통을 도모하는 기술의 하나로서, 소위 와이어 본딩법이 있다. 이 와이어 본딩법에서는, 예를들어 우선 금(Au)과 같은 금속으로 되는 본딩 와이어의 선단부분을 방전가공, 수소(H<sub>2</sub>) 토오지(torch) 등에 의해 가열하여 용융하고, 그 선단부분에 볼(ball)을 형성하고, 그 볼부분을 펠릿의 본딩패드전극에 눌러서 제 1본딩을 실행한다. 다음에, 상기 와이어가 루프를 형성하도록 본딩용 캐필러리를 내부 리이드위의 소정의 부위에 위치시키고, 본딩 와이어를 내부 리이드에 누르는 것에 의해서 제 2본딩을 실행한다. 최후로, 본딩 와이어의 나머지 부분을 절단하여 본딩을 완료하는 것이다.

그런데, 플래트 패키지(flat package)형의 반도체 장치에 사용되는 리이드 프레임인 경우, 탭의 모서리 부분에 탭서스펜딩 리이드(이하, 탭걸이 리이드라 한다)가 배치되어 있고, 다 핀화를 포함하는

내부 리이드(여러개의 내부 리이드가 마련되어 있는 것)에서는 텁의 모서리 부분 근방, 즉 텁걸이 리이드(텅을 리이드 프레임의 프레임에 연결하여 텁을 지지하고 있는 리이드)에 가깝게 마련되어 있는 내부 리이드와 펠릿의 패드전극과의 거리가 크게 떨어지게 되므로, 이에 따라서 본딩 와이어의 인장거리도 길어지게 된다. 이로 인해, 본딩 와이어에 느슨함을 일으키기 쉽고, 본딩 와이어와 다른 내부 리이드 또는 본딩 와이어와 텁걸이 리이드 등과의 전기적 쇼트를 일으키기 쉬운 것이 본 발명자에 의해서 발견되었다.

또 텁걸이 리이드에 인접해서 마련되어 있는 내부 리이드가 다른 내부 리이드와 같은 리이드폭 및 같은 리이드 길이를 갖고 있지 않을 경우의 와이어 본딩시는 상기 리이드 프레임에 있어서의 텁모서리 부분에 결합하고 있는 텁걸이 리이드 가까이의 내부 리이드 위쪽에서 본딩 와이어가 떨어지는 일이 일어난다. 이로인해, 제 2본딩에 의한 와이어의 지지가 불충분하게 되고, 이것이 와이어의 느슨함의 한 원인이 되는 것도 본 발명자에 의해서 명확하게 되었다.

그리고, 와이어 본딩의 기술로서 상세하게 기술되어 있는 예로써는 일본국 (주)공업조사회, 1980년 1월 15일 발행, 「IC화 실장 기술」(일본국 Microelectronics 협회편), p99~p103이 있다.

본 발명의 목적은 와이어 본딩시의 와이어의 쇼트를 방지하여 신뢰성을 높일 수가 있는 리이드 프레임을 제공하는데 있다.

본 발명의 다른 목적은 전기적으로 신뢰성이 높은 반도체 장치를 제공하는데 있다.

본 발명의 상기 및 그외의 목적과 새로운 특징은 본 명세서의 기술 및 첨부도면에서 명확하게 될 것이다.

본 출원에 있어서 개시되는 발명중 대표적인 것의 개요를 간단히 설명하면 다음과 같다.

즉, 텁걸이 리이드에 인접해서 마련된 내부 리이드의 폭 또는 길이가 다른 내부 리이드보다 크게 되도록 형성되는 리이드 프레임 구조로 하는 것에 의해 제 2본딩에 있어서 와이어의 지지가 충분하게 되므로, 본딩을 확실하게 실행할 수가 있어 와이어의 쇼트의 발생을 방지할 수가 있다.

또, 상기 기술에 의해 전기적 신뢰성이 높은 반도체 장치를 제공할 수가 있다.

#### [실시예 1]

제 1 도는 본 발명의 1실시예인 리이드 프레임에 펠릿 본딩, 와이어 본딩이 실시된 것을 도시한 확대부분 평면도, 제 2 도는 리이드 프레임의 전체를 도시한 평면도, 제 3 도는 이 리이드 프레임을 사용한 반도체 장치를 도시한 전체 단면도, 제 4 도는 본딩시의 리이드 프레임 및 그 주변부분의 단면도이다.

본 실시예 1의 리이드 프레임(1)은 특별히 제한되지 않으나, 제 3 도에 도시한 것과 같은 수지 봉지형의 플래트 패키지, 소위 FPP(Flat Plastic Package)형의 반도체 장치(21)에 사용되는 리이드 프레임이며, 제 2 도에 도시한 형상의 것을 1단위로 하여 좌우 양방향으로 여려단위를 연결한 형상으로 되는 것이다.

리이드 프레임(1)은 사각형상의 프레임부(2)와 그 프레임부(2)의 각변에서 중앙방향으로 각각 연장되어 마련된 여러개의 리이드(3) 및 그 각 리이드의 도중부분을 서로 연결하는 타이 바(tie bar)(4)를 갖고 있다. 또, 리이드 프레임(1)의 중앙부분에는 사각형상의 텁(5)이 형성되어 있고, 이 텁(5)은 그 4개의 모서리와 상기 프레임부(2)의 4개의 모서리를 각각 연결하는 텁걸이 리이드(6)에 의해서 지지되어 있다. 상기 타이 바(4)에 둘러싸인 리이드(3)의 부분은 내부 리이드(7)를 형성하고 있으며, 이 내부 리이드(7)의 적어도 선단부분의 표면에는 본딩을 양호하게 실행하기 위하여 금(Au)등의 도시하지 않은 도금층이 형성되어 있다. 본 실시예 1에 따르면, 상기 텁걸이 리이드(6)에 인접해서 마련되는 내부 리이드(7a)는 제 1 도와 같은 다른 내부 리이드(7)보다도 폭이 넓게 형성되어 있다.

이와같은 리이드 프레임(1)은, 예를들면 동(Cu), 니켈 42%, 철(Fe) 58%의 합금인 42합금 또는 철 53%, 니켈 28%, 코발트 18%로 되는 합금인 코발(coval) 등으로 되는 얇은 판상의 금속판에 에칭처리 또는 프레스처리 등을 실시하여 소정의 형상으로 가공하는 것에 의해서 얻어지는 것이다.

이와같이 하여 얻어진 리이드 프레임(1)에는 우선 그 텁(5) 위에 실리콘 반도체로 되는 펠릿(8)이 접착제(9)에 의해서 피착된다.

이와같은 펠릿이 피착된 리이드 프레임은 다음에 도시하지 않은 와이어 본딩장치의 본딩 스테이지 위에 탑재되어 금(Au) 등으로 되는 가는선 형상의 본딩 와이어(10)에 의해 펠릿(8)의 본딩 패드전극(11)과 내부 리이드(7)의 결선, 즉 와이어 본딩이 실행된다. 이 와이어 본딩 공정에서는 우선 상기 와이어(10)의 한쪽끝을 방전가공 등에 의해 가열 용융하는 것에 의해서 볼이 형성된다. 다음에, 와이어를 지지하는 본딩용 캐필러리(와이어 접속 공구)(60)이 반도체 펠릿의 본딩 패드(11)위로 이동되어 제 4도의 화살표 a와 같이 강하된다. 이로 인해서, 볼(10a)부분이 패드(11)에 압착되어 제 1본딩이 실행된다.

다음에, 와이어(10)이 루프를 형성하도록 캐필러리(60)이 이동되어 제 2본딩이 실행된다. 즉, 제 1본딩후에 캐필러리(60)이 제 4 도의 화살표 b로 나타낸 바와같이 상승되어 화살표 c로 나타낸 바와같이 내부 리이드(7a)의 본딩 에리어를 향해서 수평 이동되며, 이어서 화살표 d로 나타낸 바와같이 하강된다.

와이어(10)를 내부 리이드(7a)에 열압착시키는 누르는 힘이 캐필러리(60)에 의해서 와이어(10)에 가해지고, 그 결과 와이어 본딩이 실행된다. 그후, 캐필러리(60)이 제 4 도의 화살표 e와 같이 상승된다. 이때 와이어 본딩장치에 있어서의 도시하지 않은 와이어 클램프 기구가 동작되고, 캐필러리(60)쪽의 와이어(10')는 그 와이어 클램프 기구에 의해서 인장응력이 가해져서 제 4 도에 도시한 바와

같이 전단(shear)된다.

이로 인해서, 1사이클의 본딩 공정이 완료된다. 이상의 공정 소정회수만큼 반복하는 것에 의해서 필요로 하는 모든 패드(11)와 내부 리이드(7)가 접속되게 된다.

본 실시예 1에 의하면, 텁걸이 리이드(6)에 인접해서 마련된 내부 리이드(7a)가 상술한 것과 같이 다른 리이드(7)보다도 폭이 넓게 형성되어 있다. 따라서, 제 2본딩시에 그 내부 리이드(7a)에 대해서 루프를 추적하면서 착지되는 와이어(10)에 대하여 충분한 접촉 폭을 확보할 수가 있다. 따라서, 텁걸이 리이드(6)에 인접해서 마련된 내부 리이드(7a)에 결합되는 와이어에 일어나기 쉬운 와이어(10)의 늘어짐을 효과적으로 방지할 수가 있어 와이어(10)의 쇼트의 발생을 방지할 수가 있다.

와이어(10)의 쇼트 방지에 대하여 제 4 도의 단면도 및 제 5 도의 평면도에 따라서 상세하게 설명하면 다음과 같이 된다.

즉, 내부 리이드(7a)의 선단(7tp)에서 내부 리이드(7a)의 본딩 위치 BDP까지의 평면부분 거리 / 은 와이어(10)의 루프형상의 바라지 않는 변형을 방지하는데 유효한 부분으로 된다. 본 실시예와 같은 텁걸이 리이드(6)에 인접하는 내부 리이드(7a)의 폭이 넓게 되어 있는 경우, 와이어(10)는 반도체 펠릿(8)의 본딩되어야 할 패드(11)의 위치가 다소 변경되어도 제 5 도에 실선으로 도시한 바와같이 내부 리이드의 선단위를 통과하게 된다. 이 경우는 와이어(10)의 본딩시의 리이드 쪽으로의 루프가 부분 /에 대해서 양호하게 제한된다. 그 결과, 와이어(10)는 제 4의 실선으로 나타낸 바와같이, 실질적으로 리이드의 평면보다 위부분에만 위치되게 되어 바라지 않는 쇼트를 일으키는 일이 없다.

이에 대해서, 내부 리이드(7a)가 제 5 도에 2점 쇄선으로 나타낸 바와같이, 좁은 폭을 갖도록 되어 있을 경우, 즉 종래의 리이드 프레임에 있어서의 경우, 이때에 마련되는 와이어(10')는 제 5 도의 점선으로 나타낸 바와같이, 패드(11)의 위치의 약간의 변경에 대해서도 내부 리이드의 선단부 위를 벗어나서 연장되게 된다. 이 경우, 내부 리이드의 부분 /은 와이어(10')의 루프의 바람직하지 않는 변형을 충분히 방지할 수가 없게된다. 이것에 따라서, 와이어(10')는 제 4 도에 2점 쇄선으로 나타낸 바와같이, 리이드의 주면보다 아래쪽으로 연장하는 루프를 형성할 우려가 생긴다.

그리고, 와이어 본딩시에 내부 리이드의 선단과 텁(5)의 둘레의 공간에 돌기를 배치하는 것은 와이어의 루프의 바라지 않는 변형을 방지하는데 의미가 있다. 제 4 도에 있어서, 점선(50)은 와이어 본딩장치에 있어서의 워크 스테이션 또는 리이드 프레임용 테이블로서의 히트 블록(heat block)을 도시하고 있다. 이 경우의 히트 블록은 상술의 목적은 돌기(51)를 갖는다. 텁걸이 리이드(6)에서 떨어진 내부 리이드와 패드를 결합하는 본딩 와이어는 만약 내부 리이드의 폭이 좁아도 그 루프 형상이 돌기(51)에 대해서 양호하게 된다. 이 경우, 텁걸이 리이드(6)에 인접하는 내부 리이드와 패드를 결합하는 와이어에 대한 돌기(51)의 효과는 다음의 이유에 대해서 실질적으로 기대할 수 없다.

즉, 돌기(51)에 대한 텁걸이 리이드(6)의 위치는, 예를들면 워크 스테이션에 대한 리이드 프레임의 위치 맞춤정도에 대해서 영향을 받게 된다. 텁걸이 리이드(6)의 위치의 다소의 변동에도 불구하고 텁걸이 리이드(6)가 돌기(51)에 걸리지 않도록 하기 위하여 돌기(51)은 그것과 텁걸이 리이드(6) 사이에 비교적 큰 공간이 생기도록 크게 된다. 그 결과로서, 텁걸이 리이드(6)에 인접하는 내부 리이드(7a)와 텁(5)와의 사이에 돌기(51)를 연장시키는 것이 곤란하게 되므로, 그 리이드(7a)에 결합되는 와이어의 형상을 돌기(51)로 규정하여 성형할 수는 없다.

다음의 공정으로서 와이어 본딩이 완료된 리이드 프레임(1)은 트랜스퍼 몰드(transfer mold)법에 의해 에폭시 수지(12)로 수지봉지되고, 패키징이 실행된후, 각 리이드(3)가 독립상태로 절단·성형되어서 제 3 도에 도시한 FPP형의 반도체 장치(21)을 얻을 수가 있다.

## [실시예 2]

제 6 도는 본 발명의 다른 실시예인 리이드 프레임을 도시한 확대부분 평면도이다.

본 실시예 2의 리이드 프레임(41)은 실시예 1에서 설명한 리이드 프레임(1)과 대략 마찬가지이지만, 그 차이점은 텁걸이 리이드(6)에 인접해서 마련된 내부 리이드(47a)의 형상을 다르게 한 것이다.

즉, 이 리이드 프레임(41)에서는 텁걸이 리이드(6)에 인접해서 마련된 내부 리이드(47a)가 다른 내부 리이드(47)보다 축방향에 대해서 길게 형성되고, 그 리이드 선단은 텁(5)의 아주 가까이까지 연장되어 있다. 구체적으로는 내부 리이드(47a)와 텁의 떨어지는 거리가 다른 내부 리이드와 텁의 떨어지는 거리에 비해서 동일하던가, 그 이하의 길이이다. 이로 인해, 와이어 본딩을 할 때에는 와이어(10)의 인장거리를 짧게 할 수가 있다. 따라서, 텁걸이 리이드(6)에 인접해서 마련된 내부 리이드(47a)에 일어나기 쉬운 와이어(10)의 늘어짐을 방지할 수가 있어 와이어의 쇼트를 방지하여 전기적 신뢰성이 높은 반도체 장치를 제공할 수가 있다.

본 발명은 다음에 기술하는 여러 가지 효과가 있다.

(1) 텁걸이 리이드에 인접하여 마련된 내부 리이드가 다른 내부 리이드보다 와이어와의 본딩 면적이 크도록 형성되는 리이드 프레임 구조로 하는 것에 의해 제 2본딩에 있어서 와이어의 착지시에 충분한 활주거리를 확보할 수가 있으므로, 본딩을 확실하게 실행할 수가 있어 와이어의 쇼트를 방지할 수가 있다.

(2) 텁걸이 리이드에 인접해서 마련된 내부 리이드가 다른 리이드보다도 길게 하여 이루어지는 리이드 프레임 구조로 하는 것에 의해, 본딩 와이어의 루프길이를 짧게 할 수 있다. 이로 인해, 인접하는 리이드와 본딩 와이어와의 쇼트를 방지할 수가 있다.

(3) 상기 (1), (2)에 의해, 전기적 신뢰성이 높은 반도체 장치를 제공할 수가 있다.

(4) 상기 (1), (2)에 의해 내부 리이드가 미세화되었을 경우에 있어서도 텁걸이 리이드에 인접해서 마련된 내부 리이드에서의 와이어의 늘어짐을 방지할 수가 있으므로, 와이어 본딩의 신뢰성을 향상

시켜서 반도체 장치의 높은 집적화를 촉진할 수가 있다.

이상 본 발명자에 의해서 이루어진 발명을 실시예에 따라서 구체적으로 설명하였으나, 본 발명은 상기 실시예에 한정되는 것은 아니며, 그 요지를 이탈하지 않는 범위에서 여러 가지로 변경이 가능하다는 것을 말할 것도 없다.

예를들면, 텁걸이 리이드에 인접해서 마련된 내부 리이드의 형상으로서 폭 또는 축 방향길이를 크게 한 경우에 대해서만 설명하였으나, 이러한 형상에 한정하지 않으며, 어떠한 형상이라도 면적을 크게 한 것이면 좋다.

또, 실시예에서는 FPP형의 반도체 장치에 사용되는 리이드 프레임에 대해서만 설명하였으나, 이에 한정되지 않으며, 외부 리이드를 J자 형상으로 성형하는 소위 PLCC(Plastic leaded Chip Carrier)형의 반도체 장치에 사용되는 리이드 프레임이라도 좋다.

또한, 본딩 방법에 대해서도 와이어 본딩 애너지가 초음파 진동만으로 와이어의 접합을 실행하는 소위 웨지 본딩이라도 좋다.

실시예와 같이, 텁걸이 리이드(6)에 인접하는 내부 리이드(7a)의 폭을 증대시키는 경우에는 그것에 따라서 내부 리이드(7a)에 대한 본딩 가능 범위를 넓게 설정할 수가 있게 된다. 이로 인해서, 반도체 펠릿의 본딩되어야 할 패드 전극의 위치가 변경되었을 경우에도 이에 따라서 내부 리이드(7a)의 본딩 위치를 변경할 수가 있게 되어 와이어가 내부 리이드(7a)의 선단부 위를 통과하도록 할 수가 있다.

그러나, 이러한 내부 리이드(7a)는, 예를들면 부채형, T자형의 평면 패턴과 같이 실질적으로 그 선단부만이 폭이 넓혀져도 좋다. 이 경우에도 와이어 루프의 바라지 않는 형상을 없앨 수가 있다.

이상의 설명에서는 주로 본 발명자에 의해서 이루어진 발명을 그 이용분야인, 소위 수지 봉지형의 반도체 장치에 적용한 경우에 대해서 설명하였으나, 이에 한정되는 것은 아니며, 예를들면 저용점의 유리 등을 봉지재로 사용한 기밀봉지형의 반도체 장치에 적용하여도 유효한 기술이다.

### (57) 청구의 범위

#### 청구항 1

템에 연결되고, 그곳에서 멀어지는 방향을 향해서 연장하는 적어도 3개의 텁걸이 리이드, 제 1의 면에 여려개의 본딩패드를 갖고, 제 2의 면에서 상기 텁에 접착되어 있는 반도체칩, 각각이 텁의 주변 근방에 위치하는 자유단을 갖는 내부 리이드부와 외부 리이드부로 이루어지는 여려개의 리이드, 상기 본딩패드와 상기 자유단사이를 각각 전기적으로 접속하고 있는 본딩 와이어 및 상기 칩, 텁, 내부 리이드부, 본딩 와이어를 통하여 막고 있는 봉지재를 포함하는 반도체 장치에 있어서, 상기 내부 리이드부는 텁과 동일평면에 있으며, 적어도 각각의 자유단에서 가는 리이드와 상기 텁걸이 리이드의 근방에 배치되어 있는 폭이 넓은 리이드로 이루어지는 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 2

특허청구의 범위 제 1 항에 있어서, 상기 봉지재는 수지인 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 3

특허청구의 범위 제 1 항에 있어서, 상기 봉지재는 기밀봉지체인 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 4

특허청구의 범위 제 1항에 있어서, 상기 봉지재는 판형상의 봉지체이고, 상기 칩, 텁, 내부 리이드부 및 본딩 와이어를 포함하는 평면에 평행한 1쌍의 주면을 갖는 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 5

특허청구의 범위 제 1 항 내지 제 4 항중의 어느 한 항에 있어서, 각각의 텁걸이 리이드 근방의 모두가 폭이 넓은 리이드이고, 그 이외는 가는 리이드인 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 6

특허청구의 범위 제 1 항에 있어서, 상기 텁과 텁걸이 리이드는 금속시이트에 의해서 일체로 성형되어 있는 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 7

특허청구의 범위 제 1 항에 있어서, 상기 텁걸이 리이드는 각각 서로 직행하는 3개의 다른 방향을 향해서 연장하고 있는 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 8

특허청구의 범위 제 1 항에 있어서, 상기 텁은 4각형상이고, 3개의 텁걸이 리이드는 텁의 모서리부에서 멀어지는 방향을 향해서 연장하고 있는 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 9

특허청구의 범위 제 8 항에 있어서, 4개의 텁걸이 리이드가 4개의 모서리부에서 멀어지는 방향을 향

해서 연장하고 있는 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 10

특허청구의 범위 제 1 항 또는 제 2 항에 있어서, 상기 텁과 상기 폭이 넓은 리아드의 거리는 텁과 상기 가는 리아드의 거리와 동일하던가 또는 짧은 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 11

특허청구의 범위 제 5 항에 있어서, 상기 폭이 넓은 리아드는 상기 가는 리아드와 비교해서 폭이 넓은 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 12

특허청구의 범위 제 6 항 내지 제 9 항중의 어느 한 항에 있어서, 상기 폭이 넓은 리아드는 상기 가는 리아드와 비교해서 폭이 넓은 것을 특징으로 하는 반도체집적회로장치.

#### 청구항 13

특허청구의 범위 제 10 항에 있어서, 상기 폭이 넓은 리아드는 상기 가는 리아드와 비교해서 폭이 넓은 것을 특징으로 하는 반도체집적회로장치.

#### 도면

##### 도면1

도면2

도면3

도면4

도면5

도면6