# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(11) 공개번호 10-2009-0101173(43) 공개일자 2009년09월24일

(51) Int. Cl.

**HO3M 13/11** (2006.01)

(21) 출원번호10-2009-7012084(22) 출원일자2007년12월11일

심사청구일자 **없음**

(85) 번역문제출일자 2009년06월11일

(86) 국제출원번호 PCT/IL2007/001528

(87) 국제공개번호 WO 2008/075337 국제공개일자 2008년06월26일

(30) 우선권주장

11/876,868 2007년10월23일 미국(US) 60/870,396 2006년12월17일 미국(US) (71) 출원인

**라모트 앳 텔-아비브 유니버시티 리미티드** P.0박스 39296, 61392 텔아비브, 이스라엘

(72) 발명자

샤론 에란

이스라엘 75493 리숀 레지온 하다간 16/1

리친 시몬

이스라엘 54423 기바트 슈무엘 즈보울룬 하머

5/30

(74) 대리인

박종혁, 김정욱, 정삼영, 송봉식

전체 청구항 수 : 총 127 항

# (54) LDPC 디코딩을 위한 래지 스케줄링

# (57) 요 약

복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션의 디코더는 반복적으로 소프트 비트를 갱신하기 위한 복수의 기능 모듈을 포함한다. 각각의 소프트 비트가 적어도 몇몇 반복에 참가하는지 여부는 선택 기준에 따라, 예컨대, 확률적으로, 또는, 반복 횟수에 따라, 또는 소프트 비트의 반복 히스토리에 따라 결정된다. 예를 들어, 각각의 소프트 비트는 반복 횟수, 및 소프트 비트의 신뢰도 측정값 모두의 함수인 확률로 일부 또는 모든 반복에 참가할 수 있다. 바람직하게는, 기능 모듈은 대응 체크 노드와 메시지를 교환하기 위해 순차적으로 가변 노드를 어드레싱하는 LDPC 기능 모듈이다. 디코더는 메모리의 회로, 메모리 디바이스의 컨트롤러, 또는 메모리 디바이스의 호스트 내에 구현될 수 있다.

# 대표도

# 특허청구의 범위

#### 청구항 1

복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더로서,

적어도 하나의 디코딩 반복에서 상기 소프트 비트를 갱신하기 위한 복수의 기능 모듈을 포함하고,

각각의 상기 디코딩 반복에서, 각각의 소프트 비트에 대하여, 상기 각각의 소프트 비트가 상기 각각의 디코딩 반복에 참가하는지 여부가 선택 기준에 따라 결정되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드 워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 2

제 1 항에 있어서, 상기 복수의 기능 모듈은

- a) 상기 각각의 가변 노드에 대하여, 상기 각각의 가변 노드가 상기 각각의 디코딩 반복에 참가하는지 여부를 상기 선택 기준에 따라 결정되도록, 각각의 가변 노드에 각각의 소프트 비트를 할당하는 가변 노드 할당 모듈;

- b) 각각의 상기 디코딩 반복에서, 상기 가변 노드가 상기 각각의 디코딩 반복에 참가하는지 여부를 결정하기 위한 가변 노드 선택 모듈;

- c) 각각의 상기 디코딩 반복에서, 각각의 상기 참가하는 가변 노드에 대하여: 복수의 체크 노드 중 각각의 하위 노드(subplurality)의 각각의 맴버에 대하여: 각각의 체크-노드-투-가변-노드 메시지를 계산하기 위한 제1메시 지 패싱 모듈;

- d) 각각의 상기 디코딩 반복에서, 상기 제1메시지 패싱 모듈로부터 상기 각각의 디코딩반복에서 수신된 상기 체크-노드-투-가변-노드 메시지에 따라, 각각의 상기 참가하는 가변 노드의 상기 각각의 소프트 비트를 갱신하는 소프트 비트 갱신 모듈; 및

- e) 각각의 상기 디코딩 반복에서, 각각의 상기 참가하는 가변 노드에 대하여, 상기 각각의 참가하는 가변 노드의 체크 노드의 상기 각각의 하위노드 내의 각각의 상기 체크 노드에 대하여 각각의 가변-노드-투-체크-노드 메시지를, 상기 제1메시지 패싱 모듈로부터 가장 최근에 수신된 상기 체크-노드-투-가변-노드에 따라, 계산하는 제2메시지 패싱 모듈을 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

#### 청구항 3

제 1 항에 있어서, 상기 복수의 기능 모듈은 상기 디코딩이 수렴했는지 여부를, 상기 갱신에 응답하여, 결정하기 위한 수렴 체크 모듈을 더 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠 테이션을 디코딩하는 디코더.

# 청구항 4

제 1 항에 있어서, 상기 선택 기준은 개연적(probabilistic) 선택 기준인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 5

제 4 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 시작점에서 상기 각각의 소프트 비트의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

#### 청구항 6

제 5 항에 있어서, 상기 신뢰도 측정값은 상기 각각의 소프트 비트의 절대값인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 7

제 4 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 디코더에 의해 수신된 상기 각각의 소프트 비트의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 8

제 7 항에 있어서, 상기 신뢰도 측정값은 상기 각각의 소프트 비트의 절대값인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 9

제 4 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 일련번호의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프 리젠테이션을 디코딩하는 디코더.

#### 청구항 10

제 4 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 소프트 비트의 참가 히스토리의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 11

제 10 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 상기 디코딩 반복이 얼마나 많이 경과되었는지를 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 12

제 10 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 경과된 시간을 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩 하는 디코더.

# 청구항 13

제 1 항에 있어서, 상기 선택 기준은 상기 각각의 디코딩 반복의 일련번호의 함수인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 14

제 1 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 15

제 14 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 상기 디코딩 반복이 얼마나 많이 경과하였는지를 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 16

제 14 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 경과된 시간을 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더.

# 청구항 17

통신 수신기로서,

a) 채널로부터 수신된 메시지를 복조하고, 그로 인해 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션

을 제공하는 변조기;

b) 상기 코드워드 리프리젠테이션을 디코딩하기 위한 청구항 제1항의 디코더를 포함하는 것을 특징으로 하는 통 신 수신기.

# 청구항 18

통신 시스템으로서,

- a) 청구항 제17항의 통신 수신기;

- b) 상기 채널; 및

- c) 상기 채널을 통해 메시지를 상기 통신 수신기로 전송하는 전송기를 포함하는 통신 시스템.

#### 청구항 19

메모리 디바이스로서.

- a) 메모리;

- b) 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션으로, 상기 메모리에 데이터를 저장하고, 상기 메모리로부터 상기 데이터를 추출하는 회로; 및

- c) 상기 코드워드 리프리젠테이션을 디코딩하기 위한 청구항 제1항의 디코더를 포함하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 20

복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 디코더로서,

적어도 하나의 디코딩 반복의 각각에서, 상기 소프트 비트의 적어도 일부분을 순차적으로 갱신하기 위한 복수의 기능 모듈을 포함하고,

하나의 상기 디코딩 반복에서, 상기 소프트 비트의 일부분만이 갱신되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 디코더.

# 청구항 21

제 20 항에 있어서, 상기 복수의 기능 모듈은

- a) 각각의 소프트 비트를 각각의 가변 노드에 할당하는 가변 노드 할당 모듈; 및

- b) 상기 가변 노드와 그 가변 노드의 복수의 체크 노드 중 각각의 하위노드 사이에서 메시지를 교환하는 적어도 하나의 메시지 패싱 모듈을 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테 이션을 디코딩하기 위한 디코더.

#### 청구항 22

복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 디코더로서,

적어도 하나의 디코딩 반복에서 상기 소프트 비트를 갱신하기 위한 복수의 기능 모듈을 포함하고,

상기 각각의 소프트 비트가 상기 각각의 디코딩 반복에 참가하는 기간은, 각각의 상기 디코딩 반복에서, 각각의 소프트 비트에 대하여, 선택 기준에 따라 결정되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워 드 리프리젠테이션을 디코딩하기 위한 디코더.

#### 청구항 23

제 22 항에 있어서, 상기 선택 기준은 개연적 선택 기준인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 디코더.

#### 청구항 24

제 22 항에 있어서, 상기 선택 기준은 상기 각각의 디코딩 반복의 일련 번호의 함수인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 디코더.

## 청구항 25

제 22 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 디코더.

#### 청구항 26

제 22 항에 있어서, 상기 복수의 기능 모듈은

- a) 각각의 소프트 비트를 다이렉티드 태너 그래프의 각각의 가변 노드에 할당하는 가변 노드 할당 모듈; 및

- b) 상기 다이렉티드 태너 그래프의 에지를 따라 메시지를 패싱하기 위한 적어도 하나의 메시지 패싱 모듈을 포 한하고.

각각의 상기 메시지는 상기 각각의 에지의 상기 가변 노드에 할당된 상기 소프트 비트에 관련되어 있고, 각각의 상기 디코딩 반복에서, 상기 다이렉티드 태너 그래프의 각각의 상기 에지에 대하여, 상기 각각의 에지를 따라 상기 메시지를 패싱할 것인지 여부가, 상기 선택 기준에 따라, 결정되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 디코더.

#### 청구항 27

제 26 항에 있어서, 하나의 상기 디코딩 반복에서, 상기 메시지는 상기 메시지가 상기 태너 그래프의 적어도 하나의 체크 노드 에지를 따라 패싱된 후 상기 태너 그래프의 적어도 하나의 가변 노드 에지를 따라 패싱되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 디코더.

#### 청구항 28

제 26 항에 있어서, 하나의 상기 디코딩 반복에서, 상기 적어도 하나의 메시지 패싱 모듈은 두개의 상기 메시지를 병렬로 패싱하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기위한 디코더.

# 청구항 29

- a) 코드워드를 저장하기 위한 비휘발성 메모리 셀의 어레이; 및

- b) 상기 비휘발성 메모리 셀의 어레이로부터 상기 코드워드의 리프리젠테이션을 디코딩하기 위한 회로를 포함하고.

상기 리프리젠테이션은 적어도 하나의 디코딩 반복에서 상기 소프트 비트를 갱신함으로써 복수의 소프트 비트를 포함하고, 상기 각각의 소프트 비트가 상기 각각의 디코딩 반복에서 참가하는지 여부는, 각각의 상기 소프트 비 트에 대하여, 각각의 상기 디코딩 반복에서, 선택 기준에 따라 결정되는 것을 특징으로 하는 메모리.

# 청구항 30

제 29 항에 있어서, 상기 회로는 상기 코드워드의 상기 리프리젠테이션을

- i) 상기 각각의 가변 노드가 상기 각각의 디코딩 반복에 참가하는지 여부가, 각각의 상기 가변 노드에 대하여, 상기 선택 기준에 따라 결정되도록, 각각의 가변 노드에 각각의 상기 소프트 비트를 할당하는 단계; 및

- ii) 각각의 상기 참가하는 가변 노드에 대하여, 각각의 상기 디코딩 반복에서:

- A) 각각의 체크-노드-투-가변-노드 메시지를, 복수의 체크 노드 중 각각의 하위노드의 각각의 맴버로부터 상기 각각의 참가하는 가변 노드로 패싱하는 단계,

- B) 상기 각각의 참가하는 가변 노드의 체크 노드의 상기 각각의 하위노드로부터 가장 최근에 수신된 상기 체크-노드-투-가변-노드 메시지에 따라 상기 각각의 참가하는 가변 노드의 상기 각각의 소프트 비트를 갱신하는 단계, 및

- C) 각각의 가변-노드-투-체크-노드 메시지를, 상기 각각의 참가하는 가변 노드로부터 그것의 체크 노드

의 상기 각각의 하위노드의 각각의 맴버로 패성하는 단계를 포함하는 단계에 의해 디코딩하도록 동작하는 것을 특징으로 하는 메모리.

#### 청구항 31

제 29 항에 있어서, 상기 선택 기준은 개연적 선택 기준인 것을 특징으로 하는 메모리.

#### 청구항 32

제 31 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 시작점에서 상기 각각의 소프트 비트의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 메모리.

# 청구항 33

제 32 항에 있어서, 상기 신뢰도 측정값은 상기 각각의 소프트 비트의 절대값인 것을 특징으로 하는 메모리.

#### 청구항 34

제 31 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 디코더에 의해 수신된 상기 각각의 소프트 비트의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 메모리.

# 청구항 35

제 34 항에 있어서, 상기 신뢰도 측정값은 상기 각각의 소프트 비트의 절대값인 것을 특징으로 하는 메모리.

# 청구항 36

제 31 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 일련번호의 함수 인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 메모리.

# 청구항 37

제 31 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 소프트 비트의 참가 히스토리의함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 메모리.

# 청구항 38

제 37 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 얼마나 많은 상기 디코딩 반복이 경과하였는지를 포함하는 것을 특징으로 하는 메모리.

# 청구항 39

제 37 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 경과된 시간을 포함하는 것을 특징으로 하는 메모리.

#### 청구항 40

제 29 항에 있어서, 상기 선택 기준은 상기 각각의 디코딩 반복의 일련 번호의 함수인 것을 특징으로 하는 메모리.

# 청구항 41

제 29 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 메모리.

# 청구항 42

제 41 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 얼마나 많은 상기 디코딩 반복이 경과하였는지를 포함하는 것을 특징으로 하는 메모리.

# 청구항 43

제 41 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 경과된 시간을 포함하는 것을 특징으로 하는 메모리.

# 청구항 44

제 29 항에 있어서, c) 상기 메모리에 저장될 데이터를 상기 코드워드로 인코딩하는 회로를 더 포함하는 것을 특징으로 하는 메모리.

# 청구항 45

메모리로서,

- a) 코드워드를 저장하기 위한 비휘발성 메모리 셀의 어레이; 및

- b) 상기 비휘발성 메모리 셀의 어레이로부터 수신된 상기 코드워드의 리프리젠테이션을 디코딩하는 회로를 포함 하고,

상기 리프리젠테이션은 각각의 적어도 하나의 디코딩 반복에서 상기 소프트 비트의 적어도 일부분을 순차적으로 갱신하는 단계를 포함하는 단계에 의해 복수의 소프트 비트를 포함하고, 하나의 상기 디코딩 반복에서 상기 소 프트 비트의 일부분 만이 갱신되는 것을 특징으로 하는 메모리.

## 청구항 46

제 45 항에 있어서,

- i) 각각의 상기 소프트 비트를 각각의 가변 노드에 할당하는 회로; 및

- b) 각각의 상기 디코딩 반복에서: 적어도 두 개의 상기 가변 노드 각각에 대하여, 순차적으로, 상기 각각의 가변 노드와, 복수의 체크 노드 중 각각의 하위노드 사이에서 메시지를 교환하는 단계를 포함하는 단계에 의해 상기 소프트 비트를 갱신하는 회로를 포함하고, 하나의 상기 디코딩 반복에서, 상기 메시지는 오직 상기 가변 노드의 일부분과 체크 노드의 상기 각각의 하위노드 사이에서 교환되는 것을 특징으로 하는 메모리.

#### 청구항 47

- a) 코드워드를 저장하기 위한 비휘발성 메모리 셀의 어레이; 및

- b) 상기 비휘발성 메모리 셀의 어레이로부터 수신된 상기 코드워드의 리프리젠테이션을 디코딩하는 회로를 포함하고, 상기 리프리젠테이션은 적어도 하나의 디코딩 반복에서 상기 소프트 비트를 갱신함으로써 복수의 소프트 비트를 포함하고, 상기 각각의 소프트 비트가 상기 각각의 디코딩 반복에 참가하는 기간은, 각각의 상기 디코딩 반복에서, 각각의 상기 소프트 비트에 대하여, 선택 기준에 따라 결정되는 것을 특징으로 하는 메모리.

# 청구항 48

제 47 항에 있어서, 상기 선택 기준은 개연적 선택 기준인 것을 특징으로 하는 메모리.

#### 청구항 49

제 47 항에 있어서, 상기 선택 기준은 각각의 상기 각각의 디코딩 반복의 일련번호의 함수인 것을 특징으로 하는 메모리.

#### 청구항 50

제 47 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 메모리.

# 청구항 51

제 47 항에 있어서, 상기 회로는

i) 각각의 상기 소프트 비트를 다이렉티드 태너 그래프의 각각의 가변 노드에 할당하는 회로; 및

ii) 각각의 상기 디코딩 반복에서, 상기 다이렉티드 태너 그래프의 각각의 에지에 대하여: 상기 각각의 에지가 상기 각각의 에지의 상기 가변 노드에 할당된 상기 소프트 비트에 관한 메시지를 상기 각각의 에지를 따라 패싱 함으로써 상기 각각의 디코딩 반복에 참가하는지 여부를 상기 선택 기준에 따라 결정하는 단계를 포함하는 단계 의해 상기 소프트 비트를 갱신하는 회로를 포함하는 것을 특징으로 하는 메모리.

#### 청구항 52

제 51 항에 있어서, 하나의 상기 디코딩 반복에서, 상기 다이렉티드 태너 그래프의 적어도 하나의 가변 노드 에지는 상기 다이렉티드 태너 그래프의 적어도 하나의 체크 노드 에지가 상기 하나의 디코딩 반복에 참가한 후 상기 하나의 디코딩 반복에 참가하는 것을 특징으로 하는 메모리.

#### 청구항 53

제 51 항에 있어서, 하나의 상기 디코딩 반복에서, 상기 소프트 비트를 갱신하는 회로는 두개의 상기 메시지를 병렬로 패싱하는 것을 특징으로 하는 메모리.

#### 청구항 54

메모리 디바이스로서,

- a) 코드워드를 저장하기 위한 비휘발성 메모리; 및

- b) 상기 비휘발성 메모리로부터 상기 코드워드의 리프리젠테이션을 수신하도록, 그리고 적어도 하나의 디코딩 반복에서 상기 소프트 비트를 갱신함으로써 상기 코드워드의 상기 리프리젠테이션을 디코딩하도록 동작하는 컨트롤러를 포함하고, 상기 리프리젠테이션은 복수의 소프트 비트를 포함하고, 상기 각각의 소프트 비트가 상기 각각의 디코딩 반복에 참가하는지 여부는, 각각의 상기 디코딩 반복에서, 각각의 상기 소프트 비트에 대하여, 선택 기준에 따라 결정되는 것을 특징으로 하는 메모리 디바이스.

#### 청구항 55

제 54 항에 있어서, 상기 컨트롤러는 상기 코드워드의 상기 리프리젠테이션을

- i) 상기 각각의 가변 노드가 상기 각각의 디코딩 반복에 참가하는지 여부가, 각각의 상기 가변 노드에 대하여, 상기 선택 기준에 따라 결정되도록, 각각의 가변 노드에 각각의 상기 소프트 비트를 할당하는 단계; 및

- ii) 각각의 상기 디코딩 반복에서, 각각의 상기 참가하는 가변 노드에 대하여:

- A) 각각의 체크-노드-투-가변-노드 메시지를, 복수의 체크 노드 중 각각의 하위노드의 각각의 맴버로부터 상기 각각의 참가하는 가변 노드로 패싱하는 단계,

- B) 상기 각각의 참가하는 가변 노드의 체크 노드의 상기 각각의 하위노드로부터 가장 최근에 수신된 상기 체크-노드-투-가변-노드 메시지에 따라 상기 각각의 참가하는 가변 노드의 상기 각각의 소프트 비트를 갱신하는 단계, 및

- C) 각각의 가변-노드-투-체크-노드 메시지를, 상기 각각의 참가하는 가변 노드로부터 그것의 체크 노드의 상기 각각의 하위노드의 각각의 맴버로 패성하는 단계를 포함하는 단계에 의해 디코딩하도록 동작하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 56

제 54 항에 있어서, 상기 선택 기준은 개연적 선택 기준인 것을 특징으로 하는 메모리 디바이스.

# 청구항 57

제 56 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 시작점에서 상기 각각의 소프트 비트의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 메모리 디바이스.

#### 청구항 58

제 57 항에 있어서, 상기 신뢰도 측정값은 상기 각각의 소프트 비트의 절대값인 것을 특징으로 하는 메모리 디

바이스.

#### 청구항 59

제 56 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 디코더에 의해 수신된 상기 각각의 소프트 비트의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 메모리 디바이스.

#### 청구항 60

제 59 항에 있어서, 상기 신뢰도 측정값은 각각의 상기 소프트 비트의 절대값인 것을 특징으로 하는 메모리 디바이스.

# 청구항 61

제 56 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 일련번호의 함수 인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 62

제 56 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 소프트 비트의 참가 히스토리의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 63

제 62 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 얼마나 많은 상기 디코딩 반복이 경과하였는지를 포함하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 64

제 62 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 경과된 시간을 포함하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 65

제 54 항에 있어서, 상기 선택 기준은 상기 각각의 디코딩 반복의 일련 번호의 함수인 것을 특징으로 하는 메모리 디바이스.

#### 청구항 66

제 54 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 메모리 디바이스.

#### 청구항 67

제 66 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 얼마나 많은 상기 디코딩 반복이 경과하였는지를 포함하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 68

제 66 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 경과된 시간을 포함하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 69

제 54 항에 있어서, 상기 컨트롤러는 상기 메모리에 상기 코드워드로 저장될 데이터를 인코딩하도록 더 동작하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 70

메모리 디바이스로서,

- a) 코드워드를 저장하기 위한 비휘발성 메모리; 및

- b) 상기 비휘발성 메모리로부터 상기 코드워드의, 복수의 소프트 비트를 포함하는 리프리젠테이션을 수신하도록, 그리고 각각의 적어도 하나의 디코딩 반복에서 상기 소프트 비트의 적어도 일부분을 순차적으로 갱신하는 단계를 포함하는 단계에 의해 상기 코드워드의 상기 리프리젠테이션을 디코딩하도록 동작하는 컨트롤러를 포함하고, 하나의 상기 디코딩 반복에서, 상기 소프트 비트의 일부분만 갱신되는 것을 특징으로 하는 메모리디바이스.

#### 청구항 71

제 70 항에 있어서, 상기 컨트롤러는

- i) 각각의 상기 소프트 비트를 각각의 가변 노드에 할당하도록, 그리고

- ii) 적어도 하나의 디코딩 반복에서: 각각의 적어도 두개의 상기 가변 노드에 대하여, 순차적으로: 상기 각각의 가변 노드와 복수의 체크 노드의 각각의 하위노드 사이에서 메시지를 교환하는 단계를 포함하는 단계에 의해 상기 소프트 비트를 갱신하도록 동작하고, 하나의 상기 디코딩 반복에서, 상기 메시지는 오직 상기 가변 노드의 일부분과 체크 노드의 상기 각각의 하위노드 사이에서 교환되는 것을 특징으로 하는 메모리 디바이스.

# 청구항 72

메모리 디바이스로서,

- a) 코드워드를 저장하기 위한 비휘발성 메모리; 및

- b) 상기 비휘발성 메모리로부터 상기 코드워드의, 복수의 소프트 비트를 포함하는 리프리젠테이션을 수신하도록, 그리고 적어도 하나의 디코딩 반복에서 상기 코드워드의 상기 리프리젠테이션을 디코딩하도록 동작하는 컨트롤러를 포함하고, 상기 각각의 소프트 비트가 상기 각각의 디코딩 반복에 참가하는 기간은, 각각의 상기 소프트 비트에 대하여, 각각의 상기 디코딩 반복에서, 선택 기준에 따라 결정되는 것을 특징으로 하는 메모리 디바이스.

#### 청구항 73

제 72 항에 있어서, 상기 선택 기준은 개연적 선택 기준인 것을 특징으로 하는 메모리 디바이스.

# 청구항 74

제 72 항에 있어서, 상기 선택 기준은 상기 각각의 디코딩 반복의 일련번호의 함수인 것을 특징으로 하는 메모리 디바이스.

# 청구항 75

제 72 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 메모리 디바이스.

# 청구항 76

제 72 항에 있어서, 상기 컨트롤러는

- i) 각각의 상기 소프트 비트를 다이렉티드 태너 그래프의 각각의 가변 노드에 할당하도록, 그리고

- ii) 각각의 상기 디코딩 반복에서: 상기 다이렉티드 태너 그래프의 각각의 에지에 대하여: 상기 에지가 상기 각각의 에지의 상기 가변 노드에 할당된 상기 소프트 비트에 관련된 메시지를 상기 각각의 에지를 따라 패싱함으로써 상기 각각의 디코딩 반복에 참가하는지 여부를 상기 선택 기준에 따라 결정하는 단계를 포함하는 단계에 의해 상기 소프트 비트를 갱신하도록 동작하는 것을 특징으로 하는 메모리 디바이스.

# 청구항 77

제 76 항에 있어서, 하나의 상기 디코딩 반복에서, 상기 다이렉티드 태너 그래프의 적어도 하나의 가변 노드는 상기 다이렉티드 태너 그래프의 적어도 하나의 체크 노드가 상기 하나의 디코빙 단복에 참가한 후 상기 적어도 하나의 디코딩 반복에 참가하는 것을 특징으로 하는 메모리 디바이스.

#### 청구항 78

제 76 항에 있어서, 하나의 상기 디코딩 반복에서, 상기 컨트롤러는 두개의 상기 메시지를 병렬로 패싱하는 것을 특징으로 하는 메모리 디바이스.

#### 청구항 79

- a) 메모리 디바이스; 및

- b) 상기 메모리 디바이스로부터 복수의 소프트 비트를 포함하는 리프리젠테이션을 수신하도록, 그리고 적어도 하나의 디코딩 반복에서 상기 소프트 비트를 갱신함으로써 상기 코드워드의 상기 리프리젠테이션을 디코딩하도록 동작하는, 상기 메모리 디바이스의, 호스트를 포함하고, 상기 각각의 소프트 비트가 상기 각각의 디코딩 반복에 참가하는지 여부는, 각각의 상디 디코딩 반복에서, 각각의 상기 소프트 비트에 대하여, 선택 기준에 따라 결정되는 것을 특징으로 하는 시스템.

#### 청구항 80

제 79 항에 있어서, 상기 호스트는 상기 코드워드의 리프리젠테이션을

- i) 상기 각각의 가변 노드가 상기 각각의 디코딩 반복에 참가하는지 여부가, 각각의 상기 가변 노드에 대하여, 상기 선택 기준에 따라 결정되도록, 각각의 가변 노드에 각각의 상기 소프트 비트를 할당하는 단계; 및

- ii) 각각의 상기 디코딩 반복에서, 각각의 상기 참가하는 가변 노드에 대하여:

- A) 각각의 체크-노드-투-가변-노드 메시지를, 복수의 체크 노드의 각각의 하위노드의 각각의 맴버로부터 상기 각각의 참가하는 가변 노드로 패싱하는 단계,

- B) 상기 각각의 참가하는 가변 노드의 체크 노드의 상기 각각의 하위노드로부터 가장 최근에 수신된 상기 체크-노드-투-가변-노드 메시지에 따라 상기 각각의 참가하는 가변 노드의 상기 각각의 소프트 비트를 갱신하는 단계, 및

- C) 각각의 가변-노드-투-체크-노드 메시지를, 상기 각각의 참가하는 가변 노드로부터 그것의 체크 노드의 상기 각각의 하위노드의 각각의 맴버로 패성하는 단계를 포함하는 단계에 의해 디코딩하는 프로세서를 포함하는 것을 특징으로 하는 시스템.

# 청구항 81

제 79 항에 있어서, 상기 선택 기준은 개연적 선택 기준인 것을 특징으로 하는 시스템.

# 청구항 82

제 81 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 시작점에서 상기 각각의 소프트 비트의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 시스템.

# 청구항 83

제 82 항에 있어서, 상기 신뢰도 측정값은 상기 각각의 소프트 비트의 절대값인 것을 특징으로 하는 시스템.

# 청구항 84

제 81 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 호스트에 의해 수신된 상기 소프트 비트의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 시스템.

#### 청구항 85

제 84 항에 있어서, 상기 신뢰도 측정값은 상기 각각의 소프트 비트의 절대값인 것을 특징으로 하는 시스템.

# 청구항 86

제 81 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 일련번호의 함수

인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 시스템.

#### 청구항 87

제 81 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 소프트 비트의 참가 히스토리의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 시스템.

#### 청구항 88

제 87 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 얼마나 많은 상기 디코딩 반복이 경과하였는지를 포함하는 것을 특징으로 하는 시스템.

#### 청구항 89

제 87 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 경과된 시간을 포함하는 것을 특징으로 하는 시스템.

#### 청구항 90

제 79 항에 있어서, 상기 선택 기준은 상기 각각의 디코딩 반복의 일련 번호의 함수인 것을 특징으로 하는 시스템.

# 청구항 91

제 79 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 시스템.

# 청구항 92

제 91 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후에 얼마나 많은 상기 디코딩 반복이 경과하였는지를 포함하는 것을 특징으로 하는 시스템.

#### 청구항 93

제 91 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후 경과된 시간을 포함하는 것을 특징으로 하는 시스템.

# 청구항 94

제 79 항에 있어서, 상기 호스트는 또한 상기 메모리 디바이스에 상기 코드워드로 저장될 데이터를 인코딩하도록 더 동작하는 것을 특징으로 하는 시스템.

# 청구항 95

- a) 메모리 디바이스; 및

- b) 상기 메모리 디바이스로부터 코드워드의, 복수의 소프트 비트를 포함하는, 리프리젠테이션을 수신하도록, 그리고 각각의 적어도 하나의 디코딩 반복에서 상기 소프트 비트의 적어도 일부분을 순차적으로 갱신하는 단계를 포함하는 단계에 의해 상기 코드워드의 상기 리프리젠테이션을 디코딩하도록 동작하는, 상기 메모리 디바이스의, 호스트를 포함하고, 하나의 상기 디코딩 반복에서, 상기 소프트 비트의 일부분만이 갱신되는 것을 특징으로 하는 시스템.

# 청구항 96

제 95 항에 있어서, 상기 호스트는

- i) 각각의 상기 소프트 비트를 각각의 가변 노드에 할당하도록, 그리고

- ii) 적어도 하나의 디코딩 반복에서: 각각의 적어도 두개의 상기 가변 노드에 대하여, 순차적으로: 상기 각각의 가변 노드와 복수의 체크 노드의 각각의 하위노드 사이에서 메시지를 교환하는 단계를 포함하는 단계에 의해 상 기 소프트 비트를 갱신하도록 동작하고, 하나의 상기 디코딩 반복에서, 상기 메시지는 오직 상기 가변 노드의

일부분과 체크 노드의 상기 각각의 하위노드 사이에서 교환되는 것을 특징으로 하는 시스템.

# 청구항 97

- a) 메모리 디바이스; 및

- b) 상기 메모리 디바이스로부터 코드워드의, 복수의 소프트 비트를 포함하는, 리프리젠테이션을 수신하도록, 그리고 적어도 하나의 디코딩 반복에서 상기 소프트 비트를 갱신하는 단계에 의해 상기 리프리젠테이션을 디코딩 하도록 동작하는, 상기 메모리 디바이스의, 호스트를 포함하고, 상기 각각의 소프트 비트가 상기 각각의 디코딩 반복에 참가하는 기간은, 각각의 상기 디코딩 반복에서, 각각의 상기 소프트 비트에 대하여, 선택 기준에 따라 결정되는 것을 특징으로 하는 시스템.

# 청구항 98

제 97 항에 있어서, 상기 선택 기준은 개연적 선택 기준인 것을 특징으로 하는 시스템.

#### 청구항 99

제 97 항에 있어서, 상기 선택 기준은 상기 각각의 디코딩 반복의 일련번호의 함수인 것을 특징으로 하는 시스템.

#### 청구항 100

제 97 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 시스템.

# 청구항 101

제 97 항에 있어서, 상기 호스트는

- i) 각각의 상기 소프트 비트를 다이렉티드 태너 그래프의 각각의 가변 노드에 할당하도록, 그리고

- ii) 각각의 상기 디코딩 반복에서: 상기 다이렉티드 태너 그래프의 각각의 에지에 대하여: 상기 각각의 에지가 상기 각각의 에지의 상기 가변 노드에 할당된 상기 소프트 비트와 관련된 메시지를 상기 각각의 에지를 따라 패 성함으로써 상기 각각의 디코딩 반복에 참가하는지 여부를 상기 선택 기준에 따라 결정하는 단계를 포함하는 단계에 의해 상기 소프트 비트를 갱신하도록 동작하는 것을 특징으로 하는 시스템.

# 청구항 102

제 101 항에 있어서, 하나의 상기 디코딩 반복에서, 상기 다이렉티드 태너 그래프의 적어도 하나의 가변 노드는 상기 다이렉티드 태너 그래프의 적어도 하나의 체크 노드가 상기 하나의 디코빙 반복에 참가한 후 상기 하나의 디코딩 반복에 참가하는 것을 특징으로 하는 시스템.

#### 청구항 103

제 101 항에 있어서, 하나의 상기 디코딩 반복에서, 상기 호스트는 두개의 상기 메시지를 병렬로 패싱하는 것을 특징으로 하는 시스템.

#### 청구항 104

복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션를 디코딩하는 컴퓨터 판독가능한 코드를 내장한 컴 퓨터 판독가능한 저장 매체로서,

상기 컴퓨터 판독가능한 코드는

a) 적어도 하나의 디코딩 반복에서 상기 소프트 비트를 갱신하는 프로그램 코드를 포함하고, 상기 각각의 소프트 비트가 상기 각각의 디코딩 반복에 참가하는지 여부는 각각의 상기 디코딩 반복에서, 각각의 소프트 비트에 대하여, 선택 기준에 따라 결정되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션를 디코딩하는 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

# 청구항 105

제 104 항에 있어서,

b) 각각의 상기 가변 노드에 대하여, 상기 각각의 가변 노드가 상기 각각의 디코딩 반복에 참가하는지 여부가 상기 기준에 따라 결정되도록, 각각의 가변 노드에 대하여 각각의 소프트 비트를 할당하는 프로그램 코드를 더 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션를 디코딩하는 컴퓨터 판 독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 106

제 104 항에 있어서, 상기 선택 기준은 개연적 선택 기준인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

# 청구항 107

제 104 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 시작점에서 상기 각각의 소프트 비트의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 108

제 107 항에 있어서, 상기 신뢰도 측정값은 상기 적어도 하나의 소프트 비트의 절대값인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 109

제 106 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 소프트 비트의 초기값의 신뢰도 측정값의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 110

제 109 항에 있어서, 상기 신뢰도 측정값은 상기 각각의 소프트 비트의 절대값인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

## 청구항 111

제 106 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 디코딩 반복의 일련번호의 함수 인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 112

제 106 항에 있어서, 상기 선택 기준은 각각의 상기 소프트 비트가 상기 각각의 소프트 비트의 참가 히스토리의 함수인 확률로 각각의 상기 디코딩 반복에 참가하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

# 청구항 113

제 112 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후에 얼마나 많은 상기 디코딩 반복이 경과하였는지를 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

## 청구항 114

제 112 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후에

경과된 시간을 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코 딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 115

제 104 항에 있어서, 상기 선택 기준은 상기 각각의 디코딩 반복의 일련 번호의 함수인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 116

제 104 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장 한 컴퓨터 판독가능한 저장 매체.

#### 청구항 117

제 116 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후에 얼마나 많은 상기 디코딩 반복이 경과하였는지를 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 118

제 116 항에 있어서, 상기 참가 히스토리는 상기 각각의 소프트 비트가 참가한 마지막 상기 디코딩 반복 이후에 경과된 시간을 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 119

복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장 한 컴퓨터 판독가능한 저장 매체로서,

상기 컴퓨터 판독가능한 코드는

a) 각각의 적어도 하나의 디코딩 반복에서 상기 소프트 비트의 적어도 일부분을 순차적으로 갱신하는 단계를 포함하는 단계에 의해 상기 코드워드의 상기 리프리젠테이션을 디코딩하는 프로그램 코드를 포함하고, 하나의 상기 디코딩 반복에서, 상기 소프트 비트의 일부분만 갱신되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

# 청구항 120

제 119 항에 있어서, 상기 컴퓨터 판독가능한 코드는

b) 각각의 소프트 비트를 각각의 가변 노드에 할당하는 프로그램 코드를 더 포함하고,

상기 소프트 비트의 상기 리프리젠테이션을 디코딩하기 위한 프로그램 코드는 각각의 적어도 하나의 디코딩 반복에서: 각각의 적어도 두개의 상기 가변 노드에 대하여, 상기 각각의 가변 노드와 복수의 체크 노드의 각각의 하위노드 사이에서 메시지를 교환하는 단계를 포함하는 단계에 의해 상기 소프트 비트를 갱신하는 프로그램 코드를 포함하고, 하나의 상기 디코딩 반복에서, 상기 메시지는 오직 상기 가변 노드의 일부분과 체크 노드의 상기 각각의 하위노드 사이에서 교환되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

# 청구항 121

복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장 한 컴퓨터 판독가능한 저장 매체로서,

상기 컴퓨터 판독가능한 코드는

a) 상기 소프트 비트를 적어도 하나의 디코딩 반복에서 갱신하는 프로그램 코드를 포함하고, 상기 각각의 소프 트 비트가 상기 각각의 디코딩 반복에 참가하는 기간은, 각각의 상기 디코딩 반복에서, 각각의 소프트 비트에 대하여, 선택 기준에 따라 결정되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테 이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 122

제 121 항에 있어서, 상기 선택 기준은 개연적 선택 기준인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 123

제 121 항에 있어서, 상기 선택 기준은 상기 각각의 디코딩 반복의 일련번호의 함수인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 124

제 121 항에 있어서, 상기 선택 기준은 상기 각각의 소프트 비트의 참가 히스토리의 함수인 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 125

제 121 항에 있어서, 상기 컴퓨터 판독가능한 코드는

b) 각각의 소프트 비트를 다이렉티드 태너 그래프의 각각의 가변 노드에 할당하는 프로그램 코드를 더 포함하고,

상기 소프트 비트를 갱신하는 프로그램 코드는, 각각의 상기 디코딩 반복에서: 상기 다이렉티드 태너 그래프의 각각의 에지에 대하여: 상기 각각의 에지가 상기 각각의 에지의 상기 가변 노드에 할당된 상기 소프트 비트에 관한 메시지를 상기 각각의 에지를 따라 패싱함으로써 상기 각각의 디코딩 반복에 참가하는지 여부를 상기 선택 기준에 따라 결정하는 단계를 포함하는 단계에 의해 상기 소프트 비트를 갱신하는 프로그램 코드를 포함하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

# 청구항 126

제 125 항에 있어서, 하나의 상기 디코딩 반복에서, 상기 다이렉티드 태너 그래프의 적어도 하나의 가변 노드에지는 상기 다이렉티드 태너 그래프의 적어도 하나의 체크 노드 에지가 상기 하나의 디코딩 반복에 참가한 후, 상기 하나의 디코딩 반복에 참가하는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체.

#### 청구항 127

제 125 항에 있어서, 하나의 상기 디코딩 반복에서, 두개의 상기 메시지는 병렬로 패싱되는 것을 특징으로 하는 복수의 소프트 비트를 포함하는 코드워드의 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장 한 컴퓨터 판독가능한 저장 매체.

# 명 세 서

# 기술분야

<!> 본 발명은 코드워드의 디코딩에 관한 것이고, 더욱 상세하게는 각각의 반복에서 오직 선택된 노드의 메시지의 시리얼 갱신을 사용하는 LDPC 디코딩 방법에 관한 것이다.

#### 배경기술

<2> LDPC(low-density parity check) 코드는 일종의 선형 블록 코드이다. 명칭 "LDPC"는 이러한 코드의 패리티 체

크 매트릭스가 1 보다 더 많은 0을 가진다는 점으로부터 유래한 것이다. LDPC의 주된 이점은 다수의 상이한 채널에 대하여 용량에 매우 근접한 성능을 제공한다는 점, 이러한 디코딩 알고리즘이 시간상 선형 복잡도를 가진다는 점, 및 과다한 병렬을 사용하게 하는 구현에 적합하다는 점이다.

- <3> LDPC 코드는 'R. G. Gallager'에 의해 1960년에 그의 PhD 논문(thesis)에 처음 소개되었다. LDPC 코더 및 디 코더를 구현하기 위해 필요한 계산상의 노력으로 인해, 그리고 리드-솔로몬(Reed-Solomon) 코드의 소개로 인해, LDPC 코드는 1990년대 중반까지는 일반적으로 무시되었다.

- <4> LDPC 코드는 매트릭스, 또는 도시적으로 표현될 수 있다.

- <5> 아래의 매트릭스는 (8.4) 코드(m=4, n=8)에 대한 m×n 패리티 체크 매트릭스의 예이다:

$$H = \begin{pmatrix} 0 & 1 & 0 & 1 & 1 & 0 & 0 & 0 \\ 1 & 1 & 1 & 0 & 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 & 0 & 1 & 1 & 1 \\ 1 & 0 & 0 & 1 & 1 & 0 & 1 & 0 \end{pmatrix}$$

<6>

- <7> 두 숫자: w<sub>r</sub>, 행 내의 1의 개수, 및 w<sub>c</sub>, 열 내의 1의 개수가 이러한 매트릭스를 설명한다. 이러한 매트릭스가 "저밀도"이기 위해서는, w<sub>r</sub>은 m보다 훨씬 더 작아야 하고, w<sub>c</sub>는 n보다 훨씬 더 작아야 한다. 이것은 상기 예의 경우는 아니지만, 실제로 사용되는 훨씬 더 큰 패리티 체크 매트릭스인 경우이다.

- <8> 1981년에, 태너(Tanner)는 LDPC 코드의 효과적인 도시적 리프리젠테이션을 소개하였다. 이러한 그래프는 이러한 코드의 완벽한 리프리젠테이션을 제공함과 동시에, 디코딩 알고리즘을 설명하는데 도움을 준다.

- <9> 태너 그래프는 "이분(bipartite)" 그래프이다. 이것은 그래프의 노드가 두 개의 구별된 세트로 나누어짐을 의미하고, 그래프의 에지는 상이한 타입의 노드를 연결함을 의미한다. 태너 그래프에서 두 타입의 노드는 가변 노드(또는 v-노드), 및 체크 노드(또는 c-노드)이다.

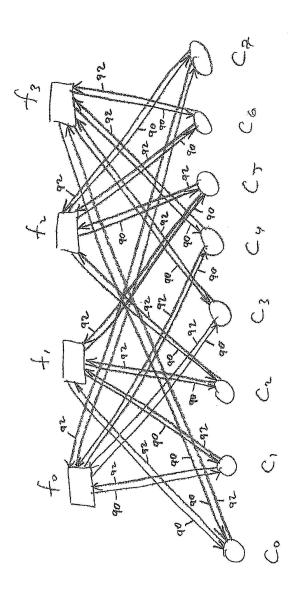

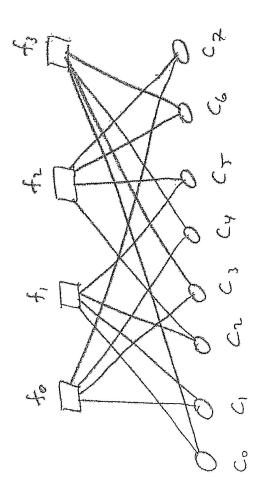

- <10> 도 1은 상기 매트릭스와 동일한 코드를 나타내는 태너 그래프를 도시한다. 이 그래프는 m개의 체크 노드(m은 패리티 비트의 개수), 및 n개의 가변 노드(n은 코드워드 내의 비트의 개수)를 가진다. 체크 노드(f<sub>j</sub>)는 H의 엘리먼트(h<sub>ii</sub>)가 1일 때, 가변 노드(c<sub>i</sub>)에 연결된다.

- <11> LDPC 코드는 모든 열이 동일한 개수의 1을 가지고(w<sub>c</sub>가 상수이고), 모든 행이 동일한 개수의 1을 가질(w<sub>r</sub>이 상수일) 때, "규칙적(regular)"이라 불린다. 상기 매트릭스는 w<sub>c</sub>=2이고, w<sub>r</sub>=4로 규칙적이다. 이 코드의 규칙성은 또한 도 1에서도 볼 수 있다: 모든 v-노드는 동일한 개수의 인커밍 에지를 가지고, 모든 c-노드는 동일한 개수의 인커밍 에지를 가진다. 패리티 체크 매트릭스가 저밀도이지만, 각각의 행 또는 열의 1의 개수가 일정하지 않으면, 그 코드는 "불규칙적인" LDPC 코드라 불린다.

- <12> LDPC 코드를 디코딩하기 위해 사용되는 기본 알고리즘은 독립적으로 수차례 발견되었으며, 상이한 명칭으로 불린다. 가장 일반적인 명칭은 "신뢰확산(belief propagation) 알고리즘", "메시지 패싱 알고리즘", 및 "합곱(sum-product) 알고리즘"이다.

- <13> 이 알고리즘은 디코딩될 코드워드의 비트의 추정값이 로그우도비(LLR):  $P_i = \log \left( \frac{\Pr(bit \ i = 0)}{\Pr(bit \ i = 1)} \right)$ 의 형태로 제 공되는 것으로 가정한다. 이 LLR 추정값은, 예컨대, 노이즈 있는 채널로부터 수신되는 심벌을 기초로 계산될 수 있다. 매 반복의 끝에서, i번째 비트의 LLR의 현재 추정값은  $Q_i$ 로 표시된다. 가변 노드 $(c_i)$ 에 의해 체크 노드 $(f_j)$ 로 전송된 메시지는  $Q_{ij}$ 로 표시된다. 체크 노드 $(f_j)$ 에서 가변 노드 $(c_i)$ 로 전송된 메시지는  $R_{ji}$ 로 표시된다. 초기에, 모든 i에 대하여,  $Q_{ij}$ = $P_i$ 이고,  $R_{ji}$ =0이다. 각각의 반복에서, 이 메시지는 다음의 갱신 룰에 따라 계산된다:

$$Q_{ij} \leftarrow P_i + \sum_{j' \in N(i) \setminus j} R_{j'i}$$

<14>

$$R_{ji} \leftarrow \varphi^{-1} \left( \sum_{i' \in N(j) \setminus i} \varphi(Q_{i'j}) \right)$$

$$Q_i \leftarrow P_i + \sum_{j \in N(j)} R_{ji}$$

<15>

<17>

<19>

<20>

<16> 여기서, N(k)는 노드(k)의 이웃의 세트를 나타낸다, 즉, k=i인 경우에, 주어진 가변 노드(c<sub>i</sub>)로 메시지를 전송하는 모든 체크 노드(f<sub>j</sub>), 및 k=j인 경우에, 주어진 체크 노드(f<sub>j</sub>)로 메시지를 전송하는 모든 가변 노드(c<sub>i</sub>)를 나타내고, 그리고

$$\varphi(x) = \left( sign(x), -\log \tanh\left(\frac{|x|}{2}\right) \right)$$

$$\varphi^{-1}(x) = (-1)^{sign} \left( -\log \tanh\left(\frac{x}{2}\right) \right)$$

<18>  $\varphi(x)$  , 및 그것의 계산은 그룹.  $F2 \times [0,\infty]$ 를 통해 한정됨을 이해해야 한다. 가변 노드 $(c_i)$ 에 의해 체크 노드 $(f_i)$ 로 전송되는 메시지가  $T_{ij} = \varphi(Q_{ij})$ 으로 재한정되면, 대칭적 갱신 룰은 다음과 같이 표현될 수 있다.

$$T_{ij} \leftarrow \varphi \left( P_i + \sum_{j' \in N(i) \setminus j} R_{j'i} \right)$$

$$R_{ji} \leftarrow \varphi^{-1} \left( \sum_{i' \in \mathcal{N}(j) \setminus i} T_{i'j} \right)$$

<21> 노드 사이에서 메시지를 패성하는 순서를 메시지 패성 디코딩 스케줄이라 한다. 종래의 메시지 패성 스케줄은, 각각의 반복에서, 처음 모든 가변 노드가 새로운 메시지를 그들의 이웃으로 패성하고, 그 다음 모든 체크 노드 가 새로운 메시지를 그들의 이웃에게 패성하는 "플러딩" 스케줄(R. G. Gallager, Low-Density Parity-Check Codes, MIT Press, 1963)이다. 반복이 가변 노드를 직렬로 트래버성함으로써 수행되고, 그것의 인커밍 메시지 및 아웃고잉 메시지를 각각 갱신하기 위한 시리얼 스케줄은 플러딩 스케줄 보다 대략 2배만큼 빠르게 수렴하기 위한, 'E. Sharon', 'S. Litsyn' 및 'J. Goldberger'의, 'Proc. Turbo-Coding-2006 Conference', 뮌헨, 2006 년 4월, "Efficient serial message-passing schedules for LDPC decoding"에서 찾을 수 있다.

- <22> 아래의 미국특허들은 LDPC 인코딩 및 디코딩의 대표적인 현재 기술이다:

- <23> 'Matsumoto'의 US 7,089,479

- <24> 'Shen et al.'의 US 7,107,511

- <25> 'Kim et al.'의 US 7,120,857

- <26> 'Richardson et al.'의 US 7,127,659

- <27> 'Richardson et al.'의 US 7,133,853

- <28> 'Cameron et al.'의 US 7,149,953

- <29> 'Boutillon et al.'의 US 7,174,495

- <30> 'Hocevar'의 US 7,181,676

# 발명의 상세한 설명

- <31> 본 발명의 기본은 반복에서 오인식될 가능성이 높은 가변 노드만 선택적으로 갱신함으로써 디코딩 계산 복잡도를 추가적으로 감소시키는, 본 명세서에서 레지 스케줄(LS)이라 불리는, 혁신적인 시리얼 스케줄의 변형이다.

- <32> 디코딩 프로세스는 통상적으로 매우 작은 반복 후 대부분의 가변 노드의 추정에 높은 신뢰도를 달성한다. 이러한 노드들은 결과적인 디코딩 반복에서 극성이 변할 가능성이 낮다. LS는 부분적인 반복을 통해 디코딩함으로써, 오직 낮은 신뢰도의 메시지만을 갱신하여, 이러한 현상을 이용한다.

- <33> 디코딩 복잡도는 수렴될 때까지 계산된 메시지의 전체 개수로 측정된다. 그러므로, LS가 수렴을 위해 필요한 반복의 횟수를 증가시키지 않는다면, 반복당 복잡도를 줄임으로써 전체 디코딩 복잡도를 줄일 가능성이 존재한다. 명백하게, LS가 디코더의 비트 에러율(BER) 성능을 저하시키거나, 인공 에러 플로어(김동호, 및 김상우의, "Bit-Level stopping of turbo decoding", IEEE Commun. Letters no. 10 pp. 183-185, 2006)를 발생시키지 않는다는 점이 중요하다. 실제로, 아래에서 볼 수 있듯이, 신중히 설계되고 최적화된 래지 스케줄은 성능 저하없이 디코딩 복잡도를 줄인다.

- <34> 본 발명에 따른 코드워드를 디코딩하는 방법이 제공되는데, 본 방법은 a) 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 채널로부터 수신하는 단계; 및 b) 각각의 적어도 하나의 디코딩 반복에서: i) 각각의 소프트 비트가 각각의 디코딩 반복에 참가하는지 여부를 선택 기준에 따라 결정하는 단계; 및 ii) 상기 결정하는 단계가 적어도 하나의 소프트 비트가 각각의 디코딩 반복에 참가하는 것으로 선택된다면, 적어도 하나의 참가하는 소프트 비트를 갱신하는 단계를 포함한다.

- <35> 본 발명에 따른 코드워드를 디코딩하는 방법이 제공되는데, 본 방법은 a) 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 채널로부터 수신하는 단계; 및 b) 각각의 적어도 하나의 디코딩 반복에서, 소프트 비트의 적어도 일부분을 순차적으로 갱신하는 단계를 포함하고, 하나의 디코딩 반복에서, 소프트 비트의 일부분 만이 갱신된다.

- <36> 본 발명에 따른 코드워드를 디코딩하는 방법이 제공되는데, 본 방법은 a) 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 채널로부터 수신하는 단계; 및 b) 각각의 적어도 하나의 디코딩 반복에서: i) 각각의 소프트 비트에 대하여, 각각의 소프트 비트가 각각의 디코딩 반복에 참가하는 기간을 선택 기준에 따라 결정하는 단계, 및 ii) 상기 결정하는 단계가 적어도 하나의 소프트 비트가 각각의 디코딩 반복에 참가하는 것으로 선택된다면, 적어도 하나의 참가하는 소프트 비트를 갱신하는 단계를 포함한다.

- <37> 본 발명에 따른 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더가 제공되는데, 본 디코더는 적어도 하나의 디코딩 반복에서 소프트 비트를 갱신하기 위한 복수의 기능 모듈을 포함하고, 각각 의 디코딩 반복에서, 각각의 소프트 비트에 대하여, 각각의 소프트 비트가 각각의 디코딩 반복에 참가하는지 여 부가 선택 기준에 따라 결정된다.

- <38> 본 발명에 따른 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더가 제공되는데, 본 디코더는 각각의 적어도 하나의 디코딩 반복에서 적어도 일부분의 소프트 비트를 순차적으로 갱신하기 위한 복수의 기능 모듈을 포함하고, 하나의 디코딩 반복에서 소프트 비트의 일부분 만이 갱신된다.

- <39> 본 발명에 따른 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더가 제공되는데, 본 디코더는 각각의 적어도 하나의 디코딩 반복에서 적어도 일부분의 소프트 비트를 순차적으로 갱신하기 위한 복수의 기능 모듈을 포함하고, 하나의 디코딩 반복에서 소프트 비트의 일부분 만이 갱신된다.

- 본 발명에 따른 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 디코더가 제공되는데, 본 디코더는 적어도 하나의 디코딩 반복에서 소프트 비트를 갱신하기 위한 복수의 기능 모듈을 포함하고, 각각 의 디코딩 반복에서, 각각의 소프트 비트에 대하여, 각각의 소프트 비트가 각각의 디코딩 반복에 참가하는 기간 이 선택 기준에 따라 결정된다.

- 본 발명에 따른 메모리가 제공되는데, a) 코드워드를 저장하기 위한 비휘발성 메모리의 어레이; 및 b) 적어도 하나의 디코딩 반복에서 소프트 비트를 갱신함으로써, 비휘발성 메모리 셀의 어레이로부터 수신된 복수의 소프 트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 회로를 포함하고, 각각의 디코딩 반복에서, 각 각의 소프트 비트에 대하여, 각각의 소프트 비트가 각각의 디코딩 반복에 참가하는지 여부는 선택 기준에 따라 결정된다.

- <42> 본 발명에 따른 메모리가 제공되는데, a) 코드워드를 저장하기 위한 비휘발성 메모리의 어레이; 및 b) 각각의 적어도 하나의 디코딩 반복에서 소프트 비트의 적어도 일부분을 순차적으로 갱신하는 단계를 포함하는 단계에

의해, 비휘발성 메모리의 어레이로부터 수신된 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코 딩하는 회로를 포함하고, 하나의 디코딩 반복에서 소프트 비트의 일부분 만이 갱신된다.

- <43> 본 발명에 따른 메모리가 제공되는데, a) 코드워드를 저장하기 위한 비휘발성 메모리의 어레이; 및 b) 적어도 하나의 디코딩 반복에서 소프트 비트를 갱신함으로써, 비휘발성 메모리의 어레이로부터 수신된 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하는 회로를 포함하고, 각각의 디코딩 반복에서, 각각의 소 프트 비트에 대하여, 각각의 소프트 비트가 각각의 디코딩 반복에 참가하는 기간이 선택 기준에 따라 결정된다.

- 본 발명에 따른 메모리 디바이스가 제공되는데, a) 코드워드를 저장하기 위한 비휘발성 메모리; 및 b) 비휘발성 메모리로부터 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 수신하도록, 그리고, 적어도 하나의 디코딩 반복에서 소프트 비트를 갱신함으로써, 코드워드 리프리젠테이션을 디코딩하도록 동작하는 컨트롤러를 포함하고, 각각의 디코딩 반복에서, 각각의 소프트 비트에 대하여, 각각의 소프트 비트가 디코딩 반복에 참가하는지 여부는 선택 기준에 따라 결정된다.

- 본 발명에 따른 메모리 디바이스가 제공되는데, a) 코드워드를 저장하기 위한 비휘발성 메모리; 및 b) 비휘발성 메모리로부터 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 수신하도록, 그리고 각각의 적어도 하나의 디코딩 반복에서 소프트 비트의 적어도 일부분을 순차적으로 갱신하는 단계를 포함하는 단계에 의해, 코드워드 리프리젠테이션을 디코딩하도록 동작하는 컨트롤러를 포함하고, 하나의 디코딩 반복에서 소프트 비트의 일부분 만이 갱신된다.

- 본 발명에 따른 메모리 디바이스가 제공되는데, a) 코드워드를 저장하기 위한 비휘발성 메모리; 및 b) 비휘발성 메모리로부터 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 수신하도록, 그리고 적어도 하나의 디코딩 반복에서 코드워드 리프리젠테이션을 디코딩하도록 동작하는 컨트롤러를 포함하고, 각각의 디코딩 반복에서, 각각의 소프트 비트에 대하여, 각각의 소프트 비트가 각각의 디코딩 반복에 참가하는 기간이 선택 기준에따라 결정된다.

- 본 발명에 따른 시스템이 제공되는데, a) 메모리 디바이스; 및 b) 메모리 디바이스로부터 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 수신하도록, 그리고 적어도 하나의 디코딩 반복에서 소프트 비트를 갱신함으로써, 코드워드 리프리젠테이션을 디코딩하도록 동작하는, 메모리 디바이스의, 호스트를 포함하고, 각각의 디코딩 반복에서, 각각의 소프트 비트에 대하여, 각각의 소프트 비트가 디코딩 반복에 참가하는지 여부는 선택 기준에 따라 결정된다.

- 본 발명에 따른 시스템이 제공되는데, a) 메모리 디바이스; 및 b) 메모리 디바이스로부터 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 수신하도록, 그리고 각각의 적어도 하나의 디코딩 반복에서 소프트 비트의 적어도 일부분을 순차적으로 갱신하는 단계를 포함하는 단계에 의해, 코드워드 리프리젠테이션을 디코딩하도록 동작하는, 메모리 디바이스의, 호스트를 포함하고, 하나의 디코딩 반복에서, 소프트 비트의 일부분 만이 갱신된 다

- 본 발명에 따른 시스템이 제공되는데, a) 메모리 디바이스; 및 b) 메모리 디바이스로부터 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 수신하도록, 그리고 적어도 하나의 디코딩 반복에서 소프트 비트를 갱신함 으로써 코드워드 리프리젠테이션을 디코딩하도록 동작하는 컨트롤러를 포함하고, 각각의 디코딩 반복에서, 각각 의 소프트 비트에 대하여, 각각의 소프트 비트가 각각의 디코딩 반복에 참가하는 기간이 선택 기준에 따라 결정 된다.

- <50> 본 발명에 따른 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체가 제공되는데, 이 컴퓨터 판독가능한 코드는 a) 적어도 하나의 디코딩 반복에서 소프트 비트를 갱신하는 프로그램 코드를 포함하고, 각각의 디코딩 반복에서, 각각의 소프트 비트에 대하여, 각각의 소프트 비트가 디코딩 반복에 참가하는지 여부는 선택 기준에 따라 결정된다.

- <51> 본 발명에 따른 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체가 제공되는데, 이 컴퓨터 판독가능한 코드는 a) 각각의 적어도 하나의 디코딩 반복에서 소프트 비트의 적어도 일부분을 순차적으로 갱신하는 단계를 포함하는 단계에 의해, 코드워드 리프리젠테이션을 디코딩하는 프로그램 코드를 포함하고, 하나의 디코딩 반복에서, 소프트 비트의 일부분만이 갱신된다.

- <52> 본 발명에 따른 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 디코딩하기 위한 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체가 제공되는데, 이 컴퓨터 판독가능한 코드는 a) 적어도 하나의 디

코딩 반복에서 소프트 비트를 갱신하는 프로그램 코드를 포함하고, 각각의 디코딩 반복에서, 각각의 소프트 비트에 대하여, 각각의 소프트 비트가 각각의 디코딩 반복에 참가하는 기간은 선택 기준에 따라 결정된다.

- <53> 본 발명의 방법은 코드워드를 디코딩하는 방법이다. 코드워드의 리프리젠테이션은 채널로부터 수신된다. "채널"은 코드워드의 리프리젠테이션을 구성하는 복수의 소프트 비트의 물리적 소스이다. 예를 들어, 통신 시스템에서, 디코더에 대한 채널은 코드워드를 포함하는 신호가 디코더를 포함하는 수신기로 전송될 때 통과하는 매체를 포함하고, 또한 복조 하드웨어와 같은, 임의의 하드웨어가, 수신기가 신호를 수신하기 위해, 그리고 디코더에 코드워드 리프리젠테이션의 소프트 비트를 제공하기 위해 포함된다. 이러한 채널은 본 명세서에서 "통신 채널"이라 불린다. 메모리 디바이스에서, 디코더로의 채널은 코드워드가 저장되는 저장 하드웨어(예컨대, 플래시메모리 셀의 어레이), 및 저장 하드웨어로부터 코드워드 리프리젠테이션의 소프트 비트를 판독하고, 디코더에 그 소프트 비트를 제공하는 희로를 포함한다. 이러한 채널은 본 명세서에서 "메모리 채널"이라 불린다. 채널에 노이즈가 있기 때문에, 디코더가 수신한 것, 본 발명의 방법이 오퍼레이팅하는 것은 오직 코드워드의 "리프리젠테이션"만이고, 예컨대, 통신 시스템에서 원래 전송된 코드워드, 또는 메모리 디바이스의 저장 하드웨어에 원래 저장된 코드워드가 아니다.

- "소프트 비트"는 그 추정의 신뢰도 측정값이 결합된 비트의 추정값이다. 종종, 동일한 숫자가 비트의 추정값, 및 신뢰도 측정값을 모두 서브한다. 예를 들어, LLR의 부호는 LLR에 의해 표현된 비트값의 추정값이고, LLR의 크기는 그 추정의 신뢰도의 측정값이다.

- <55> 본 발명의 제1의 기본 방법에서, 코드워드는 하나 이상의 디코딩 반복에서, 반복적으로 디코딩된다. 각각의 디코딩 반복에서, 각각의 소프트 비트에 대하여, 그 소프트 비트가 이 디코딩 반복에 참가하는지 여부는 선택 기준에 따라 결정된다. 그 다음, 이 디코딩 반복에 참가하는 것으로 선택된 모든 소프트 비트가 갱신된다.

- <56> 모든 소프트 비트가 매 디코딩 반복에 참가하지 않는 경우는 가능하고 통상적이다. 또한, 모든 소프트 비트가 매 디코딩 반복에 참가하는 것으로 선택된 것으로 밝혀지는 특수한 경우도 가능하다. 이러한 경우에, 본 발명과 모든 소프트 비트가 항상 참가하는 종래기술의 방법을 구별하는 본 발명의 특징은 선택 기준이 소프트 비트가 참가하는지 여부를 결정하기 위해 검사된다는 점이다: 선험적(a priori)으로, 모든 소프트 비트가 본 발명의 매 디코딩 반복에 참가한다는 보장은 존재하지 않는다. 본 발명의 하나의 수렴 기준은 디코딩 반복이 소프트 비트가 참가할 것으로 선택된 소프트 비트가 없는 상태에 도달되는 것이다.

- \*57> 바람직하게는, 디코딩 반복은 LDPC 반복이다. 각각의 소프트 비트는, 각각의 디코딩 반복에서, 각각의 가변 노드에 대하여, 그 가변 노드가 이 디코딩 반복에 참가하는지 여부가 선택 기준에 따라 결정되도록, 각각의 가변 노드에 할당된다. 각각의 디코딩 반복에서, 각각의 참가하는 가변 노드는, 복수의 체크 노드 중 각각의 하위노드(subplurality)의 각각의 맴버로부터, 각각의 체크-노드-투-가변 메시지를 수신한다. 각각의 참가하는 가변 노드는 가변 노드가 체크 노드의 그 하위노드로부터 가장 최근에 수신한 체크-노드-투-가변 메시지에 따라 그 각각의 소프트 비트를 갱신한다. 각각의 참가하는 가변 노드는 또한 그 하위노드 내의 모든 체크 노드로, 각각의 가변-노드-투-체크 노드 메시지를 패싱한다.

- 아람직하게는, 선택 기준은 개연적(probabilistic) 선택 기준이다. 즉, 소프트 비트가 참가하는 여부의 결정은 비결정적(non-deterministic) 프로세스에 의해 수행된다. 예를 들어, 본 발명의 몇몇 바람직한 실시예에서, 각 각의 소프트 비트에 대하여, 랜덤 수가 생성되고, 소프트 비트는 그 소프트 비트의 신뢰도 측정값의 몇몇 함수가 그 랜덤 수보다 작을 때만 디코딩 반복에 참가한다. 그러므로, 동일한 입력 코드워드에 대하여 본 발명의 동일한 특정 실시예의 두 개의 상이한 어플리케이션의 동일한 디코딩 반복에서, 제1어플리케이션에서 참가하는 소프트 비트의 세트는 제2어플리케이션에서 참가하는 소프트 비트의 세트와 상이할 수 있다. 본 발명의 이러한 특징은 강화된 수렴 알고리즘과 같은 종래기술의 결정적 알고리즘과 본 발명의 알고리즘을 구별하는 특징 중 하나이다.

- <59> 더욱 바람직하게는, 각각의 소프트 비트는 각각의 인코딩 반복에서, 그 디코딩 반복의 시작시, 그 소프트 비트의 절대값과 같은, 소프트 비트의 신뢰도 측정값의 함수인 확률로 참가한다. 더욱더 바람직하게는, 본 발명은 그 함수를 최적화하는 단계를 포함한다. 가장 바람직하게는, 그 함수는 복수의 트라이얼 함수를 사용하여 모든 디코딩 반복 내의 갱신을 시뮬레이션하는 단계, 및 사용할 함수로서 그 갱신의 디코딩 복잡도를 최소화하는 트라이얼 함수를 선택하는 단계를 포함하는 단계에 의해 최적화된다.

- <60> 대안으로서, 각각의 소프트 비트는 각각의 디코딩 반복에서 채널로부터 수신된 소프트 비트의 절대값과 같은 신뢰도 측정값의 함수인 확률로 참가한다. 더욱더 바람직하게는, 본 방법은 그 함수를 최적화하는 단계를 포함한

다. 가장 바람직하게는, 그 함수는 밀도전개(Density Evolution) 알고리즘을 사용하여 최적화된다.

- <61> 대안으로서, 각각의 소프트 비트는 각각의 디코딩 반복에서 현재 디코딩 반복의 반복 일련 번호의 함수인 확률로 참가한다. 대안으로서, 각각의 소프트 비트는 각각의 디코딩 반복에서 그 소프트 비트의 참가 히스토리의함수인 확률로 참가한다. 소프트 비트의 "참가 히스토리"는 그 소프트 비트가 언제 그 디코딩에 참가하였는지, 또는 얼마나 자주 참가하였는지의 기록이다. 예를 들어, 그 함수의 인수는 그 소프트 비트가 참가한 마지막 디코딩 반복 이후 얼마나 많은 디코딩 반복이 경과하였는지를 포함하고, 또는 그 소프트 비트가 참가한 마지막 디코딩 반복 이후 시스템 클록에 의해 측정되는, 얼마나 오래되었는지를 포함한다. 일반적으로, 그 함수의 인수는 단순히 반복 일련 번호, 및/또는 참가 히스토리를 포함한다. 함수의 인자가 반복 일련 번호 및/또는 참가히스토리로 한정된다면, 통상적으로 모든 소프트 비트는 제1반복에 참가한다.

- <62> 선택 기준은 반드시 개연적일 필요는 없다. 바람직한 결정적 선택 기준은 현재 디코딩 반복의 일련 번호의 함수, 및 참가 결정이 렌더링되는 소프트 비트의 참가 히스토리의 함수를 포함한다.

- <63> 본 발명의 제2의 기본 방법에서, 소프트 비트는 반복적으로 갱신된다. 각각의 하나 이상의 디코딩 반복에서, 적어도 일부의 소프트 비트는 순차적으로 갱신된다. 소프트 비트가 "순차적으로" 갱신된다는 것은 하나의 소프트 비트를 갱신하기 위해 주어진 디코딩 반복의 모든 오퍼레이션이 다음 소프트 비트를 진행하기 전에 완료된다는 것을 의미한다. 이것은 이러한 형태의 본 발명이 종래기술의 플러딩 스케줄, 및 그러므로 플러딩 스케줄을 사용하여 강화 수렴 알고리즘과 같은, 종래기술의 알고리즘과 구별되는 본 발명의 한 특징이다. 하나의 디코딩 반복에서, 모든 소프트 비트가 갱신되지 않는다. 이것은 이러한 형태의 본 발명을 'Sharon et al.'의 종래기술과 구별시키는 본 발명의 한 특징이다.

- \*64> 바람직하게는, 디코딩 반복은 LDPC 반복이다. 반복을 시작하기 전에, 각각의 소프트 비트는 각각의 가변 노드에 할당된다. 각각의 디코딩 반복에서, 각각의 참가하는 소프트 비트에 대하여, 각각의 체크-노드-투-가변-노드 메시지는 복수의 체크 노드의 각각의 하위노드의 각각의 맴버로부터, 그 소프트 비트가 할당된 가변 노드로 패 성된다. 그 다음, 그 소프트 비트는 체크 노드의 각각의 하위노드로부터 그 가변 노드에 의해 가장 최근에 수신된 체크-노드-투-가변-노드 메시지에 따라 갱신된다. 그 다음, 각각의 가변-노드-투-체크-노드 메시지는 그 가변 노드로부터 그 각각의 체크 노드로 패성된다. 모든 이러한 오퍼레이션은 다음 소프트 비트, 및 그 할당된 가변 노드로 진행하기 전에 완료된다.

- 본 발명의 제3의 기본 방법에서, 코드워드는 하나 이상의 디코딩 반복에서, 반복적으로 디코딩된다. 각각의 디코딩 반복에서, 각각의 소프트 비트에 대하여, 그 소프트 비트가 디코딩 반복에 참가하는 기간(모두 참가, 부분적으로 참가, 또는 참가하지 않음)이 선택 기준에 따라, 결정된다. 그 다음, 이 디코딩 반복에 참가하는 것으로 선택된 모든 소프트 비트가 갱신된다.

- <66> 본 발명의 제1방법에서와 마찬가지로, 선택 기준은 개연적일 수 있고, 또는 현재 디코딩 반복의 반복 일련번호의 함수, 또는 참가 기간이 결정되어 있는 소프트 비트의 참가 히스토리의 함수일 수 있다.

- 아라직하게는, 상기 디코딩 반복은 다이렉티트 태너 그래프를 사용하는 수정된 LDPC 디코딩 반복이다. 각각의 소프트 비트는 다이렉티트 태너 그래프의 각각의 가변 노드에 할당된다. 각각의 디코딩 반복에서, 다이렉티트 태너 그래프의 각각의 에지에 대하여, 그 에지가 현재 디코딩 반복에 참가하는지 여부는 선택 기준에 따라, 결정된다. 그 에지가 현재 디코딩 반복에 참가한다면, 그 에지의 가변 노드에 할당된 소프트 비트에 관련된 에지를 따라 패싱된 메시지를 가짐으로써, 그렇게 한다. 소프트 비트가 주어진 디코딩 반복에 참가하는 기간이 가변 노드의 얼마나 많은 에지가 디코딩 반복에 참가하는지에 따라, 모두 참가, 부분적 참가, 참가하지 않을 수 있음에도 불구하고, 다이렉티드 태너 그래프의 각각의 에지는 주어진 디코딩 반복에 모두 참가하거나, 참가하지 않음을 이해해야 한다. 가장 바람직하게는, 하나의 디코딩 반복에서, 적어도 하나의 가변 노드 에지는 적어도하나의 체크 노드 에지 후에 참가한다. 또한 가장 바람직하게는, 하나의 디코딩 반복에서, 두개의 메시지가 병렬로 패싱된다.

- <68> 본 발명의 디코더는 본 발명의 하나의 방법을 구현하기 위한 복수의 기능 모듈을 포함한다. 예를 들어, 디코더의 개연적 LDPC 실시예는 가변 노드 할당 모듈, 가변 노드 선택 모듈, 제1 및 제2메시지 패싱 모듈, 및 소프트비트 갱신 모듈을 포함한다. 가변 노드 할당 모듈은 , 각각의 가변 노드에 대하여, 각각의 가변 노드가 각각의 디코딩 반복에 참가하는지 여부가, 선택 기준에 따라 결정되도록, 각각의 소프트 비트를 각각의 가변 노드에 할당한다. 가변 노드 선택 모듈은 가변 노드가 각각의 디코딩 반복에 참가할지 결정한다. 각각의 디코딩 반복에서, 제1메시지 패싱 모듈은, 각각의 참가하는 가변 노드에 대하여, 복수의 체크 노드의, 각각의 하위노드의 각

각의 맴버에 대하여, 각각의 체크-노드-투-가변-노드-메시지를 계산하고, 소프트 비트 갱신 모듈은 제2메시지 패싱 모듈로부터 본 디코딩 반복에서 수신된 체크-노드-투-가변-노드-메시지에 따라 각각의 참가하는 가변 노드의 각각의 소프트 비트를 갱신하고; 그리고 제2메시지 패싱 모듈은, 각각의 참가하는 가변 노드에 대하여, 참가하는 가변 노드가 제1메시지 패싱 모듈로부터 가장 최근에 수신한 체크-노드-투-가변-노드-메시지에 따라, 그 참가하는 가변 노드의 체크 노드의 각각의 하위노드 내의 각각의 체크 노드에 대한 각각의 가변-노드-투-체크-노드 메시지를 계산한다.

- <69> 바람직하게는, 복수의 기능 모듈은 디코딩이 수렴했는지 여부를, 갱신에 응답하여, 결정하는 수렴 체크 모듈을 포함한다.

- <70> 본 발명의 범위는 또한 채널로부터 수신된 메시지를 변조하고, 그로 인해 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션을 제공하는 변조기, 및 그 코드워드 리프리젠테이션을 디코딩하기 위한 본 발명의 디코더를 갖춘 통신 수신기를 포함한다.

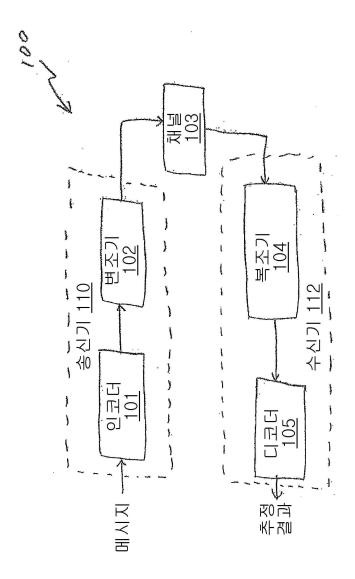

- <71> 본 발명의 범위는 또한 본 발명의 통신 수신기, 채널, 및 채널을 통해 통신 수신기로 메시지를 전송하기 위한 송신기를 갖춘 통신 시스템을 포함한다. 'Mat sumoto'의, US 7,089,479의 도 27로부터 수정된 도 2는 송신기 (110), 채널(103), 및 수신기(112)를 포함하는 통신 시스템(100)의 개략적인 하이레벨 블록 다이어그램이다. 송신기(110)는 인코더(101), 및 변조기(102)를 포함한다. 수신기(112)는 복조기(104), 및 디코더(105)를 포함한다. 인코더(101)는 메시지를 수신하고 대응하는 코드워드를 생성한다. 변조기(102)는 생성된 코드워드에 BPSK, QPSK, 또는 다중치(multi-value) QAM과 같은 디지털 변조를 적용하고, 결과적인 변조된 신호를 채널(103)로부터 수신하고, 수신된 변조된 신호를 BPSK, QPSK, 또는 다중치 QAM와 같은 디지털 복조를 적용한다. 디코더(105)는 본 발명의 방법 중 하나를 사용하여 원래의 코드워드의 결과적인 리프리젠테이션을 디코딩한다.

- <72> 본 발명의 범위는 메모리, 메모리에 데이터를 저장하고, 메모리로부터 데이터를 복수의 소프트 비트를 포함하는 코드워드 리프리젠테이션으로 추출하는 회로, 및 그 코드워드 리프리젠테이션을 디코딩하기 위한 본 발명의 디코더를 갖춘 메모리 디바이스를 포함한다.

- <73> 본 발명의 범위는 또한 코드워드를 저장하기 위한 비휘발성 메모리 셀의 어레이, 및 본 발명의 방법 중 하나를 사용하여, 비휘발성 메모리 셀의 어레이로부터 수신된 코드워드 리프리젠테이션을 디코딩하는 회로를 갖춘 메모리를 포함한다. 본 발명의 범위는 또한 코드워드를 저장하기 위한 비휘발성 메모리, 및 비휘발성 메모리로부터 코드워드 리프리젠테이션을 수신하고, 본 발명의 방법 중 하나를 사용하여 그 코드워드 리프리젠테이션을 디코딩하도록 동작하는 컨트롤러를 갖춘 메모리 디바이스를 포함한다. 본 발명의 범위는 메모리 디바이스, 및 메모리 디바이스로부터 코드워드 리프리젠테이션을 수신하고, 본 발명의 방법 중 하나를 사용하여 그 코드워드 리프리젠테이션을 디코데젠테이션을 다코딩하도록 동작하는, 메모리 디바이스의, 호스트를 갖춘 시스템을 포함한다. 본 발명의 범위는 본 발명의 방법 중 하나를 구현하는 컴퓨터 판독가능한 코드를 내장한 컴퓨터 판독가능한 저장 매체를 포함한다.

#### 실시예

- <82> 본 발명에 따른 래지 스케줄링 LDPC 디코더의 원리 및 오퍼레이션은 첨부된 도면 및 설명을 참고하여 더 잘 이해될 것이다.

- 아래의 설명은 래지 스케줄 디코딩 알고리즘의 상세한 설명이다. 각각의 반복에서, 가변 노드는 주어진 순서로 직렬로 트래버싱된다. 각각의 가변 노드(c<sub>i</sub>)에 대하여, 인커밍 및 아웃고잉 메시지는 확률, β(1,r<sub>i</sub>)로 갱신되는데, 여기서, 1은 반복 일련번호이고, r<sub>i</sub>는 가변 노드(c<sub>i</sub>)의 몇몇 신뢰도의 측정값이다. 바람직하게는, β(1,r<sub>i</sub>)은 r<sub>i</sub> 값의 함수이지만, 인텍스(i) 그 자체의 함수는 아니다. 통상적으로, 모든 i에 대하여 β(1,r<sub>i</sub>)=1이다. 플러딩 스케줄이 사용된다면, 그리고 갱신 프로세스가 결정론적이고, 반복 횟수와 무관하다면, 즉 r<sub>i</sub>가 몇몇 임계값을 초과하는지에 따라 β(1,r<sub>i</sub>)=β(r<sub>i</sub>)=0 또는 1이라면, 'P. K. Bora', 'E. Zimmermann', 'G. Fettweis' 및 'P. Pattisapu'의, 무선 개인 멀티미디어 통신((WPMCO4)의 2004) 제7회 국제 심포지엄, "Reduced complexity LDPC decoding using forced convergence"와 같은 강화된 수렴 알고리즘을 얻는다.

- <84> 신뢰도 측정값(r;)에 대한 간단한 선택은 후험적(aposteriori) LLR 메시지 크기, |Q;|이다. 실제로, 본 명세서에서 LS-1로 불리는, 이러한 선택은 상당한 복잡도 감소를 제공한다. 불행하게도, LS-1의 이론적 분석은 큰 문

제점이 있을 수 있다. 이러한 이유로,  $r_i$ 로서 선험적 LLR 채널 메시지 크기,  $|P_i|$ 를 사용하는, 본 명세서에서 LS-2로 불리는, 대안의 접근 방법을 고려한다. 이러한 선택은, 한눈에 최적은 아니라 할지라도, 몇가지 중요한 이점을 가진다. 예를 들어, LS-2의 이론적 분석이 가능하다. 이것은 시뮬레이션을 위한 재분류(resort) 없이, 갱신 확률,  $\beta(1,r_i)$ 의 최적화가 가능하게 한다. 아래에서 보여지는 바와 같이, LS-2는 또한 공평한 복잡도 감소를 제공한다.  $P_i$ 의 값을 기초로 갱신 결정을 내리는 것이 실제로 그렇게 나쁘지 않기 때문에, 결국, 채널 메시지( $P_v$ )를 기초로 반복(1)에서 후험적 메시지( $E[Q_i]$ )의 예상 값을 추정할 수 있다는 것은 놀라운 사실이 아니다. LS-2는 디코딩이 시작한 때 디코딩 스케줄이 완전히 알려지기 때문에, 구현에 이점 또한 가진다.

<85> LS 디코딩 알고리즘은 아래와 같다:

#### Initialization

for all *i* and *j*:  $T_{ii} \leftarrow \varphi(P_i)$

for all j:

$$S_j \leftarrow \sum_{i \in N(j)} T_{ij}$$

,  $R_{ji} \leftarrow \varphi^{-1} (S_j - T_{ij})$

#### Iteration

for all *i*:

execute with probability  $\beta(iteration, |Q_i| \text{ or } |P_i|)$

$$Q_i \leftarrow P_i + \sum_{j \in N(i)} R_{ji}$$

for all  $j \in N(i)$ :

$$S \leftarrow S_{j} - T_{ij}$$

$$R_{ji} \leftarrow \varphi^{-1}(S)$$

$$T_{ij} \leftarrow \varphi(Q_{i} - R_{ji})$$

$$S_{j} \leftarrow S + T_{ij}$$

end of loop

end condition

# <86> end of loop

- <87> 이러한 일반적인 LS 알고리즘에 있어서, 가변 노드(i)가 참여한 마지막 반복 이후 패싱되었던 반복 횟수와 같은, 참가 파라미터(t<sub>i</sub>)에도 의존하는 갱신 확률, β(l,r<sub>i</sub>,t<sub>i</sub>)이 사용된다. 예를 들어, 각각의 가변 노드는 β(l,r<sub>i</sub>,t<sub>i</sub>)=1, t<sub>i</sub>=4를 가짐으로써, 적어도 매 4번째 반복마다 참가하도록 포싱될 수 있다.

- <88> 메시지 패싱 디코딩의 점근(asymptotic) 분석을 위한 표준 도구는 밀도전개(DE:Density Evolution) 알고리즘 (T. J. Richardson and R. Urbanke, "The capacity of low-density parity-check codes under message passing decoding", IEEE Trans. On Info. Theory vol. 47 pp. 599-618, 2001)이다. 이 도구는 디코더에 의해 패싱되는 메시지의 기대 밀도의 반복적인 계산을 기초로 하며, 채널이 무기억(memoryless)이고, 기본적인 이분 그래프가 점근적으로 국부적으로 사이클-프리인 것으로 가정한다. 이러한 가정은, 어떤 시나리오에서, 노드의 모든 인커밍 메시지가 통계적으로 독립적임을 보여주기 위해 사용될 수 있고, 이는 분석을 매우 단순화시킨다. 불행하게도, LS-1 에 대하여, 이것은 LS-1이 DE 분석을 힘들게 만드는 복잡한 통계적 의존을 도입하기 때문에, 해당되지 않는다. 이러한 통계적 의존은 사용된 시리얼 스케줄링에 의해 발생됨은 물론, 후험적 LLR 메시지에 대한 갱신 확률, β(1,|Q₁|)의 의존에 의해 발생된다.

- <89> 본 출원인은 이 분석을 갱신 함수가 선험적 LLR 메시지의 함수인 LS-2으로 한정함으로써 이러한 문제점을 해결

하였다. 또한, LS가 시리얼 스케줄링 대신에 세미-시리얼 스케줄링을 기초로 하는 것으로 가정한다. 세미-시 리얼 스케줄링에서, 가변 노드의 서브셋은 직렬로 갱신되고, 한 서브셋 내의 가변 노드의 메시지는 병렬로 갱신 된다. 'Sharon et al.'에 의해 도시된 바와 같이, 적절하게 정의된 세미-시리얼 스케줄링은 DE 분석을 받을 수 있다. 본 출원인은 이러한 정의를 따른다. 세미-시리얼 스케줄을 생성하기 위해, 각각의 가변 노드에 대하여 1부터 M까지의 정수를 동등한 확률로 독립적으로 선택한다. 이것은 가변 노드가 속하는 서브셋의 개수이다. 이 서브셋은 자신의 서브셋 개수에 따라 시리얼로 갱신된다. 서브셋의 개수, M가 증가함에 따라, 그 세미-시리 얼 스케줄의 기대 수렴율은 시리얼 스케줄의 기대 수렴율에 매우 근접하게 된다. 아래 나타난 시뮬레이션에서, M=100이다.

DE 식을 유도하기 위해, 'Richardson' 및 'Urbanke'와 유사한 접근법을 사용한다.  $f_P$   $f_Q^{(l)}$  및 <90>  $f_{\it Rm}^{(\it I)}$ 는 채널 메시지( $P_{i}$ ), 1번째 반복에서 가변-투-체크 메시지( $Q_{ij}$ ), 1번째 반복에서 m번째 서브셋에 속하는 가변 노드로부터 전송된 가변-투-체크 메시지(Q;;), 및 1번째 반복에서 m번째 서브셋에 속하는 가변 노드로 전송 된 체크-투-가변 메시지 $(R_{ii})$ 의 기대 확률밀도함수(pdf)에 대응하여 나타낸다고 하자. 모든 pdf는 0 코드워드가 전송된다는 가정을 조건으로 한다. 모든 그래프 에지, 앙상블로부터의 모든 트리형 그래프, 모든 세미-시리얼 스케줄, 및 모든 디코더 입력에 걸쳐 예상값이 얻어진다. 그 다음, 예상된 가변-투-체크 메시지 pdf는 다음과 같이 주어진다:

$$\begin{split} f_{Qm}^{(l)}(q) &= \int_{-\infty}^{\infty} f_P(p) \Big( \beta(l,|p|) \lambda(f_{Rm}^{(l)})(q-p) + (1-\beta(l,|p|)) f_Q^{(l-1)}(q) \Big) dp \\ f_{Qm}^{(0)} &= f_P \qquad m=1,...,M \\ f_Q^{(l)} &= \frac{1}{M} \sum_{m=1}^{M} f_{Qm}^{(l)} \end{split}$$

<92>

$\lambda(f) = \sum_{j=2}^{w_c} \lambda_j \otimes^{j-1} f$  이고,  $w_c$ 는 패리타-체크 매트릭스의 임의의 열 내의 1의 최대 개수이고,  $\otimes$ 은 컨벌루션을 나타낸다. 예상된 체크-투-가변 메시지 pd는 다음과 같이 주어진다:

$$f_{Rm}^{(l)} = \Gamma^{-1} \left( \rho \left( \Gamma \left( \frac{1}{M} \left( \sum_{k=1}^{m-1} f_{Qk}^{(l)} + \sum_{k=m}^{M} f_{Qk}^{(l-1)} \right) \right) \right) \right)$$

$\rho(f) = \sum_{j=2}^{r} \rho_j \otimes^{j-1} f$ 여기서,  $\Gamma$ 는 밀도  $f_x$ 를 가진 실 랜덤 변수, X에 대하여,  $\phi(x)$ 의 밀도가  $\Gamma(f_x)$ 이고, <94>

이고. w.이 패리티-체크 매트릭스의 임의의 행 내의 1의 최대 개수이도록 정의된다. 여기서, 컨벌루션은 그룹, F2×[0,∞] 상에서 취해짐을 이해해야 한다.

<95> 이러한 DE 분석을 사용하여, 디코딩 복잡도 함수를 최소화하고, LS에 의해 인공적인 고유 에러 플로어가 도입되 지 않음을 보장하기 위해, 갱신 확률, β(1,|p|)을 최적화할 수 있다. DE 분석은 점근적이지만, 실제 디코딩 복잡도는 코드의 유한한 길이(N)에 의해 영향을 받는다. 그러므로, β(1, |p|)의 최적화를 위해 아래의 대략적 인 유한 길이 노멀라이징된 디코딩 복잡도(NDC) 함수를 사용한다:

$$NDC = \sum_{l=1}^{\infty} P_B^{(l)} \cdot C^{(l)}$$

<91>

<93>

<96>

여기서,  $P_{B}^{(l)}\cong 1-\left(1-P_{b}^{(l-1)}\right)^{N}$  는 알로리즘이 디코딩 반복(1)에 도달하는 시간까지 아직 디코딩되지 않은 코

$P_b^{(l)} = \int\limits_{-\infty}^0 f_Q^{(l)}(q) dq$ 는 1번째 반복 후 예상 BER이고, 드워드의 예상된 비율(fraction)의 어림값이고,

$$C^{(l)} = \int_{-\infty}^{\infty} f_p(p)\beta(l,|p|)dp$$

는 디코딩 반복(1)의 예상 비용이다. 이 덧셈은  $P_B^{(I)}$  가 소정의 임계값 아래로

떨어질 때 종료된다.

- <98> 실제로, 본 출원인은 채널 LLR 메시지 크기를 동등한 간격의 이진수로 동등하게 분할하는 16개의 가능 값을 가진 양자화된 갱신 확률, β(1,|p|)을 사용하였다. LS-1에 대하여, DE 분석이 적용되기 힘들기 때문에, 본 출원인은 그 대신에 디코더의 예상 행동을 대략적으로 모델링하기 위한 시뮬레이션을 사용하였고, 갱신 확률에 대하여 유사한 최적화를 수행하였다. 즉, 본 출원인은 디코더를 몇가지 트라이얼(trial) 갱신 확률 함수를 사용하여 시뮬레이션하였고, 가장 낮은 디코딩 복잡도를 제공한 함수를 선택하였다.

- <9> 본 출원인은 시뮬레이션에서 10<sup>4</sup> 길이의 규칙적인 (3,6) LDPC 코드를 사용하였다. LS는 사용된 반복의 최대 개수가 높을 때, 플러드 또는 시리얼 스케줄링과 비교하여 성능 저하를 도입시키지 않는다. 제한된 횟수의 반복을 가지더라도, 성능 저하는 무시할만하다(0.1dB 미만). 다시 도면을 참조하면, 도 3은 BiAWGN 채널에 대한 시뮬레이션 및 이론적 DE 결과를 도시한다. (BiAWGN 채널은 이진 입력 추가 백색 가우시안 노이즈 채널이다, 즉, BPSK 변조를 가진 추가 백색 가우시안 노이즈 채널이다). 이 곡선은 채널 SNR의 함수로서 다양한 스킴의 노멀라이징된 디코딩 복잡도를 나타낸다. 디코딩 반복의 최대 횟수는 50으로 설정되었고, 그러므로 모든 스킴은 동일한 BER 성능을 제공한다. LS의 복잡도 감소는 채널 SNR 조건에 의존한다. LS-1은 시리얼 스케줄과 비교하여 40-50%, 및 플러딩 스케줄과 비교하여 70-75%의 복잡도 감소를 제공한다. LS-2는 시리얼 스케줄과 비교하여 20-25%, 및 플러딩 스케줄과 비교하여 60-62.5%의 복잡도 감소를 제공한다. 이와 비교하면, 'P. K. Bora', 'E. Zimmermann', 'G. Fettweis' 및 'P. Pattisapu'의, 무선 개인 멀티미디어 통신(WPMC04), 2004, 제7회 국제심포지엄, "Reduced complexity LDPC decoding using forced convergence"의 강화된 수렴 디코더는 성능 손실없이 플러딩 스케줄과 비교하여 단지 35%까지의 복잡도 감소를 제공한다.

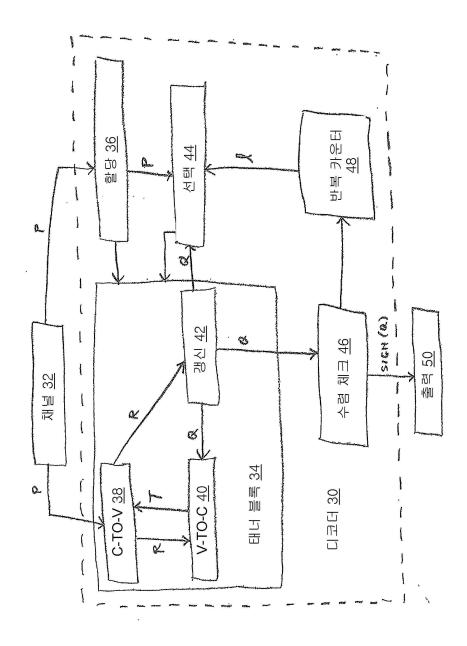

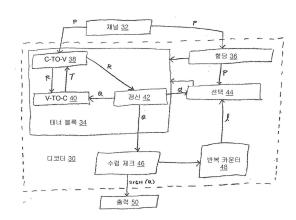

- <100> 본 발명은 하드웨어, 폄웨어, 또는 소프트웨어, 또는 이들의 조합으로 구현될 수 있다. 도 4는 본 발명의 일반적인 디코더(30)의 기능 블록 다이어그램이다. 도 4의 기능 블록은 하드웨어, 펌웨어, 또는 소프트웨어, 또는 이들의 조합으로 구현될 수 있다. 도 4는 또한 본 발명의 방법의 바람직한 실시예의 플로우 차트로서역할한다.

- <101> 디코더(30)는 노이즈 있는 채널(32)로부터, 한 세트의 소프트 비트{P<sub>i</sub>}의 형태인, 코드워드를 수신한다. 할당 모듈(36)은 각각의 소프트 비트를 각각의 가변 노드에 할당한다. 각각의 디코딩 반복의 시작점에서, 선택 모듈 (44)은 반복 횟수(1)에 따라, 그리고 입력 소프트 비트{P<sub>i</sub>}(LS-2) 또는 디코딩 반복의 시작점에서 소프트 비트 의 값 $\{Q_i\}(LS-1)$ 에 따라 디코딩 반복에 참가할 가변 노드를 선택한다. 체크-노드-투-가변-노드 모듈(38) 및 가 변-노드-투-체크-노드 모듈(40)을 포함하는 태너 그래프 모듈 블록(34)은 할당 모듈(36)로부터 가변 노드 할당 을 수신하고, 선택 모듈(44)로부터 가변 노드 선택을 수신한다. 체크-노드-투-가변-노드 모듈(38)은, 각각의 체크 노드(j)에 대하여, 그 체크 노드(j)에 연결되어 있는 참가하는 가변 노드(i)로 전송하기 위한 메시지(R<sub>ii</sub>) 를 계산하고, 그 메시지(R<sub>ii</sub>)를 각각의 가변 노드로 전송한다. 갱신 모듈(42)은 가변 노드가 현재 디코딩 반복 에서 체크 노드로부터 수신한 메시지 $(R_{ij})$ 에 따라 참가하는 가변 노드(i)의 소프트 비트 $(Q_i)$ 를 갱신한다. 가변-노드-투-체크-노드 모듈(40)은, 각각의 참가하는 가변 노드(i)에 대하여, 그 가변 노드(i)에 연결되어 있는 체 크 노드(j)로 전송하기 위한 메시지( $T_{ij}$ )를 계산하고, 그 메시지( $T_{ij}$ )를 각각의 체크 노드로 전송한다. 체크 노 드는, 그 가변 노드가 현재 디코딩 반복에 참가하든 참가하지 않든, 체크 노드가 연결되어 있는 모든 가변 노드 로부터 가장 최근에 수신된 가변-노드-투-체크-노드 메시지를 기초로 체크-노드-투-가변-노드 메시지를 계산함 을 이해해야 한다. 수렴 체크 모듈(46)은 현재의 디코딩 반복이 수렴하였는지를 판단한다. 현재의 디코딩 반 복이 수렴하였다면, 수렴 체크 모듈(46)은 디코딩된 코드워드(50)를 출력한다. 그렇지 않다면, 수렴 체크 모듈 (46)은 반복 카운터(48) 내의 1을 증가시키고, 디코더(30)는 다음 디코딩 반복으로 진행한다.

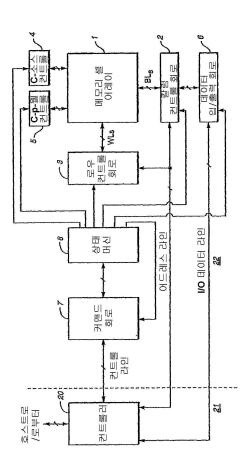

- <102> 도 5는 'Chen et al.'의 US 6,522,580의 도 1로부터 취한 도면으로, 본 발명의 플래시 메모리 디바이스의 블록다이어그램이다. 매트릭스 내에 정렬된 복수의 메모리 셀(M)을 포함하는 메모리 셀 어레이(1)는 칼럼 컨트롤회로(2), 로우 컨트롤 회로(3), C-소스 컨트롤 회로(4), 및 C-p-웰 컨트롤 회로(4)에 의해 컨트롤된다. 칼럼 컨트롤 회로(2)는 메모리 셀(M)에 저장된 데이터를 판독하기 위해, 프로그램 오퍼레이션 동안 메모리 셀(M)의 상태를 판단하기 위해, 그리고 프로그래밍을 촉진하거나, 프로그래밍을 차단하기 위해 비트 라인(BL)의 전압 레

벨을 컨트롤하기 위해 비트 라인(BL)에 연결되어 있다. 로우 컨트롤 회로(3)는 하나의 워드 라인(WL)을 선택하기 위해, 판독 전압을 인가하기 위해, 칼럼 컨트롤 회로(2)에 의해 컨트롤되는 비트 라인 전압 레벨과 결합된 프로그래밍 전압을 인가하기 위해, 그리고 메모리 셀(M)이 형성되어 있는 p-타입 영역의 전압과 연결된 삭제 전압을 인가하기 위해, 워드 라인(WL)에 연결된다. C-소스 컨트롤 회로(4)는 메모리 셀(M)에 연결된 공통 소스라인을 컨트롤한다. C-p-웰 컨트롤 회로(4)는 C-p-웰 전압을 컨트롤한다. 전형적으로, NAND 플래시 디바이스에서, 하나의 워드 라인에 의해 컨트롤되는 셀은 그 디바이스의 하나 또는 두 페이지에 대응한다.

- <103> 메모리 셀(M)에 저장된 데이터는 칼럼 컨트롤 회로(2)에 의해 판독되고, I/O 라인 및 데이터 입/출력 버퍼(6)를 통해 외부 I/O 라인으로 출력된다. 메모리 셀에 저장될 프로그램 데이터는 외부 I/O 라인을 통해 데이터 입/출력 버퍼(6)로 입력되고, 칼럼 컨트롤 회로(2)로 전달된다. 외부 I/O 라인은 컨트롤러(20)에 연결된다.

- <104> 플래시 메모리 디바이스를 컨트롤하기 위한 커맨드 데이터는 컨트롤러(20)에 연결되어 있는 외부 컨트롤 라인에 연결된 커맨드 인터페이스로 입력된다. 커맨드 데이터는 플래시 메모리에 어떤 오퍼레이션이 필요한지 알린다. 입력된 커맨드는 칼럼 컨트롤 회로(2), 로우 컨트롤 회로(3), C-소스 컨트롤 회로(4), C-p-웰 컨트롤 회로(4), 및 데이터 입/출력 버퍼(6)를 컨트롤하는 상태 머신(8)으로 전달된다. 상태 머신(8)은 'READY/BUSY' 또는 'PASS/FAIL'과 같은 플래시 메모리의 상태 데이터를 출력할 수 있다.

- 전트롤러(20)는 퍼스널 컴퓨터, 디지털 카메라, 개인 휴대 정보 단말기와 같은 호스트 시스템에 연결되거나 연결가능하다. 호스트는 메모리 어레이(1)에 데이터를 저장하거나, 그로부터 데이터를 판독하기 위한 커맨드를 초기화하고, 이러한 데이터를 각각 제공하거나 수신한다. 컨트롤러(20)는 이러한 커맨드를 커맨드 회로(7)에 의해 해석되고 실행될 수 있는 커맨드 신호로 변환한다. 컨트롤러(20)는 또한 메모리 어레이(1)에 기록되거나, 그로부터 판독될 사용자 데이터에 대한 버퍼 메모리를 포함하는 것이 전형적이다. 전형적인 메모리 디바이스는 컨트롤러(20)를 포함하는 하나의 집적회로 칩(21), 및 각각 메모리 어레이 및 관련 컨트롤, 입/출력, 및 상태 머신 회로를 포함하는 하나 이상의 집적회로 칩(22)을 포함한다. 물론, 하나 이상의 집적회로 칩 상에 디바이스의 메모리 어레이와 컨트롤러 회로를 함께 집적하는 것이 추세이다. 메모리 디바이스는 호스트 시스템의 일부분에 내장될 수 있고, 또는 호스트 시스템의 접합 소켓에 제거가능하게 삽입가능한 메모리 카드에 포함될 수도 있다. 이러한 카드는 전체 메모리 디바이스를 포함할 수 있고, 또는 관련 주변 회로와 함께 컨트롤러, 및 메모리 어레이는 개별 카드내에 제공될 수도 있다.

- <106> 메모리 어레이(1)에 저장된 데이터는 메모리 셀(M)의 임계전압으로서 인코딩된다. 메모리 셀의 임계전압은 하나 이상의 비트 값을 나타내는 심벌에 대응한다. 이러한 심벌의 세트는 통신 시스템의 신호 배열 (constellation)과 유사한 신호 배열을 구성한다. 칼럼 컨트롤 회로(2)는, 디지털 수신기의 회로가 수신된 심벌을 수신된 비트의 LLR로 변환하는 것처럼, 판독되는 메모리 셀(M)의 임계전압을 그 셀에 저장된 비트의 LLR로 변환한다. 2006년 12월 21일에 출원된 미국특허출원 제11/642,708호는 셀당 한비트의 플래시 셀의 임계 전압을 LLR로서 판독하는 방법의 예를 포함한다.

- <107> 본 발명의 플래시 메모리 디바이스의 몇몇 바람직한 실시예에서, 칼럼 컨트롤 회로(2)는 또한 메모리 어레이 (1)에 저장될 코드워드와 같은 데이터의 LDPC 인코딩을 위한 회로, 및 메모리 어레이(1)로부터 판독된 에러 가능성이 있는 코드워드의, 본 발명의 방법에 따른, LDPC 디코딩을 위한 회로를 포함한다. 본 발명의 플래시 메모리 디바이스의 다른 바람직한 실시예에서, 컨트롤러(20)는 메모리 어레이(1)에 저장될 코드워드와 같은 데이터의 LDPC 인코딩, 및 메모리 어레이(1)로부터 판독된 에러 가능성이 있는 코드워드의, 본 발명의 방법에 따른, LDPC 디코딩을 수행한다. 이러한 두 실시예 모두에서, 커맨드 회로(7)의 디코딩 회로가 디코딩될 코드워드를 수신하는 "채널"은 메모리 어레이(1)와 데이터 입/출력 버퍼(6)의 조합이다.

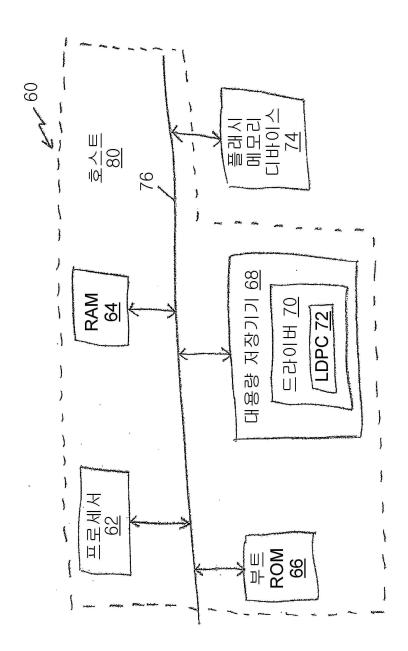

- <108> 도 6은 본 발명의 시스템(60)의 하이-레벨 블록 다이어그램이다. 시스템(60)은 프로세서(62), 및 4개의 메모리 디바이스: 모두 공통 버스(76)를 통해 통신하는 RAM(64), ROM(66), 대용량 저장 디바이스(68)(하드 디스크), 및 종래기술의 플래시 메모리 디바이스(74)를 포함한다. 플래시 메모리 디바이스(74)의 소프트웨어 드라이버(70)는 대용량 저장 디바이스(68)에 저장되고, 플래시 메모리 디바이스(74)에 액세스하기 위해 프로세서(62)에 의해 실행된다. 드라이버(70)는 본 발명의 방법을 사용하여 플래시 메모리 디바이스(74)에 저장될 데이터를 인코딩하고, 플래시 메모리 디바이스(74)로부터 수신된 코드워드를 디코딩하기 위한 LDPC 모듈(72)을 포함한다. 시스템(60)에서, 자신을 통해 디코딩될 코드워드가 프로세서(62)에 의해 수신되는 "채널"은 플래시 메모리 디바이스(74) 및 버스(76)를 포함한다.

- <109> 도 6에서, 시스템(60)의 플래시 메모리 디바이스(74) 이외의 컴포넌트는 플래시 메모리 디바이스(74)의 호스트 (80)를 구성한다. 대용량 저장 디바이스(68)는 본 발명을 구현하기 위한 컴퓨터 판독가능한 코드를 내장한 컴

퓨터 판독가능한 저장 매체의 하나의 예이다. 이러한 컴퓨터 판독가능한 저장 매체의 다른 예는 이러한 코드를 내장한 CD 와 같은 판독전용 메모리를 포함한다.

- <110> 일반적인 래지 스케줄링 디코딩 알고리즘은 "다이렉티드" 태너 그래프를 사용한다. 다이렉티드 태너 그래프에서, 각각의 가변 노드는 두개의 에지, 가변 노드 에지 및 체크 노드 에지에 의해 각각의 체크 노드에 연결된다. 메시지는 가변 노드 에지를 따라 그들 각각의 가변 노드에서부터 그들 각각의 체크 노드로 패싱된다. 메시지는 체크 노드를 따라 그들 각각의 체크 노드로부터 그들 각각의 가변 노드로 패싱된다. 도 7은 도 1의 태너 그래 프가 다이렉티드 태너 그래프를 산출하기 위해 어떻게 변형되는지를 도시한다. 각각의 가변 노드(c<sub>i</sub>)는 두개의에지: c<sub>i</sub>에서부터 f<sub>j</sub>로 포인팅하는 가변 노드 에지(90), 및 f<sub>j</sub>에서부터 c<sub>i</sub>로 포인팅하는 체크 노드 에지(92)에의해 각각의 자신의 체크 노드(f<sub>j</sub>)에 연결된다.

- <111> 메시지 패싱 디코딩 스케줄은 에지의 정렬된 목록을 생성함으로써 형성된다. 예를 들어, 플러딩 스케줄에 대한 순서는 다음과 같다:

- <112> 가변 노드(c<sub>1</sub>)의 가변 노드 에지

- <113>

- <114>

- <115>

- <116> 가변 노드(c<sub>n</sub>)의 가변 노드 에지

- <117> 가변 노드(c<sub>1</sub>)의 체크 노드 에지

- <118>

- <119>

- <120>

- <121> 가변 노드(c<sub>n</sub>)의 체크 노드 에지

- <122> 그리고, 'Sharon et al.'의 시리얼 스케줄에 대한 순서는 다음과 같다:

- <123> 가변 노드(c<sub>1</sub>)의 가변 노드 에지

- <124> 가변 노드(c<sub>1</sub>)의 체크 노드 에지

- <125> 가변 노드(c2)의 가변 노드 에지

- <126> 가변 노드(c<sub>2</sub>)의 체크 노드 에지

- <127>

- <128>

- <129>

- <130> 가변 노드(c<sub>n</sub>)의 가변 노드 에지

- <131> 가변 노드(cn)의 체크 노드 에지

- <132> 각각의 디코딩 반복에서, 에지의 목록은 트래버싱되고, 그 에지가 그 에지를 따라 패싱된 하나 이상의 메시지를 가짐으로써 현재의 디코딩 반복에 참가하는지 여부가, 가변 노드에 대하여 앞서 사용된 선택 기준과 유사한 하나 이상의 선택 기준에 따라, 각각의 에지에 대하여, 개별적으로 결정된다. 본 발명의 이러한 변형의 하나의 세트의 실시예에서, 에지의 참가는 그 에지와 관련된 신뢰도 수치를 개연적으로 조건으로 한다. 예를 들어, |Q<sub>i</sub>|는 가변 노드(c<sub>i</sub>)가 소프트 비트(i)의 현재 추정값(Q<sub>i</sub>)의 것임을 얼마나 확신하는지의 측정값이다. 이와 유사하게, 가변 노드(c<sub>i</sub>)로부터 체크 노드(f<sub>i</sub>)로, 가변 노드(c<sub>i</sub>)로부터 체크 노드(f<sub>i</sub>)로 포인팅하는 가변 노드 에

지(90)를 따라 전송되는 메시지( $Q_{ij}$ )는 가변 노드( $c_i$ )가 체크 노드( $f_j$ )를 제외한 모든 체크 노드로부터 가장 최근에 수신한 메시지를 기초로 하는 소프트 비트(i)의 현재 추정값이고,  $|Q_{ij}|$ 는 가변 노드( $c_i$ )가  $Q_i$ 의 것임을 얼마나 확신하는지의 측정값이다. 이와 유사하게, 체크 노드( $f_j$ )로부터 가변 노드( $c_i$ )로, 체크 노드( $f_j$ )로부터 가변 노드( $c_i$ )로 포인팅하는 체크 노드 에지( $g_i$ )를 따라 전송되는 메시지( $g_i$ )는 소프트 비트( $g_i$ )에 대한 체크 노드( $g_i$ )의 현재 제안된 보정이고,  $|g_i|$ 는 체크 노드( $g_i$ )가  $g_i$ 에 대한 제안된 보정의 것임을 얼마나 확신하는지의 측정값이다. 이와 유사하게,  $|g_i|$ 는 체크 노드( $g_i$ )의 신뢰도의 측정값, 즉, 체크 노드( $g_i$ )에 연결된 모든 가변 노드의 현재 소프트 비트 추정값의 전체적인 신뢰도의 측정값이다. 직관적으로, 이들 크기가 높을수록, 현재 디코딩 반복 내의 연관된 에지를 따라 메시지를 전송하는 것이 덜 중요해진다. 예를 들어,  $|g_i|$ 가 높을수록, 현재 디코딩 반복에서  $g_i$ 를 갱신할 필요성이 줄어든다.

- <133> 다른 선택 기준은, 예컨대, 짝수의 디코딩 반복을 짝수의 에지로 제한하고, 홀수의 디코딩반복을 홀수의 에지로 제한하는, 디코딩 반복의 일련번호의 함수, 및, 예컨대, 에지가 5개의 가장 최근의 디코딩 반복에 참가하지 않았다면, 그 에지를 참가하도록 포싱하는, 에지 참가 히스토리의 함수를 포함한다.

- <134> 바람직하게는, 둘 이상의 에지의 메시지는 병렬로 패싱된다. 병렬 구현 방법은 주지되어 있다. 예를 들어, 'Sharon et al.'은 자신의 시리얼 스케줄의 병렬 구현을 사용하였다. 실제 어플리케이션에서, 병렬화는 통상적으로 요구되는 높은 쓰루풋을 달성하기 위해 필요하다.

- <135> 본 발명은 한정된 개수의 실시예에 관하여 서술되었으나, 본 발명의 다양한 변형, 수정 및 다른 어플리케이션이 이루어질 수 있음이 이해될 것이다.

# 도면의 간단한 설명

- <74> 본 발명은 첨부된 도면을 참조하여, 예시의 방법으로, 본 명세서에 서술되어 있다.

- <75> 도 1은 태너 그래프를 도시하고;

- <76> 도 2는 본 발명의 통신 시스템의 블록 다이어그램이고;

- <77> 도 3은 본 발명의 3가지 디코딩 스킴 vs. 두 가지 종래기술의 디코딩 스킴의 노멀라이징된 디코딩 복잡도의 그 래프이고;

- <78> 도 4는 본 발명의 일반적인 디코더의 블록 다이어그램이고;

- <79> 도 5는 본 발명의 시스템의 플래시 메모리 디바이스의 블록 다이어그램이고;

- <80> 도 6은 본 발명의 시스템의 블록 다이어그램이고;

- <81> 도 7은 다이랙티드 태너 그래프를 도시한다.

도면4