(72) 발명자

린 총후아

중화민국 대만 타이페 푸싱 사우스 로드 섹터 2 넘

버 198 4에프

시에 형창

중화민국 대만 신주 시티 쿵푸 로드 섹터 1 레인

531 넘버 72-12 9에프

## 명세서

### 청구범위

#### 청구항 1

핀형 전계 효과 트랜지스터(FinFET, fin-like field-effect transistor) 소자를 제조하기 위한 방법에 있어서, 기판을 수용하는 단계;

상기 기판 위에 복수의 맨드릴 피쳐(mandrel feature)들을 형성하는 단계;

제1 공간을 형성하도록 하나 이상의 맨드릴 피쳐들을 제거하기 위하여 제1 컷(cut)을 수행하는 단계;

라인-엔드(line-end) 및 엔드-투-엔드(end-to-end) 공간을 형성하도록 하나 이상의 맨드릴 피쳐들의 일부분을 제거하기 위하여 제2 컷을 수행하는 단계;

상기 제1 컷 및 상기 제2 컷 이후에, 핀들을 형성하기 위하여 상기 엔드-투-엔드 공간 및 상기 제1 공간을 갖는 상기 맨드릴 피쳐들을 에칭 마스크로서 사용하여 상기 기판을 에칭하는 단계;

상기 에칭 이후에, 상기 맨드릴 피쳐들을 제거하는 단계;

인접한 핀들 사이의 공간 내를 완전히 충진하고, 상기 엔드-투-엔드 공간 및 상기 제1 공간에 인접한 상기 핀들 사이의 측벽들을 커버하기 위하여, 스페이서 층을 성막하는 단계;

상기 엔드-투-엔드 공간 및 상기 제1 공간에 인접한 상기 핀들 상에 측벽 스페이서들을 형성하기 위하여 상기 스페이서 층을 에칭하는 단계; 및

상기 인접한 핀들 사이의 공간 내를 충진하는 상기 스페이서 층 및 상기 핀들을 커버하는 상기 측벽 스페이서들로 상기 엔드-투-엔드 공간 및 상기 제1 공간 내에 절연 트렌치를 형성하는 단계

를 포함하는, 핀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

#### 청구항 2

제1항에 있어서,

상기 스페이서 층을 성막하는 단계 동안, 상기 제1 공간 및 상기 엔드-투-엔드 공간 양자 모두는 부분적으로 충진되고, 2개의 인접한 핀들 사이의 공간은 완전히 충진되는 것인, 핀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

#### 청구항 3

제1항에 있어서,

상기 스페이서 층을 에칭하는 에칭 프로세스는 상기 제1 공간과 상기 엔드-투-엔드 공간 내의 스페이서 층을 제거하여 상기 스페이서 층으로 충진된 2개의 인접한 핀들 사이에 공간을 남기도록 제어되는 것인, 핀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

#### 청구항 4

제1항에 있어서,

상기 절연 트렌치는 상기 제1 공간 및 상기 엔드-투-엔드 공간 내의 상기 측벽 스페이서들을 사용하여 상기 기판을 자가-정렬 에칭함으로써 형성되는 것인, 핀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

#### 청구항 5

제4항에 있어서,

상기 절연 트렌치는 상기 엔드-투-엔드 공간의 폭 및 상기 제1 공간의 폭에 비하여 더 작은 폭을 갖도록 형성되

는 것인, 펀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

### 청구항 6

제1항에 있어서,

절연 유전체 층으로 상기 절연 트렌치 내를 충진하는 단계; 및

상기 절연 트렌치 내에 절연 피쳐를 형성하기 위하여 상기 절연 유전체 층을 리세스하는 단계

를 더 포함하는, 펀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

### 청구항 7

제6항에 있어서,

상기 절연 유전체 층으로 상기 절연 트렌치 내를 충진하는 단계 이후에, 상기 펀들의 측벽들을 드러내기 위해 상기 인접한 펀들 사이의 상기 스페이서 층을 제거하는 단계를 더 포함하는, 펀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

### 청구항 8

제1항에 있어서,

상기 맨드릴 피쳐들을 형성하는 단계 이전에, 상기 기판 위에 하드 마스크를 성막하는 단계; 및

상기 펀들을 형성하기 위하여 상기 기판을 에칭하는 단계 동안에, 상기 하드 마스크의 부분들이 상기 펀들의 상부 층들이 되도록 상기 하드 마스크를 에칭하는 단계

를 더 포함하는, 펀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

### 청구항 9

핀형 전계 효과 트랜지스터(FinFET, fin-like field-effect transistor) 소자를 제조하기 위한 방법에 있어서, 하드 마스크를 갖는 기판을 수용하는 단계;

상기 하드 마스크 위에 복수의 맨드릴 피쳐들을 형성하는 단계;

제1 공간을 형성하기 위하여 하나 이상의 맨드릴 피쳐들을 제거하는 단계;

라인-엔드(line-end) 및 엔드-투-엔드(end-to-end) 공간을 형성하기 위하여 적어도 하나의 맨드릴 피쳐들의 일부분을 제거하는 단계;

상기 하드 마스크와 상기 기판을 에칭하여 펀들을 형성하기 위하여, 상기 제1 공간 및 상기 엔드-투-엔드 공간을 갖는 상기 맨드릴 피쳐들을 에칭 마스크로서 사용하는 단계;

상기 에칭 이후에, 상기 맨드릴 피쳐들을 제거하는 단계;

상기 기판 위에 스페이서 층을 성막하는 단계 – 상기 성막하는 단계는, 2개의 인접한 펀들 사이의 공간 내를 완전히 충진하는 단계, 상기 제1 공간 및 상기 엔드-투-엔드 공간 내의 상기 펀들의 측벽들을 커버하는 단계, 및 상기 제1 공간 및 상기 엔드-투-엔드 공간 내를 부분적으로 충진하는 단계를 포함함 – ;

상기 제1 공간 및 상기 엔드-투-엔드 공간 내의 상기 펀들 상에 측벽 스페이서들을 형성하기 위하여 그리고 상기 기판을 노출시키도록 상기 제1 공간과 상기 엔드-투-엔드 공간의 바닥부들에서 상기 스페이서 층을 제거하기 위하여, 스페이서 에칭을 수행하는 단계;

절연 트렌치를 형성하기 위하여 상기 노출된 기판을 에칭하는 단계;

절연 유전체 층으로 상기 절연 트렌치를 충진하는 단계;

인접한 펀들 사이의 공간 사이에 있는 상기 스페이서 층을 제거하는 단계; 및

상기 절연 트렌치 내에 절연 피쳐를 형성하기 위하여 상기 절연 유전체 층을 리세스하는 단계

를 포함하는, 펀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

## 청구항 10

핀형 전계 효과 트랜지스터(FinFET, fin-like field-effect transistor) 소자를 제조하기 위한 방법에 있어서, 기판을 제공하는 단계;

상기 기판 위에 복수의 맨드릴 피쳐(mandrel feature)들을 형성하는 단계;

제1 공간을 형성하도록 하나 이상의 맨드릴 피쳐들을 제거하기 위하여 제1 컷(cut)을 수행하는 단계;

라인-엔드(line-end) 및 엔드-투-엔드(end-to-end) 공간을 형성하도록 하나 이상의 맨드릴 피쳐들의 일부분을 제거하기 위하여 제2 컷을 수행하는 단계;

상기 제1 컷 및 상기 제2 컷 이후에, 상기 기판 위에 복수의 핀들을 형성하기 위하여 상기 엔드-투-엔드 공간 및 상기 제1 공간을 갖는 상기 맨드릴 피쳐들을 에칭 마스크로서 사용하여 상기 기판을 에칭하는 단계;

상기 에칭 이후에, 상기 맨드릴 피쳐들을 제거하는 단계;

상기 핀들 사이에 제1 공간 및 엔드-투-엔드(end-to-end) 공간을 형성하는 단계;

인접한 핀들 사이의 공간 내를 충진하고 상기 제1 공간과 상기 엔드-투-엔드 공간 내의 상기 핀들의 측벽들을 커버하기 위하여, 스페이서 층을 성막하는 단계;

상기 제1 공간 및 상기 엔드-투-엔드 공간 내에서 상기 핀들 상에 측벽 스페이서들을 형성하는 단계;

상기 제1 공간 및 상기 엔드-투-엔드 공간 내에 절연 트렌치를 형성하는 단계 – 상기 핀들은 상기 스페이서 층 및 상기 스페이서에 의하여 보호됨 – ; 및

절연 유전체 층을 성막함으로써 상기 절연 트렌치 내에 절연 피쳐를 형성하는 단계

를 포함하는, 핀형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법.

## 발명의 설명

### 배경 기술

[0001]

반도체 집적 회로(IC) 산업은 급속한 성장을 경험해왔다. IC의 발전 동안에, 기능적 밀도(즉, 칩 면적 당 상호 연결된 소자들의 수)는 일반적으로 증가해온 반면, 기하학적 사이즈(즉, 제조 프로세스를 사용하여 생성될 수 있는 가장 작은 컴포넌트(또는 라인))는 감소해왔다. 이러한 스케일링 다운=scaling down) 프로세스는 일반적으로 제조 효율을 증가시키고 관련 비용을 낮춤으로써 이익들을 제공한다.

[0002]

IC들의 프로세싱 및 제작의 복잡성은 또한 증가하였으며, 이러한 진보들이 실현되기 때문에, IC 프로세싱 및 제작에 있어서의 유사한 개발들이 필요하다. 예를 들어, 핀형 전계 효과 트랜지스터(FinFET, fin-like field-effect transistor)와 같은 3차원 트랜지스터가 평면 트랜지스터를 교체하기 위하여 도입되었다. 현존하는 FinFET 소자들 및 FinFET 소자들의 제조 방법들은 일반적으로 그들의 의도된 목적들을 위해 적응되어 왔으나, 그들은 모든 점에 있어서 완전히 만족스럽지 않을 수도 있다. 예를 들어, 핀 및 절연 구조물들을 형성하기 위한 더욱 플렉서블한 통합이 요구된다.

## 발명의 내용

[0003]

본 개시물은 현존하는 접근법들에 대해 하나 이상의 향상들을 제공하는 FinFET 소자를 제작하는 다수의 상이한 실시예들을 제공한다. 일 실시예에서, FinFET 소자를 제작하기 위한 방법은 기판을 수용하는 단계, 기판 위에 맨드릴 피쳐들을 형성하는 단계를 포함한다. 방법은 제1 공간을 형성하도록 하나 이상의 맨드릴 피쳐들의 일부를 제거하기 위하여 제2 컷을 수행하는 단계를 또한 포함한다. 방법은 제1 컷 및 상기 제2 컷 이후에, 핀들을 형성하기 위하여 에칭 마스크로서 엔드-투-엔드 공간 및 제1 공간을 갖는 맨드릴 피쳐들을 사용함으로써 기판을 에칭하는 단계를 또한 포함한다. 방법은 인접한 핀들 사이의 공간 내를 완전히 충진하고, 엔드-투-엔드 공간 및 제1 공간에 인접한 상기 핀들의 측벽들을 커버하기 위하여, 스페이서 층을 성막하는 단계를 또한 포함한다. 방법은 엔드-투-엔드 공간 및 제1 공간에 인접한 핀들 상에 측벽 스페이서들을 형성하기 위하여 스페이서 층을 에칭하는 단계, 및 인접한 핀들 사이의 공간 내를 충진하는 스페이서 층 및 핀들을 커버하는 측

벽 스페이서들로 엔드-투-엔드 공간 및 제1 공간 내에 절연 트렌치를 형성하는 단계를 또한 포함한다.

[0004] 다른 실시예에서, FinFET 소자를 제조하기 위한 방법은, 하드 마스크를 갖는 기판을 수용하는 단계, 하드 마스크 위에 복수의 맨드릴 피쳐들을 형성하는 단계, 제1 공간을 형성하기 위하여 하나 이상의 맨드릴 피쳐들을 제거하는 단계, 엔드-투-엔드 공간을 형성하기 위하여 적어도 하나의 맨드릴 피쳐들의 중간 부분을 제거하는 단계를 포함한다. 방법은 펈들을 형성하기 위하여 맨드릴 피쳐들을 사용하여 하드 마스크 및 기판을 에칭하기 위한 에칭 마스크로서 제1 공간 및 엔드-투-엔드 공간을 사용하는 단계를 또한 포함한다. 방법은 에칭 이후에, 맨드릴 피쳐들을 제거하는 단계를 또한 포함한다. 방법은 기판 위에 스페이서 층을 성막하는 단계를 또한 포함하며, 상기 성막하는 단계는, 2개의 인접한 펈 사이의 공간 내를 완전히 충진하는 단계, 제1 공간 및 엔드-투-엔드 공간 내의 상기 펈들의 측벽들을 커버하는 단계, 및 제1 공간 및 엔드-투-엔드 공간 내를 부분적으로 충진하는 단계를 포함한다. 방법은 제1 공간 및 엔드-투-엔드 공간 내의 펈 상에 측벽 스페이서들을 형성하기 위하여 그리고 기판을 노출시키도록 제1 공간과 엔드-투-엔드 공간의 바닥부들에서 스페이서 층을 제거하여, 스페이서 에칭을 수행하는 단계를 또한 포함한다. 방법은 절연 트렌치를 형성하기 위하여 노출된 기판을 에칭하는 단계, 절연 유전체 층으로 절연 트렌치 내를 충진하는 단계를 또한 포함한다. 방법은 절연 트렌치 내에 절연 피쳐를 형성하기 위하여 절연 유전체 층을 리세스하는 단계, 및 인접한 펈 사이에 스페이서 층을 제거하는 단계를 또한 포함한다.

[0005] 또 다른 실시예에서, 편형 전계 효과 트랜지스터(FinFET) 소자를 제조하기 위한 방법은, 기판을 제공하는 단계, 기판 위에 복수의 펈들을 형성하는 단계, 펈 사이에 제1 공간 및 엔드-투-엔드 공간을 형성하는 단계, 인접한 펈 사이의 공간 내를 충진하고 제1 공간 및 엔드-투-엔드 공간 내의 펈들의 측벽들을 커버하기 위하여 스페이서 층을 성막하는 단계, 제1 공간 및 엔드-투-엔드 공간 내의 펈 상에 측벽 스페이서들을 형성하는 단계, 제1 공간 및 엔드-투-엔드 공간 내에 절연 트렌치를 형성하는 단계 – 펈들은 스페이서 및 스페이서 층에 의해 보호됨 –, 및 절연 유전체 층을 성막함으로써 절연 트렌치 내에 절연 피쳐를 형성하는 단계를 포함한다.

[0006] 본 개시물은 첨부된 도면들과 함께 판독될 때 하기의 상세한 설명으로부터 가장 잘 이해된다. 산업 분야의 표준 관행에 따라, 다양한 피쳐들은 축적에 따라 그려지지 않으며, 단지 예시를 목적으로 사용됨이 강조된다. 사실상, 다양한 피쳐들의 차원들은 논의의 명료성을 위해 임의적으로 증가되거나 감소될 수 있다.

### 도면의 간단한 설명

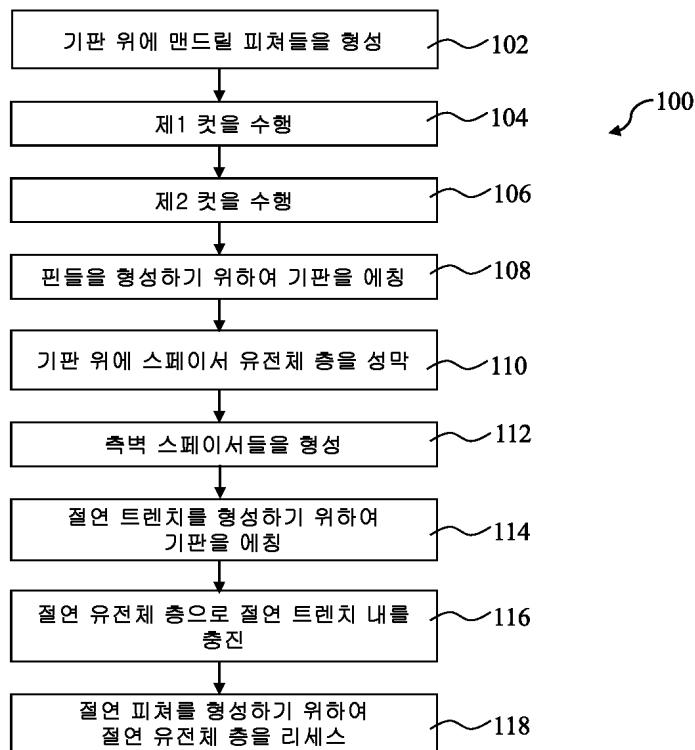

[0007] 도 1은 본 개시물의 다양한 양상들에 따른 반도체 소자를 제조하기 위한 예시적인 방법의 흐름도이다.

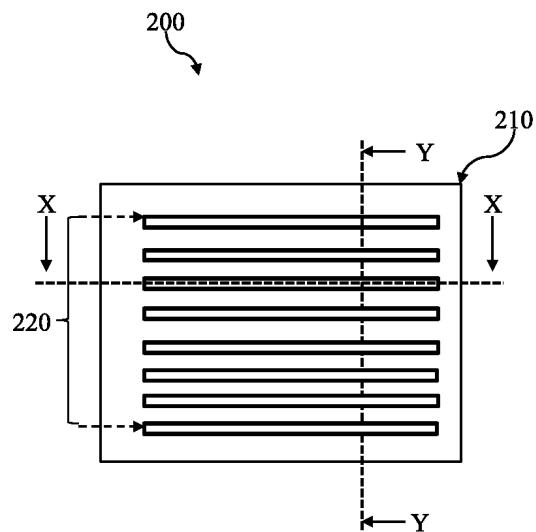

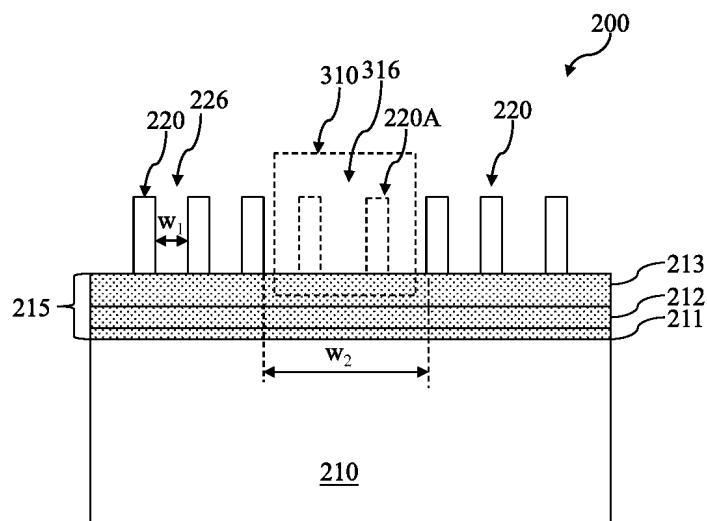

도 2a는 도 1의 방법에 따라 구성되는 제조 스테이지들에서의 FinFET 소자의 도식적 상부도이다.

도 2b는 도 1의 방법에 따라 구성되는 제조 스테이지들에서의 도 2a에서 라인 Y-Y를 따르는 예시적인 FinFET 소자의 단면도이다.

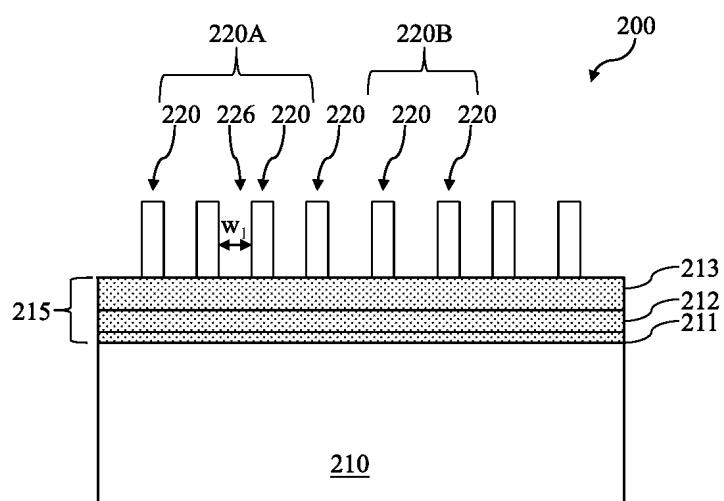

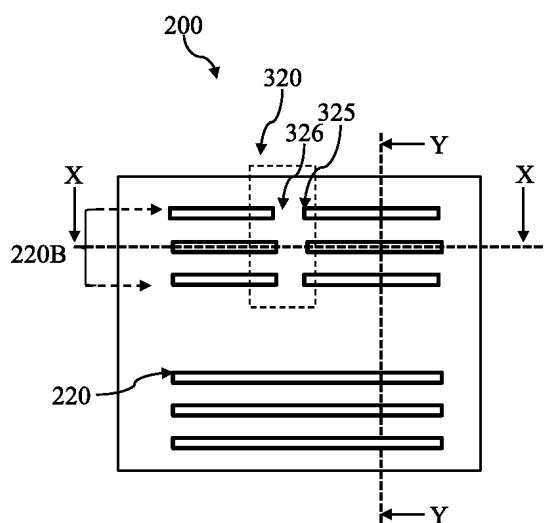

도 3a는 도 1의 방법에 따라 구성되는 제조 스테이지들에서의 FinFET 소자의 도식적 상부도이다.

도 3b는 도 1의 방법에 따라 구성되는 제조 스테이지들에서의 도 3a에서 라인 X-X를 따르는 예시적인 FinFET 소자의 단면도이다.

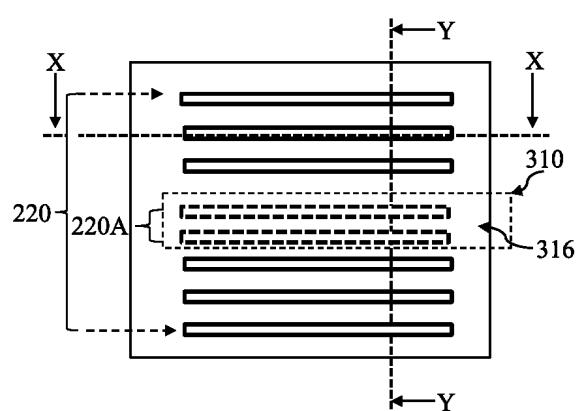

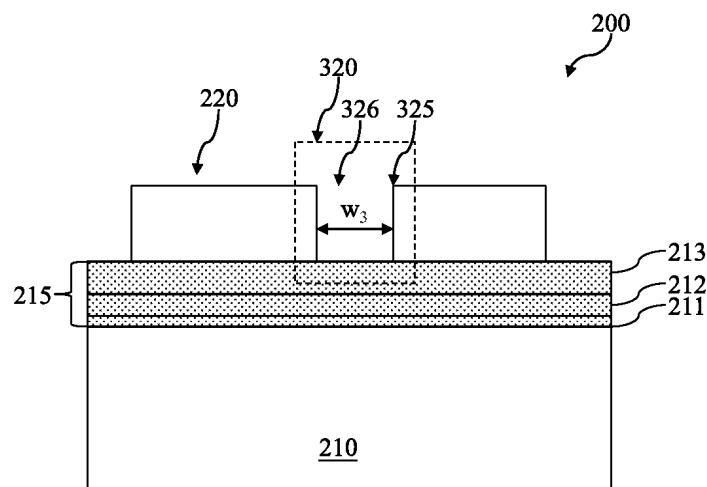

도 4a는 도 1의 방법에 따라 구성되는 제조 스테이지들에서의 FinFET 소자의 도식적 상부도이다.

도 4b는 도 1의 방법에 따라 구성되는 제조 스테이지들에서의 도 4a에서 라인 Y-Y를 따르는 예시적인 FinFET 소자의 단면도이다.

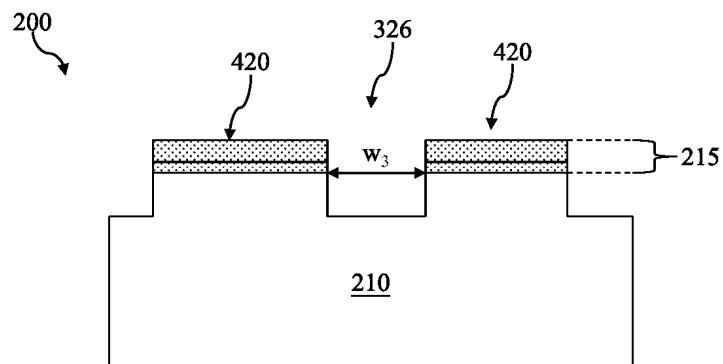

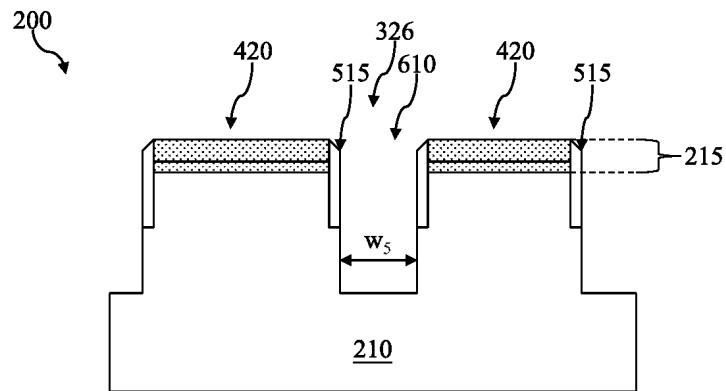

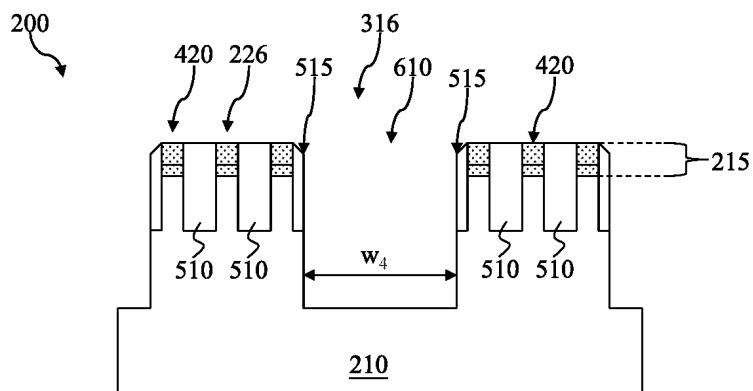

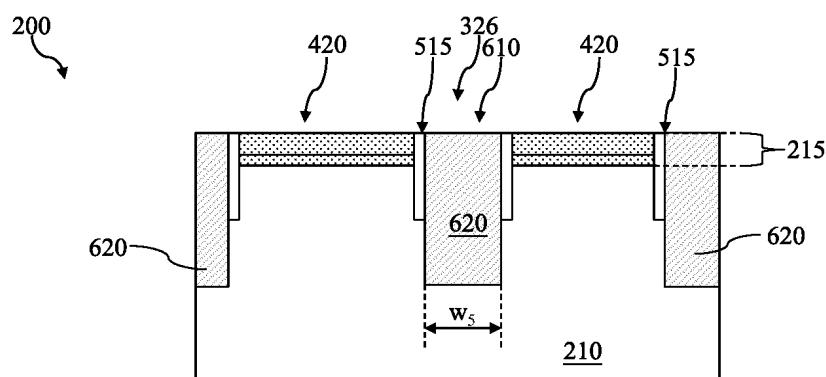

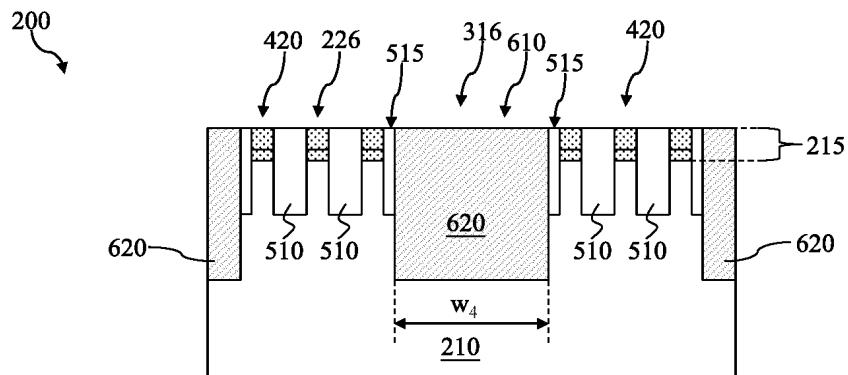

도 5a, 6a, 7a, 8a, 9a 및 10a는 도 1의 방법에 따라 구성되는 제조 스테이지들에서의 도 4a에서 라인 X-X를 따르는 예시적인 FinFET 소자의 단면도들이다.

도 5b, 6b, 7b, 8b, 9b 및 10b는 도 1의 방법에 따라 구성되는 제조 스테이지들에서의 도 4a에서 라인 Y-Y를 따르는 예시적인 FinFET 소자의 단면도들이다.

### 발명을 실시하기 위한 구체적인 내용

[0008] 다음의 개시내용은 발명의 상이한 피쳐들을 구현하기 위한 다수의 상이한 실시예들 또는 예시들을 제공한다. 여기에서 본 개시내용을 간략화하기 위하여 컴포넌트들 및 장치들의 특정 예시들이 설명된다. 물론, 이들은 단지 예시이며, 제한하는 것으로 의도되지 않는다. 예를 들어, 뒤따르는 설명에서 제2 피쳐 위의 또는 제2 피쳐 상의 제1 피쳐는 제1 피쳐 및 제2 피쳐가 직접 접촉하여 형성되는 실시예들을 포함할 수 있으며, 또한 제1 피쳐

및 제2 피쳐가 직접 접촉하지 않을 수 있도록 제1 피쳐와 제2 피쳐 사이에 부가적인 피쳐들이 형성될 수 있는 실시예들도 또한 포함할 수 있다.

[0009] 본 개시물은 별도의 제한이 없으면 FinFET 소자에 관한 것이다. FinFET 소자는 예를 들어, P-타입 금속-산화물-반도체(PMOS, P-type metal-oxide-semiconductor) FinFET 소자 및 N-타입 금속-산화물-반도체(NMOS, N-type metal-oxide-semiconductor) FinFET 소자를 포함하는 상보성 금속-산화물-반도체(CMOS, complementary metal-oxide-semiconductor) 소자일 수 있다. 다음의 개시내용은 본 발명의 다양한 실시예들을 예시하기 위하여 FinFET 예시로 계속될 것이다. 그러나 애플리케이션은 명확히 청구되는 것을 제외하고, 특정 타입의 소자로 제한되어서는 안된다는 것이 이해된다.

[0010] 도 1은 본 개시물의 양상들에 따른 FinFET 소자를 제조하기 위한 방법(100)의 흐름도이다. 상기 방법 이전에, 그 동안에, 또는 그 이후에 부가적인 단계들이 제공될 수 있으며, 설명된 단계들 중 일부는 방법의 다른 실시예들을 위해 교체되거나 제거될 수 있는 것이 이해된다. 방법(100)은 예시를 위하여 도 2a 내지 10b에 보여지는 FinFET 소자(200)를 참고로 하여 하기에서 상세히 논의된다. 본 개시물은 다양한 실시예들에서 참조 번호들 및 /또는 문자들을 반복한다. 이러한 반복은 간략성 및 명료성을 목적으로 하며, 그 자체로 논의된 다양한 실시예들 및/또는 구성들 간의 관계를 구술하지 않는다.

[0011] 도 1 및 2a-2b를 참고하여, 방법(100)은 단계(102)에서 기판(210) 상에 복수의 맨드릴 피쳐들(220)을 형성함으로써 시작된다. 맨드릴 피쳐들(220)은 직사각형 형상의 라인들로서 예시되나, 그러한 것은 몇몇 실시예들에 대해서는 요구되지 않는다. 각각의 맨드릴 피쳐(220)는 더미 피쳐이며, 추후의 제작 스텝에서 제거될 것이다.

[0012] 기판(210)은 실리콘 웨이퍼와 같은 반도체 기판을 포함한다. 대안적으로, 기판(210)은 게르마늄, 실리콘 게르마늄 또는 다른 적절한 반도체 재료들을 포함한다. 일 실시예에서, 기판(210)은 에피택시(또는 에피) 반도체 층을 포함한다. 다른 실시예에서, 기판(210)은 주입 산소에 의한 분리(SIMOX, separation by implanted oxygen)로 지칭되는 기술과 같은 적절한 기술에 의해 형성된 절연을 위한 매립 유전체 재료 층을 포함한다. 몇몇 실시예들에서, 기판(210)은 절연체 상 실리콘(SOI, silicon on insulator)과 같은 절연체 상의 반도체일 수 있다.

[0013] 기판(210)은 본 기술분야에 알려진 바와 같은 설계 요건들에 따라 다양한 도핑된 영역들을 포함할 수 있다. 도핑된 영역들은 p-타입 도편트들, 예컨대 붕소 또는 BF<sub>2</sub>; n-타입 도편트들, 예컨대 인 또는 비소; 또는 이들의 조합들로 도핑될 수 있다. 도핑된 영역들은 P-우물(well) 구조로, N-우물 구조로, 이중-우물 구조로, 또는 융기된(raised) 구조를 사용하여, 기판(210) 상에 직접 형성될 수 있다. 기판(210)은 N-타입 금속-산화물-반도체 트랜지스터 소자에 대하여 구성된 영역들 및 P-타입 금속-산화물-반도체 트랜지스터 소자에 대하여 구성된 영역들과 같은 다양한 활성 영역들을 더 포함할 수 있다.

[0014] 일 실시예에서, 맨드릴 피쳐들(220)을 형성하기 이전에, 하드 마스크(215)가 기판(210) 위에 형성되어, 후속 프로세스들에서 핀 구조에 대한 보호를 제공한다. 하드 마스크(215)는 프로세스 플렉서빌리티를 얻기 위해 다중 층들을 포함할 수 있다. 본 예에서, 하드 마스크(215)는 기판(210) 위에 성막된 제1 산화물 층(211), 제1 산화물 층(211) 위에 성막된 실리콘 질화물 층(212), 및 실리콘 질화물 층(212) 위에 성막된 제2 실리콘 산화물 층(213)을 포함한다. 층들(211, 212 및 213) 중 하나 이상이 열적 산화, 화학 기상 증착(CVD) 프로세스, 플라즈마 강화 CVD(PECVD), 원자 층 증착(ALD), 및/또는 본 기술분야에 알려진 다른 방법들을 포함하는 다양한 방법들에 의해 형성될 수 있다.

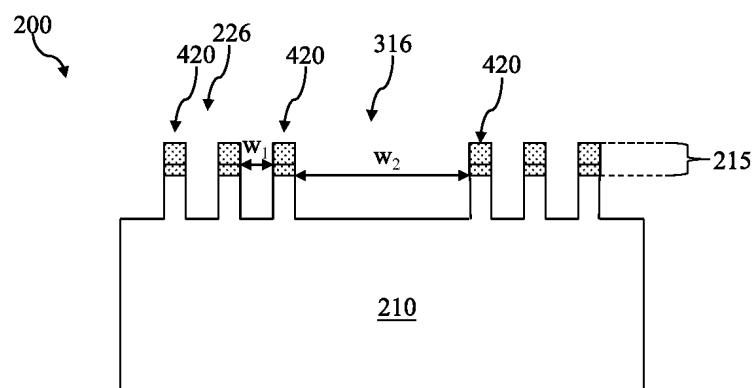

[0015] 맨드릴 피쳐들(220)은 그 후 하드 마스크(215) 위에 형성된다. 일 실시예에서, 맨드릴 피쳐들(220)은 유전체 재료(예를 들어, 실리콘 산화물, 실리콘 질화물)와 같은 맨드릴 재료 층을 성막하는 것; 맨드릴 재료 층 위에 패터닝된 포토레지스트 층을 형성하는 것, 및 예칭 마스크로서 패터닝된 레지스트 층을 사용하여 맨드릴 재료 층을 예칭하여, 맨드릴 피쳐들(220)을 형성하는 것에 의해 형성된다. 다른 실시예에서, 맨드릴 피쳐들(220)은 레지스트 패턴들이다. 일 실시예에서, 인접한 맨드릴 피쳐들(220) 사이의 제1 공간(226)은 제1 폭(w1)이다.

[0016] 도 1 및 3a-3b를 참고하여, 방법(100)은 제2 폭(w2)을 갖는 제2 공간(316)을 형성하기 위하여 그룹(220A)과 같은 맨드릴 피쳐들(220)의 서브세트를 제거하기 위해 X-X 방향을 따라서 제1 영역(310) 내에서 제1 컷을 수행함으로써 단계(104)로 진행된다. 몇몇 경우들에 있어서, 제1 컷은 X-컷으로서 지칭된다. 일 실시예에서, 제1 컷은 220A로 라벨붙여진 맨드릴 피쳐들(220)의 서브세트가 커버되지 않도록, 제1 개구들을 갖는 패턴에 제1 컷을 수행함으로써 형성된다. 그 후, 맨드릴 피쳐들(220A)을 제거하기 위하여 후속 예칭 프로세스 동안 제1 컷 패턴

이 에칭 마스크로서 사용된다.

[0017] 도 1 및 4a-4b를 참고하여, 방법(100)은 라인-엔드(325) and 엔드-투-엔드 공간(326)을 형성하기 위하여, 제2 컷으로서 지칭되는, 제2 영역(320) 내의 그룹(220B)의 각각의 맨드릴 피쳐의 일부를 제거함으로써 단계(106)로 진행된다. 몇몇 경우들에 있어서, 제2 컷은 Y-컷으로서 지칭된다. 본 실시예에서, 라인-엔드(325)는 제1 방향 X-X에 직각인 제2 방향 Y-Y으로 정렬된다. 엔드-투-엔드 공간(326)은 제1 폭(w1)보다 실질적으로 더 큰 제3 폭(w3)을 갖는다. 일 실시예에서, 제2 컷은 제2 개구들 내의 그룹(220B)의 각각의 맨드릴 피쳐의 일부가 커버되지 않도록, 제2 영역(320) 내의 제2 개구를 갖는 패턴의 제2 컷을 수행함으로써 수행된다. 그 후 제2 컷 패턴은 제2 개구들 내의 그룹(220B)의 각각의 맨드릴 피쳐의 일부를 제거하기 위하여 후속 에칭 프로세스 동안 에칭 마스크로서 사용된다. 에칭 프로세스는 습식 에칭, 건식 에칭, 또는 이들의 조합과 같은 임의의 적절한 기법들에 의해 구현될 수 있다. 컷 기법을 사용함으로써, 라인-엔드(325)는 실질적으로 수직 프로파일을 가지고 형성될 수 있으며, 이것은 라인-엔드 단축 및 코너 라운딩의 문제들을 드라마틱하게 감소시킬 수 있다.

[0018] 도 1 및 5a-5b를 참고하여, 방법(100)은 에칭 마스크로서 맨드릴 피쳐들(220)을 사용함으로써 복수의 핀들(420)을 형성하기 위해 기판(210)을 리세스함으로써 단계(108)로 진행된다. 핀들(420)은 제1 공간(226), 엔드-투-엔드 공간(326) 및 제1 공간들(316)을 수반한다(carry). 일 실시예에서, 기판(210)은 선택적 에칭에 의해 에칭된다. 에칭 프로세스는 하드 마스크(215)뿐 아니라 기판(210)을 선택적으로 제거하나, 실질적으로 맨드릴 피쳐들(220)은 에칭하지 않는다. 에칭 프로세스는 건식 에칭, 습식 에칭 및/또는 이들의 조합을 포함할 수 있다. 습식 에칭 프로세스는 테트라메틸암모늄 수산화물(TMAH, tetramethylammonium hydroxide), HF/HNO<sub>3</sub>/CH<sub>3</sub>COOH 용액, NH<sub>4</sub>OH, KOH(포타슘 수산화물), HF(불화수소산), 또는 다른 적절한 용액과 같은 용액들을 사용할 수 있다. 건식 에칭 프로세스는 염소-기반 화학물질을 사용하는 플라즈마 에칭 프로세스를 포함할 수 있다. 다른 건식 에칭 제 가스들은 CF<sub>4</sub>, NF<sub>3</sub>, SF<sub>6</sub>, 및 He를 포함한다. 건식 에칭은 트랜스포머 결합 플라즈마(TCP, transformer coupled plasma) 에칭, 전자 사이클로트론 궁명(ECR, electron cyclotron resonance) 에칭 및 반응성 이온 에칭(RIE, reactive ion etch)을 포함할 수 있다.

[0019] 본 실시예에서, 핀들(420)은 (제1 폭(w1)을 갖는)제1 공간(226), (제2 폭(w2)을 갖는)제2 공간(316), (제3 폭(w3)을 갖는)엔드-투-엔드 공간(326)을 수반하도록 형성되며, 그것의 상부 층으로서 하드 마스크(215)를 갖는다.

[0020] 그 후에, 맨드릴 피쳐들(220)은 적절한 프로세스에 의해 제거된다. 맨드릴 피쳐들(220)이 레지스트 패턴들인 일 예에서, 그들은 습식 스트립핑 또는 플라즈마 애싱에 의해 제거된다. 다른 예에서, 맨드릴 피쳐들(220)은 유전체 재료에 의해 만들어지고, 이것은 맨드릴 재료를 선택적으로 제거하기 위하여 습식 에칭 프로세스에 의해 제거될 수 있다. 일 실시예에서, 제2 산화물 층(213)과 같은 하드 마스크(215)의 하나 이상의 층들이 또한 제거된다.

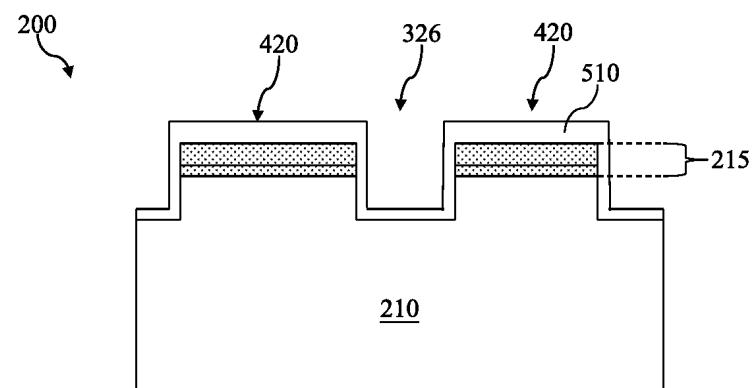

[0021] 도 1 및 6a-6b를 참고하여, 방법(100)은 기판(210) 위에 스페이서 층(510)을 성막함으로써 단계(110)로 진행된다. 본 실시예에서, 스페이서 층(510)은 이것이 제1 공간(226) 내를 완전히 충진하고, 제2 공간(316) 및 엔드-투-엔드 공간(326) 내의 측벽들을 커버하고, 제2 공간(316) 및 엔드-투-엔드 공간(326)을 부분적으로 충진하도록 구성된다. 스페이서 층(510)은 실리콘 산화물, 실리콘 질화물, 실리콘 산질화물, 또는 다른 적절한 재료들, 또는 이들의 조합물들을 포함한다. 스페이서 층(510)은 CVD, ALD 또는 임의의 다른 적절한 기법들에 의해 성막될 수 있다.

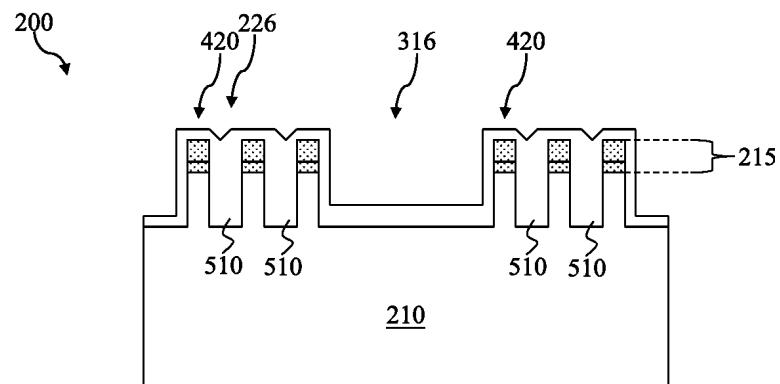

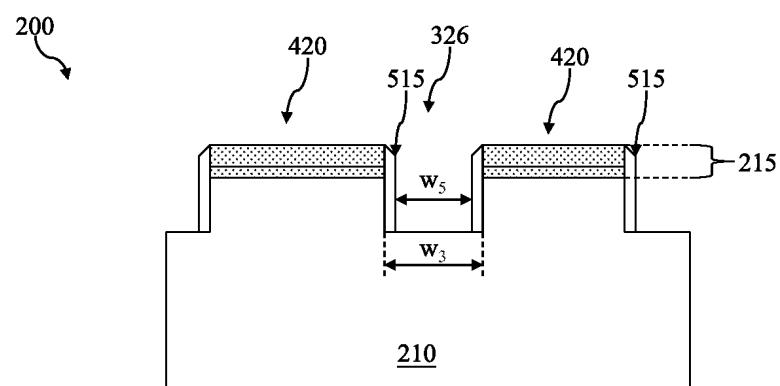

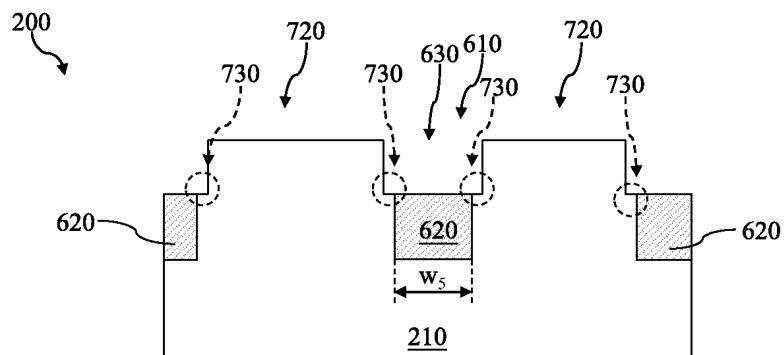

[0022] 도 1 및 7a-7b를 참고하여, 방법(100)은 제2 공간(316) and 엔드-투-엔드 공간(326) 내의 핀들(420)의 측벽들 상에 스페이서들(515)을 형성하기 위해 스페이서 층(510)을 에칭함으로써 단계(112)로 진행된다. 본 실시예에서, 스페이서에 에칭 프로세스는 이것이 핀들(420) 내에서 하드 마스크(215) 상의 스페이서 층(510)을 제거하고; 기판(210)을 노출시키기 위해 엔드-투-엔드 공간(326) 및 제2 공간(316)의 바닥부에서 스페이서 층(510)을 제거하고, 스페이서 층(510)으로 충진되는 제1 공간(226) 내에 유지되도록, 제어된다. 에칭 프로세스는 이방성 플라즈마 에칭과 같은 임의의 적절한 프로세스들을 포함할 수 있다. 스페이서(515)로, 제2 공간(316)의 제2 폭(w2) 및 엔드-투-엔드 공간(326)의 제3 폭(w3)은 더 작아지게 되며, 이는 각각 제4 폭(w4) 및 제5 폭(w5)으로 불린다.

[0023] 도 1 및 8a-8b를 지칭하여, 방법(100)은 절연 트렌치들(610)을 형성하기 위하여 제2 공간(316) 및 엔드-투-엔드 공간(326) 내에 기판(210)의 노출된 부분을 에칭하기 위해 트렌치 에칭을 수행함으로써 단계(114)로 진행된다. 에칭 프로세스는 선택적 습식 에칭 또는 선택적 건식 에칭을 포함할 수 있다. 습식 에칭 용액은 테트라메틸암

모늄 수산화물(TMAH), HF/HNO<sub>3</sub>/CH<sub>3</sub>COOH 용액 또는 다른 적절한 용액을 포함한다. 건식 에칭 프로세스들은 염소-기반 화학물질을 사용하는 바이어성된 플라즈마 에칭 프로세스를 포함한다. 다른 건식 에칭제 가스들은 CF<sub>4</sub>, NF<sub>3</sub>, SF<sub>6</sub> 및 He를 포함한다. 에칭 프로세스는 에칭 효과를 최적화시키기 위해 다수의 에칭 단계들을 포함할 수 있다.

[0024] 하드 마스크(215), 제1 공간(226) 내에 충진된 스페이서 층(510) 및 스페이서(515)의 조합에 의하여 보호되어, 핀들(420)은 트렌치 에칭 동안 온전히 남아있다. 이것은 특히 제2 공간(316) 및 엔드-투-엔드 공간(326)에 가까운 것들에 대해, 제1 공간(226) 및 핀(420)의 사이즈들의 균일성에 대한 트렌치 에칭 영향들을 최소화시킬 뿐 아니라, 트렌치 에칭 프로세스의 제약들을 완화시킬 수 있다. 트렌치 에칭은 스페이서(515)와 정렬될 수 있고, 따라서 절연 트렌치(610)는 에칭 프로세스 원도우 향상에 유익할 수 있는 자가-정렬 성질을 가지고 형성될 수 있다. 절연 트렌치(610)는 절연 트렌치(610)는 각각 제2 공간(316)에서 그리고 엔드-투-엔드 공간(326)에서 제4 폭(w4) 및 제5 폭(w5)과 동일한 폭을 가지고 형성된다.

[0025] 도 1 및 9a-9b를 참고하여, 방법(100)은 절연 유전체 층(620)으로 절연 트렌치(610) 내를 충진함으로써 단계(116)로 진행된다. 절연 유전체 층(620)은 실리콘 산화물, 실리콘 질화물, 실리콘 산질화물, 또는 다른 적절한 재료들, 또는 이들의 조합물들을 포함한다. 몇몇 예들에서, 절연 유전체 층(620)은 다중-층 구조를 갖는다. 절연 유전체 층(620)은 CVD, ALD 또는 임의의 다른 적절한 기법들에 의해 성막될 수 있다. 핀들(420) 내의 하드 마스크(215)를 노출시키고 또한 실질적으로 평탄한 표면을 제공하기 위해 초과 절연 유전체 층(620)을 제거하도록 화학 기계적 연마(CMP) 프로세스가 후속하여 수행될 수 있다.

[0026] 도 1 및 10a-10b를 참고하여, 방법(100)은 이제 참조 번호(720)로 라벨붙여진 핀들을 드러내기 위해 제1 공간(226) 내의 스페이서 층(510) 및 하드 마스크(215)를 제거하는 것, 및 절연 트렌치(610) 내에 절연 피쳐(630)를 형성하기 위해 절연 유전체 층(620)을 리세스하는 것에 의하여, 단계(118)로 진행된다. 절연 피쳐(630)는 활성 영역들 사이에 전기적 절연을 제공한다. 에칭 프로세스들은 선택적 습식 에칭 또는 선택적 건식 에칭, 또는 이들의 조합을 포함한다. 일 실시예에서, t 하드 마스크(215) 및 스페이서 층(510)은 제거되고, 그 후 절연 유전체 층(620)이 리세스된다. 다른 실시예에서, t 하드 마스크(215), 스페이서 층(510) 및 절연 유전체 층(620)은 동시에 에칭된다. 스페이서들(515)이 제거된 이후, 이전에 스페이서들(515)을 가진 핀들(720) 중 일부의 발치에 기판(210) 내에 쇼울더-형 구조물(730)이 남겨진다. 쇼울더-형 구조물(730) 각각은 실질적으로 동일한 폭을 갖는다.

[0027] 부가적인 단계들은 방법(100) 이전에, 그 동안에, 그리고 그 이후에 제공될 수 있으며, 설명된 단계들 중 일부는 방법의 다른 실시예들에 대해 대체되거나 삭제될 수 있다.

[0028] FinFET 소자(200)는 다양한 피쳐들 및 영역들을 형성하기 위하여 추가적 CMOS 또는 MOS 기술 프로세싱을 겪는다. FinFET 소자(200)는 게이트 영역 내에 핀들(720)의 일부 위를 래핑하는 것을 포함하는, 기판(210) 위의 하이-k(HK)/금속 게이트(MG)를 포함할 수 있으며, 핀들(720)은 게이트 채널 영역의 역할을 할 수 있다. 게이트 제1 프로세스 방식에서, HK/MG는 기능적 게이트의 전부 또는 일부이다. 반대로, 게이트 최종 프로세스 방식에서, 더미 게이트가 먼저 형성되고, 소스/드레인 형성 동안 열적 프로세스들과 같은 높은 열적 온도 프로세스들이 수행된 이후에 HK/MG에 의하여 추후에 교체된다.

[0029] FinFET 소자(200)는 기판(210) 위에 HK/MG 사이에 형성된 층간 유전체(ILD) 층을 또한 포함할 수 있다. ILD 층은 실리콘 산화물, 산질화물, 또는 다른 적절한 재료들을 포함한다. ILD 층은 단일층 또는 다수의 층들을 포함한다.

[0030] FinFET 소자(200)는 핀들(720)의 다른 부분에서 포함하는, 기판(210) 내의 소스/드레인 영역들 내의 소스/드레인 피쳐를 또한 포함할 수 있다. 예로서, 소스/드레인 영역들 내의 핀들(720)의 일부가 먼저 리세스된다. 그 후, 반도체 재료는 소스/드레인 피쳐를 형성하기 위하여 핀들(720)의 리세스된 부분 내에서 에피택셜하게 성장한다. 반도체 재료는 Ge, Si, GaAs, AlGaAs, SiGe, GaAsP 또는 다른 적절한 재료를 포함한다.

[0031] FinFET 소자(200)는 기판(210) 위에 다양한 콘택들/비아들/라인들 및 다층 상호접속 피쳐들(예를 들어, 금속 층들 및 층간 유전체들)을 또한 포함할 수 있다. 예를 들어, 다층 상호접속은 수직 상호접속들, 예컨대 종래의 비아들 또는 콘택들, 및 수평 상호접속들, 예컨대 금속 라인들을 포함한다. 다양한 상호접속 피쳐들은 구리, 텅스텐 및/또는 실리사이드를 포함하는 다양한 도전성 재료들을 구현할 수 있다. 일예에서, 다마신 및/또는 듀얼 다마신 프로세스가 구리 관련 다층 상호접속 구조물을 형성하는데 사용된다.

[0032] 상기 내용에 기반하여, 본 개시물은 FinFET 소자를 제작하기 위한 방법을 제공한다. 방법은 먼저 핀을, 그리고 X-컷 및 Y-컷 그리고 마지막에 절연 트렌치를 형성하는 방식을 채용한다. 방법은 절연 트렌치의 형성 동안 핀을 보호하는 것을 채용한다. 방법은 절연 트렌치 형성에 자가-정렬 성질 및 감소된 폭을 제공한다. 방법은 핀들 사이의 공간 및 핀의 사이즈의 균일성 및 프로세스 원도우의 향상들을 증명한다.

[0033] 전술한 내용은 본 기술분야의 당업자들이 본 개시물의 양상을 더 잘 이해할 수 있도록, 수 개의 실시예들의 피쳐들을 개략한다. 본 기술분야의 당업자들은 그들이 본 명세서에 도입된 실시예들의 동일한 장점들을 달성하고 및/또는 동일한 목적들을 실행하기 위한 다른 프로세스들 및 구조들을 설계 또는 변형하기 위한 기반으로서 본 개시물을 쉽게 사용할 수 있다는 것을 인식해야 한다. 본 기술분야의 당업자들은 또한 그러한 등가적인 구조들이 본 개시물의 진의 및 범위를 벗어나지 않으며, 그들이 본 개시물의 진의 및 범위를 벗어나지 않고서 본 명세서 내의 다양한 변화들, 대체들 및 변경들을 할 수 있다는 것을 또한 인식해야 한다.

## 도면

### 도면1

## 도면2a

## 도면2b

## 도면3a

도면3b

도면4a

도면4b

도면5a

도면5b

도면6a

도면6b

도면7a

도면7b

도면8a

도면8b

도면9a

도면9b

도면10a

도면10b