CA

N

C

S

O

H

**SCHWEIZERISCHE EIDGENOSSENSCHAFT**

**BUNDESAMT FÜR GEISTIGES EIGENTUM**

⑤ Int. Cl. 3: G 01 S

G 09 G

7/06

1/06

**Erfindungspatent für die Schweiz und Liechtenstein**

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

**⑫ PATENTSCHRIFT A5**

⑪

**618 520**

⑯ Gesuchsnummer: 3124/77

⑬ Inhaber:

Hollandse Signaalapparaten B.V., Hengelo/O

(NL)

⑭ Anmeldungsdatum: 11.03.1977

⑯ Priorität(en): 26.03.1976 NL 7603159

⑭ Erfinder:

Antoon Hendrikus Brands, Borne (NL)

Jouke Gietema, Hengelo (NL)

Hendrik Cornelis Bleijerveld, Borne (NL)

⑯ Patent erteilt: 31.07.1980

⑯ Patentschrift

veröffentlicht: 31.07.1980

⑭ Vertreter:

Fritz Isler, Patentanwaltsbureau, Zürich

**⑮ Einrichtung zum Auslesen der in einem Speicher mit wahlfreiem Zugriff eingeschriebenen und auf einem zeilenweise arbeitenden Monitorschirm anzuseigenden Informationen.**

⑯ Die Einrichtung dient zum Auslesen von in einem RAM-Speicher (1) eingeschriebenen Informationen eines Radarbildes und deren Anzeige auf einem zeilenweise arbeitenden Monitorschirm. Der RAM-Speicher ist aus  $N \times N$  gleichzeitig zugänglichen Teilspeichern aufgebaut. Für jede Bildzeile werden die Informationen gleichzeitig aus  $N$  Teilspeichern ausgelesen. Die Einrichtung besitzt einen Bildzeilenspeicher (11) zum Einspeichern der zu einer Bildzeile gehörenden Informationen, zwecks Auslesen in der für die Abbildung erforderlichen Reihenfolge. Der Vorteil der Einrichtung besteht in einer einfachen Darstellungsmöglichkeit eines Teils der im RAM-Speicher vorhandenen Informationen auf dem gesamten Monitorschirm, also einer Ausschnittsvergrößerung. Die Einrichtung besitzt dazu einen Bildpunktadressierkreis (12), um nur einen Teil der Gesamtanzahl Bildzeilen und nur einen Teil der Gesamtanzahl Bildpunkte einer Bildzeile im Bildzeilenspeicher (11) zum Auslesen zu adressieren. Mit einer Bildpunktumsetzungsschaltung (16) werden die aufeinanderfolgenden Gruppen Bits aus dem Bildzeilenspeicher (11) umgruppiert und einer Bildpunktvervielfacherschaltung (26) zugeführt, um die Anzahl der Bildpunkte auf die Anzahl Bildpunkte zu erweitern, die eine Bildzeile insgesamt für die Wiedergabe benötigt. Mittels eines Speicheradressierkreises (4) wird die Anzahl Bildlinien durch mehrmaliges Auslesen derselben Bildlinien auf die für die Wiedergabe auf dem Monitorschirm benötigte Anzahl erweitert.

## PATENTANSPRUCH

Einrichtung zum Auslesen der in einem Speicher mit wahlfreiem Zugriff, im folgenden RAM-Speicher genannt, eingeschriebenen und auf einem zeilenweise arbeitenden Monitorschirm anzuseigenden Informationen, wobei der RAM-Speicher (1) aus  $N \times N$  gleichzeitig zugänglichen Teilspeichern mit jeweils  $a \times a$  Speicherzellen aufgebaut ist, wobei weiter für jede Bildzeile die betreffende Informationen, pro Zyklus des RAM-Speichers in  $q$  Speicherzellen pro Teilspeicher gleichzeitig aus den betreffenden  $N$  Teilspeichern ausgelesen werden und die Einrichtung zumindest einen Bildzeilenspeicher (11) besitzt, worin die vorgenannten, zu einer Bildzeile gehörenden Informationen eingeschrieben werden, damit diese in der für die Abbildung auf dem Monitorschirm erforderlichen Reihenfolge ausgelesen werden können, dadurch gekennzeichnet, dass, um von einem durch die Bildpunktkoordinaten  $x_0, y_0$  bestimmten Startpunkt aus einem Teil  $\beta^2$ , wobei  $\beta = 1, \frac{1}{2}, \frac{1}{3}$  der im RAM-Speicher vorhandenen Informationen auf dem gesamten Raster des Monitorschirms abbilden zu können, die Einrichtung einen Bildpunktadressiererkreis (12) besitzt, um in einer  $\frac{1}{\beta}$  mal so langen Zeit wie sie für die Abbildung der gesamten Speicherinformationen auf dem Monitorschirm erforderlich ist, beginnend bei dem durch die Bildpunktkoordinaten  $q \cdot [\frac{x_0}{q}], y_0$  bestimmten Punkt, wobei der eckige Klammerausdruck die grösste ganze Zahl bedeutet, die nicht grösser als der Quotient  $\frac{x_0}{q}$  ist für einen Teil  $\beta$  der gesamten Anzahl Bildzeilen einen Teil  $\beta$  der Anzahl Bildpunkte einer Bildzeile im Bildzeilenspeicher (11) so zu adressieren, dass die im Bildzeilenspeicher vorhandenen Informationen in den gleichen Gruppen von  $q$  ausgelesenen Speicherzellen, wie diese Informationen auch im Bildzeilenspeicher (11) eingeschrieben sind, in der für die Bildzeilenwiedergabe erforderlichen Reihenfolge ausgelesen werden, dass weiter eine Bildpunktumsetzung (16) vorhanden ist, um nach Zufuhr der letztgenannten aufeinanderfolgenden Gruppen von  $q$  ausgelesenen Speicherzellen neue aufeinanderfolgende Gruppen von  $q$  ausgelesenen Speicherzellen abgeben zu können, welche pro Bildzeilelenteil die abzubildenden Speicherinformationen ab der Bildpunktkoordinate  $x_0$  repräsentiert, sowie eine an die Bildpunktumsetzung (16) angeschlossene Bildpunktvervielfacherschaltung (26), um die Anzahl der darzustellenden Informationen repräsentierenden Bildpunkte auf die Anzahl Bildpunkte zu erweitern, die eine Bildzeile insgesamt für die Wiedergabe benötigt, und einen Speicheradressiererkreis (4), womit, ab der Bildpunktkoordinate  $y_0$  ein Teil  $\beta$  der Anzahl Bildlinien  $\frac{1}{\beta}$  mal aus dem RAM-Speicher ausgelesen und in den Bildzeilenspeicher (11) gesetzt wird.

---

Die Erfindung bezieht sich auf eine Einrichtung zum Auslesen der in einem Speicher mit wahlreiem Zugriff, im folgenden RAM-Speicher genannt, eingeschriebenen und auf einem zeilenweise arbeitenden Monitorschirm anzuseigenden Informationen, wobei der RAM-Speicher aus  $N \times N$  gleichzeitig zugänglichen Teilspeichern mit jeweils  $a \times a$  Speicherzellen aufgebaut ist, wobei weiter für jede Bildzeile die betreffenden Informationen pro Zyklus des RAM-Speichers in  $q$  Speicherzellen pro Teilspeicher gleichzeitig aus den betreffenden  $N$  Teilspeichern ausgelesen werden und die Einrichtung zumindest einen Bildzeilenspeicher besitzt, worin die vorgenannten, zu einer Bildzeile gehörende Informationen eingeschrieben werden, damit diese in der für die Abbildung auf dem Monitorschirm erforderlichen Reihenfolge ausgelesen werden können.

Eine solche Einrichtung ist aus der U.S. Patentschrift 4 128 838 bekannt und kommt dort zur Anwendung in einem Radarabtaster zum Umwandeln von Daten in Polarkoordinatendarstellung in eine Darstellung mit kartesischen Koordinaten für die Anzeige von aus Videosignalen einer Radaranlage erhaltenen Radarinformationen auf einem zeilenweise arbeitenden Monitorschirm, bei dem die ankommenden Radarinformationen quantisiert und in einem Radareingangsspeicher eingeschrieben werden, wobei das Einschreiben der Radarinformationen aus dem Sichtfeld der Radaranlage mit einer ersten Geschwindigkeit erfolgt und der Radarabtaster einen Speicher mit wahlfreiem Zugriff (RAM) zur Aufnahme von Radarinformationen aus dem Radareingangsspeicher besitzt, sowie einen Adressierkreis, der für die Radarinformationen mit der ersten Geschwindigkeit Adressen zum Einschreiben der Radarinformationen aus dem Radareingangsspeicher in dem RAM-Speicher erzeugt, derart dass die natürliche Adressenfolge im RAM-Speicher der Reihenfolge der Bildpunkte auf dem Monitorschirm entspricht. Die eingangs beschriebene Einrichtung sorgt für das Auslesen der in dem RAM-Speicher eingeschriebenen und mit einer zweiten Geschwindigkeit auf dem Monitorschirm darzustellenden Radarinformationen.

In der vorgenannten U.S. Patentschrift wird erklärt, wie, im Zusammenhang mit einer genauen Bildwiedergabe, die maximale Anzahl Bildzeilen realisiert und die Aufteilung des RAM-Speichers in Teilspeicher bestimmt werden kann. Zur Verdeutlichung des Zweckes der Erfindung wird angegeben, dass auf dem Monitorschirm  $b$  Bildzeilen mit jeweils  $b$  Bildpunkten dargestellt werden können, jeder Bildpunkt mit einer Speicherzelle des RAM-Speichers korrespondiert, und dieser RAM-Speicher aus  $N \times N$  Teilspeichern mit jeweils  $a \times a$  Speicherzellen, wobei daher,  $a = \frac{b}{N}$ , aufgebaut ist; weiter ist jeder Teilspeicher aus 1024 Speicherzellenzählenden Speichereinheiten aufgebaut und es wird pro Teilspeicher in  $q = \frac{a_2}{1024}$  Speicherzellen parallel ausgelesen. Das Auslesen der eine Bildzeile repräsentierenden Informationen geschieht aus  $N$  Teilspeichern gleichzeitig, und zwar in  $q$  Speicherzellen parallel pro Teilspeicher und pro Speicherzyklus. In einem Speicherzyklus werden  $qN$  Speicherzellen ausgelesen; die eine Bildzeile repräsentierenden Informationen werden dann in  $\frac{b}{qN}$  Speicherzyklen ausgelesen. Wenn  $b = 896$ ,  $N = 7$  und  $q = 16$ , wird eine Bildzeile in acht Speicherzyklen ausgelesen: und zwar werden während eines ersten Speicherzyklus die Speicherzellen:

0–15, 124–143, 256–271, 384–399, 512–527, 640–655,

768–783 ; während eines zweiten Speicherzyklus die Speicherzellen

16–31, 144–159, 272–287, 400–415, 528–543, 656–671,

784–799 und während eines achten und letzten Speicherzyklus die Speicherzellen

112–127, 240–255, 368–383, 496–511, 624–639, 752–767,

880–895.

In dieser Reihenfolge werden die eine Bildzeile repräsentierende Informationen in den Bildzeilenspeicher gesetzt, wonach diese Informationen in der Reihenfolge

0–15, 16–31, 32–47, 48–63, . . . , 864–879, 880–895 aus dem Bildzeilenspeicher ausgelesen werden. Dieses Verfahren wiederholt sich für jede Bildzeile und ergibt eine Abbildung des gesamten Speicherinhaltes auf dem Monitorschirm.

Wird beabsichtigt, einen bestimmten Teil der in dem RAM-Speicher vorhandenen Informationen auf dem gesamten Monitorschirm abzubilden, dann muss den mit den ausgelesenen Informationen korrespondierenden Bildpunkten eine derartige Anzahl Bildzeilen und Bildpunkte zugeführt werden, dass der gesamte Monitorschirm bestrichen wird, ohne dass dies Anlass

zu einer Verformung auf Kosten der Genauigkeit des Bildes gibt.

Soll z.B. ein Viertel des Speicherinhaltes abgebildet werden, also die die zu 448 Bildzeilen gehörigen Informationen, und von diesen Bildzeilen nur 448 Bildpunkte, zu beginnen bei z.B. der 140. Bildzeile und dem 50. Bildpunkt, dann müssen die zu den ersten 139 und den letzten 308 Bildzeilen gehörigen Informationen nicht abgebildet werden, ebenso die Informationen, die zum 140. bis zum 587. Bildpunkt gehören, aber nicht die Informationen der ersten 49 und der letzten 399 Bildpunkte. Die zu den übrigen Bildpunkten gehörenden Informationen müssen dagegen viermal so gross abgebildet werden, d.h. neben den zu jedem dieser Bildpunkte gehörigen Informationen müssen Informationen die zu den drei zugefügten Bildpunkten gehören, erzeugt werden.

Die Erfindung hat den Zweck, eine eingangs beschriebene Einrichtung mit einer Schaltung zu versehen, mit deren Hilfe eine einfache Abbildung eines Teiles der Informationen im RAM-Speicher möglich ist.

Entsprechend der Erfindung ist die Einrichtung dadurch gekennzeichnet, dass, um von einem durch die Bildpunktkoordinaten  $x_o, y_o$  bestimmten Startpunkt aus einen Teil  $\beta^2$ , wobei  $\beta = 1, \frac{1}{2}, \frac{1}{3}, \dots$ , der im RAM-Speicher vorhandenen Informationen auf dem gesamten Raster des Monitorschirms abbilden zu können, die Einrichtung einen Bildpunktadressierkreis (12) besitzt, um in einer  $\frac{1}{\beta}$  mal so langen Zeit wie sie für die Abbildung der gesamten Speicherinformationen auf dem Monitorschirm erforderlich ist, beginnend bei dem durch die Bildpunktkoordinaten  $q \cdot [\frac{x_o}{q}], y_o$  bestimmten Punkt, wobei der eckige Klammerausdruck die grösste ganze Zahl bedeutet, die nicht grösser als der Quotient  $\frac{x_o}{q}$  ist, für einen Teil  $\beta$  der gesamten Anzahl Bildzeilen einen Teil  $\beta$  der Anzahl Bildpunkte einer Bildzeile im Bildzeilenspeicher (11) so zu adressieren, dass die im Bildzeilenspeicher vorhandenen Informationen in den gleichen Gruppen von  $q$  ausgelesenen Speicherzellen, wie diese Informationen auch im Bildzeilenspeicher (11) eingeschrieben sind, in der für die Bildzeilenwiedergabe erforderlichen Reihenfolge ausgelesen werden, dass weiter eine Bildpunktumsetzschatzung (16) vorhanden ist, um nach Zufuhr der letztgenannten aufeinanderfolgenden Gruppen von  $q$  ausgelesenen Speicherzellen neue aufeinanderfolgende Gruppen von  $q$  ausgelesenen Speicherzellen abgeben zu können, welche pro Bildzeileteil die abzubildenden Speicherinformationen ab der Bildpunktkoordinate  $x_o$  repräsentiert, sowie eine an die Bildpunktumsetschaltung (16) angeschlossene Bildpunktvervielfacherschaltung (26), um die Anzahl der darzustellenden Informationen repräsentierenden Bildpunkte auf die Anzahl Bildpunkte zu erweitern, die eine Bildzeile insgesamt für die Wiedergabe benötigt, und einen Speicheradressierkreis (4), womit, ab der Bildpunktkoordinate  $y_o$  ein Teil  $\beta$  der Anzahl Bildlinien  $\frac{1}{\beta}$  mal aus dem RAM-Speicher ausgelesen und in den Bildzeilenspeicher (11) gesetzt wird.

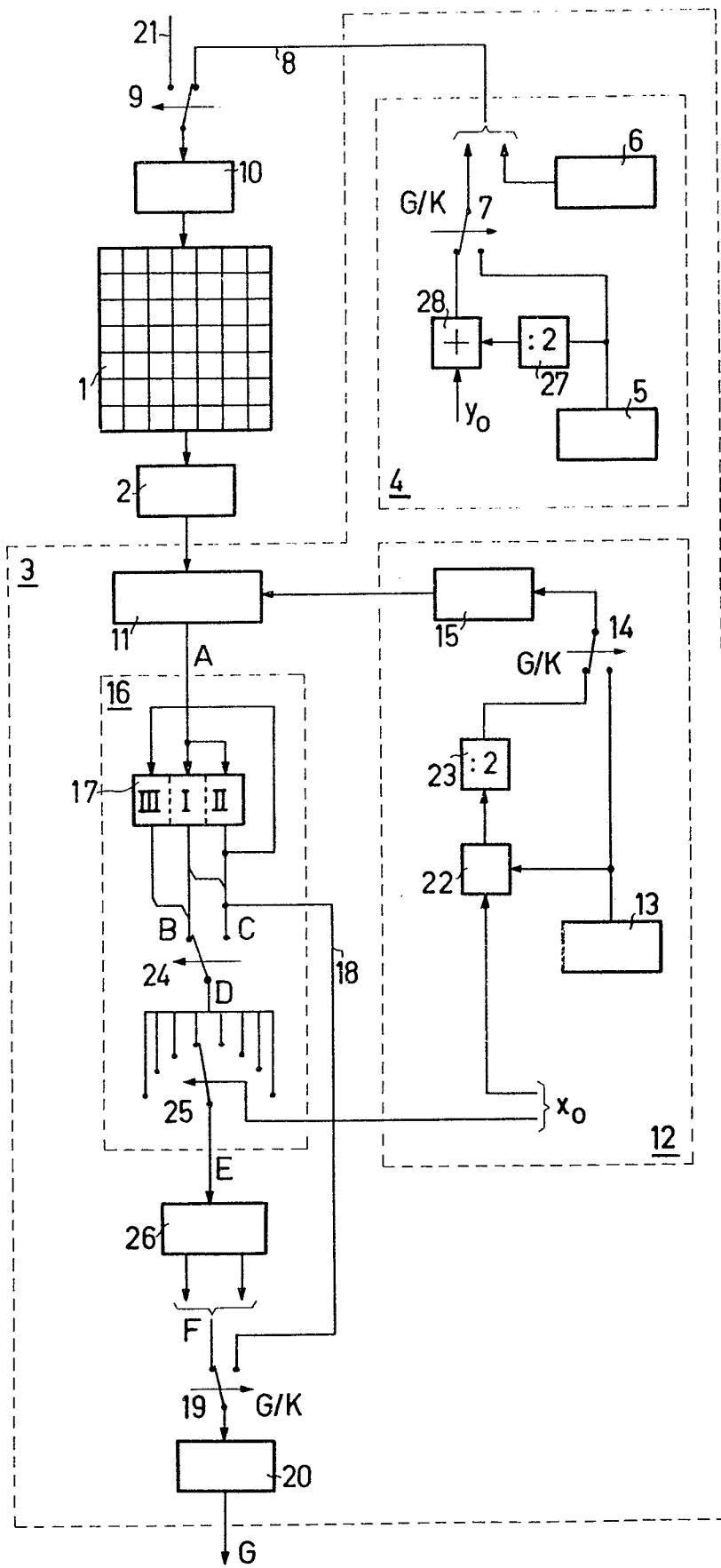

Die Erfindung wird jetzt anhand beiliegender Figur, die die erfundungsgemässen Einrichtung schematisch wiedergibt, beispielweise näher erklärt.

In dieser Figur ist der RAM-Speicher mit 1 bezeichnet. Dieser Speicher ist aufgebaut aus  $N \times N$ , jeweils  $a \times a$  Speicherzellen besitzende und gleichzeitig zugängliche Teilspeicher. Jede Speicherzelle korrespondiert mit einem Punkt des Monitorschirms, auf dem die im Speicher vorhandenen Informationen mit einer bestimmten Frequenz abgebildet werden. Auf diesem nicht in der Figur angegebenen Monitorschirm können  $b$  Bild-

zeilen mit jeweils  $b$  Bildpunkten abgebildet werden, so dass der Speicher  $b^2$  (mit  $b = Na$ ) Speicherzellen umfasst.

In einer Vorzugsausführung ist gewählt:  $b = 896$ ,  $N = 7$  und somit  $a = 128$ . Weiter werden bei dieser Ausführung die mit Speicher 1 vorhandenen Informationen mit einer Frequenz von 55 Hz ausgelesen. Für jede Bildzeile geschieht dieses Auslesen aus sieben auf einer horizontalen Reihe gelegenen Teilspeichern gleichzeitig. In dieser Vorzugsausführung ist jeder der Teilspeicher aus  $1024 \times 1$  statischem RAM aufgebaut und können diese Teilspeicher aus 16 Speicherzellen parallel ausgelesen werden. Für das Auslesen einer Bildzeile werden zunächst die ersten 16 in einer Reihe liegenden Zellen der diesbezüglichen sieben Teilspeicher ausgelesen, danach die folgenden 16 in einer Reihe liegenden Zellen des genannten Teilspeichers, usw. Pro Speicherzyklus werden auf diese Weise  $7 \times 16$  Zellen ausgelesen, so dass eine Bildzeile von 896 Zellen in acht Speicherzyklen ausgelesen wird. Wenn jede Speicherzelle aus einem Bit besteht, werden pro Speicherzyklus sieben Worte von 16 Bits parallel ausgelesen, danach jedoch in Serie zum Pufferregister 2 transportiert. Wenn jede Speicherzelle aus mehreren  $p$  Bits besteht, werden pro Speicherzyklus  $7 \times p$  Worte von 16 Bits parallel ausgelesen und über  $p$  Kanäle in Serie zum Pufferregister 2 transportiert, welches eine  $p$  mal so grosse Kapazität besitzt. Einfachheitshalber wird weiterhin angenommen, dass eine Speicherzelle aus einem Bit besteht, so dass  $p = q$ .

Da nun mehr  $p = q$  gilt, werden die Teilspeicher aus  $q$  Bits parallel ausgelesen. Für das Auslesen einer Bildzeile werden dann zuerst die ersten  $q$  in einer Reihe liegenden Bits der diesbezüglichen  $N$  Teilspeicher ausgelesen, danach die folgenden  $q$  in einer Reihe liegenden Bits des genannten Teilspeichers, usw. Pro Speicherzyklus werden auf diese Weise  $qN$  Bits ausgelesen, so dass eine Bildzeile von  $b$  Bits in  $\frac{b}{qN}$  Speicherzyklen ausgelesen wird. Die pro Speicherzyklus parallel ausgelesenen  $N$  Worte von  $q$  Bits werden in Serie zum Pufferregister 2 transportiert und von dort zu einer Einrichtung 3, die die angebotene Information in eine für die Abbildung auf dem Monitorschirm geeignete Form verarbeitet.

Das Auslesen des Speichers 1 geschieht unter Steuerung des Speicheradressierkreises 4. Dieser Kreis enthält einen Zähler 5, der die  $b$  Bildzeilen, und einen Zähler 6, der die Gruppen von  $q$  Bits in den korrespondierenden Teilspeichern abzählt. In der bereits genannten Vorzugsausführung wird vom Zähler 5 die Bildzeilenadresse in 10 Adressbits angegeben und vom Zähler 6 die Adresse der Gruppen von 16 Bits in 3 Adressbits. Im letzteren Fall werden nämlich für die ersten Teilspeicher die Adressen für die Speicherzellen 0, 16, 32, 48, 64, 80, 96 und 112 abgegeben, welche Adressen gleichzeitig für die entsprechenden Speicherzellen der übrigen Teilspeicher gelten, folglich vom zweiten Teilspeicher die Adressen für die Speicherzellen 128, 144, 160, 176, 192, 208, 224 und 240, und vom dritten Teilspeicher die Adressen für die Speicherzellen 256, 272, 288, 304, 320, 336, 352 und 368, usw. Die vom Zähler 5 abgegebenen Bildzeilenadressen werden über einen Schalter 7, der sich hierbei in der nicht angegebenen Stellung befindet, über Leitung 8, zusammen mit den vorgenannten, vom Zähler 6 abgegebenen Speicherzellengruppenadressen, über einen Schalter 9, der hierbei in der angegebenen Stellung steht, in das Pufferregister 10 eingeschrieben. Von dort werden sie dem Speicher 1 zugeführt.

Die Reihenfolge, mit der die Zellen des Speichers 1 ausgelesen werden unterscheidet sich von der Reihenfolge, die für das Abbilden der korrespondierenden Bildpunkte erforderlich ist. Daher besitzt die Einrichtung 3 einen Bildzeilenspeicher 11, dem bei der genannten Vorzugsausführung nacheinander die Informationen bezüglich der Bildpunkte.

0–15, 128–143, 256–271, 384–399, 512–527, 640–655,

768–783;

16–31, 144–159, 272–287, 400–415, 528–543, 656–671,

784–799;

.....

112–127, 240–255, 368–383, 496–511, 624–639, 752–767,

880–895;

gespeichert werden. Im allgemeinen werden im Bildzeilenspeicher 11 nacheinander die Informationen bezüglich der Bildpunkte

$0 - (n-1), a - (a+q-1), \dots, (N-1) a - ((N-1)a+q-1)$

$q - (2q-1), (a+q) - (a+2q-1), \dots, ((N-1)a+q) - ((N-1)a+2q-1)$

.....

$(a-q) - (a-1), (2a-q) - (2a-1), \dots, (Na-q) - (Na-1)$

gespeichert.

Die im Bildzeilenspeicher 11 eingeschriebenen Informationen werden bei der genannten Vorzugsausführung in folgender Reihenfolge ausgelesen:

0–15, 16–31, 32–47,..., 880–895,

und im allgemeinen in folgender Reihenfolge:

0 – (q – 1), q – (2q – 1), 2q – (3q – 1), ..., (na – q) – (Na – 1). Diese Art des Auslesens wird durch den Bildpunktadresserkreis h12 realisiert, der hierzu einen Zähler 13 und einen mittels eines Schalters 14 hierauf anzuschliessenden Dekodierer 15 besitzt. Der Schalter 14 befindet sich hierbei in der nicht angegebenen Stellung.

Obwohl die vorgenannte Weise für das Einlesen des Bildzeilenspeichers 11 ebenso mit Hilfe eines Zählers und eines Dekodierers realisiert werden kann, sind letztgenannte Mittel nicht in der Figur angegeben, da für ein gutes Begreifen der Erfindung nur der Adresserkreis 12 wichtig ist. Die Frequenz, mit der der Bildzeilenspeicher 11 eingelesen wird, braucht nicht gleich der Frequenz zu sein mit der der Bildzeilenspeicher ausgelesen wird; wohl müssen beide Frequenzen grösser als die Frequenz sein, die mit der für die Abbildung einer Bildzeile benötigten Zeit korrespondiert und von der Anzahl Bildzeilen und der Bildwiedergabefrequenz bestimmt wird.

Die aus dem Bildzeilenspeicher 11 ausgelesene Informationen, d.h. die pro Bildzeile nacheinander erscheinenden  $\frac{b}{q}$  Worte von q Bits, werden aufeinanderfolgend einem zur Bildpunktumsetzung 16 gehörenden Register 17 zugeführt. Jedes der nacheinander angebotenen Worte wird in die Teile I und II dieses Registers eingeschrieben, danach ausgelesen, über eine q Adern besitzende Leitung 18 transportiert und über Schalter 19 in das Pufferregister 20 eingeschrieben. Der Schalter 19 befindet sich in der hier nicht angegebenen Stellung. Vom Pufferregister 20 werden die diesbezüglichen Informationen dem Monitorschirm zugeführt. Obwohl die aus dem Bildzeilenspeicher 11 ausgelesenen Informationen dem Pufferregister 20 direkt zugeführt werden könnten, geschieht dieses, wie nachfolgend erklärt wird, im Zusammenhang mit einer günstigeren Ausführung der Einrichtung 3 über die Bildpunktumsetzung 16.

Die bisher beschriebene Einrichtung kann in einem Radarabtaster zum Umwandeln von Daten in Polarkoordinatendarstellung in eine Darstellung mit kartesischen Koordinaten für die Anzeige von aus Videosignalen einer Radaranlage erhaltenen Radarinformationen auf einem zeilenweise arbeitenden Monitorschirm, wie beschrieben in der U.S. Patentschrift 4 128 838, angewendet werden. Bei diesem Radarabtaster werden die ankommenden Radarinformationen quantisiert und in einem Radareingangsspeicher eingeschrieben, wobei das Einschreiben der Radarinformationen aus dem Sichtfeld der Radaranlage mit einer ersten Geschwindigkeit erfolgt. Dieser

Radarabtaster enthält dazu einen RAM-Speicher, der auf vorgenannte Weise eingerichtet ist. Der Entfernungsmessbereich des Radarsignales ist für jeden Azimutwinkel ( $\varphi$ ) in n Stücke mit jeweils k Entfernungsinkrementen  $\Delta r$  aufgeteilt, wobei  $n \leq N$  und die Länge  $k\Delta r$  der Entfernung entspricht, die durch a Speicherzellen, multipliziert mit einem Faktor  $\sqrt{2}$ , gegeben ist. Genannter Radarabtaster enthält weiter einen Adressierkreis, der für die Radarinformationen mit der ersten Geschwindigkeit Adressen zum Einschreiben der Radarinformationen aus dem Radareingangsspeicher in dem RAM-Speicher erzeugt, derart dass die natürliche Adressenfolge im RAM-Speicher der Reihenfolge der Bildpunkte auf dem Monitorschirm entspricht. Dieser Adressierkreis besteht dazu aus einem Azimutwinkelzähler, einem Sinus-/Kosinusgenerator, einem Startadressengenerator, der aus den durch den Sinus-/Kosinusgenerator, zugeführten Signalen die Startadressen  $jk\Delta r \cos \varphi$  und  $jk\Delta r \sin \varphi$  mit  $j = 0, 1, 2, \dots, n-1$  erzeugt, und einem Inkrement-Adressengenerator, der, ausgehend von den n Startadressen, diese jeweils pro Speicherzyklus um  $\Delta r \cos \varphi$ , bzw.  $\Delta r \sin \varphi$  so erhöht, dass unter Berücksichtigung der virtuellen Positionen  $(x_c, y_c)$  der Radaranlage gegenüber der Darstellung auf dem Monitorschirm in k aufeinanderfolgenden Speicherzyklen die Adressen  $x = x_c + (jk+m)\Delta r \cos \varphi$  und  $y = y_c + (jk+m)\Delta r \sin \varphi$  mit  $m = 0, 1, 2, \dots, k-1$  erzeugbar sind. Die im Radareingangsspeicher vorhandenen Radarinformationen, n Entfernungsstücken entsprechend, sind auf in dem jeweiligen Speicherzyklus erzeugten Adressen des RAM-Speichers einschreibbar, wobei jede Adresse eine einzige innerhalb eines Teilspeichers gelegene Speicheradresse bezeichnet.

Ausser den Informationen, die aus Videosignalen einer Radaranlage erhalten werden, können in dem RAM-Speicher auch synthetische Informationen eingeschrieben werden.

Informationen, die in den RAM-Speicher übernommen werden sollen, müssen über Leitung 21, mittels Schalter 9, der sich dabei in der nicht gegebenen Stellung befindet, in das Pufferregister 10 eingeschrieben werden. Von dort werden diese Informationen in den Speicher 1 gesetzt. Der Schalter 9 befindet sich dabei abwechselnd in der Stellung, worin Informationen mit der zugehörigen Adressierung über die Leitung 21 in den Speicher 1 eingeschrieben werden können und in der Stellung, wobei Informationen, deren Adressierung über Leitung 8 erfolgt, aus diesem Speicher ausgelesen werden können. Dieser Schalter wird von einer Zeitsteureinheit gesteuert, welche die erforderlichen Steuersignale für die in der Figur abgebildeten Einheiten liefert. Da für ein gutes Begreifen der Erfindung eine Beschreibung der Zeitsteuerung nicht erforderlich ist, ist diese nicht in der Figur angegeben.

Soll ein bestimmter Teil der in dem RAM-Speicher befindlichen Informationen auf dem ganzen Monitorschirm abgebildet werden, muss den mit den ausgelesenen Informationen korrespondierenden Bildpunkten eine Anzahl Bildzeilen und Bildpunkte zugefügt werden, damit der gesamte Monitorschirm ausfüllt wird.

Angenommen wird, dass ein Teil  $\beta^2$  des Speicherinhaltes abgebildet werden soll, also Informationen, die korrespondieren mit  $\beta b$  Bildpunkten von  $\beta b$  Bildzellen. In diesem Fall müssen die Informationen bezüglich der übrigen für die Abbildung erforderlichen  $(1-\beta)b$  Bildzeilen und der übrigen  $(1-\beta)b$  Bildpunkte der genannten  $\beta b$  Bildzellen zugeführt werden. Die in der Figur abgebildete Schaltung gilt für  $\beta = \frac{1}{2}$ ; zuerst wird daher die Erfindung für diesen  $\beta$ -Wert erklärt, danach werden kurz die zu treffenden Massnahmen für  $\beta$ -Werte von  $\frac{1}{3}, \frac{1}{4}$ , usw. angegeben. Einfachheitshalber werden wieder die vorgenannten für die Vorzugsausführung der hier beschriebenen Einrichtung geltenden Parameter ( $b=896, q=16$ ) angenommen.

Die erfindungsgemäße Schaltung arbeitet mit anderen Parametern ähnlich.

Weiter wird angenommen, dass die Informationen bezüglich der Bildzeilen 140–587 und der Bildpunkte 50–497 auf dem gesamten Schirm abgebildet werden sollen. Für jede Bildzeile befinden sich diese Informationen aufeinanderfolgend im Bildzeilenspeicher 11. Aus diesem Bildzeilenspeicher werden die Informationen für eine Bildzeile in Gruppen von 16 Bits ausgelesen. Für die Bildzeilen 140–587 sind jetzt nur die Informationen bezüglich der Bildpunkte 50–497 wichtig; aus dem Bildzeilenspeicher werden jedoch die Informationen bezüglich der Bildpunkte 48–63, 64–79, 80–95, ..., 480–495, 496–511 ausgelesen.

Die Adressierung dieser Informationen im Bildzeilenspeicher wird im Bildpunktadressierkreis 12 realisiert. Der Zähler 13 in diesem Kreis zählt die Plätze im Bildzeilenspeicher ab, wo sich aufeinanderfolgend in Gruppen von 16 Bits die auszulesenden Informationen befinden. Dieser Zähler muss jedoch nicht mit der Adresse der ersten Gruppe von 16 Bits starten, sondern, da nur Information bezüglich der Bildpunkte ab dem durch die Koordinate  $x_0$  (für  $x_0$  ist hier 50 gewählt worden) festgelegten Bildpunkte wichtig ist, mit der Adresse der dritten Gruppe von 16 Bits. Die Gruppe Bits, mit deren Adressierung der Zähler beginnen muss, wird bestimmt durch den Wert  $\lceil \frac{x_0}{q} \rceil$ ; dieses ist hier  $\lceil \frac{50}{16} \rceil = 3$ . Dieser Wert wird dann der Schaltung 22

zugeführt, worin die durch den Zähler 13 angegebenen Adressen derartig geändert werden, dass die Adressen der gewünschten Gruppen von 16 Bits, zu beginnen mit der Adresse der durch  $x_0$  bestimmten Gruppe, erhalten werden. Die Geschwindigkeit mit der die Schaltung 22 die Adressen der aus dem Bildzeilenspeicher zu lesenden Gruppen von 16 Bits verschafft, muss, da in derselben Zeit die Hälfte der Gruppen ausgelesen wird, halbiert werden. Diese Halbierung geschieht mit dem Frequenzteiler 23. Von dort werden die Adressen über den sich dann in der angegebenen Stellung befindlichen Schalter 14 dem Dekodierer 15 zugeführt, der schliesslich dafür sorgt, dass die Informationen bezüglich der Bildpunkte 48–63, 64–79, 80–95, ..., 480–495, 496–511 nacheinander aus dem Bildzeilenspeicher ausgelesen werden. Der Schalter 14 wird manuell bedient, abhängig davon, ob die vollständige Information (grosses Bild) oder ein Teil der Information (kleines Bild) aus dem RAM-Speicher auf dem gesamten Schirm abgebildet werden soll. Das für den Schalter 14 manuell erhältene Steuersignal wird mit G/K (Grossbild/Kleinbild) bezeichnet und ist für die Schalter 7, 14 und 19 gleich.

Die aus dem Bildzeilenspeicher ausgelesenen Informationen werden der Bildpunktumsetzung 16 zugeführt, wo aus den angebotenen Gruppen von 16 Bits neue Gruppen von 16 Bits abgeleitet werden, die pro Bildzeilenteil die abzubildenden Speicherinformationen ab der Bildpunktkoordinate  $x_0$  darstellen.

Eine Gruppe von 16 Bits wird in die Teile I und II des Registers 17 eingeschrieben; in den Teil III dieses Registers werden die Bits eingeschrieben, die, bevor die genannte Gruppe eingeschrieben wird, in dem Teil II des Registers vorhanden waren.

Im Register 17 befinden sich daher nacheinander folgende Bits

| Teil III | Teil II | Teil I  |

|----------|---------|---------|

| –        | 48–55   | 56–63   |

| 56–63    | 64–71   | 72–79   |

| 72–79    | 80–87   | 88–95   |

| ...      | ...     | ...     |

|          | 480–487 | 488–495 |

| 488–495  | 496–503 | 504–511 |

Die an den Ausgängen B und C des Register 17 verfügbare Information ist jetzt aufeinanderfolgend:

| Ausgang B | Ausgang C |

|-----------|-----------|

| 48–54     | 48–62     |

| 56–70     | 64–78     |

| 72–86     | 80–94     |

| ...       | ...       |

| 472–486   | 480–494   |

| 488–502   | 496–510   |

Hierzu sei bemerkt, dass das die höchste Bildpunktnummer bezeichnende Bit bei den Ausgängen B und C nicht mehr wichtig und daher weggelassen worden ist. Der Schalter 24 lässt die Information an B und C wechselweise durch; die Schaltfrequenz dieses Schalters ist zweimal so gross wie die Frequenz, mit der die Information dem Register 17 zugeführt wird. Am durch 15 Bits bestimmten Punkt D erscheinen nacheinander die Informationen für folgende Bildpunkte:

48–62, 56–70, 64–78, 72–86, ..., 488–502, 496–510.

Von den Bits 0–14 am Punkt D können vom Schalter 25 die Bits 0–7, 1–8, 2–9, 3–10, 4–11, 5–12, 6–13 oder 7–14 durchgelassen werden, abhängig von dem Wert  $x_0 - q \cdot \lceil \frac{x_0}{q} \rceil$ . Dieser Wert kann sein 0, 1, 2, ..., 7 womit die Bits 0–7, 1–8, 2–9, ..., oder 7–14 durchgelassen werden. Im hier beschriebenen Fall ist

$x_0 - q \cdot \lceil \frac{x_0}{q} \rceil$  gleich 2 und werden die Bits 2–9 durchgelassen. Am Punkt E erscheinen jetzt nacheinander die Informationen der Bildpunkte:

50–57, 58–65, 66–73, 74–81, ..., 490–497, 498–505.

Diese Informationen werden der Bildpunktvervielfacherschaltung 26 zugeführt. Bevor jedoch die Wirkungsweise dieser Schaltung erklärt wird, muss erst der Speicheradressierkreis 4 näher betrachtet werden.

Wenn der Schalter 7 des Speicheradressierkreises 4 in der gezeichneten Stellung steht, werden die Informationen bezüglich der Bildzeilen  $y_0 - (y_0 + \frac{1}{2}b)$ , hier 140–587, zweimal ausgelesen. Der Speicheradressierkreis 4 besitzt dafür eine

Schaltung 27, die das Ausgangssignal des Zählers 5 durch zwei dividiert; folglich anstelle der b Bildzeilen die Hälfte der Anzahl Bildzeilen zweimal so langsam abzählt. Da es sich um die

Informationen handelt, die zu den Bildzeilen  $y_0 - (y_0 + \frac{1}{2}b)$

gehören, muss das Ausgangssignal der Schaltung 27 mit dem Wert  $y_0$  erhöht werden; dieses geschieht im Addierkreis 28. Da in einer zweimal so langen Zeit die Informationen, die zu den

Bildzeilen  $y_0 - (y_0 + \frac{1}{2}b)$  gehören, in dem RAM-Speicher 1

adressiert werden, werden diese Informationen stets zweimal ausgelesen. Somit werden an der Einrichtung 3 die Informationen ausgelesen, die zu den Bildzeilen 140, 140, 141, 141, 142, 142, ..., 586, 586, 587, 587 gehören; auf diese Weise sind abermals Informationen ausgelesen worden, die zu 896 Bildzeilen gehören.

In der Bildpunktvervielfacherschaltung 26 müssen jetzt die Informationen, die zu den Bildpunkten 50–505 gehören, in Informationen umgesetzt werden, die zu den erforderlichen 896 Bildpunkten gehören. Hierzu wird jede Ader der Zuführleitung beim Punkt E verdoppelt. Die Informationen, die zu den Bildpunkten 50–57, 58–65, 66–73, 74–81, ..., 490–497, 498–505 gehören, werden dann in Informationen umgesetzt, die zu den Bildpunkten 100–115, 116–131, 132–147, 148–163, ..., 980–995, 996–1011 gehören oder genauer numeriert: 0–15, 16–31, 32–47, 48–63, ..., 880–896.

Die Bildpunkte 896–911 haben für die Abbildung keinerlei Bedeutung. Hierbei ist die zu zwei nebeneinander gelegenen

Bildpunkten gehörende Information identisch. Da die Informationen, die zu einer Bildzeile gehören, stets zweimal nacheinander ausgelesen werden, wird die Information, die zu jedesmal vier in einem Quadrat formierter Bildpunkt gehört, identisch sein.

Die aus der Bildpunktvervielfacherschaltung 26 stammenden Informationen werden über den sich wie in der Figur angegebenen Stellung befindlichen Schalter 19 in das Pufferregister 20 eingeschrieben und von dort dem Monitorschirm zugeführt.

Bis jetzt ist nur beschrieben worden wie die Einrichtung 3 für den Fall aufgebaut ist, wobei ein Viertel der im Speicher 1 vorhandenen Informationen auf dem gesamten Schirm abgebildet wird. Ist jedoch  $\beta = \frac{1}{3}$  oder wird ein Neuntel der im Speicher 1 vorhandenen Informationen auf dem gesamten Schirm abgebildet, muss ein Drittel der Gesamtanzahl Bildzeilen dreimal nacheinander ausgelesen und folglich dreimal so lange adressiert werden, muss ein Drittel der Anzahl Bildpunkte in einer dreimal so langen Zeit ausgelesen werden und muss die Bildpunktvervielfacherschaltung so aufgebaut sein, dass jeweils neun, in einem Quadrat formierter Bildpunkte identisch sind.