(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4698776号

(P4698776)

(45) 発行日 平成23年6月8日(2011.6.8)

(24) 登録日 平成23年3月11日(2011.3.11)

(51) Int.Cl.

H03D 7/14 (2006.01)

H03D 7/00 (2006.01)

F 1

H03D 7/14

H03D 7/00C

D

請求項の数 10 (全 9 頁)

(21) 出願番号 特願平10-15076

(22) 出願日 平成10年1月9日(1998.1.9)

(65) 公開番号 特開平10-209760

(43) 公開日 平成10年8月7日(1998.8.7)

審査請求日 平成15年9月24日(2003.9.24)

審判番号 不服2007-33157(P2007-33157/J1)

審判請求日 平成19年12月7日(2007.12.7)

(31) 優先権主張番号 9700486.5

(32) 優先日 平成9年1月11日(1997.1.11)

(33) 優先権主張国 英国(GB)

(73) 特許権者 593096712

インテル コーポレイション

アメリカ合衆国 95052 カリフォルニア州 サンタクララ ミッション カレッジ ブールバード 2200

(74) 代理人 100079980

弁理士 飯田 伸行

(72) 発明者 ピアチエスラフ イゴール スーチノフ

イギリス, エスエヌ2 3キュウジー ウィルトシア, スウィンドン, ラーチモア

クロウス 44

最終頁に続く

(54) 【発明の名称】低電圧二重平衡型ミキサー回路装置

## (57) 【特許請求の範囲】

## 【請求項 1】

- a ) シングルエンド入力端とシングルエンド出力端とを有する増幅段と、

- b ) 第1及び第2電流信号入力端と、同相入力インピーダンスを有する局部発振ドライバー側第1及び第2入力端と、第1及び第2差動出力端とを配置したミキサー<sub>コア</sub>の構成であり、且つこの第1電流信号入力端を前記増幅段の前記シングルエンド出力端に接続するミキサー<sub>コア</sub>と、

- c ) 接地部と、前記ミキサー<sub>コア</sub>の前記第2電流信号入力端との間に配したDC電流源を有するバイアス回路と、

- d ) 前記バイアス回路の出力部と前記接地部のそれぞれに接続するキャパシタとを備えており、更に、

e ) 発振入力端を配置して且つ第1及び第2発振出力端を配置した局部発振ドライバー回路の前記第1及び第2発振出力端を、前記ミキサー<sub>コア</sub>の局部発振ドライバー側第1及び第2入力端へそれぞれ接続すると共に、この局部発振ドライバー側第1及び第2入力端の同相入力インピーダンスが、前記局部発振ドライバー回路の前記第1及び第2発振出力端における同相出力インピーダンスに比べて低い関係を成す前記局部発振ドライバー回路とを備えたことを特徴とするミキサー回路。

## 【請求項 2】

前記ミキサー<sub>コア</sub>が二重平衡型である請求項1に記載のミキサー回路。

## 【請求項 3】

10

20

前記増幅段が相互コンダクタンス増幅器として動作する増幅用トランジスタを含む請求項1に記載のミキサー回路。

【請求項4】

前記増幅段のトランジスタは、その制御電極を前記シングルエンド入力端からの信号入力端にして、このトランジスタの第1主電極を前記シングルエンド出力端に接続して、更に、第2主電極を接地部に接続する請求項3に記載のミキサー回路。

【請求項5】

前記増幅段のトランジスタの前記制御電極にDCバイアスを与えて、更に、入力キャパシタを介して前記シングルエンド入力端に接続する請求項4に記載のミキサー回路。

【請求項6】

前記増幅段のトランジスタの前記第2主電極と前記接地部との間にインダクタを接続する請求項4に記載のミキサー回路。

【請求項7】

前記バイアス回路が、DCバイアスする制御電極と、この出力部とする第1主電極と、前記接地部に接続する第2主電極と有するバイアス用トランジスタを含む請求項1に記載のミキサー回路。

【請求項8】

前記局部発振ドライバー回路が、2つの前記発振入力端と、第1及び第2トランジスタとを有するものであって、前記第1及び第2トランジスタのそれぞれが制御電極と第1及び第2主電極とを備え、

そして、

前記第1トランジスタの制御電極を一方の前記発振入力端に接続して、

前記第2トランジスタの制御電極を他方の前記発振入力端に接続して、

前記第1及び第2トランジスタの各第2主電極を互いに接続して且つ電流源に接続して、前記第1及び第2トランジスタの各第1主電極を、前記局部発振ドライバー回路の前記第1及び第2発振出力端のそれぞれに接続する請求項1に記載のミキサー回路。

【請求項9】

前記第1トランジスタの前記第1主電極と電圧供給源との間に第1の抵抗を接続して、前記第2トランジスタの前記第1主電極と前記電圧供給源との間に第2の抵抗を接続する請求項8に記載のミキサー回路。

【請求項10】

前記局部発振ドライバー回路が、更に、第3の抵抗を前記第1及び第2トランジスタの各前記第1主電極間に接続する請求項9に記載のミキサー回路。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、ミキサー回路装置に関し、特にシングルエンド入力と差動出力とを有するミキサー回路装置に関する。

【0002】

【従来の技術】

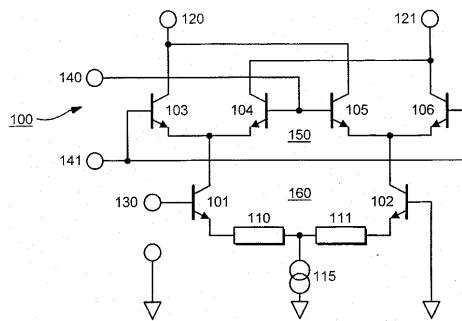

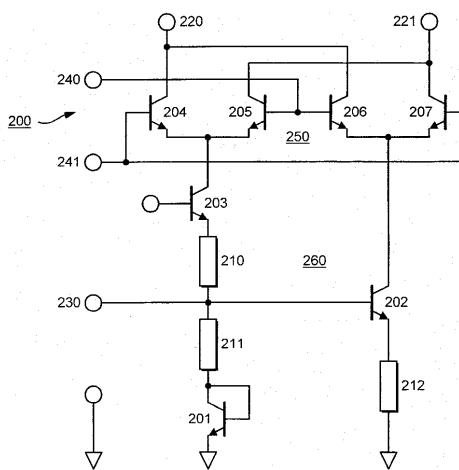

R Fミキサー回路は、最新の無線システムにおいて重要な構成部であり、このミキサー回路のパラメータが、ミキサー回路が使用されるシステムの主な特性を決定する。従来、最も一般的なミキサー回路構成は、ギルバートセル構成もしくはマイクロミキサー構成であり、図3及び図4に示されている。

【0003】

図3及び図4において、各ミキサー回路は、入力端子において、シングルエンドrf入力信号を受信し、出力端子において、差動信号を出力する。この差動信号は、入力信号を増幅し、続いてそれを局部発振器からの信号と混合したものである。両ミキサー回路とも、容易にIC構成で実施することができ、自動車電話等においてよく使用される。しかし、従来のこのような回路構成を有するミキサー回路は、雑音特性が悪い。また、このよう

10

20

30

40

50

なミキサー回路においては、2.7Vあるいはそれ以上の供給電圧が必要であり、これは電源と接地との間に3つのトランジスタが直列に配置されているからである。従って、これらミキサー回路は、低電圧適用に適さない場合がある。

【0004】

図3は、従来のミキサー回路である、ギルバートセル回路を示す図である。図3によると、ギルバートセル回路100は、入力端子130でシングルエンド入力電圧信号を受信し、入力端子140、141で局部発振器電圧の差動信号を受信する。トランジスタ101、102、抵抗110、111、及び電源115は、差動型相互コンダクタンス増幅回路160を形成し、トランジスタ103～106はミキサーコア150を形成する。入力端子130における入力電圧の増加は、トランジスタ101のコレクタ電極からの信号電流を増加させる。電源115及び抵抗110、111は、トランジスタ102のコレクタ電極から相補形減少電流が送られることを確実にする。これら電流信号は、電源115が定電流源として適用されている場合、平衡調整される。

【0005】

ミキサーコア150は、入力端子140、141において局部発振器の差動信号を受信する。入力端子140の電圧が正の場合、入力端子141の電圧は負になり、トランジスタ104、105は、ONに切り換えられ、トランジスタ103、106は、OFFに切り換えられる。従って、トランジスタ101のコレクタ電流は出力端子121へと送られ、トランジスタ102のコレクタ電流は、出力端子120へと送られる。トランジスタ101、102のコレクタ電流は、入力端子141の電圧が入力端子140よりも高い場合、逆の出力端子121、120に切り換えられる。

【0006】

図4は、従来のミキサー回路である、マイクロミキサー回路を示す図である。図4によると、マイクロミキサー回路200は、入力端子230においてシングルエンド入力信号を受信し、出力端子240、241において、局部発振器の差動信号を受信する。トランジスタ201～203及び抵抗210～212は、相互コンダクタンス増幅回路260を形成し、トランジスタ204～207は、ミキサーコア250を形成する。

【0007】

入力端子230における電圧の増加は、トランジスタ202のコレクタ電極から送られる電流を増加させ、トランジスタ203のコレクタ電極から送られる電流を減少させる。従って、このミキサー回路は、シングルエンド入力と差動出力とを有する、相互コンダクタンス増幅回路として機能する。増幅回路260からの出力は、差動電流信号としてトランジスタ202、203のコレクタ電極に与えられ、ミキサーコア250に出力される。

【0008】

ミキサーコア250は、図3に示されるミキサー回路におけるミキサーコア150と同様に機能する。

【0009】

【発明が解決しようとする課題】

図3に示されるギルバートセル回路において、雑音特性が悪いのは、主に抵抗110、111による熱雑音によるところが大きく、抵抗110、111は、電流路に直接雑音を生じさせる。電源115もまた出力信号に雑音を発生させる。これは、電源115の入力端子と出力端子にかけて大きな電圧の振れが生じるからである。また、トランジスタ101、102は、ベース抵抗が直列に配置されているため、出力端子120、121においてかなり大きな雑音が発生することになる。

【0010】

図4に示されるマイクロミキサー回路は、非常に線形的な特性と無線周波数における大きなダイナミックレンジとを有している。しかし主電流路において使用される抵抗の数が多いため、雑音特性は、ギルバートセル回路よりもむしろ悪い。

【0011】

本発明は、上記事情に鑑みなされたもので、より優れた雑音特性と低電圧供給条件とを

10

20

30

40

50

有するミキサー回路装置を提供することを目的とする。

【0012】

【課題を解決するための手段】

本発明は、ミキサーコアと、シングルエンド増幅段とを有するミキサー回路装置において、前記ミキサーコアは、第1の信号入力で前記増幅段からのシングルエンド出力信号を受信し、該シングルエンド出力信号に対応して差動出力信号を出力することを特徴とする。

【0013】

本発明は、入力される信号に応じて差動出力信号を出力し、ミキサーコアと、シングルエンド増幅段と、バイアス手段とを有するミキサー回路装置において、前記ミキサーコアは、第1の電流信号入力と、第2の電流信号入力と、第1の局部発振器信号入力と、第2の局部発振器信号入力とを有し、前記シングルエンド増幅段は、前記入力信号に応じて前記ミキサーコアの前記第1の電流信号入力に電流信号を与え、前記バイアス手段は、低インピーダンスを有し、前記ミキサーコアの前記第2の信号入力にバイアス電流を与えることを特徴とする。

【0014】

【発明の実施の形態】

次に、本発明に係るミキサー回路の実施の形態について、図面を参照して詳細に説明する。

【0015】

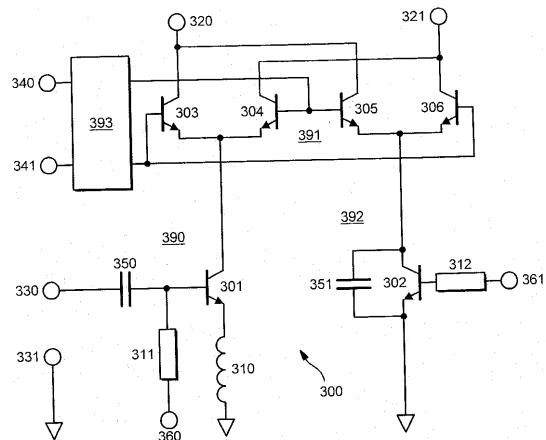

図1は、本発明の実施の形態である二重平衡型ミキサー回路を示す図である。

【0016】

図1において、ミキサー回路300は、増幅回路390と、バイアス装置392とミキサーコア391と、局部発振器ドライバ回路393によって構成される。その動作において、局部発振器の差動信号が入力端子340、341に入力され、バイアス電位が端子360、361に印加され、シングルエンド入力信号が入力端子330に入力され、差動出力信号が出力端子320、321で得られる。

【0017】

増幅回路390は、トランジスタ301の周辺に配置されている。トランジスタ301のベース電極は、抵抗311を介して端子360に接続し、またキャパシタ350を介して入力端子330に接続している。インダクタ310は、トランジスタ301のエミッタ電極と接地電位との間に接続されている。トランジスタ301のコレクタ電極は、ミキサーコア391への出力電流路を形成している。

【0018】

電流バイアス装置392は、トランジスタ302を有している。トランジスタ302は、エミッタ電極が接地電位に直接接続し、ベース電極が抵抗312を介して端子361に接続している。またトランジスタ302は、コレクタ電極からミキサーコア391に対して電流信号を与える。キャパシタ351は、トランジスタ302のコレクタ電極と接地電位との間に接続されている。

【0019】

ミキサーコア391は4つのトランジスタ303～306を有している。トランジスタ303、304は、お互いのエミッタ電極が結合し、増幅回路390からの出力電流信号を受信する。また、トランジスタ305、306は、お互いのエミッタ電極が結合し、バイアス装置392から電流を与えられる。トランジスタ303、305のコレクタ電極は、お互いに接続し、また出力端子320に接続している。トランジスタ304、306のコレクタ電極は、お互いに接続し、また出力端子321に接続している。ミキサーコア391は、トランジスタ303～306のベース電極と局部発振ドライバ回路393の差動出力との接合点において、局部発振ドライバ回路393によって制御されている。トランジスタ303、306は、ベース電極がお互いに接続し、また局部発振ドライバ回路393の第1の出力に接続している。また、トランジスタ304、305は、ベース電極がお

10

20

30

40

50

互いに接続し、また局部発振ドライバ回路 393 のもう一方の出力に接続している。

【0020】

増幅回路 390 は、入力端子 330 で、R F 電圧信号を受信し、これを電流信号に変換する。変換された電流信号は、トランジスタ 301 の ベース電極に与えられる。従って、増幅回路 390 は、高インピーダンス電源を構成する。キャパシタ 350 は、入力信号のあらゆる d c 要素を阻止すべく動作する。トランジスタ 301 の D C バイアスは、抵抗 311 及び端子 360 に印加されるバイアス電位によって実行される。トランジスタ 301 のエミッタ接地電流利得 の複雑な特性により、インダクタ 310 は、トランジスタ 301 のベースエミッタ回路において直列負帰還を実行する。

【0021】

10

インダクタ 310 は非雑音素子であり、特定の周波数領域において周波数に無関係の負帰還を実行する。この周波数領域は、インダクタ 310 の値及び所望の周波数におけるトランジスタ 301 のベースエミッタ抵抗に左右される。またインダクタ 310 の値は増幅回路 390 の利得及び線形性に影響を及ぼす。抵抗をインダクタ 310 の代わりに使用することもできるが、インダクタ 310 を使用する方が増幅回路 390 においてより多くの線形特性及び優良な雑音特性を得ることができる。

【0022】

インダクタ 310 は、全体もしくは一部分において、I C 実装の寄生インダクタンス、及び／もしくはボンディングワイヤー、及び／もしくは、接続ピンによって構成することができる。

20

【0023】

トランジスタ 301 は、ベースエミッタ抵抗による雑音の発生を軽減するために、広域エミッタ領域を有するトランジスタであることが望ましい。しかし、エミッタ領域の大きいトランジスタは寄生容量も高く、従って、リーク及び低電流密度による電流利得 の低減が生じる。従って、特定のミキサー回路に組み込まれるトランジスタ領域及び駆動電流を選択する際に、雑音特性を優先するか利得を優先するかを選択する必要がある。

【0024】

ミキサー回路 300 の入力インピーダンスは、インダクタ 310 の値及び、トランジスタ 301 の f<sub>T</sub> (トランジション周波数) によって決定される。

30

【0025】

バイアス装置 392 は、トランジスタ 302 のコレクタ電極からミキサー コア 391 のトランジスタ 305、306 にバイアス電流を与えるために動作する。抵抗 312 は、トランジスタ 302 のベース電極をバイアス電位が印加されている端子 361 に接続する。キャパシタ 351 は、トランジスタ 302 のコレクタ電極における信号の a c 要素の低インピーダンス接地を実行する。この信号の d c 要素は、適度に一定に保たれる。

【0026】

局部発振ドライバ回路 393 の 条件 は、局部発振ドライバ回路の 入力端 に入力される電圧信号を変換して出力端に与えることと、この入力信号に応じた出力端で接地電位基準の 同相出力インピーダンスを高くすること が必要である。これに対する理由は、下記に述べるミキサー コア 391 の動作の説明の中で明らかにする。

40

【0027】

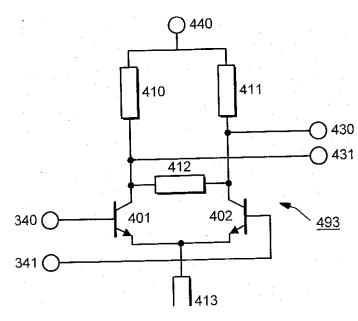

局部発振ドライバ回路 393 は、変成器として適用することができる。局部発振ドライバ回路 393 が、全ミキサー回路 300 と同一のチップ上に搭載されなければならない場合には、図 2 に示されるような局部発振ドライバ回路 493 を適用することができる。

【0028】

ドライバ回路 493 は、ロングテイルトランジスタ組であるトランジスタ 401、402 を有し、トランジスタ 401、402 は、ベース電極がそれぞれ局部発振器信号入力端子 340、341 に接続している。抵抗 410、411 はそれぞれトランジスタ 401、402 のコレクタ電極を供給電圧端子 440 に接続している。抵抗 412 はトランジスタ 4

50

01及び402のエミッタ電極の間に接続されている。局部発振ドライバ回路出力端子430、431は、トランジスタ402、401のコレクタ電極にそれぞれ接続され、これら出力端子430、431は、図1に示されるミキサーコア391のトランジスタ303～306のベース電極への接続を形成する。

【0029】

局部発振ドライバ回路493は、局部発振器信号入力端子340、341に入力される局部発振器信号によって制御される。トランジスタ401、402は、交互に動作し、また正の電圧を交互に出力端子430、431に与えるよう、局部発振器信号によって「ハード切り換え」がされる。この電圧は、トランジスタ304、305、及びトランジスタ303、306を交互にONに切り換える。

10

【0030】

トランジスタ304、305がONになるとき、トランジスタ301のコレクタ電流は、トランジスタ304のエミッタ電極を通過しトランジスタ304のベース電極及びコレクタ電極へと送られる。出力端子321へと送られるトランジスタ304のコレクタ電流は、ベース電流に比例し、トランジスタの電流利得係数に応じて増大する。トランジスタ305の入力インピーダンスが、局部発振ドライバ回路493の同相出力インピーダンスに比べて低いという条件の下、トランジスタ304のベース電極からの信号電流は、主としてトランジスタ305のベース電極へと送られ、またトランジスタ305のコレクタ電流は、トランジスタ304のコレクタ電流を補足する。接地への入力信号を基準とする同相出力インピーダンスが、トランジスタ305の入力インピーダンスよりも十分に高い場合、差動出力端子320、321において平衡出力が得られる。

20

【0031】

ミキサーコアの出力の平衡は、さらにトランジスタ303、306及びトランジスタ304、305によるインピーダンスバイアスによって制御することができ、この制御は、端子360、361に印加される電位を変化させることで得ることができる。

【0032】

トランジスタ303、306がONに切り換えられるとき、トランジスタ301のコレクタ電流は、逆の差動出力端子320へと送られ、相補形出力は、もう一方の出力端子321へと送られる。

30

【0033】

従って、シングルエンド入力信号から差動出力信号への変換は、ミキサーコア391自身で実行され、これによりミキサー回路の実施において使用されるトランジスタ数は削減され、使用される供給電圧は低減される。

【0034】

トランジスタ305、306の相補形電流は、トランジスタ303、304のエミッタ領域をトランジスタ305、306のそれよりも大きく設定することで増加させることができる。例えば、関連する周波数に応じて3:2または、2:1の比率で設定することができる。このことにより、トランジスタ303、304のベース電流は高くなり、ミキサーコアにおけるトランジスタの寄生容量による損失が補われる。

40

【0035】

局部発振ドライバ回路493の同相出力インピーダンスは、抵抗410、411によって決定される。これら抵抗の値は、ドライバ回路493の適切な動作に対応してできるだけ高い方が望ましい。通常、抵抗410、411は、抵抗412よりもかなり大きく、抵抗412の抵抗は、局部発振ドライバ回路493の差動出力インピーダンスを決定するものである。抵抗410、411を双方とも同様に適当なインダクタと交換してもほとんど同様の効果を得ることができる。

【0036】

本実施の形態は、n p n二極性トランジスタについてのみ説明がなされているが、本発明はこれに限定されるものではなく、同様に、p n p二極性トランジスタまたは、電界効果トランジスタでも実現が可能である。上述のコレクタ電極及びエミッタ電極は、電界効

50

果トランジスタの第1及び第2の主電極としてのドレイン電極及びソース電極に対応する。

【0037】

【発明の効果】

上記の説明のように、本発明に係るミキサー回路装置において、シングルエンド入力信号から差動出力信号への変換は、ミキサー コア 391 自体で実行され、これによりミキサー回路の実施において使用されるトランジスタ数は削減され、使用される供給電圧は低減される。また、非雑音素子である負帰還インダクタ 310 の適用により雑音値は軽減される。従って、雑音の少ない低電圧二重平衡型ミキサー回路を得ることができる。

【図面の簡単な説明】

10

【図1】 本発明の実施の形態であるミキサー回路装置を示す図である。

【図2】 本発明の実施の形態である図1のミキサー回路に適当な局部発振ドライバ回路を示す図である。

【図3】 従来のギルバートセルミキサー回路を示す図である。

【図4】 従来のマイクロミキサー回路を示す図である。

【符号の説明】

100、200、300 ミキサー回路

101～106、201～207、

301～306、401、402 トランジスタ

110、111、210～212、

311、312、410～413 抵抗

20

115 電源

120、121、220、221、

320、321、430、431 出力端子

130、140、141、230、240、241、

330、340、341 入力端子

150、250、391 ミキサー コア

160、260、390 増幅回路

310 インダクタ

350、351 キャパシタ

30

360、361 バイアス電位の端子

392 バイアス装置

393、493 局部発振ドライバ回路

440 供給電圧端子

【 図 1 】

【図2】

【 図 3 】

【 図 4 】

---

フロントページの続き

合議体

審判長 長島 孝志

審判官 飯田 清司

審判官 加内 慎也

(56)参考文献 特開平4-207210 (JP, A)

欧州特許出願公開第 (EP, A1) 0584870

欧州特許出願公開第 (EP, A1) 0726646

国際公開第 / (WO, A1) 96/23365

(58)調査した分野(Int.Cl., DB名)

H03D 7/00-9/06