## SCHWEIZERISCHE EIDGENOSSENSCHAFT

BUNDESAMT FÜR GEISTIGES EIGENTUM

<sub>①</sub> CH 671837 A5

(51) Int. Cl.4: G 06 F

12/16

Erfindungspatent für die Schweiz und Liechtenstein

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

## **PATENTSCHRIFT** A5

(21) Gesuchsnummer:

1541/86

(73) Inhaber:

Sartorius GmbH, Göttingen (DE)

(22) Anmeldungsdatum:

17.04.1986

30 Priorität(en):

20.04.1985 DE 3514430

(72) Erfinder:

Knothe, Erich, Eddigehausen (DE) Melcher, Franz-Josef, Hardegsen 3 (DE) Oldendorf, Christian, Göttingen (DE)

(24) Patent erteilt:

29.09.1989

(74) Vertreter:

A. Braun, Braun, Héritier, Eschmann AG, Patentanwälte, Basel

45 Patentschrift veröffentlicht:

29.09.1989

(54) Verfahren zum Abspeichern von Daten in einem elektrisch löschbaren Speicher und elektrisch löschbarer Speicher zur Durchführung des Verfahrens.

(57) Um die in dem mit einem Mikroprozessor verbundenen Speicher abgespeicherten Daten vor einem versehentlichen Überschreiben bei einer Fehlfunktion des Mikroprozessors sicher zu schützen, umfasst die Erfindung einen Überschreib-Schutz, der aus einem Schreibschutz-Flip-Flop (1) besteht, dessen beiden logischen Zustände "mit Schreibschutz" bzw. "ohne Schreibschutz" bedeuten, weiter ein Gate (3) in der Schreibleitung, das vom Schreibschutz-Flip-Flop (1) angesteuert wird und bei dessem logischen Zustand "mit Schreibschutz" die Weiterleitung von Schreibbefehlen zu den einzelnen Speicherzellen verhindert, und schliesslich ein mechanisches Schaltelement (5). Diese Bauelemente sind so geschaltet, dass das Schreibschutz-Flip-Flop (1) im Normalfall durch den Mikroprozessor nur in den einen logischen Zustand "mit Schreibschutz" gebracht werden kann. In den anderen logischen Zustand "ohne Schreibschutz" dagegen kann es nur gebracht werden, wenn das mechanische Schaltelement (5) betätigt ist. Der Überschreib-Schutz kann sich je nach Ausgestaltung auf den ganzen elektrisch löschbaren Speicher oder nur auf Teilbereiche erstrecken.

## **PATENTANSPRÜCHE**

- 1. Verfahren zum Abspeichern von Daten in einem elektrisch löschbaren Speicher, der mit einem Mikroprozessor verbunden ist, dadurch gekennzeichnet,

- dass während einer Initialisierungsphase beliebige Daten vom Mikroprozessor in den elektrisch löschbaren Speicher eingeschrieben werden können,

- dass der Mikroprozessor am Ende der Initialisierungsphase zumindest einen Teilbereich des elektrisch löschbaren Flops als geschützt definiert,

- dass das Schreibschutz-Flip-Flop in seinem logischen Zustand «mit Schreibschutz» die Schreibleitung zum zugehörigen Teilbereich des elektrisch löschbaren Speichers sperrt

- und dass das Schreibschutz-Flip-Flop vom Mikroprozessor nur in den logischen Zustand «mit Schreibschutz» gebracht werden kann, während es in den anderen logischen Zustand «ohne Schreibschutz» nur durch das Betätigen eines mechanischen Schaltelementes gebracht werden kann.

- 2. Verfahren zum Abspeichern von Daten in einem elektrisch löschbaren Speicher, der mit einem Mikroprozessor verbunden ist, dadurch gekennzeichnet,

- dass während einer Initialisierungsphase beliebige Daten vom Mikroprozessor in den elektrisch löschbaren Speicher eingeschrieben werden können,

- dass der Mikroprozessor am Ende der Initialisierungsphase zumindest einen Teilbereich des elektrisch löschbaren Speichers durch Setzen mindestens eines Schreibschutz-Flip-Flops als geschützt definiert,

- dass das Schreibschutz-Flip-Flop in seinem logischen Zustand «mit Schreibschutz» die Schreibleitung zum zugehörigen Teilbereich des elektrisch löschbaren Speichers sperrt, und

- dass das Schreibschutz-Flip-Flop nur dadurch in den logischen Zustand «ohne Schreibschutz» gebracht werden kann, wenn sowohl ein mechanisches Schaltelement betätigt wird als auch ein entsprechender Mikroprozessor-Befehl vorliegt.

- 3. Verfahren nach Anspruch 1 oder 2 dadurch gekennzeichnet,

- dass der elektrisch löschbare Speicher in mehrere Teilbereiche unterteilt ist und dass jedem Teilbereich ein Teilbereich-Schreibschutz-Flip-Flop zugeordnet ist.

- 4. Verfahren nach Anspruch 3, dadurch gekennzeichnet,

- dass den Teilbereich-Schreibschutz-Flip-Flops ein Haupt-Schreibschutz-Flip-Flop übergeordnet ist, das die einzelnen Teilbereich-Schreibschutz-Flip-Flops aktiviert.

- 5. Elektrisch löschbarer Speicher zur Durchführung des Verfahrens nach Anspruch 1 oder 2, dadurch gekennzeichnet.

- dass mindestens ein Schreibschutz-Flip-Flop (1, 1', 1") vorhanden ist, dessen beide logischen Zustände «mit Schreibschutz» bzw. «ohne Schreibschutz» bedeuten,

- dass mindestens ein Gate (3, 3', 3", 23', 23", 23"') in der 55 Schreibleitung des elektrisch löschbaren Speichers (4, 4', 4", 4") vorhanden ist, das vom Schreibschutz-Flip-Flop (1, 1', 1") angesteuert wird und bei dessen logischen Zustand «mit Schreibschutz» die Weiterleitung von Schreibfehlern zu den einzelnen Speicherzellen verhindert,

- dass ein mechanisches Schaltelement (5) vorhanden ist

- und dass das Schreibschutz-Flip-Flop (1, 1', 1") durch den Mikroprozessor nur in den einen logischen Zustand «mit Schreibschutz» gebracht werden kann, während es in den anderen logischen Zustand «ohne Schreibschutz» nur gebracht werden kann, wenn das mechanische Schaltelement (5) betätigt ist.

- 6. Elektrisch löschbarer Speicher nach Anspruch 5 zur

- Durchführung des Verfahrens nach Anspruch 3, dadurch gekennzeichnet,

- dass jedem Speicher-Teilbereich (4', 4", 4"') ein Schreibschutz-Flip-Flop (1', 1") zugeordnet ist.

- 7. Elektrisch löschbarer Speicher nach Anspruch 5 oder 6 zur Durchführung des Verfahrens nach Anspruch 4, dadurch gekennzeichnet,

- dass jedem Teilbereich (4', 4", 4"') je ein Teilbereich-Schreibschutz-Flip-Flop-(2', 2", 2"') zugeordnet ist und dass Speichers durch Setzen mindestens eines Schreibschutz-Flip- 10 diese Teilbereich-Schreibschutz-Flip-Flops (2', 2", 2"') von einem Haupt-Schreibschutz Flip-Flop (1) angesteuert

## **BESCHREIBUNG**

Die Erfindung bezieht sich einmal auf ein Verfahren zum Abspeichern von Daten in einem elektrisch löschbaren 20 Speicher, der mit einem Mikroprozessor verbunden ist. Weiter bezieht sich die Erfindung auf einen elektrisch löschbaren Speicher zur Durchführung dieses Verfahrens. Elektrisch löschbare Speicher dieser Art sind allgemein bekannt; übliche Kurzbezeichnungen sind:

EEPROM = electrical erasible programmable read only

EAROM = electrical alterable read only memory oder NVRAM = non volatible random access memory.

Im folgenden Text wird für diesen elektrisch löschbaren 30 Speicher immer die Abkürzung EEPROM benutzt.

In Speichern dieser Art besteht die Gefahr, dass der Mikroprozessor durch ungewolltes Überschreiben wichtige abgespeicherte Daten vernichtet. Zum Schutz davor sind verschiedene Schaltungen bekannt, die jedoch alle das einwand-35 freie Funktionieren des Mikroprozessors zur Voraussetzung haben. Wird dagegen der Mikroprozessor beispielsweise durch äussere elektrische Störungen vollkommen ausser Tritt gebracht, so bieten diese Schaltungen keinen absoluten

Aufgabe der Erfindung ist es daher, ein Verfahren und eine Schaltung anzugeben, die zwar das Einschreiben von Daten durch den Mikroprozessor während einer Initialisierungsphase erlauben, das spätere Löschen von abgespeicherten Daten jedoch zuverlässig und unter allen Umständen 45 verhindern.

Schutz vor Datenverlusten.

Dies wird bei dem Verfahren zum Abspeichern von Daten in einem elektrisch löschbaren Speicher, der mit einem Mikroprozessor verbunden ist, erfindungsgemäss nach den kennzeichnenden Merkmalen aus den Ansprüchen 1 oder 2 50 erreicht.

Der elektrisch löschbare Speicher zur Durchführung dieser beiden Verfahrensvarianten ist dadurch gekennzeichnet, dass mindestens ein Schreibschutz-Flip-Flop vorhanden ist, dessen beide logischen Zustände «mit Schreibschutz» bzw. «ohne Schreibschutz» bedeuten, dass mindestens ein Gate in der Schreibleitung des elektrisch löschbaren Speichers vorhanden ist, das vom Schreibschutz-Flip-Flop angesteuert wird und bei dessen logischen Zustand «mit Schreibschutz» die Weiterleitung von Schreibfehlern zu den 60 einzelnen Speicherzellen verhindert, dass ein mechanisches Schaltelement vorhanden ist und dass das Schreibschutz-Flip-Flop durch den Mikroprozessor nur in den einen logischen Zustand «mit Schreibschutz» gebracht werden kann, während es in den anderen logischen Zustand «ohne Schreib-65 schutz» nur gebracht werden kann, wenn das mechanische

Schaltelement betätigt ist. Bei diesem Verfahren wird der Mikroprozessor also nach Abschluss der Initialisierung und dem damit verbundenen

3 671 837

Einschreiben von Daten in den EEPROM-Speicher das zusätzliche Speicherelement in den logischen Zustand «mit Schreibschutz» bringen und damit die weitere Abspeicherung von Daten - und das damit verbundene Löschen der alten Daten - verhindern. Eine Aufhebung dieses Schreibschutzes ist nur durch das manuelle Betätigen des Schaltelementes möglich, beispielsweise im Rahmen einer Revision oder Reparatur des Gerätes.

Der Schreibschutz kann sich auf den ganzen EEPROM-Speicher beziehen, der damit praktisch zu einem ROM-Speicher wird, er kann sich aber auch auf einen oder mehrere Teilbereiche beschränken, während die anderen Teilbereiche dem Mikroprozessor als normale EEPROM-Speicher bleiben. Dabei kann entweder jedem zu schützenden Teilbereich ein gesondertes Schreibschutz-Flip-Flop zugeordnet sein, oder es wird ein Haupt-Schreibschutz-Flip-Flop benutzt, das nachgeordnete Teilbereich-Schreibschutz-Flip-Flops ansteuert, die dann die einzelnen Teilbereiche vor dem Überschreiben schützen.

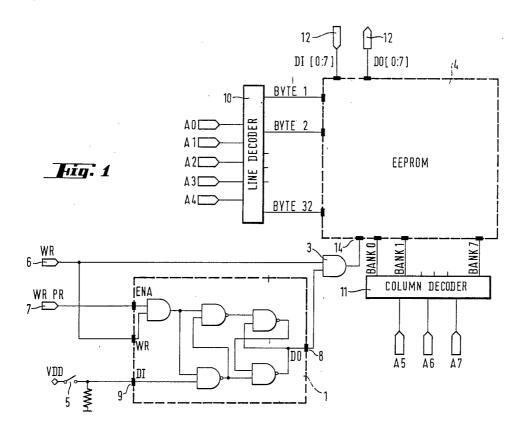

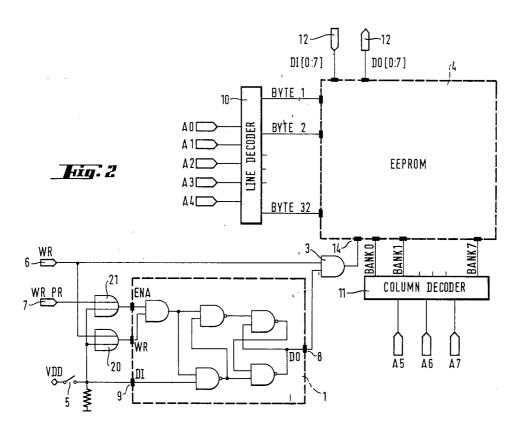

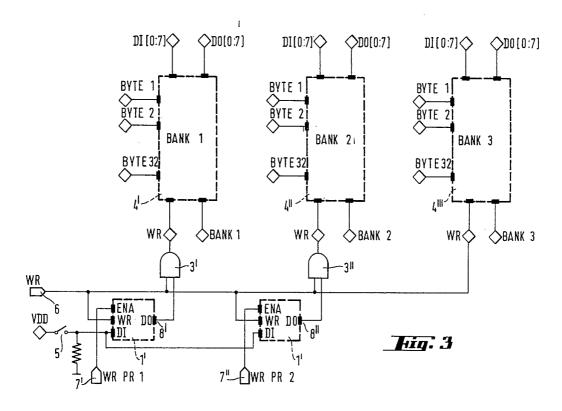

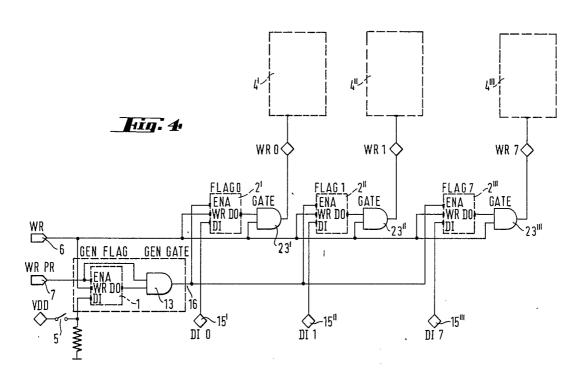

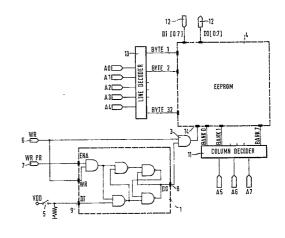

Die Erfindung wird im folgenden anhand der Schaltschemata erläutert. Dabei zeigt:

Fig. 1 ein Blockschaltbild eines ganz geschützten EEPROM Speichers,

Fig. 2 ein Blockschaltbild eines ganz geschützten EEPROM Speichers in einer anderen Ausgestaltung, Fig. 3 ein Blockschaltbild eines teilweise geschützten EEPROM-Speichers in einer ersten Ausgestaltung und Fig. 4 ein Blockschaltbild eines teilweise geschützten EEPROM-Speichers in einer zweiten Ausgestaltung.

Das Blockschaltbild in Fig. 1 zeigt einen EEPROM-Speicher 4 mit seinen üblichen Ansteuerelementen 10 für die Auswahl der Zeile und 11 für die Auswahl der Spalte, seinen Datenein- und Ausgängen 12 und dem Schreibeingang 14. Solche EEPROM-Speicher sind allgemein bekannt, weshalb auf eine nähere Erläuterung ihres inneren Aufbaues hier verzichtet werden kann.

In der Schreibleitung ist nun zwischen der Zuleitung 6 vom Mikroprozessor und dem Eingang 14 in den Speicher 4 ein Gate 3 eingebaut. Der zweite Eingang des Gates 3 liegt am Ausgang 8 eines Schreibschutz-Flip-Flops 1. Damit bestimmt das Schreibschutz-Flip-Flop 1, ob Schreibbefehle zum Speicher 4 durchgelassen werden oder nicht. Liegt am Ausgang 8 des Schreibschutz-Flip-Flops 1 eine logische «1», so werden Schreibbefehle durchgelassen, dies ist der logische Zustand «ohne Schreibschutz». In diesem Zustand befindet sich das Schreibschutz-Flip-Flop 1 bei der ersten Initialisierung. Am Dateneingang 9 des Schreibschutz-Flip-Flops 1 ist jedoch bereits die logische «0» fest verdrahtet und kann vom 50 getrennte Entriegelung durch zwei mechanische Schaltele-Mikroprozessor durch ein Signal auf der Schreibleitung 6 und der Schreibschutzaktivierungsleitung 7 in das Schreibschutz-Flip-Flop 1 übernommen werden. Damit wird das Gate 3 gesperrt und es sind keine Schreiboperationen mehr im Speicher 4 möglich; dies ist also der logische Zustand «mit 55 Schreibschutz-Flip-Flop 1 vorhanden, die Ansteuerung der Schreibschutz». Aus diesem Zustand kann das Schreibschutz-Flip-Flop 1 – das als nichtflüchtiges Speicherelement vorausgesetzt wird - vom Mikroprozessor nicht herausgebracht werden, da der Mikroprozessor auf den Dateneingang niker, kann der Mikroprozessor durch Signale auf den beiden Leitungen 6 und 7 den Urzustand «ohne Schreibschutz» wieder herstellen. Das mechanische Schaltelement 5 kann dabei je nach Erfordernis des speziellen Anwendungsfalles z. B. als mechanischer Taster ausgeführt sein oder als 2polige Buchse, die durch einen Kurzschlussstecker überbrückt werden kann, oder als Lötaugen oder Lötstifte, die

durch ein metallisches Werkzeug elektrisch verbunden werden können.

Die in Fig. 1 dargestellte Schaltung erlaubt es also, dem Mikroprozessor in einer Initialisierungsphase den Speicher 4 5 mit Daten zu beschreiben und nach Abschluss der Initialisierungsphase diese Daten vor versehentlicher späterer Änderung zu schützen. Dieser Schutz ist für den Mikroprozessor irreversibel und kann nur durch mechanische Eingriffe von aussen bei Bedarf aufgehoben werden.

Die in Fig. 2 gezeigte Ausgestaltung unterscheidet sich von der in Fig. 1 gezeigten nur durch die Beschaltung der Eingänge des Schreibschutz-Flip-Flops 1. Beim Betätigen des mechanischen Schaltelementes 5 wird nicht nur die logische «1» auf den Dateneingang 9 gegeben, sondern gleichzeitig 15 über zwei Oder-Gates 20 und 21 der Schreibbefehl (WR) und der Freigabebefehl (ENA) an das Schreibschutz-Flip-Flop 1 gegeben, so dass das Schreibschutz-Flip-Flop 1 ohne Mitwirkung des Mikroprozessors nur durch das Betätigen des mechanischen Schaltelementes 5 in den logischen Zustand 20 «ohne Schreibschutz» gebracht wird.

In Fig. 1 und 2 wurde jeweils der gesamte Speicher 4 mit oder ohne Schreibschutz benutzt. In Fig. 3 ist gezeigt, wie Teilbereiche mit einem Schreibschutz versehen werden können. Der Teilbereich 4" des Speichers ist von vornherein 25 als normaler, ungeschützter EEPROM-Speicher vorgesehen. Der Bereich 4' ist durch ein Schreibschutz-Flip-Flop 1' in Verbindung mit dem Gate 3' schützbar, der Bereich 4" ist durch ein zweites Schreibschutz-Flip-Flop 1" in Verbindung mit dem Gate 3" schützbar. Beide Schreibschutz-Flip-Flops 30 1' und 1" sind wie das Schreibschutz-Flip-Flop 1 in Fig. 1 aufgebaut und daher hier nur schematisch wiedergegeben. Die beiden Schreibschutzaktivierungsleitungen 7' und 7" sind getrennt zum Mikroprozessor herausgeführt, um eine getrennte, vom Programm des Mikroprozessors gesteuerte 35 Auslösung des Schreibschutzes zu ermöglichen. Dadurch können beispielsweise Gerätevarianten, die verschieden viele zu schützende Grunddaten und allgemeine, nicht zu schützende EEPROM-Daten benötigen, mit der gleichen Hardware realisiert werden; in der einen Gerätevariante 40 wird dann am Ende der Initiatisierung für beide Schreibschutz-Flip-Flops 1' und 1" der Befehl für den Schreibschutz softwaremässig vorgesehen, während in der anderen Gerätevariante nur für das eine Schreibschutz-Flip-Flop 1' der

Befehl für den Schreibschutz softwaremässig gegeben wird, 45 so dass der Speicherbereich 4" als normaler, überschreibbarer EEPROM-Speicher bleibt. Die Entriegelung des Schreibschutzes mittels des mechanischen Schaltelementes 5 erfolgt in Fig. 3 für beide Schreibschutz-Flip-Flops 1' und 1" zusammen. Selbstverständlich ist bei Bedarf auch eine mente 5 möglich.

Eine andere Ausgestaltung des Schreibschutzes für Speicher-Teilbereiche ist in Fig. 4 gezeigt. Hier ist für alle Speicherteilbereiche 4', 4", 4" ein gemeinsames Haupt-Gates 23', 23", 23"' zum Sperren der Schreibimpulse erfolgt jedoch unter Zwischenschaltung von Teilbereich-Schreibschutz-Flip-Flops 2', 2", 2". Bei der ersten Initialisierung befinden sich das Haupt-Schreibschutz-Flip-Flop 1 und die 9 keinen Zugriff hat. Nur nach Schliessen des mechanischen 60 Teilbereich-Schreibschutz-Flip-Flops 2', 2", 2"' im logischen Schaltelementes 5, beispielsweise durch einen Service-Tech-Zustand «1», so dass die Gates 23', 23", 23"' Schreibimpulse durchlassen. Nach Abschluss der Initialisierung kann dann der Mikroprozessor beim Aktivieren des Schreibschutzes gleichzeitig festlegen, welche Teilbereiche schreibgeschützt 65 werden sollen. Soll z. B. nur der zweite Teilbereich 4" schreibgeschützt werden, so gibt der Mikroprozessor auf dessen Dateneingang 15" eine logische «0» und auf die Dateneingänge 15', 15" der anderen Teilbereiche 4', 4"

671 837

4

eine logische «1». Dadurch wird beim Eintreffen des Schreibsignals auf dem Anschluss 6 und des Schreibschutzaktivierungssignals auf dem Anschluss 7 von den Teilbereich-Schreibschutz-Flip-Flops 2', 2", 2"' nur das eine Teilbereich-Schreibschutz-Flip-Flop 2" in den logischen Zustand s schützte und nichtschreibgeschützte Bereiche zu ändern. «0» gebracht, während die anderen Teilbereich-Schreibschutz-Flip-Flops 2', 2" im logischen Zustand «1» bleiben; gleichzeitig übernimmt natürlich das Haupt-Schreibschutz-Flip-Flop 1 die an seinem Eingang fest verdrahtete logische «0» und sperrt damit das Gate 13, so dass an dessen Ausgang 10

16 keine Freigabesignale für die Teilbereich-Schreibschutz-Flip-Flops 2', 2", 2" mehr erscheinen können. Dadurch ist der Mikroprozessor nicht mehr in der Lage, die am Ende der Initialisierungsphase festgelegte Unterteilung in schreibge-Auch die generelle Aufhebung des Schreibschutzes (durch Einspeichern der logischen «1» in das Haupt-Schreibschutz-Flip-Flop 1) ist, wie in den anderen Ausgestaltungen, nur nach Betätigen des mechanischen Schaltelementes 5 möglich.