(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5033376号

(P5033376)

(45) 発行日 平成24年9月26日(2012.9.26)

(24) 登録日 平成24年7月6日(2012.7.6)

(51) Int.Cl.

F 1

|             |              |                  |      |      |      |

|-------------|--------------|------------------|------|------|------|

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/36 |      |

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20 | 621F |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G09G | 3/20 | 631R |

|             |              |                  | G09G | 3/20 | 641P |

|             |              |                  | G09G | 3/20 | 612U |

請求項の数 8 (全 10 頁) 最終頁に続く

(21) 出願番号 特願2006-221948 (P2006-221948)

(22) 出願日 平成18年8月16日 (2006.8.16)

(65) 公開番号 特開2007-219474 (P2007-219474A)

(43) 公開日 平成19年8月30日 (2007.8.30)

審査請求日 平成21年7月13日 (2009.7.13)

(31) 優先権主張番号 10-2006-0015822

(32) 優先日 平成18年2月17日 (2006.2.17)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 129

129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic

of Korea

(74) 代理人 100072349

弁理士 八田 幹雄

(74) 代理人 100110995

弁理士 奈良 泰男

(74) 代理人 100114649

弁理士 宇谷 勝幸

最終頁に続く

(54) 【発明の名称】データ処理装置およびこの駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

液晶表示装置において、映像を表示する表示部を駆動するためのフレームデータを補正して、当該フレームデータよりも高い電圧のデータを出力すると共に、当該表示部の液晶をプレチルトするためのデータを出力するデータ処理装置であって、

第1フレームデータに基づいて補正された、当該第1フレームに関する補正データである第1補正データを出力するメモリと、

前記第1補正データと第2フレームデータとに基づいて、当該第2フレームに関する補正データである第2補正データを生成し、当該第2補正データを前記メモリに記憶する第1補正部と、

前記第2フレームデータと前記第1補正データとに基づいて、前記第1フレームに関する補正データである第3補正データを生成する第2補正部と、

を含み、

前記第2補正部は、

前記第1補正データがあらかじめ設定された第2基準値より小さく、前記第2フレームデータがあらかじめ設定された第3基準値より大きい場合、前記第1補正データにあらかじめ設定された補正值を加えた前記第3補正データを生成し、

前記第1補正データが前記第2基準値以上、または、前記第2フレームデータが前記第3基準値以下の場合、前記第1補正データと同一の前記第3補正データを生成することを特徴とするデータ処理装置。

## 【請求項 2】

前記第1補正部は、前記第1補正データが前記第2フレームデータより小さい場合、前記第2フレームデータより大きい値を有する前記第2補正データを生成することを特徴とする請求項1に記載のデータ処理装置。

## 【請求項 3】

前記第1補正部は、前記第1補正データと前記第2フレームデータとの差の値があらかじめ設定された第1基準値の以下の場合、前記第2補正データは前記第2フレームデータと同一の値を有する一方、前記第1基準値より大きい場合、前記第2フレームデータよりあらかじめ設定された第1補正值だけ増加した前記第2補正データを生成することを特徴とする請求項2に記載のデータ処理装置。

10

## 【請求項 4】

前記第1フレームデータ及び第2フレームデータは、連続した第1フレーム及び第2フレームに対応する映像データであることを特徴とする請求項1～3のいずれか一項に記載のデータ処理装置。

## 【請求項 5】

前記メモリは、1フレームに対応する記憶領域を有するフレームメモリであることを特徴とする請求項1～4のいずれか一項に記載のデータ処理装置。

## 【請求項 6】

液晶表示装置において、映像を表示する表示部を駆動するためのフレームデータを補正して、当該フレームデータよりも高い電圧のデータを出力すると共に、当該表示部の液晶をプレチルトするためのデータを出力するデータ処理装置の駆動方法であって、

20

第1フレームデータに基づいて補正された、当該第1フレームの補正データである第1補正データを読み出して、第2フレームデータを受信する段階と、

前記第2フレームデータと前記第1補正データに基づいた、当該第2フレームの補正データである第2補正データを生成する段階と、

生成された前記第2補正データを記憶する段階と、

前記第2フレームデータと前記第1補正データとに基づいて、前記第1フレームの補正データである第3補正データを生成する段階と、

を含み、

前記第3補正データを生成する段階は、

30

前記第1補正データとあらかじめ設定された第2基準値とを比較し、前記第2フレームデータとあらかじめ設定された第3基準値とを比較する段階と、

前記第1補正データが前記基準値より小さく、前記第2フレームデータが前記第3基準値より大きい場合、前記第1補正データにあらかじめ設定された補正值を加えて前記第3補正データを生成し、前記第1補正データが前記第2基準値の以上、または、前記第2フレームデータが前記第3基準値の以下の場合、前記第1補正データと同一の前記第3補正データを生成する段階と、を含むことを特徴とするデータ処理装置の駆動方法。

## 【請求項 7】

前記第2補正データを生成する段階は、

第1補正データと前記第2フレームデータとの差の値と、あらかじめ設定された第1基準値とを比較する段階と、

40

前記第1補正データと前記第2フレームデータとの差の値が前記第1基準値の以下の場合、前記第2フレームデータと同一の値を有する前記第2補正データを生成し、前記第1補正データと前記第2フレームデータとの差の値が前記第1基準値より大きい場合、前記第2フレームデータよりあらかじめ設定された第1補正值だけ増加した前記第2補正データを生成することを特徴とする請求項6に記載のデータ処理装置の駆動方法。

## 【請求項 8】

前記第1フレームデータ及び第2フレームデータは、連続した第1フレーム及び第2フレームに対応する映像データであることを特徴とする請求項6または7に記載のデータ処理装置の駆動方法。

50

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、液晶の応答速度を改善することができるデータ処理装置およびこの駆動方法に関する。

**【背景技術】****【0002】**

一般的に液晶表示装置は、2つの表示基板とその間に介在された液晶層からなる。液晶表示装置は、液晶層に電界を印加し、電界の強さを調節して液晶層を通過する光の透過率を調節することによって、所望の映像を表示する表示装置である。

10

**【0003】**

このような液晶表示装置は、コンピュータの表示装置だけでなく、近年では、テレビの表示画面に広く用いられている。したがって、静止画のみならず、動画も表示することができる液晶表示装置の必要性が高まっている。しかしながら、従来の液晶表示装置は、液晶の応答速度が遅く、動画を実現しにくいという問題があった。

**【0004】**

具体的には、液晶分子の応答速度が遅く、液晶キャパシタに充電される電圧が目標電圧（すなわち、所望の輝度を得ることができる電圧）に到達するまで一定の時間（遅延時間）が必要となる。このような遅延時間は、液晶キャパシタにあらかじめ充電されている電圧との電位差によって変わる。

20

**【0005】**

特に、目標電圧とあらかじめ充電されている電圧との差が大きい場合、はじめから目標電圧のみを印加すれば、スイッチング素子がターンオンされる1フレーム時間の間、目標電圧に到達できないおそれがある。

**【発明の開示】****【発明が解決しようとする課題】****【0006】**

本発明の目的は、液晶の応答速度を改善して、メモリの個数を減少させることができるデータ処理装置を提供することにある。

**【0007】**

30

また、本発明の他の目的は、上記したデータ処理装置の駆動方法を提供することにある。

**【課題を解決するための手段】****【0009】**

本発明に係るデータ処理装置は、液晶表示装置において、映像を表示する表示部を駆動するためのフレームデータを補正して、当該フレームデータよりも高い電圧のデータを出力すると共に、当該表示部の液晶をプレチルトするためのデータを出力するデータ処理装置であって、メモリ、第1補正部及び第2補正部を含む。前記メモリは第1フレームデータに基づいて補正された、当該第1フレームに関する補正データである第1補正データを出力する。前記第1補正部は前記第1補正データと前記第2フレームデータに基づいて、当該第2フレームに関する補正データである第2補正データを生成し、前記メモリから前記第1補正データが出力された以後に前記第2補正データを前記メモリに記憶する。前記第2補正部は前記第2フレームデータと前記第1補正データに基づいて、前記第1フレームに関する補正データである第3補正データを生成する。前記第2補正部は、前記第1補正データがあらかじめ設定された第2基準値より小さく、前記第2フレームデータがあらかじめ設定された第3基準値より大きい場合、前記第1補正データにあらかじめ設定された補正値を加えた前記第3補正データを生成し、前記第1補正データが前記第2基準値以上、または、前記第2フレームデータが前記第3基準値以下の場合、前記第1補正データと同一の前記第3補正データを生成することを特徴とする。

40

**【0010】**

50

本発明に係るデータ処理装置の駆動方法は液晶表示装置において、映像を表示する表示部を駆動するためのフレームデータを補正して、当該フレームデータよりも高い電圧のデータを出力すると共に、当該表示部の液晶をプレチルトするためのデータを出力するデータ処理装置の駆動方法であって、データ処理装置は第1フレームデータに基づいて補正された、当該第1フレームの補正データである第1補正データを読み出し、第2フレームデータを受信する。以後、前記第2フレームデータと前記第1補正データに基づいた、当該第2フレームの補正データである第2補正データを生成し、生成された前記第2補正データを記憶する。次に、前記第2フレームデータと前記第1補正データに基づいて、前記第1フレームの補正データである第3補正データを生成する。前記第3補正データを生成する段階は、前記第1補正データとあらかじめ設定された第2基準値とを比較し、前記第2フレームデータとあらかじめ設定された第3基準値とを比較する段階と、前記第1補正データが前記基準値より小さく、前記第2フレームデータが前記第3基準値より大きい場合、前記第1補正データにあらかじめ設定された補正值を加えて前記第3補正データを生成し、前記第1補正データが前記第2基準値の以上、または、前記第2フレームデータが前記第3基準値の以下の場合、前記第1補正データと同一の前記第3補正データを生成する段階を含む。10

【発明の効果】

【0012】

以上のように構成された本発明に係るデータ処理装置およびこの駆動方法によれば、第1フレームデータから補正された第1補正データと第2フレームデータに基づいて第2補正データを生成し、生成された第2補正データをメモリにフィードバックさせて記憶することによって、メモリの全体的な個数を減少させることができる。20

【0013】

また、前記第1補正データと第2フレームデータに基づいて第3補正データを生成し、前記第3補正データを利用して第1フレームで液晶をプレチルトさせることによって、液晶の応答速度を改善することができる。

【発明を実施するための最良の形態】

【0014】

以下、添付した図面を参照して、本発明の望ましい実施形態をより詳細に説明する。

【0015】

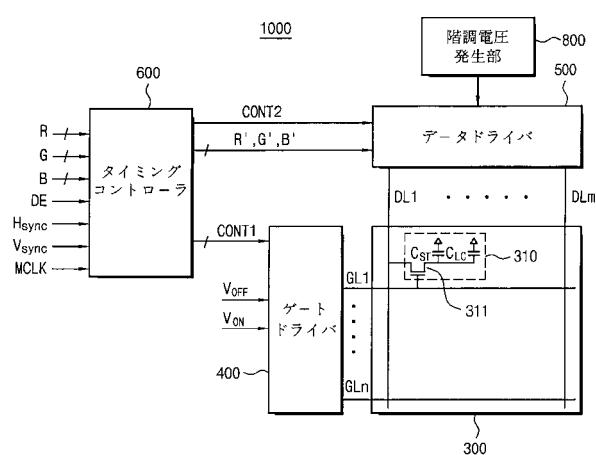

図1は、本発明の一実施形態に係る液晶表示装置の概略構成を示すブロック図である。30

【0016】

図1を参照すれば、液晶表示装置1000は映像を表示する表示部300、表示部300を駆動させるゲートドライバ400、データドライバ500、データドライバ500に連結された階調電圧発生部800、及びゲートドライバ400とデータドライバ500とを制御するタイミングコントローラ600を備えている。

【0017】

表示部300にはゲート電圧が入力される多数のゲートライン $GL_1 \sim GL_n$ とデータ電圧が入力される多数のデータライン $DL_1 \sim DL_m$ が具備される。多数のゲートライン $GL_1 \sim GL_n$ と多数のデータライン $DL_1 \sim DL_m$ によって、表示部300にはマトリックス形態で多数の画素領域が定義され、各画素領域には画素310が具備される。画素310は、薄膜トランジスタ311、液晶キャパシタ $C_{LC}$ 、及びストレージキャパシタ $C_{ST}$ を有する。40

【0018】

図に示したように、薄膜トランジスタ311のゲート電極は第1ゲートライン $GL_1$ に連結され、ソース電極は第1データライン $DL_1$ に連結され、液晶キャパシタ $C_{LC}$ とストレージキャパシタ $C_{ST}$ は薄膜トランジスタ311のドRAIN電極に並列に連結される。

【0019】

本実施形態において、表示部300は、下部表示基板、前記下部表示基板と対向して配

10

20

30

40

50

置される上部表示基板、及び前記下部表示基板と前記上部表示基板との間に介在された液晶層を有する。

【0020】

前記下部表示基板には、複数のゲートライン  $GL_1 \sim GL_n$ 、複数のデータライン  $DL_1 \sim DL_m$ 、薄膜トランジスタ  $311$ 、及び液晶キャパシタ  $C_{LC}$  の第1電極である画素電極が形成される。したがって、薄膜トランジスタ  $311$  は前記ゲート電圧に応答して前記データ電圧を前記画素電極に印加する。

【0021】

一方、前記上部表示基板には、前記液晶キャパシタ  $C_{LC}$  の第2電極である共通電極が形成され、前記共通電極には共通電圧が印加される。前記画素電極と前記共通電極との間に介在された液晶層は誘電体の機能を有する。したがって、液晶キャパシタ  $C_{LC}$  には前記データ電圧と前記共通電圧の電位差に対応する電圧が充電される。

10

【0022】

ゲートドライバ  $400$  は、表示部  $300$  に具備された複数のゲートライン  $GL_1 \sim GL_n$  と電気的に連結され、多数のゲートライン  $GL_1 \sim GL_n$  に前記ゲート電圧を提供する。前記データドライバ  $500$  は前記表示部  $300$  に具備された多数のデータライン  $DL_1 \sim DL_m$  と電気的に連結され、前記階調電圧発生部  $800$  からの階調電圧を選択して前記多数のデータライン  $DL_1 \sim DL_m$  に前記データ電圧として提供する。

【0023】

タイミングコントローラ  $600$  に外部のグラフィック制御器（図示はしない）から第1映像信号  $R$ 、 $G$ 、 $B$  と、各種の制御信号、例えば垂直同期信号  $V_{sync}$ 、水平同期信号  $H_{sync}$ 、メインクロック  $MCLK$ 、データイネーブル信号  $DE$  などが入力される。タイミングコントローラ  $600$  は、前記第1映像信号  $R$ 、 $G$ 、 $B$  を処理して第2映像信号  $R'$ 、 $G'$ 、 $B'$  を出力し、前記各種の制御信号を基づいてゲート制御信号  $CONT1$  とデータ制御信号  $CONT2$  を出力する。

20

【0024】

ゲート制御信号  $CONT1$  は、ゲートドライバ  $400$  の動作を制御するための信号であって、ゲートドライバ  $400$  に送信される。ゲート制御信号  $CONT1$  は、ゲートドライバ  $400$  の動作を開始する垂直開始信号、前記ゲート電圧の出力時期を決めるゲートクロック信号、及びゲート電圧のオンパルス幅を決める出力イネーブル信号などを含む。

30

【0025】

ゲートドライバ  $400$  は、タイミングコントローラ  $600$  からのゲート制御信号  $CONT1$  に応答して、ゲートオン電圧  $V_{on}$  とゲートオフ電圧  $V_{off}$  の組み合わせからなる前記ゲート電圧を出力する。

【0026】

データ制御信号  $CONT2$  は、データドライバ  $500$  の動作を制御する信号であって、データドライバ  $500$  に送信される。データ制御信号  $CONT2$  は、データドライバ  $500$  の動作を開始する水平開始信号、前記データ電圧の極性を反転させる反転信号、及び前記データ駆動部から前記データ電圧が出力される時期を決める出力指示信号などを含む。

【0027】

データドライバ  $500$  にタイミングコントローラ  $600$  からのデータ制御信号  $CONT1$  に応答して一行の画素に対応する第2映像信号  $R'$ 、 $G'$ 、 $B'$  が入力される。階調電圧発生部  $800$  からの階調電圧のうち、前記第2映像信号  $R'$ 、 $G'$ 、 $B'$  に対応する階調電圧を選択して前記データ電圧に変換して出力する。

40

【0028】

タイミングコントローラ  $600$  は、液晶の応答速度を改善するためのデータ処理部をさらに含むことができる。前記データ処理部の詳細な説明は、後述する。

【0029】

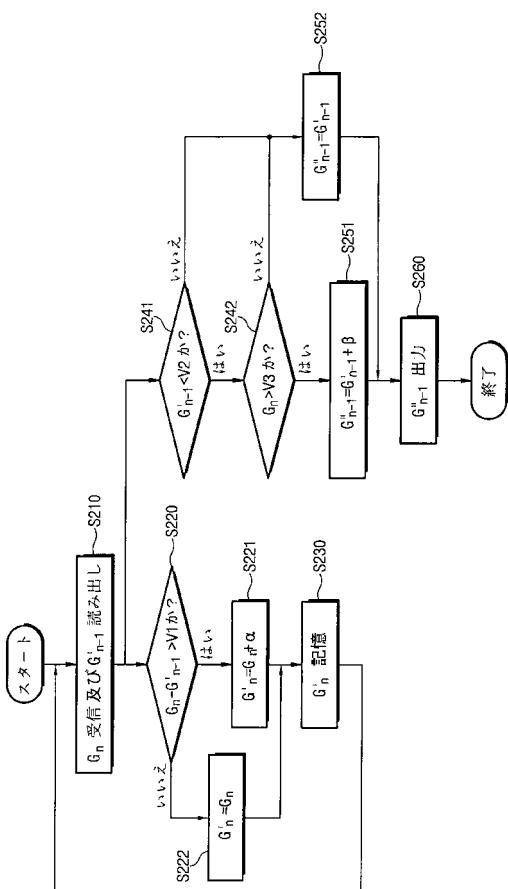

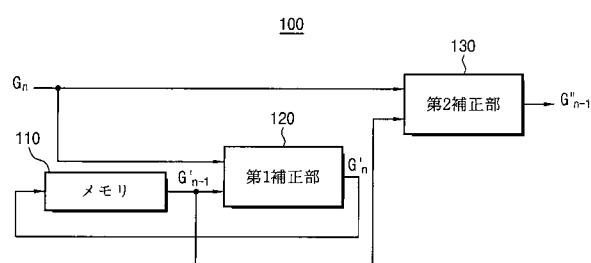

図2は、本発明の一実施形態に係るデータ処理部の概略構成を示すブロック図であり、図3は図2に示したデータ処理部の動作過程を示したフローチャートである。

50

## 【0030】

図2を参照すれば、データ処理部100は、メモリ110、第1補正部120、及び第2補正部130を含む。

## 【0031】

第1補正部120は、n番目の前のフレーム(n-1番目のフレーム)の映像信号(以下、第1映像信号)を補正した前記n-1番目のフレームの補正信号(以下、「第1補正信号」と称する)G'n-1をメモリ110から読み出す。ここで、第1補正信号G'n-1は、n-1番目の前のフレーム(n-2番目のフレーム)の補正信号と前記n-1番目のフレームの映像信号とに基づいて生成された信号である。

## 【0032】

10

また、第1補正部120には、現在のフレーム(n番目のフレーム)の映像信号(以下、「第2映像信号」と称する)Gnが入力される。第1補正部120は、第1補正信号G'n-1と第2映像信号Gnとに基づいてn番目のフレームの補正信号(以下、「第2補正信号」と称する)Gn'を出力し、第2補正信号Gn'はメモリ110にフィードバックされて記憶される。したがって、メモリ110には1フレーム単位の補正信号が続いて記憶される。

## 【0033】

第2補正部130は、第1補正信号G'n-1と第2映像信号Gnとに基づいて第3補正信号G'n-1を出力する。

## 【0034】

20

図3に示したように、データ処理部100(図2参照)は、外部からn番目のフレームの第2映像信号Gnを受信し、メモリ110(図2参照)に記憶されたn-1番目のフレームの第1補正信号G'n-1を読み出す(S210)。

## 【0035】

データ処理部100は、第1補正部120(図2参照)で第2映像信号Gnと前記第1補正信号G'n-1との差の値を、あらかじめ設定された第1基準値V1と比較する(S220)。比較の結果、第2映像信号Gnと第1補正信号G'n-1との差の値が第1基準値V1より大きい場合、第2映像信号Gnにあらかじめ設定された第1補正值を加えて第2補正信号Gn'を生成する(S221)。一方、比較の結果、第2映像信号Gnと前記第1補正信号G'n-1との差の値が第1基準値以下の場合、第2映像信号Gnと同一の第2補正信号Gn'を生成する(S222)。

30

## 【0036】

次に、生成された第2補正信号Gn'は、メモリ110に記憶される(S230)。第2補正信号Gn'は現在のフレームの次のフレーム(n+1番目のフレーム)で第1補正部120によって読み出される。

## 【0037】

一方、データ処理部100は第2補正部130(図2参照)で第1補正信号G'n-1とあらかじめ設定された第2基準値V2とを比較し(S241)、その結果に応じて、第2映像信号Gnとあらかじめ設定された第3基準値V3とを比較する(S242)。第1補正信号G'n-1が第2基準値V2より小さく、第2映像信号Gnが前記第3基準値V3より大きい場合、第1補正信号G'n-1より第2補正值だけ大きい第3補正信号G'n-1を生成する(S251)。一方、比較の結果、第1補正信号G'n-1が第2基準値V2の以上であるか、または第2映像信号Gnが第3基準値V3の以下であれば、第1補正信号G'n-1と同一の第3補正信号G'n-1を生成する(S252)。

40

## 【0038】

次に、生成された第3補正信号G'n-1は、データ処理部100から出力され、データ駆動部500(図1参照)に送信される(S260)。

## 【0039】

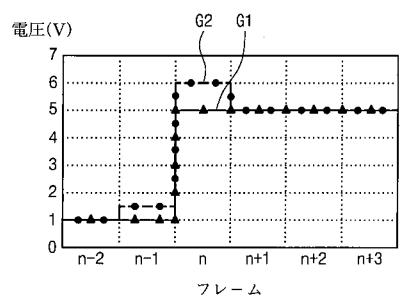

図4は、図2に示したデータ処理部の入力信号と補正信号とを示したグラフである。なお、図4において、x軸はフレームであり、y軸は電圧Vである。図4に示した第1グラ

50

FG 1 はデータ処理部 100 (図 2 参照) に入力される映像信号を示し、第 2 グラフ G 2 はデータ処理部 200 によって映像信号から補正された補正信号を示す。

【0040】

図 4 の第 1 グラフ G 1 に示したように、入力信号は、n - 2 番目及び n - 1 番目のフレームで 1 V に維持され、n 番目～n + 3 番目のフレームで 5 V に維持される。ここで、電圧 V は絶対値として表示される。

【0041】

第 2 グラフ G 2 に示したように、第 1 補正部 120 (図 2 参照) は、n - 1 番目のフレームの第 1 補正信号 (n - 1 番目のフレームの第 1 入力信号と同様であると仮定する場合、1 V を有する) と、n 番目のフレームの第 2 入力信号の 5 V との差に応じて n 番目のフレームの第 2 補正信号の 6 V を生成する。第 1 補正信号の 1 V と第 2 入力信号の 5 V との差の値である 4 V は、あらかじめ設定された第 1 基準値 (例えば、3.5 V) より大きい。したがって、第 1 補正部 120 は、第 2 入力信号の 5 V よりあらかじめ設定された第 1 補正值の 1 V だけ増加した 6 V の電圧を有する第 2 補正信号を生成する。

【0042】

また、第 2 補正部 130 (図 2 参照) は、n - 1 番目のフレームの第 1 補正信号 (n - 1 番目のフレームの第 1 入力信号と同様であると仮定する場合、1 V を有する) と n 番目のフレームの第 2 入力信号の 5 V とに基づいて n - 1 番目のフレームの第 3 補正信号 1.5 V を生成する。

【0043】

第 1 補正信号の 1 V は、あらかじめ設定された第 2 基準値 1.5 V より小さく、第 2 入力信号 5 V はあらかじめ設定された第 3 基準値 4.5 V より大きい。したがって、第 2 補正部 130 は、第 1 補正信号 1 V よりあらかじめ設定された第 2 補正值の 0.5 V だけ増加した第 3 補正信号の 1.5 V を出力する。

【0044】

このように、n - 1 番目のフレームにおいて、第 3 補正信号の 1.5 V を画素に印加して液晶をプレチルトさせ、次に、n 番目のフレームにおいて、目標電圧より高い第 2 補償信号の 6 V を印加することによって、液晶キャパシタ  $C_{Lc}$  の電圧が目標電圧に迅速に到達することができ、結果的に液晶の応答速度が向上する。

【0045】

また、データ処理部 100 は、フレームデータ毎の補正された値である補正信号を記憶するフレームメモリのみを要するので、タイミングコントローラ 600 (図 1 参照) の内部に具備されるメモリの個数を全体的に減少させることができる。

【0046】

以上、本発明は、図面に図示された実施形態を参考として説明されたが、これは例示的なものに過ぎず、当業者ならばこれより多様な変形及び均等な他の実施形態が可能であるという点を理解できる。したがって、本発明の技術的範囲は、特許請求の範囲によって決定されなければならない。

【産業上の利用可能性】

【0047】

本発明は、表示装置のデータ処理に関する技術分野に有用である。

【図面の簡単な説明】

【0048】

【図 1】本発明の一実施形態に係る液晶表示装置の概略構成を示すブロック図である。

【図 2】本発明の一実施形態に係るデータ処理部の概略構成を示すブロック図である。

【図 3】図 2 に示したデータ処理部の動作過程を示したフローチャートである。

【図 4】図 2 に示したデータ処理部の入力信号と補正信号とを示したグラフである。

【符号の説明】

【0049】

1 1 0 メモリ、

1 2 0 第1補正部、

1 3 0 第2補正部、

3 0 0 表示部、

4 0 0 ゲート駆動部、

5 0 0 データ駆動部、

6 0 0 タイミングコントローラ、

8 0 0 階調電圧発生部、

1 0 0 0 液晶表示装置。

【図1】

【図3】

【図2】

【図4】

---

フロントページの続き

(51)Int.Cl.

F I

G 0 9 G 3/20 6 3 1 B

G 0 2 F 1/133 5 7 0

G 0 2 F 1/133 5 7 5

(72)発明者 趙 賢 相

大韓民国忠清南道天安市仏党洞 ドンギルハイビル 206 - 1801

審査官 福村 拓

(56)参考文献 特開2004-310113 (JP, A)

特開2005-049840 (JP, A)

特開2002-099249 (JP, A)

特開2002-351409 (JP, A)

特開2005-141216 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 3 6

G 0 2 F 1 / 1 3 3

G 0 9 G 3 / 2 0