(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3894305号

(P3894305)

(45) 発行日 平成19年3月22日(2007.3.22)

(24) 登録日 平成18年12月22日(2006.12.22)

(51) Int.C1.

F 1

|             |               |                  |      |        |

|-------------|---------------|------------------|------|--------|

| <b>HO3F</b> | <b>3/217</b>  | <b>(2006.01)</b> | HO3F | 3/217  |

| <b>HO3F</b> | <b>3/30</b>   | <b>(2006.01)</b> | HO3F | 3/30   |

| <b>HO3K</b> | <b>17/16</b>  | <b>(2006.01)</b> | HO3K | 17/16  |

| <b>HO3K</b> | <b>17/695</b> | <b>(2006.01)</b> | HO3K | 17/687 |

F

B

請求項の数 15 (全 17 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2002-162437 (P2002-162437)  |

| (22) 出願日     | 平成14年6月4日 (2002.6.4)          |

| (65) 公開番号    | 特開2003-218647 (P2003-218647A) |

| (43) 公開日     | 平成15年7月31日 (2003.7.31)        |

| 審査請求日        | 平成17年4月18日 (2005.4.18)        |

| (31) 優先権主張番号 | 特願2001-352922 (P2001-352922)  |

| (32) 優先日     | 平成13年11月19日 (2001.11.19)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                           |

|-----------|-------------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都品川区北品川6丁目7番35号 |

| (74) 代理人  | 100091546<br>弁理士 佐藤 正美                    |

| (72) 発明者  | 増田 稔彦<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内   |

| (72) 発明者  | 大栗 一敦<br>東京都品川区北品川6丁目7番35号 ソ<br>ニー株式会社内   |

審査官 伏本 正典

最終頁に続く

(54) 【発明の名称】パワーアンプ

## (57) 【特許請求の範囲】

## 【請求項 1】

入力信号のレベルを示す第1のパルス変調信号(+PA)と、上記入力信号のレベルの補数を示す第2のパルス変調信号(+PB)をレベル反転して得られる第2の反転パルス変調信号(-PB)とを、第1のパルス信号として基準周期ごとに交互に出力するとともに、上記第2のパルス変調信号(+PB)と、上記第1のパルス変調信号をレベル反転して得られる第1の反転パルス変調信号(-PA)とを、第2のパルス信号として上記基準周期ごとに交互に出力するパルス変調手段と、

スイッチング素子を含み、上記パルス変調手段からの上記第1のパルス信号にしたがってスイッチング出力を供給する第1の出力回路と、

スイッチング素子を含み、上記パルス変調手段からの上記第2のパルス信号にしたがってスイッチング出力を供給する第2の出力回路とを備え、

上記パルス変調手段は、

上記入力信号を、上記基準周期ごとにそのレベルを示す第1のパルス変調信号に変換して出力する第1のパルス変調回路と、

上記入力信号を、上記基準周期ごとにそのレベルの補数を示す第2のパルス変調信号に変換して出力する第2のパルス変調回路と、

上記第1のパルス変調回路からの出力を、レベル反転して第1の反転パルス変調信号を出力する第1の反転回路と、

10

20

上記第2のパルス変調回路からの出力を、レベル反転して第2の反転パルス変調信号を出力する第2の反転回路と、

上記第1のパルス変調信号と、上記第2の反転パルス変調信号とを、上記基準周期ごとに交互に選択して上記第1のパルス信号を出力する第1の選択回路と、

上記第2のパルス変調信号と、上記第1の反転パルス変調信号とを、上記基準周期ごとに交互に選択して上記第2のパルス信号を出力する第2の選択回路と

を備え、

上記第1の出力回路の出力端と、上記第2の出力回路の出力端との間に、負荷が接続される

ことを特徴とするパワーアンプ。

10

#### 【請求項2】

請求項1に記載のパワーアンプにおいて、

上記パルス変調手段は、

上記入力信号のレベルに対応付けて、少なくともそのレベルを示す第1のパルス波形データを格納されるメモリと、

上記メモリからの読み出しを制御する制御回路と

を備え、

上記制御回路は、上記メモリからの読み出しを上記基準周期ごとに変更して、上記第1および第2のパルス信号を出力させる

ことを特徴とするパワーアンプ。

20

#### 【請求項3】

請求項2に記載のパワーアンプにおいて、

上記メモリは、上記入力信号のレベルを示す第1のパルス波形データと、上記入力信号のレベルの補数を示す第2のパルス波形データとを格納し、

上記制御回路は、上記基準周期ごとに、上記第1のパルス波形データと、上記第2のパルス波形データをレベル反転した第2の反転パルス波形データとを交互に読み出すとともに、上記基準周期ごとに、上記第2のパルス波形データと、上記第1のパルス波形データをレベル反転した第1の反転パルス波形データとを交互に読み出すよう上記メモリの読み出しを制御する

ことを特徴とするパワーアンプ。

30

#### 【請求項4】

請求項2に記載のパワーアンプにおいて、

上記制御回路は、上記基準周期ごとに、上記第1のパルス波形データと、上記第1のパルス波形データを逆の順序で読み出した逆順パルス波形データとを交互に読み出すとともに、上記基準周期ごとに、上記逆順パルス波形データをレベル反転した第2の反転パルス波形データと、上記第1のパルス波形データをレベル反転した第1の反転パルス波形データとを交互に読み出すよう上記メモリの読み出しを制御する

ことを特徴とするパワーアンプ。

#### 【請求項5】

請求項1に記載のパワーアンプにおいて、

40

上記パルス変調手段は、

上記入力信号を、上記基準周期ごとにそのレベルを示す第1のパルス変調信号に変換して出力する第1のパルス変調回路と、

上記入力信号を、上記基準周期ごとにそのレベルの補数を示す第2のパルス変調信号に変換して出力する第2のパルス変調回路と、

上記第1のパルス変調信号の時間軸の前後を反転して第2の時間反転パルス変調信号を出力する第1の反転回路と、

上記第2のパルス変調信号の時間軸の前後を反転して第1の時間反転パルス変調信号を出力する第2の反転回路と、

上記第1のパルス変調信号と、上記第2の時間反転パルス変調信号とを、上記基準周

50

期ごとに交互に選択して上記第1のパルス信号を出力する第1の選択回路と、

上記第2のパルス変調信号と、上記第1の時間反転パルス変調信号とを、上記基準周

期ごとに交互に選択して上記第2のパルス信号を出力する第2の選択回路とを備える

ことを特徴とするパワーアンプ。

【請求項6】

請求項1に記載のパワーアンプにおいて、

上記第1および第2の出力回路は、1対のスイッチング素子がプッシュプル接続されて

構成され、

上記第1の出力回路の上記1対のスイッチング素子には、上記第1のパルス信号と、こ

の第1のパルス信号をレベル反転した第1の反転パルス信号とが、それぞれ供給され、

上記第2の出力回路の上記1対のスイッチング素子には、上記第2のパルス信号と、こ

の第2のパルス信号をレベル反転した第2の反転パルス信号とが、それぞれ供給される

ことを特徴とするパワーアンプ。

【請求項7】

請求項1に記載のパワーアンプにおいて、

上記パルス変調信号がPWM信号である

ことを特徴とするパワーアンプ。

【請求項8】

入力信号のレベルを示す第1のパルス変調信号(+PA)と、上記入力信号のレベルの

補数を示す第2のパルス変調信号(+PB)をレベル反転して得られる第2の反転パルス

変調信号(-PB)とを、出力パルス信号として基準周期ごとに交互に出力するパルス変

調手段と、

スイッチング素子を含み、上記パルス変調手段からの上記出力パルス信号にしたがって

スイッチング出力を供給する出力回路と

を備え、

上記出力回路の出力端に負荷が接続される

ことを特徴とするパワーアンプ。

【請求項9】

請求項8に記載のパワーアンプにおいて、

上記パルス変調手段は、

上記入力信号を、上記基準周期ごとにそのレベルを示す第1のパルス変調信号に変換

して出力する第1のパルス変調回路と、

上記入力信号を、上記基準周期ごとにそのレベルの補数を示す第2のパルス変調信号

に変換し、レベル反転して第2の反転パルス変調信号を出力する第2のパルス変調回路と

、

上記第1のパルス変調信号と、上記第2の反転パルス変調信号とを、上記基準周期ご

とに交互に選択して上記出力パルス信号を出力する選択回路とを備える

ことを特徴とするパワーアンプ。

【請求項10】

請求項8に記載のパワーアンプにおいて、

上記パルス変調手段は、

上記入力信号のレベルに対応付けて、少なくともそのレベルを示す第1のパルス波形

データを格納されるメモリと、

上記メモリからの読み出しを制御する制御回路とを備え、

上記制御回路は、上記メモリからの読み出しを、上記基準周期ごとに変更して、上記

出力パルス信号を出力する

ことを特徴とするパワーアンプ。

【請求項11】

請求項10に記載のパワーアンプにおいて、

上記メモリは、上記入力信号のレベルを示す第1のパルス波形データと、上記入力信号

10

20

30

40

50

のレベルの補数を示す第2のパルス波形データとを格納し、

上記制御回路は、上記基準周期ごとに、上記第1のパルス波形データと、上記第2のパルス波形データをレベル反転した第2の反転パルス波形データとを交互に読み出すよう上記メモリの読み出しを制御する

ことを特徴とするパワーアンプ。

#### 【請求項12】

請求項10に記載のパワーアンプにおいて、

上記制御回路は、上記基準周期ごとに、上記第1のパルス波形データと、上記第1のパルス波形データを逆の順序で読み出した逆順パルス波形データとを交互に読み出すように上記メモリの読み出しを制御する

10

ことを特徴とするパワーアンプ。

#### 【請求項13】

請求項8に記載のパワーアンプにおいて、

上記パルス変調手段は、

上記入力信号を、上記基準周期ごとにそのレベルを示す上記第1のパルス変調信号に変換して出力するパルス変調回路と、

上記第1のパルス変調信号の時間軸の前後を反転して時間反転パルス変調信号を出力する時間反転回路と、

上記第1のパルス変調信号と、上記時間反転パルス変調信号とを、上記基準周期ごとに交互に選択して上記出力パルス信号を出力する選択回路とを備える

20

ことを特徴とするパワーアンプ。

#### 【請求項14】

請求項8に記載のパワーアンプにおいて、

上記出力回路は、1対のスイッチング素子がプッシュプル接続されて構成され、

上記出力回路の上記1対のスイッチング素子には、上記出力パルス信号と、このパルス信号をレベル反転した反転パルス信号とが、それぞれ供給される

ことを特徴とするパワーアンプ。

#### 【請求項15】

請求項8に記載のパワーアンプにおいて、

上記パルス変調信号がPWM信号である

30

ことを特徴とするパワーアンプ。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は、パワーアンプに関する。

##### 【0002】

##### 【従来の技術】

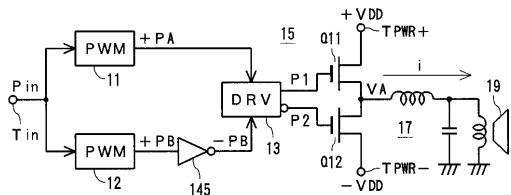

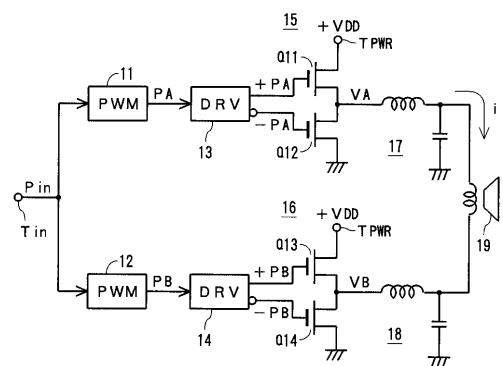

オーディオ用のパワーアンプとして、いわゆるD級アンプがある。このD級アンプは、スイッチングにより電力増幅を行うものであるが、例えば図10に示すように構成される。

##### 【0003】

すなわち、デジタルオーディオ信号Pinが、入力端子Tinを通じてPWM変調回路11、12に供給され、その入力信号Pinは1対のPWM信号PA、PBに変換される。

40

##### 【0004】

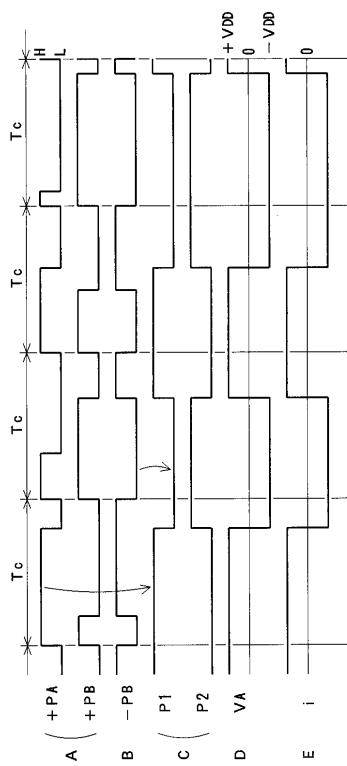

この場合、PWM信号PA、PBのパルス幅は、入力信号Pinの示すレベル（信号Pinとなったアナログ信号のサンプルごとのレベル。以下同様）に対応して変化するものであるが、図12に示すように、一方のPWM信号PAのパルス幅は、入力信号Pinの示すレベルに対応した大きさとされ、他方のPWM信号PBのパルス幅は、入力信号Pinの示すレベルの2の補数に対応した大きさとされる。また、PWM信号PA、PBは、その立ち上がり時点が、基準周期、すなわち、PWM信号PA、PBの1サイクル期間Tcの開始時点に固定され、その立ち下がり時点が入力信号Pinの示すレベルに対応して変化するものとさ

50

れる。

**【0005】**

さらに、 PWM 信号 PA、 PB のキャリア周波数  $f_c (= 1 / T_c)$  は、入力デジタルオーディオ信号 Pin のサンプリング周波数  $f_s$  の例えれば 16 倍とされ、  $f_s = 48 \text{ kHz}$  とすれば、  $f_c = 16 f_s = 16 \times 48 \text{ kHz} = 768 \text{ kHz}$  とされる。

**【0006】**

そして、そのような PWM 信号 PA がドライブ回路 13 に供給されて図 11A に示すように、信号 PA と同レベルおよびレベル反転した 1 対のドライブ電圧 + PA、 - PA が形成され、これらドライブ電圧 + PA、 - PA が、1 対の n チャンネルの MOS-FET (Q11、Q12) のゲートにそれぞれ供給される。この場合、FET (Q11、Q12) はプッシュプル回路 15 を構成するものであり、FET (Q11) のドレインが電源端子 TPWR に接続され、そのソースが FET (Q12) のドレインに接続され、この FET (Q12) のソースが接地に接続される。また、電源端子 TPWR には、安定した直流電圧 + VDD が電源電圧として供給される。なお、電圧 + VDD は、例えれば 20V ~ 50V である。

**【0007】**

そして、FET (Q11) のソースおよび FET (Q12) のドレインが、コイルおよびコンデンサを有するローパスフィルタ 17 を通じてスピーカ 19 の一端に接続される。

**【0008】**

また、PWM 变調回路 11 からの PWM 信号 PB に対しても、PWM 信号 PA に対してと同様に構成される。すなわち、PWM 信号 PB がドライブ回路 14 に供給されて図 11B に示すように、信号 PB と同レベルおよびレベル反転した 1 対のドライブ電圧 + PB、 - PB が形成され、これらドライブ電圧 + PB、 - PB が、プッシュプル回路 16 を構成する 1 対の n チャンネルの MOS-FET (Q13、Q14) のゲートにそれぞれ供給される。

**【0009】**

そして、FET (Q13) のソースおよび FET (Q14) のドレインが、コイルおよびコンデンサを有するローパスフィルタ 18 を通じてスピーカ 19 の他端に接続される。

**【0010】**

したがって、+ PA = "H" のときには、- PA = "L" であり、FET (Q11) がオンになるとともに、FET (Q12) がオフになるので、FET (Q11、Q12) の接続点の電圧 VA は、図 11C に示すように、電圧 + VDD となる。また、逆に、+ PA = "L" のときには、- PA = "H" であり、FET (Q11) がオフになるとともに、FET (Q12) がオンになるので、VA = 0 となる。

**【0011】**

同様に、+ PB = "H" のときには、- PB = "L" であり、FET (Q13) がオンになるとともに、FET (Q14) がオフになるので、FET (Q13、Q14) の接続点の電圧 VB は、図 11D に示すように、電圧 + VDD となる。また、逆に、+ PB = "L" のときには、- PB = "H" であり、FET (Q13) がオフになるとともに、FET (Q14) がオンになるので、VB = 0 となる。

**【0012】**

そして、VA = + VDD、かつ、VB = 0 の期間には、図 10 および図 11E に示すように、FET (Q11、Q12) の接続点から、ローパスフィルタ 17 スピーカ 19 ローパスフィルタ 18 のラインを通じて、FET (Q13、Q14) の接続点へと、電流 i が流れる。

**【0013】**

また、VA = 0、かつ、VB = + VDD の期間には、FET (Q13、Q14) の接続点から、ローパスフィルタ 18 スピーカ 19 ローパスフィルタ 17 のラインを通じて、FET (Q11、Q12) の接続点へと、逆向きに電流 i が流れる。さらに、VA = VB = + VDD の期間、および VA = VB = 0 の期間には、電流 i は流れない。つまり、プッシュプル回路 15、16 が BTL 回路を構成していることになる。

**【0014】**

10

20

30

40

50

そして、電流*i*の流れる期間は、もとのPWM信号PA、PBが立ち上がっている期間に対応して変化するとともに、電流*i*がスピーカ19を流れるとき、電流*i*はローパスフィルタ17、18により積分されるので、結果として、スピーカ19を流れる電流*i*は、入力信号Pinの示すレベルに対応したアナログ電流であって電力増幅された電流となる。つまり、電力増幅された出力がスピーカ19に供給されることになる。

#### 【0015】

こうして、図10の回路はパワーアンプとして動作するが、このとき、FET(Q11~Q14)は、入力されたデジタルオーディオ信号Pinに対応して電源電圧+VDDをスイッチングして電力増幅をするので、効率が高く、また、大出力を得ることができる。

#### 【0016】

【発明が解決しようとする課題】10

ところで、上述のパワーアンプは、図11C、Dにも示すように、電源電圧+VDDを高速にスイッチングして出力電圧VA、VBを形成しているので、出力電圧VA、VBの立ち上がりエッジおよび立ち下がりエッジにより輻射を生じてしまう。しかも、そのスイッチング時、電源電圧+VDDは、例えば20V~50Vと高い電圧なので、その輻射もかなりの大きさとなってしまう。また、PWM信号PA、PBのキャリア周波数fcは、上記のように例えば768kHzであり、これは中波放送の放送帯に含まれる。

#### 【0017】

このため、上述のようなD級パワーアンプが、カーオーディオなどのように、受信機と一緒に化されていましたり、受信機に近接して配置されたりすると、出力電圧VA、VBの立ち上がりエッジおよび立ち下がりエッジによる輻射が、放送の受信に妨害を与えててしまう。また、出力電圧VA、VBの立ち上がりエッジおよび立ち下がりエッジは急峻であって高調波成分を多く含み、その高調波成分も輻射されるので、FM受信機やテレビ受像機などの受信に妨害を与えることもある。20

#### 【0018】

この発明は、そのような輻射を低減させたパワーアンプを提供しようとするものである。

#### 【0019】

##### 【課題を解決するための手段】

この発明においては、

入力信号のレベルを示す第1のパルス変調信号(+PA)と、上記入力信号のレベルの補数を示す第2のパルス変調信号(+PB)をレベル反転して得られる第2の反転パルス変調信号(-PB)とを、第1のパルス信号として基準周期ごとに交互に出力するとともに、上記第2のパルス変調信号(+PB)と、上記第1のパルス変調信号をレベル反転して得られる第1の反転パルス変調信号(-PA)とを、第2のパルス信号として上記基準周期ごとに交互に出力するパルス変調手段と。30

スイッチング素子を含み、上記パルス変調手段からの上記第1のパルス信号にしたがってスイッチング出力を供給する第1の出力回路と、

スイッチング素子を含み、上記パルス変調手段からの上記第2のパルス信号にしたがってスイッチング出力を供給する第2の出力回路とを備え、40

上記パルス変調手段は、

上記入力信号を、上記基準周期ごとにそのレベルを示す第1のパルス変調信号に変換して出力する第1のパルス変調回路と、

上記入力信号を、上記基準周期ごとにそのレベルの補数を示す第2のパルス変調信号に変換して出力する第2のパルス変調回路と、

上記第1のパルス変調回路からの出力を、レベル反転して第1の反転パルス変調信号を出力する第1の反転回路と、

上記第2のパルス変調回路からの出力を、レベル反転して第2の反転パルス変調信号を出力する第2の反転回路と、

上記第1のパルス変調信号と、上記第2の反転パルス変調信号とを、上記基準周期ご

50

とに交互に選択して上記第1のパルス信号を出力する第1の選択回路と、

上記第2のパルス変調信号と、上記第1の反転パルス変調信号とを、上記基準周期ご

とに交互に選択して上記第2のパルス信号を出力する第2の選択回路と

を備え、

上記第1の出力回路の出力端と、上記第2の出力回路の出力端との間に、負荷が接続される

ことを特徴とするパワーアンプ

とするものである。

したがって、出力電圧のエッジの数が1/2となり、輻射が低減する。

#### 【0020】

10

#### 【発明の実施の形態】

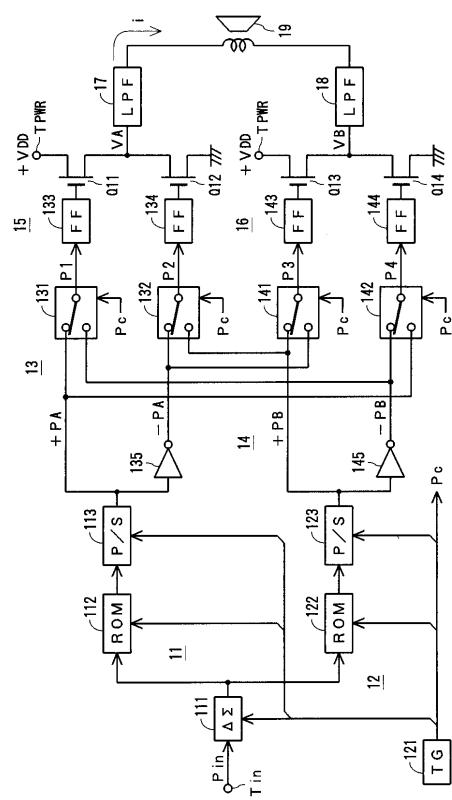

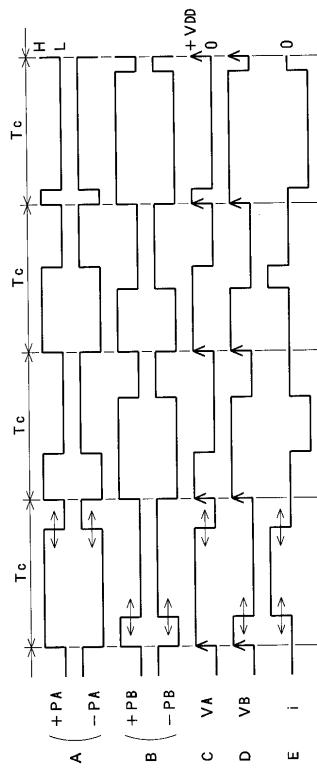

図1は、この発明によるD級パワーアンプの一例を示し、この例においては、デジタルオーディオ信号Pinが、入力端子Tinを通じて変調回路111に供給される。この変調回路111は、ROM112および並列入力直列列出力のシフトレジスタ113とともに、第1のPWM変調回路11を構成し、ROM122および並列入力直列列出力のシフトレジスタ123とともに、第2のPWM変調回路12を構成するものである。そして、デジタルオーディオ信号Pinは、PWM変調回路11、12により、例えば図2A、Bに示すようなPWM信号+PA、+PBに変換される。

#### 【0021】

20

ここで、PWM信号+PA、+PBのパルス幅は、入力信号Pinの示すレベルに対応して変化するものであるが、図12に示すように、一方のPWM信号+PAのパルス幅は、入力信号Pinの示すレベルに対応した大きさとされ、他方のPWM信号+PBのパルス幅は、入力信号Pinの示すレベルの例えば2の補数に対応した大きさとされる。また、PWM信号+PA、+PBは、その立ち上がり時点が、PWM信号+PA、+PBの1サイクル期間Tcの開始時点に固定され、その立ち下がり時点がオーディオ信号Pinの示すレベルに対応して変化するものとされる。

#### 【0022】

30

さらに、PWM信号+PA、+PBのキャリア周波数fc(=1/Tc)は、デジタルオーディオ信号Pinのサンプリング周波数fsの例えば16倍とされ、fs=48kHzとすれば、

$$f_c = 16 f_s = 16 \times 48 \text{ kHz} = 768 \text{ kHz}$$

とされる。

#### 【0023】

30

このようなPWM信号+PA、+PBを形成するため、PWM変調回路11においては、入力端子Tinからのデジタルオーディオ信号Pinが、変調回路111に供給されて可聴帯域内の量子化ノイズを抑えつつビット数を少なくしたデジタルオーディオ信号、例えば、量子化周波数(=fc)が16fsで、量子化ビット数が6ビットのデジタルオーディオ信号に変換され、このデジタルオーディオ信号がROM112に供給されてその量子化レベルに対応した並列デジタルデータに変換され、この並列デジタルデータがシフトレジスタ113に供給されて直列信号、すなわち、PWM信号+PAに変換される。

#### 【0024】

40

また、PWM変調回路12においては、変調回路111から出力されるデジタルオーディオ信号が、ROM122に供給されてそのレベルの2の補数に対応した並列デジタルデータに変換され、この並列デジタルデータがシフトレジスタ123に供給されて直列信号、すなわち、PWM信号+PBに変換される。

#### 【0025】

なお、このとき、タイミング信号形成回路121において各種のタイミングの信号が形成され、これらのタイミング信号が回路111～113、122、123にそれぞれ供給される。

#### 【0026】

そして、PWM信号+PA、+PBがドライブ回路13、14に供給されてドライブ電圧P

50

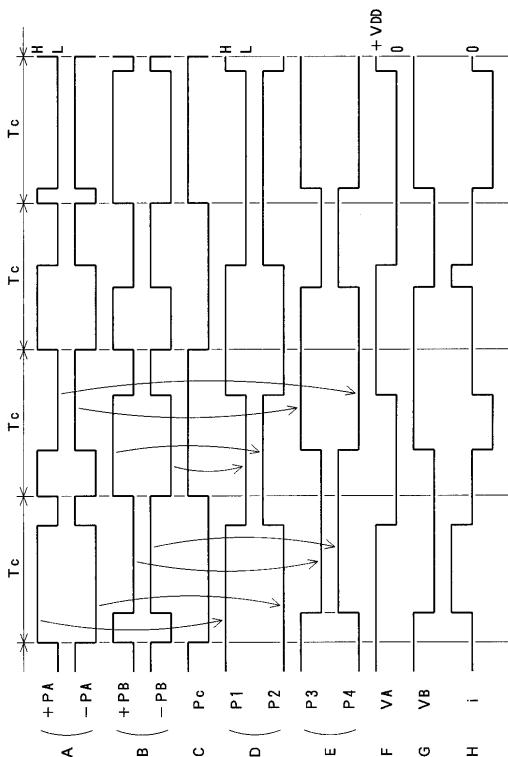

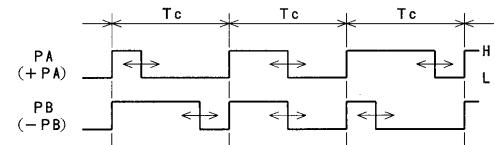

1～P4が形成される。すなわち、PWM信号+PAがセレクタ回路131、142に供給されるとともに、インバータ135に供給されて図2Aに示すように、レベルの反転したPWM信号-PAとされ、このPWM信号-PAがセレクタ回路132、141に供給される。また、PWM信号+PBがセレクタ回路141、132に供給されるとともに、インバータ145に供給されて図2Bに示すように、レベルの反転したPWM信号-PBとされ、このPWM信号-PBがセレクタ回路142、131に供給される。なお、図2A、Bは、図11A、Bと同じである。

#### 【0027】

さらに、タイミング信号形成回路12から図2Cに示すように、1サイクル期間Tcごとにレベルの反転する信号Pcが取り出され、この信号Pcがセレクタ回路131、132、141、142にその切り換え制御信号として供給される。

10

#### 【0028】

こうして、セレクタ回路131、132からは、図2Dに示すように、Pc=“L”的期間Tcには、信号+PA、-PAがドライブ電圧P1、P2として取り出され、Pc=“H”的期間Tcには、信号-PB、+PBがドライブ電圧P1、P2として取り出される。また、セレクタ回路141、142からは、図2Eに示すように、Pc=“L”的期間Tcには、信号+PB、-PBがドライブ電圧P3、P4として取り出され、Pc=“H”的期間Tcには、信号-PA、+PAがドライブ電圧P1、P2として取り出される。

#### 【0029】

そして、これらのドライブ電圧P1、P2、P3、P4がフリップフロップ回路133、134、143、144により整形されたのち、ドライブ電圧P1、P2が、1対のスイッチング素子、例えばnチャンネルのMOS-FET(Q11、Q12)のゲートにそれぞれ供給される。この場合、FET(Q11、Q12)はプッシュプル回路15を構成するものであり、FET(Q11)のドレインが電源端子TPWRに接続され、そのソースがFET(Q12)のドレインに接続され、このFET(Q12)のソースが接地に接続される。また、電源端子TPWRには、安定した直流電圧+VDD、例えば20V～50Vの直流電圧が電源電圧として供給される。

20

#### 【0030】

さらに、FET(Q11)のソースおよびFET(Q12)のドレインが、例えばコイルおよびコンデンサにより構成されたローパスフィルタ17を通じてスピーカ19の一端に接続される。

30

#### 【0031】

また、ドライブ回路14からのドライブ電圧P3、P4に対してても、ドライブ電圧P1、P2に対してと同様に構成される。すなわち、ドライブ電圧P3、P4が、プッシュプル回路16を構成する1対のnチャンネルのMOS-FET(Q13、Q14)のゲートにそれぞれ供給される。また、FET(Q13)のソースおよびFET(Q14)のドレインが、コイルおよびコンデンサを有するローパスフィルタ18を通じてスピーカ19の他端に接続される。

#### 【0032】

このような構成によれば、P1=“H”的ときには、P2=“L”であり、FET(Q11)がオンになるとともに、FET(Q12)がオフになるので、FET(Q11、Q12)の接続点の電圧VAは、図2Fに示すように、電圧+VDDとなる。また、逆に、P1=“L”的ときには、P2=“H”であり、FET(Q11)がオフになるとともに、FET(Q12)がオンになるので、VA=0となる。

40

#### 【0033】

同様に、P3=“H”的ときには、P4=“L”であり、FET(Q13)がオンになるとともに、FET(Q14)がオフになるので、FET(Q13、Q14)の接続点の電圧VBは、図2Gに示すように、電圧+VDDとなる。また、逆に、P3=“L”的ときには、P4=“H”であり、FET(Q13)がオフになるとともに、FET(Q14)がオンになるので、VB=0となる。

50

**【 0 0 3 4 】**

そして、 $V_A = +V_{DD}$ 、かつ、 $V_B = 0$  の期間には、図 1 および図 2 H に示すように、FET (Q11、Q12) の接続点から、ローパスフィルタ 17 スピーカ 19 ローパスフィルタ 18 のラインを通じて、FET (Q13、Q14) の接続点へと、電流  $i$  が流れる。

**【 0 0 3 5 】**

また、 $V_A = 0$ 、かつ、 $V_B = +V_{DD}$  の期間には、FET (Q13、Q14) の接続点から、ローパスフィルタ 18 スピーカ 19 ローパスフィルタ 17 のラインを通じて、FET (Q11、Q12) の接続点へと、逆向きに電流  $i$  が流れる。さらに、 $V_A = V_B = +V_{DD}$  の期間、および  $V_A = V_B = 0$  の期間には、電流  $i$  は流れない。つまり、プッシュプル回路 15、16 が BTL 回路を構成していることになる。10

**【 0 0 3 6 】**

そして、電流  $i$  の流れる期間は、もとの PWM 信号 +PA、+PB が立ち上がっている期間に対応して変化するとともに、電流  $i$  がスピーカ 19 を流れるとき、電流  $i$  はローパスフィルタ 17、18 により積分されるので、結果として、スピーカ 19 を流れる電流  $i$  は、デジタルオーディオ信号 Pin の示すレベルに対応したアナログ電流であって電力増幅された電流となる。したがって、図 1 に示す回路は、D 級パワーアンプとして動作していることになり、電力増幅された出力がスピーカ 19 に供給されることになる。

**【 0 0 3 7 】**

こうして、図 1 に示すパワーアンプは、スイッチングにより電力増幅を行うことができるが、図 2 にも示すように、PWM 信号 +PA、+PB の立ち上がりおよび立ち下がりは、1 サイクル期間  $T_c$  ごとに 1 回ずつ生じているが、出力電圧  $V_A$ 、 $V_B$  の立ち上がりおよび立ち下がりは、1 サイクル期間  $T_c$  にどちらか 1 回しか生じないので、出力電圧  $V_A$ 、 $V_B$  の立ち上がりエッジおよび立ち下がりエッジの数は、図 10 に示すパワーアンプにおける出力電圧  $V_A$ 、 $V_B$  (図 11 C、D 参照) の立ち上がりエッジおよび立ち下がりエッジの数の 1 / 2 となっている。したがって、出力電圧  $V_A$ 、 $V_B$  の変化により生じる輻射を低減することができる。20

**【 0 0 3 8 】**

また、出力電圧  $V_A$ 、 $V_B$  の周波数は、図 10 に示すパワーアンプにおける出力電圧  $V_A$ 、 $V_B$  の周波数の 1 / 2 になるので、カーオーディオなどのように、パワーアンプが受信機と一緒に化されており、受信機に近接して配置されたりしても、輻射が放送の受信に与える妨害を低減することができる。そして、このように輻射が放送の受信に与える妨害を低減することができるので、輻射に対して受信機をシールドするための部材を削減することができ、コストを低減できる。また、受信機をパワーアンプにより近接させることができるので、省スペースとすることもできる。30

**【 0 0 3 9 】**

さらに、例えば、プッシュプル回路 15 において、ドライブ電圧 P1 が立ち下がるとともに、ドライブ電圧 P2 が立ち上がるときに、ドライブ電圧 P1 の立ち下がりが遅れると、瞬間的ではあるが、両方のドライブ電圧 P1、P2 が “L” になる期間を生じ、この期間に FET (Q11、Q12) が同時にオンになって FET (Q11、Q12) に貫通電流が流れてしまう。40

**【 0 0 4 0 】**

しかし、図 1 に示すパワーアンプは、図 10 に示すパワーアンプに比べ、ドライブ電圧 P1～P4 の周波数が 1 / 2 になっているので、FET (Q11、Q12) や FET (Q13、Q14) が同時にオンになって FET (Q11、Q12) や FET (Q13、Q14) に貫通電流が流れ回数を半減することができる。

**【 0 0 4 1 】**

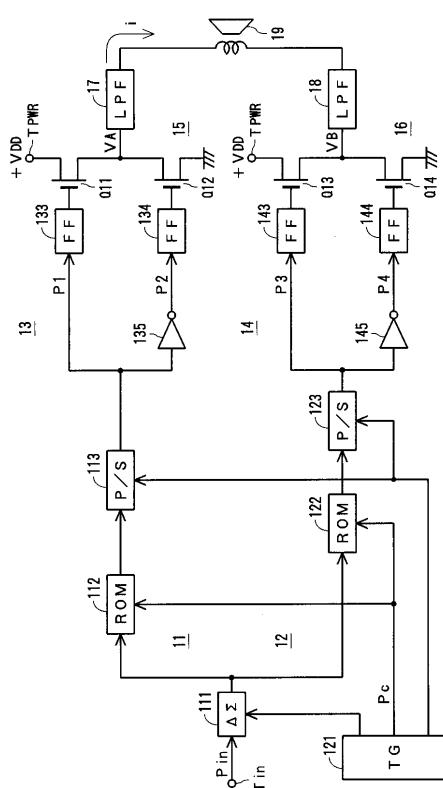

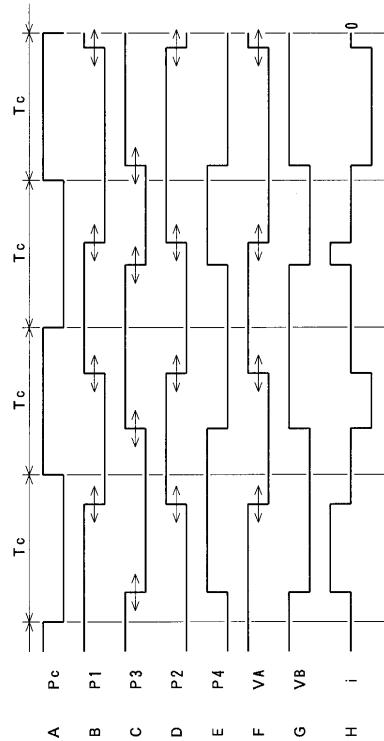

ところで、図 2 からも明かなように、 $P_c = "H"$  の期間  $T_c$  のドライブ電圧 P1、P2 は、信号 +PA、-PA の時間軸の前後を逆にしたものと等価であり、 $P_c = "H"$  の期間  $T_c$  のドライブ電圧 P3、P4 は、信号 +PB、-PB の時間軸の前後を逆にしたものと等価である。50

**【0042】**

そこで、図3に示すPWM変調回路11、12においては、ROM112、122から読み出されるデータを、 $P_c = "L"$ の期間 $T_c$ と $P_c = "H"$ の期間 $T_c$ とで切り換えることにより、ドライブ電圧P1～P4の内容を、図2のものと同様とする場合である。

**【0043】**

すなわち、この例においては、変調回路111から出力されるデジタルオーディオ信号は1サンプルが6ビットなので、図4に示すように、ROM112は、アドレスが1ビット多い7ビットA6～A0とされ、各アドレスのデータサイズが1サンプル6ビットに対応して64ビットD63～D0とされる。

**【0044】**

ここで、変調回路111から出力されるデジタルオーディオ信号は1サンプルが6ビットであるから、そのデジタルオーディオ信号は図5の左欄に示すように、0から±31までの63値を取ることになる。そして、この63値は2の補数により表現されているので、これを2進数で示すと図5の中欄のようになり、この2進数が自然2進数であるとみなして10進数に変換すると、図5の右欄に示すようになる。

**【0045】**

そこで、図4に示すように、ROM112の任意のアドレスをm番地(0～m～127)とするとき、m=32番地は不使用とされ、m=33～63番地には、最上位ビットD63からビットD(96-m)までが“1”であり、ビットD(95-m)から最下位ビットD0までが“0”的値が用意される。また、m=0～31番地には、最上位ビットD63からビットD(32-m)までが“1”であり、ビットD(31-m)から最下位ビットD0までが“0”的値が用意される。

**【0046】**

さらに、ROM112のm=(64+32)番地は不使用とされ、m=(64+33)～(64+63)、(64+0)～(64+31)番地には、m=33～63、0～31番地におけるビット配列の上位ビットと下位ビットとを逆にしたものが用意される。すなわち、m=(64+33)～(64+63)番地には、最上位ビットD63からビットD(m-96)までが“0”であり、ビットD(m-97)から最下位ビットD0までが“1”的値が用意される。また、m=(64+0)～(64+31)番地には、最上位ビットD63からビットD(m-32)までが“0”であり、ビットD(m-33)から最下位ビットD0までが“1”的値が用意される。

**【0047】**

さらに、ROM122の0～63番地は、ROM112の63～0番地と等しいデータとされ、ROM122の64～127番地は、ROM112の127～64番地と等しいデータとされる。なお、ROM112、122の0～63番地のデータを、図1におけるROM112、122の0～63番地のデータとすることができる。

**【0048】**

そして、図4の下方に示すように、ROM112、122の7ビットのアドレスA6～A0のうち、下位の6ビットA5～A0に、変調回路111から出力されるデジタルオーディオ信号が供給され、最上位ビットA6に、タイミング信号形成回路121から1サンプル期間 $T_c$ ごとに反転する信号 $P_c$ が供給される。

**【0049】**

したがって、図4からも理解されるように、 $P_c = "L"$ の期間 $T_c$ には、ROM112のアドレスの最上位ビットA6は“0”となるので、0～63番地のデータのうち、変調回路111からのデジタルオーディオ信号に対応するアドレスのデータD63～D0が出力される。また、 $P_c = "H"$ の期間 $T_c$ には、ROM112のアドレスの最上位ビットA6は“1”となるので、(64+0)～(64+63)番地のデータのうち、変調回路111からのデジタルオーディオ信号に対応するアドレスのデータD63～D0が出力される。そして、このようなデータD63～D0が並列入力直列出力のシフトレジスタ113に供給されて直列信号に変換される。

**【0050】**

したがって、この変換結果の直列信号は、図6Bに示すように、 $P_c = "L"$ の期間 $T_c$ に

10

20

30

40

50

は、この期間  $T_c$  の開始時には立ち上がっていて、立ち下がる時点がデジタルオーディオ信号の示すレベルに対応して変化し、 $P_c = "H"$  の期間  $T_c$  には、立ち上がる時点がデジタルオーディオ信号の示すレベルに対応して変化し、期間  $T_c$  の終了時点には立ち上がっている PWM 信号  $P_1$  となる。

#### 【0051】

また、ROM122 については、 $P_c = "L"$  の期間  $T_c$  には、アドレスの最上位ビットが “1” となるので、64~127番地のデータのうち、入力されたデジタルオーディオ信号に対応するアドレスのデータ  $D_{63} \sim D_0$  が outputされる。また、 $P_c = "H"$  の期間  $T_c$  には、アドレスの最上位ビットが “0” となるので、0~63番地のデータのうち、入力されたデジタルオーディオ信号に対応するアドレスのデータ  $D_{63} \sim D_0$  が outputされる。そして、このようなデータ  $D_{63} \sim D_0$  が並列入力直列出力のシフトレジスタ123 に供給されて直列信号に変換される。10

#### 【0052】

したがって、この変換結果の直列信号は、図 6C に示すように、 $P_c = "L"$  の期間  $T_c$  には、この期間  $T_c$  の開始時には立ち上がっていて、立ち下がる時点がデジタルオーディオ信号の示すレベルの補数に対応して変化し、 $P_c = "H"$  の期間  $T_c$  には、立ち上がる時点がデジタルオーディオ信号の示すレベルの補数に対応して変化し、期間  $T_c$  の終了時点には立ち上がっている PWM 信号  $P_3$  となる。

#### 【0053】

そして、PWM 信号  $P_1$  がフリップフロップ回路133 を通じて FET (Q11) のゲートに供給されるとともに、インバータ135 に供給されて図 6D に示すように、レベルの反転した信号  $P_2$  とされ、この信号  $P_2$  がフリップフロップ回路134 を通じて FET (Q12) のゲートに供給される。また、PWM 信号  $P_3$  がフリップフロップ回路143 を通じて FET (Q13) のゲートに供給されるとともに、インバータ145 に供給されて図 6E に示すように、レベルの反転した信号  $P_4$  とされ、この信号  $P_4$  がフリップフロップ回路144 を通じて FET (Q14) のゲートに供給される。20

#### 【0054】

したがって、FET (Q11、Q12) の接続点の電圧  $V_A$  および FET (Q13、Q14) の接続点の電圧  $V_B$  は、図 6F、G に示すように、図 2F、G の電圧  $V_A$ 、 $V_B$  と同じとなるので、スピーカ19 には図 6H に示す電流  $i$  が供給されることになり、この結果、スピーカ19 には電力増幅された出力が供給されることになる。30

#### 【0055】

そして、この図 3 のパワーアンプによれば、図 1 のパワーアンプと同様の効果が得られるだけでなく、さらに、図 1 におけるスイッチ回路131、132、141、142 を省略することができる。

#### 【0056】

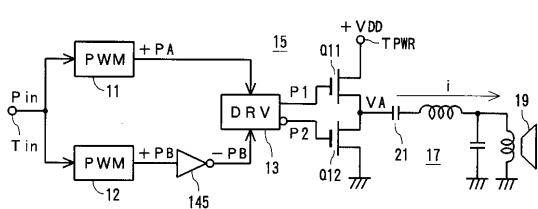

上述においては、パワーアンプの出力段が BTL 回路とされている場合であるが、シングル回路とすることもできる。図 7 は、そのようなパワーアンプの一形態を示す。

#### 【0057】

すなわち、図 7 に示すパワーアンプにおいては、PWM 变調回路11、12 から図 8A に示すように PWM 信号 + PA、+ PB が取り出され、PWM 信号 + PA がドライブ回路13 に供給され、PWM 信号 + PB がインバータ145 に供給されて図 8B に示すように、レベルの反転した PWM 信号 - PB とされ、この PWM 信号 - PB がドライブ回路13 に供給される。40

#### 【0058】

そして、ドライブ回路13 からドライブ電圧  $P_1$ 、 $P_2$  が取り出され、これらドライブ電圧  $P_1$ 、 $P_2$  がブッシュプル回路15 に供給される。この場合、図 8C に示すように、ドライブ電圧  $P_1$  は、PWM 信号 + PA と、PWM 信号 - PB とを、1 サイクル期間  $T_c$  ごとに交互に取り出した信号であり、ドライブ電圧  $P_2$  はドライブ電圧  $P_1$  のレベルを反転した信号である。50

**【0059】**

また、図7に示すパワーアンプにおいては、ブッシュプル回路15が正負の電源を使用する場合であり、FET(Q11)のドレインが正の電源端子TPWR+に接続され、FET(Q12)のソースが負の電源端子TPWR-に接続される。そして、電源端子TPWR+、TPWR-には、正負一対の直流電圧+VDD、-VDDが電源電圧として供給される。そして、ブッシュプル回路15の出力端が、ローパスフィルタ17を通じてスピーカ19の一端に接続され、その他端は接地される。

**【0060】**

したがって、ブッシュプル回路15の出力電圧VAは、ドライブ電圧P1、P2に対応して図8Dに示すような波形となり、図8Eに示すように、スピーカ19には入力信号Pinに10対応した極性および大きさの電流iが流れることになり、電力増幅が行われる。

**【0061】**

そして、このパワーアンプにおいても、ドライブ電圧P1、P2の立ち上がりエッジおよび立ち下がりエッジの数は、PWM信号+PA、+PBの1/2となっているので、FET(Q11、Q12)、(Q13、Q14)に流れる貫通電流が半減する。また、出力電圧VAの周波数が1/2となっているので、この出力電圧VAにより生じる輻射も低減する。

**【0062】**

図9に示すパワーアンプは、図7に示すパワーアンプと同様、出力段がシングル回路されるとともに、ブッシュプル回路15の電源電圧を直流電圧+VDDだけとした場合である。したがって、この場合には、例えば、ブッシュプル回路15の出力端と、ローパスフィルタ17との間に、直流カット用のコンデンサ21が接続される。

20

**【0063】**

なお、上述においては、入力信号Pinがデジタルオーディオ信号の場合であるが、アナログオーディオ信号であってもよい。また、PWM信号+PA、+PB、-PA、-PBはPNM信号などとすることもできる。さらに、PWM変調回路11、12は、アップカウンタ、ダウンカウンタおよび比較回路により構成することもできる。

**【0064】**

また、図4におけるROM112、122のデータテーブルは、0~63番地のデータの上位ビットと下位ビットとを入れ換えると、64~127番地のデータとなるので、Pc="L"の期間Tcと、Pc="H"の期間Tcとで、シフトレジスタ113、123にロードしたデータを最下位ビットD0から取り出すか最上位ビットD63から取り出すかを切り換えることより期間Tcごとに時間軸の前後を反転すれば、ROM112、122は0~63番地だけとすることができます、ROM112、122の容量を1/2にすることができる。

30

**【0065】**

さらに、上述においては、パワーアンプがオーディオ用のアンプの場合であるが、モータなどの電力機器をドライブするためのアンプとして使用することもできる。また、スピーカ19に代えて任意の負荷を接続すれば、その負荷に動作電圧を供給することができるとともに、入力信号Pinを変更することにより負荷に供給される電圧の大きさを変更することができ、したがって、可変電源回路として使用することもできる。

**【0066】**

[この明細書で使用している略語の一覧]

|         |                                      |

|---------|--------------------------------------|

| BTL     | : Bridged-Tied Load                  |

| MOS-FET | : Metal Oxide Semiconductor type FET |

| FET     | : Field Effect Transistor            |

| PNM     | : Pulse Number Modulation            |

| PWM     | : Pulse Width Modulation             |

| ROM     | : Read Only Memory                   |

**【0067】****【発明の効果】**

この発明によれば、出力電圧の立ち上がりエッジおよび立ち下がりエッジの数が、その出

50

力電圧を形成する PWM 信号の立ち上がりエッジおよび立ち下がりエッジの数の 1 / 2 となるので、出力電圧の変化により生じる輻射を低減することができる。

【0068】

したがって、カーオーディオなどのように、パワーアンプが受信機と一体化されたり、受信機に近接して配置されていても、輻射が放送の受信に与える妨害を低減することができる。また、このことから、輻射に対して受信機をシールドするための部材を削減することができ、コストを低減することができる。さらに、受信機をパワーアンプにより近接させることができるので、省スペースとすることもできる。

【0069】

また、出力電圧の立ち上がりエッジおよび立ち下がりエッジの数が 1 / 2 となるので、その出力電圧を形成するためのプッシュプル回路に貫通電流が流れる回数を半減することができ、アンプの損失を低減し、デバイスからの発熱も抑えることができる。さらに、出力用のスイッチング素子のスイッチングの回数が半減するので、スイッチングノイズにより生じるオーディオ特性の劣化を抑えることもできる。

【図面の簡単な説明】

【図 1】この発明の一形態を示す系統図である。

【図 2】図 1 の回路を説明するための波形図である。

【図 3】この発明の他の形態を示す系統図である。

【図 4】データテーブルの一形態を示す図である。

【図 5】信号とアドレスの関係を説明するための図である。

【図 6】図 3 の回路を説明するための波形図である。

【図 7】この発明の他の形態を示す系統図である。

【図 8】図 7 の回路を説明するための波形図である。

【図 9】この発明の他の形態を示す系統図である。

【図 10】この発明を説明するための系統図である。

【図 11】図 10 の回路を説明するための波形図である。

【図 12】図 10 の回路を説明するための波形図である。

【符号の説明】

11 および 12 ... PWM 変調回路、13 および 14 ... ドライブ回路、15 および 16 ... プッシュプル回路、17 および 18 ... ローパスフィルタ、19 ... スピーカ

10

20

30

【図1】

【図2】

【図3】

【図4】

| アドレスn | データ |     |     |     |     |     |     |    |    |    |    |    |    |   |   |   |

|-------|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|---|---|---|

|       | D63 | D62 | D61 | D60 | D59 | D58 | ... | D5 | D4 | D3 | D2 | D1 | D0 |   |   |   |

| 32    | *   | *   | *   | *   | *   | *   | *   | *  | *  | *  | *  | *  | *  | * | * | * |

| 33    | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 |

| 34    | 1   | 1   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 |

| 35    | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 |

| 36    | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 |

| 37    | 1   | 1   | 1   | 1   | 1   | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 |

| ...   |     |     |     |     |     |     |     |    |    |    |    |    |    |   |   |   |

| 63    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 |

| 0     | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 |

| ...   |     |     |     |     |     |     |     |    |    |    |    |    |    |   |   |   |

| 27    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 0  | 0  | 0  | 0  | 0 | 0 | 0 |

| 28    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 0  | 0  | 0  | 0 | 0 | 0 |

| 29    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 0  | 0  | 0 | 0 | 0 |

| 30    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 0  | 0 | 0 | 0 |

| 31    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 0 | 0 | 0 |

| 32    | *   | *   | *   | *   | *   | *   | *   | *  | *  | *  | *  | *  | *  | * | * | * |

| 33    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 1 |

| 34    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 1 | 1 |

| 35    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1 | 1 | 1 |

| 36    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 1  | 1 | 1 | 1 |

| 37    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 1  | 1  | 1  | 1 | 1 | 1 |

| ...   |     |     |     |     |     |     |     |    |    |    |    |    |    |   |   |   |

| 63    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 |

| 0     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 |

| ...   |     |     |     |     |     |     |     |    |    |    |    |    |    |   |   |   |

| 27    | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 |

| 28    | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 |

| 29    | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 |

| 30    | 0   | 0   | 0   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 |

| 31    | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 |

Pc デジタルオーディオ信号

【図5】

|     | 2の補数 |   |   |   |   | 自然数 |    |

|-----|------|---|---|---|---|-----|----|

| -31 | 1    | 0 | 0 | 0 | 0 | 1   | 33 |

| -30 | 1    | 0 | 0 | 0 | 1 | 0   | 34 |

| -29 | 1    | 0 | 0 | 0 | 1 | 1   | 35 |

| -28 | 1    | 0 | 0 | 1 | 0 | 0   | 36 |

| ⋮   | ⋮    | ⋮ | ⋮ | ⋮ | ⋮ | ⋮   | ⋮  |

| -3  | 1    | 1 | 1 | 1 | 0 | 1   | 61 |

| -2  | 1    | 1 | 1 | 1 | 1 | 0   | 62 |

| -1  | 1    | 1 | 1 | 1 | 0 | 1   | 63 |

| 0   | 0    | 0 | 0 | 0 | 0 | 0   | 0  |

| 1   | 0    | 0 | 0 | 0 | 0 | 1   | 1  |

| 2   | 0    | 0 | 0 | 0 | 1 | 0   | 2  |

| 3   | 0    | 0 | 0 | 0 | 1 | 1   | 3  |

| ⋮   | ⋮    | ⋮ | ⋮ | ⋮ | ⋮ | ⋮   | ⋮  |

| 28  | 0    | 1 | 1 | 1 | 0 | 0   | 28 |

| 29  | 0    | 1 | 1 | 1 | 0 | 1   | 29 |

| 30  | 0    | 1 | 1 | 1 | 1 | 0   | 30 |

| 31  | 0    | 1 | 1 | 1 | 1 | 1   | 31 |

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

---

フロントページの続き

(56)参考文献 特開2003-152468(JP,A)

特開2002-158549(JP,A)

特開2002-158544(JP,A)

特開2001-292040(JP,A)

特開2001-185961(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00-3/72

H03K 17/00-17/70