República Federativa do Brasil

Ministério da Economia

Instituto Nacional da Propriedade Industrial

**(11) BR 102013013386-8 B1**

**(22) Data do Depósito: 29/05/2013**

**(45) Data de Concessão: 28/06/2022**

**(54) Título:** MÉTODO E APARELHO PARA SINCRONIZAÇÃO DE AMOSTRAS DE DADOS E DE ERRO EM UM SISTEMA DE COMUNICAÇÕES

**(51) Int.Cl.:** H04L 27/00; H04L 25/03; H04L 27/26.

**(52) CPC:** H04L 27/0014; H04L 2025/03477; H04L 2025/03636; H04L 25/03038; H04L 27/2689; (...).

**(30) Prioridade Unionista:** 29/05/2012 US 13/482,686.

**(73) Titular(es):** HUGHES NETWORK SYSTEMS, LLC.

**(72) Inventor(es):** KRISHNARAJ VARMA; TONY HUANG; SRI BHAT.

**(57) Resumo:** MÉTODO E APARELHO PARA SINCRONIZAÇÃO DE AMOSTRAS DE DADOS E DE ERRO EM UM SISTEMA DE COMUNICAÇÕES Um método e aparelho para processar sinais de dados de entrada transmitidos em um modo contínuo, ou em um modo de rajadas, de transmissão de sinal, tal como um sistema de comunicações via satélite ou um de rede de computadores. Um receptor recebe sinais de dados de entrada e um armazenamento temporário armazena os dados de entrada recebidos. Conjunto de circuitos de processamento gera sinais de controle de sincronização de regulação de tempo de quadro para gravar os quadros de dados de entrada para armazenamento, gera sinais de controle de erro de sincronismo correspondendo a um processamento para os dados de entrada, para sincronizar leitura dos dados armazenados pelo armazenamento temporário com base em uma diferença de sincronismo entre os sinais de controle de erro de sincronismo e os sinais de controle de sincronização de regulação de tempo de quadro para ajustar para um atraso arbitrário ao processo de entrada. O conjunto de circuitos de processamento pode incluir um circuito de atualização de gradiente de derivação para gerar um gradiente de derivação correspondendo aos dados lidos, com base em sinais de erro (...).

**MÉTODO E APARELHO PARA SINCRONIZAÇÃO DE AMOSTRAS DE DADOS E

DE ERRO EM UM SISTEMA DE COMUNICAÇÕES**

CAMPO DA INVENÇÃO

A presente invenção diz respeito a métodos e aparelho para demodulação de sinais de dados em um sistema de comunicações, tal como em sistemas de comunicações de banda larga via satélite ou sistemas de computadores. E, mais particularmente, a presente invenção promove equalização de sinais de dados de entrada, e diz respeito a sincronizar amostras de erro e amostras de dados para ajustar para um atraso arbitrário entre amostras de dados de entrada e amostras de erro para os dados de entrada, assim como para aprimorar estimativa de fase e de frequência de ajuste para recuperação de portadora e recuperação de sincronismo de quadro, ao processar sinais de dados recebidos em um modo contínuo, assim como em um modo de rajadas, de transmissão de sinal de dados.

ANTECEDENTES

As capacidades totais de satélites de banda larga estão aumentando exponencialmente, e tais aumentos de capacidade apresentam desafios exclusivos nos projetos de sistemas e de redes terrestres associados. O objetivo dos projetistas de sistemas, operadores de sistemas e provedores de serviços é suportar e fornecer serviços eficientes, robustos, confiáveis e flexíveis, em um ambiente de rede de largura de banda compartilhada, utilizando tais sistemas de satélite de altas capacidades. Em sistemas de comunicações via satélite anteriores, os canais de dados de enlace de descida (isto é, transmissão de dados do satélite para o terminal de satélite)

tipicamente utilizavam larguras de banda na ordem de 20 MHz ou menos. Em tais sistemas, por causa de a largura de banda estreita ser utilizada, tipicamente não existia necessidade de permitir equalização na parte de demodulador/modem do receptor, já que as distorções de amplitude e fase dos componentes eram substancialmente constantes.

Entretanto, em sistemas atuais, tais como sistemas de comunicações via satélite de Difusão de Vídeo Digital de Segunda Geração (DVB-S2), por exemplo, à medida que a necessidade de largura de banda adicional nos canais de dados de enlace de descida de sistemas de comunicações via satélite se torna necessária a fim de que tais sistemas forneçam várias aplicações (por exemplo, alta capacidade de acesso à Internet) para usuários finais, também existe uma necessidade de fornecer equalização na parte de demodulador/modem de canal receptor do sistema, tal como para as distorções de fase e de amplitude de sinal, as quais podem se tornar significativas em um canal de banda larga. Tais distorções de amplitude e de fase devem ser anuladas ou compensadas a fim de possibilitar recebimento e demodulação apropriados do sinal de dados de entrada. Adicionalmente, abordagem de distorções de fase e de amplitude também deve ser feita com um custo razoável.

Demoduladores para sistemas de comunicações via satélite (por exemplo, demoduladores do tipo DVB-S2) tipicamente executam equalização de amostras de dados e amostras de erro dos sinais de dados de entrada após a recuperação de portadora. Tal equalização tipicamente é executada por um filtro de Resposta Finita ao Impulso (FIR) e o erro computação é executado localmente após o bloco de

Módulo de Sincronização de Portadora (CSM). Entretanto, onde o demodulador executa a equalização antes de recuperação de sincronismo de quadro e recuperação de portadora, tal como, por exemplo, em um terminal de Júpiter 5 do sistema de satélite de Júpiter, um desempenho significativamente melhor em detecção de Texto Exclusivo (UW) no processador de Texto Exclusivo (UWP), e em fase e estimativa de frequência no CSM, é possível. Portanto, melhor recuperação de portadora tipicamente pode resultar.

10 Exemplos de demodulação em sistemas de comunicações via satélite são descritos na patente US 6.985.523 para Sims e outros, intitulada "Method and System for Adaptive Equalization for Receivers in a Wide-Band Satellite Communications System", e na publicação de pedido de patente 15 US 2002/0131528 para Clewer e outros, intitulada "System and Method of Parallel Partitioning a Satellite Communications Modem", cujas totalidades estão incorporadas neste documento pela referência. Adicionalmente, um exemplo de controle de ganho automático e demodulação em sistemas 20 de comunicações via satélite é descrito na patente US 6.904.273 para Steber e outros, intitulada "Method and System for Automatic Gain Control in a Satellite Communications System", cuja totalidade está incorporada a este documento pela referência.

25 Mas, mesmo onde o demodulador executa a equalização antes de recuperação de sincronismo de quadro e recuperação de portadora, a computação de erro ainda acontece após a recuperação de portadora, o que tipicamente resulta na introdução de um atraso arbitrário entre as amostras de 30 entrada e as amostras de erro. Assim, existe uma

necessidade de sincronizar as amostras de dados e amostras de erro em relação à equalização dos sinais de dados de entrada tal como para tal atraso arbitrário, particularmente para transmissão de dados de modo contínuo, 5 assim como para transmissão de dados intermitente, ou de rajadas, no modo de rajadas de transmissão de dados. E, portanto, existe uma necessidade de métodos e aparelho de demodulação, tais como, por exemplo, com filtragem adaptativa de Mínimos Médios Quadrados (LMS), que aborda as 10 amostras de dados de entrada e amostras de erro sendo sincronizadas de forma apropriada, em virtude de um atraso arbitrário introduzido ao processar sinais de dados, tal como onde um demodulador executa a equalização antes de recuperação de sincronismo de quadro e recuperação de 15 portadora, particularmente em um modo contínuo de transmissão de dados.

Sistemas atuais, portanto, podem falhar para suportar, neste aspecto, serviços de banda larga eficientes, robustos, confiáveis e flexíveis, em tais ambientes de rede 20 de largura de banda compartilhada, utilizando tais sistemas de satélite de altas capacidades. Alcançar serviços de banda larga eficientes, robustos, flexíveis e rápidos em uma rede de sistema de satélite de largura de banda compartilhada de alta capacidade como esta, portanto, pode 25 propor desafios exclusivos para projetistas e operadores de sistemas.

Desta maneira, existe uma necessidade de métodos e aparelho com custo reduzido para equalizar os sinais de dados de banda larga de entrada para compensar variações de 30 amplitude e de fase na parte de demodulador/modem do

receptor em uma dada largura de banda quando sinais são introduzidos para recepção e processamento, particularmente em um modo contínuo de transmissão de dados, que promovam aumento de precisão ao processar os sinais recebidos, 5 mantendo efetivamente um bloqueio nos sinais de dados após aquisição dos sinais para processar os dados de entrada, e minimizando degradar a precisão de estimativa de fase e de frequência para o processamento de sinal ou de dados.

Desta maneira, existe uma necessidade de um método e 10 aparelho com custo reduzido para sincronização precisa em processamento de quadros de dados transmitidos, particularmente em um modo contínuo de transmissão de dados, de uma rede de comunicações de largura de banda compartilhada de alta capacidade, tal como uma rede de 15 comunicações via satélite, ou uma rede de comunicações de computadores, que empregue uma arquitetura, aparelho e métodos dinâmicos e flexíveis para sincronizar as amostras de erro e as amostras de dados de entrada, que satisfaça várias exigências e desejos associados com serviços de 20 banda larga eficientes, robustos, confiáveis e flexíveis em uma rede de satélite de largura de banda compartilhada de alta capacidade, e que seja relativamente eficiente e automatizado a partir de um ponto de vista de gerenciamento de rede e balanceamento de carga.

25 ALGUMAS MODALIDADES EXEMPLARES

A presente invenção diz respeito a métodos e aparelho para fornecer equalização adaptativa com custo reduzido de 30 sinais de dados, tal como em uma parte de demodulador/modem do terminal de satélite ou de um receptor, em uma rede de comunicações via satélite, para mitigar os efeitos de não

linearidades de amplitude e de fase contidas na seção de demodulação do terminal de satélite, tal como em um demodulador de Sistema em um Chip (SoC) e, mais particularmente, para aprimorar a precisão de desempenho de 5 detecção de Texto Exclusivo (UW) para recuperação de sincronismo de quadro e estimativa de fase e de frequência para recuperação de portadora dos sinais de dados transmitidos, particularmente em um modo contínuo de transmissão de dados ou de sinal, assim como em um modo de 10 rajadas, isto é, de forma intermitente, de transmissão de dados ou de sinal.

De acordo com as modalidades exemplares, os aspectos da presente invenção dizem respeito a um aparelho para fornecer equalização adaptativa de um canal receptor de um 15 sistema de comunicações que recebe sinais de dados em um modo contínuo, ou em um modo de rajadas, de transmissão de dados, tal como um terminal de satélite de um sistema de comunicações via satélite, e para compensar e ajustar para um atraso arbitrário resultando de processamento de sinal 20 ou de dados. Adicionalmente, de acordo com as modalidades exemplares, reaquisição de sincronismo de quadro pode ser capacitada, tal como onde o sinal recebido de dados ou fluxo de dados é interrompido ou corrompido temporariamente, assim como aprimorando a capacidade do 25 equalizador para criar novamente seus coeficientes, tal como entre períodos de serviço contínuo, por exemplo. Aspectos da invenção também promovem aprimoramento de estimativa de fase e de frequência em uma rede de comunicações de alta capacidade ao sincronizar amostras de 30 erro e amostras de dados dos dados de entrada, assim para

aprimorar estimativa de fase e de frequência de ajuste para recuperação de portadora e recuperação de sincronismo de quadro, tal como em rede de largura de banda compartilhada para processamento de sinal ou de dados, tal como, por 5 exemplo, em um sistema de comunicações de rede de satélite.

De acordo com as modalidades e aspectos exemplares da invenção, o aparelho compreende um demodulador para um sistema de comunicações, o demodulador compreendendo um circuito receptor para receber um fluxo de dados de entrada 10 transmitido em um sistema de comunicações, o fluxo de dados de entrada compreendendo quadros de dados de entrada, um circuito processador de sincronismo de quadro para gerar sinais de controle de sincronização de regulação de tempo de quadro, os sinais de controle de sincronização de 15 regulação de tempo de quadro para gravar os quadros dos dados de entrada para armazenamento, um circuito de sincronização de portadora para gerar sinais de controle de erro de sincronismo correspondendo a um atraso de processamento para os dados de entrada, e um circuito de 20 armazenamento temporário para receber os dados de entrada do receptor, para armazenar os dados de entrada em resposta aos sinais de controle de sincronização de regulação de tempo de quadro e para sincronizar uma leitura dos dados de entrada armazenados com base em uma diferença de 25 sincronismo entre os sinais de controle de erro de sincronismo e os sinais de controle de sincronização de regulação de tempo de quadro para ajustar para um atraso arbitrário ao processar os dados de entrada.

De acordo com as modalidades e aspectos exemplares da 30 invenção, um aparelho para processar dados de entrada, tal

como por demodulação, inclui adicionalmente um circuito de atualização de gradiente de derivação para gerar um gradiente de derivação para corresponder aos dados lidos ao processar os dados de entrada, com base em sinais de erro de equalizador para ajustar o gradiente de derivação gerado pelo circuito de sincronização de portadora.

De acordo com as modalidades exemplares, o sistema de comunicações compreende uma rede de comunicações de largura de banda compartilhada de alta capacidade, tal como uma rede de comunicações via satélite ou uma rede de comunicações de computadores, por exemplo.

De acordo com as modalidades exemplares, em um aparelho para processar sinais de dados transmitidos em um sistema de comunicações, o demodulador compreende um demodulador (por exemplo, um demodulador do tipo DVB-S2), o circuito de filtro compreende um Filtro Equalizador de Resposta Finita ao Impulso (FIR), o circuito processador de sincronismo de quadro compreende um processador de Texto Exclusivo (UWP), o circuito de sincronização de portadora compreende um Módulo de Sincronização de Portadora (CSM), o circuito de armazenamento temporário compreende um Armazenamento Temporário de Equalizador, e o circuito de atualização de derivação compreende um circuito de Atualização de Derivação de Mínimos Médios Quadrados (LMS).

Também, o circuito receptor compreende um circuito de Processamento de Sinal de Lado Cliente e um Filtro Raiz de Cosseno Elevado (RRC).

De acordo com as modalidades exemplares, um aparelho, de acordo com aspectos da invenção, recebe e processa os sinais de dados de entrada em um formato paralelo.

Adicionalmente, de acordo com aspectos da invenção, o aparelho recebe e processa os sinais de dados de entrada ao decompor, ou formatar, os sinais de dados de entrada em uma pluralidade de segmentos de dados, tais como dois ou mais 5 segmentos de dados, para processamento de sinal em um modo contínuo, ou em um modo de rajadas, de transmissão de sinal de dados.

De acordo com as modalidades e aspectos exemplares da invenção, o circuito de armazenamento temporário, 10 armazenamento temporário ou o armazenamento temporário de equalizador tipicamente inclui uma capacidade de armazenamento de dados predeterminada suficiente para armazenar dados de entrada correspondendo a um atraso arbitrário máximo entre as amostras de dados de entrada e 15 as amostras de erro resultando do processamento da entrada.

Também, de acordo com as modalidades e aspectos exemplares da invenção, uma faixa do atraso arbitrário variável tipicamente acomodada pelo armazenamento temporário de equalizador, armazenamento temporário ou circuito de 20 armazenamento temporário tipicamente está entre 1 mega símbolos por segundo a 225 mega símbolos por segundo, tal como para a um sistema de comunicações via satélite, por exemplo.

Também, de acordo com as modalidades e aspectos 25 exemplares da invenção, um aparelho para receber e processar um fluxo de dados de entrada compreende um receptor para receber um fluxo de dados de entrada transmitido em um sistema de comunicações, o fluxo de dados de entrada compreendendo quadros de dados de entrada, um 30 armazenamento temporário para armazenar os dados de

entrada, e conjunto de circuitos de processamento para gerar sinais de controle de sincronização de regulação de tempo de quadro para gravar os quadros dos dados de entrada para armazenamento no armazenamento temporário, para gerar 5 sinais de controle de erro de sincronismo correspondendo a um atraso de processamento para os dados de entrada, e para sincronizar uma leitura dos dados de entrada armazenados pelo armazenamento temporário com base em uma diferença de sincronismo entre os sinais de controle de erro de sincronismo e os sinais de controle de sincronização de regulação de tempo de quadro para ajustar para um atraso 10 arbitrário ao processar os dados de entrada.

De acordo com as modalidades e aspectos exemplares da invenção, o aparelho compreende adicionalmente um circuito 15 de atualização de gradiente de derivação para gerar um gradiente de derivação para corresponder aos dados lidos ao processar os dados de entrada, com base em sinais de erro de equalizador para ajustar o gradiente de derivação gerado pelo conjunto de circuitos de processamento.

20 De acordo com as modalidades e aspectos exemplares da invenção, os sinais de controle de erro de sincronismo compreendem um ou mais de sinais de controle de sincronização de regulação de tempo de quadro de erro ajustado e sinais de controle válidos de erro ajustado para 25 sincronizar amostras de erro correspondendo às amostras de dados de entrada para sincronização de regulação de tempo de quadro para ajustar para o atraso arbitrário ao processar os dados de entrada.

De acordo com as modalidades e aspectos exemplares da 30 invenção, o conjunto de circuitos de processamento

compreende um demodulador de Sistema em um Chip (SoC), tal como um demodulador do tipo DVB-S2 para um sistema de comunicações via satélite.

De acordo com as modalidades e aspectos exemplares da invenção, um método para receber e processar sinais de dados de entrada em um sistema de comunicações comprehende receber um fluxo de dados de entrada transmitido em um sistema de comunicações, o fluxo de dados de entrada comprehendendo quadros de dados de entrada, demodular os dados de entrada recebidos para processar os dados de entrada, em que a demodulação dos dados de entrada recebidos comprehende gerar sinais de controle de sincronização de regulação de tempo de quadro para gravar os quadros dos dados de entrada para armazenamento, armazenar os dados de entrada com base nos sinais de controle de sincronização de regulação de tempo de quadro gerados, gerar sinais de controle de erro de sincronismo correspondendo a um atraso de processamento para os dados de entrada, e sincronizar uma leitura dos dados de entrada armazenados com base em uma diferença de sincronismo entre os sinais de controle de erro de sincronismo e os sinais de controle de sincronização de regulação de tempo de quadro para ajustar para um atraso arbitrário ao processar os dados de entrada.

De acordo com as modalidades e aspectos exemplares da invenção, um método comprehende adicionalmente os sinais de controle de erro de sincronismo comprehendendo um ou mais de sinais de controle de sincronização de regulação de tempo de quadro de erro ajustado e sinais de controle válidos de erro ajustado para sincronizar amostras de erro

correspondendo às amostras de dados de entrada para sincronização de regulação de tempo de quadro para ajustar para o atraso arbitrário ao processar os dados de entrada.

De acordo com uma outra modalidade exemplar, um método 5 também compreende gerar sinais de erro de equalizador para ajustar um gradiente de derivação para corresponder aos dados lidos ao processar os dados de entrada.

De acordo com uma modalidade exemplar adicional, um método também compreende demodular os dados de entrada 10 recebidos em um formato paralelizado. Adicionalmente, de acordo com aspectos da invenção, a demodulação compreende processar os dados de entrada ao decompor, ou formatar, os sinais de dados de entrada em uma pluralidade de segmentos de dados, tais como dois ou mais segmentos de dados, para 15 processamento de sinal em um modo contínuo, ou em um modo de rajadas, de transmissão de sinal de dados.

De acordo com as modalidades exemplares adicionais, o fluxo de dados de entrada para processamento, tal como por demodulação, é transmitido em um modo contínuo ou em um 20 modo de rajadas em um sistema de comunicações via satélite, ou em um sistema de comunicações de rede de computadores.

De acordo com as modalidades exemplares, um método compreende adicionalmente armazenar os dados ao permitir uma capacidade de armazenamento para considerar uma 25 quantidade máxima de atraso arbitrário no processamento de sinal de dados.

Portanto, os métodos e aparelho da invenção vantajosamente abordam as necessidades indicadas acima, assim como outras necessidades, ao fornecer uma arquitetura 30 e método dinâmicos e flexíveis para redução de erro e

desempenho melhorado em recepção de sinal em redes de satélite de largura de banda compartilhada de alta capacidade, em um modo contínuo, ou em um modo de rajadas, de transmissão de sinal de dados, o que satisfaz várias 5 exigências e desejos associados com serviços de banda larga eficientes, robustos, confiáveis e flexíveis em uma rede de comunicações de largura de banda compartilhada de alta capacidade, tal como uma rede de satélite, e que é relativamente eficiente e automatizada a partir de um ponto 10 de vista de gerenciamento de rede e balanceamento de carga. Adicionalmente, de acordo com aspectos da invenção, os métodos e aparelho da invenção vantajosamente promovem mitigação dos efeitos de não linearidades de amplitude e de fase, tais como podem ocorrer na seção de demodulação de um 15 terminal de satélite, em um modo com custo reduzido, e aprimoram processamento de sinal preciso ao ajustar para um atraso arbitrário ao processar dados de entrada. Vantagens adicionais da presente invenção se tornarão aparentes para os versados na técnica a partir da descrição detalhada a 20 seguir de modalidades e aspectos exemplares da invenção.

Ainda outros aspectos, recursos e vantagens da presente invenção estarão prontamente aparentes a partir da descrição detalhada a seguir, simplesmente ao ilustrar diversas modalidades e implementações particulares, 25 incluindo o modo considerado como o melhor para executar a presente invenção. A presente invenção também é capaz de outras e diferentes modalidades, e seus diversos detalhes podem ser modificados em vários aspectos óbvios, todos sem divergir do espírito e escopo da presente invenção. Desta 30 maneira, os desenhos e descrição são para ser considerados

como ilustrativos em natureza, e não como restritivos.

#### DESCRIÇÃO RESUMIDA DOS DESENHOS

A presente invenção está ilustrada a título de exemplo, e não a título de limitação, nas figuras dos 5 desenhos anexos e em que números de referência iguais se referem a elementos similares e em que:

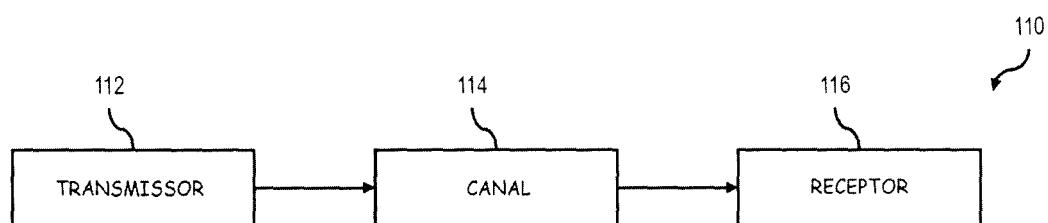

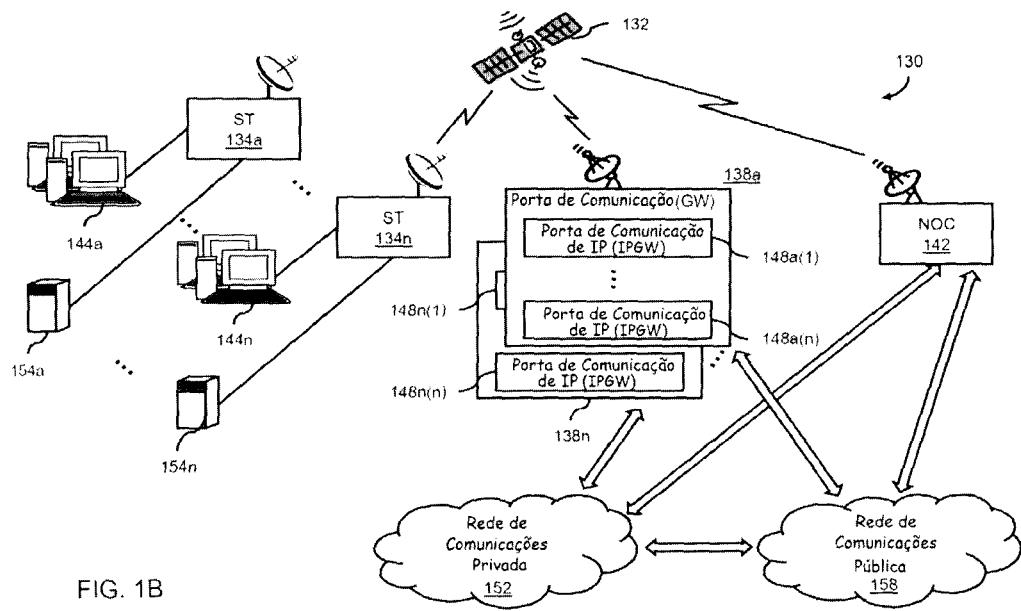

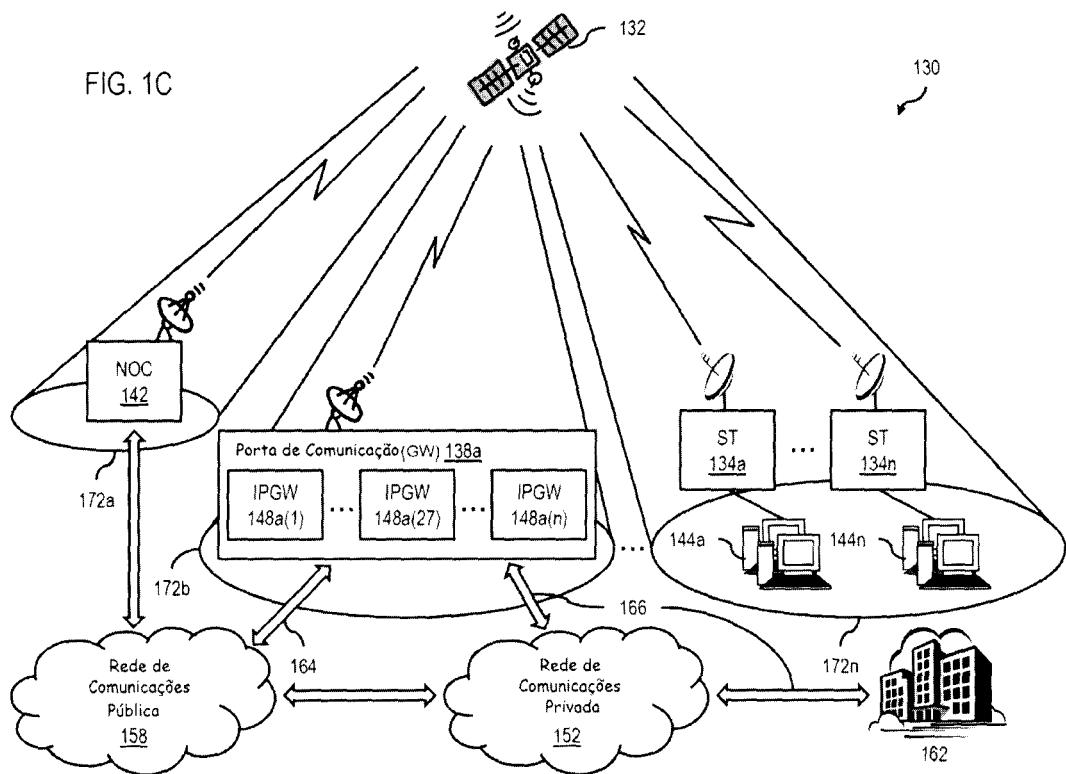

As figuras 1A, 1B e 1C ilustram sistemas de comunicações capazes de empregar um aparelho e métodos para sincronização, assim como para equalização, de acordo com 10 várias modalidades exemplares;

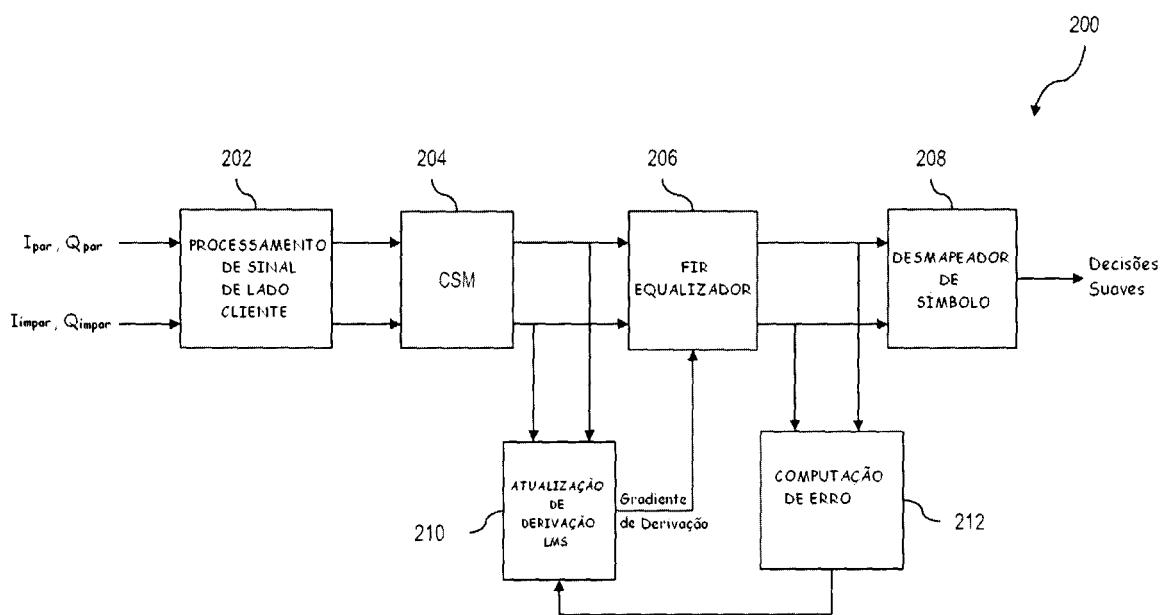

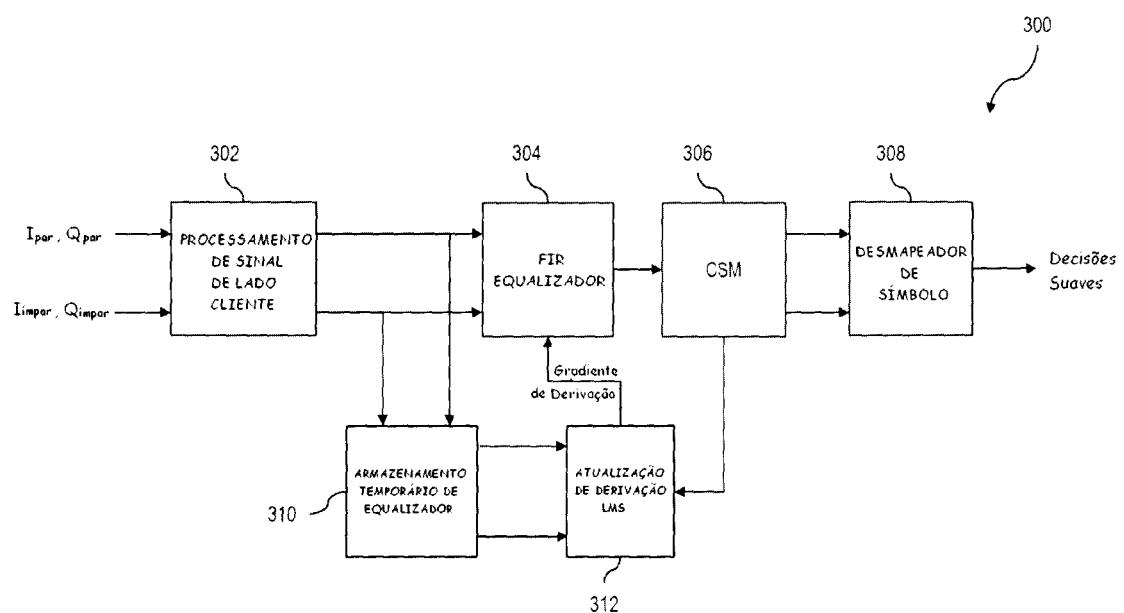

As figuras 2 e 3 ilustram diagramas de blocos de demoduladores exemplares, de acordo com as modalidades exemplares;

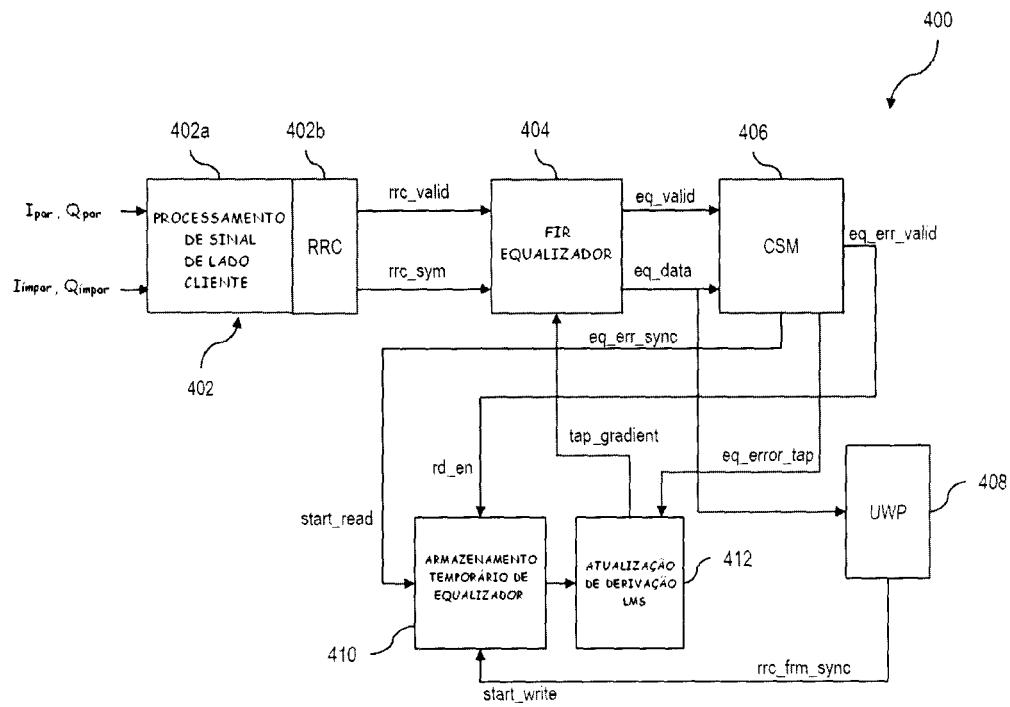

A figura 4 ilustra um diagrama de blocos de um 15 demodulador exemplar, em que o filtro equalizador fica localizado antes do módulo de sincronização de portadora, para sincronizar amostras de erro e amostras de dados para ajustar para um atraso arbitrário ao processar os dados de entrada, de acordo com as modalidades exemplares;

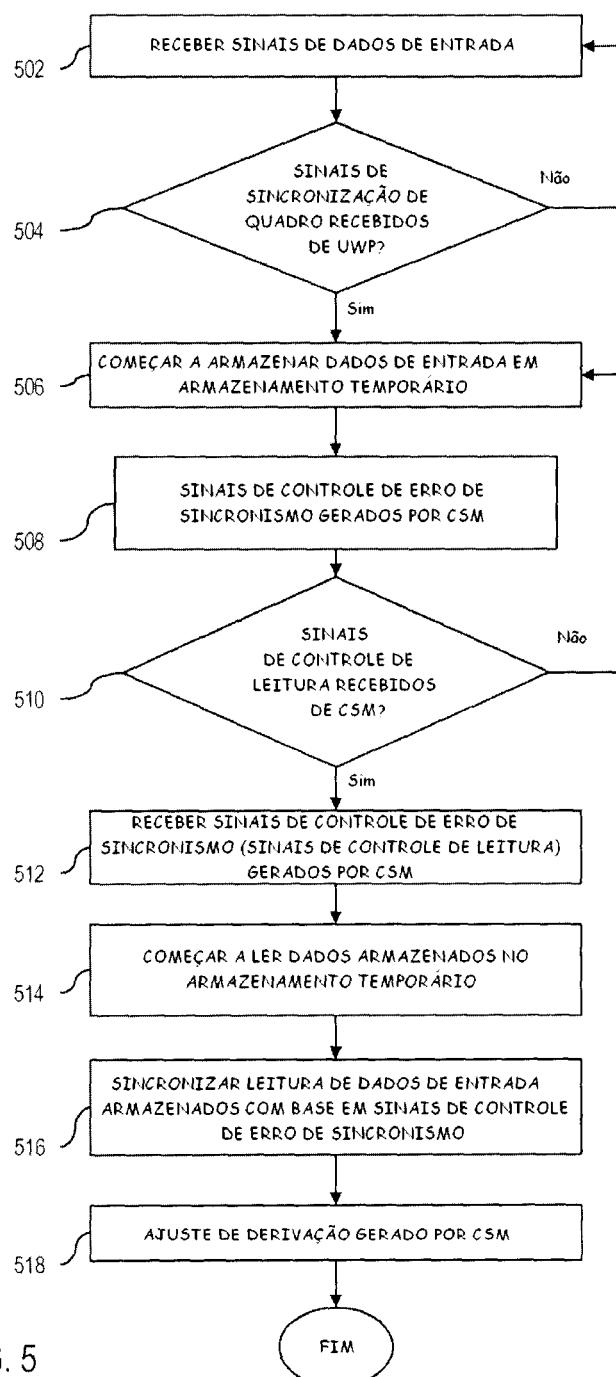

20 A figura 5 ilustra um fluxograma de um algoritmo exemplar, para sincronizar amostras de erro e amostras de dados para ajustar para um atraso arbitrário ao processar os dados de entrada, assim como para aprimorar estimativa de fase e de frequência de ajuste para recuperação de 25 portadora e recuperação de sincronismo de quadro, de acordo com as modalidades exemplares;

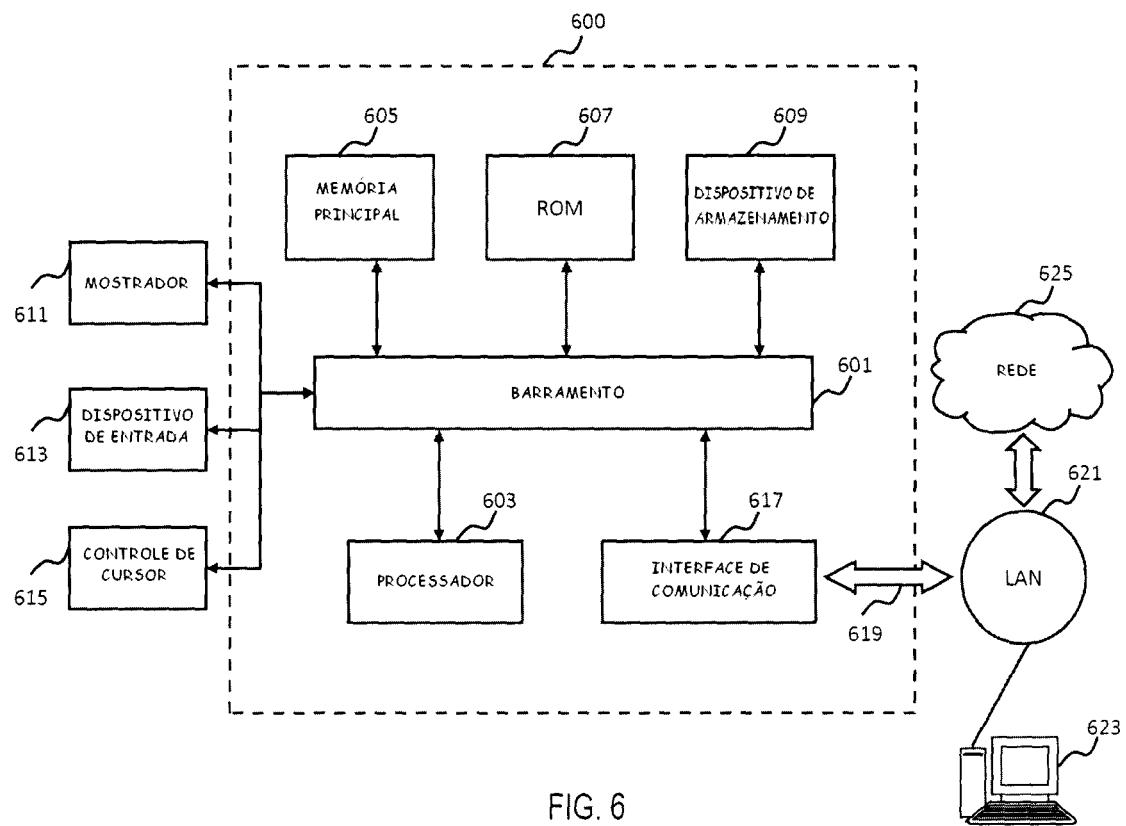

A figura 6 representa um diagrama de blocos de um sistema de computador no qual arquiteturas, aparelho e métodos podem ser implementados, de acordo com as 30 modalidades exemplares; e

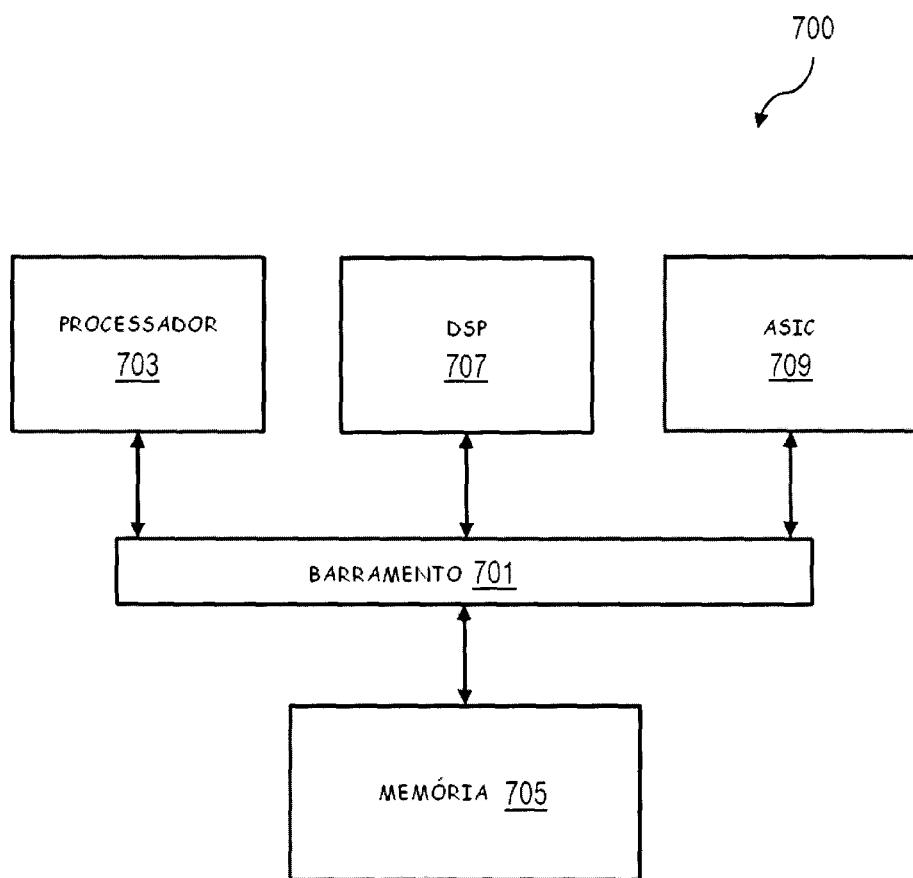

A figura 7 representa um diagrama de blocos de um conjunto de chips que pode ser utilizado ao implementar arquiteturas, aparelho e métodos, de acordo com as modalidades exemplares.

5

#### DESCRIÇÃO DETALHADA

De acordo com um aspecto da presente invenção, arquiteturas, aparelho e métodos dinâmicos e flexíveis são fornecidos que promovem equalização de sinais de dados de entrada, e que sincronizam amostras de erro e amostras de dados para ajustar para um atraso arbitrário ao processar os dados de entrada, assim como para aprimorar estimativa de fase e de frequência de ajuste para recuperação de portadora e recuperação de sincronismo de quadro, para fluxo de dados de entradas recebido em um modo contínuo, assim como em um modo de rajadas, de transmissão de sinal, tal como em um sistema de comunicações via satélite ou em um sistema de comunicações de rede de computadores, os quais satisfazem várias exigências e desejos associados com serviços de banda larga eficientes, robustos, confiáveis e flexíveis em uma rede de satélite de largura de banda compartilhada de alta capacidade, e que são relativamente eficientes e automatizados a partir de um ponto de vista de gerenciamento de rede e balanceamento de carga.

Em uma rede de largura de banda compartilhada como esta, por exemplo, onde múltiplos nós remotos acessam serviços de banda larga por meio de um ou mais nós de agregação (por exemplo, portas de comunicação), de acordo com várias modalidades exemplares, as arquiteturas, aparelho e métodos presentes promovem equalização de sinais de dados de entrada, e sincronizam amostras de erro e

amostras de dados para ajustar para um atraso arbitrário entre amostras de dados de entrada e amostras de erro ao processar os dados de entrada, assim como para aprimorar estimativa de fase e de frequência de ajuste para 5 recuperação de portadora e recuperação de sincronismo de quadro, para fluxos de dados recebidos em um modo contínuo, assim como em um modo de rajadas, de transmissão de sinal, tal como em um sistema de comunicações via satélite ou em um sistema de comunicações de rede de computadores, os 10 quais possibilitam satisfazer várias exigências e desejos relacionados com a provisão de serviços de banda larga eficientes, robustos, confiáveis e flexíveis de alta capacidade.

Por exemplo, diretriz de uso de taxa de transferência 15 e volume de transferência pode representar dois critérios de serviço quantitativos que necessitam ser satisfeitos em uma transmissão de largura de banda de alta capacidade em um sistema de comunicações. A taxa de transferência reflete a velocidade máxima (em Mbps) que um terminal é configurado 20 para sustentar na direção de recebimento da rede, para dados de usuário. A taxa de transferência pode ser baseada no plano de serviço ao qual o terminal está inscrito (por exemplo, baseada nas inscrições de serviço de usuário). O volume de uso de transferência é a quantidade de dados em 25 megabytes (MB) ou gigabytes (GB) que um terminal é configurado para receber do nó de agregação na direção de transferência antes de ter sua taxa de transferência diminuída (por exemplo, com base em uma diretriz de acesso justa do provedor de serviços). O volume de uso de 30 transferência pode ser baseado em uma opção selecionada

pelo usuário ao se inscrever em um plano de serviço. Um terminal se associa a um nó de agregação ao selecionar um nó particular (de um conjunto de nós de agregação adequados disponíveis para o terminal) para provisão dos serviços 5 exigidos para o terminal. Uma vez que o terminal completa um processo de associação de acordo com protocolos exemplares, e o nó de agregação aceita a associação, o terminal se torna associado ao nó de agregação selecionado.

De acordo com uma modalidade exemplar, uma rede de 10 largura de banda compartilhada de alta capacidade como esta transmitindo dados em um modo de transmissão contínua, ou em um de rajadas, pode compreender um sistema de comunicações via satélite de banda larga, onde múltiplos nós remotos (por exemplo, terminais de satélite (STs)) 15 acessam serviços de banda larga por meio de um ou mais nós de agregação (por exemplo, portas de comunicação (GWS) ou portas de comunicação de IP (IPGWS)). Por exemplo, diferentes STs se inscrevem para diferentes serviços, pelo que os STs se associam às respectivas IPGWS que suportam os 20 respectivos serviços do terminal. Um ST selecionaria dinamicamente uma IPGW de um conjunto elegível de IPGWS que suportam configurações e inscrições de serviço que satisfazem as exigências de serviço do ST. O ST se associa à IPGW selecionada para provisão dos serviços exigidos para 25 o terminal. Uma vez que o ST completa um processo de associação, e a IPGW aceita a associação, o terminal se torna associado à IPGW selecionada.

As figuras 1A - 1C ilustram sistemas de comunicações capazes de empregar as arquiteturas, aparelho e métodos 30 dinâmicos e flexíveis que podem ser utilizados ao

implementar a sincronização de amostras de erro e amostras de dados para ajustar para um atraso arbitrário ao processar os dados de entrada, assim como para aprimorar estimativa de fase e de frequência de ajuste para 5 recuperação de portadora e recuperação de sincronismo de quadro, ao processar sinais de dados recebidos em um modo contínuo, assim como em um modo de rajadas, de transmissão de sinal, tal como em um sistema de comunicações via satélite, de acordo com várias modalidades exemplares da 10 invenção. Com referência à figura 1A, um sistema de comunicações digitais 110 inclui um ou mais transmissores 112 (dos quais está mostrado um) que geram formas de onda de sinal por meio de um canal de comunicações 114 para um ou mais receptores 116 (dos quais está mostrado um). Neste 15 sistema de comunicações distinto 110, o transmissor 112 tem uma fonte de sinal que produz um conjunto distinto de sinais de dados, onde cada um dos sinais de dados tem uma forma de onda de sinal correspondente. Estas formas de onda de sinal são atenuadas, ou alteradas de outro modo, pelo 20 canal de comunicações 114. Para combater ruído e outras questões associadas com o canal 114, codificação pode ser utilizada. Por exemplo, códigos de correção antecipada de erros (FEC) podem ser empregados.

A figura 1B ilustra um sistema de comunicações via 25 satélite exemplar 130 capaz de suportar comunicações entre terminais com capacidades variadas, de acordo com as modalidades exemplares da invenção. O sistema de comunicações via satélite 130 inclui um satélite 132 que suporta comunicações entre os múltiplos terminais de 30 satélite (STs) 134a-134n, as diversas portas de comunicação

(GWs) 138a-138n e um centro de operações de rede (NOC) 142.

O NOC 142 executa as funções de plano de gerenciamento do

sistema 130, enquanto que as GWs 138a-138n executam as

funções de plano de dados do sistema 133. Por exemplo, o

5 NOC 142 pode executar funções tais como gerenciamento e

configuração de rede, transferências de software (por

exemplo, para os STs 134a-134n), monitoramento de status,

funções de estatística (por exemplo, coleta, agregação e

divulgação), funções de segurança (por exemplo, geração,

10 gerenciamento e distribuição de chave), registro e

autenticação de ST e gerenciamento diversidade de GW. O NOC

142 pode se comunicar com cada GW por meio do satélite 132,

ou por meio de uma rede de comunicações privada segura 152

(por exemplo, um túnel de IPsec em um enlace dedicado ou em

15 uma rede privada virtual (VPN) ou túnel de IPsec por meio

de uma rede pública, tal como a Internet). Adicionalmente,

cada GW e o NOC podem ter conectividade para uma ou mais

redes de comunicações públicas, tais como a Internet ou uma

PSTN.

20 De acordo com uma modalidade exemplar adicional, cada

uma das GWs 138a- 138n pode incluir uma ou mais portas de

comunicação (IPGWs) - pelo que as funções de plano de dados

são divididas entre uma GW e suas respectivas IPGWs. Por

exemplo, a GW 138a pode incluir as IPGWs 148a(1)-148a(n) e

25 a GW 138n pode incluir as IPGWs 148n(1)-148n(n). Uma GW

pode executar funções tais como codificação e modulação de

rota de saída de camada de enlace e de camada física (por

exemplo, codificação e modulação adaptativas de DVB-S2),

manuseio de rota de entrada de camada de enlace e de camada

30 física (por exemplo, IPOS), alocação de largura de banda de

rota de entrada e balanceamento de carga, priorização de rota de saída, aceleração de rede e compressão HTTP, controle de fluxo, criptografia, alterações de redundância e aplicação de diretriz de restrição de tráfego.

5 Considerando que a IPGW pode executar funções tais como compactação de dados, aprimoramentos de desempenho TCP (por exemplo, proxies de aprimoramento de desempenho TCP, tais como enganador TCP), qualidade de funções de serviço (por exemplo, classificação, priorização, diferenciação, 10 detecção antecipada aleatória (RED), controle de fluxo TCP/UDP), policiamento de uso de largura de banda, balanceamento de carga dinâmico e roteamento. Adicionalmente, uma GW e respectiva IPGW podem ser colocadas juntas com o NOC 142. Os STs 134a-134n podem 15 fornecer conectividade para um ou mais hospedeiros 144a-144n e/ou para os roteadores 154a-154n, respectivamente. O sistema de comunicações via satélite 130 pode operar como um sistema de canal em curva, onde o satélite opera essencialmente como um repetidor ou canal em curva. 20 Alternativamente, o sistema 130 pode empregar um satélite de comutação ou de processamento suportando comunicações de malha (comunicações ponto a ponto diretamente entre, por exemplo, os dois STs 134a e 134n).

Em um sistema de comunicações 130 que emprega um 25 satélite de processamento (por exemplo, incluindo uma operação de comutação por pacote, por exemplo, em uma camada de enlace de dados), o sistema pode suportar comunicações de difusão ponto a ponto diretas (ponto a ponto) e comunicações de multidifusão entre os STs 134a-30 134n e as GWs 138a- 138n. No caso de um satélite de

processamento, o satélite 132 decodifica o sinal recebido e determina o ST ou STs e/ou GWs de destino. O satélite 132 endereça então os dados desta maneira, codifica e modula os dados, e transmite o sinal modulado para o ST ou STs (por exemplo, o ST 134n) e/ou GWs de destino (e suas respectivas IPGWs). Um demodulador (por exemplo, um demodulador do tipo DVB-S2), de acordo com modalidades exemplares, pode ser associado com um ou mais STs (por exemplo, o ST 134n) e/ou GWs 138a-138n, em relação à equalização de sinais de dados de entrada, e em relação a sincronizar amostras de erro e amostras de dados para ajustar para um atraso arbitrário entre amostras de dados de entrada e amostras de erro para os dados de entrada, assim como para aprimorar estimativa de fase e de frequência de ajuste para recuperação de portadora e recuperação de sincronismo de quadro, ao processar sinais de dados recebidos em um modo contínuo, assim como em um modo de rajadas, de transmissão de sinal de dados, de acordo com as modalidades e aspectos exemplares da invenção. De acordo com as modalidades exemplares, o sistema 130 fornece assim uma arquitetura inteiramente em malha, pela qual os STs 134a-134n podem se comunicar diretamente, por meio de um único salto, através do satélite 132.

Em um sistema de canal em curva de uma modalidade exemplar, o satélite 132 opera como um repetidor ou canal em curva e comunicações para e a partir dos STs 134a-134n são transmitidas por meio do satélite 132 para e a partir de respectivas IPGWs associadas com STs particulares. Adicionalmente, em um sistema de feixes pontuais, qualquer feixe pontual (por exemplo, os feixes 172a-172n) opera como

um canal em curva para a região geográfica coberta pelo feixe. Por exemplo, cada feixe pontual opera como um canal de comunicações em curva para e a partir dos STs e/ou IPGW(s) dentro da região geográfica coberta pelo feixe.

5   Também, por exemplo, diversas GWs/IPGWs são distribuídas através da região geográfica coberta por todos os feixes pontuais do satélite 132, onde, em um feixe em que uma GW (e respectivas IPGWs) fica localizada, somente a uma GW (e nenhum ST) ocupa esse feixe. Adicionalmente, cada IPGW pode

10 servir como um nó de agregação para uma multiplicidade de nós remotos ou STs. O número total de GWs/IPGWs e a distribuição geográfica das GWs/IPGWs dependem de diversos fatores, tais como a capacidade total do satélite dedicado para tráfego de dados, carga de tráfego geográfica do

15 sistema (por exemplo, baseada em densidades de população e a distribuição geográfica dos STs), localizações de centros de dados terrestres disponíveis (por exemplo, troncos de dados terrestres para acesso a redes dedicadas públicas e privadas).

20   Mais especificamente, com referência à figura 1C, por exemplo, para uma comunicação de dados do ST 134a para uma rede de comunicações pública 158 (por exemplo, a Internet), o ST 134a pode ser associado a uma IPGW (por exemplo, IPGW 148a(1) - selecionada de um conjunto de IPGWs disponíveis para o ST 134a, tais como as IPGWs 148a(1)-148a(27) - onde o conjunto de IPGWs é um subconjunto adequado das IPGWs 148a(1)-148a(n) localizadas na GW 138a). Tais STs ou GWs podem ser associados a demoduladores (por exemplo, um Demodulador do tipo DVB-S2), de acordo com as modalidades

25 exemplares, em relação à equalização de sinais de dados de

30

entrada, e em relação a sincronizar amostras de erro e amostras de dados para ajustar para um atraso arbitrário entre amostras de dados de entrada e amostras de erro para os dados de entrada, assim como para aprimorar estimativa 5 de fase e de frequência de ajuste para recuperação de portadora e recuperação de sincronismo de quadro, ao processar sinais de dados recebidos em um modo contínuo, assim como em um modo de rajadas, de transmissão de sinal, de acordo com as modalidades e aspectos exemplares da 10 invenção. Os dados são primeiro transmitidos, por meio do satélite 132, do ST 134a para a IPGW associada 148a(1). A IPGW 148a(1) determina o destino como sendo a Internet 158. A IPGW então empacota novamente os dados (por exemplo, como uma comunicação TCP/IP), e encaminha a comunicação de 15 dados, por meio do enlace terrestre 164, para a Internet 158. Adicionalmente, em uma rede corporativa, por exemplo, uma corporação pode posicionar vários STs remotos em escritórios remotos. Mais especificamente, o ST 134n, localizado em uma localização remota de corporação, pode 20 desejar se comunicar de forma segura com a matriz 162. Desta maneira, para uma comunicação de dados do ST 134n para a matriz 162, os dados são primeiro transmitidos, por meio do satélite 132, do ST 134n para uma IPGW associada ao ST 134n (por exemplo, a IPGW 148a(27)). A IPGW 148a(27) 25 determina o destino como sendo a matriz 162. A IPGW então empacota novamente os dados (por exemplo, como uma comunicação IPseg), e encaminha a comunicação de dados IPseg, por meio dos enlaces terrestres seguros 166 (pela rede privada 152), para a matriz 162. No cenário de rede 30 corporativa, um exemplo adicional pode envolver uma

comunicação de corporação da matriz para um número de sítios remotos (por exemplo, uma comunicação de multidifusão para os STs 134a-134n) - onde os STs 134a-134n estão associados correspondente mente com as duas IPGWs 5 148a(1) e 148a(27) (por exemplo, agrupadas entre as duas IPGWs com base em balanceamento de carga e capacidades IPGW). Neste cenário, uma porta de comunicação ou roteador, dentro da rede local da matriz 162, transmite a comunicação de dados, por meio dos enlaces terrestres seguros 166 (pela rede privada 152), para as IPGWs 148a(1) e 148a(27). As 10 IPGWs determinam que a comunicação é destinada para os STs remotos 134a-134n, e empacota os dados como uma comunicação de multidifusão endereçada para a comunidade dos STs 134a-134n. As IPGWs transmitem então a comunicação de dados, por 15 meio do satélite 132, para decodificação pela comunidade dos STs 134a-134n. Desta maneira, o satélite 132 de um sistema como este age como um canal em curva ou repetidor, transmitindo comunicações entre os STs 134a-134n e suas respectivas IPGWs associadas 148a-148n.

20       Também, por exemplo, os terminais são configurados com informação com relação a qual serviço eles recebem. Para este propósito, esta informação é denominada coletivamente de Informação de Parâmetro de Serviço. A Informação de Parâmetro de Serviço pode incluir, por exemplo: um 25 identificador indicando a taxa de transferência que o terminal deve ser capaz de receber; um identificador indicando os volumes de uso de transferências por prioridade que o terminal deve ser capaz de receber; um ou mais identificadores indicando vários serviços que o 30 terminal pode receber, tais como, Voz sobre IP, Fluxo

Continuo de Vídeo, Videoconferência, Serviços IP de Multidifusão, uma sub-rede IPv4IPv6 estática, se o terminal está inscrito para um plano IPv4/IPv6 estático. Um terminal pode usar tal informação de configuração para casamento com 5 as capacidades sendo relatadas pelas IPGWs no fluxo de rota de saída do terminal. Com base no recebimento de uma mensagem de multidifusão de capacidades (CMM) de uma dada IPGW, o terminal pode acrescentar essa IPGW ao conjunto de IPGWs elegíveis capazes de suportar os serviços para os 10 quais o terminal está configurado/inscrito. Isto permite que a IPGW seja selecionada por terminais para Associação. Contanto que terminais recebam a CMM desta IPGW e o status de IPGW não indique que a IPGW não está aceitando associações, terminais podem se associar com a IPGW. Se a 15 CMM parar de ser recebida ou o status de IPGW na CMM indicar que ela não está mais em serviço, terminais removem a IPGW de seus conjuntos elegíveis e terminais já associados com a IPGW perdem suas associações com a IPGW.

Adicionalmente, por exemplo, a IPGW é configurada com 20 informação com relação aos serviços que ela suporta. Tal informação pode incluir: identificador(s) indicando a(s) taxa(s) de transferência que a IPGW suporta juntamente com a(s) taxa(s) de transferência para a(s) qual(s) o(s) identificador(s) mapeia(m); os volumes de uso de 25 transferências que a IPGW fornece; a configuração para os serviços que a IPGW fornece, tal como classificação e regras de policiamento de tráfego para serviços de voz e de vídeo, IP de multidifusão e informação de acesso condicional para serviços IP de multidifusão; e se a IPGW 30 suporta sub-redes IPv4/IPv6 estáticas e, se assim, as sub-

redes IPv4/IPv6 estáticas que ela serve. Assim que a IPGW alcança um estado operacional onde a IPGW está pronta para servir a terminais, a IPGW inicia multidifusão de uma mensagem de capacidades (CMM).

- 5 A IPGW transmite periodicamente sua mensagem de multidifusão de capacidades (CMM). A CMM indica a carga, capacidades de serviço e estado corrente da IPGW. A CMM é multidifundida de cada IPGW para cada terminal no fluxo de rota de saída no qual o tráfego de IPGWs é transmitido.

- 10 Cada IPGW multidifunde periodicamente a CMM, desde que a IPGW tenha uma chave de assinatura de serviço, esteja em um estado de serviço (por exemplo, não em um estado de manutenção) e tenha uma configuração relacionada para capacidades. Uma chave de assinatura de serviço é usada no

- 15 fornecimento de uma assinatura, a qual serve para proteger contra violação da Informação de Parâmetro de Serviço de um ST em uma tentativa para atualizar os planos de serviços do ST além daqueles planos de serviços para os quais o ST está inscrito. Embora cada IPGW envie a CMM em uma periodicidade

- 20 similar, a periodicidade é configurável, e sincronização não é exigida através de IPGWs tal como para quando elas realmente enviam a CMM. Sob certas condições (abordadas a seguir), uma IPGW pode enviar a CMM mais frequentemente do que a periodicidade padrão. Adicionalmente, cada IPGW

- 25 tipicamente tem uma configuração particular que permite a ela relatar informação de serviço (por exemplo, capacidades da IPGW) em uma mensagem (por exemplo, a CMM) para os STs. A qualquer hora que uma IPGW receba uma atualização de configuração que muda sua configuração ou capacidades de

- 30 serviços, a IPGW transmite prontamente uma nova CMM

divulgando a configuração de serviços atualizada.

Por exemplo, cada CMM pode conter uma cadeia alfanumérica servindo como um identificador lógico (ID) para a IPGW. O identificador lógico pode ser acessível para 5 um usuário do ST ou para um sistema de serviço de cliente a fim de facilitar divulgação de paradas ou problemas de serviço com relação a uma IPGW particular. A CMM também pode conter um endereço IP WAN de dados da IPGW, o qual serve como o endereço IP através do qual STs se comunicam 10 com a IPGW. A CMM também pode conter uma métrica de carga corrente, a qual indica um nível de carga relativa da IPGW comparado ao de outras IPGWs no mesmo conjunto IPGW, e um indicador de status de serviço de IPGW (por exemplo, fora 15 de serviço, degradado, operação normal). Divulgação de status a não ser normal, por exemplo, facilita menor tempo de nova associação (tal como o oposto a um término da transmissão das mensagens CMM da IPGW), e a provisão de informação para condições de transporte onde serviço pode ser degradado. A CMM também pode conter uma Etiqueta de 20 Tempo de Última Reinicialização, a qual transporta o tempo da última vez na qual a IPGW reinicializada. Desta maneira, conhecimento do tempo da última reinicialização da IPGW permitiria ao ST recuperar em um modo mais eficiente e na hora certa, tal como o oposto a esperar por um tempo limite 25 de associação. Em outras palavras, se um ST determinar que o tempo da última reinicialização de uma IPGW com a qual o ST está associado for mais recente que o tempo de associação, então a IPGW não mais reconhecerá a associação com esse ST (a associação teria sido terminada pela 30 reinicialização de IPGW). A CMM também pode conter um

Número de Sequência de Mudança, o qual reflete uma versão ou status de mudança da IPGW (por exemplo, o Número de Sequência de Mudança pode consistir de um número crescente de forma uniforme que é mudado quando informação estática dentro do CMM muda). O Número de Sequência de Mudança notifica o ST tal como para quando os campos estáticos de CMM tiverem mudado, de maneira que o ST não necessita ser carregado com analisar sintaticamente a maior parte da CMM quando campos estáticos não tiverem mudado. De acordo com uma modalidade adicional, a CMM pode incluir informação refletindo os servidores de aceleração de rede (por exemplo, servidores de rede principal PEP) disponível por meio da respectiva IPGW, juntamente com informação de carga de corrente para cada um dos servidores. Em um caso como este, os STs podem executar adicionalmente balanceamento de carga através dos servidores de aceleração de rede ao se associar com uma IPGW que forneceria acesso a um servidor de aceleração de rede adequado que não estivesse sobrecarregado.

As arquiteturas, aparelho e métodos para equalização de sinais de dados de entrada, e para sincronizar amostras de erro e amostras de dados para ajustar para um atraso arbitrário ao processar os dados de entrada, assim como para aprimorar estimativa de fase e de frequência de ajuste para recuperação de portadora e recuperação de sincronismo de quadro, ao processar sinais de dados recebidos em um modo contínuo, assim como em um modo de rajadas, de transmissão de sinal, tal como em um sistema de comunicações via satélite ou em um sistema de comunicações de rede de computadores, de acordo com as modalidades e

aspectos exemplares da invenção, podem ser implementados, pelo menos em parte, por meio de um ou mais conjuntos de chips, incluindo um ou mais processadores e memória, tal como ilustrado na figura 7 (mostrando um processador como este). O conjunto de chips 700 pode ser incorporado aos STs e/ou GWs/IPGWs, e como tal o conjunto de chips 700 fornece um dispositivo para executar várias partes dos algoritmos e protocolos descritos e ilustrados neste documento. Adicionalmente, aspectos diferentes de tais algoritmos e protocolos podem ser alocados para os componentes do conjunto de chips, tal como seria prudente com base em opções de projeto que estariam aparentes para os versados na técnica.

A figura 2 ilustra um diagrama de blocos de um demodulador 200 (por exemplo, um demodulador do tipo DVB-S2), de acordo com uma modalidade exemplar, para recebimento e processamento de sinais de dados transmitidos, onde o filtro equalizador é colocado após o módulo de sincronização de portadora gerando um atraso relativamente fixo para sincronização de amostras de erro e de dados dos dados recebidos.

Referindo-se ao diagrama de circuito do demodulador da figura 2, no demodulador 200, a equalização de canal é executada após a recuperação de portadora. Portanto, os dados de entrada,  $I_{par}$ ,  $Q_{par}$  e  $I_{ímpar}$ ,  $Q_{ímpar}$ , prosseguem através do receptor, por exemplo, o circuito de processamento de Sinal de Lado Cliente 202, para o circuito de Módulo de Sincronização de Portadora (CSM) 204. E a computação de erro é executada localmente na saída do circuito de filtro de Resposta Finita ao Impulso (FIR)

Equalizador 206 pelo circuito de computação de erro 212.

A partir do circuito de filtro FIR Equalizador 206, o erro na saída do circuito de filtro FIR Equalizador 206 é determinado pelo Circuito de Computação de Erro 212. O 5 determinado erro pelo Circuito de Computação de Erro 212 é fornecido para um Circuito de Atualização de Derivação de Mínimos Médios Quadrados (LMS) 210. O Circuito de Atualização de Derivação LMS 210 gera um gradiente de derivação com base no erro determinado na saída do circuito 10 de filtro FIR Equalizador 206, recebido do Circuito de Computação de Erro 212. O gradiente de derivação do circuito de Atualização de Derivação LMS 210 é introduzido no circuito de filtro FIR Equalizador 206 para mudar seus 15 valores de derivação para ajustar para o erro introduzido no circuito de filtro FIR Equalizador 206. Os dados de saída do circuito de filtro FIR Equalizador 206 são fornecidos para um circuito Desmapeador de Símbolo 208 para demodular os símbolos de entrada para bits de dados e também para fornecer decisões suaves.

20 Tal como observado a partir do demodulador 200 da figura 2, o circuito de filtro FIR Equalizador 206 e seu erro são localizados de uma maneira geral na mesma área no circuito do demodulador 200. Portanto, no demodulador 200 da figura 2, o atraso entre as amostras de dados de entrada 25 e as amostras de erro tipicamente é sempre o atraso de encadeamento do circuito de filtro FIR Equalizador 206. Também, a quantidade de tal atraso é um atraso relativamente fixo ou constante, tipicamente conhecido, determinado a partir do projeto do demodulador. Assim, no 30 demodulador 200 da figura 2, onde o circuito de filtro FIR

Equalizador 206 é colocado após o circuito CSM 204, tipicamente não existe um problema com referência a sincronizar as amostras de dados de entrada com as amostras de erro em que um atraso arbitrário tipicamente não está 5 presente.

A figura 3 ilustra um diagrama de blocos de um demodulador 300 (por exemplo, um demodulador do tipo DVB-S2), de acordo com uma modalidade exemplar, para 10 recebimento e processamento de sinais de dados, em um arranjo onde o filtro equalizador é colocado antes do módulo de sincronização de portadora que tipicamente gera um atraso arbitrário em processamento de sinal apresentando necessidades tais como para sincronização de amostras de erro e amostras de dados dos dados recebidos.

Referindo-se à figura 3, no demodulador 300, os dados de entrada,  $I_{\text{par}}$ ,  $Q_{\text{par}}$  e  $I_{\text{ímpar}}$ ,  $Q_{\text{ímpar}}$ , prosseguem através de um circuito receptor, o circuito de Processamento de Sinal de Lado Cliente 302, e são armazenados no circuito de Armazenamento Temporário de Equalizador 310 associado ao 20 circuito de filtro FIR Equalizador 304. O circuito de filtro FIR Equalizador 304 no demodulador 300 da figura 3 foi deslocado para antes do circuito CSM 306, ao contrário do demodulador 200 da figura 2. Como tal, o circuito CSM 306 age sobre os símbolos equalizados de canal provenientes 25 do circuito de filtro FIR Equalizador 304, tipicamente promovendo recuperação de portadora relativamente melhor.

Com base na saída do circuito CSM 306, do demodulador 300, correção de erro de sincronismo ocorre, pelo que um atraso arbitrário é introduzido entre as amostras de 30 entrada e as amostras de erro, resultando de processamento

de bloco por bloco dentro do circuito CSM 306. Neste aspecto, no demodulador 300 da figura 3, o erro surge após o circuito CSM 306, e existe um atraso arbitrário a partir de onde o erro surge e quando as amostras de dados de 5 entrada entram no lado de entrada do circuito de filtro FIR Equalizador 304. Tal atraso arbitrário tipicamente afeta a sincronização entre as amostras de erro e as amostras de dados de entrada. Ao contrário do atraso fixo e conhecido do demodulador 200 da figura 2, este atraso de 10 processamento do circuito CSM 306 é arbitrário e tipicamente depende de um ou mais de a taxa de símbolos, o comprimento do quadro e presença de piloto, por exemplo. Presença de piloto resulta de um símbolo piloto sendo inserido no fluxo de dados, onde em um modo "sem piloto" os 15 dados são transmitidos costa a costa, e em um modo "com piloto" um símbolo conhecido especial é inserido entre grupos ou amostras de dados no fluxo de dados transmitidos, tal como para indicar grupos de dados ou para sincronismo, por exemplo.

20 Na derivação no demodulador 200 na figura 2, ao contrário do demodulador 300 na figura 3 e ao contrário do demodulador 400 na figura 4, a taxa de símbolos no demodulador 200 é constante e um atraso conhecido ocorre que de forma típica é exatamente erro de deslocamento 25 baseado no atraso conhecido. Onde o atraso não é constante, entretanto, tal como nos demoduladores 300 e 400 nas figuras 3 e 4, as amostras de dados de entrada têm que ser alinhadas com as amostras de erro correspondentes a fim de determinar a atualização de derivação. Embora o Circuito de 30 Atualização de Derivação LMS 312 no demodulador 300 da

figura 3 gera um gradiente de Derivação para o Filtro FIR Equalizador 304 para mudar seus valores de Derivação para ajustar para o erro introduzido pela informação de erro fornecida pelo CMS circuito 306, o gradiente de derivação gerado no demodulador 300 não leva em consideração de forma relativamente efetiva o atraso arbitrário resultando de processamento no circuito CSM 306.

Portanto, no processamento de sinal no demodulador 300 da figura 3, as amostras de dados de entrada não são sincronizadas de forma apropriada com as amostras de erro, resultando tipicamente em redução de desempenho. E quando os blocos de dados armazenados no Armazenamento Temporário de Equalizador 310 por alguma quantidade de tempo são então processados, erros tipicamente podem resultar no processamento em virtude de atraso arbitrário em processamento introduzido pelo circuito CSM 306. Tal atraso arbitrário do circuito CSM 306 também pode afetar o circuito Desmapeador de Símbolo 308 para demodular os símbolos de entrada para bits de dados, assim como pode afetar fornecer decisões suaves do circuito Desmapeador de Símbolo 308.

Métodos e aparelho exemplares, de acordo com aspectos da invenção, serão descritos agora com referência às figuras 4 e 5 tal como para promover equalização de sinais de dados de entrada, e sincronizar amostras de erro e amostras de dados para ajustar para um atraso arbitrário ao processar os dados de entrada, assim como para aprimorar estimativa de fase e de frequência de ajuste para recuperação de portadora e recuperação de sincronismo de quadro, ao processar sinais de dados recebidos em um modo

continuo, assim como em um modo de rajadas, de transmissão de sinal de dados. Também, os métodos, aparelho e aspectos exemplares da invenção, tais como ilustrados e descritos com relação às figuras 4 e 5, podem ser implementados em 5 combinação, por exemplo, com o conjunto de chips 700, incluindo o processador 703 e a memória 705, ou pelo sistema de computador 600, incluindo o processador 603 e a memória principal 605, incorporada ao demodulador 400 ou usada com ele, por exemplo.

10 Tal como está evidente, uma pessoa de conhecimento comum na técnica perceberia vários detalhes e funcionalidade de implementação de projeto para os demodulador exemplares 200, 300 e 400, tais como ilustrados nas figuras 2-4. Entretanto, tal como para os recursos, 15 funções, elementos e aspectos inéditos adicionais da invenção descrito e ilustrados nas modalidades exemplares neste documento, tal como com relação ao demodulador exemplar 400 da figura 4 e ao processo de fluxo exemplar da figura 5, tais aspectos inéditos da invenção podem ser 20 implementados com o conhecimento e guia da revelação neste documento em virtude dos projetos e funções de uma maneira geral conhecidos de tais demoduladores. Por exemplo, uma equação exemplar para os módulos de Filtro FIR Equalizador das figuras 2, 3 e 4 pode ser  $y(n) = w^H(n) * u(n)$ , uma 25 equação exemplar para o sinal de erro para a Atualização de Derivação LMS das figuras 2, 3 e 4 pode ser  $e(n) = d(n) - y(n)$  (onde  $d(n)$  reflete o atraso), e uma equação exemplar para os módulos de Atualização de Derivação LMS das figuras 2, 3 e 4 pode ser  $\hat{w}(n+1) = \hat{w}(n) - \mu * u(n) * e^*(n)$ .

30 A figura 4 ilustra um diagrama de blocos de um

demodulador exemplar 400 (por exemplo, um demodulador do tipo DVB-S2), de acordo com uma modalidade exemplar, configurado de modo em que o filtro equalizador é colocado antes do Módulo de Sincronização de Portadora, o que 5 tipicamente resulta em um atraso arbitrário ao processar os dados de entrada e que, de acordo com aspectos da invenção, o demodulador exemplar 400 sincroniza amostras de erro e de dados dos dados de entrada recebidos para ajustar para o atraso arbitrário ao processar os dados de entrada, de 10 acordo com as modalidades e aspectos exemplares da invenção.

A figura 5 ilustra um fluxograma de um processo para equalização de sinais de dados de entrada, e para sincronizar amostras de erro e amostras de dados para 15 ajustar para um atraso arbitrário em processamento para os dados de entrada, assim como para aprimorar estimativa de fase e de frequência de ajuste para recuperação de portadora e recuperação de sincronismo de quadro, ao processar sinais de dados recebidos em um modo contínuo ou 20 em um modo de rajadas, de acordo com as modalidades exemplares.

Referindo-se às figuras 4 e 5, de acordo com as modalidades exemplares, o demodulador 400 (por exemplo, um demodulador do tipo DVB-S2) facilita sincronização entre as 25 amostras de dados de entrada e amostras de erro com um atraso arbitrário em processamento entre elas. O demodulador 400 recebe e processos sinais de dados,  $I_{par}$ ,  $Q_{par}$  e  $I_{impar}$ ,  $Q_{impar}$ , recebidos em um modo contínuo, ou em um modo de rajadas, de transmissão de sinal, tal como de um 30 satélite ou de uma porta de comunicação GW associada com

satélite, tal como em um formato paralelizado, tal como ilustrado na figura 4. Também, de acordo com aspectos da invenção, os dados recebidos no fluxo de dados podem ser transmitidos em um modo "com piloto" ou em um "sem piloto", 5 por exemplo. Embora um formato paralelizado esteja ilustrado para a transmissão e recepção de dados na figura 4, o sinal de dados de entrada pode ser decomposto adicionalmente em uma pluralidade de segmentos maior que dois (2), e o conjunto de circuitos dentro do demodulador 10 400 pode ser modificado desta maneira para processar tais múltiplos segmentos de dados, de acordo com aspectos da invenção.

Continuando com referência às figuras 4 e 5, o processo estando na etapa 502 onde sinais de dados de entrada são recebidos pelo demodulador 400 como um fluxo de dados de entrada transmitido em um sistema de comunicações, 15 o fluxo de dados de entrada incluindo quadros de dados de entrada. O demodulador 400 inclui um receptor ou circuito receptor 402 para receber sinais de dados de entrada, tal como incluindo um circuito de processamento de Sinal de 20 Lado Cliente 402a e um circuito de Filtro Raiz de Cosseno Elevado (RRC) 402b, para executar filtragem casada nos dados de entrada recebidos. O circuito receptor 402 gera 25 sinais de controle de pulsos *rrc\_valid* para os dados de entrada e produz símbolos correspondentes *rrc\_sym* no fluxo de dados de entrada, cujos símbolos podem representar ou transportar um ou diversos bits de dados na transmissão de dados recebida. Os sinais de pulsos de controle *rrc\_valid* indicam se os símbolos correspondentes de pulsos de dados 30 são válidos. Os sinais de controle (*rrc\_valid*) e os

símbolos correspondentes de dados (*rrc\_sym*) provenientes do circuito receptor 402 são fornecidos para o filtro ou circuito de filtro 404, tal como incluindo circuito de filtro de resposta finita ao impulso (FIR) equalizador 404.

5 O circuito receptor 402 é associado com o circuito de filtro FIR Equalizador 404. O circuito receptor 402 envia os dados e símbolos correspondentes para um armazenamento temporário, armazenamento temporário de equalizador, ou o circuito de armazenamento temporário 410, tal como incluindo um circuito de Armazenamento Temporário de Equalizador 410, para armazenar os dados de entrada. O circuito de filtro FIR Equalizador 404, por exemplo, tipicamente inclui um filtro de equalização, para filtrar os dados de entrada para ajustar os dados de entrada para 10 uma ou mais de distorções de fase e de amplitude.

15

O circuito de filtro FIR Equalizador 404 filtra os dados de entrada, e gera símbolos equalizados de canal de dados para os dados de entrada (*eq\_data*), correspondendo aos símbolos de dados do circuito de filtro FIR Equalizador 20 404, e gera sinais de controle válidos equalizados (*eq\_valid*), indicando que os símbolos equalizados de canal correspondentes de dados do circuito de filtro FIR Equalizador 404 são válidos.

Os símbolos equalizados de canal gerados de dados 25 (*eq\_data*) e os sinais de controle válidos equalizados (*eq\_valid*), provenientes do circuito de filtro FIR Equalizador 404, são introduzidos em um circuito de sincronização de portadora 406, tal como incluindo um circuito de módulo de sincronização de portadora (CSM) 406.

30 Os símbolos equalizados de canal de dados (*eq\_data*),

provenientes do circuito de filtro FIR Equalizador 404, também são fornecidos para um circuito processador de sincronização de quadro 408 (por exemplo, um módulo Processador de Texto Exclusivo (UWP)). O UWP 408 analisa os 5 dados de entrada para determinar o início de um quadro, os dados sendo divididos em quadros que são pacotes de informação, e gera os pulsos de sinal de controle de sincronização de regulação de tempo de quadro (rrc\_frm\_sync) para sincronização com os quadros dos dados 10 de entrada. O circuito UWP 408 localiza um texto exclusivo no começo de cada quadro, o qual sinaliza o início de um quadro de dados. O circuito UWP 408 gera os sinais de controle de sincronização de regulação de tempo de quadro, como deixas para o circuito de Armazenamento Temporário de 15 Equalizador 410, para indicar o início dos quadros para os dados do circuito RRC 402b do receptor 402 enviados para o circuito de Armazenamento Temporário de Equalizador 410, indicando assim para o circuito de Armazenamento Temporário de Equalizador 410 começo de salvamento dos quadros 20 correspondentes dos dados de entrada.

O circuito UWP 408 identifica o segmento de texto exclusivo dos dados de entrada recebidos, e assim sincroniza com o início do quadro de dados. O circuito UWP 408 gera então e envia sinais de controle start\_write, tais 25 como sinais de controle de sincronização de regulação de tempo de quadro, rrc\_frm\_sync (sinais de Sincronização de Quadro), para o circuito de Armazenamento Temporário de Equalizador 410 para ativar o início de armazenamento dos dados de entrada no circuito de Armazenamento Temporário de 30 Equalizador 410. Em outras palavras, mediante recebimento

dos sinais de controle `start_write` o circuito de Armazenamento Temporário de Equalizador 410 pode determinar a primeira amostra de dados correspondente, assim como amostras de dados subsequentes correspondente para 5 armazenamento no circuito de Armazenamento Temporário de Equalizador 410. Desta maneira, com referência à figura 5, o circuito de Armazenamento Temporário de Equalizador 410 do demodulador 400 continua recebendo os sinais de dados de entrada (Etapa 502), monitorando concorrentemente para 10 recebimento dos sinais de controle de sincronização de regulação de tempo de quadro, isto é, sinais `rrc_frm_sync` `start_write`, do circuito UWP 408 (Etapa 504), em cujo tempo o circuito de Armazenamento Temporário de Equalizador 410 começa a armazenar os dados de entrada no circuito de 15 Armazenamento Temporário de Equalizador 410 (Etapa 506). Se os sinais de controle de sincronismo de quadro não forem recebidos na etapa 504, o processo retorna para a Etapa 502.

Tal como mencionado anteriormente, o circuito CSM 406 20 recebe do circuito de filtro FIR Equalizador 404 os símbolos equalizados de canal de dados (`eq_data`) e os sinais de controle válidos equalizados (`eq_valid`), indicando que os símbolos equalizados de canal correspondentes de dados do circuito de filtro FIR 25 Equalizador 404 são válidos. Na etapa 508, com base nos símbolos equalizados de canal de dados (`eq_data`) e nos sinais de controle válidos equalizados (`eq_valid`) recebidos do circuito de filtro FIR Equalizador 404, o circuito CSM 406 30 gera os sinais de controle de erro de sincronismo (por exemplo, os sinais de controle de sincronização de

regulação de tempo de quadro de erro ajustado eq\_err\_sync),

o quais indicam o início de quadros para os sinais de erro

para ajustar para um atraso arbitrário ao processar as

amostras de dados de entrada para sincronizar as amostras

5 de erro e as amostras de dados para ajustar para o atraso

arbitrário entre amostras de dados de entrada e amostras de

erro para os dados de entrada, assim como para aprimorar

estimativa de fase e de frequência de ajuste para

recuperação de portadora e recuperação de sincronismo de

10 quadro.

Também, por exemplo, após o sincronismo de quadro ter

sido estabelecido, o circuito CSM 406 pode levar algum

tempo para determinar que os valores de erro necessitam

ajustar, ou corrigir, os coeficientes de equalizador, o que

15 tipicamente é função do tipo de quadro corrente dos dados

de entrada sendo processados, mas também pode ser variável.

Como tal, de acordo com aspectos da invenção, os métodos e

aparelho exemplares vantajosamente podem possibilitar a

capacidade para operar o equalizador, tal como o circuito

20 de filtro FIR Equalizador 404, mesmo quando o atraso em

processamento no circuito CSM 406 é variável. Quando o

circuito CSM 406 é contentado com determinar os valores de

erro, ele fornece, ou dá de volta, os valores de erro para

o circuito de filtro FIR Equalizador 404. O circuito de

25 filtro FIR Equalizador 404 pode então usar a informação de

erro recebida, e os dados de entrada que ele tenha

armazenado desde que o circuito UWP 408 determinou o começo

dos quadros correspondentes de dados, para então determinar

uma atualização para seus coeficientes de filtro FIR, tal

30 como por um ajuste de derivação por meio do Circuito de

Atualização de Derivação de Mínimos Médios Quadrados (LMS) 412, tal como discutido neste documento, por exemplo. De acordo com aspectos da invenção, em que o circuito CSM 412, o qual fornece os valores de erro para atualizar os 5 coeficientes de filtro FIR do circuito de filtro FIR Equalizador 404, assim como o circuito UWP 408, o qual identifica o início de quadro correspondente de dados, situados a jusante do circuito de filtro FIR Equalizador 404, qualidade de sinal melhorada do circuito de filtro FIR 10 Equalizador 404 é aprimorada e promovida, tal como onde os coeficientes do filtro FIR são mantidos atualizado, por exemplo.

Os sinais de controle de erro de sincronismo (eq\_err\_sync, pulsos de sinal de controle de sincronização de regulação de tempo de quadro de erro ajustado) indicam o 15 início de quadros para os sinais de erro. Para quadros correspondentes existe um conjunto de sinais de erro, e os pulsos de sinal de controle de sincronização de regulação de tempo de quadro de erro ajustado eq\_err\_sync 20 correspondem a uma amostra de origem para quadros de dados correspondentes. Os pulsos de sinal de controle de sincronização de regulação de tempo de quadro de erro ajustado (eq\_err\_sync) provenientes do circuito CSM 406 também são enviados para o circuito de Armazenamento 25 Temporário de Equalizador 410 como sinais de controle de início de leitura (start\_read - Sinais de Controle de Leitura), para iniciar leitura de dados de entrada correspondentes do circuito de Armazenamento Temporário de Equalizador 410. Os sinais de controle de erro de 30 sincronismo também podem incluir como sinais de Controle de

Leitura pulsos de sinal de controle válido de erro ajustado (eq\_err\_valid) que indicam sinais de controle válidos de erro de sincronismo para quadros correspondentes de dados. Os pulsos de sinal de controle válido de erro ajustado (eq\_err\_valid) também são enviados para o circuito de Armazenamento Temporário de Equalizador 410 como sinais de controle de capacitação de leitura (rd\_en) para ler dados de entrada armazenados pelo circuito de Armazenamento Temporário de Equalizador 410.

O Armazenamento Temporário de Equalizador 410 promove o armazenamento de dados de entrada suficientes para acomodação para qualquer atraso entre o sinal eq\_err\_sync e o sinal rrc\_frm\_sync do UWP. Desta maneira, o sistema não necessita considerar de outro modo o sincronismo exato do sinal eq\_err\_sync com relação ao rrc\_frm\_sync. Adicionalmente, o sinal eq\_err\_valid é qualificado com o relógio. O sinal é sempre alto em que um novo valor de erro está pronto para ser lido pelo CSM. A frequência da leitura de um novo valor de erro é dependente da razão entre a taxa de relógio e a taxa de símbolos mais alta. Em outras palavras, o sinal eq\_err\_valid é alto sempre que um valor de erro estiver disponível em um período de relógio particular. De acordo com uma modalidade, por exemplo, com uma taxa de relógio de 240 MHz e uma taxa de símbolos mais alta de 255 MHz (ou Msps), um novo valor de erro estará pronto em quase todo pulso de relógio.

De forma similar, na etapa 510, o circuito de Armazenamento Temporário de Equalizador 410, tal como em combinação com um processador associado ao demodulador 400, monitora concorrentemente para recebimento de sinais de

controle de erro de sincronismo, como sinais start\_read, ou sinais de controle de leitura, gerados por e a partir do circuito CSM 406 para ativar o inicio de leitura dos dados armazenados fora do circuito de Armazenamento Temporário de Equalizador 410. Se na etapa 510 os sinais de controle de erro de sincronismo, isto é, sinais de Controle de Leitura, forem detectados, o processo prossegue para a Etapa 512. Na Etapa 512, os sinais de controle de erro de sincronismo, isto é, sinais de Controle de Leitura, gerados pelo circuito CSM 406 são então recebidos pelo circuito de Armazenamento Temporário de Equalizador 410. A geração dos sinais de controle de erro de sincronismo pelo circuito CSM 406 capacita sincronizar uma leitura dos dados de entrada armazenados com base em uma diferença de sincronismo entre os sinais de controle de erro de sincronismo e os sinais de controle de sincronização de regulação de tempo de quadro para ajustar para um atraso arbitrário ao processar os dados de entrada, tal como introduzido pelo processamento no circuito CSM 406, por exemplo.

Se, na Etapa 512, o circuito de Armazenamento Temporário de Equalizador 410 receber os sinais de controle de erro de sincronismo gerados pelo circuito CSM 406 (na Etapa 508), o circuito de Armazenamento Temporário de Equalizador 410 na Etapa 514 começa a ler os dados armazenados pelo circuito de Armazenamento Temporário de Equalizador 410, e na Etapa 516 sincroniza a leitura dos dados de entrada armazenados com base em uma diferença de sincronismo entre os sinais de controle de erro de sincronismo recebidos do circuito CSM 406 e os sinais de controle de sincronização de regulação de tempo de quadro

recebidos do circuito UWP 408. Se, na Etapa 510, for determinado que os sinais de controle de erro de sincronismo, isto é, sinais de Controle de Leitura, não foram recebidos pelo circuito de Armazenamento Temporário de Equalizador 410, o processo retorna para a Etapa 506 para continuar a armazenar dados de entrada no circuito de Armazenamento Temporário de Equalizador 410 ou, alternativamente, para a Etapa 502 para receber sinais de dados de entrada e, dependendo de recebimento dos sinais de controle de sincronização de regulação de tempo de quadro na Etapa 504, começar a armazenar, ou não armazenar, os dados de entrada recebidos no circuito de Armazenamento Temporário de Equalizador 410, tal como descrito. Quando o circuito de Armazenamento Temporário de Equalizador 410 15 recebe os sinais de controle de erro de sincronismo, como sinais de comando de início de leitura, do circuito CSM 406, o circuito de Armazenamento Temporário de Equalizador 410 inicia a empurrar para fora, ou ler, dados do circuito de Armazenamento Temporário de Equalizador 410. Os sinais de controle válidos de erro ajustado correspondentes (eq\_err\_valid), recebidos pelo circuito de Armazenamento Temporário de Equalizador 410 provenientes do circuito CSM 20 406, indicam que os pulsos de sinal de controle de sincronização de regulação de tempo de quadro de erro ajustado (eq\_err\_sync) são válidos para os quadros de dados correspondentes, e os pulsos de sinal de controle válido de erro ajustado (eq\_err\_valid) também são sinais de controle de capacitação de leitura (rd\_en) para capacitar leitura do circuito de Armazenamento Temporário de Equalizador 410 de 25 quadros correspondentes de dados armazenados.

Portanto, os pulsos de sinal de controle de sincronização de regulação de tempo de quadro de erro ajustado gerados (eq\_err\_sync) à medida que validados pelos pulsos de sinal de controle válido de erro ajustado gerados 5 (eq\_err\_valid) são usados para ajustar para o atraso arbitrário, introduzido pelo processamento dos dados de entrada, tal como pelo processamento no circuito CSM 406, entre amostras de dados de entrada e amostras de erro para os dados de entrada, em combinação com os pulsos de sinal 10 de controle de sincronização de regulação de tempo de quadro (rrc\_frm\_sync) gerados pelo circuito UWP 408, para fornecer uma diferença de regulação de tempo para sincronização das amostras de erro e amostras de dados, assim como para aprimorar estimativa de fase e de 15 frequência de ajuste para recuperação de portadora e recuperação de sincronismo de quadro, ao processar sinais de dados recebidos em um modo contínuo, assim como em um modo de rajadas, de transmissão de sinal de dados.

Também, o ajuste para o atraso arbitrário ao processar 20 os dados de entrada, tal como resultando de processamento no circuito CSM 406, pelos pulsos de sinal de controle de sincronização de regulação de tempo de quadro de erro ajustado (eq\_err\_sync) à medida que validados pelos pulsos de sinal de controle válido de erro ajustado (eq\_err\_valid) 25 em combinação com os pulsos de sinal de controle de sincronização de regulação de tempo de quadro (rrc\_frm\_sync) capacitam o primeiro e quadros de dados subsequentes gravados no circuito de Armazenamento Temporário de Equalizador 410, para corresponder ao 30 primeiro e aos quadros de dados subsequentes que resultam

de processamento no circuito CSM 406. Portanto, de acordo com aspectos da invenção, tipicamente não importa como a quantidade do atraso arbitrário introduzido pelo processamento no circuito CSM 406, em que o primeiro e os 5 dados de entrada subsequentes gravados no circuito de Armazenamento Temporário de Equalizador 410 e os pulsos de sinal de controle de sincronização de regulação de tempo de quadro de erro ajustado (eq\_err\_sync) como uma leitura início dos quadros correspondentes de dados, será alinhada 10 para capacitar leitura de dados relativamente precisa do circuito de Armazenamento Temporário de Equalizador 410.

Entretanto, de acordo com aspectos da invenção, o circuito de Armazenamento Temporário de Equalizador 410, o qual pode incluir uma pluralidade de armazenamentos 15 temporários ou outras mídias de armazenamento, tipicamente deve ter capacidade de armazenamento suficiente para os dados recebidos para acomodar ou armazenar os dados de entrada para um atraso de pior caso, ou máximo, que possivelmente pode ocorrer pelo processamento de dados, tal 20 como pelo processamento no circuito CSM 406. De acordo com aspectos da invenção, o circuito de Armazenamento Temporário de Equalizador 410 tipicamente é pelo menos tão grande em capacidade de armazenamento quanto para acomodar tal quantidade máxima do atraso arbitrário. Mas para 25 qualquer atraso arbitrário abaixo de tal atraso máximo o circuito de Armazenamento Temporário de Equalizador 410 tipicamente deve ser capaz de manusear o armazenamento de dados para ajustar para o atraso arbitrário. Tipicamente, por exemplo, em sistemas de comunicações via satélite em um 30 modo contínuo de transmissão de dados, a faixa de atraso de