#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization

International Bureau

#

# (10) International Publication Number WO 2009/102304 A1

# (43) International Publication Date 20 August 2009 (20.08.2009)

- (51) International Patent Classification: G06F 9/00 (2006.01)

- (21) International Application Number:

PCT/US2008/002836

(22) International Filing Date:

3 March 2008 (03.03.2008)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

12/070,074 14 February 2008 (14.02.2008)

US

(71) Applicant (for all designated States except US): HEWLETT-PACKARD DEVELOPMENT COMPA-NY, L.P. [US/US]; 11445 Compaq Center Drive West, Houston, TX 77070 (US).

- (72) Inventors; and

- Inventors/Applicants (for US only): ROTH, Ron, M. [IL/IL]; 33 Ruth Street, 34404 Haifa (IL). VONTOBEL, Pascal, O. [CH/US]; 1501 Page Mill Road, Palo Alto, California 94304-1100 (US).

- (74) Agent: LEHMANN, Eileen; Hewlett-Packard Company, Intellectual Property Administration, P.O. Box 272400, M/S 35, Fort Collins, Colorado 80527-2400 (US)

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG,

[Continued on next page]

(54) Title: METHOD AND SYSTEM FOR DETECTION AND CORRECTION OF PHASED-BURST ERRORS, ERASURES, SYMBOL ERRORS, AND BIT ERRORS IN A RECEIVED SYMBOL STRING

Figure 15A

(57) Abstract: Embodiments of the present invention include ECC-based encoding-and-decoding schemes that are well suited for correcting phased bursts of errors or erasures as well as additional symbol errors and bit errors. Each encoding-and-decoding scheme that represents an embodiment of the present invention is constructed from two or more component error-correcting codes and a mapping function  $f(\cdot)$ . The composite error-correcting codes that represent embodiments of the present invention can correct longer phased bursts or a greater number of erasures in addition to single-bit errors and symbol errors, respectively, than either of the component codes alone, and are more efficient than previously developed ECC-based encoding-and-decoding schemes for correcting phased bursts of symbol errors and erasures combined with additional bit errors and symbol errors.

WO 2009/102304 A1

# WO 2009/102304 A1

- SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE,

ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, NO, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

— with international search report (Art. 21(3))

# METHOD AND SYSTEM FOR DETECTION AND CORRECTION OF PHASED-BURST ERRORS, ERASURES, SYMBOL ERRORS, AND BIT ERRORS IN A RECEIVED SYMBOL STRING

#### 5 TECHNICAL FIELD

The present invention is related to correction of errors or erasures that occur in symbol strings passed through an error-and-erasure-introducing channel, including electronic transmission of the symbol string or storage of the symbol strings in, and retrieval of the symbol strings from, an electronic memory.

10

15

20

25

30

#### BACKGROUND OF THE INVENTION

The field of error-correcting codes ("ECCs") has been well studied and researched for over 50 years. Many different types of encoding-and-decoding schemes based on error-correcting codes have been developed for application to many different problem domains. ECC-based encoding-and-decoding schemes generally involve introduction of redundant information into an encoded information stream to allow various types of errors subsequently introduced in the information stream to be detected and corrected. As with most computational techniques, there are a variety of advantages, disadvantages, efficiencies, and inefficiencies associated with any particular encoding-and-decoding scheme applied to any particular problem domain. For example, as the amount of redundant information added to an information stream increases, the quantities and types of errors that can be detected and corrected within the information stream generally increases, but the information, or space, efficiency of transmission of the information stream decreases due to the increasing overhead of the redundant information. Space inefficiencies can also result from the need to create and maintain large amounts of data needed for encoding or decoding, such as decoding tables, discussed below. As another example, a symbol efficient code may involve complex computation, and may therefore be computationally, or time, inefficient. The overall efficiency of a code is related to the sum of the space and time efficiencies of the code, but space efficiency is often obtained at the expense of time efficiency, and vice versa. Certain types of ECC-based encoding-and-decoding schemes are better suited to detecting and correcting certain types of errors, and may

2

be less well suited for detecting and correcting other types of errors. As new problem domains are recognized, or as new problem domains emerge as a result of the development of new types of technologies, continued development of new ECCs and ECC-based encoding-and-decoding schemes well suited for the newly recognized problem domains or newly developed technologies are needed in order to provide for efficient and accurate error detection and correction.

#### SUMMARY OF THE INVENTION

5

10

15

20

25

30

Embodiments of the present invention include ECC-based encoding-and-decoding schemes that are well suited for correcting phased bursts of errors or erasures as well as additional symbol errors and bit errors. Each encoding-and-decoding scheme that represents an embodiment of the present invention is constructed from two or more component error-correcting codes and a mapping function  $f(\cdot)$ . The composite error-correcting codes that represent embodiments of the present invention can correct longer phased bursts or a greater number of erasures in addition to single-bit errors and symbol errors, respectively, than either of the component codes alone, and are more efficient than previously developed ECC-based encoding-and-decoding schemes for correcting phased bursts of symbol errors and erasures combined with additional bit errors and symbol errors.

According to one embodiment of the present invention, encoding of information into a composite-code codeword is carried out by receiving  $K_I$  information symbols and encoding the  $K_I$  information symbols by a first component code  $C_1$  encoder to produce a  $C_1$  codeword  $\mathbf{u}$  of length  $N_I$  symbols. Then,  $K_2$  information symbols are encoded by a second component code  $C_2$  encoder to produce a codeword  $\mathbf{v}$  of length  $N_2$ . A vector  $\mathbf{w}$  of length  $N_2$  symbols is obtained by adding a non-identity mapping of  $\mathbf{u}$ ,  $f(\mathbf{u})$ , to  $\mathbf{v}$ . Finally, a composite-code-C codeword is generated by concatenating  $\mathbf{u}$  and  $\mathbf{w}$  together.

According to one embodiment of the present invention, decoding of a composite-code codeword is carried out by decoding component-code codewords. A component-code- $C_1$  codeword  $\mathbf{u}$  of length  $N_I$  containing  $K_I$  information symbols and

10

15

25

a modified component-code- $C_2$  codeword of length  $N_2$ ,  $\mathbf{w} = \mathbf{v} + f(\mathbf{u})$ , generated, during encoding, from a component-code- $C_2$  codeword v containing  $K_2$  information symbols, where  $K = K_1 + K_2$  and  $N = N_1 + N_2$ , and a non-identity mapping function,  $f(\cdot)$ , are extracted from a composite-code-C codeword. An estimated componentcode- $C_2$  codeword  $\hat{\mathbf{v}}$  and an estimated error word  $\hat{\mathbf{e}}$  are then generated from the modified component-code-C2 codeword by applying a C2 decoder to the modified component-code-C2 codeword. Which of a number of types of expected errors that may occur subsequent to encoding of the composite-code-C codeword is determined from the error word ê. When more than a first threshold number of erasures and erasures have occurred, but less than a second threshold number of errors have occurred, the determined errors are assigned to either the component-code-C1 codeword or to the modified component-code-C2 codeword, and when assigned to the component-code-C<sub>1</sub> codeword, are corrected. Other error and erasure occurrences are marked. An estimated component-code- $C_1$  codeword  $\hat{\mathbf{u}}$  is obtained by applying a  $C_1$ decoder to the estimated component-code- $C_1$  codeword  $\hat{\mathbf{u}}$ . Finally,  $K_I$  information symbols are extracted from the estimated component-code- $C_1$  codeword  $\hat{\mathbf{u}}$  and  $K_2$ information symbols are extracted from the estimated component-code-C2 codeword  $\hat{\mathbf{v}}$  to produce K extracted information symbols.

#### 20 BRIEF DESCRIPTION OF THE DRAWINGS

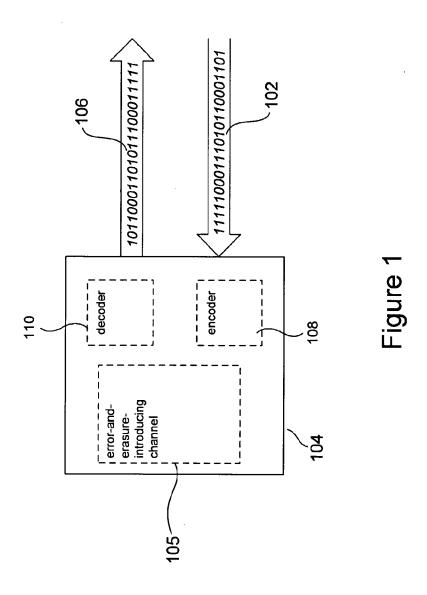

Figure 1 illustrates a basic problem to which ECC-based encodingand-decoding schemes are applied.

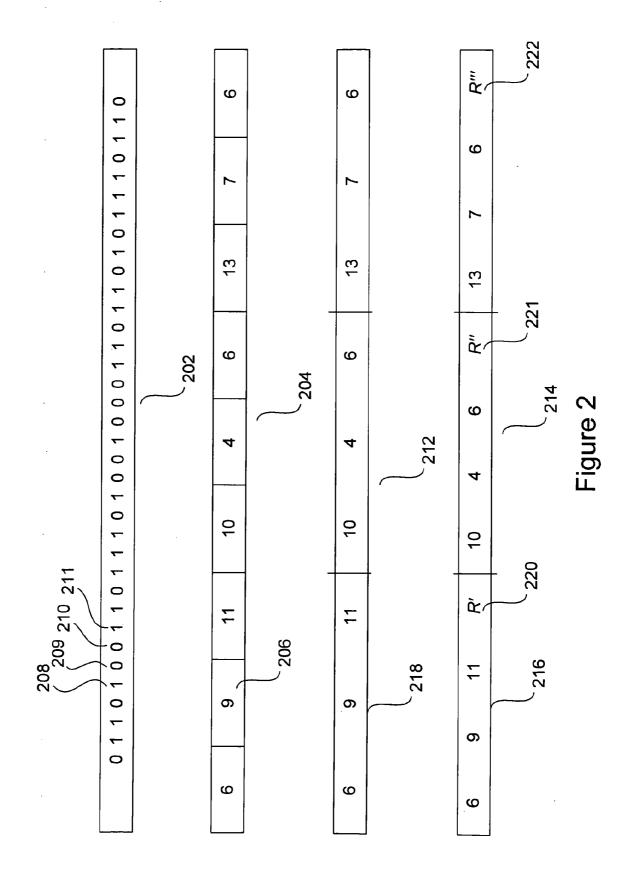

Figure 2 illustrates various different views of a digitally encoded information stream.

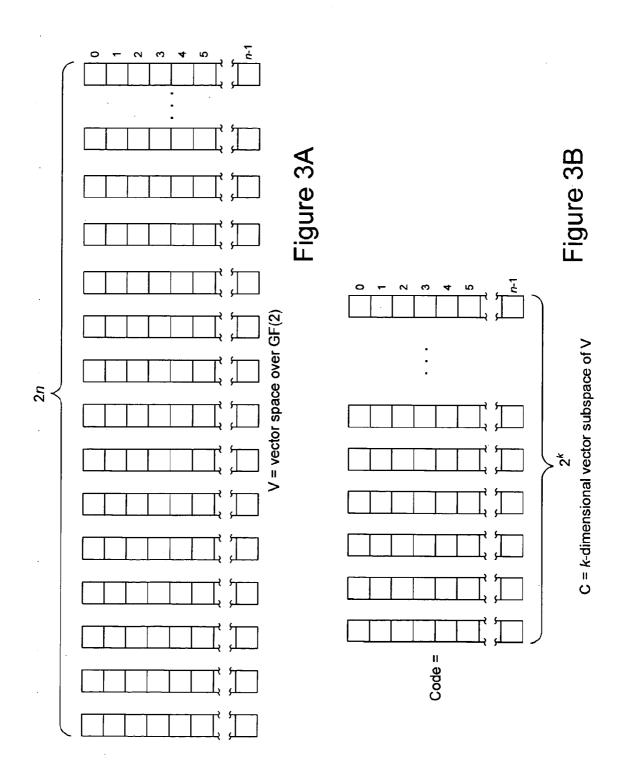

Figure 3A illustrates the vector space V of all possible codewords produced by a systematic linear block code that encodes information into codewords of length n.

Figure 3B shows an exemplary code, or vector subspace, of the vector space V shown in Figure 3A.

Figure 4 shows the distance between any two codewords v and w, D(v,w).

4

Figure 5 illustrates encoding and transmission of a vector  $\mathbf{u}$  of k information bits by a systematic linear block code.

Figure 6 illustrates encoding of the information-bit vector **u** to produce codeword **v**, as discussed with reference to Figure 5.

Figures 7A-B show an exemplary systematic generator matrix **G** and an exemplary systematic parity-check matrix **H** for a systematic linear block code.

Figure 8 shows a property of the transpose of the parity-check matrix,  $\mathbf{H}^{T}$ .

Figure 9 illustrates a portion of the decoding process for a systematic linear block code.

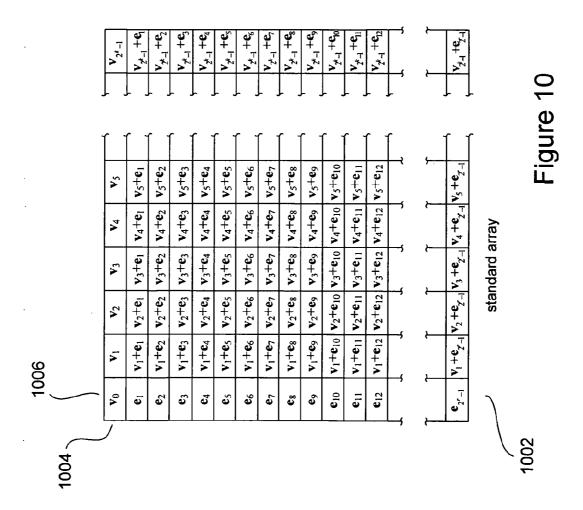

Figure 10 illustrates a decoding table that can be constructed for any systematic linear block code over GF(2).

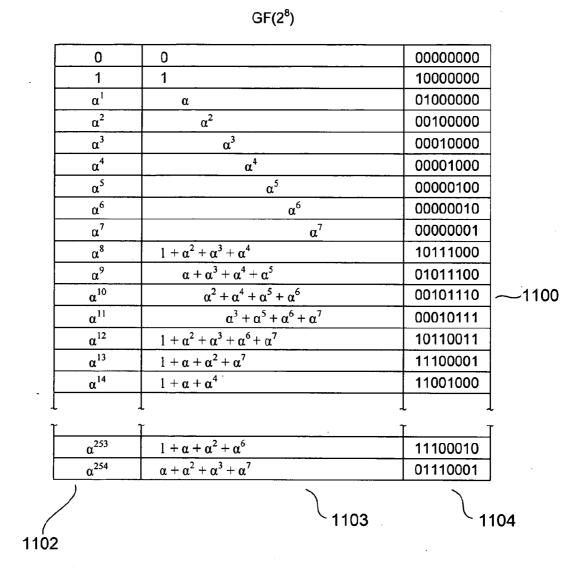

Figure 11 shows a portion of the table of elements for  $GF(2^8)$ .

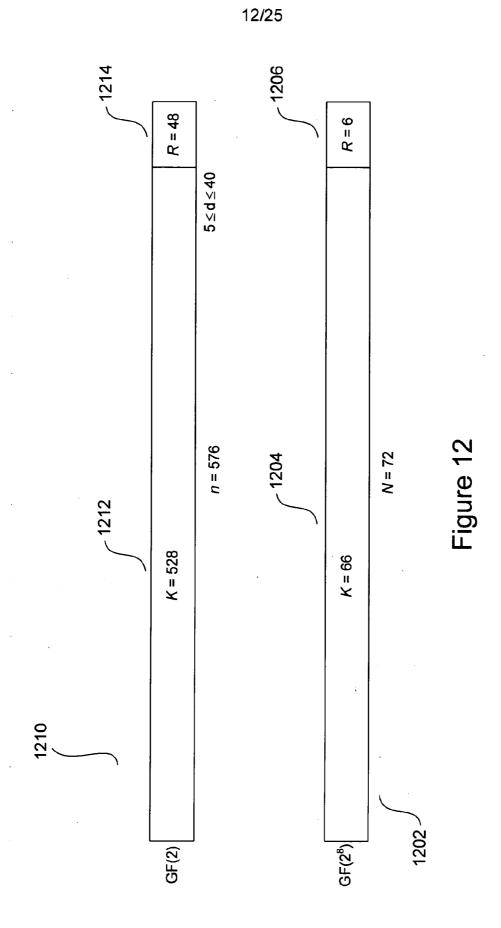

Figure 12 illustrates the basic characteristics of a composite code that represents one embodiment of the present invention.

15

25

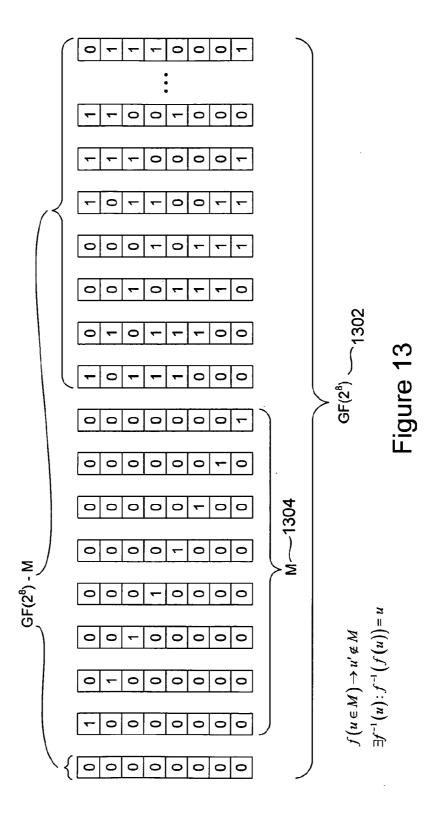

Figure 13 illustrates the characteristics of the symbol-to-symbol mapping function  $f(\cdot)$  used in embodiments of the present invention.

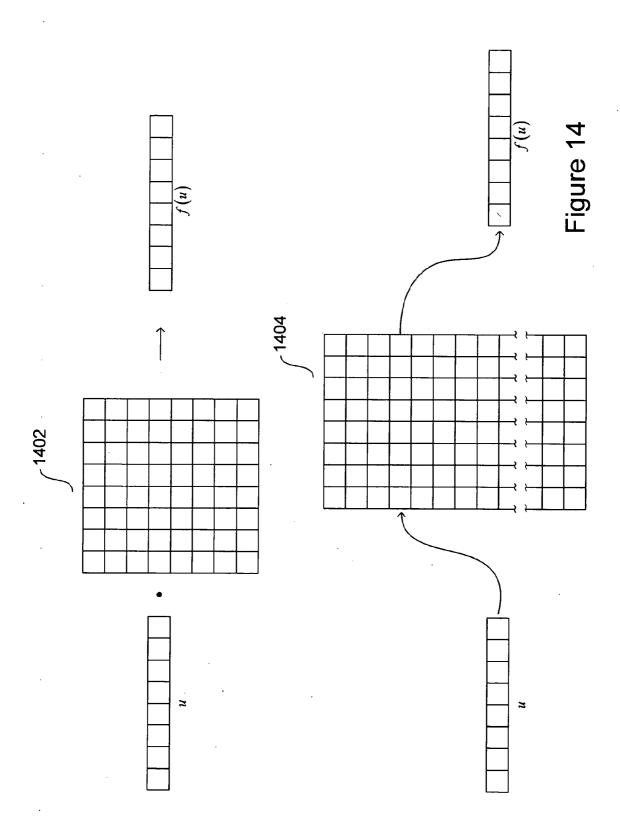

Figure 14 shows two different implementations of the symbol-to-symbol mapping function  $f(\cdot)$ .

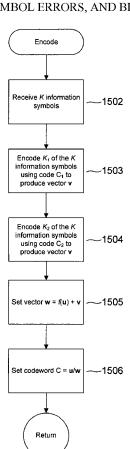

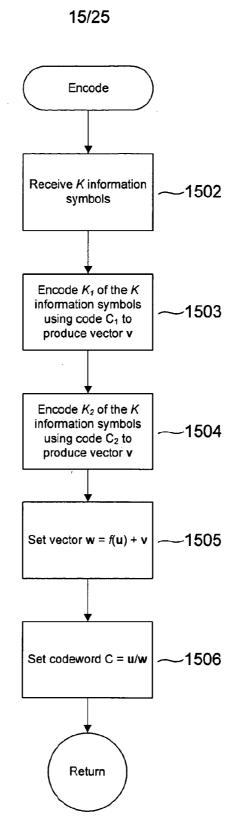

Figure 15A provides a high-level control-flow diagram for encoding of information bits into a composite-code codeword according to one embodiment of the present invention.

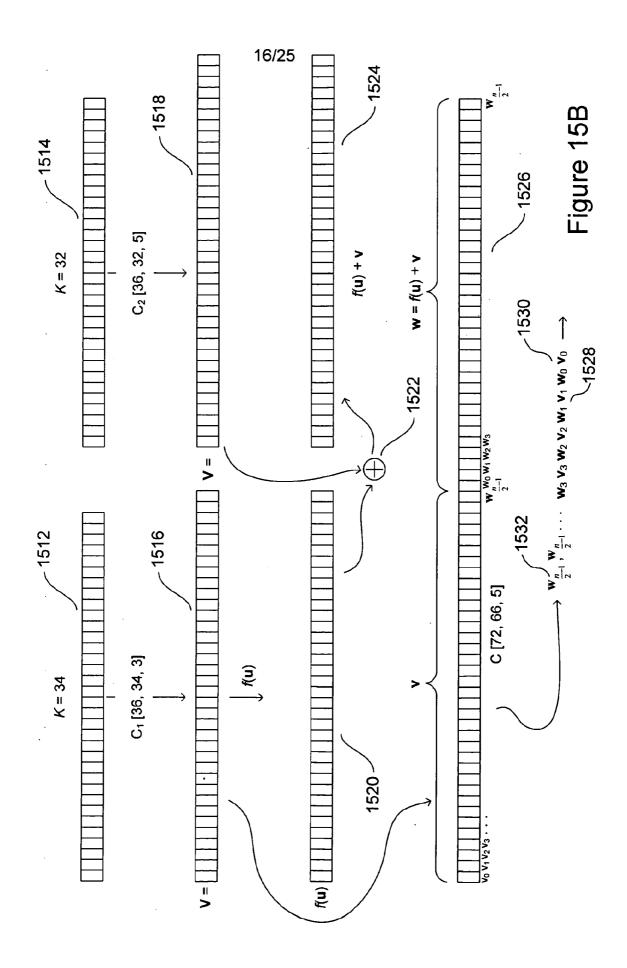

Figure 15B illustrates construction of the composite code C[72,66,5] that represents one embodiment of the present invention.

Figure 16 illustrates a method of encoding a composite-code codeword that can be carried out repeatedly on an input stream of information symbols to produce an output stream of composite-code codewords.

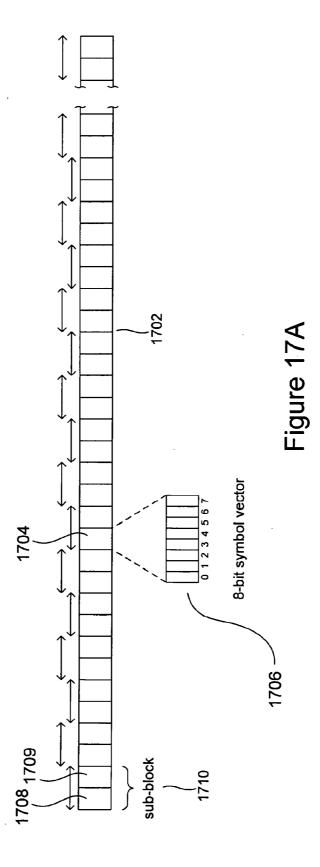

Figure 17A illustrates the notion of a sub-block within a codeword of the composite code that represents one embodiment of the present invention.

5

Figure 17B illustrates the various different types of errors that the composite code that represents one embodiment of the present invention is designed to detect and correct.

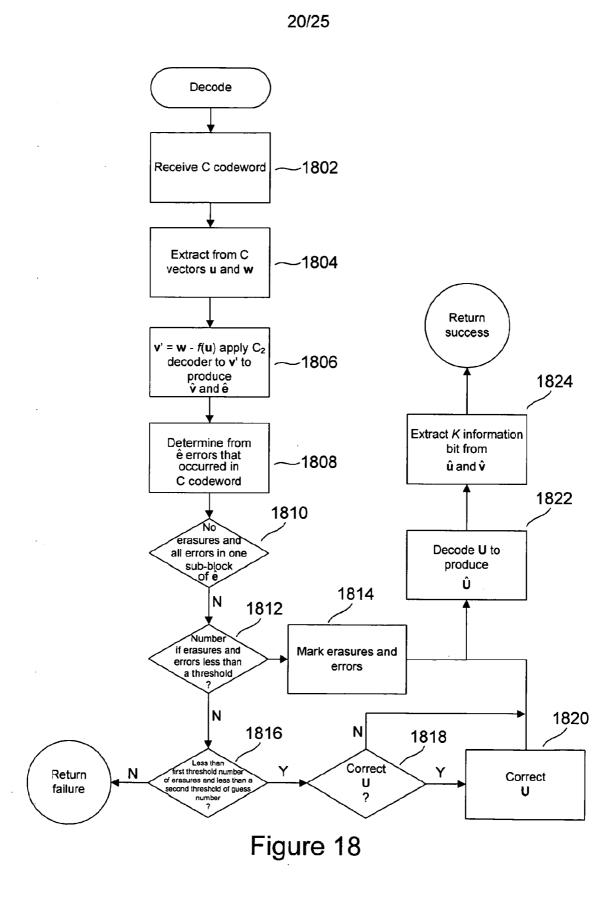

Figure 18 provides a high-level control-flow diagram for decoding of a composite code that represents one embodiment of the present invention.

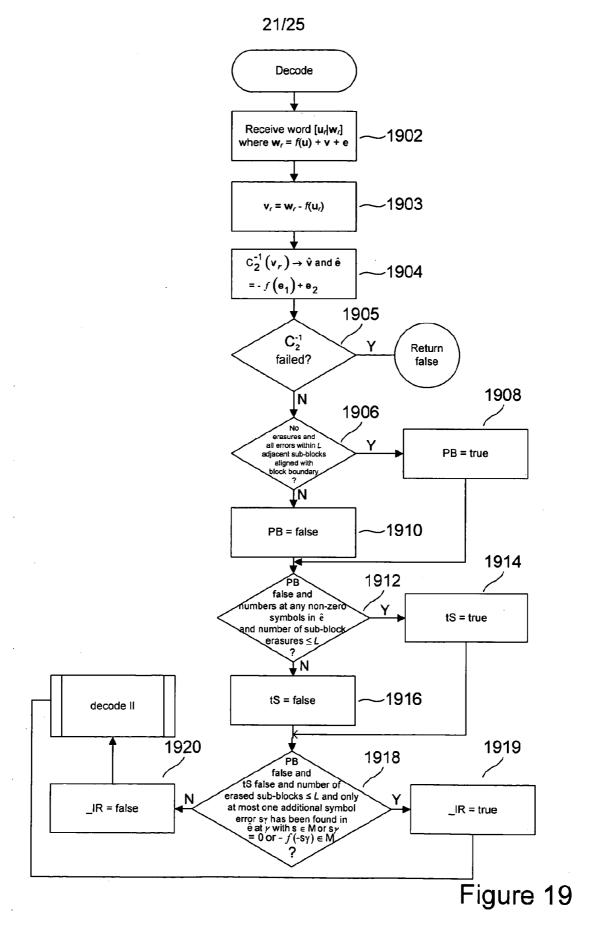

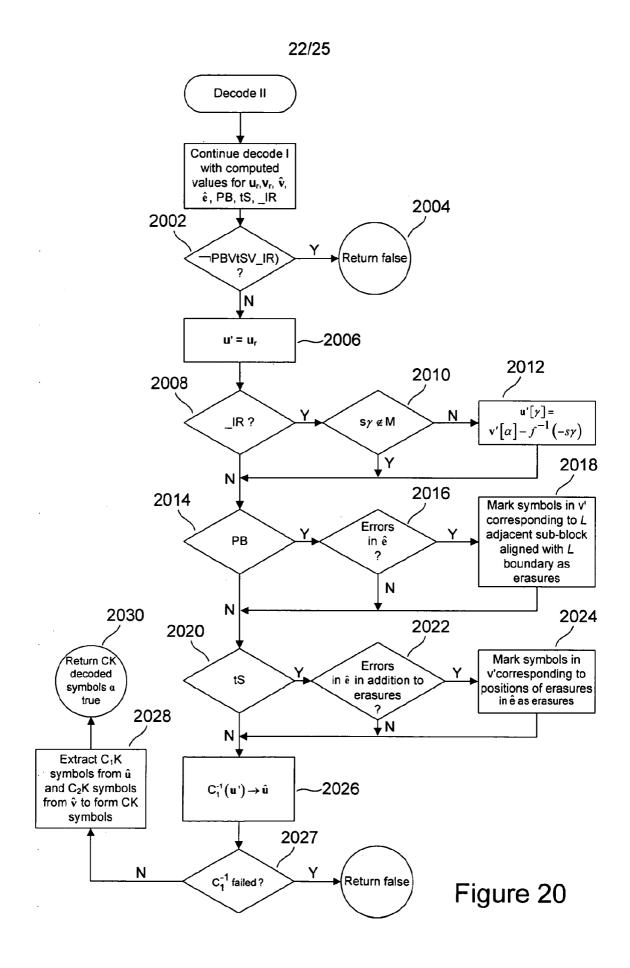

Figures 19-20 provide a control-flow diagram that illustrates one embodiment of the decoding process for composite codes that represent embodiments of the present invention.

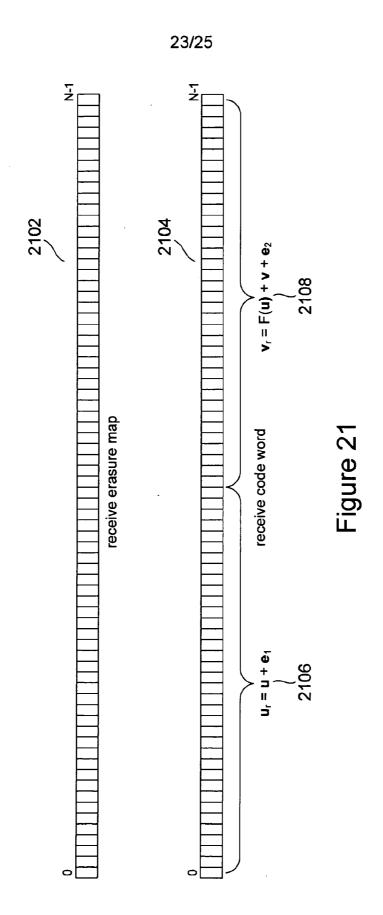

Figure 21 illustrates the information received for each step of a decoding method for the composite code that represents one embodiment of the present invention.

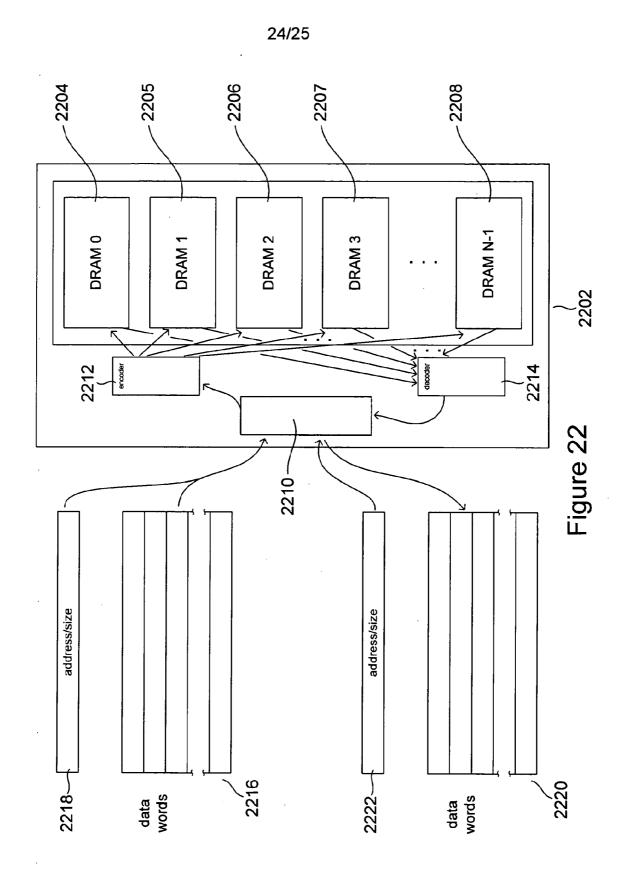

Figure 22 shows a block diagram of a physical memory device in which embodiments of the present invention may be employed.

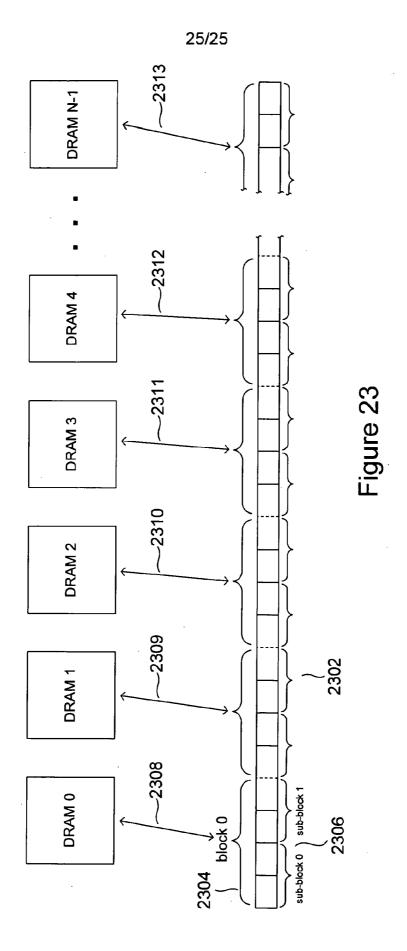

Figure 23 illustrates mapping between codeword symbols and DRAM units in a bank of DRAM units that together comprise the electronic data storage component of the physical memory device illustrated in Figure 22.

## DETAILED DESCRIPTION OF THE INVENTION

5

15

20

25

30

The present invention is directed to error-correcting codes ("ECCs") and ECC-based encoding-and-decoding schemes well suited for detecting and correcting phased bursts of symbol errors and/or erasures and additional single-bit errors and symbol errors, respectively, in a symbol string passed through an erasure-and-error-introducing channel. The present invention is discussed, below, in three subsections. In a first subsection, an overview of one family of error-correcting codes is provided. These error-correcting codes are examples of component ECCs that may be used to construct the composite ECCs that represent embodiments of the present invention, although many additional types of ECCs may be used as components for the composite ECCs. In a following subsection, a brief summary of groups and fields is provided. Finally, in a third subsection, composite codes and composite-code-based encoding-and-decoding schemes to which the present invention is directed are

6

described, with detailed descriptions of encoding and decoding methods for one disclosed composite code.

## Systematic Linear Block Codes

5

10

15

20

25

30

Figure 1 illustrates a basic problem to which ECC-based encodingand-decoding schemes are applied. In Figure 1, a binary-encoded information stream 102 is input to a memory, communications system, or other electronic device, subsystem, or system 104 that exhibits characteristics of an error-introducing channel 105. Subsequently, the digitally encoded information stream is extracted 106 from the memory, communications system, or other electronic device, subsystem, or system 104. It is desirable, and generally necessary, that the extracted information stream 106 be identical to the originally input information stream 102. In order to achieve error-free recovery of information input to the memory, communications system, or other electronic device, subsystem, or system 104, an encoder 108 can be used to introduce redundant information into the information stream and decoder 110 can be used to employ the redundant information to detect and correct any errors introduced by the error-introducing-channel characteristics of the memory, communications system, or other electronic device, subsystem, or system 104. In Figure 1, the binary-encoded information stream is represented in a left-to-right direction 102 when input and in a right-to-left direction when extracted 106. However, in general discussions of ECC-based encoding-and-decoding schemes, an encoded information stream is generally represented in left-to-right order, regardless of whether the information stream represents an input information stream or a received information stream, with the understanding that encoded information is generally transmitted sequentially, bit-by-bit, or byte-by-byte, and then reassembled on reception.

Error-introducing-channel characteristics may be exhibited by an electronic communications medium, such as a fiber-optic cable with a transmitting port on one end and a receiving port at the other end, an Ethernet link with Ethernet ports and controllers included in computing devices that are connected by the Ethernet link, and in other familiar electronic-communications media. Alternatively,

error-introducing-channel characteristics may be exhibited by an information-storage device or component, including different types of electric memories, a mass-storage device, or a physical data-storage medium, such as a DVD or CD. In the case of a communications medium, an information stream initially input to a transmission port may be subsequently received as a corrupted information stream by a receiving port, with errors introduced into the information stream by port-processing components, noise in the transmission medium, and other such error-introducing phenomena. In the case of a storage medium, an initial information stream input to the storage medium may be subsequently retrieved from the storage medium in a corrupted form, with errors introduced into the information stream by storage-component controllers and other processing components, by noise and transmission media, and by electronic, magnetic, and/or optical instabilities in the storage media.

There are various types of errors that may corrupt an encoded information stream. Random bit or symbol errors may result in alteration of the bit or symbol values of certain bits and symbols in the information stream, with the bits or symbols in the information stream having a known or estimable probability of corruption. Burst errors result in corruption in runs of adjacent bits and/or symbols. Many different types of systematic errors, in addition to burst errors, may also occur.

Figure 2 illustrates various different views of a digitally encoded information stream. A digitally encoded information stream can be viewed as an ordered sequence of bit values, or, in other words, the information stream comprises a long, linear array of bit values. Alternatively, the same encoded information stream can be viewed as the ordered sequence of symbols, each symbol comprising a fixed number of bit values. For example, in Figure 2, the binary encoded information stream 202 can be alternately viewed as an ordered sequence of four-bit symbols 204. The value "9" shown in Figure 2 for the second symbol 206 in the ordered sequence of symbols corresponds to the ordered set of bit values 208-211 in the bit-value representation of the encoded information stream 202. In yet another view, the encoded information stream may be viewed as an ordered sequence of blocks 212, each block including an ordered sequence of a fixed number of symbols. Finally, an information stream may be encoded, by a systematic linear block code, to include

8

redundant information to allow for errors to be subsequently detected and corrected. The encoded information stream 214 comprises an ordered sequence of blocks, or codewords, each codeword corresponding to a block in the information stream. For example, the codeword 216 of the encoded information stream corresponds to the block of symbols 218 in the block-view of the information stream 212. Each codeword includes an additional symbol 220-222, represented in Figure 2 by the characters R', R'', and R'''. This extra symbol represents the redundant information included in the information stream by one type of systematic linear block code. In alternative types of linear block codes, each codeword may comprise a first, selected number of information symbols as well as a second selected number of additional symbols representing added redundant information, with the ratio of redundant information symbols to information symbols generally correlated with the number of errors or erasures that may be detected and the number of errors or erasures that may be corrected.

5

10

15

20

25

30

One commonly used type of ECC is a systematic linear block code over a finite field GF(q), where q represents the number of symbols in a field over which the code is defined. When q is a power of 2,  $2^m$ , the symbols of the field are represented as m-tuples. When m is equal to 8, symbols are conveniently represented as bytes. The notation "GF(2)" stands for the binary Galois field with two elements, or symbols, "0" and "1." Given a fixed number of bits in each encoded block, or codeword, produced by a systematic linear block code over GF(2), all of the possible codewords together comprise a vector space. A vector space has certain algebraic properties, including being commutative under addition, closure under scalar multiplication, and is distributive and associative with respect to vector addition and scalar multiplication of vectors. Figure 3A illustrates the vector space V of all possible bit vectors of length n over GF(2). A particular systematic linear block code C that produces codewords of length n is a k-dimensional vector subspace of V, the vector subspace having all of the properties of a vector space. Figure 3B shows an exemplary code, or vector subspace, of the vector space V shown in Figure 3A. Each k-dimensional vector in the vector subspace represents k bits of information from an information stream. The k bits of information are supplemented, by the systematic

linear block code, with r = n-k additional bits to produce a codeword. There is one particular pattern of r additional bits, or parity bits, for each different possible k-dimensional vector of information bits. Thus, a systematic linear block code comprises  $2^k$  different n-bit vectors of the vector space V that constitute a vector subspace. For a systematic linear block code over GF(q), rather than bits, each vector containing n symbols, of which k symbols are information symbols and n - k symbols are redundant information used for detecting and correcting errors. The vector subspace comprising the codewords of the systematic linear block code over GF(q) contains  $q^k$  vectors.

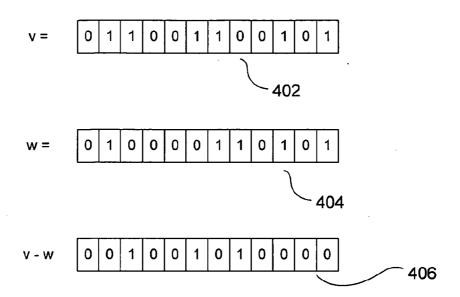

An important characteristic of an ECC is the minimal distance d between any two codewords of the code. Figure 4 shows the distance between any two codewords  $\mathbf{v}$  and  $\mathbf{w}$ ,  $D(\mathbf{v}, \mathbf{w})$ , of an ECC over GF(2). The vector  $\mathbf{v}$  is a 12-bit codeword 402 and  $\mathbf{w}$  is a second 12-bit codeword 404. Subtracting  $\mathbf{w}$  from  $\mathbf{v}$  by modulo 2 subtraction, equivalent to a bit-by-bit XOR operation, produces the difference between  $\mathbf{v}$  and  $\mathbf{w}$ ,  $\mathbf{v}$  -  $\mathbf{w}$ , 406. In the case of an ECC over GF(2), the number of bits with bit value "1" in the vector  $\mathbf{v}$  -  $\mathbf{w}$  406 is equal to the distance between  $\mathbf{v}$  and  $\mathbf{w}$ ,  $D(\mathbf{v}, \mathbf{w})$ . In the general case of an ECC over GF(q), the number of non-zero positions in the difference vector  $\mathbf{v}$  -  $\mathbf{w}$  is the distance between the two codewords  $\mathbf{v}$  and  $\mathbf{w}$ . The weight of any particular codeword  $\mathbf{v}$ ,  $W(\mathbf{v})$ , is the number of non-zero positions in the codeword. Thus,  $D(\mathbf{v}, \mathbf{w}) = W(\mathbf{v} - \mathbf{w}) = 3$  in the example shown in Figure 4.

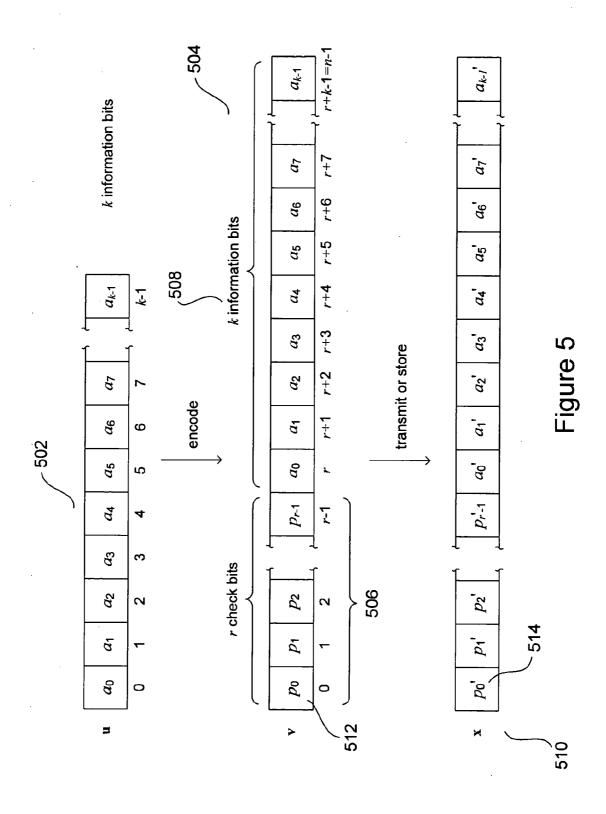

Figure 5 illustrates encoding and transmission of a vector  $\mathbf{u}$  of k information symbols by a q-ary systematic linear block code. The k information symbols are considered to be a k-dimensional vector  $\mathbf{u}$  502. A systematic linear block code encodes the k information symbols, represented by the vector  $\mathbf{u}$ , as a vector  $\mathbf{v}$  of length k+r=n 504. A systematic linear block code places r check symbols, or parity symbols, together in a subvector of vector  $\mathbf{v}$  having length r, generally either at the beginning or the end of vector  $\mathbf{v}$ . In the example shown in Figure 5, and continued in subsequent figures, the parity symbols  $p_0, p_1, \ldots, p_{r-1}$  506 are shown in the initial part of vector  $\mathbf{v}$ , and the k information symbols 508 follow. The codeword  $\mathbf{v}$  is then transmitted through a communications medium or stored to, and retrieved from, a

storage medium to produce the corresponding received word x 510. When no errors occur in transmission or storage,  $\mathbf{x} = \mathbf{v}$ . However, when random transmission or storage errors occur,  $\mathbf{x} \neq \mathbf{v}$ . In many cases, the recipient of the vector  $\mathbf{x}$  cannot compare  $\mathbf{x}$  with the initial, corresponding vector  $\mathbf{v}$  in order to ascertain whether errors have or have not occurred. Therefore, the recipient of vector  $\mathbf{x}$  assumes that each symbol, or bit, in  $\mathbf{x}$  may have been corrupted with some probability of corruption. Therefore, the symbols in  $\mathbf{x}$  are primed, in Figure 5, to indicate that the symbols may have been corrupted with a known or estimable probability of corruption. Thus, symbol  $p_0$  512 in codeword  $\mathbf{v}$  corresponds to symbol  $p_0$  514 in the received word  $\mathbf{x}$ .

5

10

15

20

25

30

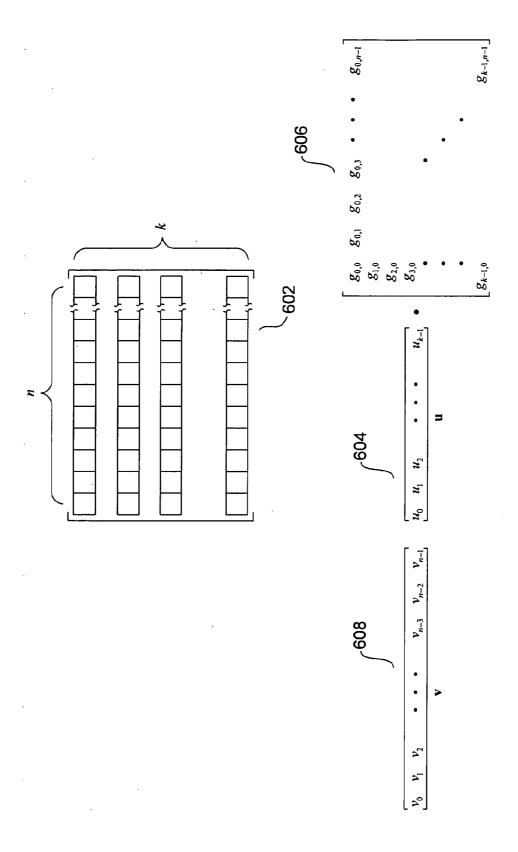

Figure 6 illustrates encoding of the information-bit vector  $\mathbf{u}$  to produce codeword  $\mathbf{v}$ , as discussed with reference to Figure 5. A  $k \times n$  matrix  $\mathbf{G}$  602 can be found, for a given systematic linear block code, to generate a unique codeword  $\mathbf{v}$  corresponding to each possible information-symbol vector  $\mathbf{u}$ . As shown in Figure 6,  $\mathbf{u}$  604 is multiplied by  $\mathbf{G}$  606 to produce the codeword  $\mathbf{v}$  608 corresponding to  $\mathbf{u}$ . The matrix  $\mathbf{G}$  is called a generator matrix for the systematic linear block code. The matrix  $\mathbf{G}$  consists of k linearly independent codewords of the systematic linear block code  $\mathbf{C}$ . Thus, codewords for systematic linear block codes are easily and mechanically generated from corresponding blocks of information symbols by matrix multiplication. In fact, each matrix  $\mathbf{G}$  defines a systematic linear block code.

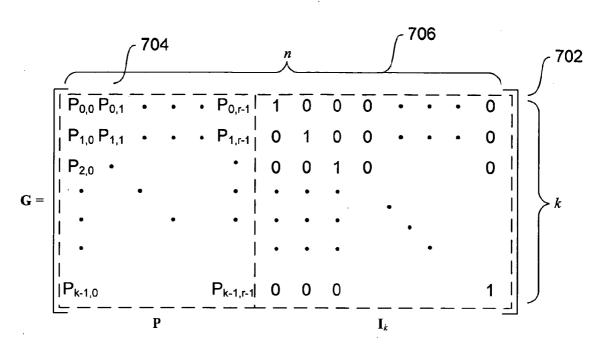

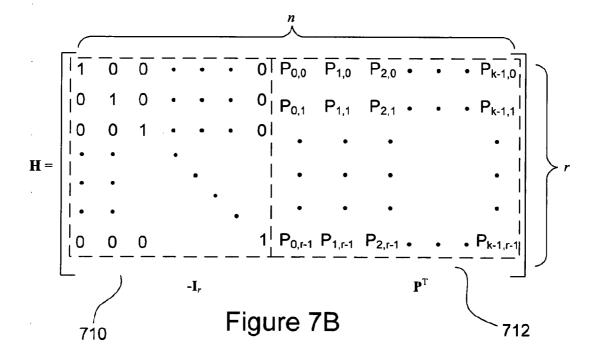

Figures 7A-B show an exemplary systematic generator matrix G and an exemplary systematic parity-check matrix H for a systematic linear block code. The generator matrix G 702, as shown in Figure 7A, can be spatially partitioned into a parity-bit matrix P 704 of dimension  $k \times r$ , and a  $k \times k$  identity matrix  $I_k$  706. The parity-bit matrix P, during matrix multiplication of P0 P1 P2 generates the P3 P3 generates the P4 P4 within the codeword P5.

For each systematic linear block code, there is a parity-check matrix  $\mathbf{H}$  corresponding to the generator matrix  $\mathbf{G}$ . Figure 7B illustrates the form of the parity-check matrix  $\mathbf{H}$ . As can be seen in Figure 7B, the parity-check matrix is an  $r \times n$  matrix that can be spatially partitioned into an  $r \times r$  identity matrix  $-\mathbf{I}_r$  710 and the transpose of the parity-check matrix  $\mathbf{P}^T$  712. Any particular systematic linear block

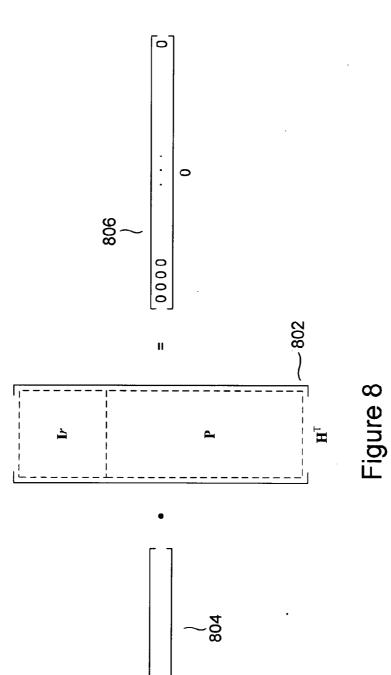

code is completely specified either by a generator matrix G or by the parity-check matrix H corresponding to the generator matrix G. The parity-check matrix H is itself a generator for a linear code, with each codeword including r information symbols. The linear code generated by the parity-check matrix is the dual code of the systematic linear block code C generated by the generator matrix G. Figure 8 shows a property of the transpose of the parity-check matrix,  $H^T$ . As shown in Figure 8, the transpose of the parity-check matrix,  $H^T$  802, when used to multiply a codeword V of the systematic linear block code C, always generates the all-zero vector, V0, of dimension V 806. In other words, for each codeword V0 of systematic linear block code V1.

5

10

15

20

## $\mathbf{v} \cdot \mathbf{H}^{\mathrm{T}} = \mathbf{0}$

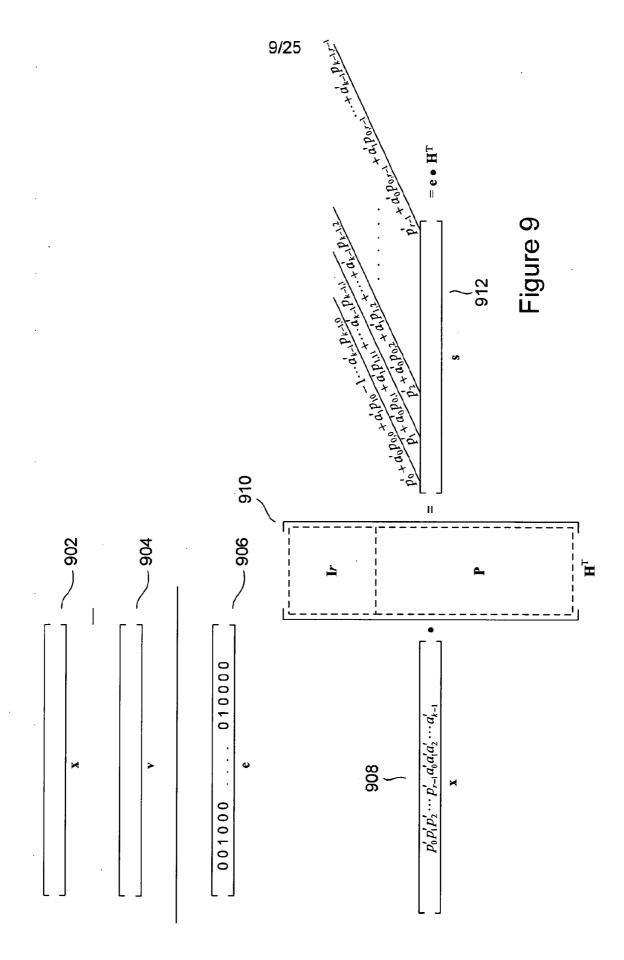

Figure 9 illustrates a portion of the decoding process for a systematic linear block code. As discussed above, the received word  $\mathbf{x}$  902 may contain errors with respect to the corresponding, initially transmitted or stored codeword  $\mathbf{v}$  904. As discussed above, subtracting  $\mathbf{v}$  from  $\mathbf{x}$ , in the case that both  $\mathbf{v}$  and  $\mathbf{x}$  are known, produces a resultant vector 906 in which a non-additive-identity symbol ("1" in the case of GF(2)) appears at every position at which vectors  $\mathbf{x}$  and  $\mathbf{v}$  differ. Thus,  $\mathbf{x} - \mathbf{v} = \mathbf{e}$ , where  $\mathbf{e}$  is referred to as the "error vector," essentially a map of occurred errors Of course, in general, only  $\mathbf{x}$  is known. Thus,  $\mathbf{x}$  equals  $\mathbf{v} + \mathbf{e}$ , where both  $\mathbf{v}$  and  $\mathbf{e}$  are generally unknown. Multiplication of the received word  $\mathbf{x}$  908 by the transpose of the parity-check matrix,  $\mathbf{H}^T$ , 910, produces an r-dimension vector  $\mathbf{s}$  912 referred to as the "syndrome" of  $\mathbf{x}$ . The syndrome of  $\mathbf{x}$  is equal to  $\mathbf{e} \cdot \mathbf{H}^T$ . Thus:

$$\mathbf{s} = \mathbf{e} \cdot \mathbf{H}^{\mathsf{T}} = \mathbf{x} \mathbf{H}^{\mathsf{T}}$$

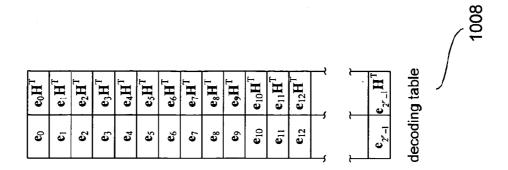

systematic linear block code over GF(q). As shown in Figure 10, a  $q^r \times q^k$  table, called the "standard array," 1002 can be constructed for any systematic linear block code. The first row 1004 of the standard array is an ordered sequence of the codewords  $\mathbf{v}_0, \mathbf{v}_1, \mathbf{v}_2, \ldots, \mathbf{v}_{q-1}^k$ . The codeword  $\mathbf{v}_0$  is the all-zero-symbol code vector (0, 0, ..., 0). Each column i of the standard array can be considered to contain all possible received words  $\mathbf{x}_j$  corresponding to the codeword  $\mathbf{v}_i$  in the first element of the column. In other words, the set of all possible received words  $\mathbf{V}$  has  $q^n$  elements, and

12

is partitioned into  $q^k$  partitions, each partition corresponding to a codeword of the systematic linear block code C, with any received word  $\mathbf{x}$  considered to correspond to the codeword associated with the partition of all possible codewords to which  $\mathbf{x}$  belongs. For example, all of the elements of the first column 1006 of the standard array  $\{e_1, e_2, ..., e_{2^{r}-1}\}$  correspond to all possible error vectors that, when added to the all-zero codeword  $\mathbf{v}_0$ , produce received words that are decoded to the all-zero codeword  $\mathbf{v}_0$ .

As discussed with reference to Figure 9, multiplication of a received word  $\mathbf{x}$  by the transpose of the parity-check matrix  $\mathbf{H}^T$  produces a syndrome vector  $\mathbf{s}$  equal to  $\mathbf{e} \cdot \mathbf{H}^T$ . The syndromes computed for all of the elements in each row of the standard array are therefore identical, depending only on  $\mathbf{e}$  and  $\mathbf{H}^T$ . Therefore, information contained in the standard array, for decoding purposes, can be compressed into a decoding table 1008 that shows the association between each recognized error pattern  $\mathbf{e}_i$  and the syndrome corresponding to that error pattern  $\mathbf{e}_i$   $\mathbf{H}^T$ . Decoding of codewords of a systematic linear block code is, like encoding, carried out by a relatively conceptually simple process:

10

15

20

$$\mathbf{s_x} = \mathbf{xH}^T$$

$$\hat{\mathbf{e}} = \mathbf{e} \text{ in decoding table associated with } \mathbf{s_x}$$

$$\hat{\mathbf{v}} = \mathbf{x} + \hat{\mathbf{e}}$$

However, although conceptually simple, designing codes that can be efficiently decoded is a decidedly non-trivial task. Decoding tables, for example, are impractical for codes with medium and large q, r and/or n parameters, since the size of the decoding table 1008 is proportional to 2(q')(n). Thus, great effort is generally undertaken to design codes with properties that allow for decoding algorithms that are both space and time efficient.

As can be seen in the standard array shown in Figure 10, by increasing the number of parity symbols included in each codeword, a larger number of different error patterns may be recognized. However, as the ratio  $\frac{r}{n}$  increases, the space efficiency of encoding decreases. In general, the error patterns recognized by a systematic linear code are chosen to be the most probable error patterns. For random-

bit errors, the error vectors with least weight are generally the most probable error patterns. For other types of errors, different sets of error patterns may be more probable.

While systematic linear block codes over GF(2) have been discussed, above, systematic linear block codes, including Reed-Solomon codes, can be analogously constructed over any field GF(q). Often, it is convenient to construct systematic linear block codes over extension fields of GF(2), generally specified as  $GF(2^m)$ , where m is an integer greater than 1.

#### 10 Groups and Fields

5

15

25

30

In this subsection, an overview of groups and fields is provided. A group is a set of elements, over which a binary operation \* is defined. The group is closed under the binary operation \*. In other words, for any two elements of the group  $a_1$  and  $a_2$ ,  $a_1*a_2 = a_i$ , where  $a_i$  is also an element of the group. The binary operation \* is associative, so that:

$$(a_1 * a_2) * a_3 = a_1 * (a_2 * a_3)$$

A group has a unique identity element e such that, for every element  $a_i$  in the group, there is an inverse element  $a_i^{-1}$ :

$$a_i * a_i^{-1} = a_i^{-1} * a_i = e$$

A group is commutative, or Abelian, when, for any pair of elements  $a_i$  and  $a_j$ :

$$a_i * a_i = a_i * a_i$$

A field is a commutative group with respect to two different binary operations. One operation may be denoted "+," with the identity element for the operation +,  $e_+$ , equal to 0, and the other operation may be denoted "\*," with  $e_*$ , the identity element for the operation \*, equal to 1. Furthermore, the operation \* is distributive:

$$a*(b+c) = a*b+a*c$$

GF(2) is a binary field, with the + operation equivalent to modulo-2 addition, or the binary XOR operation, and the \* operation equivalent to modulo-2 multiplication, or the Boolean AND operation. GF(q) is a field over the elements

$\{0,1,\ldots,q-1\}$  where q is a prime number. The field  $GF(q^m)$  is an extension field of GF(q), where the elements are defined as polynomials with coefficients in GF(q).  $GF(2^m)$  is an extension field of GF(2) where elements are polynomials with coefficients in GF(2).

A polynomial  $p(\xi)$  of degree m is primitive when the smallest positive integer n for which  $p(\xi)$  divides  $\xi^n + 1$  is equal to  $n = 2^m-1$ . The extension field  $GF(2^m)$  can be represented as a field F of polynomial elements, as follows:

GF

$$(2^m)$$

=F =  $\{0,1,\alpha,\alpha^2,...,\alpha^{2^{m-2}}\}$

where  $\alpha$  is a third symbol, in addition to 1 and 0;

$p(\alpha) = 0$ ;

$$\alpha^{2^{m-1}}=1$$

; and

$\alpha^{2^{m-1}}+1=0.$

For the operation \* in F:

10

$$e_* = 1$$

$$\left(\alpha^i\right)^{-1} = \alpha^{2^m - i - 1}$$

For the operation + in F:

$$e_{+} = 0$$

$$-\alpha^{i} = \alpha$$

In addition to representing the elements of F as powers of α, each element in F can

also be represented as a polynomial with binary coefficients:

$$\alpha^{i} = a_{i,0} + a_{i,1}\alpha + a_{i,2}\alpha^{2} + \dots + a_{i,m-1}\alpha^{m-1}$$

Addition of elements of F is easily carried out by polynomial addition, and multiplication of elements of F is easily carried out by adding exponents of the elements expressed as powers of  $\alpha$ .

For an extension field, such as GF(2<sup>8</sup>), a table can be constructed for each element in GF(2<sup>8</sup>), each entry of which shows the powers representation of the element, the polynomial representation of the element, and a tuple of binary values comprising the coefficients of the polynomial representation of the element. Figure 11 shows a portion of the table of elements for GF(2<sup>8</sup>). The first column 1102 of the

table 1100 shows the powers representation of the elements of  $GF(2^8)$ , the middle column 1103 provides the polynomial representation for the elements, and the final column 1104 shows the 8-bit binary-coefficient-tuple representation of each element. Additional tables can be constructed for multiplication and addition operations. Thus, the field  $GF(2^8)$  can be expressed as a set of 256 elements, each element an 8-bit tuple, with multiplication, addition, and subtraction operations specified by tables based on operations performed on the underlying polynomials. It is important to note that the multiplication, subtraction, and addition operations for the 8-bit element of  $GF(2^8)$  are not equivalent to familiar binary arithmetic operations supported by electronic computers. As one example, in binary arithmetic:

$$00100000 + 10111000 = 11011000$$

but in GF(2<sup>8</sup>) addition:

5

10

15

20

25

$$\alpha^{2} = 00100000 = \alpha^{2}$$

$$\alpha^{8} = 10111000 = 1 + \alpha^{2} + \alpha^{3} + \alpha^{4}$$

$$\alpha^{2} + \alpha^{8} = \alpha^{193} = 1 + \alpha^{3} + \alpha^{4} = 10011000$$

The example of  $GF(2^8)$  is provided, because, in one disclosed embodiment of the present invention, a composite code over  $GF(2^8)$  is constructed from two component codes over  $GF(2^8)$ . Each symbol in a codeword can be viewed as an 8-bit tuple that represents an element of  $GF(2^8)$ . Note that there are 256 elements in  $GF(2^8)$ . Thus, every possible 8-bit tuple is an element of  $GF(2^8)$ . In general, for encoding and decoding purposes, information bytes are considered to be symbols in  $GF(2^8)$ , but prior to encoding and following decoding, the information bytes are viewed as standard binary-encoded bytes. In the following discussion of the present invention, example codes over  $GF(2^8)$  are discussed, but, the methods of the present invention can be applied to creation of composite codes over any field GF(q). It turns out, for computing efficiency, composite codes over  $GF(2^m)$  are desirable, for efficiency in symbol representation and efficiency in computational operations.

16

## **Embodiments of the Present Invention**

The present invention is directed to a family of composite error-correcting codes that are constructed using at least two component codes and a function  $f(\cdot)$ , described below, that maps symbols of a field over which the composite code is defined to other symbols of the field. In the following discussion, one particular composite code from the family of composite codes that represent embodiments of the present invention is discussed. The discussed composite code is a code over 8-bit symbols of the extension field  $GF(2^8)$ . However, composite codes can be analogously constructed for symbols of an arbitrary field GF(q) or  $GF(q^m)$ , using component codes constructed for symbols of the arbitrary field.

5

10

15

20

25

30

Figure 12 illustrates the basic characteristics of a composite code that represents one embodiment of the present invention. The composite code is constructed over  $GF(2^8)$  and produces codewords of length N = 72, where N is the length, in 8-bit symbols. An exemplary codeword 1202 is shown in Figure 12. The codeword contains K = 66 information symbols and R = 6 parity-check symbols. The minimum distance between codewords is D = 5 symbols. The composite code can also be viewed as a code over GF(2). An exemplary codeword of the composite code over GF(2) 1210 is also shown in Figure 12. When viewed as a code over GF(2), each codeword has n = 576 bits of which k = 528 bits 1212 are information bits and r = 48 bits 1214 are parity-check bits. The minimum distance between codewords is in the range  $5 \le d \le 40$ , depending on the nature of the particular component codes used to construct the code. A linear block code having the characteristics N = 72, K = 66, and D = 5 would be expected to be able to detect and correct (D - 1)/2 = 2 symbol errors or 4 symbol erasures. However, the composite code that represents an embodiment of the present invention can correct a larger number of symbol errors when they occur in bursts, a larger number of erasures, and a number of symbol errors and bit errors in addition to error bursts and erasures.

Coding and decoding methods for the composite code that represents one embodiment of the present invention relies on a symbol-to-symbol mapping function  $f(\cdot)$ . Figure 13 illustrates the characteristics of the symbol-to-symbol

17

mapping function  $f(\cdot)$  used in embodiments of the present invention. In Figure 13, a sequence of 256 8-bit symbols representing the 256 elements of  $GF(2^8)$  1302 is partially displayed. The second through ninth symbols of  $GF(2^8)$ , referred to as the set "M," 1304 include those symbols with 8-bit-tuple representations that each includes only a single bit with bit value "1." These 8-bit vectors in the set M correspond to  $GF(2^8)$  elements  $\{1, \alpha^1, \alpha^2, \ldots, \alpha^7\}$  in the representation of  $GF(2^8)$  shown in Figure 11. Any function  $f(\cdot)$  that maps symbols of  $GF(2^8)$  to other symbols of  $GF(2^8)$  can be employed for coding and decoding of the composite code that represents an embodiment of the present invention, providing that the function  $f(\cdot)$  is linear, has a strict inverse function  $f(\cdot)^{-1}$ , and maps any symbol of the set M to a symbol of  $GF(2^8)$  that is not in the set M:

5

10

15

20

25

$$f(u \in M) \to u' \notin M$$

$$\exists f^{-1}(u) : f^{-1}(f(u)) = u$$

Figure 14 shows two different implementations of the symbol-to-symbol mapping function  $f(\cdot)$ . In one implementation, f(u) may be implemented as multiplication of a bit-vector representation of symbol u by an  $m \times m$  matrix 1402, where m is the m of the binary extension field  $GF(2^m)$  over which the code is constructed, in the current case, 8. In an alternative embodiment, a lookup table 1404 can be prepared to provide f(u) values for each possible symbol u. In the case of  $GF(2^8)$  symbols, the symbol represented by the bit-vector u can be used as a numeric byte value to index the lookup table.

In alternative embodiments, the mapping function  $f(\cdot)$  may be a different function. In general, the purpose of  $f(\cdot)$  is to map certain types of errorword symbols to alternative symbol values, to allow the occurrence of errors of that type to be assigned either to an estimated  $C_2$  codeword or to a  $C_1$  codeword extracted from a composite-code codeword during decoding. All embodiments of the present invention employ a non-identity mapping function  $f(\cdot)$ .

The function  $f(\cdot)$  may be applied to symbols, as discussed above, or may be applied to a vector of symbols. For example, the function  $f(\cdot)$  may be applied to an entire codeword  $\mathbf{u}$  to produce a modified codeword  $f(\mathbf{u})$ , with the symbol function  $f(\cdot)$  applied to each symbol of the codeword to generate each corresponding symbol of the modified codeword.

5

10

15

20

25

30

Figure 15A provides a high-level control-flow diagram for encoding of information bits into a composite-code codeword according to one embodiment of the present invention. In step 1502,  $K_I$  information symbols are received. In step 1503,  $K_I$  information symbols are encoded by a first component code  $C_1$  encoder to produce a  $C_1$  codeword  $\mathbf{u}$  of length  $N_I$  symbols. In step 1504,  $K_2$  information symbols are encoded by a second component code  $C_2$  encoder to produce a codeword  $\mathbf{v}$  of length  $N_2$ . In step 1505, a vector  $\mathbf{w}$  of length  $N_2$  symbols is obtained by adding a non-identity mapping of  $\mathbf{u}$ ,  $f(\mathbf{u})$ , to  $\mathbf{v}$ . Finally, in step 1506, a composite-code-C codeword is generated by concatenating  $\mathbf{u}$  and  $\mathbf{w}$  together, the composite-code-C codeword having a length  $N = N_1 + N_2$  and containing  $K = K_1 + K_2$  information symbols.

Figure 15B illustrates construction of the composite code C[72,66,5] that represents one embodiment of the present invention. As discussed above, the composite code relies on two component codes. The component codes may be Reed-Solomon codes, systematic linear-block codes defined over GF(q), binary systematic linear block codes, or other types of codes. In the disclosed embodiment, the first component code C<sub>1</sub> produces codewords with  $N_1 = 36$ ,  $K_1 = 34$ , and  $D_1 = 3$  and the second component C<sub>2</sub> has the characteristics  $N_2 = 36$ ,  $K_2 = 32$ , and  $D_2 = 5$ . It is assumed that C<sub>1</sub> can detect and correct s1 symbol erasures and t1 symbol errors, where  $s1 + 2t1 < D_1$ , and that C<sub>2</sub> can detect and correct s2 symbol erasures and t2 symbol errors, where  $s2 + 2t2 < D_2$ . In fact, such codes are well known.

As shown in Figure 15B,  $C_1$  encodes  $K_I = 34$  information symbols 1512 to produce a 36-symbol  $C_1$  codeword **u** 1516 and  $C_2$  encodes  $K_2 = 32$  information symbols 1514 to produce a 36-symbol  $C_2$  codeword **v** 1518. These codewords are combined to create a codeword of the composite code C [72,66,5] that

5

10

15

20

composite-code codewords.

represents one embodiment of the present invention. Thus,  $K_1 + K_2 = 32 + 34 = 66$ information symbols are encoded into each 72-symbol codeword of the composite code that represents one embodiment of the present invention. Both C1 codeword u and  $C_2$  codeword v have N=36 symbols. The function  $f(\bullet)$  is applied successively to each symbol in  $\mathbf{u}$  to produce a vector  $f(\mathbf{u})$  1520. The vector  $f(\mathbf{u})$  is then added to the  $C_2$  codeword v 1522 to produce the vector  $\mathbf{w} = f(\mathbf{u}) + \mathbf{v}$  1524. Then, the codeword **u** 1516 is concatenated with  $\mathbf{w} = f(\mathbf{u}) + \mathbf{v}$  to produce an N = 72 codeword 1526 of the composite code that represents one embodiment of the present invention. When the symbols of this codeword are transmitted or stored, the symbols from u and w alternate in the transmitted symbols, as shown in the sequence of transmitted symbols 1528, with symbol  $\mathbf{u}_0$  1530 first transmitted and symbol  $\mathbf{w}_{\frac{n}{-1}}$  1532 last Figure 16 illustrates a method of encoding a composite-code transmitted. codeword that can be carried out repeatedly on an input stream of information symbols to produce an output stream of composite-code codewords. In step 1602,  $K_I$ +  $K_2$  information symbols are received for encoding. In step 1604, the first  $K_1$ information symbols are encoded by a C1 encoder to produce a C1 codeword u. In step 1606, the next  $K_2$  information symbols are encoded by a  $C_2$  encoder to produce a  $C_2$  codeword v. In step 1608, the vector  $\mathbf{w} = f(\mathbf{u}) + \mathbf{v}$  is generated from  $\mathbf{u}$  and  $\mathbf{v}$ using the symbol-to-symbol mapping function  $f(\cdot)$ . Finally, in step 1610, **u** and **w** are concatenated together to produce a composite-code codeword. The encoding of a composite-code codeword by the method illustrated in Figure 16 can be carried out repeatedly on an input stream of information symbols to produce an output stream of

The above method of computing vector  $\mathbf{w}$  generates a non-systematic code C. A systematic code C can be obtained by precoding. Precoding is carried out by extracting a prefix of length  $K_2$  from  $f(\mathbf{u})$ ,  $prefix(f(\mathbf{u}))$ , and creating a vector  $\mathbf{a}$  comprising the next  $K_2$  information symbols from the input stream. A word  $\mathbf{v}'$  is then produced as:  $\mathbf{v}' = \mathbf{a} - prefix(f(\mathbf{u}))$ . Finally,  $\mathbf{v}'$  is used as the  $K_2$  information symbols

20

that are encoded into a  $C_2$  codeword  $\mathbf{v}$ , and  $\mathbf{v}$  is then used to compute vector  $\mathbf{w}$  by:  $\mathbf{w} = f(\mathbf{u}) + \mathbf{v}$ .

In alternative embodiments of the present invention, composite-code codewords can be produced by other methods. The order of encoding using component codes may differ, the component codes may differ, and different symbol-to-symbol mapping functions may be employed. Alternative composite codes within the family of composite codes that represent embodiments of the present invention may have different characteristics N, K, and D, depending on the underlying code characteristic of the component codes  $C_1$  and  $C_2$ . In alternative embodiments of the present invention, each component code may itself be generated from two or more underlying component codes.

5

10

15

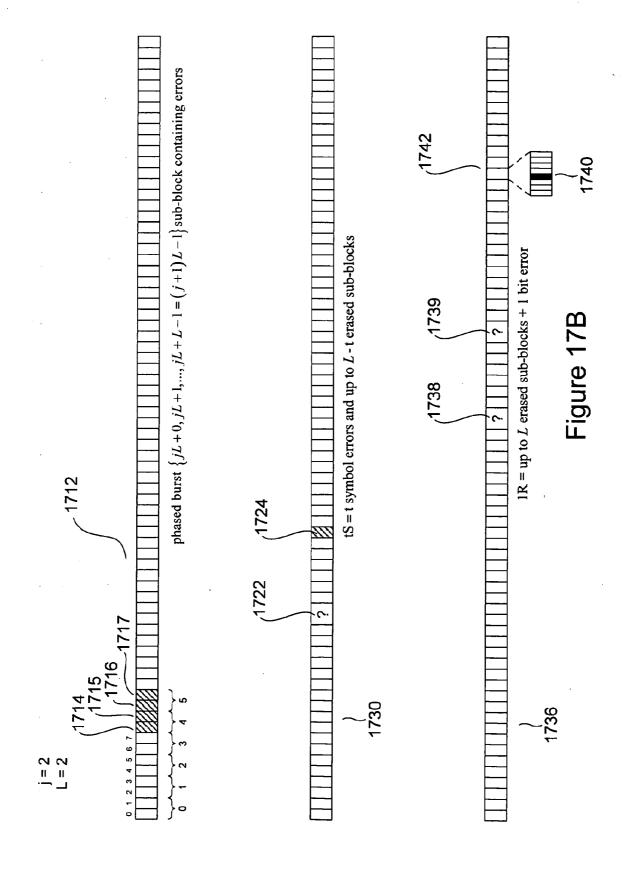

Figure 17A illustrates the notion of a sub-block within a codeword of the composite code that represents one embodiment of the present invention. As shown in Figure 17, a composite-code codeword 1702 can be viewed as containing 8-bit symbols, such as symbol 1704 alternatively shown expanded into an 8-bit symbol vector 1706. Each pair of symbols, such as the pair of symbols 1708-1709, can be together viewed as a sub-block 1710. Thus, a composite-code codeword can be viewed alternatively as an ordered sequence of bits, an ordered sequence of 8-bit symbols, or as ordered sequence of sub-blocks.

Figure 17B illustrates the various different types of errors that the composite code that represents one embodiment of the present invention is designed to detect and correct. An important additional parameter of the composite code is the parameter *L*, a largest integer less than *D/2*. For various types of alternative composite codes, the value *L* may be fixed within the range of integers  $1 < L < \frac{D}{2}$ . A first type of error is referred to as a "phased-burst" error. A phased-burst error is illustrated in the first word 1712 shown in Figure 17B. A phased-burst error is any number of corrupted symbols within a block of adjacent symbols comprising *L* subblocks. As shown in the word 1712 in Figure 17B, four symbols, shown with crosshatching 1714-1717 are corrupted, and all four symbols fall within a block comprising sub-blocks 4 and 5. It is assumed that a codeword containing a phased-

burst error does not contain any sub-block erasures. In the case of the phased-burst error, when all four symbols within a block are corrupted, there is a small probability that the composite code may not be able to correct the errors. However, this small probability is smaller than the probability that a Reed-Solomon code with equivalent redundancy cannot correct the errors, and the composite codes of the current invention are more time efficient than Reed-Solomon codes with equivalent redundancy. When less than four symbols within the block are corrupted, all of the corrupted symbols can be corrected.

A tS error type is illustrated in the second codeword 1730 shown in Figure 17B. The tS error type includes up to L - t sub-block erasures and t corrupted symbols. In the example shown in Figure 17B, there is a single sub-block erasure 1722 and a single additional corrupted symbol 1724, so that t=1 and L-t=1 erased sub-block. Alternatively, there may be two erased sub-blocks and no additional corrupted symbols or two corrupted symbols and no additional erased sub-blocks. A third type of error condition to which the composite codes of the present invention are directed are 1R errors in which up to L sub-blocks are erased and one additional 1-bit error has occurred. The third codeword 1736 in Figure 17B illustrates a 1R error in which two sub-blocks 1738-1739 are erased and a single-bit error 1740 occurs in symbol 1742.

One motivation for development of the composite codes that represent embodiments of the present invention is for error correction of a newly developed type of electronic memory. Because of the construction of this memory, the majority of expected errors include phased-burst errors, tS-type errors, and 1R-type errors. Error correction is carried out in hardware in these electronic-memory systems, and therefore the error correction component represents a significant design and manufacturing overhead. For this reason, designers and manufacturers wish to use as efficient a code as possible for detecting and correcting the expected phased-burst, tS, and 1R errors. The composite codes that represent embodiments of the present invention successfully detect and correct these expected error types using less parity-check symbols than would be needed by a conventional Reed-Solomon code for an equal number of information symbols.

5

10

15

20

Figure 18 provides a high-level control-flow diagram for decoding of a composite code that represents one embodiment of the present invention. 1802, a composite-code-C codeword of length N, containing K information symbols, is received. In steps 1804-1806, a component-code- $C_1$  codeword **u** of length  $N_1$ containing  $K_1$  information symbols and a modified component-code- $C_2$  codeword of length  $N_2$ ,  $\mathbf{w} = \mathbf{v} + f(\mathbf{u})$ , generated, during encoding, from a component-code- $C_2$ codeword v containing  $K_2$  information symbols, where  $K = K_1 + K_2$  and  $N = N_1 + N_2$ , and a non-identity mapping function,  $f(\cdot)$ , are extracted from the composite-code-C codeword and an estimated component-code- $C_2$  codeword  $\hat{\mathbf{v}}$  and an estimated error word ê are generated from the modified component-code-C2 codeword by applying a C<sub>2</sub> decoder to the modified component-code-C<sub>2</sub> codeword. In step 1808, which of a number of types of expected errors occurred subsequent to encoding of the composite-code-C codeword is determined from the error word ê. When more than a first threshold number of erasures and erasures have occurred, but less than a second threshold number of errors have occurred, as determined in step 1816, the determined errors are assigned to either the component-code-C<sub>1</sub> codeword or to the modified component-code-C<sub>2</sub> codeword, and when assigned to the component-code-C<sub>1</sub> codeword, are corrected in steps 1818 and 1820. Other error and erasure occurrences are noted, in steps 1810, 1812, and 1814. In step 1822, an estimated componentcode-C<sub>2</sub> codeword  $\hat{\mathbf{u}}$  is obtained by applying a C<sub>1</sub> decoder to the estimated component-code- $C_1$  codeword  $\hat{\mathbf{u}}$ . Finally, in step 1824,  $K_I$  information symbols are extracted from the estimated component-code- $C_2$  codeword  $\hat{\mathbf{u}}$  and  $K_2$  information symbols are extracted from the estimated component-code- $C_2$  codeword  $\hat{\mathbf{v}}$  to produce K extracted information symbols.

Next, decoding of a received composite-code codeword is discussed. Figures 19-20 provide a control-flow diagram that illustrates one embodiment of the decoding process for composite codes that represent embodiments of the present

invention. First, in step 1902, a composite-code C codeword is received. The

received word can be viewed as two parts:

$$[\mathbf{u}_r | \mathbf{w}_r]$$

23

where  $\mathbf{u}_r$  is the received  $\mathbf{u}$ , or  $\mathbf{u} + \mathbf{e}_1$  $\mathbf{w}_r$  is the received  $\mathbf{w}$ , or  $\mathbf{f}(\mathbf{u}) + \mathbf{v} + \mathbf{e}_2$

5

10

15

20

25

Next, in step 1903, the addition of  $f(\mathbf{u})$  to  $\mathbf{v}$  or  $\mathbf{v}$ " during encoding is reversed by:

$$\mathbf{v}_r = -f(\mathbf{u}_r) + \mathbf{w}_r$$

Next, in step 1904, the computed word  $\mathbf{v}_r$  is decoded using a  $C_2$  decoder to produce estimated codeword  $\hat{\mathbf{v}}$  and estimated error word  $\hat{\mathbf{e}}$ :

$$C_2^{-1}(\mathbf{v}_r) \rightarrow \hat{\mathbf{v}} \text{ and } \hat{\mathbf{e}}$$

where  $\hat{\mathbf{e}} = -f(\mathbf{e}_1) + \mathbf{e}_2$

where the function-like symbol  $C_2^{-1}(\bullet)$  represents decoding by a decoder for component code  $C_2$ .

If the  $C_2$  decoding of  $v_r$  fails, as determined in step 1905, decoding of the composite-code codeword fails. Next, in a series of conditional steps, Boolean flags representing phased-burst ("PB"), tS, and 1R errors are set to indicate whether or not these types of errors appear to have occurred within the received word. Note that the notation " 1R" is used for the 1R flag, below, to be consistent with later-discussed pseudocode. It should be noted that the presence of erased sub-blocks is generally indicated by a separate, out-of-band erasure indication that is not part of the received word. When no erasures have occurred and when all symbol errors have occurred within L adjacent sub-blocks lined with a block boundary, as determined in step 1906 and as discussed above with reference to Figure 17B, then the flag PB is set TRUE in step 1908. Otherwise the flag PB is set to FALSE, in step 1910. When the flag PB contains the value FALSE and when the number of erased sub-blocks and the number of any additional non-zero symbols in the estimated error vector ê sum to a value less than or equal to L, as determined in step 1912, then the flag tS is set TRUE in step 1914. Otherwise the flag tS is set to be FALSE in step 1916. When both PB and tS contain the Boolean value FALSE, and when the number of erased sub-blocks is less than or equal to L and at most only one additional 1-bit symbol error has been found in the error vector ê, as determined in step 1917B, then the flag 1R is set TRUE in step 1919. Otherwise the flag 1R is set to be FALSE in step 1920. A 1-bit error is detected when a non-zero symbol s in the estimated error vector  $\hat{\mathbf{e}}$  is either an

24

element of the set M or -s is mapped to the set M by the symbol-to-symbol function  $f^{-1}()$ , alternatively expressed as:

$$s \in M$$

or  $f^{-1}(-s) \in M$

5

10

15

20

25

30

Thus,  $f(\cdot)$  maps a single-bit error that occurs in  $\mathbf{u}_r$  to a symbol with more than two bits with bit value "1," so that a single-bit error in  $\mathbf{u}_r$  can be distinguished from a single-bit error in  $v_r$ . Coding resumes in the flow-control diagram of Figure 20. If none of the three Boolean flags PB, tS, and 1R are set to TRUE, as determined in step 2002, then the decoder returns a FALSE value in step 2004. Otherwise, vector u is set to the first half of the received C codeword  $\mathbf{u}_r$  in step 2006. If the flag 1R is set to TRUE, as determined in step 2008, then if a single non-zero symbol  $s_{\gamma}$  is found in the estimated error vector  $\hat{\mathbf{e}}$  at position  $\gamma$  and  $\mathbf{s}_{\gamma}$  is not an element of the set M, as determined in step 2010, the symbol at the same position  $\gamma$  in  $\mathbf{u}$  is replaced with the original symbol from which the inversely mapped negative error symbol is subtracted by GF(2<sup>8</sup>) subtraction in step 2012. Steps 2008, 2010, and 2012 allow for detection of a single-bit error in addition to L sub-block erasures. When the non-zero  $\hat{\mathbf{e}}$  symbol s<sub>y</sub> is an element of M, then the single-bit error occurred in the latter half of the received word, or, in other words, in  $\mathbf{v}_r$ . However, when  $\mathbf{s}_{\gamma}$  can be mapped to M by  $F^{-1}(-s_{\gamma})$ , the single-bit error occurred in the first portion of the C codeword. In that case, the error is corrected in step 2012. Next, if the Boolean flag PB contains the value TRUE, as determined in step 2014, and if there are non-zero symbols in ê, as determined in step 2016, then the symbols in the block containing the errors are marked as erased in step 2018. If the flag tS contains the Boolean value TRUE, as determined in step 2020, and if there are any non-zero symbols in ê outside of any detected erasures, as determined in step 2022, then those additional symbol errors are marked as erasures in step 2024. In step 2026, a C<sub>1</sub> decoder is applied to u to produce the estimated original vector  $\hat{\bf u}$ . If the  $C_1$  decoder fails, as determined in step 2027, composite-code decoding fails. Otherwise, in step 2028,  $K_I$  symbols are extracted from  $\hat{\mathbf{u}}$  and  $K_2$  symbols are extracted from  $\hat{\mathbf{v}}$  that together form a sequence of K decoded information symbols that are returned in step 2030. As in the case of step 1904, should the C<sub>1</sub> decoder fail, in step 2026, then decoding fails.

25

Next, a C++-like pseudocode implementation of a decoding method for decoding the above-described composite code that represents one embodiment of the present invention is provided. Figure 21 illustrates the information received for each step of a decoding method for the composite code that represents one embodiment of the present invention. Received information includes an erasure map 2102 with a single bit for each symbol in the codeword indicating whether or not the symbol has been erased. The received information includes an erasure map 2102 that includes a bit flag for each symbol of a received word indicating whether or not the symbol has been erased, and a received word 2104 that, as discussed above, includes a first portion 2106  $\mathbf{u}_r$  which equals  $\mathbf{u} + e_1$ , although  $\mathbf{u}$  and  $e_1$  are not known, and a second part 2108  $\mathbf{v}_r$  which equals  $\mathbf{F}(\mathbf{u}) + \mathbf{v} + e_2$ , although  $\mathbf{u}$ ,  $\mathbf{v}$ , and  $e_2$  are not known.

The pseudocode implementation first includes a number of constant integer declarations:

```

1 const int C1K = 34:

2 const int C2K = 32:

15

3 const int CK = C1K + C2K;

4 const int C1R = 2;

5 const int C2R = 4;

6 const int CR = C1R + C2R;

20

7 const int C1D = 3;

7 const int C2D = 5:

8 const int CD = 2 * C1D > C2D ? C2D : 2 * C1D;

9 const int N = CR + CK;

10 const int L = floor((CD-1) / 2);

25

11 const int symPSubBlk = 2;

12 const int Nsub = N / symPSubBlk;

13 const int N2 = N / 2;

14 const int blkPlus = N2 / symPSubBlk;

15 const int b = 8;

```

5

10

30

35

These constants include the basic parameters for composite code C and component codes C1 and C2, discussed above, including: (1) C1K, C2K, and CK, the number of information symbols in the codewords of C1, C2, and C, respectively; (2) C1R, C2R, and CR, the number of parity-check symbols in codewords of C1, C2, and C, respectively; (3) the minimum distance between codewords C1D, C2D, and CD for codewords of C1, C2, and C, respectively; (4) a constant N, the number of symbols in a codeword of the composite code C; (5) the number L, equal to the largest integer

less than (CD-1)/2 in the disclosed implementation, as discussed above; (6) N2, the

number of symbols in codewords of component code C1 and C2, where N2 = N/2; symPSubBlk. the number of symbols per sub-block; (7) blkPlus, that, when added to the sub-block index of a block in a first portion of a composite codeword, generates the sub-block index of the corresponding sub-block of a second portion of the composite codeword; and (8) a constant b, the number of bits in a symbol, or, equivalently, a number equal to m in the expression  $GF(2^m)$  for the field over which the composite code C is constructed.

Next, type definitions are provided: (1) for a codeword symbol; (2) C, C1, and C2 codewords; and (3) erasure maps for C, C1, and C2 codewords:

```

10    1 typedef unsigned char symbol; // b <= 8 only

2 typedef symbol C_WORD[N];

3 typedef symbol C1_WORD[N2];

4 typedef symbol C2_WORD[N2];</pre>

```

5

20

25

5 typedef bool C\_ERASURE\_WORD[N];

15 6 typedef bool C1\_ERASURE\_WORD[N2];

7 typedef bool C2\_ERASURE\_WORD[N2];

It should be noted that the C++ type "unsigned char" can only be used to represent a symbol when the constant b is less than or equal to 8. When b = 8, the unsigned-char data type, also referred to as a "byte," is exactly the size needed to represent each symbol expressed as a tuple of binary coefficients, and thus  $GF(2^8)$  is a most convenient field over which to construct a code, for computational efficiency.

Next, a declaration is provided for the set M which includes all symbols with 8-bit-tuple representations that include only a single bit with the bit value "1." This declaration employs the fact that the tuples in set M correspond to bytes, in normal binary byte-value representations, to powers of two:

1 const symbol M[b] = {1, 2, 4, 8, 16, 32, 64, 128}; // elements of GF(2^b) with a // single-bit tuple representation

Next, declarations for five functions are provided:

```

1 bool C1(C1_WORD c1Word, C1_ERASURE_WORD erasures,

2 C1_WORD decodedC1Word, C1_WORD errors);

3 bool C2(C2_WORD c2Word, C2_ERASURE_WORD erasures,

4 C2_WORD decodedC2Word, C2_WORD errors);

5 symbol f(symbol a);

6 symbol fInverse(symbol a);

7 symbol GF2bSubtraction(symbol y, symbol z);

```

27

The first two functions are decoders for component codes C1 and C2. These two functions receive a codeword and erasure map and return a decoded codeword and an error word, as described above. The function  $f(\cdot)$  and the function  $f^{-1}(\cdot)$ , discussed above, are declared on lines 5 and 6 of the above code block. Finally, on line 7, a GF( $2^8$ ) subtraction function for subtracting a GF( $2^8$ ) symbol z from a GF( $2^8$ ) symbol y is provided. As discussed above, it is assumed that component codes C1 and C2 exist, and that encoders and decoders are available for these component codes. No implementations are provided for the above five functions, as the decoder implementations depend on the particular component codes selected for use in constructing a composite code, because the functions  $f(\cdot)$  and  $f^{-1}(\cdot)$  are straightforwardly implemented, the implementations depending on the field over which the composite code is defined, and because GF( $2^b$ ) subtraction is well known.

Next, a number of class declarations are provided. First, three classes that represent an input symbol stream, an input erasure stream, and an output symbol stream are provided:

```

1 class symbolStream

2 {

3

public:

4

bool start();

bool getNext(int num, symbol* buffer);

20

5

6 };

1 class erasureStream

2 {

25

3

public:

4

bool start();

5

bool getNext(int num, bool* buffer);

6 };

30

1 class outputStream

2 {

3

public:

4

bool start();

5

void outputNext(int num, symbol* buffer);

35

6

void finish();

7 };

```

5

10

15

The various streams can be started and then accessed in order to input or output specified numbers of symbols. Implementations are not provided for these classes,

since stream input and output is both well known, operating-system dependent, and possibly hardware-platform dependent.

Next, a class declaration for a class "C-decoder" is provided:

```

1 class C_decoder

5

2 {

3

private:

4

symbolStream s;

5

erasureStream Er;

6

outputStream out;

10

7

void deInterleave(C_WORD c, C_ERASURE_WORD er);

8

bool decodeNextBlock(C_WORD c, C_ERASURE_WORD er,

9

symbol* buffer);

10

11

15

12

public:

bool decode();

13

14 };

```

The class "C\_decoder" includes three private data members s, Er, and out that represent instances of the symbol stream, erasure stream, and output stream classes, respectively. The class "C\_decoder" includes two private function members, declared on lines 8-10. The first private function member, "deInterleave," transforms n symbols received from an input stream into a C codeword by deinterleaving the symbols that are interleaved, as discussed with reference to Figure 15 (specifically 1518 in Figure 15). The private function member "decodeNextBlock" receives a C codeword and a corresponding erasure map and outputs K decoded information symbols to an output stream. The single public function member "decode," declared on line 13, continuously decodes symbols from an input stream and outputs corresponding decoded information symbols to an output stream.

Implementation of the function member "decode" is next provided:

```

1 bool C_decoder::decode()

2 {

3

s.start();

4

Er.start();

35

5

out.start();

6

C WORD c;

C_ERASURE_WORD er;

7

8

symbol buffer[CK];

9

40

while (s.getNext(N, c) && Er.getNext(N, er))

10

11

```

20

25

30

29

```

deInterleave (c, er);

13 if (!decodeNextBlock(c, er, buffer)) return false;

14 out.outputNext(CK, buffer);

15 }

5 16 return (true);

17 };

```

In the while-loop of lines 10-15, the function member "decode" extracts a next codeword and corresponding erasure map from the input streams c and Er, deinterleaves the input symbols on line 12, decodes the codeword on line 13, and outputs corresponding decoded information symbols on line 14. This loop continues until either decoding fails, on line 13, or until there are no additional coded symbols available from the information stream, as determined on line 10.

Next, an implementation of the function member "decodeNextBlock"

is provided:

10

```

1 bool C_decoder::decodeNextBlock(C_WORD c, C_ERASURE_WORD er,

symbol* buffer)

2

3 {

4

symbol* ur = \&(c[0]);

20

5

symbol* wr = \&(c[N2]);

6

7

bool* er1 = &(er[0]);

8

bool* er2 = &(er[N2]);

9

25

10

C1 WORD uHat, uPrime, e1Hat;

11

C2 WORD vHat, vr, e2Hat;

12

13

bool PB, tS, _1R, erased;

14

30

15

symbol gamma;

16

17

int i, j, blklndex, gammalndex;

18

int erasures[L];

19

int numErasures = 0;

35

int nonZeroSymbols[L];

20

21

int numNonZeroSymbols = 0;

22

23

for (i = 0; i < N2; i++)

24

vr[i] = -f(ur[i]) + wr[i]; //vr = v + -f(e1) + e2

40

25

26

if (!C2(vr, er2, vHat, e2Hat)) return false;

27

28

for (i = 0; i < N; i++)

29

{

45

30

if (er[i])

```

```

31

{

32

blkIndex = (i / symPSubBlk) * symPSubBlk;

33

if ((i != blkIndex) && er[blkIndex]) continue;

34

if (numErasures == L) return false;

5

35

else erasures[numErasures++] = blkIndex;

36

}

37

}

38

39

for (i = 0; i < N2; i++)

10

40

41

erased = false;

blkIndex = (i / symPSubBlk) * symPSubBlk;

42

43

for (j = 0; j < numErasures; j++)

44

15

45

if (erasures[j] == blklndex || erasures[j] == blklndex + blkPlus)

46

erased = true: break:

47

48

if (erased)

49

i = ((blkIndex + 1) * symPSubBlk) - 1;

20

50

else

51

{

52

if (e2Hat[i] != 0)

53

{

if (numNonZeroSymbols == L) return false;

54

25

55

else nonZeroSymbols[numNonZeroSymbols++] = i;

56

}

}

57

58

}

59

30

60

if (numErasures == 0)

61

if (numNonZeroSymbols == 0) PB = true;

62

63

else if (nonZeroSymbols[numNonZeroSymbols - 1] -

64

nonZeroSymbols[0] <= L)

35

65

PB = true:

else PB = false;

66

67

}

68

69

if (!PB && numNonZeroSymbols + numErasures < L) tS = true;

40

70

else tS = false;

71

72

if (!PB && !tS && numNonZeroSymbols == 1)

73

74

gammaIndex = nonZeroSymbols[0];

45

75

gamma = 0;

76

if (e2Hat[gammaIndex] == 0) _1R = true;

77

else

78

{

79

1R = false;

50

80

for (i = 0; i < b; i++)

81

{·

82

if ((e2Hat[gammaIndex] == M[i]))

```

```

83

{

1R = true;

84

85

break:

86

}

5

87

gamma = flnverse(-e2Hat[gammaIndex]);

if (gamma = M[i])

88

89

90

_1R = true;

91

break;

10

92

93

gamma = 0:

94

}

95

}

96

}

15

97

if (!PB && !tS && !_1R) return false;

98

99

for (i = 0; i < N2; i++) uPrime[i] = ur[i];

100

101

20

102

if (PB)

for (i = 0: i < numErasures: i++)

103

104

for (j = 0; j < symPSubBlk; j++)

105

er1[i + j] = true;

106

25

107

if (tS)

for (i = 0; i < numNonZeroSymbols; i++)

108

er1[nonZeroSymbols[i]] = true;

109

110

111

uPrime[i] = GF2bSubtraction(uPrime[i], gamma);

30

112

113

if (!C1(uPrime, er1, uHat, e1Hat)) return false;

114

115

for (i = 0; i < C1K; i++) *buffer++ = uPrime[i];

for (i = 0; i < C2K; i++) *buffer++ = vHat[i];

116

35

117

return true;

118}

```

The function member "decodeNextBlock" receives a composite-code codeword c, corresponding erasure map er, and a symbol buffer in which to place the decoded information symbols corresponding to received word c. On lines 4-5 symbol pointers ur and wr are declared to point to the first and second halves of the received word C. These symbol pointers ur and wr correspond to  $u_r$  and  $w_r$  in Figure 21. Similarly, on lines 7-8, erasure-map pointers er1 and er2 are declared to point to the portions of the received erasure word er corresponding to the first half and the second half of the received word C, respectively.

32

On lines 10-21, a number of local variables are declared. These local variables have names corresponding to the notation used in the above discussions of the composite code, component codes, composite-code encoding, and composite-code decoding. For example, the variable vHat, declared on line 11, represent the estimated decoded codeword  $\hat{\mathbf{v}}$  discussed above. The arrays "erasures" and "nonZeroSymbols," declared on lines 18 and 20, respectively, contain the indices of erased sub-blocks and the indices of additional errors detected in the erasure map and the estimated error vector e2Hat, respectively. The use of the local variables is clarified by their use, described below, in the function member "decodeNextBlock."

10

15

5

On lines 23-24, the vector "vr" is computed as vr = wr - f(ur). On line 26, vr is decoded to produce  $\hat{\mathbf{v}}$  and  $\hat{\mathbf{e}}$ , referred in the code as "vHat" and "e2Hat," respectively. In the *for*-loop of lines 28-37, indices of all erased sub-blocks are determined and stored in the array "erasures." Note that if the number of sub-block erasures is greater than L, the decode routine fails, since only up to L erasures can be detected and corrected by the composite code implemented in the pseudocode. Note also that if the C2 decoder, invoked on line 26, fails, then decoding fails. Next, in the *for*-loop of lines 39-58, any errors in  $\hat{\mathbf{e}}$ , represented by non-zero symbols, apart from any detected erased sub-blocks are noted, and the indices of the non-zero symbols corresponding to the errors are stored in the array "nonZeroSymbols."

20

25

On lines 60-67, the Boolean flag PB is set to TRUE or FALSE, depending on whether or not a phased-burst error is detected in the codeword. PB is set to TRUE when there are no erasures and when either there are no additional error symbols or all of the error symbols occur within a single block composed of L adjacent sub-blocks. Recall that the function member "decodeNextBlock" will have already failed if there are more than L erased sub-blocks. Next, on lines 69-70, the Boolean flag tS is set to TRUE or FALSE, depending on whether or not a tS-type error is detected in the received word. The flag tS is set to TRUE when PB is FALSE and the number of erased sub-blocks added to the number of additional error symbols produces a sum less than or equal to L.

30

Next, on lines 72-96, the Boolean flag \_1R is set to TRUE or FALSE.

The Boolean flag \_1R is set to TRUE when there is a single additional 1-bit error, or

no additional errors, along with up to L erased sub-blocks. Note that decoding has already failed, on line 34, if more than L erased sub-blocks were detected. An error symbol represents a 1-bit error when either the error symbol is a member of the set M, as determined on line 81, or an inverse mapping by  $f^{-1}(\cdot)$  of the  $GF(2^b)$ -additive inverse of the symbol value of the error symbol maps to M, as determined on line 88.

When all of the Boolean flags are FALSE, as determined on line 98, then decoding fails. Otherwise, *uPrime* is set to the first portion of the received word *c* on line 100. When PB is TRUE, all symbols of all sub-blocks containing errors are marked as erasures, on lines 102-105. When *tS* is TRUE, then all additional error symbols are marked as erasures, on lines 107-109. When a 1-bit additional error is detected in the first portion of the codeword, on line 88, then, on line 109, *uPrime* is altered to correct the area by subtraction of the inversely mapped inverse symbol value from *uPrime*, on line 111. Finally, on line 113, *uPrime* is decoded by the C1 decoder. If the C1 decoder fails, then decoding fails. Otherwise, the information symbols in *uPrime* and *vHat* are placed in the buffer for return to the member function "decode."