(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-177320

(P2015-177320A)

(43) 公開日 平成27年10月5日(2015.10.5)

| (51) Int.Cl.                | F 1                | テーマコード (参考) |

|-----------------------------|--------------------|-------------|

| <b>HO4N 5/374 (2011.01)</b> | HO 4 N 5/335 7 4 0 | 5 C 0 2 4   |

| <b>HO4N 5/376 (2011.01)</b> | HO 4 N 5/335 7 6 0 |             |

| <b>HO4N 5/357 (2011.01)</b> | HO 4 N 5/335 5 7 0 |             |

審査請求 未請求 請求項の数 5 O L (全 12 頁)

|           |                            |          |                                                   |

|-----------|----------------------------|----------|---------------------------------------------------|

| (21) 出願番号 | 特願2014-51861 (P2014-51861) | (71) 出願人 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号             |

| (22) 出願日  | 平成26年3月14日 (2014.3.14)     | (74) 代理人 | 100089118<br>弁理士 酒井 宏明                            |

|           |                            | (72) 発明者 | 岡元 立太<br>東京都港区芝浦一丁目1番1号 株式会社<br>東芝内               |

|           |                            |          | F ターム (参考) 5C024 CX03 CY16 GY31 HX02 HX29<br>HX47 |

(54) 【発明の名称】 固体撮像装置

## (57) 【要約】

【課題】チャージポンプ回路のノイズの増大を抑制しつつ、画素駆動の高速化を図る。

【解決手段】画素アレイ部1には、光電変換した電荷を蓄積する画素PCがロウ方向RDおよびカラム方向CDにm行×n列分だけマトリックス状に配置され、駆動電圧発生回路8は、画素PCの駆動の開始のタイミングに基づいて駆動電圧DVを発生する駆動力を増大させる。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

光電変換した電荷を蓄積する画素がマトリックス状に配置された画素アレイ部と、前記画素の駆動時に前記画素を駆動する駆動電圧を発生するとともに、前記駆動の開始のタイミングに基づいて前記駆動電圧を発生する駆動力を増大させる駆動電圧発生回路とを備える固体撮像装置。

## 【請求項 2】

前記駆動電圧発生回路は、

自己の出力電圧に基づいて動作される第 1 チャージポンプ回路と、

前記駆動の開始時に動作される第 2 チャージポンプ回路とを備える請求項 1 に記載の固体撮像装置。

10

## 【請求項 3】

前記第 1 チャージポンプ回路は、前記画素からの放電による電圧低下分を補償するよう

に駆動力が設定される請求項 2 に記載の固体撮像装置。

## 【請求項 4】

前記第 2 チャージポンプ回路は、前記画素の駆動の開始時の前記駆動電圧の立ち上がり

時間が短くなるように駆動力が設定される請求項 3 に記載の固体撮像装置。

## 【請求項 5】

前記駆動電圧発生回路は、

第 1 チャージポンプ回路と、

第 2 チャージポンプ回路と、

前記第 1 チャージポンプ回路および前記第 2 チャージポンプ回路から出力されるバイアス電圧を分圧する電圧分圧部と、

参照電圧を発生する参照電圧発生回路と、

前記電圧分圧部にて生成された分圧電圧と前記参照電圧とを比較するコンパレータと、

前記コンパレータによる比較結果に基づいてクロックを前記第 1 チャージポンプ回路に

出力する第 1 AND 回路と、

前記駆動の開始のタイミングに基づいて前記第 1 AND 回路の出力を前記第 2 チャージ

ポンプ回路に出力する第 2 AND 回路と、

前記画素の駆動時に前記駆動電圧を前記バイアス電圧にシフトさせるレベルシフタとを

備える請求項 1 に記載の固体撮像装置。

20

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明の実施形態は、固体撮像装置に関する。

## 【背景技術】

## 【0002】

固体撮像装置では、画素を駆動するための電圧を内部で生成するため、チャージポンプ

回路を設けたものがある。ここで、画素の高速駆動を図るために、チャージポンプ回路の

駆動力を高めることが行われている。

40

## 【先行技術文献】

## 【特許文献】

## 【0003】

【特許文献 1】特開 2010-51133 号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

本発明の一つの実施形態は、チャージポンプ回路のノイズの増大を抑制しつつ、画素駆

動の高速化を図ることが可能な固体撮像装置を提供することを目的とする。

## 【課題を解決するための手段】

10

20

30

40

50

## 【0005】

本発明の一つの実施形態によれば、画素アレイ部と駆動電圧発生回路とが設けられている。画素アレイ部は、光電変換した電荷を蓄積する画素がマトリックス状に配置されている。駆動電圧発生回路は、前記画素の駆動時に前記画素を駆動する駆動電圧を発生するとともに、前記駆動の開始のタイミングに基づいて前記駆動電圧を発生する駆動力を増大させる。

## 【図面の簡単な説明】

## 【0006】

【図1】図1は、第1実施形態に係る固体撮像装置の概略構成を示すブロック図である。

10

【図2】図2は、図1の固体撮像装置の画素の構成例を示す回路図である。

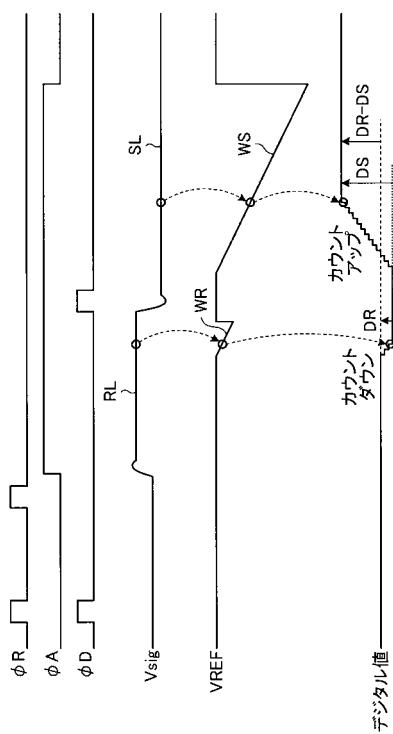

【図3】図3は、図1の画素の読み出し動作時の各部の電圧波形を示すタイミングチャートである。

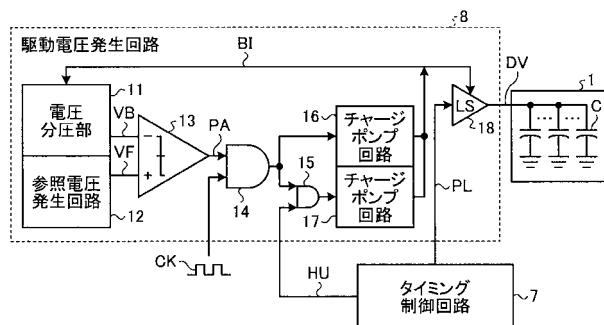

【図4】図4は、図1の固体撮像装置の駆動電圧発生回路の構成例を示すブロック図である。

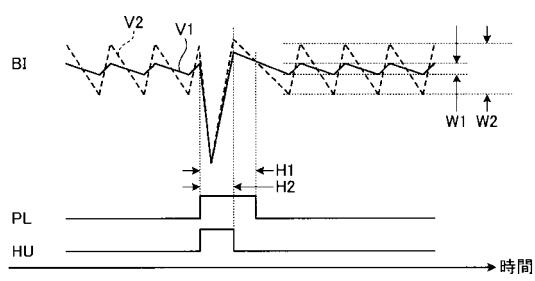

【図5】図5は、図4のチャージポンプ回路の動作時の電圧波形を示すタイミングチャートである。

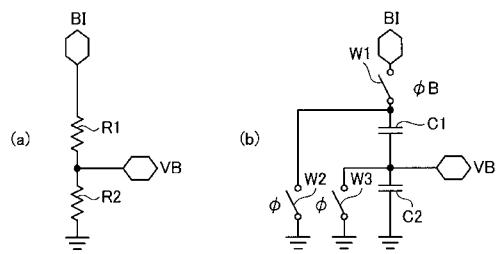

【図6】図6(a)は、図4の電圧分圧部の構成例を示す回路図、図6(b)は、図4の電圧分圧部のその他の構成例を示す回路図である。

【図7】図7(a)は、図4のコンパレータの構成例を示す回路図、図7(b)は、図4のコンパレータのその他の構成例を示す回路図である。

20

【図8】図8(a)は、図4のチャージポンプ回路の構成例を示す回路図、図8(b)は、図4のチャージポンプ回路のその他の構成例を示す回路図である。

【図9】図9は、図4のレベルシフタの構成例を示す回路図である。

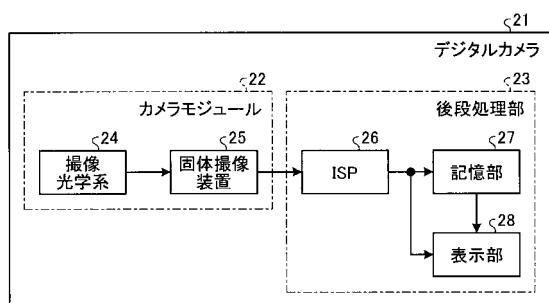

【図10】図10は、第2実施形態に係る固体撮像装置が適用されたデジタルカメラの概略構成を示すブロック図である。

## 【発明を実施するための形態】

## 【0007】

以下に添付図面を参照して、実施形態に係る固体撮像装置を詳細に説明する。なお、これらの実施形態により本発明が限定されるものではない。

30

## 【0008】

## (第1実施形態)

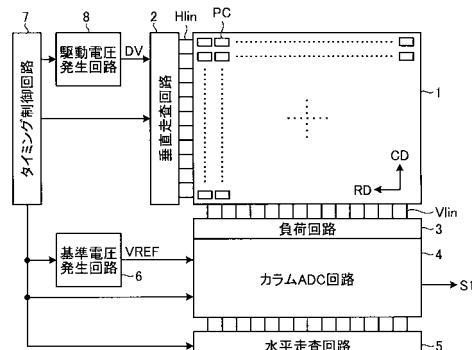

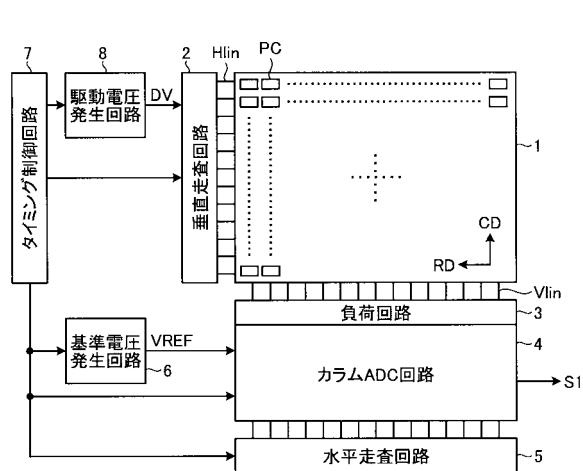

図1は、第1の実施形態に係る固体撮像装置の概略構成を示すブロック図である。

図1において、固体撮像装置には、画素アレイ部1が設けられている。画素アレイ部1には、光電変換した電荷を蓄積する画素PCがロウ方向RDおよびカラム方向CDにm( mは正の整数)行×n( nは正の整数)列分だけマトリックス状に配置されている。また、この画素アレイ部1において、ロウ方向RDには画素PCの読み出し制御を行う水平制御線H1inが設けられ、カラム方向CDには画素PCから読み出された信号を伝送する垂直信号線V1inが設けられている。

## 【0009】

また、固体撮像装置には、読み出し対象となる画素PCを垂直方向に走査する垂直走査回路2、画素PCとの間でソースフォロア動作を行うことにより、画素PCから垂直信号線V1inにカラムごとに画素信号を読み出す負荷回路3、各画素PCの信号成分をCD Sにてカラムごとに検出するカラムADC回路4、読み出し対象となる画素PCを水平方向に走査する水平走査回路5、カラムADC回路4に基準電圧VREFを出力する基準電圧発生回路6、各画素PCの読み出しや蓄積のタイミングを制御するタイミング制御回路7および画素PCの駆動時に画素PCを駆動する駆動電圧DVを発生する駆動電圧発生回路8が設けられている。駆動電圧発生回路8は、画素PCの駆動の開始のタイミングに基づいて駆動電圧DVを発生する駆動力を増大させることができる。なお、基準電圧VREFはランプ波を用いることができる。

40

## 【0010】

50

そして、垂直走査回路 2 にて画素 P C が垂直方向に走査されることで、ロウ方向 R D に画素 P C が選択され、駆動電圧発生回路 8 にて発生された駆動電圧 D V が画素 P C に供給される。そして、負荷回路 3 において、その画素 P C との間でソースフォロア動作が行われることにより、画素 P C から読み出された画素信号が垂直信号線 V 1 i n を介して伝送され、カラム A D C 回路 4 に送られる。また、基準電圧発生回路 6 において、基準電圧 V R E F としてランプ波が設定され、カラム A D C 回路 4 に送られる。そして、カラム A D C 回路 4 において、画素 P C から読み出された信号レベルとリセットレベルがランプ波のレベルに一致するまでクロックのカウント動作が行われ、その時の信号レベルとリセットレベルとの差分がとられることで各画素 P C の信号成分が C D S にて検出され、出力信号 S 1 として出力される。

10

## 【 0 0 1 1 】

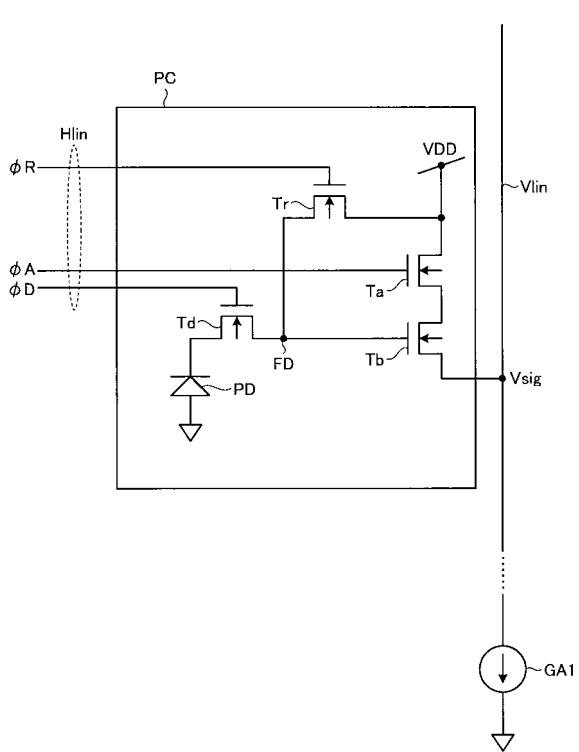

図 2 は、図 1 の固体撮像装置の画素の構成例を示す回路図である。

図 2 において、各画素 P C には、フォトダイオード P D、行選択トランジスタ T a、増幅トランジスタ T b、リセットトランジスタ T r および読み出しトランジスタ T d が設けられている。また、増幅トランジスタ T b とリセットトランジスタ T r と読み出しトランジスタ T d との接続点には検出ノードとしてフローティングディフュージョン F D が形成されている。

## 【 0 0 1 2 】

そして、画素 P C において、読み出しトランジスタ T d のソースは、フォトダイオード P D に接続され、読み出しトランジスタ T d のゲートには、読み出し信号 D が入力される。また、リセットトランジスタ T r のソースは、読み出しトランジスタ T d のドレインに接続され、リセットトランジスタ T r のゲートには、リセット信号 R が入力され、リセットトランジスタ T r のドレインは、電源電位 V D D に接続されている。また、行選択トランジスタ T a のゲートには、行選択信号 A が入力され、行選択トランジスタ T a のドレインは、電源電位 V D D に接続されている。また、増幅トランジスタ T b のソースは、垂直信号線 V 1 i n に接続され、増幅トランジスタ T b のゲートは、読み出しトランジスタ T d のドレインに接続され、増幅トランジスタ T b のドレインは、行選択トランジスタ T a のソースに接続されている。なお、図 1 の水平制御線 H 1 i n は、読み出し信号 D、リセット信号 R および行選択信号 A をロウごとに画素 P C に伝送することができる。図 1 の負荷回路 3 には定電流源 G A 1 がカラムごとに設けられ、定電流源 G A 1 は垂直信号線 V 1 i n に接続されている。なお、駆動電圧 D V は、行選択信号 A、読み出し信号 D およびリセット信号 R のパルス電圧として用いることができる。

20

## 【 0 0 1 3 】

図 3 は、図 1 の画素の読み出し動作時の各部の電圧波形を示すタイミングチャートである。

30

## 【 0 0 1 4 】

図 3 において、行選択信号 A がロウレベルの場合、行選択トランジスタ T a がオフ状態となりソースフォロワ動作しないため、垂直信号線 V 1 i n に信号は出力されない。この時、読み出し信号 D とリセット信号 R がハイレベルになると、読み出しトランジスタ T d がオンし、フォトダイオード P D に蓄積されていた電荷がフローティングディフュージョン F D に排出される。そして、リセットトランジスタ T r を介して電源電位 V D D に排出される。

40

## 【 0 0 1 5 】

フォトダイオード P D に蓄積されていた電荷が電源電位 V D D に排出された後、読み出し信号 D がロウレベルになると、フォトダイオード P D では、有効な信号電荷の蓄積が開始される。

## 【 0 0 1 6 】

次に、リセット信号 R が立ち上ると、リセットトランジスタ T r がオンし、フローティングディフュージョン F D にリーク電流などで発生した余分な電荷がリセットされる。

50

## 【0017】

そして、行選択信号 A がハイレベルになると、画素 P C の行選択トランジスタ T a がオンし、増幅トランジスタ T b のドレインに電源電位 V D D が印加されることで、増幅トランジスタ T b と定電流源 G A 1 とでソースフォロアが構成される。そして、フロータイミングディフュージョン F D のリセットレベル R L に応じた電圧が増幅トランジスタ T b のゲートにかかる。ここで、増幅トランジスタ T b と定電流源 G A 1 とでソースフォロアが構成されているので、増幅トランジスタ T b のゲートに印加された電圧に垂直信号線 V 1 i n の電圧が追従し、リセットレベル R L の画素信号 V s i g が垂直信号線 V 1 i n を介してカラム A D C 回路 4 に出力される。

## 【0018】

この時、基準電圧 V R E F としてランプ波 W R が与えられ、リセットレベル R L の画素信号 V s i g と基準電圧 V R E F とが比較される。そして、リセットレベル R L の画素信号 V s i g が基準電圧 V R E F のレベルと一致するまでダウンカウントされることで、リセットレベル R L の画素信号 V s i g がデジタル値 D R に変換され保持される。

## 【0019】

次に、読み出し信号 D が立ち上ると、読み出しトランジスタ T d がオンし、フォトダイオード P D に蓄積されていた電荷がフロータイミングディフュージョン F D に転送され、フロータイミングディフュージョン F D の信号レベル S L に応じた電圧が増幅トランジスタ T b のゲートにかかる。ここで、増幅トランジスタ T b と定電流源 G A 1 とでソースフォロアが構成されているので、増幅トランジスタ T b のゲートに印加された電圧に垂直信号線 V 1 i n の電圧が追従し、信号レベル S L の画素信号 V s i g が垂直信号線 V 1 i n を介してカラム A D C 回路 4 に出力される。

この時、基準電圧 V R E F としてランプ波 W S が与えられ、信号レベル S L の画素信号 V s i g と基準電圧 V R E F とが比較される。そして、信号レベル S L の画素信号 V s i g が基準電圧 V R E F のレベルと一致するまで今度はアップカウントされることで、信号レベル S L の画素信号 V s i g がデジタル値 D S に変換される。そして、リセットレベル R L の画素信号 V s i g と信号レベル S L の画素信号 V s i g との差分 D R - D S が保持され、出力信号 S 1 として出力される。

## 【0020】

図 4 は、図 1 の固体撮像装置の駆動電圧発生回路の構成例を示すブロック図である。なお、図 4 に示した画素アレイ部 1 では、画素 P C を容量 C で表した。駆動電圧 D V が行選択信号 A のパルス電圧として用いられる場合、容量 C は行選択トランジスタ T a のゲート容量である。駆動電圧 D V が読み出し信号 D のパルス電圧として用いられる場合、容量 C は読み出しトランジスタ T d のゲート容量である。駆動電圧 D V がリセット信号 R のパルス電圧として用いられる場合、容量 C はリセットトランジスタ T r のゲート容量である。

## 【0021】

図 4 において、駆動電圧発生回路 8 には、電圧分圧部 1 1 、参照電圧発生回路 1 2 、コンパレータ 1 3 、 A N D 回路 1 4 、 1 5 、チャージポンプ回路 1 6 、 1 7 およびレベルシフタ 1 8 が設けられている。電圧分圧部 1 1 は、チャージポンプ回路 1 6 、 1 7 から出力されるバイアス電圧 B I を分圧する。参照電圧発生回路 1 2 は参照電圧 V F を発生する。コンパレータ 1 3 は、電圧分圧部 1 1 にて生成された分圧電圧 V B と参照電圧 V F とを比較する。 A N D 回路 1 4 は、コンパレータ 1 3 の出力 P A に基づいてクロック C K をチャージポンプ回路 1 6 および A N D 回路 1 5 に出力する。 A N D 回路 1 5 は、画素 P C の駆動の開始のタイミングに基づいて A N D 回路 1 4 の出力をチャージポンプ回路 1 7 に出力する。チャージポンプ回路 1 6 は、自己の出力電圧に基づいて動作される。なお、チャージポンプ回路 1 6 は、画素 P C からの放電による電圧低下分を補償するように駆動力を設定することができる。チャージポンプ回路 1 7 は、画素 P C の駆動の開始時に動作される。なお、チャージポンプ回路 1 7 は、画素 P C の駆動の開始時の駆動電圧 D V の立ち上がり時間が短くなるように駆動力を設定することができる。レベルシフタ 1 8 は、画素 P C

10

20

30

40

50

の駆動時に駆動電圧 D V をバイアス電圧 B I にシフトさせる。また、タイミング制御回路 7 は、タイミング制御信号 P L をレベルシフタ 18 に出力し、タイミング制御信号 H U をチャージポンプ回路 17 に出力する。

#### 【0022】

そして、チャージポンプ回路 16、17 から出力されたバイアス電圧 B I は、電圧分圧部 11 で分圧され、コンパレータ 13 に出力される。また、参照電圧発生回路 12 で発生された参照電圧 V F はコンパレータ 13 に出力される。なお、この参照電圧 V F は、例えば、1 V 程度に設定することができる。バイアス電圧 B I は、例えば、3.8 V 以上に設定することができる。そして、電圧分圧部 11 で生成された分圧電圧 V B が参照電圧 V F を下回ると、コンパレータ 13 の出力 P A が立ち上がり、クロック CK が AND 回路 14 からチャージポンプ回路 16 および AND 回路 15 に供給される。チャージポンプ回路 16 にクロック CK が供給されると、チャージポンプ回路 16 が駆動され、バイアス電圧 B I の昇圧動作が行われる。また、電圧分圧部 11 で生成された分圧電圧 V B が参照電圧 V F を下回った状態でタイミング制御信号 H U が立ち上がると、クロック CK が AND 回路 15 からチャージポンプ回路 17 に供給される。チャージポンプ回路 17 にクロック CK が供給されると、チャージポンプ回路 17 が駆動され、バイアス電圧 B I の昇圧動作が行われる。

10

#### 【0023】

そして、バイアス電圧 B I の昇圧動作が行われた結果、電圧分圧部 11 で生成された分圧電圧 V B が参照電圧 V F を上回ると、コンパレータ 13 の出力 P A が立ち下がり、AND 回路 14 からのクロック CK の供給が停止される。

20

また、画素 P C が駆動される場合、タイミング制御信号 P L が立ち上がる。この結果、駆動電圧 D V がバイアス電圧 B I にシフトされ、画素 P C に供給される。この時、駆動電圧 D V にて容量 C が充電されるため、駆動電圧 D V が低下する。駆動電圧 D V が低下し、電圧分圧部 11 で生成された分圧電圧 V B が参照電圧 V F を下回ると、コンパレータ 13 の出力 P A が立ち上がる。このため、クロック CK がチャージポンプ回路 16 に供給され、バイアス電圧 B I の昇圧動作が行われる。また、タイミング制御信号 P L が立ち上がるタイミングでタイミング制御信号 H U が立ち上がると、クロック CK がチャージポンプ回路 17 に供給され、チャージポンプ回路 16 と協働してバイアス電圧 B I の昇圧動作が行われる。

30

#### 【0024】

ここで、画素 P C の駆動の開始時にチャージポンプ回路 16、17 が協働してバイアス電圧 B I の昇圧動作を行うことにより、駆動電圧 D V の立ち上がり時間を短くすることができ、画素 P C の高速駆動を図ることができる。また、画素 P C の駆動の開始時に駆動電圧 D V が立ち上がると、チャージポンプ回路 17 を停止させ、チャージポンプ回路 16 のみを駆動することができる。この時、画素 P C の駆動の開始時における駆動電圧 D V の立ち上がり時間の短縮に必要な駆動力をチャージポンプ回路 17 に受け持たせることができる。このため、チャージポンプ回路 16 の駆動力は、画素 P C からの放電による電圧低下分を補償するように設定すればよく、画素 P C の駆動の開始時における駆動電圧 D V の立ち上がり時間の短縮に必要な駆動力までチャージポンプ回路 16 に受け持たせた場合に比べて、チャージポンプ回路 16 の駆動力を低下させることができるとなる。この結果、チャージポンプ回路 16 のリップルによるノイズを低減することができとなり、画素 P C の駆動開始後におけるノイズを低減することができる。

40

#### 【0025】

図 5 は、図 4 のチャージポンプ回路の動作時の電圧波形を示すタイミングチャートである。なお、V 1 はチャージポンプ回路 16 にチャージポンプ回路 17 を追加した時の波形、V 2 はチャージポンプ回路 16 にチャージポンプ回路 17 を追加しない時の波形を示す。

図 5 において、チャージポンプ回路 16、17 が駆動されると、バイアス電圧 B I にはリップル W 1 が発生する。一方、チャージポンプ回路 17 がない場合、画素 P C の駆動開

50

始時（タイミング制御信号 P L の立ち上がり時）に、チャージポンプ回路 1 7 がある時と同じ立ち上がり時間に設定するには、チャージポンプ回路 1 7 がある場合に比べてチャージポンプ回路 1 6 の駆動力を上げる必要がある。このため、バイアス電圧 B I にはリップル W 1 よりも大きなりップル W 2 が発生する。

ここで、タイミング制御信号 H U のパルス幅 H 2 はタイミング制御信号 P L のパルス幅 H 1 よりも短くすることができる。これにより、タイミング制御信号 P L が立ち下がる前にタイミング制御信号 H U を立ち下げることができ、チャージポンプ回路 1 7 の駆動によるリップル W 1 の増大の影響を低減することができる。

#### 【0026】

また、チャージポンプ回路 1 7 の前段に A N D 回路 1 5 を設けることにより、電圧分圧部 1 1 で生成された分圧電圧 V B が、タイミング制御信号 H U が立ち下がる前に参照電圧 V F を上回った場合には、タイミング制御信号 H U が立ち下がる前にチャージポンプ回路 1 7 の昇圧動作を停止させることができ、チャージポンプ回路 1 7 の駆動によるリップル W 1 の増大の影響を低減することができる。

なお、タイミング制御信号 H U が立ち上がるタイミングは、行選択信号 A 、読み出し信号 D またはリセット信号 R が立ち上がるタイミングに比べて所定クロック数分だけそれぞれ遅らせてもよいし進ませてもよい。また、タイミング制御信号 H U が立ち下がるタイミングも、行選択信号 A 、読み出し信号 D またはリセット信号 R が立ち下がるタイミングに比べて所定クロック数分だけそれぞれ遅らせてもよいし進ませてもよい。

#### 【0027】

図 6 ( a ) は、図 4 の電圧分圧部の構成例を示す回路図、図 6 ( b ) は、図 4 の電圧分圧部のその他の構成例を示す回路図である。

図 6 ( a ) において、この電圧分圧部には、抵抗 R 1 、 R 2 が設けられている。抵抗 R 1 、 R 2 は互いに直列に接続されている。そして、バイアス電圧 B I が抵抗 R 1 の一端に印加されると、バイアス電圧 B I が抵抗 R 1 、 R 2 にて分圧され、抵抗 R 1 、 R 2 の接続点から分圧電圧 V B が出力される。

図 6 ( b ) において、この電圧分圧部には、容量 C 1 、 C 2 およびスイッチ W 1 ~ W 3 が設けられている。容量 C 1 、 C 2 は互いに直列に接続されている。バイアス電圧 B I と容量 C 1 との間にはスイッチ W 1 が接続されている。容量 C 2 と並列にスイッチ W 3 が接続されている。容量 C 1 、 C 2 の直列回路と並列にスイッチ W 2 が接続されている。

そして、スイッチ W 2 、 W 3 には信号 A が印加され、スイッチ W 1 には信号 B が印加される。なお、信号 B は信号 A を反転させた信号である。そして、信号 A が立ち上ると、スイッチ W 1 がオフ、スイッチ W 2 、 W 3 がオンし、容量 C 1 、 C 2 がリセットされる。次に、信号 A が立ち下がると、スイッチ W 1 がオン、スイッチ W 2 、 W 3 がオフする。そして、バイアス電圧 B I が容量 C 1 の一端に印加されると、バイアス電圧 B I が容量 C 1 、 C 2 にて分圧され、容量 C 1 、 C 2 の接続点から分圧電圧 V B が出力される。

#### 【0028】

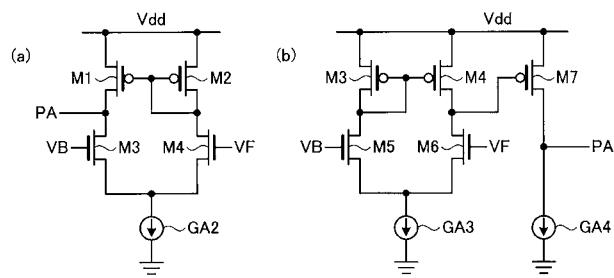

図 7 ( a ) は、図 4 のコンパレータの構成例を示す回路図、図 7 ( b ) は、図 4 のコンパレータのその他の構成例を示す回路図である。

図 7 ( a ) において、このコンパレータには、P チャネルトランジスタ M 1 、 M 2 、 N チャネルトランジスタ M 3 、 M 4 および電流源 G A 2 が設けられている。P チャネルトランジスタ M 1 と N チャネルトランジスタ M 3 は互いに直列に接続され、P チャネルトランジスタ M 2 と N チャネルトランジスタ M 4 は互いに直列に接続されている。N チャネルトランジスタ M 3 、 M 4 のソースは電流源 G A 2 に接続されている。P チャネルトランジスタ M 1 、 M 2 のゲートは N チャネルトランジスタ M 4 のドレインに接続されている。

#### 【0029】

N チャネルトランジスタ M 3 のゲートには分圧電圧 V B が印加され、N チャネルトランジスタ M 4 のゲートには参照電圧 V F が印加される。そして、分圧電圧 V B が参照電圧 V F を上回ると、N チャネルトランジスタ M 3 がオン、N チャネルトランジスタ M 4 がオフする。この結果、コンパレータ 1 3 の出力 P A が N チャネルトランジスタ M 3 を介して接

10

20

30

40

50

地され、コンパレータ 1 3 の出力 P A が立ち下がる。一方、分圧電圧 V B が参照電圧 V F を下回ると、N チャネルトランジスタ M 3 がオフ、N チャネルトランジスタ M 4 がオンする。この結果、P チャネルトランジスタ M 1 、M 2 がオンし、コンパレータ 1 3 の出力 P A が P チャネルトランジスタ M 1 を介して電源電位 V d d に接続され、コンパレータ 1 3 の出力 P A が立ち上がる。

【 0 0 3 0 】

図 7 ( b )において、このコンパレータには、P チャネルトランジスタ M 3 、M 4 、M 7 、N チャネルトランジスタ M 5 、M 6 および電流源 G A 3 、G A 4 が設けられている。P チャネルトランジスタ M 3 と N チャネルトランジスタ M 5 は互いに直列に接続され、P チャネルトランジスタ M 4 と N チャネルトランジスタ M 6 は互いに直列に接続されている。N チャネルトランジスタ M 5 、M 6 のソースは電流源 G A 3 に接続されている。P チャネルトランジスタ M 3 、M 4 のゲートは N チャネルトランジスタ M 5 のドレインに接続されている。P チャネルトランジスタ M 7 のゲートは N チャネルトランジスタ M 6 のドレインに接続されている。P チャネルトランジスタ M 7 のドレインは電流源 G A 4 に接続されている。

10

【 0 0 3 1 】

N チャネルトランジスタ M 5 のゲートには分圧電圧 V B が印加され、N チャネルトランジスタ M 6 のゲートには参照電圧 V F が印加される。そして、分圧電圧 V B が参照電圧 V F を上回ると、N チャネルトランジスタ M 6 がオフ、N チャネルトランジスタ M 5 がオンする。この結果、P チャネルトランジスタ M 4 がオン、P チャネルトランジスタ M 7 がオフし、コンパレータ 1 3 の出力 P A が立ち下がる。一方、分圧電圧 V B が参照電圧 V F を下回ると、N チャネルトランジスタ M 6 がオン、N チャネルトランジスタ M 5 がオフする。この結果、P チャネルトランジスタ M 7 がオンし、コンパレータ 1 3 の出力 P A が P チャネルトランジスタ M 7 を介して電源電位 V d d に接続され、コンパレータ 1 3 の出力 P A が立ち上がる。

20

【 0 0 3 2 】

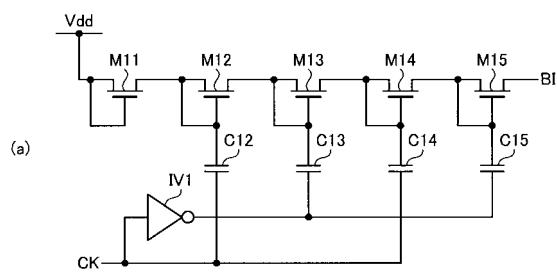

図 8 ( a )は、図 4 のチャージポンプ回路の構成例を示す回路図、図 8 ( b )は、図 4 のチャージポンプ回路のその他の構成例を示す回路図である。

図 8 ( a )において、このチャージポンプ回路には、N チャネルトランジスタ M 1 1 ~ M 1 5 、容量 C 1 2 ~ C 1 5 およびインバータ I V 1 が設けられている。N チャネルトランジスタ M 1 1 ~ M 1 5 は互いに直列に接続されている。N チャネルトランジスタ M 1 1 ~ M 1 5 のゲートは、N チャネルトランジスタ M 1 1 ~ M 1 5 のドレインにそれぞれ接続されている。

30

【 0 0 3 3 】

N チャネルトランジスタ M 1 2 、M 1 4 のゲートには、容量 C 1 2 、C 1 4 をそれぞれ介してクロック C K が印加され、N チャネルトランジスタ M 1 3 、M 1 5 のゲートには、インバータ I V 1 および容量 C 1 3 、C 1 5 をそれぞれ介してクロック C K が印加される。そして、N チャネルトランジスタ M 1 1 のゲートには電源電位 V d d が印加されるため、N チャネルトランジスタ M 1 1 がオンし、容量 C 1 2 が電源電位 V d d - V t h まで充電される。なお、V t h は N チャネルトランジスタ M 1 1 のしきいち電圧である。そして、クロック C K が立ち上がると、N チャネルトランジスタ M 1 2 、M 1 4 がオンし、容量 C 1 2 、C 1 4 に充電されていた電荷が N チャネルトランジスタ M 1 2 、M 1 4 をそれぞれ介して容量 C 1 3 、C 1 5 に送られる。一方、クロック C K が立ち下がると、N チャネルトランジスタ M 1 3 、M 1 5 がオンし、容量 C 1 3 に充電されていた電荷が N チャネルトランジスタ M 1 3 を介して容量 C 1 4 に送られるとともに、容量 C 1 5 の電圧がバイアス電圧 B I として出力される。

40

【 0 0 3 4 】

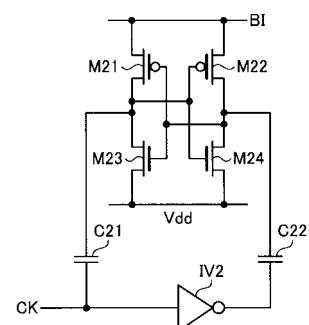

図 8 ( b )において、このチャージポンプ回路には、P チャネルトランジスタ M 2 1 、M 2 2 、N チャネルトランジスタ M 2 3 、M 2 4 、容量 C 2 1 、C 2 2 およびインバータ I V 2 が設けられている。P チャネルトランジスタ M 2 1 と N チャネルトランジスタ M 2

50

3は互いに直列に接続され、PチャネルトランジスタM22とNチャネルトランジスタM24は互いに直列に接続されている。PチャネルトランジスタM21およびNチャネルトランジスタM23のゲートはPチャネルトランジスタM22およびNチャネルトランジスタM24のドレインに接続され、PチャネルトランジスタM22およびNチャネルトランジスタM24のゲートはPチャネルトランジスタM21およびNチャネルトランジスタM23のドレインに接続されている。

【0035】

PチャネルトランジスタM21およびNチャネルトランジスタM23のゲートには、容量C21を介してクロックCKが印加され、PチャネルトランジスタM22およびNチャネルトランジスタM24のゲートには、インバータIV2および容量C22を介してクロックCKが印加される。そして、クロックCKが立ち上がると、PチャネルトランジスタM21およびNチャネルトランジスタM24がオン、PチャネルトランジスタM22およびNチャネルトランジスタM23がオフする。この結果、NチャネルトランジスタM24を介して容量C22が電源電位Vddまで充電される。一方、クロックCKが立ち下がると、PチャネルトランジスタM21およびNチャネルトランジスタM24がオフ、PチャネルトランジスタM22およびNチャネルトランジスタM23がオンする。この結果、NチャネルトランジスタM23を介して容量C21が電源電位Vddまで充電される。

【0036】

容量C21が電源電位Vddまで充電されている状態で、クロックCKが立ち上がると、PチャネルトランジスタM21がオン、NチャネルトランジスタM23がオフする。この結果、クロックCKのレベルが電源電位Vdd分だけ昇圧された電圧が、バイアス電圧BIとしてPチャネルトランジスタM21のソースから出力される。また、容量C22が電源電位Vddまで充電されている状態で、クロックCKが立ち下がると、PチャネルトランジスタM22がオン、NチャネルトランジスタM24がオフする。この結果、クロックCKのレベルが電源電位Vdd分だけ昇圧された電圧が、バイアス電圧BIとしてPチャネルトランジスタM22のソースから出力される。

【0037】

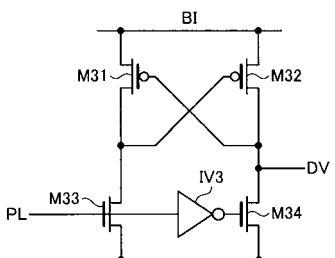

図9は、図4のレベルシフタの構成例を示す回路図である。

図9において、このレベルシフタには、PチャネルトランジスタM31、M32、NチャネルトランジスタM33、M34およびインバータIV3が設けられている。PチャネルトランジスタM31とNチャネルトランジスタM33は互いに直列に接続され、PチャネルトランジスタM32とNチャネルトランジスタM34は互いに直列に接続されている。PチャネルトランジスタM31のゲートはNチャネルトランジスタM34のドレインに接続され、PチャネルトランジスタM32のゲートはNチャネルトランジスタM33のドレインに接続されている。

【0038】

PチャネルトランジスタM31、M32のソースにはバイアス電圧BIが印加される。NチャネルトランジスタM33のゲートにはタイミング制御信号PLが印加され、NチャネルトランジスタM34のゲートにはインバータIV3を介してタイミング制御信号PLが印加される。そして、タイミング制御信号PLが立ち上がると、NチャネルトランジスタM33がオン、NチャネルトランジスタM34がオフする。この結果、PチャネルトランジスタM32のゲートがNチャネルトランジスタM33を介して接地され、PチャネルトランジスタM32がオンする。このため、駆動電圧DVがバイアス電圧BIにシフトされるとともに、PチャネルトランジスタM31がオフする。一方、タイミング制御信号PLが立ち下がると、NチャネルトランジスタM33がオフ、NチャネルトランジスタM34がオンする。この結果、駆動電圧DVが接地電圧にシフトされるとともに、PチャネルトランジスタM31がオン、PチャネルトランジスタM32がオフする。

【0039】

(第2実施形態)

図10は、第2実施形態に係る固体撮像装置が適用されたデジタルカメラの概略構成を

示すブロック図である。

図10において、デジタルカメラ21は、カメラモジュール22および後段処理部23を有する。カメラモジュール22は、撮像光学系24および固体撮像装置25を有する。後段処理部23は、イメージシグナルプロセッサ(ISP)26、記憶部27及び表示部28を有する。なお、固体撮像装置25は、図1の構成を用いることができる。また、ISP26の少なくとも一部の構成は固体撮像装置25とともに1チップ化するようにしてもよい。

#### 【0040】

撮像光学系24は、被写体からの光を取り込み、被写体像を結像させる。固体撮像装置25は、被写体像を撮像する。ISP26は、固体撮像装置25での撮像により得られた画像信号を信号処理する。記憶部27は、ISP26での信号処理を経た画像を格納する。記憶部27は、ユーザの操作等に応じて、表示部28へ画像信号を出力する。表示部28は、ISP26あるいは記憶部27から入力される画像信号に応じて、画像を表示する。表示部28は、例えば、液晶ディスプレイである。なお、カメラモジュール22は、デジタルカメラ21以外にも、例えばカメラ付き携帯電話やスマートフォン等の電子機器に適用するようにしてもよい。

#### 【0041】

なお、上述した固体撮像装置は、単層構造の半導体チップに形成されていてもよいし、積層構造の半導体チップに形成されていてもよい。

#### 【0042】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

#### 【符号の説明】

#### 【0043】

1 画素アレイ部、2 垂直走査回路、3 負荷回路、4 カラムADC回路、5 水平走査回路、6 基準電圧発生回路、7 タイミング制御回路、8 駆動電圧発生回路、PC 画素、Ta 行選択トランジスタ、Tb 増幅トランジスタ、Tr リセットトランジスタ、Td 読み出しトランジスタ、PD フォトダイオード、FD フローティングディフュージョン、Vlin 垂直信号線、Hlin 水平制御線

10

20

30

【図1】

【図2】

【図3】

【図4】

【図5】

【図 6】

【図 8】

【図 7】

【図 9】

【図 10】