(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2024-18354

(P2024-18354A)

(43)公開日 令和6年2月8日(2024.2.8)

(51)国際特許分類

**H 04 N 25/779 (2023.01)**

**H 04 N 25/40 (2023.01)**

F I

**H 04 N**    5/376

**H 04 N**    5/341

テーマコード(参考)

**5 C 0 2 4**

審査請求 未請求 請求項の数 15 O L (全28頁)

(21)出願番号 特願2022-121644(P2022-121644)

(22)出願日 令和4年7月29日(2022.7.29)

(71)出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100094112

弁理士 岡部 讓

(74)代理人 100101498

弁理士 越智 隆夫

(74)代理人 100106183

弁理士 吉澤 弘司

(74)代理人 100136799

弁理士 本田 亜希

(72)発明者 有嶋 優

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

岩田 公一郎

最終頁に続く

(54)【発明の名称】 光電変換装置及びその駆動方法

## (57)【要約】

【課題】駆動モードに応じて出力線間の電位ばらつきを効果的に抑制しうる光電変換装置を提供する。

【解決手段】光電変換装置は、複数の行及び複数の列をなすように配され、各々が光電変換部を有する複数の画素と、複数の列の各々に少なくとも2つが配され、それぞれが対応する列の画素に接続された複数の出力線と、複数の行のうちの一部の複数行を順次選択するように構成された走査回路と、走査回路に入力される制御信号とは別の制御信号が入力される入力部を備え、複数の行のうちの他の一部の行を選択するように構成された選択回路と、を有する。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

複数の行及び複数の列をなすように配され、各々が光電変換部を有する複数の画素と、前記複数の列の各々に少なくとも 2 つが配され、それぞれが対応する列の画素に接続された複数の出力線と、

前記複数の行のうちの一部の複数行を順次選択するように構成された走査回路と、前記走査回路に入力される制御信号とは別の制御信号が入力される入力部を備え、前記複数の行のうちの他の一部の行を選択するように構成された選択回路と

を有することを特徴とする光電変換装置。

**【請求項 2】**

前記走査回路及び前記選択回路を制御する制御回路を更に有し、

前記制御回路は、

前記走査回路により前記一部の複数行のうちの第 1 の行を選択し、前記第 1 の行の画素の信号を前記複数の出力線のうちの第 1 の出力線に出力する期間に、

前記選択回路により前記他の一部の行のうちの第 2 の行を選択し、前記第 2 の行の画素の信号を前記第 1 の出力線と同じ列に配された第 2 の出力線に出力する

ことを特徴とする請求項 1 記載の光電変換装置。

**【請求項 3】**

前記第 1 の出力線と前記第 2 の出力線とは隣接している

ことを特徴とする請求項 2 記載の光電変換装置。

20

**【請求項 4】**

前記他の一部の行に配された画素は、光電変換部を含まないヌル画素である

ことを特徴とする請求項 2 又は 3 記載の光電変換装置。

**【請求項 5】**

前記他の一部の行に配された画素は、光電変換部が遮光された遮光画素である

ことを特徴とする請求項 2 又は 3 記載の光電変換装置。

**【請求項 6】**

前記第 2 の出力線に出力される前記信号は、前記第 2 の行の画素から出力される N 信号である

ことを特徴とする請求項 4 記載の光電変換装置。

30

**【請求項 7】**

前記第 1 の出力線に出力される信号の用途と前記第 2 の出力線に出力される信号の用途

とが異なっている

ことを特徴とする請求項 2 又は 3 記載の光電変換装置。

**【請求項 8】**

前記選択回路に入力される前記制御信号は、同じ列に配された出力線のうち前記一部の複数行の画素からの信号が出力されない出力線に関する情報を含む

ことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の光電変換装置。

**【請求項 9】**

前記選択回路は、前記走査回路の外部に設けられている

ことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の光電変換装置。

40

**【請求項 10】**

前記選択回路は、前記走査回路に設けられている

ことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の光電変換装置。

**【請求項 11】**

前記一部の複数行に配された画素の各々は複数の光電変換部を有する

ことを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の光電変換装置。

**【請求項 12】**

複数の行及び複数の列をなすように配され、各々が光電変換部を有する複数の画素と、前記複数の列の各々に少なくとも 2 つが配され、それぞれが対応する列の画素に接続され

50

た複数の出力線と、前記複数の行のうちの一部の複数行を順次選択する走査回路と、前記複数の行のうちの他の一部の行を選択する選択回路と、を有する光電変換装置の駆動方法であって、

前記走査回路により前記一部の複数行のうちの第1の行を選択し、前記第1の行の画素の信号を前記複数の出力線のうちの第1の出力線に出力する期間に、

前記選択回路により前記他の一部の行のうちの第2の行を選択し、前記第2の行の画素の信号を前記第1の出力線と同じ列に配された第2の出力線に出力する

ことを特徴とする光電変換装置の駆動方法。

#### 【請求項 1 3】

請求項1乃至3のいずれか1項に記載の光電変換装置と、

10

前記光電変換装置から出力される信号を処理する信号処理装置と

を有することを特徴とする撮像システム。

#### 【請求項 1 4】

移動体であって、

請求項1乃至3のいずれか1項に記載の光電変換装置と、

前記光電変換装置からの信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と

を有することを特徴とする移動体。

#### 【請求項 1 5】

20

請求項1乃至3のいずれか1項に記載の光電変換装置と、

前記光電変換装置に対応する光学装置、

前記光電変換装置を制御する制御装置、

前記光電変換装置から出力された信号を処理する処理装置、

前記光電変換装置で得られた情報に基づいて制御される機械装置、

前記光電変換装置で得られた情報を表示する表示装置、及び、

前記光電変換装置で得られた情報を記憶する記憶装置、の少なくともいずれかと

を備えることを特徴とする機器。

#### 【発明の詳細な説明】

##### 【技術分野】

30

##### 【0 0 0 1】

本発明は、光電変換装置及びその駆動方法に関する。

##### 【背景技術】

##### 【0 0 0 2】

画素領域の各列に複数の出力線を配し、複数の画素行の画素信号をこれら複数の出力線に同時に読み出すことで画素信号を高速に読み出すように構成した光電変換装置が知られている。このような光電変換装置では、出力線間の電位ばらつきによって読み出す信号量が変化し、画質が劣化することがある。特許文献1には、画素リセット信号の読み出しの前に出力線を所定の電位に固定することで、出力線間の電位ばらつきを抑制し、出力線間で読み出す信号量が異なるように構成した撮像素子が記載されている。

40

##### 【先行技術文献】

##### 【特許文献】

##### 【0 0 0 3】

##### 【特許文献1】国際公開第2015/151793号

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0 0 0 4】

しかしながら、特許文献1に記載の撮像素子では、駆動モードによっては出力線間の電位ばらつきを十分に抑制できないことがあった。

##### 【0 0 0 5】

50

本発明の目的は、駆動モードに応じて出力線間の電位ばらつきを効果的に抑制しうる光電変換装置及びその駆動方法を提供することにある。

【課題を解決するための手段】

【0006】

本明細書の一開示によれば、複数の行及び複数の列をなすように配され、各々が光電変換部を有する複数の画素と、前記複数の列の各々に少なくとも2つが配され、それぞれが対応する列の画素に接続された複数の出力線と、前記複数の行のうちの一部の複数行を順次選択するように構成された走査回路と、前記走査回路に入力される制御信号とは別の制御信号が入力される入力部を備え、前記複数の行のうちの他の一部の行を選択するように構成された選択回路とを有する光電変換装置が提供される。

10

【0007】

また、本明細書の他の一開示によれば、複数の行及び複数の列をなすように配され、各々が光電変換部を有する複数の画素と、前記複数の列の各々に少なくとも2つが配され、それぞれが対応する列の画素に接続された複数の出力線と、前記複数の行のうちの一部の複数行を順次選択する走査回路と、前記複数の行のうちの他の一部の行を選択する選択回路と、を有する光電変換装置の駆動方法であって、前記走査回路により前記一部の複数行のうちの第1の行を選択し、前記第1の行の画素の信号を前記複数の出力線のうちの第1の出力線に出力する期間に、前記選択回路により前記他の一部の行のうちの第2の行を選択し、前記第2の行の画素の信号を前記第1の出力線と同じ列に配された第2の出力線に出力する光電変換装置の駆動方法が提供される。

20

【発明の効果】

【0008】

本発明によれば、駆動モードに応じて出力線間の電位ばらつきを効果的に抑制し、ノイズを低減した高品質な信号を出力することが可能となる。

【図面の簡単な説明】

【0009】

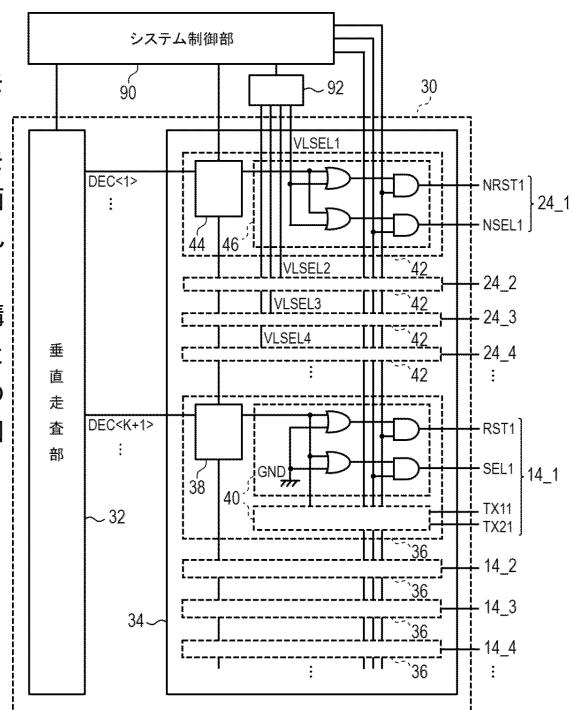

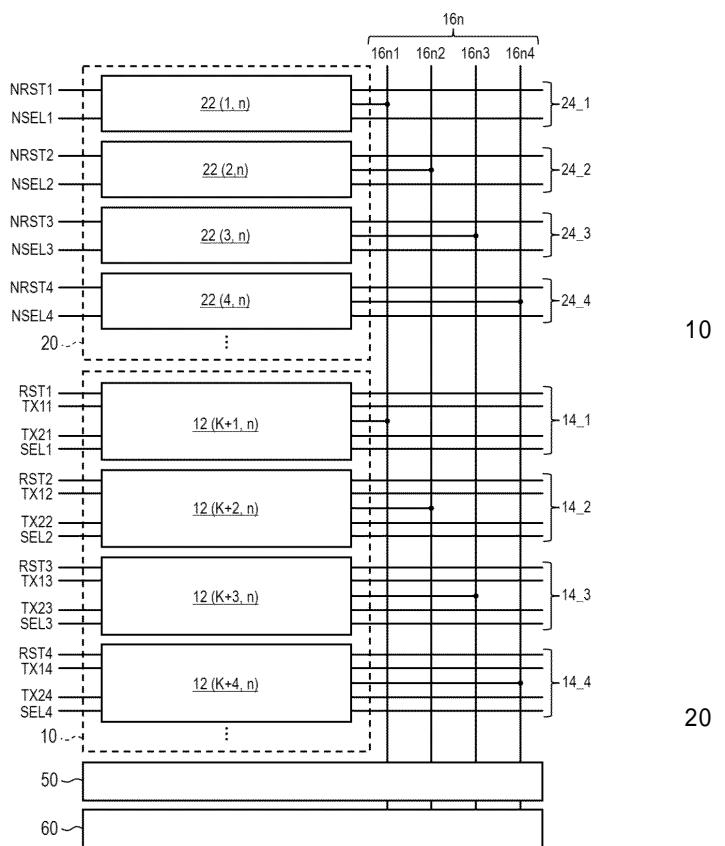

【図1】本発明の第1実施形態による光電変換装置の概略構成を示すブロック図である。

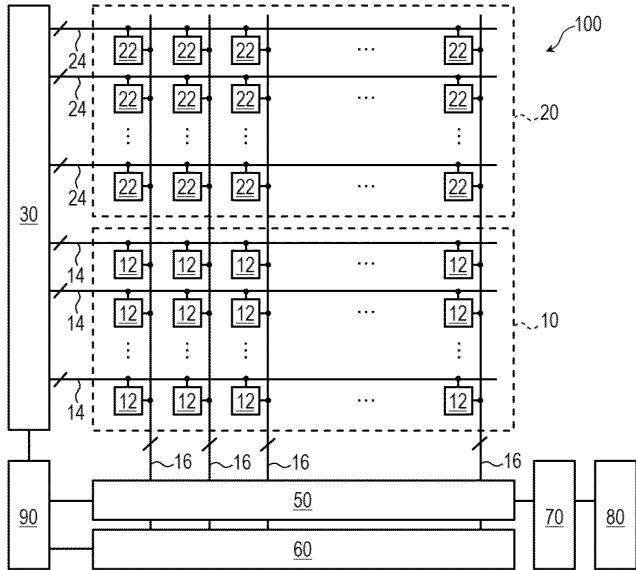

【図2】本発明の第1実施形態による光電変換装置における単位画素の構成例を示す等価回路図である。

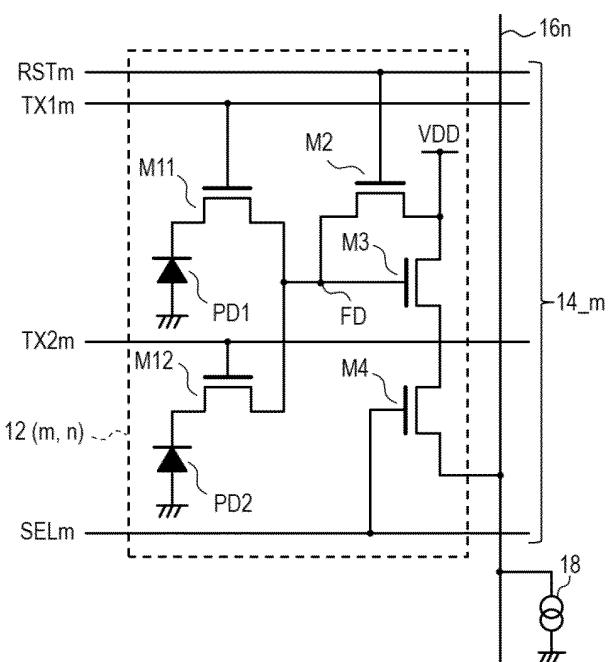

【図3】本発明の第1実施形態による光電変換装置におけるヌル画素の構成例を示す等価回路図である。

30

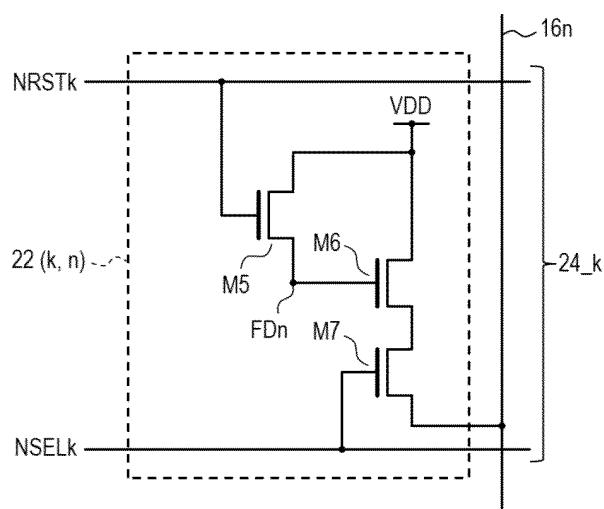

【図4】本発明の第1実施形態による光電変換装置における単位画素及びヌル画素の接続例を示す概略図である。

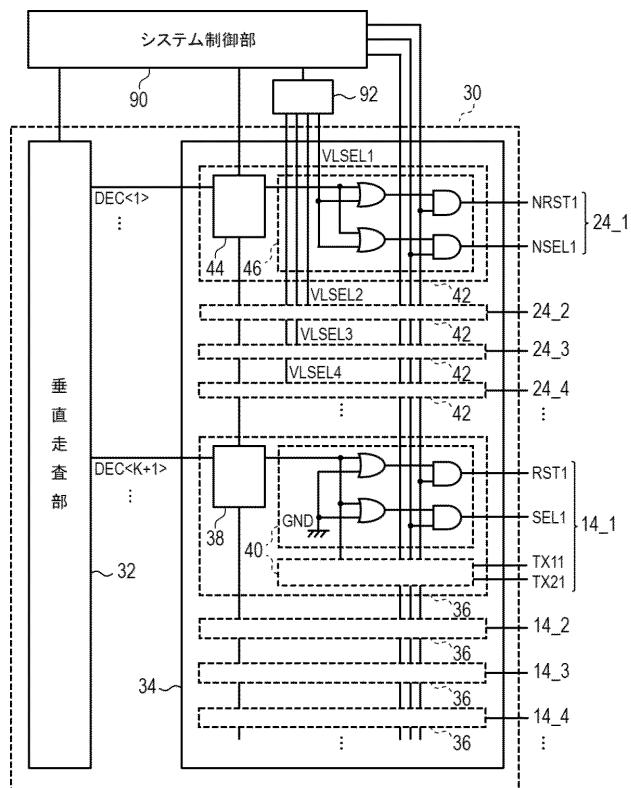

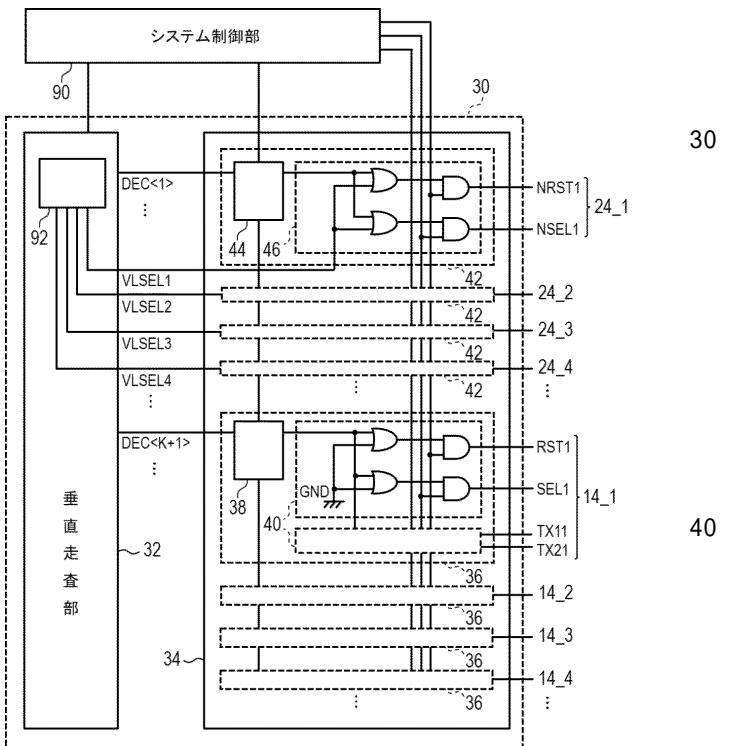

【図5】本発明の第1実施形態による光電変換装置における垂直駆動回路の構成例を示すブロック図である。

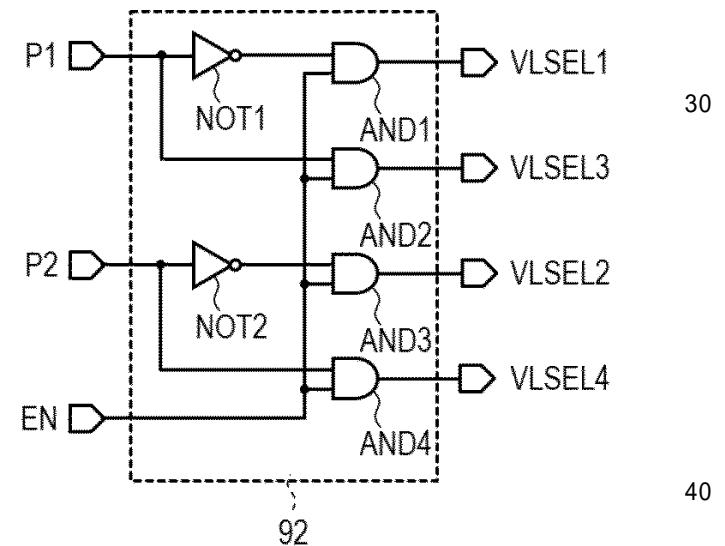

【図6】本発明の第1実施形態による光電変換装置における制御回路の構成例を示す回路図である。

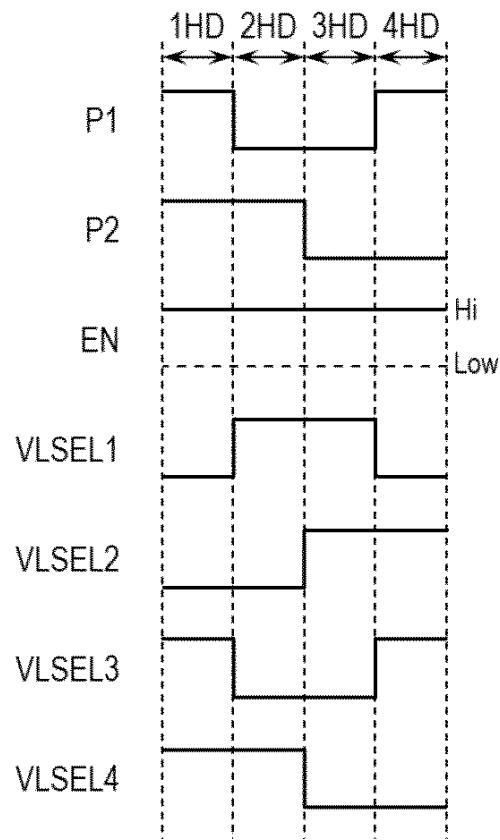

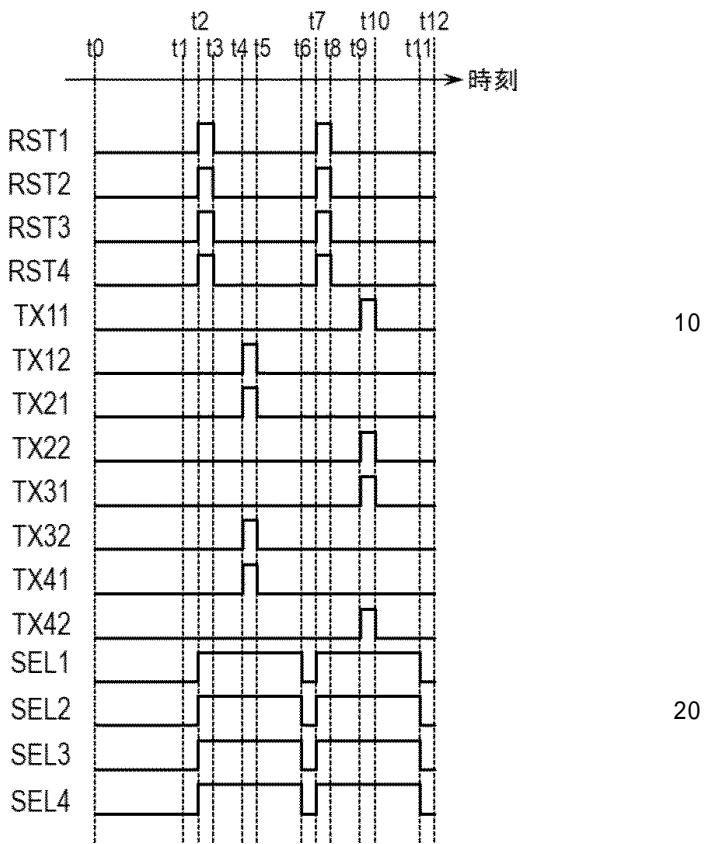

【図7】本発明の第1実施形態による光電変換装置における制御回路の動作を示すタイミング図である。

【図8】本発明の第1実施形態による光電変換装置の駆動例を示すタイミング図（その1）である。

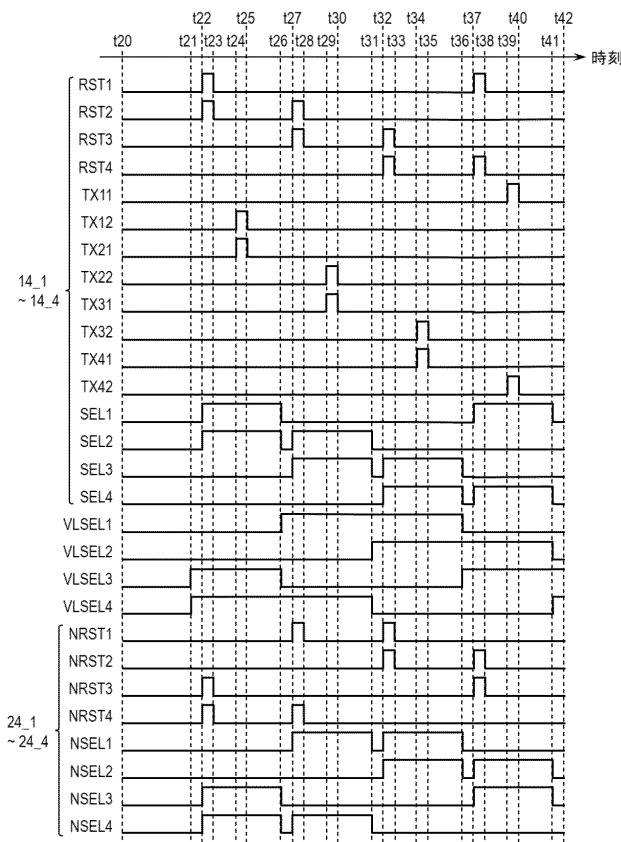

40

【図9】本発明の第1実施形態による光電変換装置の駆動例を示すタイミング図（その2）である。

【図10】本発明の第2実施形態による光電変換装置における垂直駆動回路の構成例を示すブロック図である。

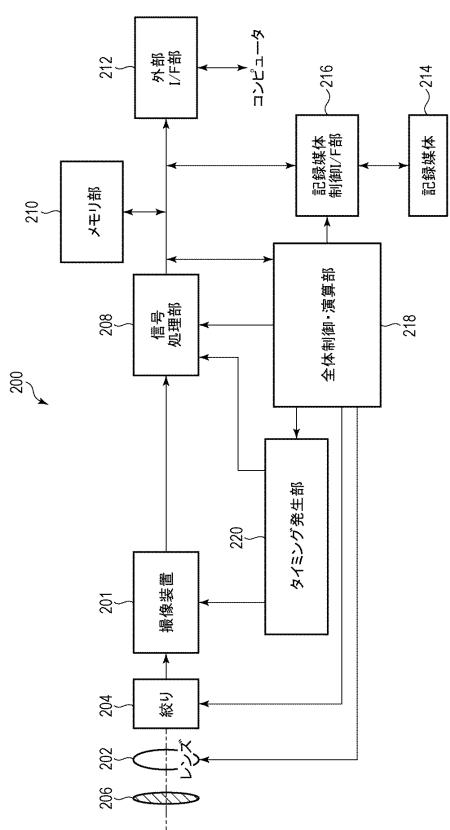

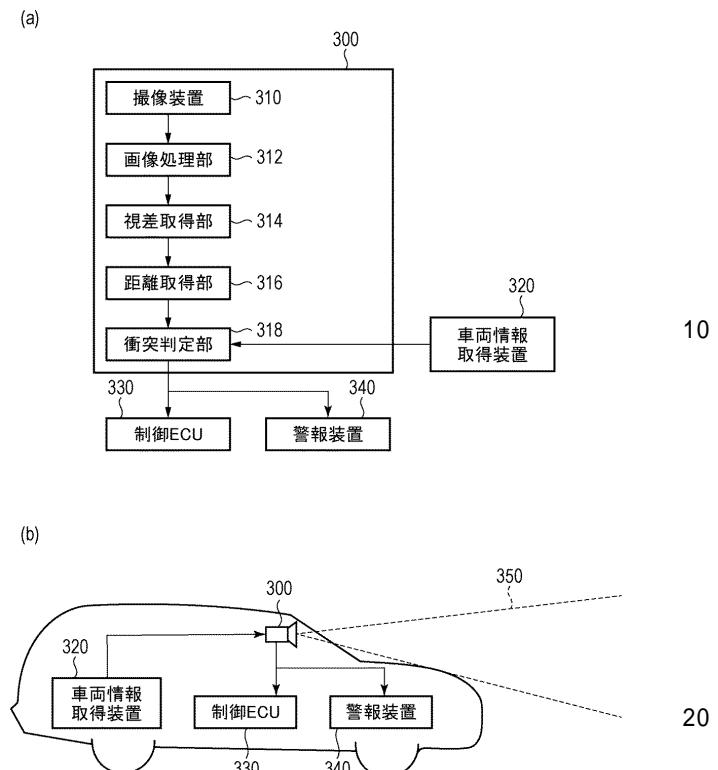

【図11】本発明の第3実施形態による撮像システムの概略構成を示すブロック図である。

【図12】本発明の第4実施形態による撮像システム及び移動体の構成例を示す図である。

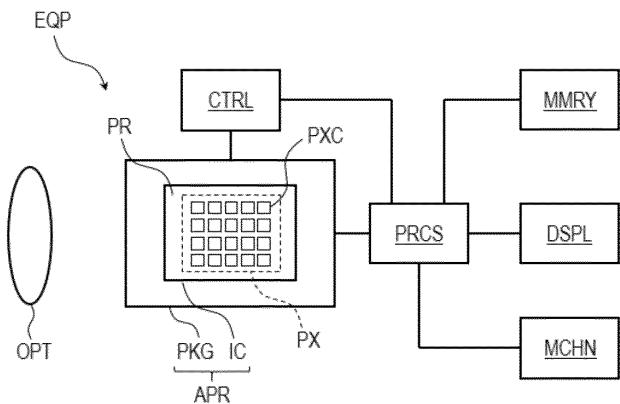

【図13】本発明の第5実施形態による機器の概略構成を示すブロック図である。

50

**【発明を実施するための形態】**

**【0010】**

**[第1実施形態]**

本発明の第1実施形態による光電変換装置について、図1乃至図5を用いて説明する。図1は、本実施形態による光電変換装置の概略構成を示すブロック図である。図2は、本実施形態による光電変換装置における単位画素の構成例を示す等価回路図である。図3は、本実施形態による光電変換装置におけるヌル画素の構成例を示す等価回路図である。図4は、本実施形態による光電変換装置における単位画素及びヌル画素の接続例を示す概略図である。図5は、本実施形態による光電変換装置における垂直駆動回路の構成例を示すブロック図である。

10

**【0011】**

本実施形態による光電変換装置100は、図1に示すように、画素領域10，20と、垂直駆動回路30と、列回路部50と、水平駆動回路60と、信号処理部70と、出力回路80と、システム制御部90と、を有する。

**【0012】**

画素領域10には、複数の行及び複数の列に渡って行列状に配された複数の単位画素12が設けられている。複数の単位画素12の各々は、フォトダイオード等の光電変換素子からなる光電変換部を含み、入射光の光量に応じた画素信号を出力する。なお、画素領域10には、入射光の光量に応じた画素信号を出力する有効画素のほか、光電変換部が遮光されたオプティカルブラック画素や、信号を出力しないダミー画素などが配置されていてもよい。

20

**【0013】**

画素領域20には、複数の行及び複数の列に渡って行列状に配された複数のヌル画素( NULL画素)22が設けられている。複数のヌル画素22の各々は、光電変換部を含まず、与えられた電圧に応じた所定の画素信号を出力する。

**【0014】**

画素領域20を構成する複数のヌル画素22は、画素領域10を構成する複数の単位画素12が配された列と同じ列の異なる行に配される。例えば、画素領域10にはM行×N列の行列状に配列された複数の単位画素12が配され、画素領域20にはK行×N列の行列状に配列された複数のヌル画素22が配され得る。この場合、画素領域20の先頭行を第1行とすると、第1行から第K行の各行にはN個のヌル画素22が配され、第(K+1)行から第(K+M)行の各行にはN個の単位画素12が配され得る。第1列から第N列の各列には、K個のヌル画素22とM個の単位画素12とが配され得る。なお、画素領域10，20に配される画素アレイの行数及び列数は、特に限定されるものではない。

30

**【0015】**

画素領域10の各行には、第1の方向(図1において横方向)に延在して、制御線14が配されている。制御線14の各々は、第1の方向に並ぶ単位画素12にそれぞれ接続され、これら単位画素12に共通の信号線をなしている。また、画素領域20の各行には、第1の方向に延在して、制御線24が配されている。制御線24の各々は、第1の方向に並ぶヌル画素22にそれぞれ接続され、これらヌル画素22に共通の信号線をなしている。制御線14，24の延在する第1の方向は、行方向或いは水平方向と呼ぶことがある。制御線14，24の各々は、複数の信号線を含み得る。制御線14，24は、垂直駆動回路30に接続されている。

40

**【0016】**

画素領域10，20の各列には、第1の方向と交差する第2の方向(図1において縦方向)に延在して垂直出力線16が配されている。垂直出力線16の各々は、第2の方向に並ぶ単位画素12及びヌル画素22に接続され、これら単位画素12及びヌル画素22に共通の信号線をなしている。垂直出力線16の延在する第2の方向は、列方向或いは垂直方向と呼ぶことがある。垂直出力線16の各々は、複数の出力線を含む。垂直出力線16は、列回路部50に接続されている。なお、単位画素12及びヌル画素22と垂直出力線

50

16との間の具体的な接続関係については後述する。

#### 【0017】

垂直駆動回路30は、システム制御部90から供給される制御信号を受け、単位画素12及びヌル画素22を駆動するための制御信号を生成し、制御線14, 24を介して単位画素12及びヌル画素22に供給する機能を備える制御回路である。垂直駆動回路30には、シフトレジスタやアドレスデコーダといった論理回路が用いられ得る。垂直駆動回路30は、各行の制御線14, 24に順次制御信号を供給し、画素領域10, 20の単位画素12及びヌル画素22を行単位で順次駆動する。行単位で単位画素12及びヌル画素22から読み出された信号は、画素領域10, 20の各列に設けられた垂直出力線16を介して列回路部50に入力される。

10

#### 【0018】

列回路部50は、画素領域10, 20の各列の垂直出力線16を構成する複数の出力線の各々に対応して設けられ、各々が処理回路及び信号保持回路を含む複数の列回路を有する。処理回路は、対応する出力線を介して出力される画素信号に対して所定の信号処理を行う機能を備える。処理回路が行う信号処理としては、例えば、増幅処理、相関二重サンプリング(CDS: Correlated Double Sampling)による補正処理、アナログ・デジタル変換(ADC変換)処理などが挙げられる。信号保持回路は、処理回路で処理された画素信号を保持するためのメモリとしての機能を備える。

#### 【0019】

水平駆動回路60は、システム制御部90から供給される制御信号を受け、列回路部50から画素信号を読み出すための制御信号を生成し、列回路部50に供給する機能を備える制御回路である。水平駆動回路60は、列回路部50の各列の列回路を順次走査し、各々に保持されている画素信号を、順次信号処理部70へと出力させる。水平駆動回路60には、シフトレジスタやアドレスデコーダといった論理回路が用いられ得る。

20

#### 【0020】

信号処理部70は、列回路部50から転送される画素信号に対して所定の信号処理を行う機能を備える。信号処理部70が実行する処理としては、例えば、演算処理や、増幅処理や、CDSによる補正処理などが挙げられる。

#### 【0021】

出力回路80は、外部インターフェース回路を有し、信号処理部70で処理された信号を光電変換装置100の外部へ出力するための回路である。出力回路80が備える外部インターフェース回路は、特に限定されるものではない。外部インターフェース回路には、例えば、LVDS(Low Voltage Differential Signaling)回路、SILV(Scalable Low Voltage Signaling)回路等のSerDes(SERializer/DESerializ)送信回路を適用可能である。

30

#### 【0022】

システム制御部90は、垂直駆動回路30、列回路部50及び水平駆動回路60等の動作を制御する制御信号を生成し、各機能ブロックに供給する制御回路である。なお、垂直駆動回路30、列回路部50及び水平駆動回路60等の動作を制御する制御信号は必ずしもシステム制御部90から供給される必要はなく、これらのうちの少なくとも一部は光電変換装置100の外部から供給されてもよい。

40

#### 【0023】

次に、本実施形態による光電変換装置における単位画素12の構成例について、図2を用いて説明する。図2には、画素領域10を構成する複数の単位画素12のうち、第m行、第n列に配された単位画素12(m, n)を抜き出して示している。ここで、mは1~Mの整数であり、nは1~Nの整数である。画素領域10を構成するその他の単位画素12の回路構成は、単位画素12(m, n)と同様であり得る。

#### 【0024】

単位画素12(m, n)は、例えば図2に示すように、光電変換素子PD1, PD2と、転送トランジスタM11, M12と、リセットトランジスタM2と、増幅トランジスタ

50

M3と、選択トランジスタM4と、により構成され得る。単位画素12(m,n)は、入射光が光電変換素子PD1, PD2に導かれるまでの光路上に配されたマイクロレンズ及びカラーフィルタを有していてもよい。マイクロレンズは、入射光を光電変換素子PD1, PD2に集光する。カラーフィルタは、所定の色の光を選択的に透過する。

#### 【0025】

光電変換素子PD1, PD2は、例えばフォトダイオードである。光電変換素子PD1は、アノードが基準電圧ノードに接続され、カソードが転送トランジスタM11のソースに接続されている。また、光電変換素子PD2は、アノードが基準電圧ノードに接続され、カソードが転送トランジスタM12のソースに接続されている。転送トランジスタM11のドレイン及び転送トランジスタM12のドレインは、リセットトランジスタM2のソース及び増幅トランジスタM3のゲートに接続されている。転送トランジスタM11のドレイン、転送トランジスタM12のドレイン、リセットトランジスタM2のソース及び増幅トランジスタM3のゲートが接続されるノードFDは、いわゆる浮遊拡散(フローティングディフュージョン)部である。浮遊拡散部は、容量成分(浮遊拡散容量)を含み、電荷保持部としての機能を備える。浮遊拡散容量には、pn接合容量や配線容量などが含まれ得る。リセットトランジスタM2のドレイン及び増幅トランジスタM3のドレインは、電源電圧(電圧VDD)が供給されるノードに接続されている。増幅トランジスタM3のソースは、選択トランジスタM4のドレインに接続されている。選択トランジスタM4のソースは、垂直出力線16nに接続されている。垂直出力線16nには、電流源18が接続されている。

#### 【0026】

図2の回路構成の場合、第m行の制御線14\_mは、転送トランジスタM11のゲート、転送トランジスタM12のゲート、リセットトランジスタM2のゲート及び選択トランジスタM4のゲートに接続された4本の信号線を含む。第m行の単位画素12の転送トランジスタM11のゲートには、垂直駆動回路30から制御信号TX1mが供給される。第m行の単位画素12の転送トランジスタM12のゲートには、垂直駆動回路30から制御信号TX2mが供給される。第m行の単位画素12のリセットトランジスタM2のゲートには、垂直駆動回路30から制御信号RSTMが供給される。第m行の単位画素12の選択トランジスタM4のゲートには、垂直駆動回路30から制御信号SELmが供給される。各トランジスタがN型MOSトランジスタで構成される場合、垂直駆動回路30からハイレベルの制御信号が供給されると対応するトランジスタがオンになる。また、垂直駆動回路30からローレベルの制御信号が供給されると対応するトランジスタがオフになる。

#### 【0027】

なお、本実施形態では、光入射によって光電変換素子PD1, PD2で生成される電子正孔対のうち、電子を信号電荷として用いる場合を想定して説明を行う。信号電荷として電子を用いる場合、単位画素12を構成する各トランジスタは、N型MOSトランジスタによって構成され得る。ただし、信号電荷は電子に限られるものではなく、正孔を信号電荷として用いてもよい。信号電荷として正孔を用いる場合、各トランジスタの導電型は、本実施形態で説明するものとは逆導電型となる。なお、MOSトランジスタのソース及びドレインの呼称はトランジスタの導電型や着目する機能によって異なることがある。本実施形態において使用するソース及びドレインの名称の一部又は全部は、逆の名称で呼ばれることがある。

#### 【0028】

光電変換素子PD1, PD2は、入射光をその光量に応じた量の電荷に変換(光電変換)し、生じた電荷を蓄積する。転送トランジスタM11は、オンになることにより光電変換素子PD1が保持する電荷をノードFDに転送する。転送トランジスタM12は、オンになることにより光電変換素子PD2が保持する電荷をノードFDに転送する。光電変換素子PD1, PD2から転送された電荷は、ノードFDの容量(浮遊拡散容量)に保持される。その結果、ノードFDは、浮遊拡散容量による電荷電圧変換によって、光電変換素子PD1, PD2から転送された電荷の量に応じた電位となる。

10

20

30

40

50

## 【 0 0 2 9 】

選択トランジスタM 4は、オンになることにより増幅トランジスタM 3を垂直出力線16nに接続する。増幅トランジスタM 3は、ドレインに電圧VDDが供給され、ソースに垂直出力線16n及び選択トランジスタM 4を介して電流源18からバイアス電流が供給される構成となっており、ゲートを入力ノードとする増幅部（ソースフォロワ回路）を構成する。これにより増幅トランジスタM 3は、ノードFDの電圧に基づく信号を、選択トランジスタM 4を介して垂直出力線16nに出力する。この意味で、増幅トランジスタM 3及び選択トランジスタM 4は、ノードFDに保持された電荷の量に応じた画素信号を出力する出力部である。

## 【 0 0 3 0 】

リセットトランジスタM 2は、電荷保持部としてのノードFDをリセットするための電圧（電圧VDD）のFDノードへの供給を制御する機能を備える。リセットトランジスタM 2は、オンになることによりノードFDを電圧VDDに応じた電圧にリセットする。この際、転送トランジスタM 1 1を同時にオンにすることで、光電変換素子PD 1を電圧VDDに応じた電圧にリセットすることも可能である。また、転送トランジスタM 1 2を同時にオンにすることで、光電変換素子PD 2を電圧VDDに応じた電圧にリセットすることも可能である。

## 【 0 0 3 1 】

転送トランジスタM 1 1, M 1 2、リセットトランジスタM 2及び選択トランジスタM 4を適宜制御することにより、各々の単位画素12からは、ノードFDのリセット電圧に応じた信号と光電変換素子PD 1, PD 2への入射光量に応じた信号とが読み出される。以下では、ノードFDのリセット電圧に応じた信号をノイズ信号（N信号）と呼び、光電変換素子PD 1, PD 2への入射光量に応じた信号を光電変換信号（S信号）と呼ぶものとする。

## 【 0 0 3 2 】

本実施形態の単位画素12は、2つの光電変換素子PD 1, PD 2が1つの浮遊拡散部（ノードFD）を共有している。このような単位画素12からは、光電変換素子PD 1で生成された電荷に基づく画素信号と、光電変換素子PD 2で生成された電荷に基づく信号と、を別々に読み出すことが可能である。この場合、まず、N信号と光電変換素子PD 1で生成された電荷に基づくS信号とを読み出し、次に、N信号と光電変換素子PD 2で生成された電荷に基づくS信号とを読み出すことができる。

## 【 0 0 3 3 】

次に、本実施形態による光電変換装置におけるヌル画素22の構成例について、図3を用いて説明する。図3には、画素領域20を構成する複数のヌル画素22のうち、第k行、第n列に配されたヌル画素22（k, n）を抜き出して示している。ここで、kは1～Kの整数であり、nは1～Nの整数である。画素領域20を構成するその他のヌル画素22の回路構成は、ヌル画素22（k, n）と同様であり得る。

## 【 0 0 3 4 】

ヌル画素22（k, n）は、例えば図3に示すように、リセットトランジスタM 5と、増幅トランジスタM 6と、選択トランジスタM 7と、により構成され得る。すなわち、ヌル画素22は、光電変換素子PD 1, PD 2及び転送トランジスタM 1 1, M 1 2を備えていない点で、単位画素12とは異なっている。リセットトランジスタM 5、増幅トランジスタM 6及び選択トランジスタM 7の物理的な構成は、単位画素12のリセットトランジスタM 2、増幅トランジスタM 3及び選択トランジスタM 4と同様であり得る。

## 【 0 0 3 5 】

リセットトランジスタM 5のソースは、増幅トランジスタM 6のゲートに接続されている。リセットトランジスタM 5のソースと増幅トランジスタM 6のゲートとが接続されるノードFDnは、単位画素12のノードFDと同様の浮遊拡散部である。リセットトランジスタM 5のドレイン及び増幅トランジスタM 6のドレインは、電源電圧（電圧VDD）が供給されるノードに接続されている。増幅トランジスタM 6のソースは、選択トランジ

10

20

30

40

50

スタM 7 のドレインに接続されている。選択トランジスタM 7 のソースは、垂直出力線 16 n に接続されている。

#### 【 0 0 3 6 】

図3の回路構成の場合、第k行の制御線 24\_k は、リセットトランジスタM5のゲート及び選択トランジスタM7のゲートに接続された2本の信号線を含む。第k行のヌル画素22のリセットトランジスタM5のゲートには、垂直駆動回路30から制御信号NRS\_T\_kが供給される。第k行のヌル画素22の選択トランジスタM7のゲートには、垂直駆動回路30から制御信号NSE\_L\_kが供給される。

#### 【 0 0 3 7 】

ヌル画素22のリセットトランジスタM5、増幅トランジスタM6及び選択トランジスタM7は、前述の通り、単位画素12のリセットトランジスタM2、増幅トランジスタM3及び選択トランジスタM4と同じ構成を有している。したがって、ヌル画素22からは、単位画素12のN信号から光電変換素子PD1, PD2及び転送トランジスタM11, M12の影響を除いたN信号が読み出される。

#### 【 0 0 3 8 】

次に、単位画素12及びヌル画素22と垂直出力線16との間の接続例について、図4を用いて説明する。なお、本実施形態では一例として、各列の垂直出力線16が4本の出力線を含む場合について説明を行うが、各列の垂直出力線16に含まれる出力線の数は4本に限定されるものではない。

#### 【 0 0 3 9 】

各列の垂直出力線16が4本の出力線によって構成される場合、第n列の垂直出力線16\_nは、例えば図4に示すように、出力線16\_n\_1と、出力線16\_n\_2と、出力線16\_n\_3と、出力線16\_n\_4と、を含む。画素領域20は、各列の垂直出力線16を構成する出力線の本数と同じ数の行を少なくとも含む。

#### 【 0 0 4 0 】

各々の単位画素12は、対応する列に配された垂直出力線16の4本の出力線のうちのいずれか1本に接続されている。例えば図4に示すように、第(K+1)行、第n列に配された単位画素12(K+1, n)は、第n列の垂直出力線16\_nを構成する出力線16\_n\_1に接続されている。第(K+2)行、第n列に配された単位画素12(K+2, n)は、第n列の垂直出力線16\_nを構成する出力線16\_n\_2に接続されている。第(K+3)行、第n列に配された単位画素12(K+3, n)は、第n列の垂直出力線16\_nを構成する出力線16\_n\_3に接続されている。第(K+4)行、第n列に配された単位画素12(K+4, n)は、第n列の垂直出力線16\_nを構成する出力線16\_n\_4に接続されている。第5行目以降の単位画素12についても、第1行から第4行の単位画素12と同様、4行周期で出力線16\_n\_1～16\_n\_4のうちのいずれかに接続されている。

#### 【 0 0 4 1 】

第(K+m)行に配された単位画素12には、垂直駆動回路30から、制御信号RST\_m, TX1\_m, TX2\_m, SEL\_mが供給される。例えば、第(K+1)行に配された単位画素12には、垂直駆動回路30から、制御信号RST1, TX1\_1, TX2\_1, SEL\_1が供給される。第2行に配された単位画素12には、垂直駆動回路30から、制御信号RST2, TX1\_2, TX2\_2, SEL\_2が供給される。第3行目以降の単位画素12についても同様である。

#### 【 0 0 4 2 】

本実施形態の単位画素12は、光電変換素子PD1及び転送トランジスタM11を含む画素と光電変換素子PD2及び転送トランジスタM12を含む画素とがリセットトランジスタM2、増幅トランジスタM3及び選択トランジスタM4を共有しているとも言える。単位画素12をこのように構成することで、リセットトランジスタM2、増幅トランジスタM3及び選択トランジスタM4を共有しない画素構成と比較して1画素当たりのトランジスタ数を減らすことができる。したがって、例えば光電変換素子の面積が同じであるレイアウトを想定した場合、リセットトランジスタM2、増幅トランジスタM3及び選択ト

10

20

30

40

50

ランジスタ M 4 を共有しない画素構成と比較して画素の微細化を図ることが可能である。

#### 【 0 0 4 3 】

各々のヌル画素 2 2 は、対応する列に配された垂直出力線 1 6 の 4 本の出力線のうちのいずれか 1 本に接続されている。例えば図 4 に示すように、第 1 行、第 n 列に配されたヌル画素 2 2 ( 1 , n ) は、第 n 列の垂直出力線 1 6 n を構成する出力線 1 6 n 1 に接続されている。第 2 行、第 n 列に配されたヌル画素 2 2 ( 2 , n ) は、第 n 列の垂直出力線 1 6 n 2 を構成する出力線 1 6 n 2 に接続されている。第 3 行、第 n 列に配されたヌル画素 2 2 ( 3 , n ) は、第 n 列の垂直出力線 1 6 n 3 を構成する出力線 1 6 n 3 に接続されている。第 4 行、第 n 列に配されたヌル画素 2 2 ( 4 , n ) は、第 n 列の垂直出力線 1 6 n 4 を構成する出力線 1 6 n 4 に接続されている。

10

#### 【 0 0 4 4 】

第 k 行に配されたヌル画素 2 2 には、垂直駆動回路 3 0 から、制御信号 N R S T k , N S E L k が供給される。例えば、第 1 行に配されたヌル画素 2 2 には、垂直駆動回路 3 0 から、制御信号 N R S T 1 , N S E L 1 が供給される。第 2 行に配されたヌル画素 2 2 には、垂直駆動回路 3 0 から、制御信号 N R S T 2 , N S E L 2 が供給される。第 3 行目以降のヌル画素 2 2 についても同様である。

#### 【 0 0 4 5 】

次に、本実施形態による光電変換装置における垂直駆動回路 3 0 の構成例について、図 5 を用いて説明する。

本実施形態による光電変換装置における垂直駆動回路 3 0 は、図 5 に示すように、垂直走査部 3 2 と、垂直論理部 3 4 と、を有する。垂直論理部 3 4 は、画素領域 1 0 を構成する M 個の行に対応する M 個の単位垂直論理部 3 6 と、画素領域 2 0 を構成する K 個の行に対応する K 個の単位垂直論理部 4 2 と、を有する。単位垂直論理部 3 6 の各々は、論理生成部 3 8 と、演算部 4 0 と、を有する。単位垂直論理部 4 2 の各々は、論理生成部 4 4 と、演算部 4 6 と、を有する。

20

#### 【 0 0 4 6 】

垂直走査部 3 2 は、画素領域 1 0 , 2 0 を構成する複数の行に対応する単位垂直論理部 3 6 , 4 2 を選択する選択回路としての役割を有する。垂直走査部 3 2 は、システム制御部 9 0 からの制御信号に応じて、画素領域 1 0 の各行に対応する行選択信号 D E C < K + 1 > ~ D E C < K + M > と、画素領域 2 0 の各行に対応する行選択信号 D E C < 1 > ~ D E C < K > と、を生成する。行選択信号 D E C < K + 1 > ~ D E C < K + M > は、単位垂直論理部 3 6 を選択するための選択信号であり、対応する行の単位垂直論理部 3 6 に入力される。垂直走査部 3 2 は、アドレスデコーダやシフトレジスタによって構成され得る。垂直走査部 3 2 がアドレスデコーダにより構成される場合、システム制御部 9 0 から入力される制御信号はアドレス信号であり、行選択信号 D E C < 1 > ~ D E C < K > , D E C < K + 1 > ~ D E C < K + M > はアドレス信号をデコードしたデコード信号である。

30

#### 【 0 0 4 7 】

行選択信号 D E C < 1 > ~ D E C < K > は、単位垂直論理部 4 2 を選択するための選択信号であり、対応する行の単位垂直論理部 4 2 に入力される。垂直走査部 3 2 は、画素領域 1 0 , 2 0 を構成する複数の行のうち、単位垂直論理部 3 6 に対応する一部の複数行を順次選択するように構成された走査回路でもある。行選択信号 D E C により各行が選択される構成は、単位垂直論理部 4 2 , 3 6 において同じである。また、各行の単位垂直論理部 4 2 には、システム制御部 9 0 による制御のもと制御回路 9 2 によって生成される制御信号 V L S E L k が入力される。

40

#### 【 0 0 4 8 】

第 k 行の単位垂直論理部 4 2 の論理生成部 4 4 は、行選択信号 D E C < k > 及びシステム制御部 9 0 からの制御信号に応じた論理値を出力する。第 k 行の単位垂直論理部 4 2 の演算部 4 6 は、論理生成部 4 4 から入力される論理値、システム制御部 9 0 からの制御信号及び制御回路 9 2 からの制御信号 V L S E L k に応じて制御信号 N R S T k , N S E L k を生成する。生成された制御信号 N R S T k , N S E L k は、制御線 2 4 \_ k を介して

50

ヌル画素 2 2 ( k , n ) に出力される。ここで、制御信号 V L S E L k は、出力線 1 6 n k に画素信号が読み出される水平走査期間であるのか、出力線 1 6 n k に画素信号が読み出されない水平走査期間であるのか、を判別するための信号である。

#### 【 0 0 4 9 】

演算部 4 6 は、制御信号 V L S E L k がハイレベルであり出力線 1 6 n k に画素信号が読み出されない水平走査期間である場合、行選択信号 D E C < k > に依らず、制御信号 N R S T k , N S E L k のヌル画素 2 2 ( k , n ) への出力を許容する。演算部 4 6 を構成する論理回路は、特に限定されるものではないが、例えば、論理生成部 4 4 の出力と制御信号 V L S E L k とを受ける O R 回路と、当該 O R 回路の出力とシステム制御部 9 0 からの制御信号とを受ける A N D 回路と、を含んで構成され得る。

10

#### 【 0 0 5 0 】

第 ( K + m ) 行の単位垂直論理部 3 6 の論理生成部 3 8 は、行選択信号 D E C < K + m > 及びシステム制御部 9 0 からの制御信号に応じた論理値を出力する。第 ( K + m ) 行の単位垂直論理部 3 6 の演算部 4 0 は、論理生成部 3 8 から入力される論理値及びシステム制御部 9 0 からの制御信号に応じて制御信号 R S T m , S E L m , T X 1 1 m , T X 2 1 m を生成する。生成された制御信号 R S T m , S E L m , T X 1 1 m , T X 2 1 m は、制御線 1 4 \_ m を介して単位画素 1 2 ( K + m , n ) に出力される。単位垂直論理部 3 6 は、行選択信号 D E C < K + m > に応じて、制御信号 R S T m , S E L m , T X 1 1 m , T X 2 1 m の単位画素 1 2 ( K + m , n ) への出力を制御する。つまり、単位垂直論理部 3 6 からは、行選択信号 D E C < K + m > によって選択されている期間以外は、制御線 1 4 \_ m に制御信号 R S T m , S E L m , T X 1 1 m , T X 2 1 m は供給されない。

20

#### 【 0 0 5 1 】

制御回路 9 2 は、画素領域 1 0 , 2 0 を構成する複数の行のうち、単位垂直論理部 4 2 に対応する他の一部の行を選択するように選択回路としての役割を有する。制御回路 9 2 は、垂直走査部 3 2 に入力される制御信号（例えば、アドレス信号）とは別の制御信号が入力される入力部を備える。制御回路 9 2 は、例えば図 6 に示すように、入力信号としてシステム制御部 9 0 からパルス信号 P 1 , P 2 及びイネーブル信号 E N を受け、制御信号 V L S E L 1 , V L S E L 2 , V L S E L 3 , V L S E L 4 を出力する回路として構成することができる。このような制御回路 9 2 を構成する論理回路は、特に限定されるものではないが、例えば図 6 に示すように、論理回路 N O T 1 , N O T 2 , A N D 1 , A N D 2 , A N D 3 , A N D 4 を含んで構成され得る。

30

#### 【 0 0 5 2 】

論理回路 N O T 1 の入力ノードには、パルス信号 P 1 が入力される。論理回路 N O T 2 の入力ノードには、パルス信号 P 2 が入力される。論理回路 A N D 1 の 2 つの入力ノードには、論理回路 N O T 1 の出力信号とイネーブル信号 E N とが入力される。論理回路 A N D 1 の出力信号が、制御信号 V L S E L 1 となる。論理回路 A N D 2 の 2 つの入力ノードには、パルス信号 P 1 とイネーブル信号 E N とが入力される。論理回路 A N D 2 の出力信号が、制御信号 V L S E L 3 となる。論理回路 A N D 3 の 2 つの入力ノードには、論理回路 N O T 2 の出力信号とイネーブル信号 E N とが入力される。論理回路 A N D 3 の出力信号が、制御信号 V L S E L 2 となる。論理回路 A N D 4 の 2 つの入力ノードには、パルス信号 P 2 とイネーブル信号 E N とが入力される。論理回路 A N D 4 の出力信号が、制御信号 V L S E L 4 となる。

40

#### 【 0 0 5 3 】

次に、制御回路 9 2 の動作について図 7 を用いて説明する。図 7 には、連続する 4 回の水平走査期間（第 1 水平走査期間 1 H D ~ 第 4 水平走査期間 4 H D ）における制御回路 9 2 の動作例を示している。パルス信号 P 1 , P 2 によって制御信号 V L S E L 1 ~ V L S E L 4 を生成する動作は、図 7 に示す 4 回の水平走査期間を 1 周期として繰り返され得る。

#### 【 0 0 5 4 】

パルス信号 P 1 は、第 1 水平走査期間 1 H D 及び第 4 水平走査期間 4 H D にハイレベル

50

となり、第2水平走査期間2HD及び第3水平走査期間3HDにおいてローレベルとなる。パルス信号P2は、第1水平走査期間1HD及び第2水平走査期間2HDにおいてハイレベルとなり、第3水平走査期間3HD及び第4水平走査期間4HDにおいてローレベルとなる。イネーブル信号ENは、第1水平走査期間1HDから第4水平走査期間4HDの間、ハイレベルである。

#### 【0055】

図7に示すように、イネーブル信号ENがハイレベルの状態において、パルス信号P1の反転パルスが制御信号VLS EL1となり、パルス信号P1の同相パルスが制御信号VLS EL3となる。また、イネーブル信号ENがハイレベルの状態において、パルス信号P2の反転パルスが制御信号VLS EL2となり、パルス信号P2の同相パルスが制御信号VLS EL4となる。

10

#### 【0056】

したがって、パルス信号P1, P2が図7のように遷移する場合、第1水平走査期間1HDには、制御信号VLS EL1, VLS EL2がローレベルとなり、制御信号VLS EL3, VLS EL4がハイレベルとなる。第2水平走査期間2HDには、制御信号VLS EL2, VLS EL3がローレベルとなり、制御信号VLS EL1, VLS EL4がハイレベルとなる。第3水平走査期間3HDには、制御信号VLS EL3, VLS EL4がローレベルとなり、制御信号VLS EL1, VLS EL2がハイレベルとなる。第4水平走査期間4HDには、制御信号VLS EL1, VLS EL4がローレベルとなり、制御信号VLS EL2, VLS EL3がハイレベルとなる。

20

#### 【0057】

次に、本実施形態による光電変換装置の駆動方法について、図8及び図9を用いて説明する。図8及び図9は、本実施形態による光電変換装置の駆動方法を示すタイミング図である。

#### 【0058】

まず、本実施形態による光電変換装置の基本的な駆動例について、図8を用いて説明する。ここでは、図4に示した単位画素12(K+1, n), 12(K+2, n), 12(K+3, n), 12(K+4, n)から画素信号を読み出す場合の動作を説明する。

#### 【0059】

以下の説明では、便宜上、これら単位画素12の構成要素のうち、光電変換素子PD1からの信号の読み出しに寄与する部分と光電変換素子PD2からの信号の読み出しに寄与する部分とを、それぞれ「画素」と呼ぶことがある。具体的には、単位画素12(K+1, n)に関し、光電変換素子PD1からの信号の読み出しに寄与する画素要素を画素A、光電変換素子PD2からの信号の読み出しに寄与する画素要素を画素Bとする。単位画素12(K+2, n)に関し、光電変換素子PD1からの信号の読み出しに寄与する画素要素を画素C、光電変換素子PD2からの信号の読み出しに寄与する画素要素を画素Dとする。単位画素12(K+3, n)に関し、光電変換素子PD1からの信号の読み出しに寄与する画素要素を画素E、光電変換素子PD2からの信号の読み出しに寄与する画素要素を画素Fとする。また、単位画素12(K+4, n)に関し、光電変換素子PD1からの信号の読み出しに寄与する画素要素を画素G、光電変換素子PD2からの信号の読み出しに寄与する画素要素を画素Hとする。

30

#### 【0060】

なお、光電変換素子PD1からの信号の読み出しに寄与する画素要素とは、光電変換素子PD1、転送トランジスタM11、リセットトランジスタM2、増幅トランジスタM3及び選択トランジスタM4である。また、光電変換素子PD2からの信号の読み出しに寄与する画素要素とは、光電変換素子PD2、転送トランジスタM12、リセットトランジスタM2、増幅トランジスタM3及び選択トランジスタM4である。

40

#### 【0061】

図8は、任意の時間において垂直出力線16を構成する全ての出力線が画素信号の読み出しに使用される駆動モードを示すタイミング図である。より具体的に言うと、各列の垂

50

直出力線 1 6 を構成する 4 本の出力線の各々が各水平走査期間の間に単位画素 1 2 と接続され、4 つの出力線からそれぞれ画素信号を読み出すモードである。図 8 には、垂直駆動回路 3 0 から供給される制御信号 R S T 1 ~ R S T 4 , T X 1 1 ~ T X 4 2 , S E L 1 ~ S E L 4 を示している。本駆動例では、画素領域 2 0 のヌル画素 2 2 からの信号の読み出しは行わない。

#### 【 0 0 6 2 】

時刻 t 0 から時刻 t 1 までの期間は読み出し開始前の状態である。この期間において、総ての制御信号 R S T 1 ~ R S T 4 , T X 1 1 ~ T X 4 2 , S E L 1 ~ S E L 4 はローレベル、すなわち非アクティブの状態である。

#### 【 0 0 6 3 】

時刻 t 1 から時刻 t 6 までの期間は、画素 B 、画素 C 、画素 F 及び画素 G の各々から N 信号及び S 信号の読み出しを行う 1 水平走査期間に対応する。

#### 【 0 0 6 4 】

時刻 t 2 において、垂直駆動回路 3 0 は、制御信号 R S T 1 , R S T 2 , R S T 3 , R S T 4 , S E L 1 , S E L 2 , S E L 3 , S E L 4 をローレベルからハイレベルに制御する。これにより、単位画素 1 2 ( K + 1 , n ) ~ 1 2 ( K + 4 , n ) の選択トランジスタ M 4 がオンになり、単位画素 1 2 ( K + 1 , n ) ~ 1 2 ( K + 4 , n ) が出力線 1 6 n 1 ~ 1 6 n 4 に接続される。また、単位画素 1 2 ( K + 1 , n ) ~ 1 2 ( K + 4 , n ) のリセットトランジスタ M 2 がオンになり、ノード F D のリセット動作が開始される。

#### 【 0 0 6 5 】

続く時刻 t 3 において、垂直駆動回路 3 0 は、制御信号 R S T 1 , R S T 2 , R S T 3 , R S T 4 をハイレベルからローレベルに制御する。これにより、単位画素 1 2 ( K + 1 , n ) ~ 1 2 ( K + 4 , n ) のリセットトランジスタ M 2 がオフになり、ノード F D のリセット状態が解除される。リセットトランジスタ M 2 がオフになる際、ノード F D の電位はリセットトランジスタ M 2 のゲートとの間のカップリングによって所定の電位まで振り下がる。リセットトランジスタ M 2 がオフになった後に静定するノード F D の電圧が、ノード F D のリセット電圧である。

#### 【 0 0 6 6 】

これにより、出力線 1 6 n 1 には単位画素 1 2 ( K + 1 , n ) のノード F D のリセット電圧に応じた信号が増幅トランジスタ M 3 及び選択トランジスタ M 4 を介して出力される。同様に、出力線 1 6 n 2 ~ 1 6 n 3 にも、単位画素 1 2 ( K + 2 , n ) ~ 1 2 ( K + 4 , n ) のノード F D のリセット電圧に応じた信号が出力される。

#### 【 0 0 6 7 】

単位画素 1 2 ( K + 1 , n ) から出力線 1 6 n 1 に出力された信号は、後段の列回路部 5 0 で処理され、画素 B の N 信号として読み出される。同様に、単位画素 1 2 ( K + 2 , n ) ~ 1 2 ( K + 4 , n ) から出力線 1 6 n 2 ~ 1 6 n 4 に出力された信号は、画素 C 、画素 F 及び画素 G の N 信号として読み出される。

#### 【 0 0 6 8 】

続く時刻 t 4 において、垂直駆動回路 3 0 は、制御信号 T X 1 2 , T X 2 1 , T X 3 2 , T X 4 1 をローレベルからハイレベルに制御する。これにより、単位画素 1 2 ( K + 2 , n ) , 1 2 ( K + 4 , n ) の転送トランジスタ M 1 1 がオンになり、所定の露光期間の間に単位画素 1 2 ( K + 2 , n ) , 1 2 ( K + 4 , n ) の光電変換素子 P D 1 に蓄積された電荷がノード F D に転送される。また、単位画素 1 2 ( K + 1 , n ) , 1 2 ( K + 3 , n ) の転送トランジスタ M 1 2 がオンになり、所定の露光期間の間に単位画素 1 2 ( K + 1 , n ) , 1 2 ( K + 3 , n ) の光電変換素子 P D 2 に蓄積された電荷がノード F D に転送される。

#### 【 0 0 6 9 】

これにより、単位画素 1 2 ( 1 , n ) の光電変換素子 P D 2 で生じた電荷の量に応じた信号が増幅トランジスタ M 3 及び選択トランジスタ M 4 を介して出力線 1 6 n 1 に出力される。同様に、単位画素 1 2 ( 2 , n ) の光電変換素子 P D 1 で生じた電荷の量に応じた

10

20

30

40

50

信号が増幅トランジスタM3及び選択トランジスタM4を介して出力線16n2に出力される。また、単位画素12(3,n)の光電変換素子PD2で生じた電荷の量に応じた信号が増幅トランジスタM3及び選択トランジスタM4を介して出力線16n3に出力される。また、単位画素12(4,n)の光電変換素子PD1で生じた電荷の量に応じた信号が増幅トランジスタM3及び選択トランジスタM4を介して出力線16n4に出力される。

#### 【0070】

続く時刻t5において、垂直駆動回路30は、制御信号TX12, TX21, TX32, TX41をハイレベルからロー・レベルに制御する。これにより、単位画素12(K+1, n)~12(K+4, n)における光電変換素子PD1, PD2からノードFDへの電荷の転送期間が終了する。単位画素12(K+1, n)から出力線16n1に出力された信号は、静定後に後段の列回路部50で処理され、画素BのS信号として読み出される。同様に、単位画素12(K+2, n)~12(K+4, n)から出力線16n2~16n4に出力された信号は、画素C、画素F及び画素GのS信号として読み出される。

10

#### 【0071】

続く時刻t6において、垂直駆動回路30は、制御信号SEL1, SEL2, SEL3, SEL4をハイレベルからロー・レベルに制御する。これにより、読み出しが行われた単位画素12(K+1, n)~12(K+4, n)の選択トランジスタM4がオフになり、単位画素12(K+1, n)~12(K+4, n)が出力線16n1~16n4から切り離される。

20

#### 【0072】

続く時刻t7から時刻t11までの期間は、時刻t2から時刻t6の期間と同様にして画素A、画素D、画素E及び画素Hの各々からN信号及びS信号の読み出しを行う1水平走査期間に対応する。

#### 【0073】

このようにして、時刻t1から時刻t11までの2つの水平走査期間を経て、画素A、画素B、画素C、画素D、画素E、画素F、画素G及び画素Hの8画素からの画素信号の読み出しを行う。この後、同様の手順により、第5行目から4行単位で画素領域10を順次走査し、画素領域10の全体から画素信号の読み出しを行う。

30

#### 【0074】

次に、各列の垂直出力線16を構成する4本の出力線のうちの2本を単位画素12と接続し、出力線に接続したこれら単位画素12からそれぞれ画素信号を読み出す駆動例について、図9を用いて説明する。

#### 【0075】

一列の垂直出力線を構成する複数の出力線について、近接する出力線の間には寄生容量が存在する。特許文献1に記載の固体撮像素子では、一列の垂直出力線を構成する複数の出力線のうちの一部の出力線から画素信号を読み出す場合、他の出力線は読み出し前に所定の電圧に固定する。そのため、画素信号を読み出す出力線と読み出さない出力線との間の寄生容量を通じた影響は、近接する出力線の電位状態によって異なることになる。その結果、垂直出力線を構成する出力線の間で、リセット信号の読み出し時における垂直出力線からノードFDへのカップリング量やリセット信号の静定時間にばらつきが発生することがある。同じ黒レベルの画像を撮影した際には、出力線間で読み出す信号量が異なることになり、画像として段差が発生し画質が劣化してしまう。このような課題を改善するために、本駆動例では、単位画素12からの信号を出力しない出力線に、ヌル画素22からの信号を出力する。

40

#### 【0076】

図9は、任意の時間において垂直出力線16を構成する出力線のうちの一部が画素信号の読み出しに使用されない駆動モードを示すタイミング図である。図9には、垂直駆動回路30から供給される制御信号RST1~RST4, TX11~TX42, SEL1~SEL4, NRST1~NRST4, NSEL1~NSEL4を示している。また、図9に

50

は、制御回路 9 2 から垂直駆動回路 3 0 に供給される制御信号 V L S E L 1 ~ V L S E L 4 を示している。各制御信号は、ハイレベルのときがアクティブ状態であり、ローレベルのときが非アクティブ状態であるものとする。

#### 【 0 0 7 7 】

時刻 t 2 0 から時刻 t 2 1 までの期間は読み出し開始前の状態である。この期間において、総ての制御信号 R S T 1 ~ 4 , T X 1 1 ~ 4 2 , S E L 1 ~ 4 , N R S T 1 ~ 4 , N S E L 1 ~ N S E L 4 は Low レベル、すなわち非アクティブの状態である。また、不図示のイネーブル信号 E N はローレベルであり、制御信号 V L S E L 1 ~ V L S E L 4 もローレベルになっている。

#### 【 0 0 7 8 】

時刻 t 2 1 から時刻 t 2 6 までの期間は、画素 B 及び画素 C の各々から N 信号及び S 信号の読み出しを行う 1 水平走査期間に対応する。この 1 水平走査期間は、図 8 における第 1 水平走査期間 1 H D に対応している。

#### 【 0 0 7 9 】

時刻 t 2 1 において、システム制御部 9 0 は、制御回路 9 2 に供給するイネーブル信号 E N 及びパルス信号 P 1 , P 2 をローレベルからハイレベルに制御する。これにより、制御信号 V L S E L 1 , V L S E L 2 はローレベル、制御信号 V L S E L 3 , V L S E L 4 はハイレベルになる。

#### 【 0 0 8 0 】

続く時刻 t 2 2 において、垂直駆動回路 3 0 は、制御信号 R S T 1 , R S T 2 , S E L 1 , S E L 2 をローレベルからハイレベルに制御する。これにより、単位画素 1 2 ( K + 1 , n ) , 1 2 ( K + 2 , n ) の選択トランジスタ M 4 がオンになり、単位画素 1 2 ( K + 1 , n ) が出力線 1 6 n 1 に、単位画素 1 2 ( K + 2 , n ) が出力線 1 6 n 2 に、それぞれ接続される。また、単位画素 1 2 ( K + 1 , n ) , 1 2 ( K + 2 , n ) のリセットトランジスタ M 2 がオンになり、ノード F D のリセット動作が開始される。

#### 【 0 0 8 1 】

また、同じく時刻 t 2 2 において、垂直駆動回路 3 0 は、制御信号 V L S E L 3 , V L S E L 4 がハイレベルであることに応じて、制御信号 N R S T 3 , N R S T 4 , N S E L 3 , N S E L 4 をローレベルからハイレベルに制御する。これにより、ヌル画素 2 2 ( 3 , n ) , 2 2 ( 4 , n ) の選択トランジスタ M 7 がオンになり、ヌル画素 2 2 ( 3 , n ) が出力線 1 6 n 3 に、ヌル画素 2 2 ( 4 , n ) が出力線 1 6 n 4 に、それぞれ接続される。また、ヌル画素 2 2 ( 3 , n ) , 2 2 ( 4 , n ) のリセットトランジスタ M 5 がオンになり、ノード F D n のリセット動作が開始される。

#### 【 0 0 8 2 】

続く時刻 t 2 3 において、垂直駆動回路 3 0 は、制御信号 R S T 1 , R S T 2 , N R S T 3 , N R S T 4 をハイレベルからローレベルに制御する。これにより、単位画素 1 2 ( K + 1 , n ) , 1 2 ( K + 2 , n ) のリセットトランジスタ M 2 がオフになり、ノード F D のリセット状態が解除される。リセットトランジスタ M 2 がオフになる際、ノード F D の電位はリセットトランジスタ M 2 のゲートとの間のカッピングによって所定の電位まで振り下がる。リセットトランジスタ M 2 がオフになった後に静定するノード F D の電圧が、ノード F D のリセット電圧である。また、ヌル画素 2 2 ( 3 , n ) , 2 2 ( 4 , n ) のリセットトランジスタ M 5 がオフになり、ノード F D n のリセット状態が解除される。リセットトランジスタ M 5 がオフになる際、ノード F D n の電位はリセットトランジスタ M 5 のゲートとの間のカッピングによって所定の電位まで振り下がる。リセットトランジスタ M 5 がオフになった後に静定するノード F D n の電圧が、ノード F D n のリセット電圧である。

#### 【 0 0 8 3 】

これにより、出力線 1 6 n 1 には単位画素 1 2 ( K + 1 , n ) のノード F D のリセット電圧に応じた信号が出力され、出力線 1 6 n 2 には単位画素 1 2 ( K + 2 , n ) のノード F D のリセット電圧に応じた信号が出力される。また、出力線 1 6 n 3 にはヌル画素 2 2

10

20

30

40

50

(3, n) のノード F D n のリセット電圧に応じた信号が出力され、出力線 1 6 n 4 にはヌル画素 2 2 (4, n) のノード F D n のリセット電圧に応じた信号が出力される。

#### 【0084】

垂直出力線 1 6 n を構成する出力線の過渡的な電位変化は、垂直出力線 1 6 n を構成する他の出力線との間のカップリングなどの寄生容量成分や配線の寄生抵抗成分などに影響される。例えば、出力線 1 6 n 1 はこれに隣接する出力線 1 6 n 2 とカップリングされ、出力線 1 6 n 2 はこれに隣接する出力線 1 6 n 1, 1 6 n 3 とカップリングされる。

#### 【0085】

時刻 t 2 2 から時刻 t 2 4 の期間において、出力線 1 6 n 1 には画素 B の N 信号の読み出しによる電位の変化が生じてあり、出力線 1 6 n 2 には画素 C の N 信号の読み出しによる電位の変化が生じている。このとき、出力線 1 6 n 3, 1 6 n 4 には、単位画素 1 2 を構成する画素の N 信号は読み出されない。ところが、出力線 1 6 n 3 にはヌル画素 2 2 (3, n) の N 信号の読み出しによる電位の変化が生じており、出力線 1 6 n 4 にはヌル画素 2 2 (4, n) の N 信号の読み出しによる電位の変化が生じている。

#### 【0086】

このようにして、単位画素 1 2 からの N 信号を読み出さない出力線にヌル画素 2 2 からの N 信号を読み出すことで、垂直出力線 1 6 n を構成する 4 本の出力線 1 6 n 1 ~ 1 6 n 4 の電位は同じタイミングで同じように変化するようになる。これにより、出力線 1 6 n 1 ~ 1 6 n 4 間における寄生容量を通じた影響を概略揃えることができる。

#### 【0087】

続く時刻 t 2 4 において、垂直駆動回路 3 0 は、制御信号 T X 1 2, T X 2 1 をローレベルからハイレベルに制御する。これにより、単位画素 1 2 (K + 1, n) の転送トランジスタ M 1 2 がオンになり、所定の露光期間の間に単位画素 1 2 (K + 1, n) の光電変換素子 P D 2 に蓄積された電荷がノード F D に転送される。また、単位画素 1 2 (K + 2, n) の転送トランジスタ M 1 1 がオンになり、所定の露光期間の間に単位画素 1 2 (K + 2, n) の光電変換素子 P D 1 に蓄積された電荷がノード F D に転送される。

#### 【0088】

これにより、単位画素 1 2 (K + 1, n) の光電変換素子 P D 2 で生じた電荷の量に応じた信号が増幅トランジスタ M 3 及び選択トランジスタ M 4 を介して出力線 1 6 n 1 に出力される。同様に、単位画素 1 2 (K + 2, n) の光電変換素子 P D 1 で生じた電荷の量に応じた信号が増幅トランジスタ M 3 及び選択トランジスタ M 4 を介して出力線 1 6 n 2 に出力される。

#### 【0089】

続く時刻 t 2 5 において、垂直駆動回路 3 0 は、制御信号 T X 1 2, T X 2 1 をハイレベルからローレベルに制御する。これにより、単位画素 1 2 (K + 1, n) における光電変換素子 P D 2 からノード F D への電荷の転送期間及び単位画素 1 2 (K + 2, n) における光電変換素子 P D 1 からノード F D への電荷の転送期間が終了する。

#### 【0090】

続く時刻 t 2 6 において、垂直駆動回路 3 0 は、制御信号 S E L 1, S E L 2, N S E L 3, N S E L 4 をハイレベルからローレベルに制御する。これにより、読み出しが行われた単位画素 1 2 (K + 1, n), 1 2 (K + 2, n) の選択トランジスタ M 4 がオフになり、単位画素 1 2 (K + 1, n), 1 2 (K + 2, n) が出力線 1 6 n 1, 1 6 n 2 から切り離される。また、ヌル画素 2 2 (3, n), 2 2 (4, n) の選択トランジスタ M 7 がオフになり、ヌル画素 2 2 (3, n), 2 2 (4, n) が出力線 1 6 n 3, 1 6 n 4 から切り離される。

#### 【0091】

時刻 t 2 6 から時刻 t 4 1 の期間は、時刻 t 2 1 から時刻 t 2 6 の期間における画素 B 及び画素 C からの N 信号及び S 信号の読み出しと同様にして、画素 A、画素 D、画素 E、画素 F、画素 G 及び画素 H からの N 信号及び S 信号の読み出しを行う期間である。

#### 【0092】

10

20

30

40

50

時刻  $t_{26}$  から時刻  $t_{31}$ までの期間は、画素D及び画素Eの各々からN信号及びS信号の読み出しを行う1水平走査期間に対応する。この1水平走査期間は、図7における第2水平走査期間2HDに対応している。画素Dの読み出しでは、制御信号SEL2がアクティブな状態となり、出力線16n2にN信号及びS信号が読み出される。画素Eの読み出しでは、制御信号SEL3がアクティブな状態となり、出力線16n3にN信号及びS信号が読み出される。

#### 【0093】

また、時刻  $t_{26}$  から時刻  $t_{31}$ までの期間には、制御信号VLSEL1, VLSEL4がハイレベルであることに応じて、制御信号NSEL1, NSEL4がアクティブな状態となる。これにより、出力線16n1にはヌル画素22(1, n)のN信号が読み出され、出力線16n4にはヌル画素22(4, n)のN信号が読み出される。このように、単位画素12からのN信号を読み出さない出力線にヌル画素22からのN信号を読み出すことで、垂直出力線16nを構成する4本の出力線16n1～16n4の電位は同じタイミングで同じように変化するようになる。これにより、出力線16n1～16n4間ににおける寄生容量を通じた影響を概略揃えることができる。

10

#### 【0094】

時刻  $t_{31}$  から時刻  $t_{36}$ までの期間は、画素F及び画素Gの各々からN信号及びS信号の読み出しを行う1水平走査期間に対応する。この1水平走査期間は、図7における第3水平走査期間3HDに対応している。画素Fの読み出しでは、制御信号SEL3がアクティブな状態となり、出力線16n3にN信号及びS信号が読み出される。画素Gの読み出しでは、制御信号SEL4がアクティブな状態となり、出力線16n4にN信号及びS信号が読み出される。

20

#### 【0095】

また、時刻  $t_{31}$  から時刻  $t_{36}$ までの期間には、制御信号VLSEL1, VLSEL2がハイレベルであることに応じて、制御信号NSEL1, NSEL2がアクティブな状態となる。これにより、出力線16n1にはヌル画素22(1, n)のN信号が読み出され、出力線16n2にはヌル画素22(2, n)のN信号が読み出される。このように、単位画素12からのN信号を読み出さない出力線にヌル画素22からのN信号を読み出すことで、垂直出力線16nを構成する4本の出力線16n1～16n4の電位は同じタイミングで同じように変化するようになる。これにより、出力線16n1～16n4間ににおける寄生容量を通じた影響を概略揃えることができる。

30

#### 【0096】

時刻  $t_{36}$  から時刻  $t_{41}$ までの期間は、画素A及び画素Hの各々からN信号及びS信号の読み出しを行う1水平走査期間に対応する。この1水平走査期間は、図7における第4水平走査期間4HDに対応している。画素Aの読み出しでは、制御信号SEL1がアクティブな状態となり、出力線16n1にN信号及びS信号が読み出される。画素Hの読み出しでは、制御信号SEL4がアクティブな状態となり、出力線16n4にN信号及びS信号が読み出される。

#### 【0097】

また、時刻  $t_{36}$  から時刻  $t_{41}$ までの期間には、制御信号VLSEL2, VLSEL3がハイレベルであることに応じて、制御信号NSEL2, NSEL3がアクティブな状態となる。これにより、出力線16n2にはヌル画素22(2, n)のN信号が読み出され、出力線16n3にはヌル画素22(3, n)のN信号が読み出される。このように、単位画素12からのN信号を読み出さない出力線にヌル画素22からのN信号を読み出すことで、垂直出力線16nを構成する4本の出力線16n1～16n4の電位は同じタイミングで同じように変化するようになる。これにより、出力線16n1～16n4間ににおける寄生容量を通じた影響を概略揃えることができる。

40

#### 【0098】

このようにして、時刻  $t_{21}$  から時刻  $t_{41}$ までの4つの水平走査期間を経て、画素A、画素B、画素C、画素D、画素E、画素F、画素G及び画素Hの8画素からの画素信号

50

の読み出しを行う。この後、同様の手順により、第5行目から4行単位で画素領域10を順次走査し、画素領域10の全体から画素信号の読み出しを行う。

#### 【0099】

このように、本実施形態においては、非選択の出力線にマル画素22のN信号を読み出すことで、同じ列の垂直出力線16を構成する複数の出力線における各出力線から他の出力線への寄生容量を通じた影響を抑えるようにしている。したがって、本実施形態によれば、出力線間の電位ばらつきを効果的に抑制し、ノイズを低減した高品質な信号を出力することが可能である。

#### 【0100】

##### [第2実施形態]

本発明の第2実施形態による光電変換装置について、図10を用いて説明する。第1実施形態による光電変換装置と同様の構成要素には同一の符号を付し、説明を省略し或いは簡潔にする。図10は、本実施形態による光電変換装置における垂直駆動回路30の構成例を示すブロック図である。

#### 【0101】

本実施形態による光電変換装置は、制御回路92の配置場所が異なるほかは、第1実施形態による光電変換装置と同様である。すなわち、第1実施形態による光電変換装置では、垂直駆動回路30から独立した回路として、垂直駆動回路30の外部に制御回路92を設けていた。これに対し、本実施形態による光電変換装置では、図10に示すように、制御回路92を垂直駆動回路30の垂直走査部32の内部に配置している。光電変換装置をこのように構成することにより、制御信号VLS EL1～VLS EL4を供給するための配線を他の機能ブロックから引き回す必要がなくなり、効率の良い配線レイアウトが可能となる。また、垂直走査部32の内部で論理を構成し、単位垂直論理部36の構成を簡素化することも可能である。例えば、垂直走査部32から、行選択信号DEC<k>と制御信号VLS ELKとの論理演算を行った後の信号を出力するように構成してもよい。垂直走査部32内の回路構成は、図10に示すものに限定されるものではない。

#### 【0102】

このように、本実施形態によれば、出力線間の電位ばらつきを効果的に抑制し、ノイズを低減した高品質な信号を出力することが可能である。また、効率の良い配線レイアウトが可能となり、回路構成を簡略化することができる。

#### 【0103】

##### [第3実施形態]

本発明の第3実施形態による撮像システムについて、図11を用いて説明する。図11は、本実施形態による撮像システムの概略構成を示すブロック図である。

#### 【0104】

上記第1及び第2実施形態で述べた光電変換装置100は、種々の撮像システムに適用可能である。適用可能な撮像システムの例としては、デジタルスチルカメラ、デジタルカムコーダ、監視カメラ、複写機、ファックス、携帯電話、車載カメラ、観測衛星などが挙げられる。また、レンズなどの光学系と撮像装置とを備えるカメラモジュールも、撮像システムに含まれる。図11には、これらのうちの一例として、デジタルスチルカメラのブロック図を例示している。

#### 【0105】

図11に例示した撮像システム200は、撮像装置201、被写体の光学像を撮像装置201に結像させるレンズ202、レンズ202を通過する光量を可変にするための絞り204、レンズ202の保護のためのバリア206を有する。レンズ202及び絞り204は、撮像装置201に光を集光する光学系である。撮像装置201は、第1及び第2実施形態のいずれかで説明した光電変換装置100であって、レンズ202により結像された光学像を画像データに変換する。

#### 【0106】

撮像システム200は、また、撮像装置201より出力される出力信号の処理を行う信

10

20

30

40

50

号処理部 208 を有する。信号処理部 208 は、撮像装置 201 が output するデジタル信号から画像データの生成を行う。また、信号処理部 208 は必要に応じて各種の補正、圧縮を行って画像データを出力する動作を行う。撮像装置 201 は、信号処理部 208 で処理されるデジタル信号を生成する A/D 変換部を備えうる。A/D 変換部は、撮像装置 201 の光電変換部が形成された半導体層（半導体基板）に形成されていてもよいし、撮像装置 201 の光電変換部が形成された半導体層とは別の半導体基板に形成されていてもよい。また、信号処理部 208 が撮像装置 201 と同一の半導体基板に形成されていてもよい。

#### 【0107】

撮像システム 200 は、更に、画像データを一時的に記憶するためのメモリ部 210、外部コンピュータ等と通信するための外部インターフェース部（外部 I/F 部）212 を有する。更に撮像システム 200 は、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体 214、記録媒体 214 に記録又は読み出しを行うための記録媒体制御インターフェース部（記録媒体制御 I/F 部）216 を有する。なお、記録媒体 214 は、撮像システム 200 に内蔵されていてもよく、着脱可能であってもよい。

10

#### 【0108】

更に撮像システム 200 は、各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部 218、撮像装置 201 と信号処理部 208 に各種タイミング信号を出力するタイミング発生部 220 を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システム 200 は少なくとも撮像装置 201 と、撮像装置 201 から出力された出力信号を処理する信号処理部 208 とを有すればよい。

20

#### 【0109】

撮像装置 201 は、撮像信号を信号処理部 208 に出力する。信号処理部 208 は、撮像装置 201 から出力される撮像信号に対して所定の信号処理を実施し、画像データを出力する。信号処理部 208 は、撮像信号を用いて、画像を生成する。

#### 【0110】

このように、本実施形態によれば、第 1 実施形態による光電変換装置 100 を適用した撮像システムを実現することができる。

#### 【0111】

##### [第 4 実施形態]

本発明の第 4 実施形態による撮像システム及び移動体について、図 12 を用いて説明する。図 12 は、本実施形態による撮像システム及び移動体の構成を示す図である。

30

#### 【0112】

図 12 (a) は、車載カメラに関する撮像システムの一例を示したものである。撮像システム 300 は、撮像装置 310 を有する。撮像装置 310 は、上記第 1 及び第 2 実施形態のいずれかに記載の光電変換装置 100 である。撮像システム 300 は、撮像装置 310 により取得された複数の画像データに対し、画像処理を行う画像処理部 312 と、撮像装置 310 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う視差取得部 314 と、を有する。また、撮像システム 300 は、算出された視差に基づいて対象物までの距離を算出する距離取得部 316 と、算出された距離に基づいて衝突可能性があるか否かを判定する衝突判定部 318 と、を有する。ここで、視差取得部 314 や距離取得部 316 は、対象物までの距離情報を取得する距離情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 318 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。距離情報取得手段は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよい。また、FPGA (Field Programmable Gate Array) や ASIC (Application Specific Integrated circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。

40

#### 【0113】

撮像システム 300 は車両情報取得装置 320 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 300 は、衝突判定部

50

318での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御E C U 330が接続されている。また、撮像システム300は、衝突判定部318での判定結果に基づいて、ドライバーへ警報を発する警報装置340とも接続されている。例えば、衝突判定部318の判定結果として衝突可能性が高い場合、制御E C U 330はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置340は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

#### 【0114】

本実施形態では、車両の周囲、例えば前方又は後方を撮像システム300で撮像する。

図12(b)に、車両前方(撮像範囲350)を撮像する場合の撮像システムを示した。車両情報取得装置320が、撮像システム300ないしは撮像装置310に指示を送る。このような構成により、測距の精度をより向上させることができる。

#### 【0115】

上記では、他の車両と衝突しないように制御する例を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。更に、撮像システムは、自車両等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体(移動装置)に適用することができる。加えて、移動体に限らず、高度道路交通システム(ITS)等、広く物体認識を利用する機器に適用することができる。

#### 【0116】

##### [第5実施形態]

本発明の第5実施形態による機器について、図13を用いて説明する。図13は、本実施形態による機器の概略構成を示すブロック図である。

#### 【0117】

図13は、光電変換装置A P Rを含む機器E Q Pを示す模式図である。光電変換装置A P Rは、第1及び第2実施形態のいずれかに記載の光電変換装置100の機能を備える。光電変換装置A P Rの全部又は一部が、半導体デバイスI Cである。本例の光電変換装置A P Rは、例えば、イメージセンサやA F(Auto Focus)センサ、測光センサ、測距センサとして用いることができる。半導体デバイスI Cは、光電変換部を含む画素回路P X Cが行列状に配列された画素エリアP Xを有する。半導体デバイスI Cは画素エリアP Xの周囲に周辺エリアP Rを有することができる。周辺エリアP Rには画素回路以外の回路を配置することができる。

#### 【0118】

光電変換装置A P Rは、複数の光電変換部が設けられた第1半導体チップと、周辺回路が設けられた第2半導体チップとを積層した構造(チップ積層構造)を有していてよい。第2半導体チップにおける周辺回路は、それぞれ、第1半導体チップの画素列に対応した列回路とすることができる。また、第2半導体チップにおける周辺回路は、それぞれ、第1半導体チップの画素あるいは画素ブロックに対応したマトリクス回路とすることができる。第1半導体チップと第2半導体チップとの接続は、貫通電極(T S V)、銅等の導電体の直接接合によるチップ間配線、チップ間のマイクロバンプによる接続、ワイヤボンディングによる接続などを採用することができる。

#### 【0119】

光電変換装置A P Rは、半導体デバイスI Cの他に、半導体デバイスI Cを収容するパッケージP K Gを含みうる。パッケージP K Gは、半導体デバイスI Cが固定された基体と、半導体デバイスI Cに対向するガラス等の蓋体と、基体に設けられた端子と半導体デバイスI Cに設けられた端子とを接続するボンディングワイヤやバンプ等の接続部材と、を含みうる。

#### 【0120】

機器E Q Pは、光学装置O P T、制御装置C T R L、処理装置P R C S、表示装置D S

10

20

30

40

50

P L、記憶装置 M M R Y 及び機械装置 M C H N のうちの少なくともいずれかを更に備えうる。光学装置 O P T は、光電変換装置としての光電変換装置 A P R に対応するものであり、例えばレンズやシャッター、ミラーである。制御装置 C T R L は、光電変換装置 A P R を制御するものであり、例えば A S I C などの半導体デバイスである。処理装置 P R C S は、光電変換装置 A P R から出力された信号を処理するものであり、A F E (アナログフロントエンド)あるいはD F E (デジタルフロントエンド)を構成する。処理装置 P R C S は、C P U (中央処理装置)やA S I C (特定用途向け集積回路)などの半導体デバイスである。表示装置 D S P L は、光電変換装置 A P R で得られた情報(画像)を表示する、E L 表示装置や液晶表示装置である。記憶装置 M M R Y は、光電変換装置 A P R で得られた情報(画像)を記憶する、磁気デバイスや半導体デバイスである。記憶装置 M M R Y は、S R A M やD R A M などの揮発性メモリ、或いは、フラッシュメモリやハードディスクドライブなどの不揮発性メモリである。機械装置 M C H N は、モーターやエンジン等の可動部あるいは推進部を有する。機器 E Q P では、光電変換装置 A P R から出力された信号を表示装置 D S P L に表示したり、機器 E Q P が備える通信装置(不図示)によって外部に送信したりする。そのために、機器 E Q P は、光電変換装置 A P R が有する記憶回路部や演算回路部とは別に、記憶装置 M M R Y や処理装置 P R C S を更に備えることが好ましい。

10

## 【0121】

図13に示した機器 E Q P は、撮影機能を有する情報端末(例えばスマートフォンやウエアラブル端末)やカメラ(例えばレンズ交換式カメラ、コンパクトカメラ、ビデオカメラ、監視カメラ)などの電子機器でありうる。カメラにおける機械装置 M C H N はズーミングや合焦、シャッター動作のために光学装置 O P T の部品を駆動することができる。また、機器 E Q P は、車両や船舶、飛行体などの輸送機器(移動体)でありうる。また、機器 E Q P は、内視鏡やC T スキャナーなどの医療機器でありうる。また、機器 E Q P は、内視鏡やC T スキャナーなどの医療機器でありうる。

20

## 【0122】

輸送機器における機械装置 M C H N は移動装置として用いられる。輸送機器としての機器 E Q P は、光電変換装置 A P R を輸送するものや、撮影機能により運転(操縦)の補助及び/又は自動化を行うものに好適である。運転(操縦)の補助及び/又は自動化のための処理装置 P R C S は、光電変換装置 A P R で得られた情報に基づいて移動装置としての機械装置 M C H N を操作するための処理を行うことができる。

30

## 【0123】

本実施形態による光電変換装置 A P R は、その設計者、製造者、販売者、購入者及び/又は使用者に、高い価値を提供することができる。そのため、光電変換装置 A P R を機器 E Q P に搭載すれば、機器 E Q P の価値も高めることができる。よって、機器 E Q P の製造、販売を行う上で、本実施形態の光電変換装置 A P R の機器 E Q P への搭載を決定することは、機器 E Q P の価値を高める上で有利である。

## 【0124】

## [変形実施形態]

本発明は、上記実施形態に限らず種々の変形が可能である。

40

## 【0125】

例えば、いずれかの実施形態の一部の構成を他の実施形態に追加した例や、他の実施形態の一部の構成と置換した例も、本発明の実施形態である。

## 【0126】

また、上記実施形態では、画素領域 10, 20 の各列の垂直出力線 16 を 4 本の出力線により構成したが、各列の垂直出力線 16 を構成する出力線の本数は 4 本に限定されるものではなく、2 本以上であればよい。

## 【0127】

また、上記実施形態では、ヌル画素 22 で不使用の出力線を駆動する際にリセットトランジスタ M 5 と選択トランジスタ M 7 を動作させているが、ヌル画素 22 で不使用の出力

50

線を駆動する構成はこれに限定されるものではない。例えば、選択トランジスタM7のみを動作するように構成してもよいし、ヌル画素22に単位画素12と同様の転送トランジスタを設けて単位画素12と同様に駆動する構成としてもよい。ヌル画素22の構成を単位画素12の構成に近づけることにより垂直線の負荷を揃えることができる。ヌル画素22の構成は、これを実現するための回路面積や画質劣化を低減する効果に応じて適宜変更が可能である。

#### 【0128】

また、上記実施形態では、ヌル画素22によって不使用の出力線を駆動する例を示したが、ヌル画素22以外の構成要素、例えば光電変換部が遮光された遮光画素（オプティカルブラック画素）を用いて不使用の出力線を駆動するように構成することも可能である。

10 不使用の出力線に焦点検出用画素の信号や故障検知画素の信号など、画像形成用の信号とは異なる用途の信号を出力するように構成することも可能である。

#### 【0129】

また、図2に示した単位画素12の回路構成は一例であり、適宜変更が可能である。例えば、各々の単位画素12が備える光電変換素子の数は1つでもよい。また、各々の単位画素12が備える光電変換素子の数は3つ以上であってもよい。この場合、複数の光電変換素子が1つのFDノードを共有する構成としてもよい。また、複数の光電変換素子が1つのマイクロレンズを共有する瞳分割画素とし、位相差を検出可能な構成としてもよい。また、単位画素12は、必ずしも選択トランジスタM4を有する必要はない。また、ノードFDの容量値が切り替え可能に構成されていてもよい。

#### 【0130】

また、上記第3及び第4実施形態に示した撮像システムは、本発明の光電変換装置を適用しうる撮像システム例を示したものであり、本発明の光電変換装置を適用可能な撮像システムは図11及び図12に示した構成に限定されるものではない。

#### 【0131】

本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

#### 【0132】

なお、上記実施形態は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されなければならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

#### 【0133】

上記実施形態の開示は、以下の構成及び方法を含む。

##### （構成1）

複数の行及び複数の列をなすように配され、各々が光電変換部を有する複数の画素と、前記複数の列の各々に少なくとも2つが配され、それぞれが対応する列の画素に接続された複数の出力線と、

前記複数の行のうちの一部の複数行を順次選択するように構成された走査回路と、前記走査回路に入力される制御信号とは別の制御信号が入力される入力部を備え、前記複数の行のうちの他の一部の行を選択するように構成された選択回路と

40 を有することを特徴とする光電変換装置。

##### （構成2）

前記走査回路及び前記選択回路を制御する制御回路を更に有し、

前記制御回路は、

前記走査回路により前記一部の複数行のうちの第1の行を選択し、前記第1の行の画素の信号を前記複数の出力線のうちの第1の出力線に出力する期間に、

前記選択回路により前記他的一部の行のうちの第2の行を選択し、前記第2の行の画

10

20

30

40

50

素の信号を前記第1の出力線と同じ列に配された第2の出力線に出力することを特徴とする構成1記載の光電変換装置。

(構成3)

前記第1の出力線と前記第2の出力線とは隣接していることを特徴とする構成2記載の光電変換装置。

(構成4)

前記他の一部の行に配された画素は、光電変換部を含まないヌル画素であることを特徴とする構成2又は3記載の光電変換装置。

(構成5)

前記他の一部の行に配された画素は、光電変換部が遮光された遮光画素であることを特徴とする構成2又は3記載の光電変換装置。

(構成6)

前記第2の出力線に出力される前記信号は、前記第2の行の画素から出力されるN信号である

ことを特徴とする構成4又は5記載の光電変換装置。

(構成7)

前記第1の出力線に出力される信号の用途と前記第2の出力線に出力される信号の用途とが異なっている

ことを特徴とする構成2又は3記載の光電変換装置。

(構成8)

前記選択回路に入力される前記制御信号は、同じ列に配された出力線のうち前記一部の複数行の画素からの信号が出力されない出力線に関する情報を含む

ことを特徴とする構成1乃至7のいずれかに記載の光電変換装置。

(構成9)

前記選択回路は、前記走査回路の外部に設けられている

ことを特徴とする構成1乃至8のいずれかに記載の光電変換装置。

(構成10)

前記選択回路は、前記走査回路に設けられている

ことを特徴とする構成1乃至8のいずれかに記載の光電変換装置。

(構成11)

前記一部の複数行に配された画素の各々は複数の光電変換部を有する

ことを特徴とする構成1乃至10のいずれかに記載の光電変換装置。

(方法1)

複数の行及び複数の列をなすように配され、各々が光電変換部を有する複数の画素と、前記複数の列の各々に少なくとも2つが配され、それぞれが対応する列の画素に接続された複数の出力線と、前記複数の行のうちの一部の複数行を順次選択する走査回路と、前記複数の行のうちの他の一部の行を選択する選択回路と、を有する光電変換装置の駆動方法であって、

前記走査回路により前記一部の複数行のうちの第1の行を選択し、前記第1の行の画素の信号を前記複数の出力線のうちの第1の出力線に出力する期間に、

前記選択回路により前記他の一部の行のうちの第2の行を選択し、前記第2の行の画素の信号を前記第1の出力線と同じ列に配された第2の出力線に出力する

ことを特徴とする光電変換装置の駆動方法。

(構成12)

構成1乃至11のいずれかに記載の光電変換装置と、

前記光電変換装置から出力される信号を処理する信号処理装置と

を有することを特徴とする撮像システム。

(構成13)

移動体であって、

構成1乃至11のいずれかに記載の光電変換装置と、

10

20

30

40

50

前記光電変換装置からの信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、

前記距離情報に基づいて前記移動体を制御する制御手段と

を有することを特徴とする移動体。

(構成 14)

構成 1 乃至 11 のいずれかに記載の光電変換装置と、

前記光電変換装置に対応する光学装置、

前記光電変換装置を制御する制御装置、

前記光電変換装置から出力された信号を処理する処理装置、

前記光電変換装置で得られた情報に基づいて制御される機械装置、

前記光電変換装置で得られた情報を表示する表示装置、及び、

前記光電変換装置で得られた情報を記憶する記憶装置、の少なくともいずれかと

を備えることを特徴とする機器。

10

20

30

40

#### 【符号の説明】

##### 【0 1 3 4】

1 0 , 2 0 ... 画素領域

1 2 ... 単位画素

1 6 ... 垂直出力線

2 2 ... ヌル画素

3 0 ... 垂直駆動回路

3 2 ... 垂直走査部

3 4 ... 垂直論理部

3 6 , 4 2 ... 単位垂直論理部

9 2 ... 制御回路

1 0 0 ... 光電変換装置

#### 【図面】

##### 【図 1】

##### 【図 2】

50

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

10

20

30

40

50

---

フロントページの続き

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 佐藤 雅紀

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 市野 真也

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ターム(参考) 5C024 CX03 GX03 GX16 GX18 GY39 GY41 GZ36