(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4681559号

(P4681559)

(45) 発行日 平成23年5月11日(2011.5.11)

(24) 登録日 平成23年2月10日(2011.2.10)

(51) Int.Cl.

F 1

G 11 C 16/02 (2006.01)

G 11 C 16/06 (2006.01)G 11 C 17/00 6 1 4

G 11 C 17/00 6 4 1

G 11 C 17/00 6 3 4 E

請求項の数 43 (全 37 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2006-533611 (P2006-533611)  |

| (86) (22) 出願日 | 平成16年6月7日 (2004.6.7)          |

| (65) 公表番号     | 特表2007-500918 (P2007-500918A) |

| (43) 公表日      | 平成19年1月18日 (2007.1.18)        |

| (86) 國際出願番号   | PCT/US2004/018172             |

| (87) 國際公開番号   | W02004/114313                 |

| (87) 國際公開日    | 平成16年12月29日 (2004.12.29)      |

| 審査請求日         | 平成19年3月12日 (2007.3.12)        |

| (31) 優先権主張番号  | 10/461,244                    |

| (32) 優先日      | 平成15年6月13日 (2003.6.13)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                      |

|-----------|------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 592012513<br>サンディスク コーポレイション<br>Sandisk Corporation<br>アメリカ合衆国 95035 カリフォルニア州、ミルピタス、マッカーシー ブルバード 601 |

| (74) 代理人  | 110000110<br>特許業務法人快友国際特許事務所                                                                         |

| (72) 発明者  | ギューテルマン、ダニエル シー。<br>アメリカ合衆国、94539、カリフォルニア州、フレモント、ジャカランダ ドライブ 305                                     |

最終頁に続く

(54) 【発明の名称】メモリ・システムのトラッキング・セル

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリ・システムに保存されているデータを読み取る方法であって、前記メモリ・システムは、マルチステート記憶素子群を含み、前記マルチステート記憶素子群は、データ記憶素子群とトラッキング記憶素子群を含み、前記データ記憶素子群の夫々は、巡回可能に符号化されたデータを複数の状態の一つとして保存することが可能であり、その方法は：

前記トラッキング記憶素子群を読み取る工程であって、前記トラッキング記憶素子群の少なくとも一つをトラッキング状態群の一つに分類する工程を含み、前記トラッキング状態群の夫々は前記複数の状態の一つと対応し、前記トラッキング状態群は前記複数の状態のうちの他の状態によって相互に分離されている、前記トラッキング記憶素子群を読み取る工程と；

前記分類に基いてローテーション・スキームを特定する工程と；

前記ローテーション・スキームを用いて、前記データ記憶素子群の少なくとも一つを読み取る工程を備える方法。

## 【請求項 2】

前記ローテーション・スキームを特定する前記工程は、前記ローテーション・スキームの識別を生成するために、2以上の非冗長なトラッキング記憶素子についての分類を組み合わせる工程を含む、請求項1の方法。

## 【請求項 3】

前記トラッキング記憶素子群を読み取る前記工程は、第1トラッキング記憶素子を第1

トラッキング状態に分類する工程と、第2トラッキング記憶素子を第2トラッキング状態に分類する工程を含み、

前記ローテーション・スキームを特定する前記工程は、前記第1トラッキング状態にある前記第1トラッキング記憶素子と前記第2トラッキング状態にある前記第2トラッキング記憶素子の組み合わせに基いて、第1識別子を生成する工程を含み、

前記第1識別子は、前記ローテーション・スキームを識別するために他の非冗長な識別子と組み合わせられる、請求項1の方法。

#### 【請求項4】

前記トラッキング記憶素子群を読み取る前記工程はさらに、第3トラッキング記憶素子を前記第1トラッキング状態に分類する工程と、第4トラッキング記憶素子を前記第2トラッキング状態に分類する工程と、第5トラッキング記憶素子を前記第1トラッキング状態に分類する工程と、第6トラッキング記憶素子を前記第2トラッキング状態に分類する工程を含み、

前記ローテーション・スキームを特定する工程はさらに、

前記第1トラッキング状態にある前記第3トラッキング記憶素子と、前記第2トラッキング状態にある前記第4トラッキング記憶素子の組み合わせに基いて、第2識別子を生成する工程と、

前記第1トラッキング状態にある前記第5トラッキング記憶素子と、前記第2トラッキング状態にある前記第6トラッキング記憶素子の組み合わせに基いて、第3識別子を生成する工程を含み、

前記第一識別子、前記第二識別子、および前記第三識別子は、前記ローテーション・スキームを識別するために、組み合わせとしてひとまとめにされる、請求項3の方法。

#### 【請求項5】

前記第1識別子は第1ビットであり、

前記第2識別子は第2ビットであり、

前記第3識別子は第3ビットであり、

前記第1ビット、第2ビット、および第3ビットは、前記ローテーション・スキームに対する巡回符号を構成する、請求項4の方法。

#### 【請求項6】

前記複数の状態は8つの状態を含み、

前記トラッキング状態群は第1状態と第2状態を含み、前記第2状態は前記第1状態から、少なくとも4つの他の状態を挟んで分離されている、請求項1の方法。

#### 【請求項7】

前記ローテーション・スキームを特定する前記工程は：

トラッキング記憶素子のペアからのデータにアクセスする工程と；

特定のペアが、第1トラッキング状態にある第1トラッキング記憶素子と、第2トラッキング状態にある第2トラッキング記憶素子を備えるか否かを特定する工程と；

前記特定のペアが第1トラッキング状態にある第1トラッキング記憶素子と第2トラッキング状態にある第2トラッキング記憶素子を備えている場合に、前記第1トラッキング記憶素子と前記第2トラッキング記憶素子に基いて、前記ローテーション・スキームを識別する符号の第1ビットを特定する工程と；

前記特定のペアが第1トラッキング状態にある第1トラッキング記憶素子と第2トラッキング状態にある第2トラッキング記憶素子を備えている場合に、前記特定のペアに前記第1の状態と前記第2の状態を割り当てるための最良な対応付けを特定する工程を含み、前記符号は前記第1ビットと少なくとも1つの他のビットを備えている、請求項1の方法。

#### 【請求項8】

前記トラッキング記憶素子群は、前記ローテーション・スキームを識別する情報に対して互いに冗長性を有する複数のセットに分割されており、

前記トラッキング記憶素子群を読み取る前記工程は、トラッキング記憶素子群の前記複

10

20

30

40

50

数のセットを読み取る工程を含み；

前記ローテーション・スキームを特定する前記工程は、トラッキング記憶素子群の1つのセットに基いて、前記ローテーション・スキームを識別することを試みる工程と、トラッキング記憶素子群の前記複数のセットの冗長性に基いて、トラッキング素子群のエラーを修復することを試みる工程を含む、請求項1の方法。

**【請求項9】**

トラッキング記憶素子群の異なるセット群が、それぞれ異なるローテーション・スキーム群を識別する場合に、前記ローテーション・スキームが、トラッキング記憶素子群の異なるセット群の中での多数決投票の方法によって選択される、請求項8の方法。

**【請求項10】**

前記データ記憶素子群の少なくとも一つを読み取る前記工程は、前記ローテーション・スキームに基いて、前記データ記憶素子群の前記少なくとも一つから読み取られたデータを復号化する工程を含む、請求項1の方法。

**【請求項11】**

前記トラッキング記憶素子群のデータが巡回的に符号化されていない、請求項1の方法。

**【請求項12】**

前記トラッキング状態群の各状態に対して複数の読み取り動作を実行する工程と、複数の読み取り動作を実行する前記工程に基いて、前記複数の状態のそれを区別するための比較値の現在のセットを特定する工程と、

比較値の前記現在のセットを用いて、前記データ記憶素子群の少なくとも1つを読み取る工程をさらに備える、請求項1の方法。

**【請求項13】**

複数の読み取り動作を実行する前記工程は、

前記トラッキング状態群の第1状態についての第1の複数の読み取り動作を実行する工程と、

前記トラッキング状態群の第2状態についての第2の複数の読み取り動作を実行する工程と、

前記第1の複数の読み取り動作に基いて、前記第1状態に対する第1数値を特定する工程と、

前記第2の複数の読み取り動作に基いて、前記第2状態に対する第2数値を特定する工程を含み、

比較値の前記現在のセットを特定する前記工程は、前記第1数値と前記第2数値に基いて、比較値の前記現在のセットを特定する工程を含む、請求項12の方法。

**【請求項14】**

比較値の現在のセットを特定する前記工程は：

第1状態に対する代表的なしきい電圧値を特定する工程と；

第2状態に対する代表的なしきい電圧値を特定する工程と；

前記第1状態に対する代表的なしきい電圧値と、前記第2状態に対する代表的なしきい電圧値に基いて、前記第1状態と前記第2状態の間の全ての状態についてのデータを用いることなく、現在の比較値を変更する工程を含む、請求項12の方法。

**【請求項15】**

前記トラッキング記憶素子群は、前記ローテーション・スキームを識別する情報に対して互いに冗長性を有する複数のセットに分割されており、

複数の読み取り動作を実行する前記工程は：

第1状態に関連する複数のしきい電圧レベルについて、前記トラッキング記憶素子群の第1セットに読み取り動作を実行する工程と；

前記トラッキング記憶素子群の前記第1セットに読み取り動作を実行する工程に基いて、前記トラッキング記憶素子群の前記第1セットに対するしきい電圧レベルを特定する工程と；

10

20

30

40

50

第2状態に関連する複数のしきい電圧レベルについて、前記トラッキング記憶素子群の第2セットに読み取り動作を実行する工程と；

前記トラッキング記憶素子群の前記第2セットに読み取り動作を実行する工程に基いて、前記トラッキング記憶素子群の前記第2セットに対するしきい電圧レベルを特定する工程を含む、請求項14の方法。

【請求項16】

トラッキング記憶素子群について読み取り動作の初期セットを実行する工程と；

読み取り動作の前記初期セットからのエラー情報を記録する工程と；

前記エラー情報に基いて品質ゲージを特定する工程と；

前記品質ゲージが低品質またはECC失敗を示しているか否かを特定する工程をさらに備え、複数の読み取り動作を実行する前記工程と比較値の新たなセットを特定する前記工程は、前記品質ゲージが低品質またはECC失敗を示していると特定されたときに実行される、請求項12の方法。 10

【請求項17】

マルチステート記憶素子群と；

前記マルチステート記憶素子群と通信可能な検出回路と；

前記検出回路と通信可能な制御回路を備えるメモリ・システムであって、

前記マルチステート記憶素子群は、データ記憶素子群とトラッキング記憶素子群を含み、

前記データ記憶素子群の夫々は、巡回可能に符号化されたデータを複数の状態の一つとして保存することが可能であり、 20

前記検出回路は、前記データ記憶素子群と前記トラッキング記憶素子群を読み取ることが可能であり、

前記制御回路は、前記検出回路によって読み取られた前記トラッキング記憶素子群の少なくとも一つをトラッキング状態群の一つに分類し、

前記トラッキング状態群の夫々は前記複数の状態の一つに対応しており、

前記トラッキング状態群は前記複数の状態のうちの他の状態を挟んで相互に分離しており、

前記制御装置は、前記分類に基いてローテーション・スキームを特定するとともに、前記特定されたローテーション・スキームを用いて前記データ記憶素子群の少なくとも一つを読み取る、メモリ・システム。 30

【請求項18】

前記制御装置は、前記ローテーション・スキームの識別を生成するため、2以上の非冗長なトラッキング記憶素子の分類を組み合わせることによって、前記ローテーション・スキームを特定する、請求項17のメモリ・システム。

【請求項19】

第1トラッキング記憶素子は、第1トラッキング状態に特徴付けられ、第2トラッキング記憶素子は、第2トラッキング状態に特徴づけられ；

前記制御装置は、前記第1トラッキング状態にある前記第1トラッキング記憶素子と、前記第2トラッキング状態にある前記第2トラッキング記憶素子との組み合わせに基いて、第1識別子を生成することによって前記ローテーション・スキームを特定し、前記第1識別子は、前記ローテーション・スキームを識別するために、他の非冗長な識別子と組み合わせられる、請求項17のメモリ・システム。 40

【請求項20】

前記複数の状態は、状態0、状態1、状態2、状態3、状態4、状態5、状態6、および状態7の、8つの状態を含み、

前記トラッキング状態群は状態1と状態6を含み、

前記分類は、特定の記憶素子が物理的に状態1もしくは状態6になくても、その特定の記憶素子が論理的に状態1もしくは状態6にあると見なされるか否かを特定することとを含む、請求項17のメモリ・システム。 50

**【請求項 2 1】**

前記制御回路は：

トラッキング記憶素子のペアからのデータにアクセスすることと；

特定のペアが第1トラッキング状態にある第1トラッキング記憶素子と第2トラッキング状態にある第2トラッキング記憶素子を備えているか否かを特定することと；

前記特定のペアが第1トラッキング状態にある第1トラッキング記憶素子と第2トラッキング状態にある第2トラッキング記憶素子を備えている場合に、前記第1トラッキング記憶素子と前記第2トラッキング記憶素子に基いて、前記ローテーション・スキームを識別する符号の第1ビットを特定することと；

前記特定のペアが第1トラッキング状態にある第1トラッキング記憶素子と第2トラッキング状態にある第2トラッキング記憶素子を備えていない場合に、前記特定のペアに前記第1の状態と前記第2の状態を割り当てるための最良な対応付けを特定することによって、前記ローテーション・スキームを特定し、10

前記符号は、前記第1ビットと少なくとも1つの他のビットを備えている、請求項17のメモリ・システム。

**【請求項 2 2】**

前記トラッキング記憶素子群のデータが巡回的に符号化されていない、請求項17のメモリ・システム。

**【請求項 2 3】**

前記トラッキング記憶素子は、フラッシュ・メモリ記憶素子である、請求項17のメモリ・システム。20

**【請求項 2 4】**

前記制御回路は、前記トラッキング状態群の各状態に対して複数の読み取り動作の実行を起動し、複数の読み取り動作の実行に基いて、前記複数の状態のそれぞれを区別するための比較値の現在のセットを特定し、比較値の前記現在のセットを用いて、前記データ記憶素子群の少なくとも1つの読み取り動作を起動する、請求項17のメモリ・システム。

**【請求項 2 5】**

比較値の前記現在のセットは、前記トラッキング状態群の第1状態に対する代表的なしきい電圧値を特定することと、前記トラッキング状態群の第2状態に対する代表的なしきい電圧値を特定することと、前記第1状態に対する代表的なしきい電圧値と、前記第2状態に対する代表的なしきい電圧値に基いて、前記第1状態と前記第2状態の間の全ての状態についてのデータを用いることなく、現在の比較値を変更することによって、特定される、請求項24のメモリ・システム。30

**【請求項 2 6】**

前記制御回路は、トラッキング記憶素子のセットについて読み取り動作の初期セットを実行することと、読み取り動作の前記初期セットからのエラー情報を記録することと、前記エラー情報に基いて品質ゲージを特定することと、前記品質ゲージが所定の基準を満たしているか否かを特定することを実行させ、

前記複数の読み取り動作を実行することと、前記比較値の現在のセットを特定することは、前記品質ゲージが前記所定の基準を満たしていると特定されたときに実行される、請求項17のメモリ・システム。40

**【請求項 2 7】**

メモリ・システムに実行される方法であり、前記メモリ・システムは記憶素子群を含み、前記記憶素子群はデータ記憶素子群とトラッキング記憶素子群を含み、その方法は：

前記トラッキング記憶素子群に読み取り動作を実行する工程と；

前記読み取り動作からのエラー情報を記録する工程と；

前記エラー情報に基いて、品質ゲージを特定する工程と；

前記品質ゲージが所定の基準を満たす場合に、予め定められた応答を実行する工程を備えており、

前記予め定められた応答は、(a)読み取り処理を強制終了する工程であって、前記ト50

ラッキング記憶素子群に読み取り動作を実行する前記工程は、前記読み取り処理の一部である工程；(b)マルチ・ビット訂正を行わないことを選択することによって、エラー訂正符号処理のパラメータを変更する工程；(c)トラッキング状態群について、前記トラッキング記憶素子群に複数の読み取り動作を実行し、前記データ記憶素子群の状態を区別するための電圧しきい値レベルである比較値の現在のセットを特定する工程、の少なくとも一つの工程を含む方法。

【請求項 28】

読み取り動作を実行する前記工程に基いて、前記データ記憶素子群の少なくとも一つについてローテーション・スキームを特定する工程と；

前記ローテーション・スキームを用いて前記データ記憶素子群の前記少なくとも一つを読み取る工程をさらに備える、請求項 27 の方法。 10

【請求項 29】

前記品質ゲージが所定の基準を満たさない場合に、ローテーション・スキームを用いて前記データ記憶素子群の前記少なくとも一つを読み取る工程をさらに備え、前記ローテーション・スキームは読み取り動作を実行する前記工程に基いて特定される、請求項 27 の方法。

【請求項 30】

読み取り動作を実行する前記工程は、前記トラッキング記憶素子群がトラッキング状態群にあるか否かを特定する工程を含み；

エラー情報を記録する前記工程は、前記トラッキング状態群の一つでない任意の前記トラッキング記憶素子に関するエラー情報を記録する工程を含む、請求項 27 の方法。 20

【請求項 31】

品質ゲージを特定する前記工程は、前記トラッキング状態群のいずれにもないトラッキング記憶素子の数を特定する工程を含む、請求項 30 の方法。

【請求項 32】

トラッキング状態以外の状態にあるトラッキング記憶素子に対して、品質ゲージを特定する前記工程は、(a)前記トラッキング記憶素子の読み取り状態に相当するしきい値電圧と、(b)前記トラッキング状態に相当するしきい値電圧の間の差を特定する工程を含む、請求項 30 の方法。

【請求項 33】

品質ゲージを特定する前記工程は、経時的にエラーの値を更新する工程を含む、請求項 30 の方法。 30

【請求項 34】

前記トラッキング記憶素子は、ペアにグループ分けされ、

読み取り動作を行う前記工程は、トラッキング記憶素子の各ペアに対して、トラッキング記憶素子の前記ペアの一方が第 1 状態であってトラッキング記憶素子の前記ペアの他方が第 2 状態であるか否か、前記トラッキング記憶素子の現在の状態を特定する工程を含み、前記第 1 状態は前記第 2 状態に隣接する状態ではなく、

エラー情報を記録する前記工程は、トラッキング記憶素子の前記ペアの前記一方が前記第 1 状態にない場合にトラッキング記憶素子の前記ペアの前記一方に対するエラー情報を記録する工程と、トラッキング記憶素子の前記ペアの前記他方が前記第 2 状態にない場合にトラッキング記憶素子の前記ペアの前記他方に対するエラー情報を記録する工程を含む、請求項 27 の方法。 40

【請求項 35】

前記データ記憶素子群の少なくとも 1 つからのデータを読み取るために、比較値の前記現在のセットを用いる工程と；

前記データにエラー訂正符号解析を実行する工程と；

前記エラー訂正符号解析が成功した場合に前記データをホストに報告する工程をさらに備える、請求項 27 の方法。

【請求項 36】

比較値の現在のセットを特定する前記工程は：

前記トラッキング状態群の第1状態に対する代表的なしきい電圧値を特定する工程と；

前記トラッキング状態群の第2状態に対する代表的なしきい電圧値を特定する工程と；

前記第1状態に対する代表的なしきい電圧値と、前記第2状態に対する代表的なしきい電圧値に基いて、前記第1状態と前記第2状態の間の全ての状態についてのデータを用いることなく、現在の比較値をシフトする工程を含む、請求項27の方法。

#### 【請求項37】

読み取り動作を実行する前記工程に基いて、前記データ記憶素子群の少なくとも一つについてのローテーション・スキームを特定する工程と、

前記ローテーション・スキームを用いて、前記データ記憶素子群の前記少なくとも一つを読み取る工程をさらに備える、請求項27の方法。10

#### 【請求項38】

前記品質ゲージが所定の基準を満たさない場合にローテーション・スキームを用いて前記データ記憶素子群の前記少なくとも一つを読み取る工程をさらに備え、前記ローテーション・スキームは読み取り動作を実行する前記工程に基いて特定される、請求項27の方法。

#### 【請求項39】

記憶素子群であって、データ記憶素子群とトラッキング記憶素子群を含み、前記データ記憶素子群は複数の状態の一つとしてデータを保存することが可能であり、前記トラッキング記憶素子群の少なくとも一つは、夫々が前記複数の状態の一つに対応するトラッキング状態群の一つに分類される、記憶素子群と；20

前記トラッキング記憶素子群と通信可能な制御装置を備えるメモリ・システムであって、

前記制御装置は、前記メモリ・システムの読み取り処理の一部として、前記トラッキング記憶素子群の読み取り動作の実行と、前記読み取り動作からのエラー情報の記録と、前記読み取り動作に基いた品質ゲージの特定を引き起こし、

前記品質ゲージが所定の基準を満足しない場合に、前記メモリ・システムの前記読み取り処理は、前記品質ゲージに対する応答を行い、

前期品質ゲージに対する前記応答が、(a)マルチ・ビット訂正は行わないことを選択することによって、エラー訂正符号処理のパラメータを変更する工程；(b)前記複数の状態の夫々の状態について、前記トラッキング記憶素子群に複数の読み取り動作を実行し、前記データ記憶素子群の状態を区別するための電圧しきい値レベルである比較値の現在のセットを特定する工程、のうちの少なくとも一つの工程を含むことを特徴とする、メモリ・システム。30

#### 【請求項40】

前記制御装置は、前記トラッキング記憶素子群がトラッキング状態にあるか否かを特定し、前記トラッキング状態にないトラッキング記憶素子に関するエラー情報を記録する、請求項39のメモリ・システム。

#### 【請求項41】

前記品質ゲージは、前記トラッキング状態にないトラッキング記憶素子の数を指示する、請求項39のメモリ・システム。40

#### 【請求項42】

前記品質ゲージに対する前記応答は、前記データ記憶素子群の前記少なくとも一つからのデータを読み取るための比較値の前記現在のセットの使用と、前記データのエラー訂正符号解析の実行と、前記エラー訂正符号解析が成功した場合の前記データのホストへの報告をさらに含む、請求項39のメモリ・システム。

#### 【請求項43】

前記制御装置は：

前記トラッキング状態群の第1状態に対する代表的なしきい電圧値を特定し；

前記トラッキング状態群の第2状態に対する代表的なしきい電圧値を特定し；50

前記第1状態に対する代表的なしきい電圧値と、前記第2状態に対する代表的なしきい電圧値に基いて、前記第1状態と前記第2状態の間の全ての状態についてのデータを用いることなく、現在の比較値をシフトすることによって、比較値の前記現在のセットを特定する、請求項3 9のメモリ・システム。

【発明の詳細な説明】

【技術分野】

【0001】

(発明の背景)

(1. 技術分野)

本発明はメモリ・デバイスを読み取る技術に関する。

10

【背景技術】

【0002】

(2. 関連技術)

半導体メモリ・デバイスは、様々な電子装置での使用で大きな人気を博している。例えば、不揮発性の半導体メモリは、セルラー電話、デジタル・カメラ、パーソナル・デジタル・アシスタント（PDA）、モバイル・コンピューティング・デバイス、非モバイル・コンピューティング・デバイス等に使用されている。電気的消去可能プログラム可能型読取専用メモリ（EEPROM）やフラッシュ・メモリは、中でも最も人気が高い不揮発性の半導体メモリである。

【0003】

20

EEPROMとフラッシュ・メモリはどちらも、フローティング・ゲートを利用する。フローティング・ゲートは、半導体基板のチャネル領域の上に位置しており、チャネル領域から絶縁されている。フローティング・ゲートはソース領域とドレイン領域の間に位置している。コントロール・ゲートは、フローティング・ゲートから絶縁されており、フローティング・ゲートの上に設けられている。トランジスタのしきい電圧は、フローティング・ゲートに保持されている電荷の量によって制御される。すなわち、トランジスタをオンに切換えて、ソースとドレインの間を導通可能にするのに先立って、コントロール・ゲートに印加されなければならない最低限の電圧は、フローティング・ゲートの電荷保持のレベルによって制御される。

【0004】

30

多くのEEPROMとフラッシュ・メモリは、二つの電荷保持範囲を保存するために使用されるフローティング・ゲートを有し、従って、メモリ・セルは二つの状態の間でプログラミング／消去をることができる。このようなメモリ・セルは、1ビットのデータを保存する。他のEEPROMとフラッシュ・メモリのメモリ・セルは、複数の電荷保持範囲を保存しているため、複数の状態にプログラミングができる。このようなメモリ・セルは複数ビットのデータを保存する。しきい電圧範囲のサイズおよびパラメータは、装置の特徴、動作状態、および履歴に依存する。

【発明の開示】

【発明が解決しようとする課題】

【0005】

40

従来のEEPROMやフラッシュ・メモリは、そのデバイスが消去とプログラミングのサイクルを経るたびに、耐久性に関するストレスを受ける。フラッシュ・メモリの耐久性とは、所定の回数の消去およびプログラミングのサイクルに耐える能力のことである。使用が重なるにつれ、メモリ・デバイス内に不具合が蓄積していき、デバイスの信頼性が極度に下がる。従来のフラッシュ・メモリ・デバイスの耐久性を制限してしまう一つの物理的な現象は、フローティング・ゲートと基板の間にある誘電体の電子の捕獲である。プログラミング中、電子は誘電体を介して基板からフローティング・ゲートに注入される。同様に、消去中、電子は誘導体を介してフローティング・ゲートから抽出される。どちらの場合も、誘電体に電子が捕獲されてしまう可能性がある。捕獲された電子は、印加された電界と、その後実行されるプログラミング／消去サイクルに対抗し、その結果、プログラ

50

ミングのしきい電圧が以前より低くなり、消去のしきい電圧が以前より高くなるという現象が起こる。これによって、プログラミングと消去の状態間の電圧範囲が徐々に狭まるよう見えるだろう。プログラミング／消去サイクルが持続された場合、デバイスは、いずれ修復不可能な故障を引き起こす恐れがある。マルチステートメモリが実装されている場合には、より的確なしきい電圧が要求されるため、この問題はさらに深刻なものとなる。

#### 【0006】

二つ目の問題はフローディング・ゲートの電荷保持に関する。例えば、フローディング・ゲートの負電荷は、しばらくすると漏れて減少する傾向がある。これが原因で、時間とともにしきい電圧がより低い値にシフトしてしまう。デバイスの寿命がくる時には、しきい電圧は1ボルト以上もシフトしているかもしれない。マルチステートデバイスでは、これによりメモリ・セルの状態が一つか二つシフトしてしまう可能性もある。

10

#### 【0007】

三つ目の問題は、メモリ・デバイスの複数のセルに、プログラミング／消去サイクルが均等に行われないことである。例えば、メモリ・セルのセットに反復的なパターンが継続的にプログラミングされることはある。従って、幾つかのセルは常にプログラミングおよび消去されるのに対して、他のセルは滅多にあるいは全くプログラミングされない。このような不均等なプログラミングと消去は、特定のセクタのセルに不均等なストレス・コンディションをもたらす。不均等なプログラミング／消去サイクルの履歴は、個々の状態の全てにおいて、しきい電圧の分布をより幅広くしてしまう。しきい電圧の分布の拡大に加え、いくつかのセルでは上述の電圧範囲の狭まり、デバイスの故障あるいは電荷保持の問題がその他のセルよりも早く生じるかもしれない。

20

#### 【課題を解決するための手段】

#### 【0008】

##### (発明の要旨)

本発明は概略では、メモリ・システムの読み取り処理を改善するために使用されるトラッキング・セルに関する。様々な実施形態において、トラッキング・セルは、データ修復処理の一部として使用され、データの品質に関する問題点を指摘する警告を提供するために使用されたり、および／または、データがメモリにおいてどのように符号化されるかについての指示を保持する手段として使用されたりする。一実施形態では、エラー訂正符号(ECC)処理がデータのエラーを訂正できない場合に、トラッキング・セルはデータ修復のためだけに使用される。

30

#### 【0009】

本発明の一実施形態は、記憶素子のセットを含むメモリ・システムに保持されているデータを読み取る工程を含む。記憶素子は、データ記憶素子とトラッキング記憶素子を含む。データ記憶素子は、複数の状態のセットにおいて巡回可能に符号化されたデータを保持することができる。トラッキング記憶素子は読み取られ、複数のトラッキング状態に分類される。トラッキング状態は、データ記憶素子によって利用される複数の状態のサブセットに対応する。トラッキング記憶素子の分類に基いて、ローテーション・スキーム(すなわち、選択される特定の巡回符号化)が特定される。幾つかあるいは全てのデータ記憶素子が、特定されたローテーション・スキームを用いて読み取られる。一つの実施例では、ローテーション・スキームを特定する工程は、2またはそれ以上の非冗長なトラッキング記憶素子の分類を組み合わせて、他の識別子と結合されることでローテーション・スキームを指示する識別子を生成する工程を含む。

40

#### 【0010】

本発明のもう一つの実施形態は、トラッキング・セルに対して複数の読み取り動作を行い、それらの動作の間にエラー情報を記録する工程を含む。記録されたエラー情報に基いて、品質ゲージが特定される。品質ゲージが所定の基準を満たしたら、所定の応答が実行される。所定の数のトラッキング記憶素子にエラーがある場合、所定の数のトラッキング・セルのしきい電圧が少なくとも所定の値だけ予想値と異なる場合、あるいはエラーしきい値の連続的なセット(例えば、時間に関して異なるエラー・レベル)を超えている場合

50

、品質ゲージは警告を含むことができる。応答の例としては、読み取り処理の強制終了や、ECC操作のパラメータの変更、および／またはデータ修復処理の開始などが含まれる。

#### 【0011】

本発明による幾つかの実施形態は、記憶素子の状態群のサブセットのそれぞれの状態に對して、複数の読み取り動作を実行する工程を含む。記憶素子の状態群は、メモリ・システムにおけるマルチステート記憶素子について、異なるデータ値を表現する。その複数の読み取り動作の結果に基いて、記憶素子の状態群のそれを識別するための比較値の現在のセットが特定される。一つの実施例では、第1の状態に關連する複数のしきい電圧レベル群についてのキャッシング記憶素子群の第1のセットに読み取り動作を実行する工程と、その記憶素子群の第1のセットに読み取り動作を実行する工程に基いて、キャッシング記憶素子群の第1のセットについてのしきい電圧レベル群を特定する工程と、第2の状態に關連する複数のしきい電圧レベル群についてのキャッシング記憶素子群の第2のセットに読み取り動作を実行する工程と、その記憶素子群の第2のセットに読み取り動作を実行する工程に基いて、キャッシング記憶素子群の第2のセットについてのしきい電圧レベル群を特定する工程と、特定された第1の状態に対するしきい電圧レベル群と第2の状態に対するしきい電圧レベル群に基いて、現在の読み取りの比較値を変更する工程を含む。ここで、第1の状態と第2の状態は、互いに隣接するものではない。

#### 【0012】

上述した様々な読み取り動作は、ホスト・デバイスがデータをリクエストした時の応答として、あるいは（例えば、他の場所へのデータのコピーや、ガバージ・コレクションなどの）内部的な動作の一部として実行される。

#### 【0013】

本発明の一実施例は、記憶素子群のセットと制御回路を含む。その記憶素子群は、マルチステート記憶素子群とキャッシング記憶素子群を含む。そのキャッシング記憶素子群は、そのデータ記憶素子群によって用いられる複数の状態群のサブセットを用いる。制御回路は、キャッシング記憶素子群と通信しており、上述の機能を実行させることができる。メモリ・システムはEEPROMメモリ・システム、フラッシュ・メモリ・システム、あるいは他の適当な種類のメモリ・システムでもよい。一実施例では、制御回路は記載された機能を達成するために特注されたハードウェアを含む。他の1つの実施例では、制御装置は記載された機能を達成するようプログラミングされる。例えば、制御装置をプログラミングするため、ソフトウェア／ファームウェアが1またはそれ以上のプロセッサで読み取り可能な記憶媒体（例えば、フラッシュ・メモリ、EEPROM、DRAM、および他の媒体）に保存されていてもよい。

#### 【0014】

典型的な一実施例では、データ記憶素子群は8つのしきい電圧状態（状態0、状態1、状態2、状態3、状態4、状態5、状態6、状態7）を利用し、キャッシング記憶素子は状態1と状態6を使用する。ローテーション・コードの1ビットを確立するため、キャッシング素子はペアにグループ分けされる。ローテーション・コードは3ビットで構築される。3つのペアの複数セット（例えば、4セット）が、冗長性のために利用される。

#### 【発明を実施するための最良の形態】

#### 【0015】

本発明の上述およびその他の目的および利点は、以下に図面とともに説明される本発明の好ましい実施形態の記載から、より明確となるであろう。

#### 【実施例】

#### 【0016】

（詳細な説明）

（1. メモリ・システム）

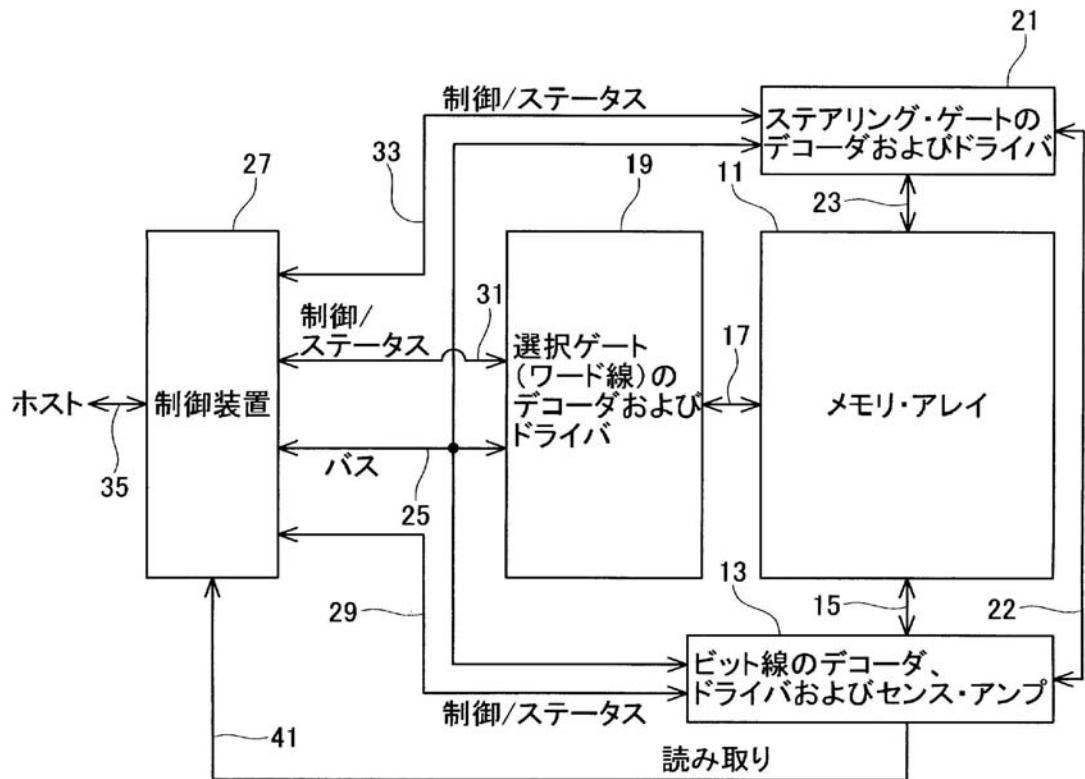

図1の構成図は、本発明の様々な特徴を取り入れたメモリ・システムの例を示す。本発明は、図1の構造だけでなく、他の構造でも使用できる。多数の個々にアドレス可能なメ

10

20

30

40

50

モリ・セル 11 は、行と列のアレイに配列されている。アレイ 11 の列に沿って延びるビット線は、線 15 を介してビット線のデコーダ、ドライバおよびセンス・アンプ回路 13 と電気的に接続されている。アレイ 11 の行に沿って延びるワード線は、線 17 を介してワード線のデコーダおよびドライバ回路 19 と電気的に接続されている。アレイ 11 のメモリ・セルの列に沿って延びるステアリング・ゲートは、線 23 を介してステアリング・ゲートのデコーダおよびドライバ回路 21 に電気的に接続されている。回路 13、19、および 21 はそれぞれバス 25 を介して制御装置 27 からアドレスを受信する。デコーダおよびドライバ 13、19、および 21 は、個々の制御およびステータス信号線 29、31 および 33 を通じても、制御装置 27 に接続されている。ステアリング・ゲートとビット線に印加される電圧は、制御装置とドライバ 13 および 21 を相互接続するバス 22 を介して調整される。10

#### 【0017】

制御装置 27 は、線 35 を介してホスト・デバイス（図示せず）に接続可能である。そのホスト・デバイスは、パソコン、ノート・パソコン、携帯型デバイス、デジタル・カメラ、オーディオ・プレーヤー、セルラー電話や、他の様々なデバイスでもよい。図 1 のメモリ・システムは、PCMCIA、CompactFlash<sup>TM</sup> Association、MMC<sup>TM</sup> Association、スマート・メディア、Secure Digital<sup>TM</sup>、メモリ・スティックなどの、現存する技術的および電気的標準規格に基づいたカードとして実装される。カード形式の場合、線 35 はそのカード上でホスト・デバイスの予備コネクタとインターフェース接続するコネクタにおいて終端処理される。あるいは、図 1 のメモリ・システムは、ホスト・デバイスに内蔵することができる。さらにあるいは、制御装置 27 をホスト・デバイスへ内蔵して、メモリ・システムの他の部分を取り外し可能なカード上に実装することができる。他の実施形態では、メモリ・システムはカード以外のパッケージに実装することができる。例えば、メモリ・システムを 1 つまたはそれ以上の集積回路、あるいは 1 つまたはそれ以上の回路基板、あるいはそれ以外のパッケージなどに実装することができる。20

#### 【0018】

デコーダおよびドライバ回路 13、19 および 21 は、制御およびステータス信号線 29、31 および 33 のそれぞれの制御信号に従って、バス 25 上でのアドレス指定のとおりに、アレイ 11 のそれぞれの線に適切な電圧を生成して、プログラミング、読み取り、および消去の機能を実行する。電圧レベルおよびその他のアレイ・パラメータを含むステータス信号は、アレイ 11 によって制御装置 27 へ同じ制御およびステータス信号線 29、31 および 33 を介して提供される。回路 13 内にある複数のセンス・アンプは、アレイ 11 内のアドレス指定されたメモリ・セルの状態を示す電流あるいは電圧レベルを受け取る。読み取り動作中に、センス・アンプは制御装置 27 に線 41 を介してメモリ・セルの状態の情報を提供する。多数のメモリ・セルの状態を並列に読み取るため、通常は多数のセンス・アンプが使用される。30

#### 【0019】

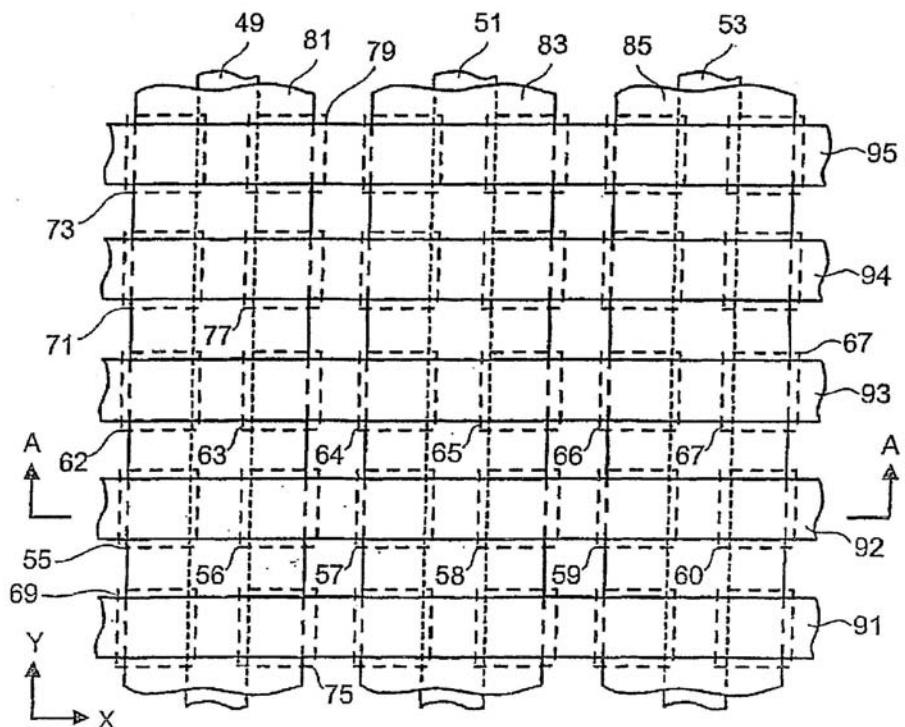

##### (2. メモリ・セル)

図 2 は、メモリ・アレイ 11 の一部分の第一実施形態を表す平面図である。図 3 は、そのメモリ・アレイのセクション A - A における部分的断面図を示す。基板と導体素子が、それらの間に配置された誘電体層の概略と共に示されている。これにより図面が簡略化されるが、導電層同士の間、および導電層と基板の間に、適切な酸化被膜が含まれると理解するべきである。40

#### 【0020】

シリコン基板 45 は、平らな上側表面 47 を含む。最初のイオン注入と、それに続く拡散によって、細長い拡散領域 49、51、および 53 が、表面 47 を介して基板 45 内に形成される。細長い拡散領域 49、51、および 53 は、メモリ・セルのソースおよびドレインとしての役割を果たす。本明細書においては、拡散領域は第 1 の「X」方向に間隔を置いて、第 2 の「Y」方向に長く伸びて示されている。これらの「X」方向と「Y」方向は原則的に互いに直交している。幾つかのフローティング・ゲートが基板表面 47 にわ50

たって、それらの間の適当なゲート誘電体とともに、行と列のアレイに配列されている。フローティング・ゲート 55、56、57、58、59、および 60 の 1 行は、フローティング・ゲート 62、63、64、65、66、および 67 の他の 1 行と平行に隣接している。フローティング・ゲート 69、55、62、71、および 73 の 1 列は、フローティング・ゲート 75、56、63、77、および 79 の他の 1 列と平行に隣接している。上記のフローティング・ゲートは、導電的にドープされた第 1 の多結晶シリコン（ポリシリコン）層から形成される。それは、表面に蒸着された後に、1 またはそれ以上のマスキング工程を用いたエッティングによって、個々のフローティング・ゲートに分離されている。

## 【0021】

10

ビット線のデコーダおよびドライバ 13（図 1 を参照）は、線 15 を介して、図 2 および図 3 の拡散領域 49、51、および 53 を含むアレイの全てのビット線のソース／ドレインの拡散領域に接続されている。個々のメモリ・セルの列のソースとドレインは、バス 25 を通して供給されるアドレスと線 29 上の制御信号に応じて読み取りあるいはプログラミングを行う上で適した動作電圧に接続されている。

## 【0022】

図 2 と図 3 の構造では、フローティング・ゲートの列の 2 列ごとに 1 つのステアリング・ゲートを用いる。ステアリング・ゲート 81、83、および 85 は、「Y」方向に伸びており、隣接する 2 つのフローティング・ゲートの列とそれらの間に配置されているソース／ドレインの拡散領域にわたって広がる「X」方向の幅を持っている。どの 2 つのステアリング・ゲートの間隔も、その 2 つのステアリング・ゲートが重ねられている隣接するフローティング・ゲートの列の「X」方向における間隔と少なくとも同程度に大きい。これは後でその間隔において基板にゲートを形成するためである。ステアリング・ゲートは、導電的にドープされた第 2 のポリシリコン層をエッティングすることによって形成される。その第 2 のポリシリコン層は、第 1 のポリシリコン層と適当なポリシリコン層間の誘電体の全表面にわたって蒸着されたものである。ステアリング・ゲートのデコーダおよびドライバ 21（図 1 を参照）は、線 23 を介して全てのステアリング・ゲートに接続され、バス 25 上で提供されるアドレスと、線 33 上の制御信号と、ドライバおよびセンス・アンプ 13 からのデータに応じて、それぞれの電圧を個々に制御することができる。

20

## 【0023】

30

図 2 および図 3 のワード線 91、92、93、94、および 95 は、「X」方向に伸びており、各ワード線がフローティング・ゲートの行に沿うように、「Y」方向に間隔を空けながら上記のステアリング・ゲートの全体に広がっている。ワード線は、導電的にドープされた第 3 のポリシリコン層をエッティングすることによって形成される。その第 3 のポリシリコン層は、第 2 のポリシリコン層、およびステアリング・ゲート同士の間で露出した領域の上にまず形成された誘電体の、上側表面の全てにわたって蒸着されたものである。ワード線は、読み取りまたは書き込みのための、ワード線の行における全てのメモリ・セルの選択を可能とする。メモリ・アレイの 1 つの行を個々に選択するため、選択ゲートのデコーダおよびドライバ 19（図 1 を参照）が、それぞれのワード線に接続されている。選択された行の個々のセルは、ビット線のデコーダおよびドライバ 13 と、ステアリング・ゲートのデコーダおよびドライバ 21（図 1 を参照）による読み取りまたは書き込みを可能にする。

40

## 【0024】

このような構造のゲートの素材は、ドープされたポリシリコン材料が好ましいが、上述した 3 層のポリシリコン層の 1 つまたはそれ以上の代わりに、他の適当な導電性材料が用いられてもよい。例えば、ワード線と選択ゲートが形成される第 3 の層については、導電性を高めるために、ポリサイド材料であってもよい。ポリサイド材料は、導電性の高融点金属（例えばタングステン）シリサイドを上面に備えるポリシリコンである。ポリサイドは、通常は第 1 のポリシリコン層や第 2 のポリシリコン層の代わりに用いられることが多い。なぜなら、ポリサイドから形成される多結晶シリコン間酸化物の品質は、たいていの

50

場合は満足のいくものではないからである。

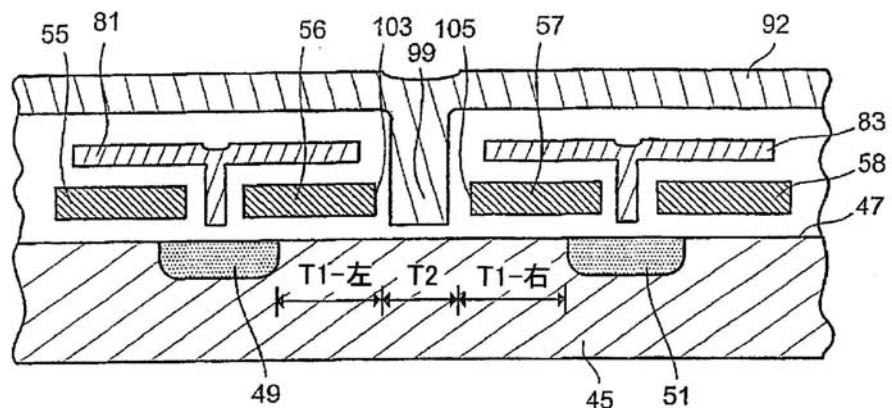

**【0025】**

図2および図3には、金属導電層が図示されていない。たいていの場合、拡散領域とポリシリコン素子の導電性は金属の導電性より極めて低いため、それぞれの金属線が全ての中間層にわたってポリシリコン素子と拡散領域の長さ方向に周期的な間隔で配置されるように、個々の層に金属の導電体が含まれている。図2および図3の実施形態の全ての拡散領域とポリシリコン素子は、別々に駆動されなければならないため、通常は多数の金属線と多数の拡散領域およびポリシリコン素子の間に、1対1の対応関係がある。

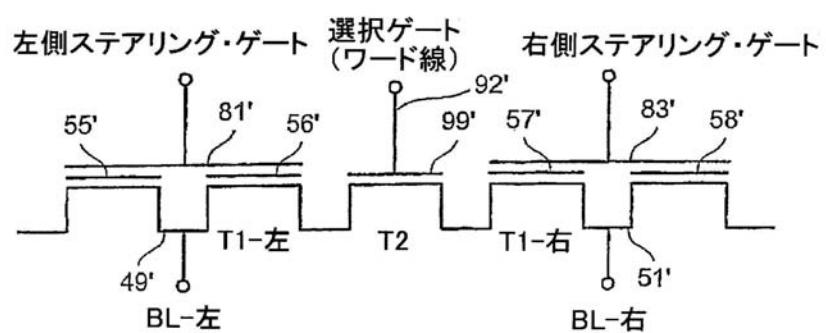

**【0026】**

図4は図3の構造と電気的に等価な回路を図示しており、等価な素子には図2および図3における参照符号と同一の符号にプライム(')を付して示している。図示された構造は、ソースおよびドレインの拡散領域を、隣接する構造と共有している。互いに隣接する拡散領域4'9および5'1の間での基板におけるチャネルの導通は、3つの異なる領域における異なるゲート素子によって制御される。左側の第1の領域(T1-左)は、真上に位置するフローティング・ゲート5'6と、容量結合されたステアリング・ゲート8'1を備えている。右側の第2の領域(T1-右)は、同様に、フローティング・ゲート5'7とステアリング・ゲート8'3によって制御される。第3の領域T2は、T1-左とT1-右の間に位置し、ワード線9'2の一部である選択ゲート9'9によって制御される。

**【0027】**

従って、拡散領域4'9および5'1の間のチャネルを電子が導通するレベルは、これらの異なるゲート素子に加えられる電圧により、これらのゲート素子によってそれぞれのチャネル領域に印加される電界によって影響を受ける。フローティング・ゲートの電圧は、ゲートが保持する正味の電荷に他のゲートおよびノードから容量結合された変位電荷を加えたレベルに依存している。フローティング・ゲートの下方のチャネル部において許容される導通のレベルは、そのフローティング・ゲートの電圧によって制御される。選択ゲート9'9の電圧は、ソース/ドレイン領域を接続する個々のセルを選択するために、チャネルを任意の導通レベルにまでオンしたりオフしたりする。1つの実施形態では、単一のメモリ・セルは、3つのトランジスタが直列接続されたものだと考えることができる。この場合において、3つの異なるチャネルの領域(T1-左、T2、T1-右)のそれぞれが、1つのトランジスタに相当する。他の実施形態では、各フローティング・ゲートが単一のメモリ・セルだと考えることができる。

**【0028】**

単一のメモリ・セルが持つ2つのフローティング・ゲートのうちの一方が、プログラミングまたは読み取りのために選択される。それは、他方の(選択されていない)フローティング・ゲートによって保持される電荷にかかわらず、その他方のフローティング・ゲートのチャネル領域が十分に導通するように、その他方のフローティング・ゲート上のステアリング・ゲートに電圧を印加することにより行われる。ワード線に加えられる十分な電圧によって、そのセルの選択トランジスタがオンに切換えられると、その選択されたフローティング・セルのみが、そのセルに指示された読み取りまたはプログラミングの実行に応じる。その一方のフローティング・ゲートの状態の読み取りをしている間、ソースとドレインの間を流れる電流は、他方のフローティング・ゲートの電荷にかかわらず、選択されたフローティング・ゲートによって保持される電荷に依存する。選択されていないフローティング・ゲートの下方のチャネル部を導通させるために、その選択されていないフローティング・ゲート上のステアリング・ゲートに加えられる電圧は、その同じステアリング・ゲートを通して隣接するセルの隣接するフローティング・ゲートにも結合されている。しかしながら、その隣接するセルの他の素子について適当な電圧コンディションを保つことによって、その隣接するセルへの影響は排除される。

**【0029】**

図2~4の実施形態のフローティング・ゲートは、そのフローティング・ゲートのビット線(ソースおよびドレインの拡散領域)と2つのステアリング・ゲートに電圧を印加し

10

20

30

40

50

、基板のチャネル領域にある電子にゲート誘電体を横切って選択されたフローティング・ゲート上へ注入されるのに十分なエネルギーを得させることによって、プログラムされることが好ましい。これを行うための好適な技術が、アメリカ合衆国特許番号 5,313,421 と番号 5,712,180 に記載されている「ソース側注入」である。これらの文献は、参照することによって、本明細書に組み込まれる。

#### 【0030】

図 2 ~ 4 の実施形態のメモリ・セルを消去するためには、電子を選択されたフローティング・ゲートからワード線の選択ゲートあるいはチャネルへ移動させるように設計され、動作させられるだろう。選択ゲートへ消去される場合、フローティング・ゲートの端部 103 と選択ゲート 99 の間の誘電体は、フローティング・ゲートの端部に成長した薄い酸化層であって、セルの様々な素子に適切な電圧が印加された時に電子がトンネル移動するものであることが好ましい。フローティング・ゲートの端部 105 と選択ゲート 99 の間に 10 も、同様のものが設けられている。選択ゲート 99 へ消去されるよう設計された場合、ゲート誘電体を横切ったその選択ゲートと基板表面 47 の間の電圧勾配が、その誘電体の破壊レベルより十分に低く維持されるように注意しなければならない。その理由は、ふつうは消去している間はワード線が 10V を超え、場合によっては 20V 以上にまでレベルが上げられるのに対して、セルに加えられる他の電圧は 5V 以下であるからである。選択ゲートの誘電体を横切る電圧勾配は、誘電体を厚くするか、通常より大きな誘電率を選択することにより、低減することができるが、これは選択トランジスタの動作に悪影響を及ぼす可能性がある。 20

#### 【0031】

セルがチャネルへ消去されるものである場合、図 2 ~ 4 の実施形態はいくらか変更される。まず、選択ゲート 99 と、隣接するフローティング・ゲートの端部 103 および 105 の間の誘電体をより厚くして、フローティング・ゲートから選択ゲートへの消去を防止する。次いで、フローティング・ゲートの下面と基板表面 47 との間のゲート誘電体の厚さを薄くして、例えば 100 オングストローム程度まで薄くして、電子のトンネル移動を容易なものとする。さらに、1 つのロックとして同時に消去されるべきセル群は、列に沿って、あるいはブロックの中でグループ化される。一実施形態では、基板上において、あるブロックは他のブロックから隔離されている。通常は、これはトリプル・ウェル処理によって行われている。ここでは、p 型基板に n ウェルが形成され、セルのブロックを保持する p ウェルが、他のブロックからそのブロックを隔離する n ウェルの内部に位置決めされる。そして、その他のブロックに影響を及ぼすことなく、消去されるべきブロックの p ウェルに適切な消去電圧が印加される。 30

#### 【0032】

図 1 ~ 5 の構造のさらなる詳細は、アメリカ合衆国特許番号 6,151,248 に記載されている。この文献は、その全てを参照することによって、本明細書に組み込まれる。図 2 ~ 4 のメモリ構造は、適切なメモリ・セルの一例である。本発明を実装するために、他の構造が用いられてもよい。例えば、一実施形態では、帶電した誘電体を含む複数層の誘電体を用いることもできる。

#### 【0033】

##### (3. メモリ・アレイの動作)

図 5 の表に、アレイ 11 のメモリ・セルをプログラミング、読み取りおよび消去するための動作電圧の例を示す。(2) の行は、選択ゲート(ワード線)へ消去される種類のセルの動作に関するものであり、(8) の行は、基板へ消去される種類のセルの動作のために変更したものを示す。これらの例では、セルが形成される基板の部分には p 型ドーピングを含み、ビット線の拡散領域は n 型である。これらの動作の間、基板は接地されている。

#### 【0034】

図 5 の表の(1) の行には、選択されていない行の電圧コンディションを示している。選択されていない行のワード線は、ドライバ回路 19 (図 1) によって接地される。選択 50

されていない行に沿うセルの、ビット線（拡散領域）とステアリング・ゲートの列における「X」は、その素子にかかる電圧が問題とならない、「無関係な」状況にあることを示す。回路13、19および21は何れも、アレイの素子に対して負の電圧を生成することはないから、この例では、行の選択ゲートの電圧が0Vであれば、その行に沿うセルのうち有効となるものは1つもないことが保証される。それらのチャネルには、電流が流れない。異なる行で同じ列にある他のセルのプログラミングや読み取りは、ワード線が0Vである行に影響を及ぼすことなく行うことができる。

#### 【0035】

表の(2)の行には、ワード線の選択ゲートへ消去されるように設計された種類のセルを消去するための電圧のセットの例を示す。10V～25Vの範囲（例えば20V）の高い消去電圧 $V_E$ が、ドライバ回路19によって、消去されるべきフローティング・ゲートのワード線の全てに印加される。これは通常は、隣接する多数の行の全てのセルを含む、少なくとも1つの特定されたセル群のブロックである。しかしながら、好ましい応用例では、より少ないセル、あるいはより多くのセルが、同時に消去されてもよい。あるいは、その消去されるブロックは、単一の行のセルに制限されてもよい。1つまたはそれ以上の選択された行に沿うセルのステアリング・ゲートは、ステアリング・ゲートとフローティング・ゲートの間の高度な容量結合を利用してフローティング・ゲートの電圧を低いレベルに維持するために、ドライバ回路21によって低電圧（例えば0V）に設定される。フローティング・ゲートとそれぞれの選択ゲート（ワード線）との間に生じる電位差は、中間に介在する誘電体を通って電子がトンネル移動する原因となる。消去についての詳細は、アメリカ合衆国特許番号5,270,979に記載されている。この文献は参照によって本明細書に組み込まれる。

10

20

30

#### 【0036】

図5の表の(3)の行と(4)の行は、メモリ・セルの2つのフローティング・ゲートの状態を読み取るための電圧の例を示す。(3)の行は左側のフローティング・ゲートに対するものであり、(4)の行は右側のフローティング・ゲートに対するものである。どちらの場合も、選択ゲートの電圧が、そのセルの選択トランジスタをオンに切換えるのに十分な電圧 $V_{SR}$ まで引き上げられて、そのチャネルを通して電流を流すことが可能となることにより、セルが有効化される。この電圧は通常、選択トランジスタのしきい電圧より1V高い。

30

#### 【0037】

図5の表の(3)の行と(4)の行に示すように、一方のフローティング・ゲートの電圧状態を読み取る場合には、その読み取られるフローティング・ゲートの上方のステアリング・ゲートには電圧 $V_M$ が印加され、他方のフローティング・ゲートの上方のステアリング・ゲートは電圧 $V_{BR}$ まで引き上げられる。選択されていないフローティング・ゲートのプログラミングされた状態にかかわらず、電圧 $V_{BR}$ はその選択されていないフローティング・ゲートの下方のセルのチャネル部が十分に導通するように、十分に高い電圧（例えば8V）とされる。選択されたフローティング・ゲートの状態を読み取るために、電圧 $V_M$ は読み取り工程の間に複数の電圧（後述する）を段階的に経る。その電圧値は、セル電流が所定のしきい電圧を通過する時に、回路13の内部のセンス・アンプによって検知される。

40

#### 【0038】

図5の表の(5)の行と(6)の行には、二重フローティング・ゲート・セルの一方のフローティング・ゲートをプログラミングするための電圧の例が示されている。動作させるセルを選択するために、選択ゲートが、そのセルの選択トランジスタをオンに切換えるために必要な電圧まで引き上げられる。ソース側注入のプログラミング速度を最適化するために、電圧 $V_{SP}$ は読み取りの間に使用される電圧 $V_{SR}$ とは異なるものとしてよい。例えば、選択トランジスタのしきい電圧が1Vの場合、 $V_{SP}=2.2V$ である。プログラミングされるように選択されたフローティング・ゲートとセルの同じ側にあるビット線の拡散領域は、プログラミング動作の間、最大ビット線電圧（例えば5V）まで引き上げられる。こ

50

の電圧は、フローティング・ゲート・チャネルと選択ゲート・チャネルの間の隙間を横切って十分な電界を発生させて、ソース側のホット・エレクトロン・プログラミングを得るために必要な大きさにされる。選択されていないフローティング・ゲートとセルの同じ側にあるビット線の拡散領域は、プログラミングの間、0 V またはその近傍にバイアスされている。

#### 【0039】

選択されていないフローティング・ゲートの上方のステアリング・ゲートは、そのフローティング・ゲートの下方のチャネル領域を十分に導通させるために必要な電圧 $V_{BP}$ （例えば、 $V_{BP} = 8 V$ ）まで引き上げられる。これは、目標とするフローティング・ゲートのプログラミングの妨げとならないようにするためである。これは、選択されていないフローティング・ゲートに、どれだけのフローティング・ゲート電圧が存在しているかにかかわらず、そのフローティング・ゲート電圧のプログラム・ウィンドウの範囲内で行われる。ホット・エレクトロン・プログラミングのために、その選択されたフローティング・ゲートをその下方のチャネルにおいて望ましい電界コンディションを作り出すことを助けるような電圧まで駆動するレベルで、その選択されたフローティング・ゲートの上方のステアリング・ゲートに、電圧 $V_p$ が印加される。例えば、電圧 $V_p$ は 5 ~ 12 V の範囲内でおい。この電圧は、プログラミング動作の間に変化することがある。通常は、まず消去されたセルに適切なプログラミング電圧のセットが印加され、続いて、適切な読み取り電圧のセットが印加される。そして、読み取り工程が、選択されたフローティング・ゲートが望ましい電圧状態にプログラミングされていると指摘しない場合、以前の電圧のセットとは部分的に異なるかも知れないプログラミング電圧が再び印加される。ここで、望ましい電圧状態は、バイナリ・ストレージのプログラミング状態であってもよいし、複数レベル・ストレージの可変ストレージ状態であってもよい。

#### 【0040】

図 5 の表の (7) の行は、プログラミングするために選択された行の内部にあって、それ自体はプログラミングされないセルに印加される電圧を示す。例えば、アレイのセグメント化された部分の 1 つの行の内部で同時にプログラミングされる複数のセルは、プログラミングされない他のセルと、その行に沿って交互に配置されている。これらのプログラミングされないセルが、図 5 の表の (7) の行に示す電圧を受ける。相対するビット線の拡散領域は、チャネルにおいて電流が流れないように、同じ電圧（例えば、両方とも 0 V、あるいは両方とも 5 V）に保たれる。（1）の行で用いている表記と同じように、「X」はこれらのセルのステアリング・ゲートの電圧が、問題とならないことを示している。

#### 【0041】

メモリ・アレイが基板へ消去されるように設計されている場合には、(2) の行の消去電圧コンディションの代わりに、(8) の行の消去電圧コンディションが適用される。消去されるべきセル群のロックを含む p ウェルと、その p ウェルの周囲の n ウェルはは、両方とも消去電圧 $V_E$ まで引き上げられ、その範囲は例えば 10 V ~ 25 V（例えば 20 V が好ましい）である。このようなセルの読み取りおよびプログラミングの間は、これらのウェルは接地されている。消去の間は、選択ゲートの誘電体を横切って印加される電圧を低減するために、選択ゲートに正の電圧 $V_{SE}$ が印加されるのが好ましい。なぜなら、基板と選択ゲートの間の過剰な電位差は、誘電体を損傷してしまうか、あるいはセルの動作に対して望ましい厚さ以上に誘電体を厚くする原因となるからである。このような電圧は、選択ゲートから消去しようとする隣接するフローティング・ゲートへ部分的に結合するので、それほど高くすることができます、さもなければ、消去を成し遂げるために高くされているそのフローティング・ゲートとその基板のチャネルとの間の電位差を、極端に低くしてしまう。電圧 $V_{SE}$ の範囲は、例えば 3 ~ 12 V であり、電圧 $V_E$ のレベルに依存する。 $V_E = 20 V$  の場合には、 $V_{SE} = 10 V$  であることが好ましい。

#### 【0042】

図 5 において提示した数値は、1 つの例である。当業者は、メモリ・システムの動作のために、適切な他の数値および方法を用いることができる。

## 【0043】

## (4. ト r a c k i n g · セル)

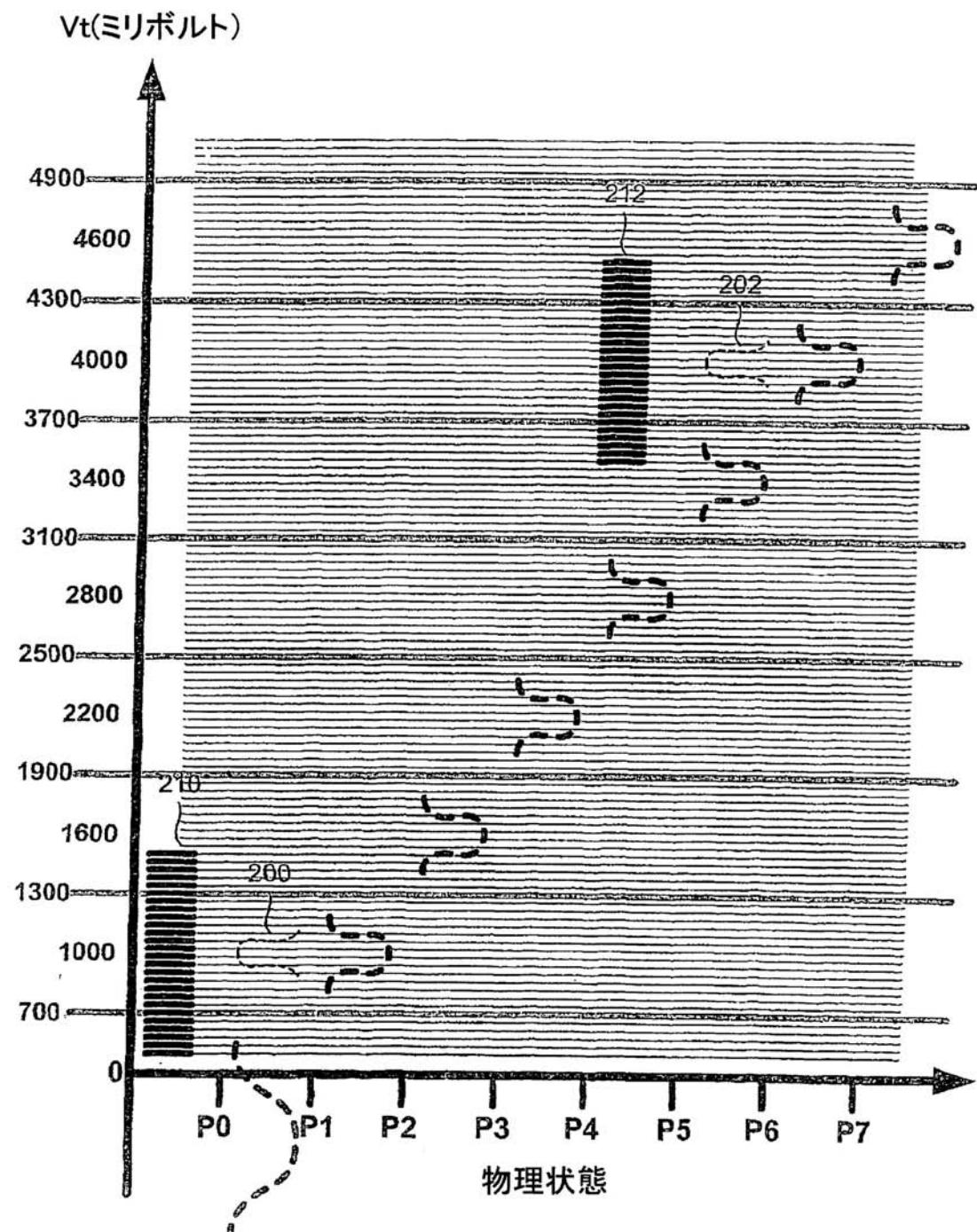

上述したように、フローティング・ゲートは、複数のレベル、すなわち複数の電荷の範囲を保持することができ、従って複数の状態を提供することができる。1つの実施形態では、フローティング・ゲートは8つの目標とする電荷の範囲を保持し、従って8つの状態を提供する。このようなフローティング・ゲートは、3ビットのデータを保持する。図6は、8つの状態を保持できるフローティング・ゲートの典型的な状態空間を図示している。図6は8つの物理状態P0、P1、P2、P3、P4、P5、P6、およびP7を示す。例示を目的として、図6の縦軸はしきい電圧をミリボルト単位で示している。しかしながら、実装形態によっては、他の単位が用いられてもよい。それぞれの物理状態に対して、図6はしきい電圧レベルの範囲または分布を釣鐘曲線で描く。通常、釣鐘曲線の頂部（すなわち、最も右側の点）が、その状態の中心である。例えば、状態P1の中心は1000mVにあり、下側の境界は800mVに、上側の境界は1200mVにある。状態間にある領域は、状態から状態へのスレッショルド・マージンである。隣り合った状態間のそれぞれに1つずつ、合計で7つのスレッショルド・マージンがある。隣り合った状態P1とP2の間には、スレッショルド・マージンがある。図6では、状態P1～P7は正の電圧であり、状態P0は負の電圧を含んでいる。他の実施形態では、より多くの、あるいはより少ない数の状態が、正または負であってもよい。さらに、様々な実施形態では、それぞれのメモリ・アレイに特有の特徴や条件に応じて、電圧範囲は0～4900mVとは異なっていてもよい。

10

20

## 【0044】

8つの状態を保持するフローティング・ゲートは、3ビットのデータを保持することができる。従って、8つの論理状態が存在する。一実施形態では、フローティング・ゲートのしきい電圧が隣の物理状態に誤ってシフトしてしまった場合に影響を受けるビットを1ビットのみに抑えるために、これらの論理状態はグレイ・コード割り当てを用いて、物理状態に割り当てられる。図7の表は、バイナリ・データを論理状態に割り当てるグレイ・コードの割り当ての例を示す。他の実施形態では、グレイ・コード以外の割り当ても用いることができる。各論理状態は一つの物理状態に割り当たられる。しかしながら、論理状態の物理状態への割り当ては巡回可能である。図8の表は、論理状態の物理状態への割り当てについての、8つの異なるローテーション・スキームを示す。例えば、ローテーション0においては、物理状態P0は論理状態L0（例えば、バイナリ・データの000）を保持し、物理状態P1は論理状態L1（例えば、バイナリ・データの001）を保持し、・・・などと続く。ローテーション1では、物理状態P0は論理状態L7（例えば、バイナリ・データの100）を保持し、物理状態P1は論理状態L0（例えば、バイナリ・データの000）を保持し、・・・などと続く。このように、プログラミングをする際には、8つのローテーション・スキームが使用可能である。本発明の一実施形態では、1つのセクタがプログラミングされるたび、そのセクタはまず消去され、そして8つのローテーション・スキームのうちの1つを用いてプログラミングされる。それに続くプログラミング／消去サイクルにおいては、そのセクタは異なるローテーション・スキームを用いてプログラミングされるであろう。一実施形態では、メモリ・デバイスはそれぞれのローテーション・スキームを順番に巡回する。他の実施形態では、メモリ・デバイスはそれぞれのプログラミング・サイクルに対して、ランダムに（あるいは擬似ランダムに）ローテーション・スキームを選択するであろう。データを巡回することによって、セクタにプログラミングされる実際のデータ・パターンとは無関係に、そのセクタの全てのセルについて、プログラミング／消去サイクルの繰り返しを通して、均一なストレス・コンディションを維持することが促進される。データの巡回に関して、一実施形態では、任意の消去プロックの全てのセクタは履歴を一致させながら動作するため、同一の消去後のローテーションをそれら全てのセクタに伝播させることが可能である点に留意されたい。さらに、内部セクタの消耗の均等化が不十分な場合には、何らかの手法による強制的にプログラミングされた内部セクタの消耗の均等化（例えば、強制レベルや論理データ・パターンの臨時的な

30

40

50

プログラミング)が必要となるかもしれない点にも留意すべきである。

#### 【0045】

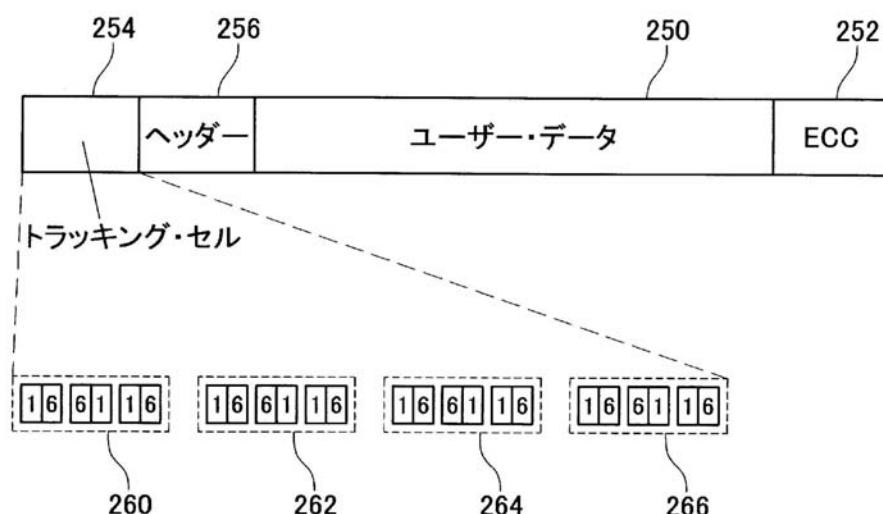

一実施形態では、メモリ・アレイ11は複数のセクタに分割される。セクタがどのように分割されるかについての一実施形態を図9に図示する。そのセクタは、ユーザー・データ250とECCデータ252を含む。そのセクタは通常、一つのワード線上のセル群のサブセットからなり、512バイトのユーザー・データを保持することができる。本発明では、セクタについて他の定義も用いることができる。そのセクタはさらに、トラッキング・セル254とヘッダー情報256(ユーザーによって直接決定はされない)を含む。ヘッダー情報は、アドレス情報、ビットおよび/またはセクタ・マッピングに関する情報およびセクタへの書き込み回数を含む。他の情報についても、ヘッダーに保持することができる。トラッキング・セルの例は、アメリカ合衆国特許番号5,172,338、番号6,222,762、および番号6,538,922に記載されている。これらの文献は全て、全体を参照することによって本明細書に組み込まれる。トラッキング・セルは、フローティング・ゲートにおける電荷の様々な状態のそれぞれに対し、最適な識別ポイントを確実に定めるために用いられる。図9に示す実施形態では、セクタは24のトラッキング・セルを含む。そのトラッキング・セルはそれぞれペアにグループ分けされ、3つのペアが1つのセットにグループ分けされる。一実施形態では、各ペアは同じセクタ内にあるフローティング・ゲートのペアを含む。ここで、そのフローティング・ゲートは図2~4に図示されたものである。図9は、トラッキング・セルの4つのセット：セット260、セット262、セット264、およびセット266を示している。一実施形態では、これらのセットは同一の情報の冗長コピーである。10

#### 【0046】

一実施形態では、トラッキング・セルは2つの状態のどちらかでしかデータを保持しない。例えば、図9はそれぞれのトラッキング・セルが物理状態P1あるいは物理状態P6のどちらかでデータを保持している様子を示す。他の実施形態では、他の状態が使用されてもよい。多くの実施形態では、全ての状態は使用されない。例えば、図6は、8つの状態を備えるメモリ状態空間を示す。従って、本発明はトラッキング・セルに対して8つ未満の状態を用いる。状態群のサブセットを用いる1つの利点は、使用されている状態群(トラッキング・セル状態群)を、1またはそれ以上の状態をそれらの間に挟んで分離できることにある。状態P1とP6を選択した理由は、異なる動作環境や動作環境に起因して異なるしきい電圧の分布統計を持つかも知れない2つの端の状態(状態P0と状態P7)を除いて、状態P1と状態P6はしきい電圧レベルが最大限に離れており、最も大きな基準を与えることができるからである。例えば状態P0は、データのプログラミングにおける統計とは反対の、消去動作における統計に従うかも知れない。最も頻繁にプログラミングされる状態(状態P7)の範囲が広がると、中間の状態P1~P6に対しての分布の違い/オフセットを招くことになるかもしれない。図6は、しきい電圧の分布を釣鐘曲線で示す。対応するトラッキング・セルの分布は、より幅が狭い釣鐘曲線200と202で示されている。P1とP6を分離する大きなしきい電圧の差のおかげで、データ部がひどく損傷していない限り、多くのトラッキング・セルで検知を誤る(すなわち、低いしきい電圧の範囲と高いしきい電圧の範囲が入れ替る)可能性は、極めて低いであろう。30

#### 【0047】

状態の数が8つではない実施形態では、トラッキング・セルは上記とは異なる状態を用いてデータを保持してよい。例えば、4つの状態(例えば、P0、P1、P2、およびP3)を備えるデバイスにおいては、トラッキング・セルは状態P1とP3でデータを保持してよい。16の状態(P0、P1、P2、...P14、P15)を備えるデバイスにおいては、トラッキング・セルは状態P1とP14でデータを保持してよい。上記の状態の代わりに、あるいは上記の状態に加えて、他の状態を使用してもよい。

#### 【0048】

1つ思い浮かぶ質問は、対応するトラッキング・セルが、データ・ストリームのどこに配置されるべきかである。それらを後端に配置すれば、継続的にシフト・アウトする必要50

がなくなり、読み取りの間の時間をわずかに短縮できるかもしれないが、トラッキング情報を必要な時に読み取るため、セクタ全体のデータをシフト・アウトしなければならない可能性もある。このことはさらに、セクタの局所的な範囲にトラッキング・セルを物理的に集めてしまい、局所的な変化に対して脆弱にしてしまう傾向がある。トラッキング・セルをセクタの全体にわたって物理的に分散して配置することは、セクタの内部での局所的な変化に対応する能力を向上するが、その管理と使用は複雑かつ面倒である。トラッキング・セルを前端に配置することは、後端に配置する場合と同様、トラッキング・セルを物理的に一箇所に集めてしまう傾向があり、さらにトラッキング・セルは全ての読み取り動作において、それが必要であろうとなからうと、読み取り経路に含まれてしまう。しかしながら、一実施形態では、トラッキング・セルは、データの巡回状態を符号化するためにも用いられる。データの巡回を符号化するためにトラッキング・セルを使用する場合は、トラッキング・セルは、各読み取り処理の間に読み取られるべきである。従って、図9に示すように、トラッキング・セルをデータ・ストリームの前端に配置することは、道理にかなっている。ここで、セクタの内部でこれらのトラッキング・セルを物理的且つ均等に分散配置するとともに、先端でのトラッキング・セルの読み取りを提供することは、そのような実施形態を反映するようにアレイの復号化処理を構築することで可能となる点に留意されたい。10

#### 【0049】

各トラッキング・セルは、P1あるいはP6の状態でデータを保持している。すなわち、しきい電圧レベルはP1かP6のいずれかに設定される。隣接するセル同士（例えば、一実施形態では隣接するフローティング・ゲート同士）でペアを組む場合、ペアの一方は状態P1に、ペアの他方は状態P6になるように、プログラミングされる。従って、そのペアは16あるいは61の2つの配置の何れかを取りうる。ペアが16の場合、そのペアは論理0と見なされる。ペアが61の場合、そのペアは論理1と見なされる。従って、トラッキング・セルのペアは、1ビットの巡回符号化データ（0あるいは1）を形成するのに使用される。3つのペアのセットが、8つの可能なローテーション・スキームのうちの1つを示すのに適した3ビットの巡回符号化データを形成する。例えば、セット260は3ビットの巡回符号化データを含む。セット260の第1ビットは16、すなわち論理0である。セット260の第2ビットは61、すなわち論理1である。そして、セット260の第3ビットは16、すなわち論理0である。従って、セット260は符号010（10進値では2、すなわちローテーション2）である。他の実施形態では、8つ以上あるいは8つ以下のローテーションが使用可能なので、ローテーション・スキームを識別する符号は、3ビット以上あるいは3ビット以下（例えば、2ビットや5ビットなど）のビット数と、6つ以上あるいは6つ以下のトラッキング・セルおよび／またはフローティング・ゲートで形成できる。一実施形態では、フローティング・ゲートは16のレベル／状態を保持することが可能であり、4つ（あるいは他のビット数）の巡回ビットが使用される。一実施形態では、それぞれのセットは互いに冗長である。この冗長性を利用して、個々のトラッキング・セルのエラーを修復することができる。従って、セット262、264、および266は、全て010を保持する。ローテーション・スキームの符号を識別するには3ビット全て（および付随する6つのセル）が必要なので、特定のセット内の3つのビットおよび6つのトラッキング・セルは、互いに冗長ではない。3040

#### 【0050】

各セットに保持された3ビットは、特定のローテーション・スキームを示す符号を表現している。上述したように、図8は本発明の一実施形態における8つの異なるローテーション・スキームを示している。図10は、セット260、262、264、および266の内部に保持されている様々な符号が、どのように巡回状態に割り当てられているのかを示している。従って、161616のデータ・パターンはローテーション0に対応し、161661はローテーション1に対応し、166116はローテーション2に対応し、166161はローテーション3に対応し、611616はローテーション4に対応し、611661はローテーション5に対応し、616116はローテーション6に対応し、650

16161はローテーション7に対応する。

#### 【0051】

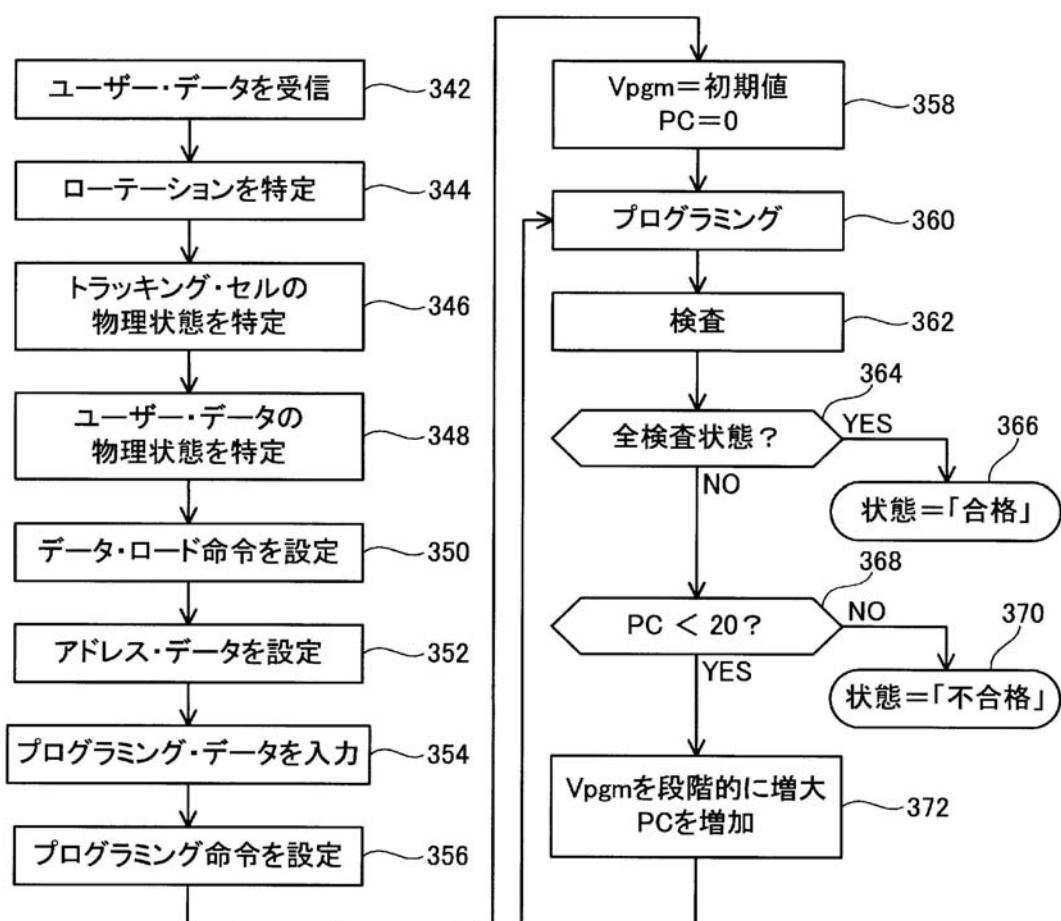

図11は、トラッキング・セルのプログラミングを含む、セクタのセルをプログラミングする処理を説明するフローチャートである。個々のセルをプログラミングする技術は上述したとおりである。図11はデバイス・レベルでの処理である。ステップ342では、ユーザー・データが受信される。すなわち、制御装置がホスト・システムからデータを受信する。別の場合には、スクラビングや、消耗の均等化や、ガベージ・コレクションなどの内部的な必要性によって、書き込まれるべきデータを内部で生成することもできる。ステップ344では、制御装置がどのローテーション・スキームを使用するかを特定する。上述したように、ローテーション・スキームは、順番に、ランダムに、疑似ランダムに、あるいは他の適当な手法によっても選択することができる。ステップ346では、選択されたローテーション・スキームに関連付けられた適切な物理状態が、それぞれのトラッキング・セルに対して特定される。すなわち、巡回符号(図10を参照)に基いて、適切なデータ・パターンがトラッキング・セルのセットに割り当てられる。一実施形態では、トラッキング・セルは巡回されない。ステップ348では、制御装置がプログラミングされる各データ値に対する物理状態を特定する。すなわち、図8の表を利用して、各データ値に対する各論理状態は、特定のメモリ・セルの物理状態に割り当てられる。幾つかの実施形態では、データがメモリに送信されると同時に、そのデータに対する物理状態が動的に計算される。

#### 【0052】

ステップ350では、制御装置から「データ・ロード」の命令が出される。ステップ352では、制御装置から適切なデコーダにアドレス・データが提供される。ステップ354では、ワード線とビット線を適切にバイアスし、選択されたビット線、ワード線、およびステアリング・ゲートを確立するためにデータとアドレスがラッチされ、プログラム・データがメモリ・アレイに入力される。ステップ356では、「プログラミング」の命令が制御装置から出される。

#### 【0053】

ステップ360では、プログラミング動作が実行される。多くの実施形態では、プログラミング電圧は多数のパルスに分割される。パルスの振幅は、それぞれのパルスごとに所定のステップ・サイズ分だけ増加する。パルスとパルスの間の期間において、検査動作が実行される。すなわち、各プログラミング・パルスの間に、並列にプログラミングされている各セルのプログラミング・レベルが読み取られ、そのデータに関連する検査レベルまで少なくとも達しているか否かを判断する。例えば、しきい電圧が2.5Vまで引き上げられている場合、検査処理はしきい電圧が少なくとも2.5Vであるか否かを判断する。一度ある任意のメモリ・セルのしきい電圧が検査レベルまで到達あるいは検査レベルを超えた判断されると、そのセルからプログラミング電圧が取り除かれて、さらなるプログラミングを終了させる。他のセルに並列に書き込まれているプログラミングは、それぞれがそれぞれの検査レベルに到達するまで持続し、到達した時点でプログラミングは終了する。

#### 【0054】

図11のステップ358では、プログラミング電圧(V<sub>pgm</sub>)が開始パルス・コンディションに初期化され、プログラム・カウンターPCが0に初期化される。ステップ360では、最初のV<sub>pgm</sub>パルスが印加される。ステップ362では、選択されたメモリ・セルのしきいレベルが検査される。選択されたセルの目的とするしきい電圧が、関連するデータから特定される適切なレベルにまで到達したと判断された場合、そのセルへのさらなるプログラミングは禁止される。しきい電圧がまだ適切なレベルに到達していないと判断された場合、そのセルへのプログラミングは禁止されない。従って、全検査状態(ステップ364)が全てのセルが適切なしきいレベルに到達したと指摘した場合には、「合格」という状態がステップ366で報告される。全てのセルが適切なしきい電圧に到達したと検査されていない場合、ステップ368でプログラム・カウンターがプログラム制限値

10

20

30

40

50

と比較される。プログラム制限値の一例は 20 である。プログラム・カウンターが 20 以上であれば、プログラム処理は失敗に終わり、ステップ 370 で「不合格」という状態が報告される。プログラム・カウンターが 20 未満であれば、ステップ 372 で、プログラム電圧レベルがステップ・サイズ分だけ増大され、プログラム・カウンターが増加される。ステップ 372 の後、処理はステップ 360 に戻り、次のプログラミング電圧パルスを印加する。

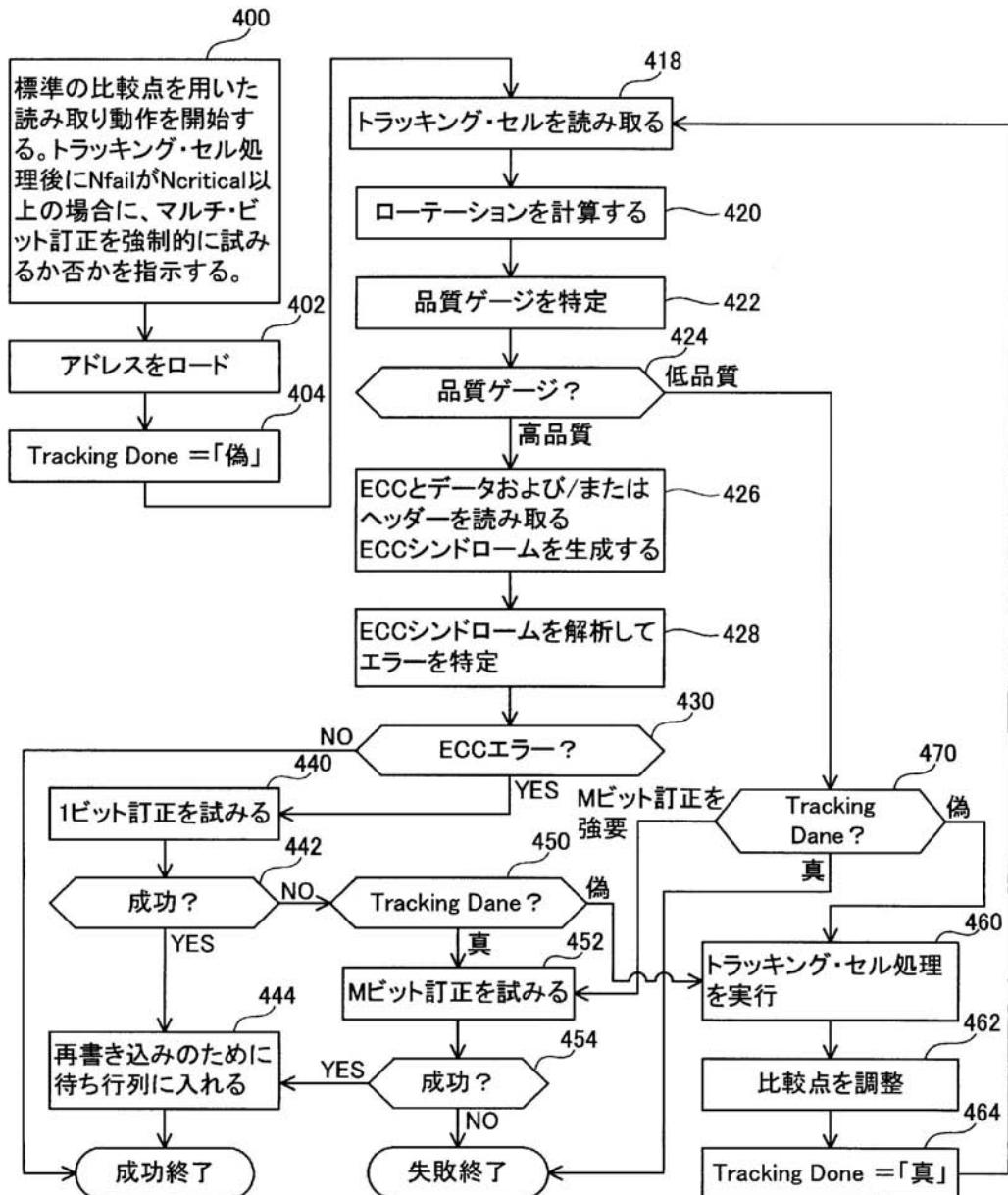

#### 【 0055 】

一度プログラミングがなされると、アレイ 11 のメモリ・セルは図 12 の処理によって読み取ることができる。ステップ 400 では、標準の比較点を用いた読み取り動作が開始する。比較点とは、2 つの電圧しきい状態の中間に設定され、そのレベルを超える状態とそのレベルに満たない状態とを区別するために用いられる、電圧しきいレベルのことである。例えば図 6 では、700 mV、1300 mV、1900 mV、2500 mV、3100 mV、3700 mV、および 4300 mV における灰色の太線として、複数の比較点を示している。加えて、下記に詳しく説明するように、トラッキング・セルの処理後におけるデータの品質が低い場合、マルチ・ビット訂正を強制的に試みるか否かを指示することもできる。これは、ホストまたは制御装置によって指示されてもよいし、メモリ・システムにプログラムされてもよい。

#### 【 0056 】

図 12 のステップ 402 では、ローカル・アドレスが特定される。すなわち、制御装置が、読み取られるデータの論理アドレス（あるいはアドレス群）を受信またはアクセスする。これらのアドレスは、特定のメモリ・アレイまたはメモリ・アレイ群における物理的なアドレスに変換される。ステップ 404 では、ブール変数の TrackingDone が「偽」に設定される。ステップ 418 では、トラッキング・セルが読み取られる。トラッキング・セルの読み取りについては、後に詳述する。ステップ 420 では、ローテーション・スキームが計算され、ステップ 422 では、関連する品質ゲージが特定（あるいは更新）される。ローテーション・スキームの計算、および品質ゲージの特定 / 更新については、後に詳述する。ステップ 424 では、品質ゲージ（後述する）に基いて、データが高品質であるか低品質であるかを判断する。品質ゲージが低品質のデータであると指摘した場合、処理はステップ 470（後述する）に進む。品質ゲージが高品質のデータであると指摘した場合、ステップ 426 で、計算されたローテーションを用いて物理的に読み取られるデータから論理データを確立して、ユーザー・データとエラー訂正符号が読み取られる。

すなわち、ステップ 420 で特定されたローテーション・スキームに基いて、ユーザー・データが復号化される。従来から知られている標準的な方法によれば、制御装置はデータの読み取り処理のために ECC シンドロームを生成する。ステップ 428 では、これらの ECC シンドロームが解析されて、データに何らかのエラーがあるか否かを判断する。ECC が何らかのエラーを発見しなかった場合（ステップ 430）、読み取り処理は成功して終了する。ホストから要求があった場合には、読み取られたデータが制御装置からホストに報告される。ECC 処理がエラーを発見した場合（ステップ 430）、ステップ 440 で制御装置は 1 ビット訂正処理を実行する。すなわち、当業者に知られている方法を用いて、誤っているデータの 1 ビットを訂正するために ECC が使用される。1 ビット訂正処理が成功した場合（ステップ 442）、訂正されたデータは付加的に（オプション・ビットで設定することにより）再書き込みのために待ち行列に入れられる。この時点で読み取り処理は成功と見なされ、（必要であれば）ホストにデータが報告され、訂正されたデータは付加的にメモリ・アレイに再度書き込まれる。データの読み取りに ECC を用いることは、この技術分野では従来から知られていることに留意すべきである。本発明は、この分野で知られている多くの ECC スキームとともに実施することができる。

#### 【 0057 】

（例えば複数のエラーが存在しているため）1 ビット訂正処理が成功しなかった場合は、ステップ 450 においてブール変数 TrackingDone をテストすることにより、トラッキング・セル処理が行われたか否かが判断される。変数 TrackingDone が「真」に設定されてい

10

20

30

40

50

れば（トラッキング・セル処理が完了したことを意味し）、処理はステップ452で複数ビット訂正処理を試みる。本発明は、この分野で知られている複数ビット訂正処理とともに実施することができる。複数ビット訂正処理が成功した場合（ステップ454）、訂正されたデータは再書き込みのために待ち行列に入れられ、読み取り処理は成功と見なされ、読み取られた（および訂正された）データは、（必要であれば）ホストに返信される。複数ビット訂正処理が成功しなかった場合（ステップ454）、読み取り処理は失敗と見なされ、状況に応じて処置が施される（例えば、ホストがそのデータを待っている場合、ホストはエラー・メッセージを受信する）。

#### 【0058】

ステップ450において、（ブール変数TrackingDoneが「偽」に設定されていたため）10

トラッキング・セル処理が行われなかつたと判断された場合は、制御装置がステップ460でトラッキング・セル処理を実行する。トラッキング・セル処理は、トラッキング・セルを処理して、新たな比較点のセットを特定することを含む。ステップ460の詳細は図15に関連して後述する。ステップ462では、現在の比較点がステップ460の結果に基いて調整され、ステップ464でブール変数TrackingDoneが「真」に設定される。ステップ464の後、処理はステップ418に戻り、システムは、新たな比較点を用いてトラッキング・セルとデータ・セルをもう一度読み取ろうとする。新たな比較点は、一時的あるいは恒久的に使用できるということに留意すべきである。さらに、新たな比較点は、その時点での考慮されているセクタのみで、あるいは、その時点で考慮されているセクタと同じように他のセクタでも使用できる。例えば、一実施形態では、セクタのセットが1つのグループ（例えば1つのファイル）として扱われ、その中の1つのセクタの比較点が調整された場合に、そのグループの全てのセクタの比較点も調整される。

20

#### 【0059】

ステップ424で、品質ゲージが低品質のデータであると指摘した場合、処理はステップ470に進む。ステップ470では、ブール変数TrackingDoneをテストすることにより、トラッキング・セル処理が行われたか否かが判断される。TrackingDoneが「真」に設定されている場合、読み取り処理は失敗する。TrackingDoneが「偽」に設定されている場合、ステップ460でトラッキング・セル処理が実行される。さらに、ステップ470では、変数をセットして、ステップ452の複数ビット訂正処理を強制的に行わせることができる。

30

#### 【0060】

図12のステップ418は、トラッキング・セルを読み取ることを含む。そのようにするためには、図6に関して説明したように、適切なステアリング・ゲートの電圧レベルが7つの比較点を段階的に経て、7つの読み取り動作が実行されるようにする。それぞれの読み取り動作において、トラッキング・セルをそれぞれの比較点でテストするために、ステアリング・ゲートの電圧は段階的に異なるレベルとされる。それぞれの比較点では、特定のトラッキング・セルがオンに切換えられたか、オフのまま保たれているのかが判断される。すなわち、電流が流れたか否かを判断する。7つの読み取り動作の最後に、読み取り動作からのデータは、制御装置にシフトされる。そして、制御装置はそのデータを図13の表に従って変換する。図13の表は、7つの読み取り動作のそれぞれから得られたデータに基いて、特定のメモリ・セルがどの状態にあるのかを示している。例えば、7つの読み取り動作の全てにおいてメモリ・セルがオンであった場合、そのメモリ・セルは物理状態P0にある。メモリ・セルが最初の読み取り動作の間はオフであり、残りの6つの読み取り動作の間はオンである場合、そのメモリ・セルは状態P1にある。メモリ・セルが最初の2つの読み取り動作の間はオフであり、残りの読み取り動作の間はオンである場合、そのメモリ・セルは状態P2にある。案の定、何のエラーもない場合には、各トラッキング・セルは、もともと書き込まれている状態である、状態P1あるいはP6の何れかである。他の実施形態では、他の状態を使用することができる。上述の読み取り処理は、電圧検知を利用していることに留意すべきである。しかしながら、電流検知あるいは他の読み取り（あるいは検知）方法もまた、本発明の範囲内にあることが理解される。

40

50

### 【0061】

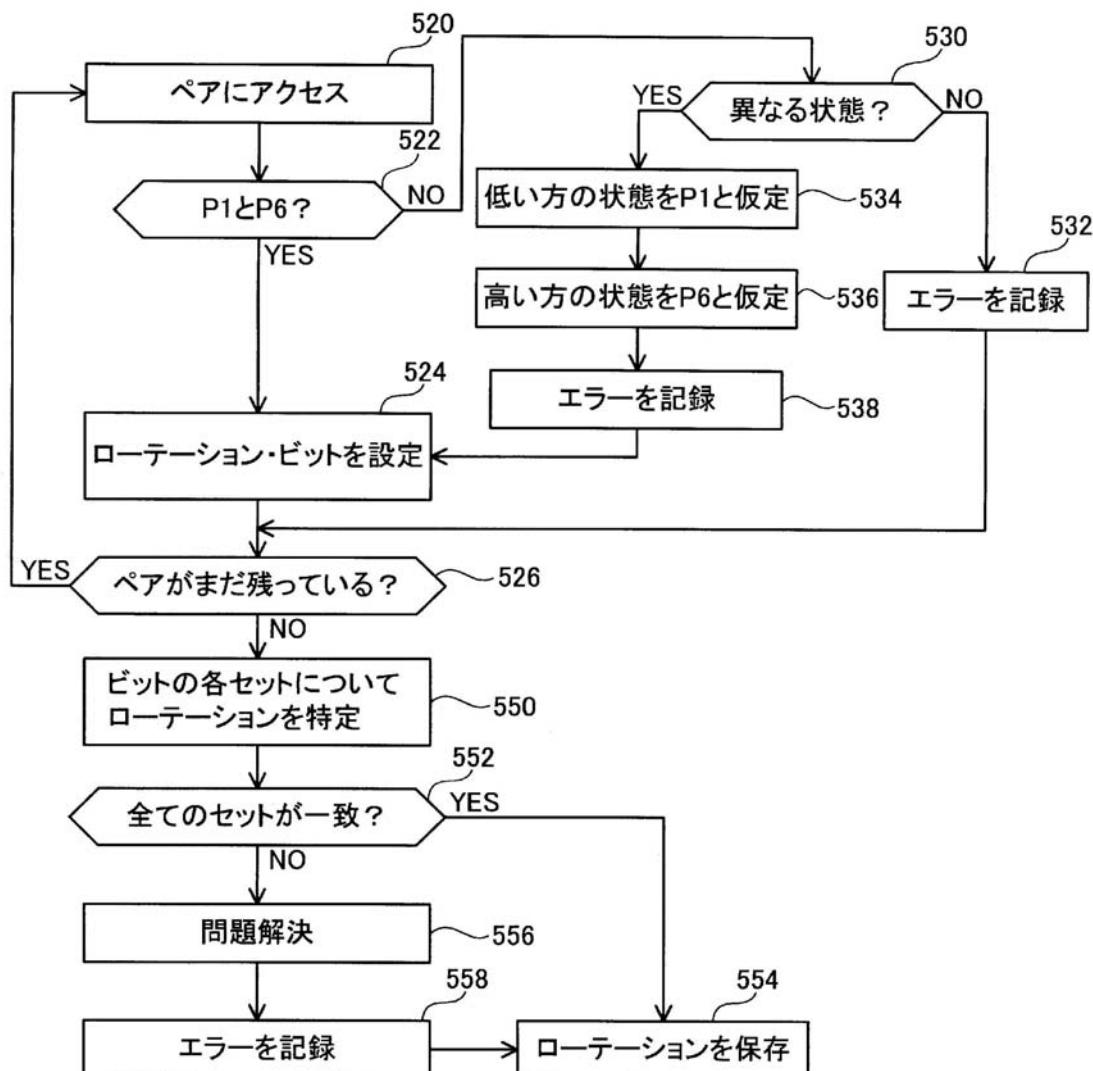

図14は(図12のステップ420の)ローテーション・スキームを計算する処理の一実施形態を説明するフローチャートである。ステップ520では、制御装置がトラッキング・セルのペア(一実施形態では、フローティング・ゲートのペア。例えば、図3~4を参照)からのデータにアクセスする。ステップ522では、トラッキング・セルのペアの一方が状態P1で、他方が状態P6であるか否かが判断される。もしそうであれば、図10に関連して記載したように、ステップ524でこれら2つのトラッキング・セルに対するビットが適切に設定される。すなわち、第1トラッキング・セルが状態P1で、第2トラッキング・セルが状態P6の場合、対応するローテーション・ビットは0に設定される。その代わりに、第1トラッキング・セルが状態P6で、第2トラッキング・セルが状態P1の場合、ローテーション・ビットは論理1に設定される。ステップ526では、処理すべきセルのペアがほかに存在するか否かが判断される。処理すべきペアがまだ残っている場合、この方法はステップ520に戻って処理を繰り返す。一実施形態では、セル群の状態がP1とP6であると判断を行う際に(ステップ522を参照)、システムは状態P1または状態P6以外の状態を扱ってもよいことに留意すべきである。例えば、状態P0、P1、P2、およびP3(あるいはこれらの状態群のサブセット)が状態P1として扱われ、状態P4、P5、P6、およびP7(あるいはこれらの状態群のサブセット)が状態P6として扱われてよい。

### 【0062】

ステップ522で、セルのペアの一方が状態P1、他方が状態P6とはなっていないと判断された場合、ステップ530でその2つのセルが互いに異なる状態にあるか否かが判断される。2つのセルが同一の状態にある場合、エラーが存在しており、ステップ532でそのエラーが記録される。ステップ532は、この特定の比較について詳細なデータを保持することの後に、順次的なエラー対策にデータを加えることができる。ステップ532で保持されるデータは、品質ゲージに使用される。2つのセルが互いに異なる状態にある場合、ステップ534で、制御装置は低い方のしきい電圧を持つセルに状態P1を割り当て(ステップ534)、高い方のしきい電圧を持つセルに状態P6を割り当てる(ステップ536)。ステップ538では、そのエラーが記録され、動作はステップ524に戻る。ステップ538は、状態P1または状態P6ではなかったセルの数、および/またはこれらの特定のセルが状態P1および/またはP6からはずれている差分を記録することを含むことができる。

### 【0063】

全てのペアが処理されたら(ステップ526)、その時点でシステムは12のペアを処理しており、従って、システムは12ビットのデータを備えている。その12ビットのデータは、図9に示すように4つのデータ・セットにグループ分けされる。ステップ550では、各セットの3ビットを図10の表と比較することにより、各セットのローテーションが特定される。ローテーションは、各セットにおいて別々に特定される。そして、セット同士が比較される。4つ全てのセットが同じ巡回符号を備えている場合(ステップ552)、ステップ554でその巡回符号が保持される。4つのセットが一致しない場合、ステップ556でその問題が解決され、そのエラー情報がステップ558で保持された後に、解決された巡回符号がステップ554で保持される。

### 【0064】

この不一致を解決する方法は多数ある。一つの方法は、投票を行って多数決をとることである。例えば、4つのセットのうち3つが1つの特定の値の符号と判断され、第4のセットのみが異なる特定の値の符号と判断される場合、その3つのセットによって選択された符号を採用して、不一致が解決される。あるいは、各ビットごとに一致しているか否かを比較し、ビットごとに投票を行う方法もある。例えば、最初の2ビットについては4つの全てのセットにおいて同一であり、第3のビットがそれらのセットのうちの1つで異なる場合には、その第3のビットは共通の値を持つ3つのセットによって判断された値とする。あるいは、これをセルごとに行って、5つのセルが全てのセットにおいて同一であり

、第6のセルがそれらのセットのうちの1つで異なる場合には、その異なるセルについては無視するという方法もある。

#### 【0065】

ローテーションを特定する他の1つの実施形態では、物理状態P1とP6の中間の比較点を用いて各トラッキング・セルを1度だけ読み取る。オンに切替わる全てのセルは状態P1にあり、オフのまま維持される全てのセルの状態はP6であると仮定する。ローテーション・ペアの両方のセルが同じ状態と演算された場合、システムは、一方のセルがオンであり他方のセルがオフである比較点を見つけるまで、詳細な分解能で、間にあるいくつもの比較点についての演算を順次行っていく。

#### 【0066】

図14は、エラーが記録されるボックス532、538、および558を示す。このエラーは、品質ゲージを形成するのに用いられる。ステップ532、538、および558で記録されるデータに基づき、品質ゲージは図12のステップ422で特定される。一実施形態では、品質ゲージはエラーの数や、しきいを超えたエラー量などを測定する。例えば、一実施形態では、品質ゲージは、状態がP1またはP6ではないトラッキング・セルの数の指標を保持してもよいし、あるいは品質ゲージは、状態がP1またはP6から異なるそれらのセルの平均値もしくは累積値を保持してもよい。あるいは、品質ゲージは複数の値を保持してもよく、例えば状態がP1またはP6ではないトラッキング・セルに対して、P1およびP6からどれだけ離れているかを各セルについて保持してもよい。エラーに関する他のデータや測定値が品質ゲージに反映されてもよい。他の1つの実施形態では、品質ゲージはエラーの数や大きさに基いて予め設定された幾つかの状態のうちの一つに設定される。測定されたデータに依存して、システムは品質ゲージを用いて、例えばしきい値に満たないとか、しきい値を超えるとか、あるいは規定や特性を満たすなど、品質ゲージが所定の基準に適合する場合に、その動作を変更することができる。

#### 【0067】

幅広いシフトやデータの状態／範囲が存在していてもローテーションを特定することは可能であるが、トラッキング・セルから読み取られる実際の状態は、目標とする状態P1およびP6から大幅に外れていることがある。幾つのセルが目標から異なっているか特定することによって、品質ゲージの一実施形態が構築される。この品質ゲージが所定のしきいレベル（もしくはしきいレベルの連続的なセット）を超えた場合、その品質ゲージに応じて警告状態（あるいは警告状態の連続的なセット）が生じるかもしれない。一実施形態では、メモリ・デバイスは、警告状態あるいはエラー・ゲージに対して反応しない（例えば、全く同じ動作で読み取り処理を続ける）。他の実施形態では、メモリ・デバイスは警告状態に反応する。例えば、処理は即座にトラッキング・セル処理（図12のステップ424）に移行して、比較点を調整して読み取り処理を再開することができる。あるいは、読み取り処理の全体を強制終了する（例えば、ステップ470を経由して終了／失敗プロックに進む）ことができる。他の実施形態では、ECCパラメータを変えることができる。例えばシステムは、品質ゲージがしきい値を超えている場合には、マルチ・ビット訂正是行わないことを選択する。警告状態を生起する基準の一例は、状態P1またはP6のいずれでもないトラッキング・セルの数が1を越えるか否かである。この場合、1つのランダムな（例えばランダム・ノイズによる）不具合ビットが見過ごされてしまう。しかしながら、2つのランダムで無相関なエラーが生起する可能性は極めて低いため、2つ以上の不具合についてはフラグされ、セクタの内部に存在するより広範な不具合状態を指示する。他の実施形態では、状態がP1またはP6のいずれでもないトラッキング・セルが2つ（あるいは他の数）であることを基準としてもよい。

#### 【0068】

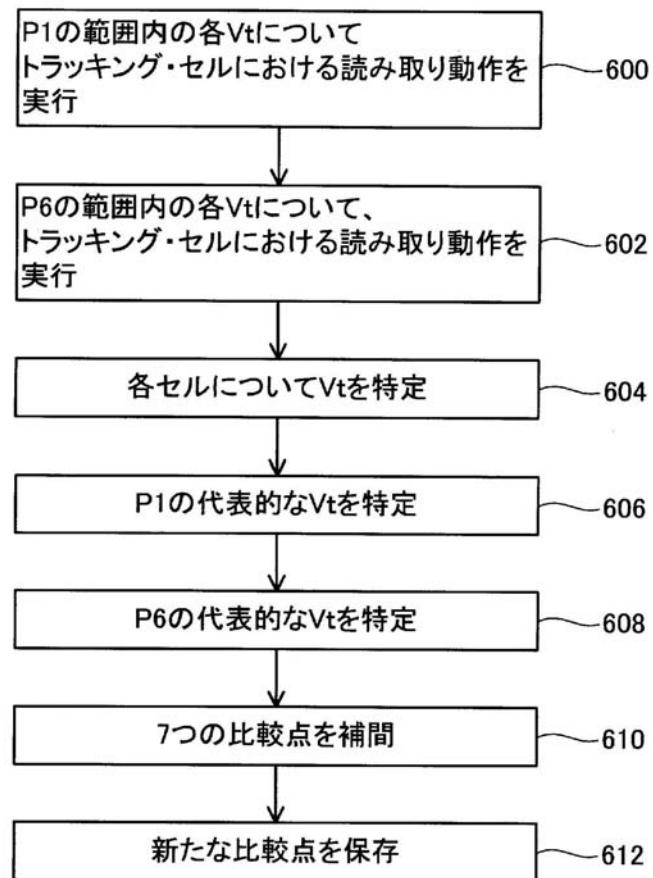

図15は、トラッキング・セル処理（図12のステップ460と462を参照）を実行する処理の一実施形態を表すフローチャートである。ステップ600では、物理状態P1に関連する所定の範囲内の各しきい電圧について、制御装置は各トラッキング・セルにおける読み取り動作を行わせる。例えば、図6は、状態P1に関連しているしきい電圧21

10

20

30

40

50

0を示す。この15の電圧は、状態P1の期待される範囲内のしきい電圧と、その範囲に満たないしきい電圧と、その範囲を超えるしきい電圧を含む。より多くのしきい電圧をテストしてより細かい分解能とすることもできるし、時間を節約するためにより少ないしきい電圧をテストしてより粗い分解能とすることもできる。他の実施形態では、図6に示す分解能で、範囲を増減することができる。一実施形態では、これらのしきい電圧のそれぞれについて、全てのトラッキング・セルが読み取り動作を備える。他の1つの実施形態では、これらのトラッキング・セルのうち状態P1であると思われるもののみが、状態P1に関連するしきい電圧についての読み取り動作を備える。例えば、状態P1であると思われる各トラッキング・セルにおいて、15の読み取り動作が実行される。他の1つの実施形態では、全てのトラッキング・セルがこれらのしきい電圧のそれについての読み取り動作を備えるが、状態P1ではないと思われるトラッキング・セルは読み取り動作の結果を破棄する。ステップ602では、物理状態P6に関連する範囲内のしきい電圧のそれぞれについて、制御装置はそれぞれのトラッキング・セルにおける読み取り動作を行わせる。例えば図6は、状態P6に関連している範囲内の15のしきい電圧212を示す。状態P1について上述した代替的な実施形態と同様のものが、状態P6にも適用される。例えば、16以上のしきい電圧を用いてより細かい分解能を実現することもできるし、14以下のしきい電圧を用いてより粗い分解能とすることもできる。一実施形態では、状態P1の場合と同様に、ステップ602で全てのトラッキング・セルに15の読み取り動作が実行される。他の実施形態では、これらのトラッキング・セルのうち状態P6であると思われるもののみが、ステップ602で読み取られる。

10

20

#### 【0069】

図15のステップ604では、ステップ600および602の読み取り動作に基いて、制御装置が各トラッキング・セルの実際のしきい電圧を特定する。制御装置は、セルがオンに切替わった最初のしきい電圧を探す。ステップ604の最後までには、制御装置は24のトラッキング・セルのそれに対応する、24のしきい電圧を特定する。ステップ606では、制御装置は状態P1の代表的なしきい電圧を特定する。ステップ608では、制御装置は状態P6の代表的なしきい電圧を特定する。2つの状態のそれぞれの代表的なしきい電圧は、周知の様々な数学的手段を用いて計算できる。例えば、各状態の分布を構築してその平均値を求めることができる。あるいは、直線回帰を使用することもできる。簡単にするために、単にそれぞれの分布の平均値を求めてよい。あるいは、外れ値を除いた単純な平均値を計算してもよい。外れ値は、フィルタリング処理によって、もしくは（例えば状態P1とP6に対する）2つの分布のそれぞれのしきい電圧の最大値と最小値を除去することによって、排除することができる。

30

#### 【0070】

ステップ610では、2つの代表的なしきい電圧に基いて、新たな7つの比較点が生成される。これらの比較点は、最適な比較点の最良推定値が得られるように、内挿法および外挿法を用いることで、確立することができる。比較点を特定する手段は多数ある。一実施例では、制御装置は状態P1とP6の代表的なしきい電圧の増加分を特定し、その二つの値を平均して平均増加分を求め、現在の比較点をその平均増加分だけ引き上げる。例えば、状態P1およびP6の代表的なしきい電圧が、平均増加分100mVで増加したと判断されると、最初に設定されている比較点のセット（700、1300、1900、2500、3100、3700、4300、4900）は、100mV引き上げられて、新たなレベル（800、1400、2000、2600、3200、3800、4400、5000に）に調整され、データはこの新たな比較点に対して読み取られる。他の1つの実施形態では、システムは8つの状態のそれぞれに対して代表的なしきい電圧を評価し、その8つの代表的なしきい電圧同士の関係を特定し、状態P1およびP6の新たな値をその関係に当てはめて、8つの状態のそれぞれの新たなしきい電圧を求めることができる。新たなしきい電圧を用いて、互いに隣接する状態間の中間地点に最も近い読み取り電圧レベルを設定することにより、状態間の新たな比較点を算出することができる。あるいは、比較点と状態P1およびP6の代表的なしきい電圧との関係を特定して、状態P1およびP

40

50

6の代表的なしきい電圧として新たな値を入れることで、比較点を変更してもよい。他のアルゴリズムを使用することもできる。

#### 【0071】

一実施形態では、新たな比較点はトラッキング・セル処理を引き起こしたセクタの読み取り不具合のみに対して使用されるのではなく、その後の読み取り（例えば、同じ読み取りセッションまたは将来の読み取りセッションにおける同じメモリの他の位置への読み取り。同じ修正が要求されるかも知れないし、要求されないかもしれない。）に対しても使用される。このような場合には、比較点は当初の基準値ではなく修正された値が好ましい。あるいは、一方が最初に設定された値を用いており、他方が最新の修正値を用いている、2つの条件のセットを、2つの参照レジスタのセットと関連する読み取りモードによって、同時に管理することができる。一方のモードを用いた読み取りが失敗した場合、データ復元を試みる第一歩として、他方のモード／参照条件を使用した再読み取りが実行される。最初に試みられるモードは、成功の見込みに基いて（例えば特性に基いて統計的に、あるいは成功の履歴に基いて動的に）最適に設定される。上述の処理は、トラッキング・セル処理の間の15のステップを説明していることに留意すべきである。他の実施形態では、15を超えた、または15に満たないステップを用いる。例えば、電圧分解能が25mVで、状態と状態の間の幅が500mVである場合には、処理は20のステップを用いる。一実施形態では、トラッキング・セル処理は、品質ゲージが低品質データを指摘した場合、あるいはECCが失敗した場合にのみ実行される。

#### 【0072】

一実施形態では、ユーザー・データ部がメモリ内で手を付けずにそのまま送信されなければならない場合に（例えば、内部でのデータ・コピー動作において）、システムはヘッダーやヘッダー・スタックを独立して読み取ることができることに留意されたい。このような場合、ユーザー・データの再書き込み（例えば、他の場所へのコピー）を実行する前に、上述したように、現在のデータ・ローテーションを抽出する必要がある。そして、新たなヘッダーとユーザー・データを、抽出したローテーションに従って書き込む。

#### 【0073】

上述した処理は、制御装置によって行われるか、制御装置の指示に従って行われる。一実施形態では、ほとんどあるいは全ての処理がファームウェアによってサポートできる。従って、コード（例えばファームウェア）はプロセッサ上の制御装置／制御装置で読み取り可能な例えばフラッシュ・メモリやRAMなどの制御装置をプログラミングするための記憶媒体の内部に埋め込まれてよい。そのコードは制御装置と通信する記憶素子に保持されていてもよい。あるいは、制御装置の内部に専用のハードウェアを含ませて、これらの機能を実現してもよい。制御装置という用語は、上述の機能を実現するメモリ・システムの内部の処理デバイスを表す、いくぶん包括的な表現であることに留意されたい。

#### 【0074】

一実施形態では、上述の方法は全てリアル・タイムに実行される。トラッキング・セルを使用することによる実際の性能への定量的な評価は、実際の実装形態によって異なる。ローテーションを計算する場合においては、関連する全ての動作がパイプライン型でプロセッサの最高速度で実行され、トラッキング・セルのデータは通常のデータ・ストリーム・フローの一部であるから、性能への影響はごくわずかである。一方、上述のトラッキング・セル処理を引き起こす実施例では、30の順次的な読み取りおよび多数のシフト・アウトが必要とされ、さらに制御装置がトラッキング・セル処理の演算を行うための時間も要求され、その後は新たな読み取り条件のロードと、最後の全体的な読み取りが続く。しきい電圧の読み取りが実行される範囲を狭めたり、しきい電圧の読み取り探索アルゴリズムを改善したりする（例えば、それぞれの分布のしきい電圧の中間点を探査するために、二分探索法を利用する）ことは可能かもしれない。それでも、その発生率はかなり低いため、全体的な性能への影響はごくわずかと予想され、完全な読み取り失敗や訂正ミスよりは明らかに好ましい。

#### 【0075】

10

20

30

40

50

上記の例は、特定のフラッシュ・メモリ・システムに関して提供されている。しかしながら、本発明の原理は他のフラッシュ・メモリ・システムや、他の種類の記憶装置（例えば、他の集積回路／ソリッド・ステート／半導体メモリなど）にも適用でき、現在使われているものだけでなく、今後の新しい技術を用いるものにも適用できる。本発明はさらに、光学システム、磁性システム、および機械的システムを含む非電気的メモリにも適用できる。

#### 【0076】

上述の本発明の詳細な説明は、図示と解説を目的として記載された。余すところなく記載する意図はなく、本発明を開示されたとおりのものに制限する意図もない。上記の説明に照らせば、多くの変形や変更が可能である。上述の実施例は、その説明に基づき当業者が多数の実施形態で使用したり、必要に応じて様々な変更を加えたりできるように、発明の原理と実際的な適用を最適に説明するために選択された。本発明の範囲は、添付の特許請求の範囲によって規定されることを意図する。10

#### 【図面の簡単な説明】

#### 【0077】

【図1】図1は本発明の一実施形態を利用するフラッシュ・メモリ・システムのブロック図である。

【図2】図2は図1のシステムのメモリ・セル・アレイの一部の一実施形態の平面図である。

【図3】図3は図2のメモリ・セル・アレイの断面A-Aにおける部分的断面図である。20

【図4】図4は図3の構造と電気的に等価な回路である。

【図5】図5はメモリ・セルを動作させる一つの手法に対する電圧の例を示す表である。

【図6】図6は本発明の一実施形態に対する状態空間を図示している。

【図7】図7は論理状態の割り当ての例を示している。

【図8】図8は異なるローテーション符号化スキームについての物理状態から論理状態への割り当ての例を示す。

【図9】図9は本発明の一実施形態に関するユーザー・データとオーバーヘッド・データを図示するデータ・マップである。

【図10】図10はトラッキング・セルのデータ・パターンからローテーション・スキームへの割り当ての例を示す。30

【図11】図11はデータの書き込みの方法の一実施形態を示すフローチャートである。

【図12】図12はデータの読み取りの方法の一実施形態を示すフローチャートである。

【図13】図13は読み取り動作の間のセルの状態を特定するために使用可能な表である。

【図14】図14はローテーション・スキームを特定するための方法の一実施形態を示すフローチャートである。

【図15】図15はトラッキング・セルを処理する方法の一実施形態を示すフローチャートである。

【図1】

【図2】

【図3】

【図4】

【図5】

| セル上で実行される機能                                       | 選択ゲート<br>(ワード線) | 左側ビット線<br>(BL-左) | 左側ステアリング<br>ゲート | 右側ステアリング<br>ゲート | 右側ビット線<br>(BL-右) |

|---------------------------------------------------|-----------------|------------------|-----------------|-----------------|------------------|

| (1) 選択されていない行                                     | 0               | X                | X               | X               | X                |

| (2) (ワード線への)消去                                    | $V_E$           | 5                | 0               | 0               | 5                |

| (3) 左側フロー・テイング・ゲートの読み取り                           | $V_{SR}$        | 0                | $V_M$           | $V_{BR}$        | 1                |

| (4) 右側フロー・テイング・ゲートの読み取り                           | $V_{SR}$        | 1                | $V_{BR}$        | $V_M$           | 0                |

| (5) 左側フロー・テイング・ゲートのプログラミング                        | $V_{SP}$        | 5                | $V_P$           | $V_{BP}$        | 0                |

| (6) 右側フロー・テイング・ゲートのプログラミング                        | $V_{SP}$        | 0                | $V_P$           | $V_P$           | 5                |

| (7) 選択された行においてプログラミングしない                          | $V_{SP}$        | 0                | X               | X               | 0                |

|                                                   |                 | 5                | X               | X               | 5                |

| (8) (チャネルへの)消去<br>[nウェルとnウェルの両方の電圧は $V_E$ 、基板は0V] | $V_{SE}$        | フロート             | 0               | 0               | フロート             |

【図6】

【図7】

| 論理状態 | バイナリ・データ |

|------|----------|

| L0   | 000      |

| L1   | 001      |

| L2   | 011      |

| L3   | 010      |

| L4   | 110      |

| L5   | 111      |

| L6   | 101      |

| L7   | 100      |

【図8】

|        | ローテーション0 | ローテーション1 | ローテーション2 | ローテーション3 | ローテーション4 | ローテーション5 | ローテーション6 | ローテーション7 |

|--------|----------|----------|----------|----------|----------|----------|----------|----------|

| 物理状態P0 | L0       | L7       | L6       | L5       | L4       | L3       | L2       | L1       |

| 物理状態P1 | L1       | L0       | L7       | L6       | L5       | L4       | L3       | L2       |

| 物理状態P2 | L2       | L1       | L0       | L7       | L6       | L5       | L4       | L3       |

| 物理状態P3 | L3       | L2       | L1       | L0       | L7       | L6       | L5       | L4       |

| 物理状態P4 | L4       | L3       | L2       | L1       | L0       | L7       | L6       | L5       |

| 物理状態P5 | L5       | L4       | L3       | L2       | L1       | L0       | L7       | L6       |

| 物理状態P6 | L6       | L5       | L4       | L3       | L2       | L1       | L0       | L7       |

| 物理状態P7 | L7       | L6       | L5       | L4       | L3       | L2       | L1       | L0       |

【図9】

【図10】

| データ・パターン ローテーション  |       | データ・パターン ローテーション  |       |

|-------------------|-------|-------------------|-------|

| <br>[1 6 1 6 1 6] | 000=0 | <br>[6 1 1 6 1 6] | 100=4 |

| <br>[1 6 1 6 6 1] | 001=1 | <br>[6 1 1 6 6 1] | 101=5 |

| <br>[1 6 6 1 1 6] | 010=2 | <br>[6 1 6 1 1 6] | 110=6 |

| <br>[1 6 6 1 6 1] | 011=3 | <br>[6 1 6 1 6 1] | 111=7 |

【図11】

【図12】

【図13】

| 状態 | 第1合格 | 第2合格 | 第3合格 | 第4合格 | 第5合格 | 第6合格 | 第7合格 |

|----|------|------|------|------|------|------|------|

| P0 | オン   |

| P1 | オフ   | オン   | オン   | オン   | オン   | オン   | オン   |

| P2 | オフ   | オフ   | オン   | オン   | オン   | オン   | オン   |

| P3 | オフ   | オフ   | オフ   | オン   | オン   | オン   | オン   |

| P4 | オフ   | オフ   | オフ   | オフ   | オン   | オン   | オン   |

| P5 | オフ   | オフ   | オフ   | オフ   | オフ   | オン   | オン   |

| P6 | オフ   | オフ   | オフ   | オフ   | オフ   | オフ   | オン   |

| P7 | オフ   |

【図14】

【図15】

---

フロントページの続き

- (72)発明者 グロス、スティーブン ジェイ .

アメリカ合衆国、95014、カリフォルニア州、クバチーノ、ヒルクレスト ロード 1016

0

- (72)発明者 ハーリド、シャザド

アメリカ合衆国、94587、カリフォルニア州、ユニオンシティ、ダービーストリート 323

92

- (72)発明者 ゴングワー、ジェフリー エス .

アメリカ合衆国、94024、カリフォルニア州、ロスアルトス、ビーチウッドレーン 5328

審査官 園田 康弘

- (56)参考文献 国際公開第02/027729 (WO , A1 )

特表2001-504973 (JP , A )

特開2004-005909 (JP , A )

国際公開第2003/041083 (WO , A1 )

- (58)調査した分野(Int.Cl. , DB名)

G11C 16/02

G11C 16/06