(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6808348号

(P6808348)

(45) 発行日 令和3年1月6日(2021.1.6)

(24) 登録日 令和2年12月11日(2020.12.11)

(51) Int.Cl.

H01L 27/146 (2006.01)

F 1

H01L 27/146

A

H04N 5/357 (2011.01)

H04N 5/357

H04N 5/374 (2011.01)

H04N 5/374

請求項の数 25 (全 19 頁)

(21) 出願番号

特願2016-91579 (P2016-91579)

(22) 出願日

平成28年4月28日(2016.4.28)

(65) 公開番号

特開2017-199875 (P2017-199875A)

(43) 公開日

平成29年11月2日(2017.11.2)

審査請求日

平成31年4月22日(2019.4.22)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 浮ヶ谷 信貴

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72) 発明者 桑原 英司

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 小山 滉

最終頁に続く

(54) 【発明の名称】光電変換装置およびカメラ

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の光電変換素子を含む画素領域を有する光電変換装置であって、

第1面および前記第1面とは反対側の第2面を有し、前記第1面と前記第2面との間に前記複数の光電変換素子が配された半導体層を備え、

前記第1面と前記第2面との間に前記第2面に沿った仮想的な平面を第3面として、前記画素領域は、前記第3面よりも前記第1面の側に配された素子分離部と、前記第3面を通るように配された第1分離部および第2分離部と、を含み、

前記素子分離部は前記半導体層に設けられた溝および前記溝の中に配された絶縁体によって構成されており、前記素子分離部の前記絶縁体は前記画素領域に設けられた半導体素子の電極と前記半導体層との間に位置し、

前記第1分離部および前記第2分離部は前記半導体層に設けられた溝によって構成されており、前記第1分離部は前記第3面に対する法線方向において前記素子分離部に重なり、

前記第2分離部の前記第1面の側の端は、前記第1分離部の前記第1面の側の端よりも前記第2面の側に位置していることを特徴とする光電変換装置。

## 【請求項 2】

前記半導体層は、前記素子分離部によって画定された素子領域として、第1光電変換素子が設けられた第1素子領域と、第2光電変換素子が設けられた第2素子領域と、を含み、前記第2分離部は、前記法線方向において前記第1素子領域と前記第2素子領域の間の

10

20

領域に重なる、請求項 1 に記載の光電変換装置。

【請求項 3】

前記半導体層は、前記素子分離部によって画定された素子領域として、前記第 1 素子領域と前記第 2 素子領域との間に配され、前記第 1 素子領域および前記第 2 素子領域とは異なる形状を有する第 3 素子領域を含み、

前記第 2 分離部は前記法線方向において前記第 3 素子領域に重なる、請求項 2 に記載の光電変換装置。

【請求項 4】

前記第 3 素子領域の上にはトランジスタのゲート電極が配されており、前記第 2 分離部は前記法線方向において前記ゲート電極に重なる、請求項 3 に記載の光電変換装置。 10

【請求項 5】

前記第 2 分離部は、第 1 部分と、第 2 部分とを有し、前記第 2 部分の前記第 1 面の側の端は、前記第 1 部分の前記第 1 面の側の端よりも前記第 2 面の側に位置し、前記第 2 部分は前記法線方向において前記ゲート電極に重なる、請求項 4 に記載の光電変換装置。

【請求項 6】

前記第 2 面に沿う方向のうち、前記第 1 素子領域と前記第 2 素子領域とが並ぶ方向を第 1 方向とし、前記第 1 方向に交差する方向を第 2 方向として、前記半導体層は、前記第 2 方向において前記第 1 素子領域に隣り合い、第 3 光電変換素子が設けられた第 4 素子領域を含み、

前記素子分離部は、前記第 1 素子領域と前記第 4 素子領域との間に位置する分離領域を有し、 20

前記第 1 分離部は、前記法線方向において前記分離領域に重なる、請求項 2 乃至 5 のいずれか 1 項に記載の光電変換装置。

【請求項 7】

前記第 3 面において、前記第 2 分離部の幅は前記第 1 分離部の幅よりも小さい、請求項 1 乃至 6 のいずれか 1 項に記載の光電変換装置。

【請求項 8】

前記第 1 分離部を構成する前記溝は、前記第 2 面に連続した側面を有する、請求項 1 乃至 7 のいずれか 1 項に記載の光電変換装置。 30

【請求項 9】

前記第 3 面と前記第 2 面との距離は前記第 3 面と前記第 1 面との距離よりも小さい、請求項 1 乃至 8 のいずれか 1 項に記載の光電変換装置。

【請求項 10】

前記半導体層の厚さを T として、前記第 2 面と前記第 3 面との距離は T / 4 である、請求項 1 乃至 9 のいずれか 1 項に記載の光電変換装置。

【請求項 11】

前記素子分離部と前記第 3 面との間に前記第 2 面に沿った仮想的な平面を第 4 面として、前記第 1 分離部を構成する前記溝は前記第 4 面を通り、前記第 2 分離部の前記第 1 面の側の前記端は前記第 4 面よりも前記第 2 面の側に位置しており、前記第 4 面と前記第 1 面との距離は前記第 4 面と前記第 2 面との距離よりも小さい、請求項 1 乃至 10 のいずれか 1 項に記載の光電変換装置。 40

【請求項 12】

複数の光電変換素子を含む画素領域を有する光電変換装置であって、

第 1 面および前記第 1 面とは反対側の第 2 面を有し、前記第 1 面と前記第 2 面との間に前記複数の光電変換素子が配された半導体層を備え、

前記画素領域は、前記第 1 面に連続した側面を有する溝および前記溝の中に配された絶縁体によって構成された素子分離部と、前記第 2 面に連続した側面を有する溝によって構成された第 1 分離部および第 2 分離部を含み、

前記素子分離部の前記絶縁体は前記画素領域に設けられた半導体素子の電極と前記半導体層との間に位置し、 50

前記第1分離部は前記第2面に対する法線方向において前記素子分離部に重なり、前記第2分離部の前記第1面の側の端は、前記第1分離部の前記第1面の側の端よりも前記第2面の側に位置していることを特徴とする光電変換装置。

**【請求項13】**

前記第2分離部の前記第2面に対する深さは、前記半導体層の厚さの1/4~3/4である、請求項1乃至12のいずれか1項に記載の光電変換装置。

**【請求項14】**

前記画素領域には浮遊拡散領域と、前記浮遊拡散領域に接続されたMOSトランジスタが配されており、前記第2分離部は前記法線方向において前記MOSトランジスタに重なる、請求項1乃至13のいずれか1項に記載の光電変換装置。 10

**【請求項15】**

前記第2分離部は、第1部分と、第2部分とを有し、前記第2部分の前記第1面の側の端は、前記第1部分の前記第1面の側の端よりも前記第2面の側に位置する、請求項1乃至14のいずれか1項に記載の光電変換装置。

**【請求項16】**

前記第1分離部は、前記素子分離部に接続している、請求項1乃至15のいずれか1項に記載の光電変換装置。

**【請求項17】**

前記素子分離部と前記第1分離部との間には前記半導体層の半導体領域が位置している、請求項1乃至15のいずれか1項に記載の光電変換装置。 20

**【請求項18】**

前記光電変換素子は信号電荷が多数キャリアである第1導電型の不純物領域を有し、前記画素領域には、前記半導体層の第2導電型の不純物領域に固定電位を供給するためのコンタクトが設けられている、請求項1乃至17のいずれか1項に記載の光電変換装置。

**【請求項19】**

前記第2分離部は前記法線方向において前記コンタクトに重なる、請求項18に記載の光電変換装置。

**【請求項20】**

前記複数の光電変換素子のうちの2つの光電変換素子が前記半導体素子を共有しており、各々が前記2つの光電変換素子のいずれかに対応する2つの転送ゲートは前記法線方向において前記第2分離部に重ならない、請求項1乃至19のいずれか1項に記載の光電変換装置。 30

**【請求項21】**

前記第1分離部を構成する前記溝の中には、絶縁体または導電体である固体が存在している、請求項1乃至20のいずれか1項に記載の光電変換装置。

**【請求項22】**

前記第1分離部を構成する前記溝の中には真空の空間あるいは気体が存在している、請求項1乃至21のいずれか1項に記載の光電変換装置。

**【請求項23】**

前記第1面の側には、複数の配線層と、前記複数の配線層の周囲の絶縁膜と、基板と、が設けられており、前記基板と前記半導体層との間に前記複数の配線層および前記絶縁膜が位置し、前記基板には集積回路が設けられている、請求項1乃至22のいずれか1項に記載の光電変換装置。 40

**【請求項24】**

請求項1乃至23のいずれか1項に記載の光電変換装置と、

前記光電変換装置から出力された信号を処理する信号処理装置、前記光電変換装置から出力された信号に基づく情報を記憶する記憶装置、前記光電変換装置から出力された信号に基づく情報を表示する表示装置、および、前記光電変換装置へ光を導く光学装置の少なくともいずれかと、

を備えるカメラ。 50

**【請求項 25】**

請求項 1 乃至 23 のいずれか 1 項に記載の光電変換装置と、

前記光電変換装置へ光を導く光学装置と、

前記光電変換装置から出力された信号を処理する信号処理装置と、

を備える移動体。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、光電変換装置に関する。

**【背景技術】****【0002】**

カメラに用いられる CMOS イメージセンサーなどの光電変換装置において半導体層に溝を設けることが検討されている。溝によって構成された分離部が光や電荷に対する隔壁として作用することで、感度が向上したり、混色が抑制されたりして、光電変換装置の性能を向上することができる。

**【0003】**

特許文献 1 には、光電変換素子 (102) が設けられた基板 (101) の裏面 (101b) 側から、基板 (101) の表面 (101a) 側の STI (111) に達するトレンチ (105) を設けることが記載されている。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献 1】米国特許出願公開第 2013 / 0069190 号明細書

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

特許文献 1 にはトレンチの平面的なレイアウトが記載されていないが、トレンチのレイアウトによっては、光電変換装置の性能の向上が十分でなかったり、却って光電変換装置の性能が低下してしまったりする場合がある。これは、例えば、トレンチを配置する場所による、感度向上の制限やノイズの増加などが理由として挙げられる。

**【0006】**

そこで本発明は、光電変換装置の性能を向上することを目的とする。

**【課題を解決するための手段】****【0007】**

本発明の観点は、複数の光電変換素子を含む画素領域を有する光電変換装置であって、第 1 面および前記第 1 面とは反対側の第 2 面を有し、前記第 1 面と前記第 2 面との間に前記複数の光電変換素子が配された半導体層を備え、前記第 1 面と前記第 2 面との間に前記第 2 面に沿った仮想的な平面を第 3 面として、前記画素領域は、前記第 3 面よりも前記第 1 面の側に配された絶縁体によって構成された素子分離部と、前記第 3 面を通るように前記半導体層に設けられた溝によって構成された第 1 分離部および第 2 分離部を含み、前記第 1 分離部は前記第 3 面に対する法線方向において前記素子分離部に重なり、前記第 2 分離部の前記第 1 面の側の端は、前記第 1 分離部の前記第 1 面の側の端よりも前記第 2 面の側に位置していることを特徴とする。

**【発明の効果】****【0008】**

本発明によれば、性能を向上した光電変換装置を提供することができる。

**【図面の簡単な説明】****【0009】**

【図 1】光電変換装置を説明するための模式図。

【図 2】光電変換装置を説明するための模式図。

10

20

30

40

50

【図3】光電変換装置を説明するための模式図。

【図4】光電変換装置を説明するための模式図。

【図5】光電変換装置の製造方法を説明するための模式図。

【発明を実施するための形態】

【0010】

以下、図面を参照して、本発明を実施するための形態を説明する。なお、以下の説明および図面において、複数の図面に渡って共通の構成については共通の符号を付している。そのため、複数の図面を相互に参照して共通する構成を説明し、共通の符号を付した構成については適宜説明を省略する。

【0011】

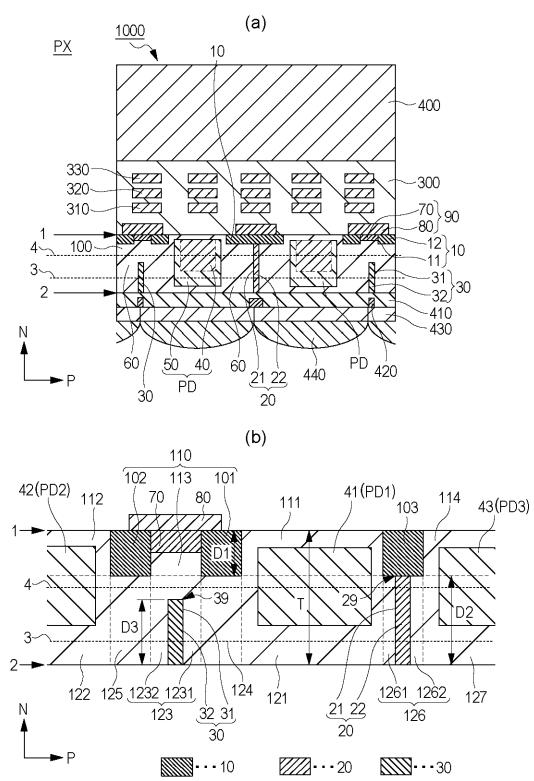

図1(a)は光電変換装置の一例として、裏面照射型の撮像装置の実施形態を示す断面図である。図1(b)は光電変換装置の半導体層およびその近傍の構造の拡大図である。

【0012】

光電変換装置1000は複数の光電変換素子PDを含む画素領域PXを有する。画素領域PXは後述するように、種々の素子を電気的あるいは光学的に分離する分離部をさらに含む。また、画素領域PXは、カラーフィルタアレイやマイクロレンズアレイを含みうる。光電変換装置1000は、画素領域以外に周辺領域(不図示)を含む。周辺領域には、画素領域PXの回路(画素回路)を駆動するための駆動回路や、画素回路からの信号を処理する信号処理回路が設けられる。以下、光電変換装置1000の画素領域PXの構成を詳細に説明する。

【0013】

光電変換装置1000は表面1と、表面1とは反対側の裏面2とを有する半導体層100を備える。画素領域PXの光電変換素子PDは半導体層100に配されている。光電変換素子PDは表面1と裏面2との間に配されている。半導体層100は例えば単結晶シリコン層であるが、光電変換が可能な半導体層であれば単結晶シリコン層に限らない。半導体層100は1~10μm程度の厚さTを有する(図1(b)参照)。半導体層100の厚さTは表面1と裏面2との距離に一致する。

【0014】

光電変換装置1000は、表面1の側に配され、半導体層100の溝11と溝11の中の絶縁体12によって構成された素子分離部10を備える。素子分離部10はSTI構造あるいはLOCOS構造を有し得る。素子分離部10の溝11は表面1に対して100~1000nm程度の深さD1を有する(図1(b)参照)。素子分離部10を構成する絶縁体12は例えば酸化シリコンからなる。

【0015】

また、光電変換装置1000は、半導体層100に設けられた溝21によって構成された画素分離部20を備える。画素分離部20は、平面3を通って配されている。平面3は、表面1と裏面2との間において、素子分離部10よりも裏面2の側に位置し、表面1および/または裏面2に沿った仮想的な平面である。平面3は、表面1と裏面2から等距離に位置する仮想的な平面である中間面と、裏面2との間、例えば裏面2からT/4の位置に設定することができる。平面3は裏面2に平行でありうる。平面3に垂直な方向を法線方向Nと称し、平面3に平行な方向を面内方向Pと称する。法線方向Nにおいては、画素分離部20は平面3に対して表面1側と裏面2側に両方に渡って延在している。本例の溝21は裏面2から表面1に向かって半導体層100に設けられている。そのため、溝21は裏面2に連続した側面を有する。ただし、溝21は表面1の側から裏面2に向かって半導体層100に設けられてもよく、溝21は裏面2に達しなくてもよい。画素分離部20の溝21は表面1に対して1~10μm程度の深さD2を有する(図1(b)参照)。平面3の面内においては、画素分離部20を挟んで半導体層100が不連続になっている。画素分離部20の溝21の中には、固体22が存在していてもよいし、真空の空間あるいは気体が存在していてもよいし、気体と固体22の両方が配置されていてもよい。溝21の中に存在する固体22としては、絶縁体、導電体、半導体のいずれでもよい。溝21の

10

20

30

40

50

中に存在する固体 2 2 としての絶縁体は酸化シリコンが典型的であるが、窒化シリコン、酸窒化シリコン、酸化タンタル、酸化ハフニウム、酸化チタンなどを用いることもできる。溝 2 1 の中に存在する固体 2 2 としての導電体は金属やポリシリコンが典型的であるが、アルミニウム、銅、タンゲステン、チタン、窒化チタン、タンタル、窒化タンタル、金属シリサイド等を用いることもできる。溝 2 1 の中に存在する固体 2 2 としての半導体は単結晶シリコンが典型的であるが、アモルファスシリコンであってもよい。溝 2 1 の中に存在する固体 2 2 としての半導体の導電型は、後述する光電変換素子で蓄積される信号電荷とは反対の導電型であることが好ましい。

#### 【 0 0 1 6 】

さらに、光電変換装置 1 0 0 0 は、半導体層 1 0 0 に設けられた溝 3 1 によって構成された画素分離部 3 0 を備える。画素分離部 3 0 も、平面 3 を通って配されている。溝 3 1 は裏面 2 から表面 1 に向かって半導体層 1 0 0 に設けられている。そのため、溝 3 1 は裏面 2 に連続した側面を有する。画素分離部 3 0 の溝 3 1 は表面 1 に対して  $1 \sim 10 \mu\text{m}$  程度の深さ D 3 を有する（図 1 ( b ) 参照）。平面 3 の面内においては、画素分離部 3 0 を挟んで半導体層 1 0 0 が不連続になっている。画素分離部 3 0 の溝 3 1 の中には、固体 3 2 が存在していてもよいし、真空の空間あるいは気体が存在していてもよいし、気体と固体 3 2 の両方が配置されていてもよい。溝 3 1 の中に存在する固体 3 2 としては、画素分離部 2 0 の溝 3 1 の中に存在する固体 3 2 と同様であるので説明を省略する。

#### 【 0 0 1 7 】

画素分離部 2 0 と画素分離部 3 0 は、面内方向 P における位置が異なる。画素分離部 2 0 は、法線方向 N において素子分離部 1 0 に重なる。つまり、図 1 ( a ) に示すように、画素分離部 2 0 は素子分離部 1 0 の下に配されている。画素分離部 3 0 は平面 3 において画素分離部 2 0 とは異なる位置に配されている。画素分離部 2 0 と画素分離部 3 0 の面内方向 P における位置については、後で詳細に説明する。

#### 【 0 0 1 8 】

画素分離部 2 0 と画素分離部 3 0 は、法線方向 N における深さが異なる。画素分離部 3 0 は画素分離部 2 0 よりも裏面 2 に対して浅く配されている。図 1 ( b ) を用いて画素分離部 2 0 と画素分離部 3 0 について説明する。画素分離部 2 0 の裏面 2 からの深さ D 2 は画素分離部 3 0 の裏面 2 からの深さ D 3 よりも大きい ( $D_2 > D_3$ )。換言すると、画素分離部 3 0 の表面 1 の側の端 3 9 は、画素分離部 2 0 の表面 1 の側の端 2 9 よりも裏面 2 の側に位置する。図 1 ( a ) には、平面 4 を記載している。平面 4 は、表面 1 と裏面 2 との間において、素子分離部 1 0 よりも裏面 2 の側に位置し、かつ、平面 3 よりも表面 1 の側に位置する、表面 1 および / または裏面 2 に沿った仮想的な平面である。平面 4 は、表面 1 と裏面 2 から等距離に位置する仮想的な平面である中間面と、表面 1 との間、例えば表面 1 から  $T / 4$  の位置に設定することができる。画素分離部 2 0 は、平面 4 を通って配されているのに対して、画素分離部 3 0 は、平面 4 を通っていない。画素分離部 2 0 の表面 1 の側の端 2 9 は、素子分離部 1 0 と平面 4 との間に位置するのに対し、画素分離部 3 0 の表面 1 の側の端 3 9 は、平面 3 と平面 4 との間に位置する。

#### 【 0 0 1 9 】

本例では、画素分離部 2 0 は素子分離部 1 0 に接続している。そのため、素子分離部 1 0 の表面 1 に対する深さ D 1 と画素分離部 2 0 裏面 2 に対する深さ D 2 との和は、半導体層 1 0 0 の厚さ T と同じかそれよりも大きい ( $D_1 + D_2 = T$ )。画素分離部 3 0 の裏面 2 に対する深さ D 3 は、半導体層 1 0 0 の厚さ T よりも小さい ( $D_3 < T$ )。画素分離部 3 0 の深さは半導体層 1 0 0 の厚さ T の半分程度、例えば  $1 / 4 \sim 3 / 4$  とするのが良い ( $T \times 1 / 4 \leq D_3 \leq T \times 3 / 4$ )。

#### 【 0 0 2 0 】

半導体層 1 0 0 の表面 1 と裏面 2 との間には光電変換素子 P D が設けられている。本例の光電変換素子 P D はフォトダイオードであるがフォトゲート等であってもよい。フォトダイオードとしての光電変換素子 P D は信号電荷（電子）を蓄積するための蓄積領域として機能する n 型の不純物領域 4 0 と、不純物領域 4 0 と p n 接合を成す p 型の不純物領域

10

20

30

40

50

50とを含む。p型の不純物領域50で光電変換により発生した電子は不純物領域40に蓄積される。平面3内には不純物領域40が位置していることが好ましい。平面3と裏面2との間には不純物領域50が位置している。ここでは電子蓄積型のフォトダイオードを例示したが、正孔蓄積型のフォトダイオードを採用することもできる。その場合には、不純物領域の導電型を電子蓄積型の場合の逆にすればよい。信号電荷が多数キャリアである導電型を第1導電型、信号電荷が少数キャリアである導電型を第2導電型とする。信号電荷が電子であれば、電子が多数キャリアであるn型が第1導電型である。なお、半導体層100内において光電変換素子PDとしてみなされる部分は、信号電荷として読み出される電荷を光電変換によって生じる部分である。厳密には、光電変換素子PDとしてみなされる部分は、半導体層100内の不純物濃度分布と印加される電圧に基づくポテンシャルプロファイルによって定まる。

10

#### 【0021】

半導体層100の表面1側には画素トランジスタ90が設けられている。図1では画素トランジスタ90のチャネル領域70とゲート電極80を記載している。画素トランジスタ90には、転送トランジスタや増幅トランジスタ、リセットトランジスタや選択トランジスタが含まれる。転送トランジスタは光電変換素子PDの信号電荷を電荷検出領域に転送する。電荷検出領域は浮遊拡散領域(フローティングディフュージョン)で構成される。増幅トランジスタは電荷に基づく信号をソースフォロワ回路によって生成するもので、電荷検出領域に接続されたゲートを有する。リセットトランジスタは電荷検出領域に接続されたドレインを有し、光電変換素子PDの電荷をリセットする。選択トランジスタは増幅トランジスタと出力線との接続/非接続を選択する。

20

#### 【0022】

半導体層100のうち、光電変換素子PDの外側はp型の不純物領域60で構成される。このp型の不純物領域60は、同じくp型の不純物領域50に比べて不純物濃度が高くなっている。不純物領域60の一部は、画素間の電荷の混合を抑制するポテンシャル障壁として機能し得る。また、不純物領域60の一部は、半導体層100と絶縁体との界面で生じたノイズ電荷が光電変換素子PDに取り込まれることを抑制するポテンシャル障壁として機能し得る。また、不純物領域60は接地電位などの固定電位を供給する導電部材が接続された、濃いp型のウェルコンタクトを含む。ウェルコンタクトから、不純物領域60を介して、光電変換素子PDの不純物領域50に電位が供給される。

30

#### 【0023】

画素分離部20、30は光電変換素子PDの周囲に配置される。画素分離部20、30は隣接する画素間での混色を抑制することが可能な構成を有する。

#### 【0024】

表面1側には複数の配線層310、320、330とそれらの周囲の複数の層間絶縁層からなる絶縁膜300が設けられている。なお、配線層で構成された出力線は光電変換素子PDで生成された信号電荷を画素トランジスタ90を介して電気信号として後段に出力するように設けられている。

#### 【0025】

図1(a)に示した裏面照射型の撮像装置では、裏面2側に誘電体膜410、遮光部材420、カラーフィルタアレイ430、マイクロレンズアレイ440が設けられている。誘電体膜410は保護膜(パッシベーション膜)、平坦化膜および/または反射防止膜として機能する。表面1側であって絶縁膜300の上には支持基板400が設けられている。支持基板400には信号処理回路等の集積回路を設けることができる。半導体層100の厚さは1~10μm程度である。支持基板の厚さは50~800μm程度である。

40

#### 【0026】

カラーフィルタアレイ430は特定の波長の光のみを選択的に透過させるように設けられる。たとえば赤、緑、青の波長を透過するカラーフィルターを配列させても良い。また、白色光を透過させる画素を混在させても良い。なお各画素に対応して配置されたマイクロレンズアレイ440の各マイクロレンズは、入射光を光電変換素子PDに集光させるよ

50

うに設けられている。

**【0027】**

図1(b)に示すように、半導体層100は、素子分離部10によって画定された素子領域を有する。素子領域は素子分離部10に対する位置によって区分される。素子領域の深さ方向の下端は深さD1の素子分離部10の底面に一致する。図2には半導体層100に含まれる素子領域として素子領域111、112、113、114を示している。素子領域111には光電変換素子PD1の蓄積領域としてのn型の不純物領域41が設けられており、素子領域112には光電変換素子PD2の蓄積領域としてのn型の不純物領域42が設けられている。素子領域113は、素子領域111と素子領域112との間に配されており、素子領域113にはトランジスタや容量素子、抵抗素子などの半導体素子が設けられている。素子領域113の形状は素子領域111や素子領域112の形状とは異なっている。素子領域113には光電変換素子PD以外のトランジスタなどの半導体素子が設けられるからである。典型的には、素子領域113の面積は素子領域111や素子領域112の面積よりも小さくなっている。

10

**【0028】**

本例では上述した素子領域113の半導体素子として画素トランジスタが設けられている。典型的な画素トランジスタはMOSトランジスタでありうる。図2にはMOSトランジスタである画素トランジスタの不純物領域としてチャネル領域70を記載しているが、素子領域113にはソース領域やドレイン領域(不図示)も設けられている。チャネル領域70の上には画素トランジスタのゲート電極80が設けられている。素子領域114には光電変換素子PD3の蓄積領域としてのn型の不純物領域43が設けられている。なお、図1(b)において光電変換素子PD1、PD2、PD3として示した範囲は、図1において光電変換素子PDの蓄積領域であるn型の不純物領域40に対応する。図2において不純物領域41、42、43として示した範囲の外には光電変換素子を成すp型の不純物領域50に対応する不純物領域が存在している。

20

**【0029】**

素子分離部10は、分離領域101、102、103を含む。分離領域101は素子領域111と素子領域113との間に位置する。分離領域102は素子領域112と素子領域113との間に位置する。分離領域103は素子領域111と素子領域114との間に位置する。

30

**【0030】**

半導体層100は表面1側における素子領域と分離領域の分布に対応した半導体領域を素子分離部10よりも裏面2側に有する。裏面2側の半導体領域は、素子分離部10の分離領域あるいは素子領域に対する位置によって区分される。各半導体領域は、法線方向Nにおいて素子分離部10のいずれかの分離領域あるいは半導体層100のいずれかの素子領域と、裏面2との間に位置することになる。このような半導体領域として、半導体層100は、半導体領域121、122、123、124、125、126、127を含む。半導体領域121は素子領域111と裏面2との間に位置し、半導体領域122は素子領域112と裏面2との間に位置する。半導体領域123は素子領域113と裏面2との間に位置する。半導体領域127は素子領域114と裏面2との間に位置する。半導体領域124は分離領域101と裏面2との間に位置し、半導体領域125は分離領域102と裏面2との間に位置し、半導体領域126は分離領域103と裏面2との間に位置する。以下の説明における「半導体領域」とは、上述のように分離領域と素子領域に対応付けられた位置を示すものである。一方、半導体層100内において半導体素子の動作のために、所定の導電型、不純物種、不純物濃度によって区分される領域は「不純物領域」として説明する。

40

**【0031】**

画素分離部20は法線方向Nにおいて分離領域103に重なる。画素分離部20は溝21により構成されている。面内方向Pにおいて、画素分離部20は半導体領域121と半導体領域127との間に位置する。画素分離部20によって半導体領域126は複数の部

50

分に分割されている。その結果、画素分離部 20 と半導体領域 121 との間に位置する部分 1261 と、画素分離部 20 と半導体領域 127 との間に位置する部分 1262 と、を含んでいる。本例では、画素分離部 20 が分離領域 103 に接続している。また、本例では、画素分離部 20 が裏面 2 に達している。つまり、画素分離部 20 を構成する溝 21 が裏面 2 に連続している。画素分離部 20 と分離領域 103 とを離間させる場合には、画素分離部 20 と分離領域 103 との間に半導体領域 126 の一部が位置することになる。画素分離部 20 と裏面 2 とを離間させる場合には、画素分離部 20 と裏面 2 との間に半導体領域 126 の一部が位置することになる。画素分離部 20 は面内方向 P における少なくとも一部が法線方向 N において素子分離部 10 に重なる部分を有していればよい。画素分離部 20 は面内方向 P における一部が法線方向 N において素子分離部 10 に重ならない部分を有していてもよい。

#### 【0032】

画素分離部 30 は法線方向 N において素子領域 111 と素子領域 112 の間の中間領域 110 に重なる。素子領域 111 と素子領域 112 の間の中間領域 110 としては、分離領域 101、分離領域 102 および素子領域 113 があり、本例では、画素分離部 30 は素子領域 113 に重なっている。画素分離部 30 は法線方向 N において、分離領域 101 および / または分離領域 102 に重なっていてもよい。画素分離部 30 は法線方向 N において、素子領域 113 に重なっていなくてもよい。このように、画素分離部 30 は法線方向 N において、素子分離部 10 に重ならない部分を有し得る。

#### 【0033】

画素分離部 30 は溝 31 により構成されている。面内方向 P において、画素分離部 30 は半導体領域 121 と半導体領域 122 との間に位置する。素子領域 113 に重なる画素分離部 30 は、面内方向 P において、画素分離部 30 は半導体領域 124 と半導体領域 125 との間に位置する。画素分離部 30 によって半導体領域 123 は複数の部分に分割されている。その結果、半導体領域 123 は、画素分離部 30 と半導体領域 121 との間に位置する部分 1231 と、画素分離部 30 と半導体領域 122 との間に位置する部分 1232 と、を含んでいる。

#### 【0034】

このように、平面 3 内において、半導体領域 121 と半導体領域 127 は画素分離部 20 によって不連続になっている。また、半導体領域 121 と半導体領域 122 は画素分離部 30 によって不連続になっている。これにより、画素間の光の混合が低減され、光電変換装置の光学的特性が向上する。また、画素間の電荷の混合が低減され、光電変換装置の電気的特性が向上する。

#### 【0035】

画素分離部 30 が素子領域 111 と素子領域 112 の間の領域、すなわち、分離領域 101、分離領域 102 および素子領域 113 から離間している。これにより画素分離部 30 に起因して画素トランジスタ 90 に生じるノイズを低減することができる。また、分離領域 101、分離領域 102 および素子領域 113 の近傍で生じるあるいは応力集中による画素トランジスタ 90 の動作への影響を低減することできる。また、応力集中によって半導体層 100 内に欠陥（転移欠陥など）が生じることを抑制できるため、光電変換素子 P D に取り込まれる暗電流を低減することもできる。

#### 【0036】

特に、画素トランジスタ 90 のゲート電極 80 にはチャネル領域 70 が位置する。チャネル領域 70 はトランジスタの中でもソース・ドレイン領域に比べて、ノイズに敏感である。よって、チャネル領域 70 やゲート電極 80 に重なるように、画素分離部 20 よりも浅い画素分離部 30 を配することが好ましい。特に、画素分離部 30 は少なくとも画素トランジスタ 90 のゲート絶縁膜には接しないことが効果的である。また、画素分離部 30 に、画素分離部 20 より浅い第 1 部分と第 1 部分よりもさらに浅い第 2 部分とを設け也好い。つまり、第 2 部分の表面 1 の側の端は、第 2 部分の表面 1 の側の端よりも裏面 2 の側に位置することになる。そして、第 2 部分がチャネル領域 70 やゲート電極 80 に重なり

10

20

30

40

50

、第1部分が他の領域、例えばソース・ドレイン領域に重なるようにしてもよい。

#### 【0037】

画素分離部30と光電変換素子PDとを分離するための濃いp型の不純物領域を設けることが望ましい。ここで、分離領域101や分離領域102の下に画素分離部30を配置すると、この濃いp型の不純物領域の分だけ光電変換素子PDの大きさが制限される。そこで、素子領域113の下に画素分離部30を配置することで、光電変換素子PDを大きくすることもできる。

#### 【0038】

さらに、半導体領域123に隣接する半導体領域124や半導体領域125をも光電変換素子PDとして利用することが可能となる。仮に半導体領域124に画素分離部20が配されていると画素分離部20が半導体領域123と半導体領域121との間の電荷の移動を妨げてしまう。そのため、半導体領域123を光電変換素子PDとして有効に利用することが困難になる。このように素子領域113の下に画素分離部30を配置することで、光電変換素子PD1を半導体領域121から半導体領域124まで延在させることができる。また、光電変換素子PD2を半導体領域122から半導体領域125まで延在させることができる。これにより、感度を向上することができる。

10

#### 【0039】

分離領域101と裏面2との間には画素分離部20が設けられていない。そのため、平面3内において半導体領域121と半導体領域123が半導体領域124を介して連続している。つまり、平面3において、素子領域111と素子領域113と分離領域101の下では半導体層100が連続している。このように、分離領域101の下で画素分離部20が設けられずに半導体層100が連続しているため、画素分離部20の溝21による光の散乱が抑制される。このため、光電変換素子PDに入射する光の量を増加させることができ、感度が向上する。また、ノイズ源となる画素分離部20を、光電変換素子PDの蓄積領域としての不純物領域40から遠ざけることにより、画素分離部20の近傍で発生したノイズが光電変換素子PDに取り込まれることを抑制できる。さらに、素子領域111や半導体領域121だけでなく、半導体領域124を光電変換素子PDとして利用することも可能となる。仮に半導体領域124に画素分離部20が配されていると、画素分離部20の分だけ光電変換素子PDの体積が小さくなり、感度が低下する。

20

#### 【0040】

30

図1に示した例では、光電変換素子PDを図2における半導体領域123、124に相当する領域まで配置している。これにより、光電変換素子PDの中心とマイクロレンズの集光位置（典型的にはマイクロレンズの光軸）を一致させるあるいは近づけることが容易になる。マイクロレンズの集光位置とフォトダイオードの中心を近づけるには、マイクロレンズの光軸と分離領域101との距離を、マイクロレンズの光軸と分離領域103との距離よりも小さくすればよい。そうすれば、画素分離部20、30から概ね等しい距離の位置にマイクロレンズで集光することができる。

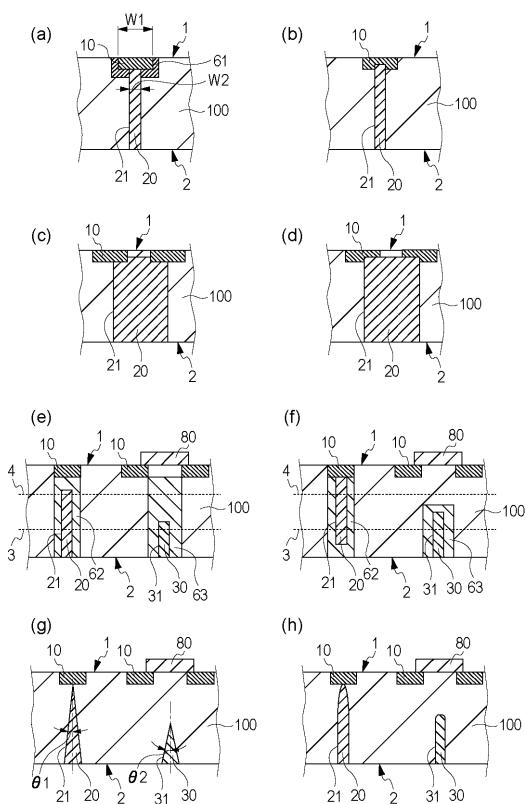

#### 【0041】

図2(a)～(d)には、素子分離部10に接続する画素分離部20の変形例を示している。図2(a)に示すように、素子分離部10の周囲にはp型のチャネルトップ用の濃いp型の不純物領域61を設けることができる。画素分離部20の底部はその不純物領域61に接するよう設けるのが望ましい。これにより画素分離部20の底部の近傍の欠陥に対しても素子分離部10と同様に暗電流などの問題を抑制することができる。

40

#### 【0042】

また、図2(b)に示すように、画素分離部20の底部が素子分離部10の底部に食い込むように画素分離部20を配置しても良い。このようにすることで素子分離部10と画素分離部20の界面を半導体層100から遠ざけることができるので、画素分離部20の底部の周囲で生じうる欠陥を低減することができる。

#### 【0043】

また、図2(a)、(b)に示すように、画素分離部20を接続させる素子分離部10

50

の分離領域の幅 W 1 は、画素分離部 2 0 の幅 W 2 よりも大きくすると良い ( $W_1 > W_2$ )。これにより、アライメントズレが生じた場合においても、画素分離部 2 0 の底部を素子分離部 1 0 の底部に接続させることが容易になる。

#### 【 0 0 4 4 】

また、図 2 ( c )、( d )に示すように、画素分離部 2 0 の一部は素子領域に対向していてよい。さらに、図 2 ( c )、( d )に示すように、画素分離部 2 0 は、素子領域を挟んで対向する複数の分離領域の双方に接続されていてよい。図 2 ( c )、( d )は、画素分離部 2 0 のうち、素子領域に対向する部分が、素子分離部 1 0 の底面よりも表面 1 側に位置している場合を示している。図 2 ( c )は、画素分離部 2 0 のうち、分離領域に對向する部分が、素子領域に對向する部分よりも裏面 2 側に位置している場合を示している。図 2 ( d )は、素子分離部 1 0 のうち、画素分離部 2 0 に對向しない部分が、画素分離部 2 0 に對向する部分よりも裏面 2 側に位置している場合を示している。10

#### 【 0 0 4 5 】

図 2 ( e )、( f )に示すように、画素分離部 2 0 の周囲には、画素分離部 2 0 から半導体素子へ、ノイズとなる電荷が混入することを抑制するための濃い p 型の不純物領域 6 2 を設けることができる。同様に画素分離部 2 0 の周囲には、画素分離部 2 0 から半導体素子へ、ノイズとなる電荷が混入することを抑制するための濃い p 型の不純物領域 6 2 を設けることができる。同様に、画素分離部 3 0 の周囲には、画素分離部 3 0 から半導体素子へ、ノイズとなる電荷が混入することを抑制するための濃い p 型の不純物領域 6 3 を設けることができる。図 2 ( e )に示すように、不純物領域 6 2 と不純物領域 6 3 を設ける位置は、画素分離部 2 0 、3 0 の深さの違いに依らずに同じでもよい。図 2 ( e )では、不純物領域 6 2 と不純物領域 6 3 は素子分離部 1 0 の深さと同程度まで設けている。また、図 2 ( e )に示すように、不純物領域 6 2 と不純物領域 6 3 を設ける位置は、画素分離部 2 0 、3 0 の深さの違いに応じて異なっていてもよい。図 2 ( e )では、裏面 2 に対して画素分離部 3 0 よりも深い画素分離部 2 0 の周囲の不純物領域 6 2 を、裏面 2 に対して画素分離部 2 0 よりも浅い画素分離部 3 0 の周囲の不純物領域 6 3 よりも、裏面 2 に対して深い位置まで設けている。なお、濃い p 型の不純物領域 6 2 、6 3 は、図 2 ( a )で示した濃い p 型の不純物領域 6 1 と連続していてよいし、一体的に形成されていてよい。20

#### 【 0 0 4 6 】

図 2 ( e )には画素分離部 2 0 が素子分離部 1 0 に接続しない場合を示している。図 2 ( f )には、画素分離部 2 0 が裏面 2 に達しない場合を示している。図 2 ( e )、( f )の場合でも、画素分離部 2 0 および画素分離部 3 0 は平面 3 を通り、画素分離部 2 0 は平面 4 を通り、画素分離部 3 0 が平面 4 を通らない。30

#### 【 0 0 4 7 】

図 2 ( g )に示すように、深さの異なる画素分離部 2 0 と画素分離部 3 0 は、溝 2 1 と溝 3 1 の側面の傾斜角を異ならせててもよい。例えば、深い画素分離部 2 0 の溝 2 1 の側面の傾斜角  $\alpha_1$  を、浅い画素分離部 3 0 の溝 3 1 の側面の傾斜角  $\alpha_2$  よりも小さくする ( $\alpha_1 < \alpha_2$ )。また表面 1 側に向けて溝 2 1 、3 1 の幅を狭くする。このように、画素分離部 3 0 の周囲において、欠陥や応力集中によるトランジスタの動作への影響が懸念される領域では、画素分離部 3 0 の体積を小さくすることで、トランジスタの動作への影響を抑制することができる。40

#### 【 0 0 4 8 】

あるいは図 2 ( h )に示すように、深さの異なる画素分離部 2 0 と画素分離部 3 0 は底部の曲率を異ならせても良い。例えば、深い画素分離部 2 0 の溝 2 1 の底面の曲率を、浅い画素分離部 3 0 の溝 3 1 の底面の曲率よりも大きくする。画素分離部 3 0 の溝 3 1 の底面の曲率を小さくすることにより局所的な応力を緩和することが可能となる。画素分離部 2 0 の溝 2 1 の底面の曲率が大きくなる場合には、図 2 ( h )のように画素分離部 2 0 の先端を素子分離部 1 0 に食い込ませても良い。

#### 【 0 0 4 9 】

1020304050

なお画素分離部 20 の形状は本実施例に限定されるものではなく、公知のトレンチ形状を適宜用いることが可能であり、例えば半導体層 100 の裏面 2 側から表面 1 側に向かって順テーパーとなるようにしてもよいし、逆テーパーとなるようにしてもよい。あるいは複数の傾斜角を備えた構造としても良い。このように画素分離部 20、30 の形状を調整することにより、各画素における混色を抑制したり、あるいは感度を向上したり、ノイズを低減したりすることができる。

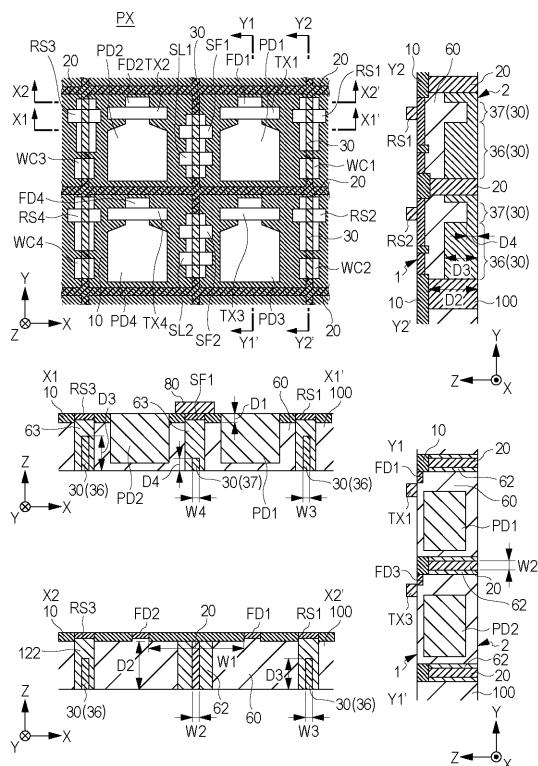

#### 【0050】

以下、図 3、4 を用いて、画素領域 P X のレイアウトの例を示す。なお、以下の例では上述した面内方向 P を互いに交差する（直交する）X 方向と Y 方向に分けて記載する。また、法線方向 P については、X 方向および Y 方向に交差する（直交する）Z 方向として記載する。図 3、4 の X - Y 平面のレイアウトは裏面 2 の側から半導体層 100、素子分離部 10、画素分離部 20、30 を透視したように記載している。10

#### 【0051】

そのため、素子分離部 10 と画素分離部 20、30 が重なる部分については、素子分離部 10 のハッキングと画素分離部 20、30 のハッキングを重ねて示している。

#### 【0052】

図 3 を用いて、画素のレイアウトの第 1 例を示す。画素分離部は、格子状に配置された画素分離部は X 方向と Y 方向で深さが異なるように形成されている。すなわち、X 方向には深い画素分離部 20 が延在し、Y 方向には浅い画素分離部 30 が延在する。20

#### 【0053】

図 3 には 4 種類の形状の素子領域を記載している。第 1 種類の素子領域にはフォトダイオード P D m、転送ゲート T X m およびフローティングディフュージョン F D m が配されている。第 2 種類の素子領域にはリセットトランジスタ R S n が配されている。第 3 種類の素子領域には増幅トランジスタ S F n および選択トランジスタ S L n が配されている。第 4 種類の素子領域にはウェルコンタクト W C n が配されている。ここで、m は m 個の画素毎に定められる数字であり、図 4 では n = 1 ~ 4 として、P D 1、P D 3、F D 2、F D 4 のように付して示している。n は画素毎に定められる数字であり、図 4 では m = 1、2 として、R S 1、R S 2、S D 1、S F 2 のように付して示している。なお、m が奇数なら n = (m + 1) / 2、m が偶数なら n = m / 2 である。30

#### 【0054】

リセットトランジスタ R S n によりフローティングディフュージョン F D m の電位がリセットされた後、フォトダイオード P D m からの電荷が、転送ゲート T X m を介してフローティングディフュージョン F D m へ転送される。フローティングディフュージョン F D m での電位変化が増幅トランジスタ S F n のゲートに不図示の配線を通じて伝えられる。ソースフォロワ回路を構成する増幅トランジスタ S F n により増幅された信号は選択トランジスタ S L n を介して順次、出力信号線（不図示）に読み出される。つまり一つの画素内で光電変換、蓄積、電荷検出、増幅、画素選択の動作が実行される。またウェルコンタクト W C n は、画素のウェル領域の電位を制御する。複数のフォトダイオード P D m がリセットトランジスタ R S n、増幅トランジスタ S F n および選択トランジスタ S L n を共有している。このときの共有の関係は、m が奇数なら n = (m + 1) / 2、m が偶数なら n = m / 2 を満足する。40

#### 【0055】

なお、複数のフォトダイオードで画素トランジスタを共有せずに、画素毎に画素トランジスタを配置してもよい。また、1 つの画素に複数のフォトダイオード P D から別々に信号を読み出して、これらの信号を合成する様にしてもよい。このように、1 画素の複数のフォトダイオード P D によって瞳分割された光線を別々に検出し、位相差検出方式による測距あるいは焦点検出が可能となる。また、1 画素の複数のフォトダイオード P D p の感度を異ならせて信号を合成することで、ダイナミックレンジの拡大を図ることもできる。

#### 【0056】

フォトダイオード P D 1 とフォトダイオード P D 2 が X 方向に並ぶ。フォトダイオード50

P D 1 とフォトダイオード P D 3 が Y 方向に並ぶ。フォトダイオード P D 3 が配された素子領域は、フォトダイオード P D 1 が配された素子領域に隣り合う。ここで、2つの素子領域が隣り合うことは、2つの素子領域の間に素子領域が存在しないことを意味する。フォトダイオード P D 1 が配された素子領域が図 1 ( a ) で説明した素子領域 1 1 1 に対応し、フォトダイオード P D 2 が配された素子領域が図 2 で説明した素子領域 1 1 2 に対応する。増幅トランジスタ S F n および選択トランジスタ S L n が配された素子領域が図 2 で説明した素子領域 1 1 3 に対応する。フォトダイオード P D 3 が配された素子領域が図 2 で説明した素子領域 1 1 4 に対応する。

#### 【 0 0 5 7 】

素子分離部 1 0 はフォトダイオード P D 1 が配された素子領域とフォトダイオード P D 3 が配された素子領域との間の分離領域 1 0 3 を有する。画素分離部 2 0 は、Z 方向において分離領域 1 0 3 に重なる。

10

#### 【 0 0 5 8 】

また、画素分離部 3 0 に、画素分離部 2 0 より浅い第 1 部分 3 6 と第 1 部分 3 6 よりもさらに浅い第 2 部分 3 7 を設けている。つまり、第 2 部分 2 7 の表面 1 の側の端は、第 2 部分 3 6 の表面 1 の側の端よりも裏面 2 の側に位置することになる。そして、第 2 部分 3 7 がチャネル領域 7 0 やゲート電極 8 0 に重なり、第 1 部分 3 6 が他の領域、例えばソース・ドレイン領域に重なるようにしてもよい。

#### 【 0 0 5 9 】

画素トランジスタの動作に影響が懸念されるチャネル領域の下については画素分離部 3 0 をより浅く設けた第 2 部分 3 7 を設けている。ソース・ドレイン領域の下については、チャネル領域の下よりも深く画素分離部 3 0 の第 1 部分 3 6 を設けているが、ソース・ドレイン領域の下についても、他の画素分離部 3 0 ( 第 1 部分 3 6 ) よりも浅く設けることもできる。半導体層 1 0 0 の表面 1 側の構造に応じて、画素分離部 2 0 、 3 0 の長手方向に沿って深さを連続的に異ならせても良い。この場合には、画素分離部 2 0 、 3 0 の長手方向に沿って画素分離部 2 0 、 3 0 の幅を連続的に異ならせても良い。また画素分離部 2 0 、 3 0 の線幅や深さが変化する箇所においては緩やかに変化させることが望ましい。

20

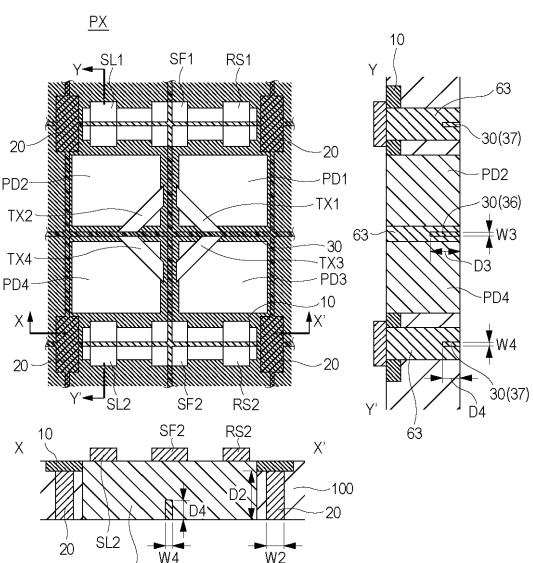

#### 【 0 0 6 0 】

図 4 を用いて、画素のレイアウトの第 2 例を示す。図 4 に示すように、酸化シリコンで形成される素子分離部 1 0 は複数のフォトダイオード P D n ( n = 1 ~ 4 ) が配された素子領域と、その周囲の画素トランジスタが設けられた素子領域との間に設けられている。隣接するフォトダイオード P D n 間には素子分離部 1 0 は設けられていない。図示はしないが隣接するフォトダイオード P D n 間においては、イオン注入による p 型の濃い不純物領域 6 3 による分離が成されている。

30

#### 【 0 0 6 1 】

図 4 に示した平面図のように、素子分離部 1 0 に対向する位置の画素分離部の幅を局所的に広くし、それ以外の領域においては幅を相対的に狭くしている。相対的に幅の広い画素分離部の方を深く形成することができる。

#### 【 0 0 6 2 】

半導体層 1 0 0 の表面 1 側の素子分離部 1 0 と接する深い画素分離部 2 0 の幅 W 2 は、半導体層 1 0 0 の途中までの深さ D 3 を有する浅い画素分離部 3 0 の幅 W 3 よりも広くなっている ( W 2 > W 3 ) 。また、半導体層 1 0 0 の途中までの深さを有する画素分離部 3 0 においても、異なる深さに応じて幅を異ならせている。すなわち、深さ D 3 を有する画素分離部 3 0 の第 1 部分 3 6 の幅 W 3 は、深さ D 3 よりも小さい深さ D 4 を有する画素分離部 3 0 の第 2 部分 3 7 の幅 W 4 よりも大きい ( W 3 > W 4 ) 。このように、画素分離部の深さが小さくなるほど、画素分離部の幅を小さくすることができる。なお、画素分離部 2 0 、 3 0 の幅が Z 方向 ( 半導体層 1 0 0 の厚さ方向 ) において変化する場合、第 3 面 3 における画素分離部 2 0 、 3 0 の幅を代表的な幅として採用することができる。第 3 面 3 においては画素分離部 2 0 と画素分離部 3 0 の双方が位置するため、幅の比較も容易である。

40

50

**【 0 0 6 3 】**

上述した本実施例によれば、隣り合うフォトダイオードを2つ含む領域を画素分離部20、30が囲む場合においても、画素分離部20、30の深さを半導体層100の表面1側の構造に応じて異ならせている。これにより、光電変換の特性あるいはトランジスタの特性などへの影響を抑制し、かつ隣接する画素間での混色を効果的に抑制することが可能である。

**【 0 0 6 4 】**

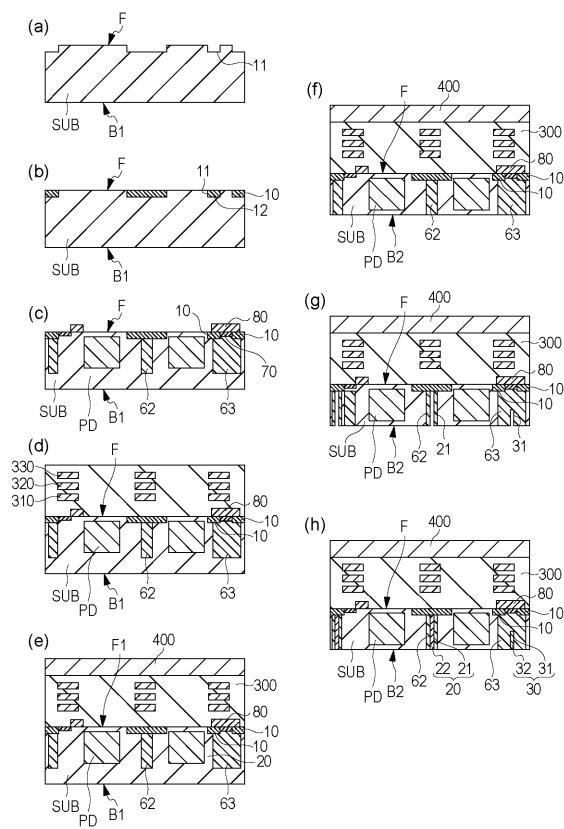

次に図5を用いて、本実施例に係る固体撮像装置の製造方法を説明する。

**【 0 0 6 5 】**

まず図5(a)に示す工程aでは、半導体基板SUBの表面F側に素子分離部10用の溝11が形成される。溝11の周囲にはイオン注入によりチャネルトップ層(不図示)が形成される。10

**【 0 0 6 6 】**

次に、図5(b)に示す工程bでは、溝11に素子分離部10のための絶縁体12を埋める。絶縁体12は酸化シリコンが好適である。溝11の外の余分な絶縁体はCMP法等により除去される。これにより、STI(Shallow Trench Isolation)構造を有する、素子分離部10が形成される。

**【 0 0 6 7 】**

次に、図5(c)に示す工程cでは、半導体基板SUBの表面F上にゲート絶縁膜(不図示)及びゲート電極80が積層されて画素トランジスタが形成(不図示)される。さらに、半導体基板SUBの表面F側から行われるイオン注入によって光電変換素子PDや画素トランジスタのソース・ドレイン領域を形成する。また、画素分離部20、30が形成される半導体領域には、本工程において、不純物領域62、63を形成しておくことができる。20

**【 0 0 6 8 】**

次に、図5(d)に示す工程dでは、ゲート電極80を覆う絶縁層が積層された後に、絶縁層にコンタクトホールが形成される。さらにコンタクトホールが形成された絶縁層上に配線層および層間絶縁層を積層することで多層配線構造が形成される。本例では3層の配線層310、320、330を形成している。配線構造には、例えば銅配線やアルミニウム配線を用いることが可能である。30

**【 0 0 6 9 】**

次に、図5(e)に示す工程eでは、絶縁膜300の上方から支持基板400が貼り合わされる。貼り合わせは接着剤による接合でも良いし、その他公知の方法を適宜用いることができる。ただし配線構造などに影響を与えないように400以下のプロセスで処理するのが好ましい。

**【 0 0 7 0 】**

次に、図5(f)に示す工程fでは、半導体基板SUBが所望の厚さになるまで、半導体基板SUBの裏面B1側から薄化処理が施される。この半導体基板SUBの薄化は裏面B1に代わって新たな裏面B2が現れる。裏面B2には光電変換素子PDが臨むように行われてもよい。例えば、化学機械研磨法(CMP)や、ドライエッティング、ウェットエッティングなどを用いることができる。またこれら手法を組合せることも可能である。例えば薄化された半導体基板SUBの膜厚は1~10μmの範囲とし、またフォトダイオードの受光感度の向上、あるいは半導体基板の機械的な強度の観点から、2~5μmの範囲とすることが好ましい。40

**【 0 0 7 1 】**

次に図5(g)に示す工程gでは、半導体基板SUBの表面F側に形成された素子分離部10に対向する位置において、半導体基板SUBの裏面B2側から画素分離部20の溝21が形成される。このとき画素分離部20の溝21の裏面B2に対する深さは、画素分離部20の底部が素子分離部10に達する深さとするのがよい。例えば薄化処理された半導体基板SUBの厚さが約2μmの場合に素子分離部10の深さが約0.3μmとすると50

、対向して配置される溝 2 1 の深さが約 1 . 7  $\mu\text{m}$  となるように形成される。このような画素分離部 2 0 は以下の手順で形成される。なお画素分離部 2 0 の底部の幅は、素子分離部 1 0 の底部の幅に対して相対的に狭くすると良い。これによりアライメントズレが生じた場合においても、画素分離部 2 0 の底部を素子分離部 1 0 の底部に接することが容易になる。

#### 【 0 0 7 2 】

画素分離部 2 0 の溝 2 1 は光電変換素子 P D に隣接する素子分離部 1 0 の一部の分離領域 1 0 1 の下には設けない。これにより、上述した光電変換性能の向上が可能となる。

#### 【 0 0 7 3 】

画素分離部 2 0 の形成方法について、より詳細に説明する。まず画素分離部 2 0 の溝 2 1 、画素分離部 3 0 の溝 3 1 を半導体基板 S U B に形成するため、例えば異方性のドライエッチング法を用いることで、所望の幅を有する溝 2 1 、 3 1 を形成する。シリコンのエッチングには、保護膜形成ステップとエッチングステップを数秒単位で繰り返すボッシュプロセスを用いることもできる。なお画素分離部 2 0 の溝 2 1 をドライエッチングにより加工する際には、半導体基板 S U B のエッチングの終端検出として素子分離部 1 0 を利用しても良い。あるいは半導体基板 S U B の膜厚に応じてエッチング時間を指定してエッチングしても良い。また素子分離部 1 0 の底部の一部をエッチングするようにしても良い。

10

#### 【 0 0 7 4 】

深さの異なる溝 2 1 、 3 1 は同一のエッチングマスク（不図示）を用いて同時形成することができる。マイクロロローディング効果を利用したエッチング条件で半導体基板 S U B をエッチングすることで、エッチングマスクのマスクパターンの広い開口の下に深い溝 2 1 を形成し、狭い開口の下に浅い溝 3 1 を形成する。マイクロロローディング効果は開口幅が小さくなるほどエッチング速度が低下する現象である。エッチングマスクのマスクパターンを設定することで、深さの異なる溝を簡単な工程で形成することができる。なお、逆マイクロロローディング効果を利用したエッチング条件で半導体基板 S U B をエッチングすることもできる。その場合には、エッチングマスクのマスクパターンの狭い開口の下に深い溝 2 1 を形成し、広い開口の下に浅い溝 3 1 を形成することができる。もちろん、深い溝 2 1 と浅い溝 3 1 を別々の工程で形成することも可能であるが、リソグラフィ工程の増大や、深い溝 2 1 に入り込むマスク残渣の問題など、不利な点が多くなる。

20

#### 【 0 0 7 5 】

次に、次に図 5 ( g ) に示す工程 g では、溝 2 1 、 3 1 の中に固体 2 2 、 3 2 を形成する。まず、半導体層 1 0 0 の裏面 2 で発生する暗電流を抑制するための固定電荷膜（不図示）を形成する。このために半導体基板 S U B の裏面 B 2 の形状に沿って固定電荷膜（不図示）が形成される。この固定電荷膜は、少なくとも半導体基板 S U B の裏面 B 2 上に形成され、さらに画素分離部 2 0 の溝 2 1 の側壁や底面を被覆するように形成しても良い。このように画素分離部 2 0 の側壁や底面を固定電荷膜で被覆することで、例えば溝 2 1 の表面で発生しうる暗電流も抑制することが可能となる。なお固定電荷膜としては、たとえば原子層堆積法 ( A L D ) により酸化ハフニウム膜を用いることができる。

30

#### 【 0 0 7 6 】

次に、半導体基板 S U B の画素分離部 2 0 の内部に誘電体、金属材料、その他の遮光性を備えた材料、あるいはそれらを組み合わせた材料からなる固体 2 2 を形成する。例えば、酸化シリコン膜や酸化チタン膜などの半導体基板 S U B を成すシリコンよりも低い屈折率を有する材料を固定電荷膜上に形成する。続いて化学気相成長法 ( C V D ) や原子層堆積法 ( A L D ) を用いて導電材料を埋設させて画素分離部 2 0 を形成することができる。あるいは原子層堆積法 ( A L D ) を用いて酸化シリコン膜を固定電荷膜上に形成した後に、 H D P ( H i g h D e n s i t y P l a s m a ) C V D 法を用いて酸化シリコン膜を堆積する。このように 2 層構造の絶縁膜で埋設させて画素分離部 2 0 を形成しても良い。特に 4 0 0 以下の低温で形成できる材料が好ましく、例えば P 型不純物をドープしたアモルファスシリコン、銅、タンゲステンなどを化学気相成長法 ( C V D ) や原子層堆積法 ( A L D ) などで形成するのが望ましい。なお、上述した固定電荷膜を固体 2 2 として

40

50

用いてもよい。

**【0077】**

なお上記で画素分離部20の内部に固体22を埋設する事例について説明しているが、溝21内の構成はこれらに限定されるものではなく、混色を抑制可能な構造であれば良く、公知の構成及び製法を適用することが可能である。また例えば画素分離部20は溝21の一部または全部が空洞であっても構わない。

**【0078】**

なお本例では、画素分離部20を半導体基板の裏面B2側から形成する場合について説明したが、画素分離部20の形成方法はここで説明する方法に限定されるものではない。例えば、工程a、bで説明した素子分離部10を形成する前に、半導体基板SUBの表面F側から溝21を形成しても良い。

10

**【0079】**

この後は図1(a)に示す構造を形成する。半導体基板SUBの裏面B2側に誘電体膜410が形成され、誘電体膜410上の画素間に遮光部材420がパターニングされる。遮光部材420はスパッタ法や化学気相成長法(CVD)により成膜された後、画素間を含む遮光構造を必要とする部分以外を除去するように加工が行われることにより形成される。遮光部材420の材料としては、例えば、チタンとタングステンの積層膜、あるいは窒化チタンとタングステンの積層膜などを用いることができる。

**【0080】**

次に平坦化膜(不図示)を形成し、平坦化膜上に各画素に対応して例えば赤、緑、青のカラーフィルタアレイ430を形成し、その上にマイクロレンズアレイ440を形成する。各カラーフィルター及びマイクロレンズは、画素アレイの各単位画素に対応して形成される。以上により、光電変換装置を完成させる。半導体基板SUBは上述した半導体層100として用いられる。

20

**【0081】**

上述した実施形態によれば、画素領域PXにおいて深い画素分離部20と浅い画素分離部30と併用している。深い画素分離部20を素子分離部10に向かって深さ方向に伸ばすことで、隣接する画素間での混色を効果的に抑制することが可能である。また、浅い画素分離部30をトランジスタ等が設けられた素子領域や欠陥が生じやすい分離領域の下に配置しても、ノイズ等の影響を低減することができる。これにより、画素分離部20、30を光電変換に適したレイアウトで配置することができる。よって光電変換装置の性能を向上することが可能となる。

30

**【0082】**

以上説明した光電変換装置は、カメラなどに用いられる撮像装置(イメージセンサ)に適用できる。この他、焦点検出(AF:オートフォーカス)用のセンサや測光(AE:オートエクスposure)用のセンサにも適用できる。カメラは、撮像装置としての光電変換装置以外に、信号処理装置、記憶装置、表示装置および光学装置の少なくともいずれかを備えることができる。信号処理装置は、例えばCPUやDSPであり、撮像装置から得られた信号を処理する。記憶装置は、例えばDRAMやフラッシュメモリであり、撮像装置から得られた信号に基づく情報を記憶する。表示装置は、例えば液晶ディスプレイや有機ELディスプレイであり、撮像装置で得られた信号に基づく情報を表示する。光学装置は、例えばレンズやミラー、シャッター、フィルタであり、撮像装置へ光を導く。ここでのいうカメラとはスチルカメラやビデオカメラ、監視カメラ等のカメラ専用機器以外に、撮影機能を有する情報端末や撮影機能を有する移動体(車両や飛行体)も包含する。

40

**【0083】**

また、本明細書に明確な記載がなくとも、添付の図面や技術常識から把握できる事項も本開示の一部を構成する。本発明は、本開示の技術思想の範囲を逸脱しない限り、適宜な変更が可能である。

**【符号の説明】**

**【0084】**

50

## 1 0 0 半導体層

1 表面

2 裏面

3 平面

1 0 素子分離部

2 0 画素分離部

3 0 画素分離部

【図1】

【図2】

【 図 3 】

【 四 4 】

【 四 5 】

---

フロントページの続き

(56)参考文献 特開2013-175494(JP,A)

特開2014-204047(JP,A)

国際公開第2011/077580(WO,A1)

米国特許出願公開第2014/0054662(US,A1)

国際公開第2012/117931(WO,A1)

米国特許出願公開第2014/0204047(US,A1)

米国特許出願公開第2011/0155893(US,A1)

欧州特許出願公開第02518768(EP,A1)

特開2012-164768(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H04N 5/357

H04N 5/374