(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3800520号

(P3800520)

(45) 発行日 平成18年7月26日(2006.7.26)

(24) 登録日 平成18年5月12日(2006.5.12)

(51) Int.C1.

F 1

|             |                |                  |      |        |         |

|-------------|----------------|------------------|------|--------|---------|

| <b>H03F</b> | <b>3/45</b>    | <b>(2006.01)</b> | H03F | 3/45   | Z       |

| <b>H03K</b> | <b>19/017</b>  | <b>(2006.01)</b> | H03K | 19/017 |         |

| <b>H03K</b> | <b>19/0175</b> | <b>(2006.01)</b> | H03K | 19/00  | 1 O 1 K |

請求項の数 18 (全 22 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2002-46740 (P2002-46740)    |

| (22) 出願日  | 平成14年2月22日 (2002.2.22)        |

| (65) 公開番号 | 特開2003-249829 (P2003-249829A) |

| (43) 公開日  | 平成15年9月5日 (2003.9.5)          |

| 審査請求日     | 平成16年3月29日 (2004.3.29)        |

|           |                                                  |

|-----------|--------------------------------------------------|

| (73) 特許権者 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号  |

| (74) 代理人  | 100081938<br>弁理士 德若 光政                           |

| (72) 発明者  | 斎藤 佳代子<br>東京都青梅市新町六丁目16番地の3 株式会社日立製作所 デバイス開発センタ内 |

| (72) 発明者  | 楠 貢<br>東京都青梅市新町六丁目16番地の3 株式会社日立製作所 デバイス開発センタ内    |

| 審査官 野元 久道 |                                                  |

最終頁に続く

(54) 【発明の名称】半導体集積回路装置と半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

一対の第1入力端子にそれぞれゲートが接続された第1導電型の第1差動MOSFET対と、該第1差動MOSFET対の共通ソースに設けられて上記第1差動MOSFET対の動作電流を形成する第1導電型の第1電流源MOSFETとを含む第1增幅部と、

上記一対の第1入力端子にそれぞれゲートが接続され、上記第1導電型と異なる第2導電型の第2差動MOSFET対と、該第2差動MOSFET対の共通ソースに設けられて上記第2差動MOSFET対の動作電流を形成する第2導電型の第2電流源MOSFETとを含む第2增幅部と、

上記第1差動MOSFET対のソース・ドレイン経路に接続された第2導電型の第1MOSFET対と、上記第2差動MOSFET対のソース・ドレイン経路に接続された第1導電型の第2MOSFET対と、

第2導電型の第5MOSFETと第7MOSFET及び第1導電型の第6MOSFETと第8MOSFETとを有し、

上記第1差動MOSFET対のドレインと上記第1MOSFET対のドレインとが接続され、

上記第2差動MOSFET対のドレインと上記第2MOSFET対のドレインとが接続され、

上記第1MOSFET対の一方と、上記第2MOSFET対の一方との間に、上記第5MOSFET及び上記第6MOSFETが直列に接続され、上記第5MOSFETと第6

10

20

MOSFETの接続点が一方の出力とされ、

上記第1MOSFET対の他方と、上記第2MOSFET対の他方との間に、上記第7MOSFET及び上記第8MOSFETが直列に接続され、上記第7MOSFETと第8MOSFETの接続点が他方の出力とされた第1の回路と、

一対の第2入力端子にそれぞれゲートが接続された第1導電型の第3差動MOSFET対及びその共通ソースに設けられて上記第3差動MOSFET対の動作電流を形成する第1導電型の第3電流源MOSFETを含む第3增幅部と、

上記一対の第2入力端子にそれぞれゲートが接続された第2導電型の第4差動MOSFET対及びその共通ソースに設けられて上記第4差動MOSFET対の動作電流を形成する第2導電型の第4電流源MOSFETを含む第4增幅部と、

上記第3差動MOSFET対のソース・ドレイン経路に接続された第2導電型の第3MOSFET対と、上記第4差動MOSFET対のソース・ドレイン経路に接続された第1導電型の第4MOSFET対と、

第2導電型の第9MOSFETと第11MOSFET及び第1導電型の第10MOSFETと第12MOSFETとを有し、

上記第3差動MOSFET対のドレインと上記第3MOSFET対のドレインとが接続され、

上記第4差動MOSFET対のドレインと上記第4MOSFET対のドレインとが接続され、

上記第3MOSFET対の一方と、上記第4MOSFET対の一方との間に、上記第9MOSFET及び上記第10MOSFETが直列に接続され、上記第9MOSFETと第10MOSFETの接続点が一方の出力とされ、

上記第3MOSFET対の他方と、上記第4MOSFET対の他方との間に、上記第11MOSFET及び上記第12MOSFETが直列に接続され、上記第11MOSFETと第12MOSFETの接続点が他方の出力とされた第2の回路とを備え、

上記第2の回路は、上記一方の出力と他方の出力、上記第3及び第4電流源MOSFET、上記第3及び第4MOSFET、第9ないし第12MOSFETのゲートが共通接続されてバイアス電圧を形成し、

上記第1の回路は、上記第1及び第2電流源MOSFET、上記第1及び第2MOSFET、第5ないし第8MOSFETに上記バイアス電圧が供給されてなることを特徴とする半導体集積回路装置。

#### 【請求項2】

請求項1において、

上記一対の第1入力端子には、互いに相補の一対の入力信号が供給され、

上記一対の第2入力端子には、互いに相補の一対の入力信号が供給されてなることを特徴とする半導体集積回路装置。

#### 【請求項3】

請求項1において、

上記一対の第1入力端子には、一方の入力端子に入力信号が供給され、

他方の入力端子には、前記入力信号レベルを判定する参照電圧が供給され、

上記一対の第2入力端子には上記参照電圧が供給されてなることを特徴とする半導体集積回路装置。

#### 【請求項4】

請求項1において、

上記第1及び第2のMOSFET対及び上記第5ないし第8MOSFETのサイズは、上記第3及び第4のMOSFET対及び上記第9ないし第12MOSFETと等しいことを特徴とする半導体集積回路装置。

#### 【請求項5】

請求項1において、

上記第1及び第2のMOSFET対及び上記第5ないし第8MOSFETのサイズは、

10

20

30

40

50

上記第3及び第4のMOSFET対及び上記第9ないし第12MOSFETのサイズよりも大きいことを特徴とする半導体集積回路装置。

【請求項6】

請求項1において、

スタンバイモードと、

上記スタンバイモードにおいて上記第1の回路と上記第2の回路とを互いに切り離す第1スイッチ回路と、

上記第1ないし第4電流源MOSFETオフ状態にさせる第2スイッチ回路と、

上記第1ないし第4MOSFET対のゲートに電源電圧を供給する第3スイッチ回路とを更に有することを特徴とする半導体集積回路装置。 10

【請求項7】

請求項6において、

上記スタンバイモードにおいて上記第1スイッチ回路により上記第1の回路と上記第2の回路とを互いに切り離し、

上記スタンバイモードにおいて上記第2スイッチ回路により上記第1ないし第4電流源MOSFETをオフ状態にさせることを特徴とする半導体集積回路装置。 20

【請求項8】

一対の第1入力端子にそれぞれゲートが接続された第1導電型の第1差動MOSFET対と、該第1差動MOSFET対の共通ソースに設けられて上記第1差動MOSFET対の動作電流を形成する第1導電型の第1電流源MOSFETを含む第1增幅部と、 20

上記一対の第1入力端子にそれぞれゲートが接続された第2導電型の第2差動MOSFET対と、該第2差動MOSFET対の共通ソースに設けられて上記第2差動MOSFET対の動作電流を形成する第2導電型の第2電流源MOSFETを含む第2增幅部と、

上記第1差動MOSFET対に流れる電流を供給する第2導電型の第1MOSFET対を含む第1出力部と、

上記第2差動MOSFET対に流れる電流を供給する第1導電型の第2MOSFET対を含む第2出力部と、

上記第1出力部の第1MOSFET対の一方と、上記第2出力部の第2MOSFET対の一方との間に設けられ、第1出力端子に接続された、第2導電型の第5MOSFET及び第1導電型の第6MOSFETと、 30

上記第1出力部の第1MOSFET対の他方と、上記第2出力部の第2MOSFET対の他方との間に設けられ、第2出力端子に接続された、第2導電型の第7MOSFET及び第1導電型の第8MOSFETとを具備して成り、

上記第1増幅部の第1差動MOSFET対のドレインと上記第1出力部の第1MOSFET対のドレインとが接続され、

上記第2増幅部の第2差動MOSFET対のドレインと上記第2出力部の第2MOSFET対のドレインとが接続され、

上記第1電流源MOSFETは、上記第1差動MOSFET対に比べてオン抵抗値が大きくなるように形成され、

上記第2電流源MOSFETは、上記第2差動MOSFET対に比べてオン抵抗値が大きくなるように形成されている特徴とする半導体集積回路装置。 40

【請求項9】

請求項8において、

一対の第2入力端子にそれぞれゲートが接続された第1導電型の第3差動MOSFET対及びその共通ソースに設けられて上記第3差動MOSFET対の動作電流を形成する第1導電型の第3電流源MOSFETを含む第3增幅部と、

上記一対の第2入力端子にそれぞれゲートが接続された第2導電型の第4差動MOSFET対及びその共通ソースに設けられて上記第4差動MOSFET対の動作電流を形成する第2導電型の第4電流源MOSFETを含む第4增幅部と、

上記第3差動MOSFET対に流れる電流を供給する第2導電型の第3MOSFET対 50

を含む第3出力部と、

上記第4差動MOSFET対に流れる電流を供給する第1導電型の第4MOSFET対を含む第4出力部とを含むバイアス回路を更に備え、

上記バイアス回路の出力は、上記第1ないし第4電流源MOSFETのゲート及び第1ないし第4MOSFETのゲートに供給してなることを特徴とする半導体集積回路装置。

**【請求項10】**

請求項9において、

上記第5ないし第8MOSFETは、上記第1ないし第4MOSFET対及び差動MOSFET対に比べてゲート長が短く形成されていることを特徴とする半導体集積回路装置。

10

**【請求項11】**

第1の電圧に設定された第1電圧端子と、

上記第1の電圧よりも高い電圧の第2の電圧に設定された第2電圧端子と、

增幅回路とを具備して成り、

上記增幅回路は、

第1入力端子と、第2入力端子と、第1出力端子とを有する第1の回路と、

第3入力端子と第4入力端子とを有する第2の回路とを含んで成り、

上記第1の回路は、第1導電型の第1ないし第5のトランジスタと、上記第1導電型とは異なる第2導電型の第6ないし第10のトランジスタと、第3の回路と、第4の回路とを含んで成り、

20

上記第2の回路は、第1導電型の第11ないし第15のトランジスタと、上記第1導電型とは異なる第2導電型の第16ないし第20のトランジスタと、第5の回路と、第6の回路とを有して成り、

上記第1のトランジスタは、上記第2電圧端子に接続されたソースを含んで成り、

上記第2のトランジスタは、上記第1入力端子に接続されたゲートと、上記第1のトランジスタのドレインに接続されたソースとを含んで成り、

上記第3のトランジスタは、上記第1のトランジスタのドレインに接続されたソースを含んで成り、

上記第4のトランジスタは、上記第2電圧端子に接続されたソースを含んで成り、

上記第5のトランジスタは、上記第2電圧端子に接続されたソースを含んで成り、

30

上記第6のトランジスタは、上記第1電圧端子に接続されたソースを含んで成り、

上記第7のトランジスタは、上記第4のトランジスタのドレインに接続されたドレインと、上記第6のトランジスタのドレインに接続されたソースと、上記第1入力端子に接続されたゲートとを含んで成り、

上記第8のトランジスタは、上記第5のトランジスタのドレインに接続されたドレインと、上記第6のトランジスタのドレインに接続されたソースと、上記第2入力端子に接続されたゲートとを含んで成り、

上記第9のトランジスタは、上記第2のトランジスタのドレインに接続されたドレインと、上記第1電圧端子に接続されたソースとを含んで成り、

上記第10のトランジスタは、上記第3のトランジスタのドレインに接続されたドレインと、上記第1電圧端子に接続されたソースとを含んで成り、

40

上記第3の回路は、上記第4のトランジスタのドレインと上記第9のトランジスタのドレインとの間の電流経路と、上記第1出力端子に接続された出力端子とを含んで成り、

上記第4の回路は、上記第5のトランジスタのドレインと上記第10のトランジスタのドレインとの間の電流経路を含んで成り、

上記第11のトランジスタは、上記第2電圧端子に接続されたソースを含んで成り、

上記第12のトランジスタは、上記第3入力端子に接続されたゲートと、上記第11のトランジスタのドレインに接続されたソースとを含んで成り、

上記第13のトランジスタは、上記第11のトランジスタのドレインに接続されたソースを含んで成り、

50

上記第14のトランジスタは、上記第2電圧端子に接続されたソースを含んで成り、

上記第15のトランジスタは、上記第2電圧端子に接続されたソースを含んで成り、

上記第16のトランジスタは、上記第1電圧端子に接続されたソースを含んで成り、

上記第17のトランジスタは、上記第14のトランジスタのドレインに接続されたドレインと、上記第16のトランジスタのドレインに接続されたソースと、上記第3入力端子に接続されたゲートとを含んで成り、

記第18のトランジスタは、上記第15のトランジスタのドレインに接続されたドレインと、上記第16のトランジスタのドレインに接続されたソースと、上記第4入力端子に接続されたゲートとを含んで成り、

上記第19のトランジスタは、上記第12のトランジスタのドレインに接続されたドレインと、上記第1電圧端子に接続されたソースとを含んで成り、

上記第20のトランジスタは、上記第13のトランジスタのドレインに接続されたドレインと、上記第1電圧端子に接続されたソースとを含んで成り、

上記第5の回路は、上記第14のトランジスタのドレインと上記第19のトランジスタのドレインとの間の電流経路と、出力端子とを含んで成り、

上記第6の回路は、上記第15のトランジスタのドレインと上記第20のトランジスタのドレインとの間の電流経路と、出力端子とを含んで成り、

上記第3の回路の電流経路は、第1導電型の第21のトランジスタと第2導電型の第22のトランジスタの直列回路からなり、上記第21のトランジスタと第22のトランジスタの接続点が上記第1出力端子に接続され、

上記第4の回路の電流経路は、第1導電型の第23のトランジスタと第2導電型の第24のトランジスタの直列回路からなり、

上記第5の回路の電流経路は、第1導電型の第25のトランジスタと第2導電型の第26のトランジスタの直列回路からなり、上記第25のトランジスタと第26のトランジスタの接続点が上記出力端子に接続され、

上記第6の回路の電流経路は、第1導電型の第27のトランジスタと第2導電型の第28のトランジスタの直列回路からなり、上記第27のトランジスタと第28のトランジスタの接続点が上記出力端子に接続され、

上記第4、第5、第9、第10、第14、第15、第19、第20及び第21ないし第28のトランジスタのゲートは、前記第5及び第6の回路の出力端子と接続されていることを特徴とする半導体装置。

#### 【請求項12】

請求項11において、

上記第1及び第11のトランジスタのゲートは、スイッチを介して上記第2電圧端子に接続され、

上記第6及び第16のトランジスタのゲートは、スイッチを介して上記第1電圧端子に接続されていることを特徴とする半導体装置。

#### 【請求項13】

請求項11において、

上記第1の電圧は接地電位であり、

上記第2の電圧は電源電圧であることを特徴とする半導体装置。

#### 【請求項14】

請求項11において、

上記第1入力端子には、第1の信号が入力され、

上記第2入力端子には、上記第1の信号の相補の信号に使用される第2の信号が入力され、

上記第3入力端子には、上記第1の信号が入力され、

上記第4入力端子には、上記第2の信号が入力されることを特徴とする半導体装置。

#### 【請求項15】

請求項11において、

10

20

30

40

50

上記第1入力端子には、第1の信号が入力され、

上記第2ないし第4入力端子には、参照電圧が入力されることを特徴とする半導体装置。

。

**【請求項16】**

請求項11において、

上記第1ないし第10のトランジスタは、上記第11ないし20のトランジスタのサイズと略同じサイズのトランジスタであることを特徴とする半導体装置。

**【請求項17】**

請求項11において、

上記第1ないし第10のトランジスタは、上記第11ないし20のトランジスタのサイズよりも大きいサイズのトランジスタであることを特徴とする半導体装置。 10

**【請求項18】**

請求項11において、

上記第1導電型はP導電型であり、

上記第2導電型はN導電型であり、

上記第1ないし第5及び上記第11ないし第15のトランジスタはそれぞれP導電型のMOSFETであり、

上記第6ないし第10及び上記第16ないし第20のトランジスタはそれぞれN導電型のMOSFETであることを特徴とする半導体装置。

**【発明の詳細な説明】**

20

**【0001】**

**【発明の属する技術分野】**

この発明は、半導体集積回路装置に関し、小振幅の入力信号が供給される半導体集積回路装置の入力回路に利用して有効な技術に関するものである。

**【0002】**

**【従来の技術】**

小振幅の入力信号を受け、高速に動作する必要のある入力回路には、一般的には差動入力回路が用いられる。しかしながら、入力電圧 $V_{in}$ が、 $V_{in} < 2 \times V_{th}$ （差動MOSFET、電流源MOSFETのしきい値電圧）のように低くなると、差動MOSFETの共通ソースに設けられた電流源MOSFETの電流が減り、正常動作が行えないという問題を有する。 30

**【0003】**

**【発明が解決しようとする課題】**

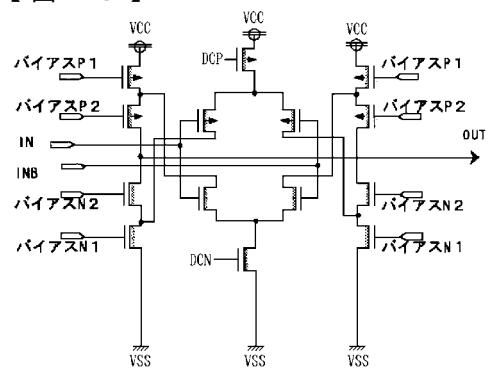

本願発明者においては、入力信号が電源電圧あるいは回路の接地電位にシフトしても動作を行うことができるレール・ツー・レール（rail-to-rail）は、米国モトラーラ社の登録商標である）回路に着目した。図13は、この発明に先立って検討されたレール・ツー・レール回路の回路図が示されている。この回路は、バイアスP1、P2、N1、N2及びDCP、DCNを必要とし、素子のプロセスバラツキ、例えばPチャネルMOSFETとNチャネルMOSFETの相互コンダクタンス比のバラツキ、入力電圧 $V_{in}$ のシフトを考慮すると、そのまま小振幅、高速入力回路として使用するのが難しい。 40

**【0004】**

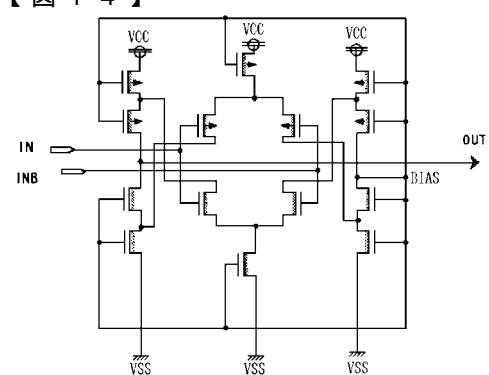

図14には、米国特許第4,958,133号公報によって提案されている自己バイアス型のレール・ツー・レール回路の回路図が示されている。また、雑誌「トランジスタ技術」2001年3月号第201頁には、オペアンプにレール・ツー・レール回路を用いた例が示されている。これらの回路は、オペアンプとして用いることができても、その信号伝達速度が遅いために、高速動作が要求されるスタティック型RAM（ランダム・アクセス・メモリ）のアドレス信号、クロック信号、各種制御信号を入力するための入力回路としては不向きである。

**【0005】**

この発明の目的は、低電圧まで安定的に高速動作が可能な入力回路を備えた半導体集積回

50

路装置を提供することにある。この発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

### 【0006】

#### 【課題を解決するための手段】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記の通りである。第1入力端子にそれぞれゲートが接続された第1導電型の第1差動MOSFET対及びその共通ソースに設けられて動作電流を形成する第1導電型の第1電流源MOSFETを第1増幅部とし、上記一対の第1入力端子にそれぞれゲートが接続された第2導電型の第2差動MOSFET対及びその共通ソースに設けられて動作電流を形成する第2導電型の第2電流源MOSFETを第2増幅部とし、上記第1差動MOSFET対に流れる電流を供給する第2導電型の第1MOSFET対を含む第1出力部、上記第2差動MOSFET対に流れる電流を供給する第1導電型の第2MOSFET対を含む第2出力部を設けて増幅回路を構成し、かかる増幅回路と同様な回路を用いてバイアス回路を構成し、その一対の出力端子を共通接続して中点に対応したバイアス電圧を形成し、上記増幅回路の第1ないし2電流源MOSFETのゲート及び第1ないし第2MOSFETのゲート及びバイアス回路の対応する電流源MOSFET及びMOSFETのゲートに供給する。

10

### 【0007】

#### 【発明の実施の形態】

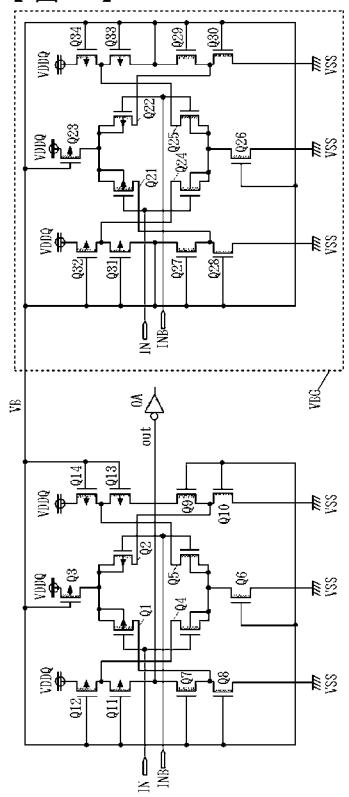

図1には、本発明に係る半導体集積回路装置に設けられる入力回路の一実施例の回路図が示されている。同図の各回路素子は、公知の半導体集積回路の製造技術によって、単結晶シリコンのような1個の半導体基板上において形成される。同図の回路は、NチャネルMOSFETとPチャネルMOSFETとからなるCMOS回路により構成され、PチャネルMOSFETは、そのバックゲート(チャネル)部に矢印を付すことによりNチャネルMOSFETと区別される。

20

### 【0008】

この実施例の入力回路は、前記レール・ツー・レール回路が利用される。すなわち、Pチャネル型の差動MOSFET Q1とQ2、その動作電流を形成するPチャネル型の電流源MOSFET Q3からなる第1増幅部と、Nチャネルの差動MOSFET Q4とQ5、その動作電流を流すNチャネル型の電流源MOSFET Q6により第2増幅部が構成される。上記Pチャネル型の電流源MOSFET Q3のソースは、電源電圧VDDQが与えられ、Nチャネル型の電流源MOSFET Q6のソースには、回路の接地電位VSSが与えられる。

30

### 【0009】

上記第1増幅部と第2増幅部の一方の差動MOSFET Q1とQ4のゲートは、第1入力端子INに接続される。上記第1増幅部と第2増幅部の他方の差動MOSFET Q2とQ5のゲートは、第2入力端子INBに接続される。これらの入力端子INとINBには、相補(非反転と反転)の入力信号が供給される。ここで、INBのBはバー(反転)信号であることを示している。

### 【0010】

上記第1差動部に対して、NチャネルMOSFET Q7～Q10からなる第1出力部が設けられ、上記第2差動部に対してPチャネルMOSFET Q11～Q14からなる第2出力部が設けられる。上記第1と第2出力部の一方である上記MOSFET Q7, Q8及びQ11, Q12が電源電圧VDDQと回路の接地電位VSSとの間には、カスコード(直列)形態に接続され、上記第1と第2出力部の他方である上記MOSFET Q9, Q10及びQ13, Q14が電源電圧VDDQと回路の接地電位VSSとの間には、カスコード形態に接続される。

40

### 【0011】

上記第1増幅部の差動MOSFET Q1とQ2のドレイン電流は、上記第1出力部のMOSFET Q8, Q10に流れるようにされる。同様に、第2増幅部の差動MOSFET Q4, Q5のドレイン電流は、上記第2出力部のMOSFET Q12, Q14に流れよう

50

にされる。上記第1出力部の一方のMOSFET Q7と、第2出力部の一方のMOSFET Q11は、いわばソース入力、ゲート接地型の増幅MOSFETとして動作し、ドレインが第1出力端子に接続される。同様に、上記第1出力部の他方のMOSFET Q9と、第2出力部の一方のMOSFET Q13も、上記同様に増幅MOSFETとして動作してドレインが第2出力端子に接続される。このような一対の出力端子のうち、特に制限されないが、第1出力端子の信号outが出力増幅回路OAに伝えられて、CMOSレベルの内部信号とされる。第2出力端子の信号を出力増幅回路に伝えてCMOSレベルの内部信号とすることもできる。

#### 【0012】

上記第2と第4の差動MOSFETの基板をソースに接続することで第2と第4の差動MOSFETのNBT劣化を防ぐことができる。 10

#### 【0013】

上記第1増幅部、第2増幅部の電流源MOSFET Q3とQ6、及び上記第1出力部と第2出力部のMOSFET Q7～Q14のゲートには、バイアス電圧VBが共通に接続される。このように、電流源MOSFET Q3、Q6及び上記第1出力部と第2出力部のMOSFET Q7～Q14のゲート共通のバイアス電圧を供給する構成は、前記図14に示した自己バイアス型のレール・ツー・レール回路と同様である。

#### 【0014】

この実施例では、前記図14のように増幅回路において自身がバイアス電圧BIASを形成する構成では、入力端子IN、INBの信号変化に対して負帰還がかかり、出力信号の変化速度が遅くなってしまうという問題を有する。つまり、本願発明にかかる半導体集積回路装置のように、高速で低振幅の入力信号を受ける入力回路には不向きなものとなる。 20

#### 【0015】

この実施例では、上記バイアス電圧VBが専用のバイアス回路VBGにより形成される。バイアス回路VBGは、上記入力回路と同じ回路により構成される。つまり、Pチャネル型の差動MOSFET Q21とQ22、その動作電流を形成するPチャネル型の電流源MOSFET Q23からなる第3増幅部と、Nチャネルの差動MOSFET Q24とQ25、その動作電流を流すNチャネル型の電流源MOSFET Q26により第4増幅部が構成される。

#### 【0016】

上記Pチャネル型の電流源MOSFET Q23のソースは、電源電圧VDDQが与えられ、Nチャネル型の電流源MOSFET Q6のソースには、回路の接地電位VSSが与えられる。上記第1増幅部と第2増幅部の一方の差動MOSFET Q1とQ4のゲートは、上記第1入力端子INに接続される。上記第1増幅部と第2増幅部の他方の差動MOSFET Q2とQ5のゲートは、上記第2入力端子INBに接続される。 30

#### 【0017】

上記第3差動部に対して、NチャネルMOSFET Q27～Q30からなる第3出力部が設けられ、上記第4差動部に対してPチャネルMOSFET Q31～Q34からなる第4出力部が設けられる。上記第3と第4出力部の一方である上記MOSFET Q27、Q28及びQ31、Q32が電源電圧VDDQと回路の接地電位VSSとの間にカスコード形態に接続され、上記第1と第2出力部の他方である上記MOSFET Q29、Q30及びQ33、Q34が電源電圧VDDQと回路の接地電位VSSとの間にカスコード形態に接続される。 40

#### 【0018】

上記第3増幅部の差動MOSFET Q21とQ22のドレイン電流は、上記第3出力部のMOSFET Q28、Q30に流れるようにされる。同様に、第4増幅部の差動MOSFET Q24、Q25のドレイン電流は、上記第4出力部のMOSFET Q32、Q34に流れるようにされる。上記第3出力部の一方のMOSFET Q27と、第4出力部の一方のMOSFET Q31のドレインは第3出力端子に接続される。同様に、上記第1出力部の他方のMOSFET Q29と、第2出力部の他方のMOSFET Q33も、上記同様に

ドレインが第4出力端子に接続される。このような一対の出力端子は、相互に接続されてバイアス電圧V<sub>B</sub>を形成する。

#### 【0019】

つまり、相補の出力端子同士を接続して、入力端子INとINBに対応した出力信号のハイレベルとロウレベルの中間電圧を形成し、それをバイアス電圧V<sub>B</sub>とし、電流源MOSFET Q23とQ26のゲートと、上記MOSFET Q27～Q34のゲートに供給される。

#### 【0020】

上記バイアス回路V<sub>BG</sub>に対しても、入力端子INとINBに対応した相補の入力信号が形成され、かかる入力信号に対応した相補の出力信号を形成する出力端子同士を相互に接続することにより、相補出力信号が一致するように電流源MOSFET Q23、Q26及びカスコード部のMOSFET Q27～Q34のゲートに供給されるバイアス電圧V<sub>B</sub>を形成します。この電圧V<sub>B</sub>を入力回路を構成する上記電流源MOSFET Q3、Q6及びカスコード部のMOSFET Q7～Q14のゲートに供給することにより、入力回路においては、入力端子INとINBに対応してハイレベル／ロウレベルに変化するような出力信号を形成する。そのうちの一方の出力信号outをCMOSインバータ回路等の出力增幅回路OAにより増幅してCMOSレベルの内部信号を形成することができる。

#### 【0021】

入力回路においては、出力信号のレベルを決める信号伝達動作において、上記バイアス電圧V<sub>B</sub>を形成するための負帰還動作を行わないから、入力端子INとINBから入力された入力信号に対応した出力信号outを形成する信号伝達動作を高速に行うようにすることができる。

#### 【0022】

図2には、本発明に係る半導体集積回路装置に設けられる入力回路の他の一実施例の回路図が示されている。この実施例の入力回路は、前記図1と同じ回路が用いられる。ただし、一対の入力端子のうちの一方の入力端子INには、入力信号が供給され、前記図1の入力回路では反転の入力信号が供給される入力端子INBに対応した入力端子は、上記入力信号のハイレベル／ロウレベルを判定する参照電圧VREFが供給される参照電圧端子とされる。

#### 【0023】

このような参照電圧VREFを用いた入力回路に供給されるバイアス電圧V<sub>B</sub>を形成するバイアス回路V<sub>BG</sub>では、一対の入力端子が共に参照電圧VREFが供給される参照電圧端子とされる。素子にバラツキがなければ、同じ参照電圧VREFが供給されるので、一対の出力信号も同じくなるはずであるが、実際には差動ペア素子でのオフセット、出力MOSFETでも同様なオフセットを持つので、かかるオフセットを補償するようなバイアス電圧V<sub>B</sub>が形成され、それが上記入力回路の対応するMOSFETに供給される。これにより、シングル構成の入力回路においても、動作の高速化と安定化を実現することができる。

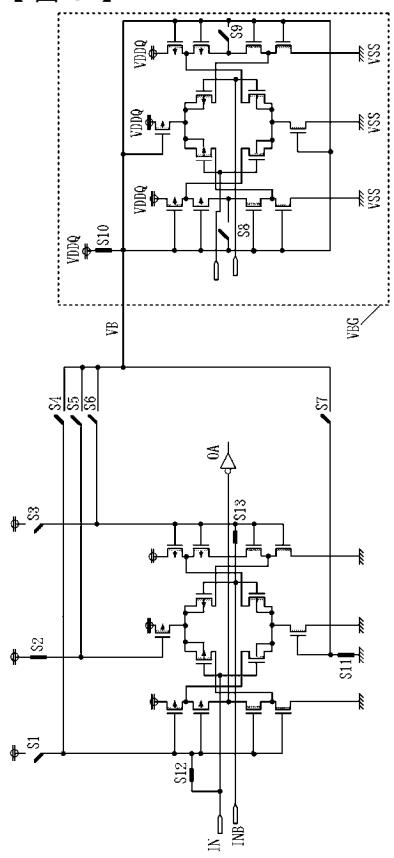

#### 【0024】

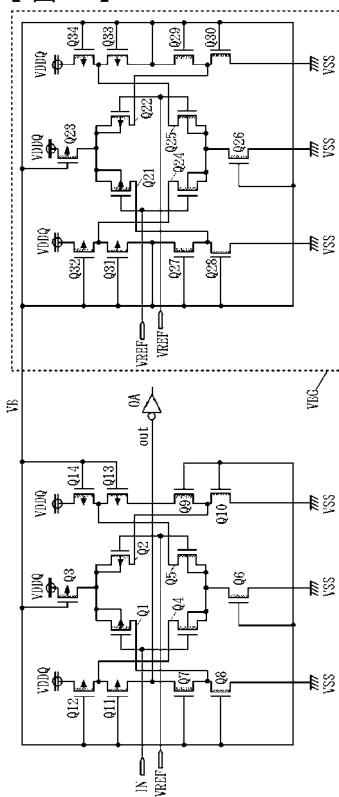

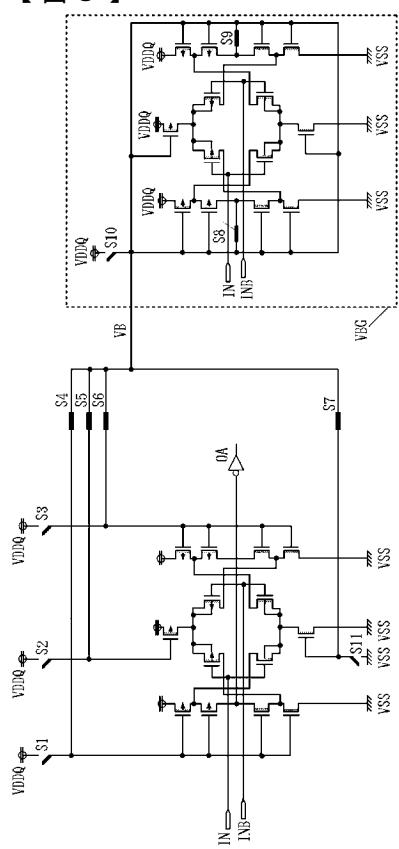

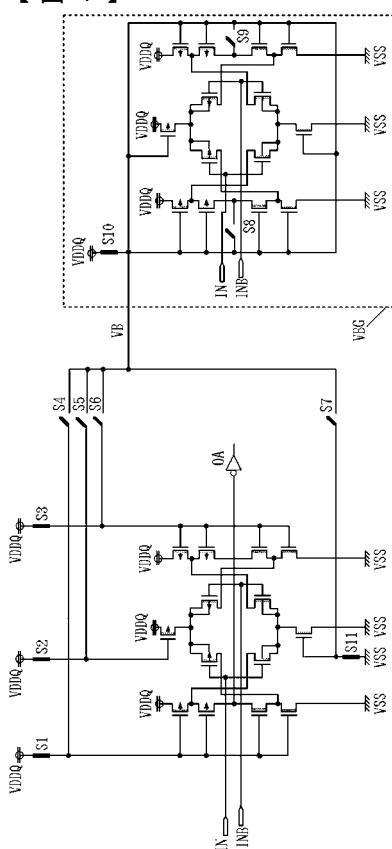

図3と図4には、本発明に係る半導体集積回路装置に設けられる入力回路の他の一実施例の回路図が示されている。この実施例の入力回路は、前記図1の実施例の改良に係るものであり、図1の実施例回路に対してスイッチS1～S11が付加されて、図3、図4の実施例が構成される。このうち、図3には、半導体集積回路装置が通常の動作を行うノーマルモード時のスイッチS1～S11の状態が示され、図4には、半導体集積回路装置が動作を行わないスタンバイモード時のスイッチS1～S11の状態が示されている。

#### 【0025】

図3、図4において、入力回路は、カスコード部が2つに分けられて、それぞれにスイッチS1、S4と、スイッチS3とS6が設けられる。また、Pチャネル型とNチャネル型の電流源MOSFETにもスイッチS2、S5と、スイッチS11とS7が設けられる。上記スイッチS1～S3は、電源電圧VDDQに選択的に接続するために設けられ、スイ

10

20

30

40

50

スイッチ S 11 は回路の接地電位 VSS に選択的に接続するために設けられる。そして、スイッチ S 4 ~ S 6 は、バイアス回路 VBG で形成されたバイアス電圧 VB を選択的に伝えるために設けられる。バイアス回路 VBG においても、カスコード部が 2 つに分けられて、それぞれにスイッチ S 8、S 9 が設けられて、それぞれの出力端子と選択的に接続される。2 つのカスコード部の MOSFET の共通接続されたゲートに対して、電源電圧 VDDQ に選択的に接続するためのスイッチ S 10 が設けられる。

#### 【0026】

図 3 のノーマルモードでは、スイッチ S 1 ~ S 3、S 11 はオフ状態にされ、スイッチ S 4 ~ S 7 はオン状態にされる。これにより、入力回路は、前記図 1 の入力回路と同じ接続構成とされる。バイアス回路 VBG は、スイッチ S 8 と S 9 がオン状態にされ、スイッチ S 10 がオフ状態にされる。これにより、バイアス回路 VBG は、前記図 1 のバイアス回路と同じ接続構成とされる。この結果、図 1 の実施例と同様に動作して、バイアス回路 VBG は入力端子 IN と INB に対応したバイアス電圧 VB を形成する。入力回路は上記バイアス回路で形成されたバイアス電圧 VB により動作し、入力端子 IN と INB から供給される入力信号に対応した信号 out を形成する。

10

#### 【0027】

図 4 のスタンバイモードでは、上記図 3 とは逆に、スイッチ S 1 ~ S 3、S 11 はオン状態にされ、スイッチ S 4 ~ S 7 はオフ状態にされる。これにより、入力回路のカスコード部の MOSFET のゲートには、バイアス電圧 VB に代えて電源電圧 VDDQ が供給されて P チャネル MOSFET がオフ状態にされ、P チャネル電流源 MOSFET には上記電源電圧 VDDQ が供給されてオフ状態にされ、N チャネル電流源 MOSFET には回路の接地電位 VSS が供給されてオフ状態にされる。したがって、入力回路においては、電源電圧 VDDQ と回路の接地電位 VSS との間で電流経路が形成されないので低消費電力となる。

20

#### 【0028】

バイアス回路 VBG においても、前記図 3 と逆に、スイッチ S 8 と S 9 がオフ状態にされ、スイッチ S 10 がオン状態にされる。これにより、バイアス回路 VBG は、P チャネル MOSFET が全てオフ状態にされるので、上記電源電圧 VDDQ によって、N チャネル電流源 MOSFET がオン状態となり、カスコード部の N チャネル MOSFET がオン状態となっても、電源電圧 VDDQ と回路の接地電位 VSS との間で電流経路が形成されないので低消費電力となる。このように、スタンバイモードでは、入力回路及びバイアス回路で直流電流が発生しないから低消費電力となる。ただし、オフ状態の P チャネル MOSFET に流れるリーク電流は無視するものとする。

30

#### 【0029】

この実施例のように、スタンバイモードにおいて、カスコード部の各 MOSFET に対して電源電圧 VDDQ を供給する構成は、P チャネル MOSFET をオフ状態にさせるものであり、P チャネル MOSFET をオン状態にさせるようにゲートと基板（チャネル間）に電圧を供給した場合に生じる NBTI (Negative Bias Temperature Instability) 劣化を防止する上で効果的である。また、差動 MOSFET の基板（チャネル）とソースとを接続する構成は、上記 NBTI 劣化を防止する上で有益である。このため、差動 MOSFET は、それぞれが電気的に独立したウェル領域に形成される。

40

#### 【0030】

図 5 には、本発明に係る半導体集積回路装置に設けられる入力回路の更に他の一実施例の回路図が示されている。この実施例の入力回路は、前記レール・ツー・レール回路と、CMOS 回路との 2 通りの入力動作に切り換えることが可能な機能が付加される。前記図 3 (図 4) の回路において、入力端子 IN と、出力信号を形成するカスコード部の各 MOSFET のゲートとの間に、スイッチ 12 が設けられる。同様に、他方のカスコード部の MOSFET のゲートと、それに対応した入力端子 INB との間にスイッチ 13 が設けられる。

#### 【0031】

50

同図には、CMOS入力モードの様子が示されており、スイッチS1、S3はオフ状態にされ、スイッチS2とS11はオン状態にされる。他のスイッチS4～S10の状態は、前記図4のスタンバイモードのときと同様であり、バイアス回路は回路動作が停止されて低消費電力状態になる。

#### 【0032】

入力回路においては、2つの差動回路の電流源MOSFETがそれぞれオフ状態にされて差動回路には電流が流れなくされる。したがって、スイッチS12のオン状態により、入力端子INの入力信号は、カスコード接続のMOSFETのゲートに共通に供給される。この構成は、2つのPチャネルMOSFETと2つのNチャネルMOSFETとが直列接続されており、それらのゲートに入力信号が供給され、NチャネルMOSFETとPチャネルMOSFETのドレイン接続点から出力信号を得るので上記カスコード部は、CMOSインバータ回路と等価の動作を行うものとされる。10

#### 【0033】

入力端子INBからの入力信号も、スイッチS13を通して他方のカスコード接続のMOSFETのゲートに共通に供給される。それ故、かかるカスコード接続のMOSFETもCMOSインバータ回路と等価となって、その出力端子から出力信号を形成し、図示しない内部回路に取り込んだ入力信号を伝えることができる。なお、入力端子INの入力信号に対して、入力端子INBの入力信号が反転信号の場合には、わざわざ2つの入力回路（カスコード接続のMOSFET）を用いて、それぞれを入力する必要はない。例えば、バー信号の場合には、入力端子INBを用い、テュルー信号の場合には入力端子INを用いるようにいずれか一方を選択的に使用すればよい。20

#### 【0034】

上記のスイッチS1～S13は、例えばMOSFETにより構成される。MOSFETの持つしきい値電圧により、入力された電圧がそのまま出力できない場合には、PチャネルMOSFETとNチャネルMOSFETを並列接続して、それらを制御信号に従ってオン／オフさせるようにするCMOSスイッチを用いるようにすればよい。

#### 【0035】

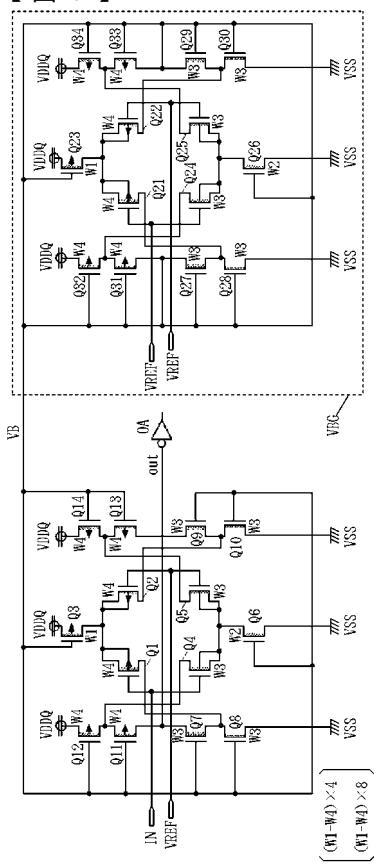

図6には、本発明に係る半導体集積回路装置に設けられる入力回路の更に他の一実施例の回路図が示されている。この実施例は、前記図2の実施例と基本的には同じである。この実施例では、入力回路のPチャネル差動MOSFETQ1とQ2、カスコード部のPチャネルMOSFETQ11～Q14は、そのチャネル幅がW4のように同一に形成される。また、入力回路のNチャネル差動MOSFETQ4とQ5、カスコード部のPチャネルMOSFETQ7～Q10は、そのチャネル幅がW3のように同一に形成される。30

#### 【0036】

上記Pチャネル差動MOSFETQ1とQ2の動作電流を形成するPチャネルMOSFETQ3は、そのチャネル幅がW3のように同じPチャネルの前記他のMOSFETQ1、Q2等のチャネル幅W4よりも小さく形成され、言い換えるならば、オン抵抗値が大きく形成される。同様に、上記Nチャネル差動MOSFETQ4とQ5の動作電流を形成するPチャネルMOSFETQ6は、そのチャネル幅がW2のように同じNチャネルの前記他のMOSFETQ4、Q5等のチャネル幅W3よりも小さく形成され、言い換えるならば、オン抵抗値が大きく形成される。バイアス回路VBGにおいても、MOSFETQ21～Q34は、対応する入力回路の前記MOSFETQ1～Q14と同じくチャネル幅がW1～W4のようにそれぞれ形成される。40

#### 【0037】

差動増幅部において、電流源MOSFETQ3（Q23）及びQ6（Q26）のオン抵抗値を大きくした理由は、それに対応した差動MOSFETQ1とQ2（Q21とQ22）のドレイン電位の変化を小さくするためである。つまり、Nチャネル差動MOSFETQ4とQ5においては、そのドレイン電位の低電圧側への落ち込みを制限し、Pチャネル差動MOSFETQ1とQ2においては、そのドレイン電位の浮き上がりを制限する。

#### 【0038】

このような差動増幅部でのドレイン電位の変動を小さくすることにより、信号切り替わりを高速にするものである。つまり、一般的な差動回路のように差動MOSFETと、その動作電流を形成する電流源MOSFETと同じサイズとした場合には、そのオン抵抗値も同様となって、差動入力に対して相対的にオン状態にせされるMOSFETのドレイン電位の落ち込み又は浮き上がりが大きくなる。例えば、差動MOSFET Q4がオン状態に、MOSFET Q5がオフ状態のときに上記MOSFET Q4のドレイン電圧の落ち込みが大きいと、入力信号が変化して出力レベルの切り換えを行うとき、上記ドレイン電圧の落ち込みはカスコード部の電流源MOSFET Q12でしか回復させることができなく、このMOSFET Q12はカスコード部の増幅MOSFET Q11へも電流を供給するので上記ドレイン電圧の落ち込みの回復に時間がかかるてしまう。

10

#### 【0039】

つまり、差動MOSFET Q4がオン状態からオフ状態に切り換えられ、MOSFET Q12の電流は増幅MOSFET Q11に供給されて、上記差動MOSFET Q4がオン状態のときの反転信号を形成する動作を行わなければならないのに、上記MOSFET Q4のドレインの寄生容量を充電するためにも使われることとなって出力の切り換えを遅くしてしまう。

#### 【0040】

これに対して、本願発明のように差動MOSFET Q1とQ2(Q4とQ5)に対して、電流源MOSFET Q3(Q6)のオン抵抗値を大きくするという単純な構成により、上記差動MOSFET Q1とQ2(Q4とQ5)のドレイン電圧の変化幅を小さくでき、結果として上記のような出力切り換えを高速に行うことが可能となる。つまり、入力信号の伝達速度を高速に行うようにすることができる。

20

#### 【0041】

この実施例のように、入力回路とバイアス回路とにおいて、対応するMOSFETのサイズをW1～W4のように互いに等しくした場合を基準にし、入力回路側の各MOSFETのサイズを(W1～W4)×4のようにそれぞれを4倍にすると、各MOSFETに流れる電流も4倍となり、信号伝達速度を高速にすることができます。この場合には、入力回路側のみに大きな電流が流れ、バイアス回路は少なくてよいのでノーマルモードでの効率的に電流を使用することができる。

#### 【0042】

30

また、入力回路とバイアス回路とにおいて、対応するMOSFETのサイズをW1～W4のように互いに等しくした場合を基準にし、入力回路側の各MOSFETのサイズを(W1～W4)×8のようにそれぞれを8倍にすると、各MOSFETに流れる電流も8倍となり、いっそうの信号伝達速度を高速にすることができます。この場合には、入力回路側のみに大きな電流が流れ、バイアス回路は少なくてよいのでノーマルモードでの効率的に電流を使用することができる。

#### 【0043】

例えば、後述するようなシンクロナスSRAMにおいて、クロック信号CLK, CLKBを入力する入力回路には、前記(W1～W4)×8のようなMOSFETを用い、制御信号S, WE, WE×等は前記(W1～W4)×4のようなMOSFETを用い、アドレス信号A0～A18・ASやDQ0～DA35は、(W1～W4)×1のようにバイアス回路VBGと等倍にするよう、それぞれの入力信号の要求される伝達速度に対応した3段階の使い分けに利用できる。

40

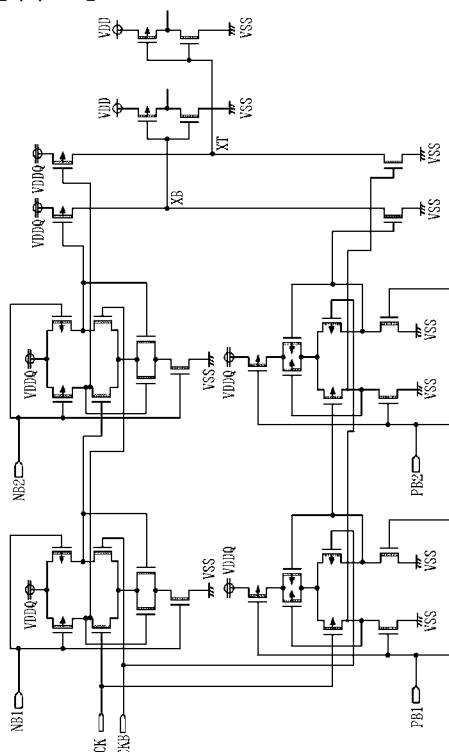

#### 【0044】

図7には、本発明に係る半導体集積回路装置に設けられる入力回路の更に他の一実施例の回路図が示されている。この実施例は、前記のようなレール・ツー・レール回路ではなく、Nチャネル差動MOSFET、Nチャネル電流源MOSFET及びPチャネル負荷MOSFETにより第1差動増幅回路を構成し、同様にPチャネル差動MOSFET、Pチャネル電流源MOSFET及びNチャネル負荷MOSFETにより第2差動増幅回路を構成し、上記第1と第2の差動増幅回路の入力端子を共通にして入力端子CK, CKBに接

50

続する。

**【0045】**

特に制限されないが、電流源MOSFETと差動MOSFETの共通ソースとの間には、差動MOSFETのドレイン出力をそれぞれのゲートに受け、並列形態にされた2つのMOSFETが設けられる。これらのMOSFETは、出力信号の変動を小さくするような負帰還動作を行うために設けられる。

**【0046】**

上記第1及び第2差動増幅回路のそれぞれに対して、それぞれ同様な第3及び第4差動増幅回路が設けられ、Nチャネル差動MOSFETを持つ第1と第3差動増幅回路とが縦列形態に接続され、Pチャネル差動MOSFETを持つ第2と第4差動増幅回路とが縦列形態に接続されて、それぞれにおいて2段増幅動作を行うようにされる。10

**【0047】**

そして、第3増幅回路の出力信号はPチャネルの出力MOSFETのゲートに供給され、第4増幅回路の出力信号はNチャネルの出力MOSFETのゲートに供給され、上記Pチャネル出力MOSFETとNチャネル出力MOSFETとの相補の増幅信号の対応するもの同士が直列形態に接続されて反転出力信号XBと非反転出力信号XTを形成する。これらの出力信号XBとXTは、CMOSインバータ回路を通して相補信号として内部回路に取り込まれる。

**【0048】**

上記第1ないし第4差動増幅回路のそれぞれは、電流源MOSFETのゲートに供給されるバイアス電圧と、それと反対導電型の負荷MOSFETのゲートに供給されるバイアス電圧とが同電位にされる。これらのバイアス電圧は、次に説明するようなバイアス回路により形成される。20

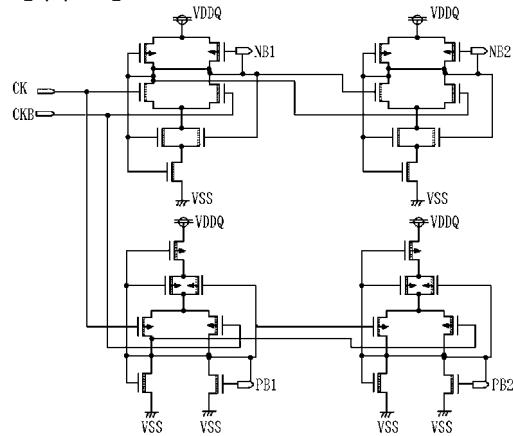

**【0049】**

図8には、図7の入力回路に用いられるバイアス回路の一実施例の回路図が示されている。バイアス回路は、前記図7の第1ないし第4差動増幅回路の電流源MOSFETと負荷MOSFETに供給される4通りのバイアス電圧NB1、PB1、NB2、PB2を形成する。

**【0050】**

バイアス回路は、前記レール・ツー・レール回路に設けられたバイアス回路と同様に、30 入力回路と同じ回路構成のものが用いられる。つまり、前記図7の入力回路の第1ないし第4差動増幅回路と同じ回路構成にされた4つの差動増幅回路が用いられる。前段の2つの差動増幅回路には、それぞれ入力回路と同じく入力端子CKとCKBに接続される。前段の差動増幅回路の差動出力が後段の差動増幅回路の入力端子に接続されるまでは前記入力回路と同様である。

**【0051】**

上記バイアス回路を構成する4つの差動増幅回路は、それぞれの差動MOSFETのドレイン出力が共通に接続される。上記4つの差動増幅回路のそれぞれにおいては、相補の出力端子を相互に接続して等しい電圧になるように、自身の負荷MOSFET及び電流源MOSFETを制御しつつ、4通りのバイアス電圧NB1、NB2、PB1、PB2を形成する。これにより、Nチャネル差動MOSFETと、Pチャネル差動MOSFETを用いて、電源電圧と回路の接地電位の範囲内で変化する入力信号に応答できる入力回路の動作の高速化と安定化を実現することができる。40

**【0052】**

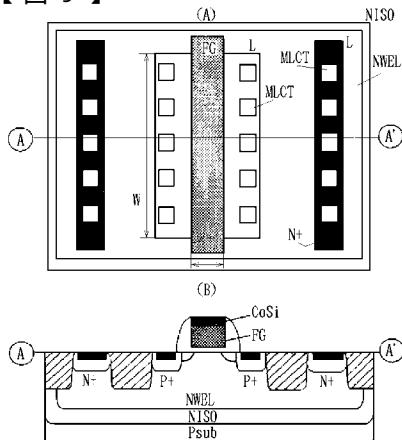

図9には、この発明に用いられるPチャネルMOSFETの一実施例の素子構造図が示されている。図9(A)には平面構造が、図9(B)には断面構造が示されている。PチャネルMOSFETは、N型ウェルNWE Lにおいて、基板上に薄いゲート絶縁膜を介して形成されたゲート電極FGを挟むようにソース、ドレインを構成するP+型半導体領域Lが形成される。NウェルNWE Lには、ウェルバイアス電圧を供給するためにN+半導体領域が設けられる。ここで、前記図6で示したゲート幅Wは、ゲート、ソース及びドレイ50

ンが平行に並ぶ方向のソース，ドレイン拡散層の長さをいう。また、ゲート長 $L_g$ は、チャル電流が流れる長さであり、ソース，ドレインの間隔に対応している。

#### 【0053】

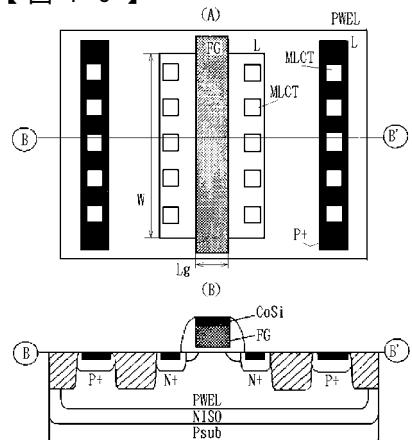

図10には、この発明に用いられるNチャネルMOSFETの一実施例の素子構造図が示されている。図10(A)には平面構造が、図10(B)には断面構造が示されている。NチャネルMOSFETは、P型ウェルNWEELにおいて、薄いゲート絶縁膜を介して形成されたゲート電極FGを挟むようにソース，ドレインを構成するN+型半導体領域Lが形成される。PウェルPWELには、ウェルバイアス電圧を供給するためにP+半導体領域が設けられる。ゲート幅Wとゲート長 $L_g$ は、上記図9と同様である。

#### 【0054】

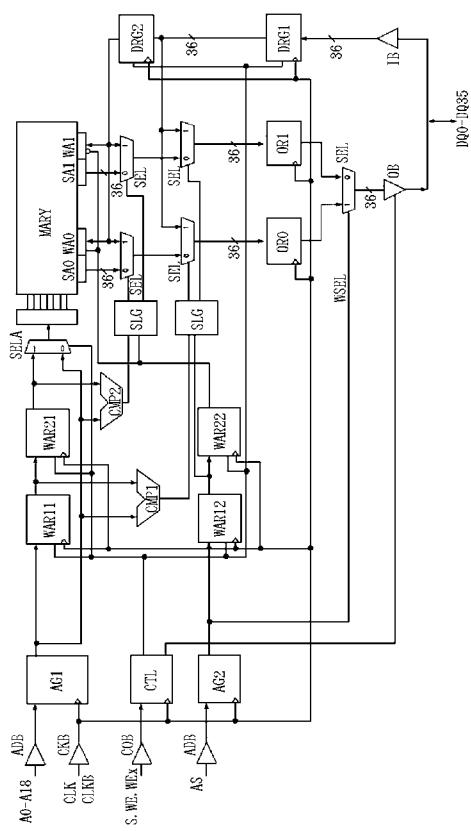

図11には、この発明が適用されるシンクロナスSRAM(以下、単にSSRAMという)の一実施例のブロック図が示されている。この実施例のシンクロナスSRAMは、公知のCMOS集積回路の製造技術により、単結晶シリコンのような1つの半導体基板上において形成される。

#### 【0055】

この実施例のSSRAMは、アドレス端子A0～A18とウェイセレクト用アドレスASからなる20ビットによって約1M(メガ)のアドレス空間を持つ。データ端子DQ0～DQ35により36ビットずつパラレルに読み出しと書き込みが行われるから、メモリアレイMARYには約36Mビットの記憶容量をもつようになる。メモリアレイMARYは、スタティック型メモリセルがワード線と相補のビット線との交点にマトリクス配置されて構成される。

#### 【0056】

上記アドレス端子A0～A18のアドレス信号は、アドレスバッファADBを通してアドレスレジスタAG1に取り込まれる。非反転と反転からなる相補のクロック信号CLK、CLKBはクロックバッファCKBを通して取り込まれる。そして、リード/ライト制御のための制御信号S, WE, WExはコントロールバッファCOBを通して取り込まれる。また前記セレクト信号ASもアドレスバッファADBを通してアドレスレジスタAG2に取り込まれる。データ端子DQ0～DQ35からの書き込みデータに対応して入力バッファIBが設けられる。

#### 【0057】

したがって、前記実施例の入力回路はこれら各種入力回路に適用される。特に、前記図6の実施例において、アドレスバッファADBやデータ入力バッファIBは、図6の実施例回路が用いられ、コントロールバッファCOBは、バイアス回路の対応するMOSFETに対してゲート幅Wが4倍にされたMOSFETにより入力回路が構成される。更に、最高速度が要求されるクロックバッファCKBは、バイアス回路に対してゲート幅Wが8倍にされたMOSFETにより入力回路が構成される。

#### 【0058】

アドレスレジスタAG1は、読み出し動作のときにはセレクタSEL AによりメモリアレイMARYのデコーダに伝えられる。書き込み動作のときには、書き込みアドレスレジスタWAR11、WAR21によって時間調整が行われてセレクタを通して上記デコーダに伝えられる。同様に、ウェイセレクト用のアドレスASも、同様なレジスタWAR12、WAR22によって時間調整が行われる。書き込み動作では、書き込みアドレスとそれに対応した書き込みデータとに1サイクルのずれがあるので、上記書き込みアドレスレジスタによってその調整が行われる。

#### 【0059】

特に制限されないが、メモリアレイMARYは、上記アドレス信号A0～A18によって、 $36 \times 2 = 72$ ビット分のデータがウェイ0(SA0)とウェイ1(SA1)によって読み出される。書き込みデータは、データレジスタDRG1, DRG2を通してメモリアレイMARYのライトアンプWA0, WA1に伝えられる。上記センスアンプSA0, SA1の読み出しデータと、データレジスタDRG2の書き込みデータとは、セレクタによ

10

20

30

40

50

り選択され、さらにその出力とデータレジスタ D R G 1 の書き込みデータとがセレクタにより選択された出力レジスタ O R 0 , O R 1 に伝えられる。

#### 【 0 0 6 0 】

上記セレクタの選択信号は、選択制御回路 S L G により形成される。この 2 つの出力レジスタ O R 0 と O R 1 に伝えられたデータのうち、一方が上記ウェイアドレス A S に対応したウェイセレクト信号 W S E L により選択されて、出力バッファ O B を通して出力される。選択制御回路 S L G は、書き込みアドレスレジスタ W A R 1 1 、 W A R 2 1 の書き込みアドレスと、入力されたアドレスとを比較するコンパレータ C M P 1 , C M P 2 の信号と、上記書き込みアドレスレジスタ W A R 1 2 、 W A R 2 2 のウェイセレクト用アドレスとを参照して上記選択信号を形成する。

10

#### 【 0 0 6 1 】

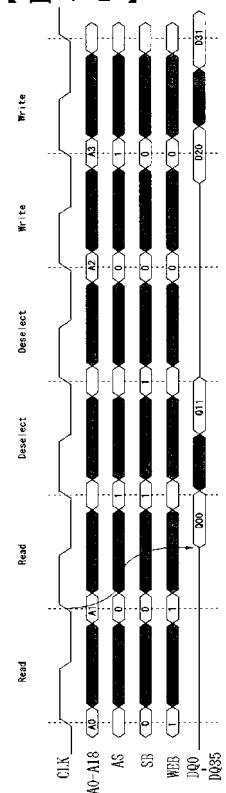

図 1 2 には、図 1 1 の S S R A M の動作の一例を説明するためのタイミング図が示されている。セレクト信号 S B のロウレベル（論理 0 ）と、ライトイネーブル信号 W E B のハイレベル（論理 1 ）によりリードサイクルとされ、アドレス信号 A 0 - A 1 8 によりアドレス A 0 が取り込まれて前記 2 ウェイ分のデータが読み出される。第 2 サイクルで同様にリードサイクルとされ、アドレス信号 A 0 - A 1 8 によりアドレス A 1 が取り込まれ前記 2 ウェイ分のメモリセルの選択動作が行われる。1 サイクル遅れてウェイアドレス A S のロウレベル（論理 0 ）が入力されてウェイ 0 が指定されると、データレジスタ D R 0 に取り込まれているウェイ 0 に対応したデータ Q 0 0 が出力される。第 3 サイクルでセレクト信号 S B のハイレベル（論理 1 ）とすると、そのサイクルは非選択サイクルとされるが、そのときにウェイアドレス A S のハイレベル（論理 1 ）が入力されて、前記アドレス A 1 に対応して読み出されているウェイ 1 に対応したデータ Q 1 1 が出力される。

20

#### 【 0 0 6 2 】

第 5 サイクル目で、セレクト信号 S B のロウレベル（論理 0 ）と、ライトイネーブル信号 W E B のロウレベル（論理 0 ）によりライトサイクルとされ、アドレス信号 A 0 - A 1 8 によりアドレス A 2 とウェイアドレス A S のロウレベル（論理 0 ）が取り込まれる。第 6 サイクル目で同様にライトサイクルとされ、アドレス信号 A 0 - A 1 8 によりアドレス A 3 とそれに対応したウェイアドレス A S のハイレベル（論理 1 ）が取り込まれ、上記アドレス A 2 とウェイアドレスの 0 に対応した書き込みデータ D 2 0 が入力される。上記ライトサイクルの間にもリードサイクルの挿入が可能とされ、その調整のためにアドレスレジスタ、ライトデータレジスタ、コンパレータ等が用いられる。

30

#### 【 0 0 6 3 】

このような S S R A M において、メモリセル等は最小加工寸法により M O S F E T のゲート長 L g が形成される。例えば、0 . 1 2 μ m プロセスの加工寸法によりメモリセルを構成する M O S F E T が形成される場合、前記入力回路（バイアス回路）の M O S F E T の寸法は、それよりも大きく形成される。この理由は、上記のような最小加工寸法で形成した場合に、ゲート長 L g のバラツキによる影響が大きくしきい値電圧の変動幅も大きくなる。

#### 【 0 0 6 4 】

例えば、図 1 において入力回路の差動 M O S F E T Q 1 , Q 2 ( Q 4 , Q 6 ) 、電流源 M O S F E T Q 3 ( Q 6 ) 及び負荷 M O S F E T Q 8 , Q 1 0 ( Q 1 2 , Q 1 4 ) は、ゲート長 L g を最小加工寸法の約 2 倍の 0 . 2 5 μ m のように大きく形成される。そして、カスケード部の M O S F E T のうち、上記負荷（電流源）としての M O S F E T Q 8 , Q 1 0 ( Q 1 2 , Q 1 4 ) は上記のように大きく形成されるが、増幅用の M O S F E T Q 7 , Q 9 ( Q 1 1 , Q 1 3 ) はゲート長 L g が 0 . 1 6 μ m のように小さく形成される。

40

#### 【 0 0 6 5 】

上記 M O S F E T Q 7 , Q 9 ( Q 1 1 , Q 1 3 ) のゲート長 L g を小さくすることにより、そのゲート容量、つまりはゲート電極とチャネル間の容量を小さくすることができる。これにより、カスコード部の出力信号経路における寄生容量が小さくなり、寄生容量の充放電によって形成される出力信号電圧 o u t の変化を高速にすることができる。

50

**【0066】**

差動増幅回路においては、前記のように差動MOSFETと電流源MOSFETのチャネル長 $L_g$ は等しく形成されるが、図6の実施例のように差動MOSFET Q1とQ2(Q4とQ5)のゲート幅W4(W3)に対して、電流源MOSFET Q3(Q6)のゲート幅W1(W2)のように小さく形成される。これにより、前記のように差動MOSFETのドレイン電圧の変化幅を小さくでき、伝達信号の切り換えを高速に行うことができるものである。

**【0067】**

S S R A Mにおいて、例えば動作電源電圧VDDQを1.2Vのように低い電圧まで動作可能にする場合、入力回路やバイアス回路のMOSFETは0.4Vのような低しきい値電圧に形成される。このような低しきい値電圧にするために、図9、図10の素子構造において、イオン打ち込み技術等によるゲート電極FG下の半導体基板表面にウェルと反対導電型の不純物の導入制御によって設定される。10

**【0068】**

上記のようなMOSFETのサイズのゲート長 $L_g$ 、ゲート幅W設定は、前記実施例のレール・ツー・レール回路の他に、前記図13や図14の示されたレール・ツー・レール回路にも適用することによって、高速化や動作の安定化を図るようにすることができる。

**【0069】**

S S R A Mにおいて、CMOSレベルの入力信号を受ける論理回路等においては、MOSFETのオフ状態でのリーク電流又はスレッショルドリーク電流を低減させるために、そのしきい値電圧は前記入力回路、バイアス回路のMOSFETよりも大きく、例えば0.6V程度の高しきい値電圧に設定される。このように、半導体集積回路装置において2種類のしきい値電圧を持つMOSFETを形成する場合、イオン打ち込み技術等によるゲート電極FG下の半導体基板表面の不純物の制御によって設定される。20

**【0070】**

以上本発明者よりなされた発明を実施例に基づき具体的に説明したが、本願発明は前記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。例えば、図2の実施例において、各入力回路のそれぞれに対してバイアス回路を設けるもの他、1つの入力回路に代表させてバイアス回路を動作させ、それにより形成されたバイアス電圧を複数の入力回路に供給する構成としてもよい。個々の入力回路に一対一に対応してバイアス回路を設ける構成は、それに供給される入力信号に対応した最適なバイアス電圧を形成することができる反面、回路規模が大きくなる。これに対して、図2のように参照電圧VREFは全入力回路において共通であるので、1つのバイアス回路で代表させて複数の入力回路に供給する構成は、回路が簡素化できる。30

**【0071】**

この発明は、入力信号の周波数が約1GHzを超える、内部回路がCMOS構成の半導体集積回路装置に有益なものとなる。入力信号の周波数が約1GHzを超えるようになると、容量反射で入力信号の振幅が小さくなり、データ有効時間も小さくなり、入力電位の中心がずれてくる傾向にあるので、かかる入力信号を受ける入力回路として前記実施例の入力回路は好適なものとなる。あるいは、入力信号振幅がCMOS振幅よりも小さい、内部回路がCMOS回路により構成される各種半導体集積回路装置に適用して好適なものとなる。40

**【0072】****【発明の効果】**

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。一対の第1入力端子にそれぞれゲートが接続された第1導電型の第1差動MOSFET対及びその共通ソースに設けられて動作電流を形成する第1導電型の第1電流源MOSFETを第1増幅部とし、上記一対の第1入力端子にそれぞれゲートが接続された第2導電型の第2差動MOSFET対及びその共通ソースに設けられて動作電流を形成する第2導電型の第2電流源MOSFETを第2増幅部とし、上記第1差動M50

O S F E T 対に流れる電流を供給する第 2 導電型の第 1 M O S F E T 対を含む第 1 出力部、上記第 2 差動M O S F E T 対に流れる電流を供給する第 1 導電型の第 2 M O S F E T 対を含む第 2 出力部を設けて増幅回路を構成し、かかる増幅回路と同様な回路を用いてバイアス回路を構成し、その一対の出力端子を共通接続して中点に対応した電圧を形成し、かかる電圧を上記増幅回路の第 1 ないし 2 電流源M O S F E T のゲート及び第 1 ないし第 2 M O S F E T のゲート及びバイアス回路の対応する電流源M O S F E T 及びM O S F E T のゲートに供給することにより、電源電圧と回路の接地電位の範囲内で変化する入力信号に応答できる入力回路の動作の高速化と安定化を実現することができる。

【図面の簡単な説明】

【図 1】本発明に係る半導体集積回路装置に設けられる入力回路の一実施例を示す回路図である。 10

【図 2】本発明に係る半導体集積回路装置に設けられる入力回路の他の一実施例を示す回路図である。

【図 3】本発明に係る半導体集積回路装置に設けられる入力回路の他の一実施例を示す回路図である。

【図 4】本発明に係る半導体集積回路装置に設けられる入力回路の他の一実施例を示す回路図である。

【図 5】本発明に係る半導体集積回路装置に設けられる入力回路の更に他の一実施例を示す回路図である。

【図 6】本発明に係る半導体集積回路装置に設けられる入力回路の更に他の一実施例を示す回路図である。 20

【図 7】本発明に係る半導体集積回路装置に設けられる入力回路の更に他の一実施例を示す回路図である。

【図 8】図 7 の入力回路に用いられるバイアス回路の一実施例を示す回路図である。

【図 9】この発明に用いられるPチャネルM O S F E T の一実施例を示す素子構造図である。

【図 10】この発明に用いられるNチャネルM O S F E T の一実施例を示す素子構造図である。

【図 11】この発明が適用されるS S R A M の一実施例を示すブロック図である。

【図 12】図 11 のS S R A M の動作の一例を説明するためのタイミング図である。 30

【図 13】この発明に先立って検討されたレール・ツー・レール回路の回路図である。

【図 14】従来の自己バイアス型のレール・ツー・レール回路の回路図である。

【符号の説明】

Q 1 ~ Q 3 4 ... M O S F E T 、 I N , I N B ... 入力端子、 O A ... 出力増幅回路、 V B G ... バイアス回路、

P W E L ... P型ウェル、 N W E L ... N型ウェル、 N I S O ... 分離領域、 F G ... ゲート電極、 P s u b ... P型基板、

S 1 ~ S 1 3 ... スイッチ、 A G 1 , A G 2 ... アドレスレジスタ、 W A R 1 1 ~ W A R 2 2 ... 書き込みアドレスレジスタ、 S E L ... セレクタ、 M A R Y ... メモリアレイ、 S L G ... 選択制御回路、 C M P 1 , C M P 2 ... コンパレータ、 D R G 1 , D R G 2 ... データレジスタ 40 ... 、 O R 0 , O R 1 ... 出力レジスタ、 I B ... 入力バッファ、 O B ... 出力バッファ、 A D B ... アドレスバッファ、 C O B ... コントロールバッファ、 C K B ... クロックバッファ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 特開昭60-128701(JP,A)

特開平11-041039(JP,A)

特開2002-344260(JP,A)

米国特許第04958133(US,A)

(58)調査した分野(Int.Cl., DB名)

H03F 3/45

H03K 19/017

H03K 19/0175