(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2016-167828

(P2016-167828A)

(43) 公開日 平成28年9月15日(2016.9.15)

(51) Int.Cl.

F 1

テーマコード (参考)

|                   |                  |        |       |

|-------------------|------------------|--------|-------|

| <b>HO4N 19/30</b> | <b>(2014.01)</b> | HO 4 N | 19/30 |

| <b>HO4N 19/51</b> | <b>(2014.01)</b> | HO 4 N | 19/51 |

| <b>HO4N 19/86</b> | <b>(2014.01)</b> | HO 4 N | 19/86 |

審査請求 有 請求項の数 1 O L 外国語出願 (全 20 頁)

|              |                                     |

|--------------|-------------------------------------|

| (21) 出願番号    | 特願2016-76400 (P2016-76400)          |

| (22) 出願日     | 平成28年4月6日 (2016.4.6)                |

| (62) 分割の表示   | 特願2014-214124 (P2014-214124)<br>の分割 |

| 原出願日         | 平成21年12月11日 (2009.12.11)            |

| (31) 優先権主張番号 | 61/149,495                          |

| (32) 優先日     | 平成21年2月3日 (2009.2.3)                |

| (33) 優先権主張国  | 米国 (US)                             |

|          |                                                                                                                                                                    |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (71) 出願人 | 501263810<br>トムソン ライセンシング<br>Thomson Licensing<br>フランス国, 92130 イッシー レ<br>ムーリノー, ル ジヤンヌ ダルク,<br>1-5<br>1-5, rue Jeanne d' Arc, 92130 ISSY LES<br>MOULINEAUX, France |

| (74) 代理人 | 100107766<br>弁理士 伊東 忠重                                                                                                                                             |

| (74) 代理人 | 100070150<br>弁理士 伊東 忠彦                                                                                                                                             |

| (74) 代理人 | 100091214<br>弁理士 大貫 進介                                                                                                                                             |

最終頁に続く

(54) 【発明の名称】 ビット深度スケーラビリティにおける平滑参照フレームを用いた動き補償のための方法および装置

置

## (57) 【要約】 (修正有)

【課題】 ビット深度スケーラビリティにおける平滑参照フレームを用いた動き補償のための方法および装置を提供する。

【解決手段】 ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分のインターレイヤ残差予測を生成することによってピクチャの当該部分のピクチャ・データを符号化するエンコーダ100を含む。この逆トーン・マッピング演算は、残差領域からピクセル領域にシフトされる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分に関するインターレイヤ残差予測を生成することによって前記部分のピクチャ・データを符号化するエンコーダ(100)を有する装置であって、

前記逆トーン・マッピング演算が残差領域から前記ピクセル領域にシフトされる、前記装置。

**【請求項 2】**

前記エンコーダは、エンハンスマント・レイヤ・リファレンスを用いた動き補償を実行してエンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ予測をベース・レイヤ・リファレンスにトーン・マッピングしてトーン・マッピング予測を生成し、前記部分に関するベース・レイヤ残差を前記トーン・マッピング予測に結合して平滑ベース・レイヤ・リファレンスを取得し、前記平滑ベース・レイヤ・リファレンスを逆トーン・マッピングして逆トーン・マッピング予測を生成することによって、前記インターレイヤ残差予測を生成し、前記エンコーダは、前記逆トーン・マッピング予測を用いた動き推定および動き補償を実行して動きベクトルを取得し、前記動きベクトルならびに前記逆トーン・マッピング予測と前記ピクチャとの間の誤差を符号化して伝送する、請求項1に記載の装置。

**【請求項 3】**

前記動き補償を前記エンハンスマント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行して前記エンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ・リファレンスは前記ベース・レイヤ・リファレンスと同じビット深度を有している、請求項2に記載の装置。

**【請求項 4】**

前記動き補償を前記エンハンスマント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行して前記エンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ・リファレンスは前記ベース・レイヤ・リファレンスより大きいビット深度を有する、請求項2に記載の装置。

**【請求項 5】**

前記ベース・レイヤ残差を空間的にアップサンプリングして、空間的にアップサンプリングされたベース・レイヤ残差を取得し、前記空間的にアップサンプリングされたベース・レイヤ残差を前記トーン・マッピング予測に結合して前記平滑ベース・レイヤ・リファレンスを取得する、請求項2に記載の装置。

**【請求項 6】**

マクロプロック・レベル・シンタックスのフラグを使用して、前記インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを使用していることを示す、請求項2に記載の装置。

**【請求項 7】**

前記平滑ベース・レイヤ・リファレンスを指すエントリが前記エンハンスマント・レイヤの既存のリファレンス・リストに追加されるように、前記インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを既存のインター・モードに埋め込んだ状態で送信する、請求項2に記載の装置。

**【請求項 8】**

ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分に関するインターレイヤ残差予測を生成することによって前記部分のピクチャ・データを符号化するステップを含む方法であって、

前記逆トーン・マッピング演算が残差領域から前記ピクセル領域にシフトされる、前記方法(400)。

10

20

30

40

50

**【請求項 9】**

前記インターレイヤ残差予測の生成が、

エンハンスマント・レイヤ・リファレンスを用いた動き補償を実行してエンハンスマント・レイヤ予測を生成するステップ(425)と、

前記エンハンスマント・レイヤ予測をベース・レイヤ・リファレンスにトーン・マッピングしてトーン・マッピング予測を生成するステップ(430)と、

前記部分に関するベース・レイヤ残差を前記トーン・マッピング予測に結合して平滑ベース・レイヤ・リファレンスを取得するステップ(440)と、

前記平滑ベース・レイヤ・リファレンスを逆トーン・マッピングして逆トーン・マッピング予測を生成するステップ(455)とを含み、

前記符号化するステップが、

前記逆トーン・マッピング予測を用いて動き推定および動き補償を実行して動きベクトルを取得するステップと、

前記動きベクトルならびに前記逆トーン・マッピング予測と前記ピクチャとの間の誤差を符号化して伝送するステップ(460)とをさらに含む、請求項8に記載の方法。

10

**【請求項 10】**

前記動き補償を前記エンハンスマント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行して前記エンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ・リファレンスは前記ベース・レイヤ・リファレンスと同じビット深度を有する、請求項9に記載の方法。

20

**【請求項 11】**

前記動き補償を前記エンハンスマント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行して前記エンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ・リファレンスは前記ベース・レイヤ・リファレンスより大きいビット深度を有する、請求項9に記載の方法。

**【請求項 12】**

前記ベース・レイヤ残差を空間的にアップサンプリングして、空間的にアップサンプリングされたベース・レイヤ残差を取得し、前記空間的にアップサンプリングされたベース・レイヤ残差を前記トーン・マッピング予測に結合して前記平滑ベース・レイヤ・リファレンスを取得する、請求項9に記載の方法。

30

**【請求項 13】**

マクロプロック・レベル・シンタックスのフラグを使用して、前記インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを使用していることを示す、請求項9に記載の方法。

**【請求項 14】**

前記平滑ベース・レイヤ・リファレンスを指すエントリが前記エンハンスマント・レイヤの既存のリファレンス・リストに追加されるように、前記インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを既存のインター・モードに埋め込んだ状態で送信するステップをさらに含む、請求項9に記載の方法。

**【請求項 15】**

ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分に関するインターレイヤ残差予測を生成することによって前記部分のピクチャ・データを復号するデコーダ(200)を有する装置であって、

40

前記逆トーン・マッピング演算が残差領域から前記ピクセル領域にシフトされる、前記装置。

**【請求項 16】**

前記デコーダは、エンハンスマント・レイヤ・リファレンスを用いた動き補償を実行してエンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ予測をベース・レイヤ・リファレンスにトーン・マッピングしてトーン・マッピング予測を生成し、前

50

記部分に関するベース・レイヤ残差を前記トーン・マッピング予測に結合して平滑ベース・レイヤ・リファレンスを取得し、前記平滑ベース・レイヤ・リファレンスを逆トーン・マッピングして逆トーン・マッピング予測を生成することによって、前記インターレイヤ残差予測を生成し、前記デコーダは、前記逆トーン・マッピング予測を用いた動き推定および動き補償を実行して動きベクトルを取得し、前記動きベクトルならびに前記逆トーン・マッピング予測と前記ピクチャとの間の誤差に基づいて前記部分の再構築バージョンを生成する、請求項15に記載の装置。

**【請求項17】**

前記動き補償を前記エンハンスマント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行して前記エンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ・リファレンスは前記ベース・レイヤ・リファレンスと同じビット深度を有する、請求項16に記載の装置。 10

**【請求項18】**

前記動き補償を前記エンハンスマント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行して前記エンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ・リファレンスは前記ベース・レイヤ・リファレンスより大きいビット深度を有する、請求項16に記載の装置。 20

**【請求項19】**

前記ベース・レイヤ残差を空間的にアップサンプリングして、空間的にアップサンプリングされたベース・レイヤ残差を取得し、前記空間的にアップサンプリングされたベース・レイヤ残差を前記トーン・マッピング予測に結合して前記平滑ベース・レイヤ・リファレンスを取得する、請求項16に記載の装置。 20

**【請求項20】**

マクロブロック・レベル・シンタックスのフラグを使用して、前記インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを使用していることを示す、請求項16に記載の装置。 20

**【請求項21】**

前記平滑ベース・レイヤ・リファレンスを指すエントリが前記エンハンスマント・レイヤの既存のリファレンス・リストに追加されるように、前記インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを既存のインター・モードに埋め込んだ状態で受信する、請求項16に記載の装置。 30

**【請求項22】**

ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分のインターレイヤ残差予測を生成することによって前記部分のピクチャ・データを復号するステップを含む方法であって、

前記逆トーン・マッピング演算が残差領域から前記ピクセル領域にシフトされる、前記方法(600)。

**【請求項23】**

前記インターレイヤ残差予測の生成が、

エンハンスマント・レイヤ・リファレンスを用いた動き補償を実行してエンハンスマント・レイヤ予測を生成するステップ(625)と、 40

前記エンハンスマント・レイヤ予測をベース・レイヤ・リファレンスにトーン・マッピングしてトーン・マッピング予測を生成するステップ(630)と、

前記部分に関するベース・レイヤ残差を前記トーン・マッピング予測に結合して平滑ベース・レイヤ・リファレンスを取得するステップ(640)と、

前記平滑ベース・レイヤ・リファレンスを逆トーン・マッピングして逆トーン・マッピング予測を生成するステップ(655)とを含み、

前記復号するステップが、

前記逆トーン・マッピング予測を用いて動き推定および動き補償を実行して動きベクトルを取得するステップと、 50

前記動きベクトルならびに前記逆トーン・マッピング予測と前記ピクチャとの間の誤差に基づいて前記部分の再構築バージョンを生成するステップ(670)とをさらに含む、請求項22に記載の方法。

**【請求項24】**

前記動き補償を前記エンハンスマント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行して前記エンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ・リファレンスは前記ベース・レイヤ・リファレンスと同じビット深度を有する、請求項23に記載の方法。

**【請求項25】**

前記動き補償を前記エンハンスマント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行して前記エンハンスマント・レイヤ予測を生成し、前記エンハンスマント・レイヤ・リファレンスは前記ベース・レイヤ・リファレンスより大きいビット深度を有する、請求項23に記載の方法。

10

**【請求項26】**

前記ベース・レイヤ残差を空間的にアップサンプリングして、空間的にアップサンプリングされたベース・レイヤ残差を取得し、前記空間的にアップサンプリングされたベース・レイヤ残差を前記トーン・マッピング予測に結合して前記平滑ベース・レイヤ・リファレンスを取得する、請求項23に記載の方法。

**【請求項27】**

マクロブロック・レベル・シンタックスのフラグを使用して、前記インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを使用していることを示す、請求項23に記載の方法。

20

**【請求項28】**

前記平滑ベース・レイヤ・リファレンスを指すエントリが前記エンハンスマント・レイヤの既存のリファレンス・リストに追加されるように、前記インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを既存のインター・モードに埋め込んだ状態で受信するステップをさらに含む、請求項23に記載の方法。

**【請求項29】**

ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分のインターレイヤ残差予測を生成することによって符号化された前記部分のピクチャ・データを含む、符号化されたビデオ信号データを有するコンピュータ可読記憶媒体であって、

30

前記逆トーン・マッピング演算が残差領域から前記ピクセル領域にシフトされる、前記コンピュータ可読記憶媒体。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本願は、2009年2月3日出願の米国仮出願第61/149495号の利益を主張するものであり、これを参照することによりその開示内容全体が本明細書中に組み込まれる。

40

**【0002】**

本発明の原理は、一般にビデオの符号化および復号に関し、さらに詳細には、ビット深度スケーラビリティにおける平滑参照フレームを用いた動き補償のための方法および装置に関する。

**【背景技術】**

**【0003】**

近年、例えば医療用画像処理、プロダクションおよびポストプロダクションにおけるデジタル映画ワークフロー、ホーム・シアター関連分野など、多くの応用分野において、8より大きいビット深度を有するデジタル画像／ビデオがますます望ましくなっている。将来の何れかの時点で従来の8ビット深度と高ビット深度のデジタル撮像システムと

50

が共存するようになると、ビット深度のスケーラビリティが有用である可能性がある。8ビット・ビデオと10ビット・ビデオとの共存に対処する方法はいくつかある。第1の従来の解決策では、10ビット符号化ビット・ストリームのみを伝送し、10ビット・プレゼンテーションにトーン・マッピング方法を適用することにより、標準的な8ビット表示装置用の8ビット表現を得る。第2の従来技術の解決策では、8ビット符号化プレゼンテーションと10ビット符号化プレゼンテーションとを含む同時放送ビット・ストリームを伝送する。どちらのビット深度を選んで復号するかは、デコーダの選好による。例えば、10ビット対応デコーダは10ビット・ビデオを復号して出力することができるが、8ビットにしか対応していない通常のデコーダは、8ビット・ビデオしか出力することができない。第1の従来技術の解決策は、本質的に、国際標準化機構国際電気標準会議（ISO/IEC）MPEG-4（Moving Picture Experts Group-4）Part 10 AVC（Advanced Video Coding）標準、国際電気通信連合電気通信標準化セクター（ITU-T）H.264勧告（以下「MPEG-4 AVC標準」）の8ビット・プロファイルに準拠していない。第2の従来技術の解決策は、現行の全ての標準に準拠しているが、必要なオーバヘッドが多くなる。しかしながら、ビット削減と後方標準互換性との間の良好な兼ね合いが、スケーラブルな解決策となる可能性がある。MPEG-4 AVC標準のスケーラブルな拡張とも呼ばれるスケーラブル・ビデオ符号化（SVC）は、ビット深度スケーラビリティのサポートを考慮している。ビット深度スケーラブル符号化には、後処理（post-processing）や同時放送（simulcast）に優る利点が少なくとも3つある。1つの利点は、ビット深度スケーラブル符号化では、MPEG-4 AVC標準のハイ・プロファイルとの後方互換性を維持した状態で、10ビット・ビデオが可能であることである。第2の利点は、ビット深度スケーラブル符号化では、様々なネットワーク帯域幅または装置の機能への適応が可能であることである。第3の利点は、ビット深度スケーラブル符号化は、複雑でなく、効率が高く、柔軟性が高いことである。

10

20

30

40

50

#### 【0004】

##### MPEG-4 AVC SVC拡張

MPEG-4 AVC標準のSVC拡張の現在のバージョンでは、单一ループ復号をサポートして、復号の複雑さを軽減している。動き補償予測およびデブロッキングも含めたインター符号化マクロブロックの完全な復号は、現在の空間的または粗粒子スケーラビリティ（CGS；coarse-grain scalability）レイヤに必要なだけである。これは、インターレイヤ・イントラ・テクスチャ予測を、低レイヤ・ピクチャのイントラ・マクロブロックで符号化された部分に制限することによって行われる。ビット深度スケーラビリティのためにインターレイヤ・イントラ・テクスチャ予測を拡張するためには、逆トーン・マッピングが使用される。SVCも、インターレイヤ残差予測をサポートしている。トーン・マッピングは、通常はピクセル領域で使用されるので、残差領域における対応する逆トーン・マッピングを見つけるのは極めて困難である。第3および第4の従来技術の手法では、インターレイヤ残差予測のためにビット・シフトを使用している。

#### 【0005】

MPEG-4 AVC標準のスケーラブル・ビデオ符号化（SVC）拡張のジョイント・ドラフト8（JD8）では、以下では第3の従来技術の手法とも呼ぶ、平滑参照予測（SRP；smooth reference prediction）と呼ばれる技術を提案している。シンタックス要素residual\_prediction\_flagおよびbase\_mode\_flagの両方が設定されたときに、1ビット・シンタックス要素smoothed\_reference\_flagが送信される。smoothed\_reference\_flag = 1であるときには、デコーダにおいて以下のステップを行い、再構築されたビデオ・ブロックを取得する。

1. エンハンスメント・レイヤ・リファレンスフレームおよびベース・レイヤからのアップサンプリング動きベクトルを用いて、予測ブロックPを取得する。

2. 対応するベース・レイヤ残差ブロック  $r_b$  をアップサンプリングし、 $U(r_b)$  を  $P$  に付加して  $P + U(r_b)$  を形成する。

3. タップ [ 1, 2, 1 ] の平滑化フィルタを、最初に水平方向に、次いで垂直方向に適用して、 $S(P + U(r_b))$  を取得する。

4. 直前のステップ(3)の結果にエンハンスメント・レイヤ残差ブロックを付加して、再構築ブロック  $R = S(P + U(r_b)) + r_e$  を取得する。

#### 【0006】

さらに、第4の従来技術の手法は、BDS(ビット深度スケーラビリティ)のためのインターレイヤ残差予測の技術を提案するものである。この第4の従来技術の手法では、インターレイヤ残差予測のために逆トーン・マッピングの問題を残差領域からピクセル領域に変換する。インターレイヤ残差予測を用いる場合には、トーン・マッピング補償済み予測とベース・レイヤからのアップサンプリング残差の合計に逆トーン・マッピングを適用する。インターレイヤ残差予測を用いるときには、デコーダにおいて以下のステップを行い、再構築されたビデオ・ブロックを取得する。

1. エンハンスメント・レイヤ・リファレンスフレームを用いて予測ブロック  $P$  を取得し、次いで  $P$  をベース・レイヤ・ビット深度にトーン・マッピングして  $T(P)$  を取得する。

2. 対応するベース・レイヤ残差ブロック  $r_b$  を空間的にアップサンプリングし、 $U(r_b)$  を  $P$  に付加して  $T(P) + U(r_b)$  を形成する。

3. フィルタを使用して、 $S(T(P) + U(r_b))$  を取得する。

4. 次いで、逆トーン・マッピングを適用して、 $T^{-1}(S(T(P) + U(r_b)))$  を取得する。

5. 直前のステップ(4)の結果にエンハンスメント・レイヤ残差ブロックを付加して、再構築ブロック  $R = T^{-1}(S(T(P) + U(r_b))) + r_e$  を取得する。

#### 【0007】

しかしながら、上述の従来技術の解決策は全て不十分である。例えば、第3の従来技術の手法では、トーン・マッピング演算および逆トーン・マッピング演算が欠けているために、エンハンスメント・レイヤとベース・レイヤとにおいて異なるビット深度を扱うことができない。さらに、第4の従来技術の手法に関しては、エンハンスメント・レイヤ予測の正確さにおいて改善の余地がある。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

本発明の原理は、従来技術の上記その他の欠点および不都合に対処するものであり、ビット深度スケーラビリティにおける平滑参照フレームを用いた動き補償のための方法および装置を対象とするものである。

#### 【課題を解決するための手段】

#### 【0009】

本発明の原理の一態様によれば、装置が提供される。この装置は、ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分のインターレイヤ残差予測を生成することによってピクチャの当該部分のピクチャ・データを符号化するエンコーダを有する。逆トーン・マッピング演算は、残差領域からピクセル領域にシフトされる。

#### 【0010】

本発明の原理の他の一態様によれば、方法が提供される。この方法は、ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分のインターレイヤ残差予測を生成することによってピクチャの当該部分のピクチャ・データを符号化するステップを含む。逆トーン・マッピング演算は、残差領域からピクセル領域にシフトされる。

#### 【0011】

10

20

30

40

50

本発明の原理のさらに他の一態様によれば、装置が提供される。この装置は、ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分のインターレイヤ残差予測を生成することによってピクチャの当該部分のピクチャ・データを復号するデコーダを有する。逆トーン・マッピング演算は、残差領域からピクセル領域にシフトされる。

#### 【0012】

本発明の原理のさらに他の一態様によれば、方法が提供される。この方法は、ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分のインターレイヤ残差予測を生成することによってピクチャの当該部分のピクチャ・データを復号するステップを含む。ここで逆トーン・マッピング演算は、残差領域からピクセル領域にシフトされる。

10

#### 【0013】

本発明の原理の上記その他の特徴、特性および利点は、以下の例示的な実施例の詳細な説明を添付の図面と関連付けて読むことにより明らかになるであろう。

#### 【0014】

本発明の原理は、以下の例示的な図面によってより理解することができる。

#### 【図面の簡単な説明】

#### 【0015】

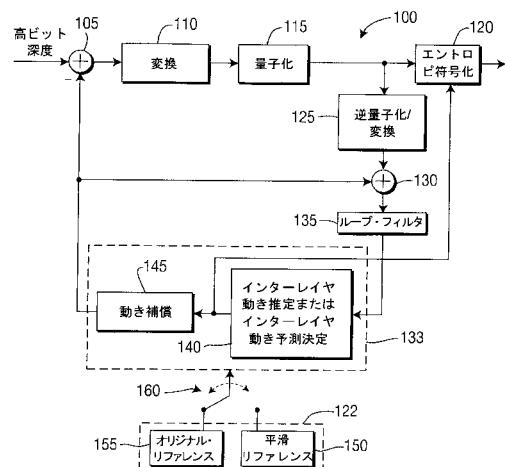

【図1】本発明の原理の実施例による、ビット深度スケーラビリティのためにインターレイヤ残差予測を用いる例示的なビデオ・エンコーダを示すブロック図である。

20

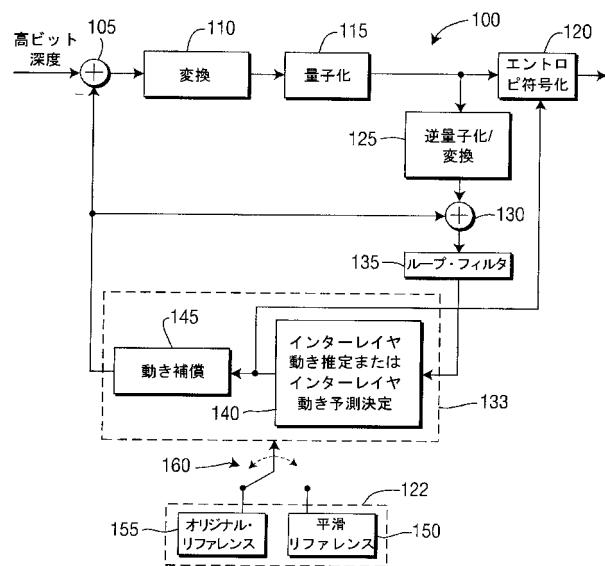

【図2】本発明の原理の実施例による、ビット深度スケーラビリティのためにインターレイヤ残差予測を用いる例示的なビデオ・デコーダを示すブロック図である。

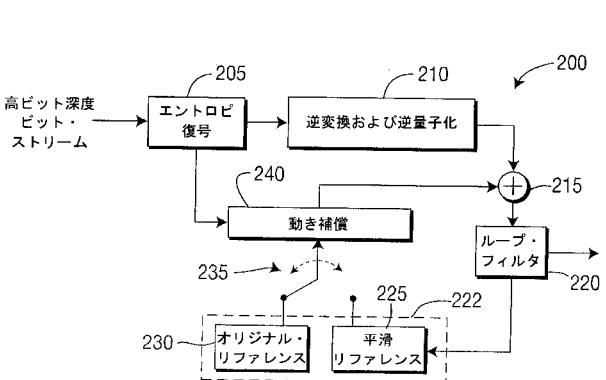

【図3】本発明の原理の実施例による、オリジナル・リファレンスおよびベース・レイヤ残差情報を用いる平滑リファレンス生成の一例を示すハイレベル・ブロック図である。

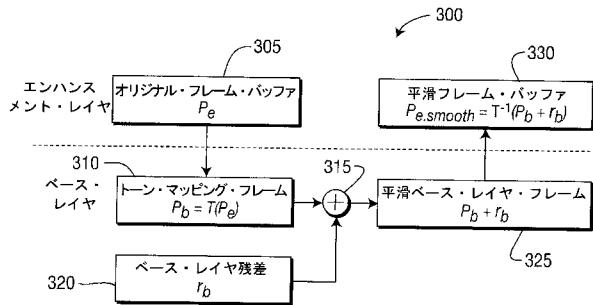

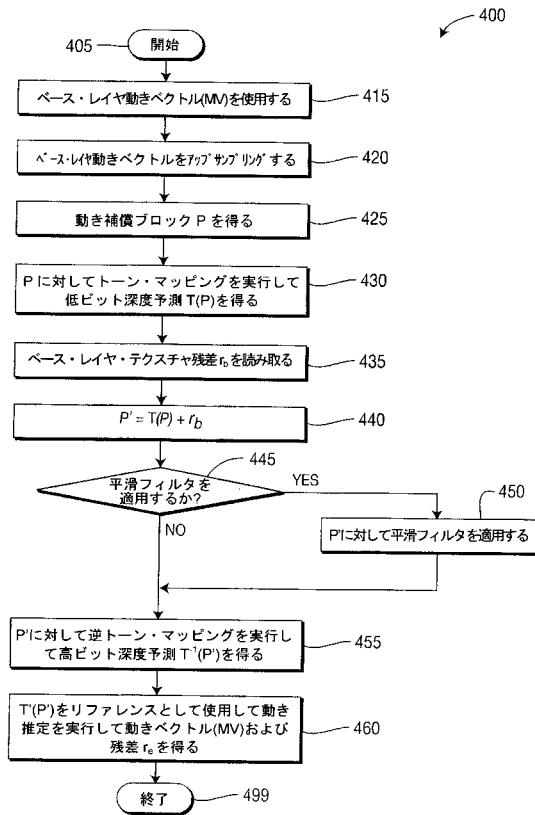

【図4】本発明の原理の実施例による、ビデオ・エンコーダにおけるビット深度スケーラビリティのためのインターレイヤ残差予測の例示的な方法を示す流れ図である。

【図5】本発明の原理の実施例による、平滑参照復号の一例を示すハイレベル・ブロック図である。

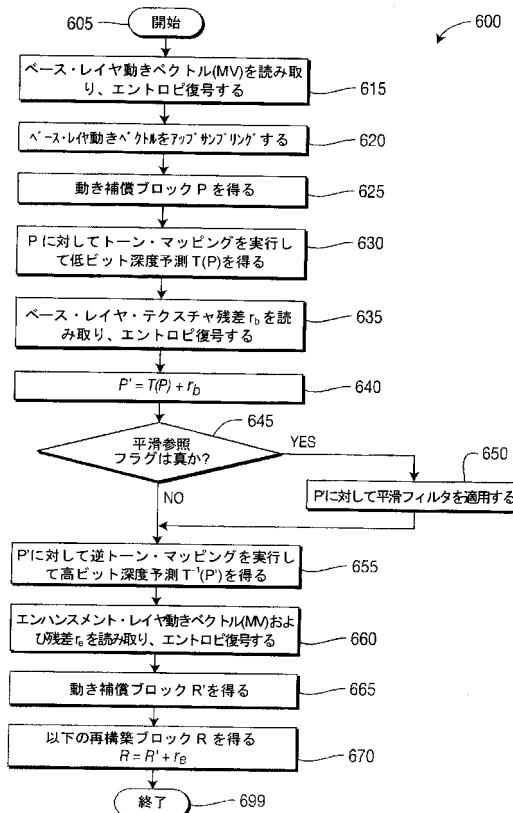

【図6】本発明の原理の実施例による、ビデオ・デコーダにおけるビット深度スケーラビリティのためのインターレイヤ残差予測の例示的な方法を示す流れ図である。

30

#### 【発明を実施するための形態】

#### 【0016】

本発明の原理は、ビット深度スケーラビリティにおける平滑参照フレームを用いた動き補償のための方法および装置を対象とするものである。

#### 【0017】

本明細書は、本発明の原理を例示するものである。従って、本明細書に明示的には記述または図示していないなくても、本発明の趣旨および範囲に含まれる本発明の原理を実現する様々な構成を、当業者なら考案することができることを理解されたい。

#### 【0018】

本明細書に記載する全ての例および条件に関する表現は、本発明の原理と、当技術分野をさらに進歩させるために発明者（等）が与える概念とを、読者が理解するのを助けるという教育的な目的を有するものであって、これらの具体的に列挙した例および条件に限定されるわけではないものと解釈されたい。

40

#### 【0019】

さらに、本発明の原理、特徴および実施例ならびに本発明の具体的な例について本明細書で述べる全ての記述は、その構造的な均等物および機能的な均等物の両方を含むものとする。さらに、これらの均等物には、現在既知の均等物だけでなく、将来開発されるであろう均等物も含まれる、すなわち、その構造に関わらず、同じ機能を実行する将来開発される任意の要素も含まれるものとする。

#### 【0020】

50

従って、例えば、当業者なら、本明細書に示すプロック図が本発明の原理を実施する例示的な回路の概念図を表していることを理解するであろう。同様に、任意のフローチャート、流れ図、状態遷移図、擬似コードなどが、コンピュータ可読媒体中に実質的に表現され、明示してある場合もしていない場合もあるコンピュータまたはプロセッサによって実質的に実行される様々なプロセスを表すことも理解されたい。

#### 【0021】

図面に示す様々な要素の機能は、専用のハードウェアを使用することによって、またソフトウェアを実行することができるハードウェアを適当なソフトウェアと関連付けて使用することによって、実現することができる。プロセッサによってそれらの機能を実現するときには、単一の専用プロセッサで実現することも、単一の共用プロセッサで実現することも、あるいはその一部を共用することもできる複数の個別プロセッサで実現することもできる。さらに、「プロセッサ」または「制御装置（コントローラ）」という用語を明示的に用いていても、ソフトウェアを実行することができるハードウェアのみを指していると解釈すべきではなく、デジタル信号プロセッサ（DSP）ハードウェア、ソフトウェアを記憶するための読み取り専用メモリ（ROM）、ランダム・アクセス・メモリ（RAM）および不揮発性記憶装置（ただしこれらに限定されない）を默示的に含むことがある。

#### 【0022】

従来の、かつ／または特注のその他ハードウェアも含まれることがある。同様に、図面に示す任意のスイッチも、概念的なものに過ぎない。それらの機能は、プログラム論理の動作によっても、専用論理によっても、プログラム制御と専用論理との相互作用によっても、あるいは手作業でも実施することができ、インプリメンタ（implementer）が、前後関係から適宜判断して特定の技術を選択することができる。

#### 【0023】

本明細書の特許請求の範囲において、特定の機能を実行する手段として表現されている任意の要素は、当該機能を実行する任意の方法を含むものとする。例えば、（a）当該機能を実行する回路素子の組合せや、（b）ファームウェアやマイクロコードなども含めた任意の形態のソフトウェアを、当該ソフトウェアを実行して当該機能を実行する適当な回路と組み合わせたものなども含むものとする。特許請求の範囲によって定義される本発明の原理は、記載した様々な手段が実施する機能を、特許請求の範囲が要求する仕方で組み合わせ、まとめることにある。従って、これらの機能を実施することができる任意の手段を、本明細書に示す手段の均等物とみなすものとする。

#### 【0024】

本明細書において、本発明の原理の「一実施例」または「実施例」あるいはその変形例と述べている場合、それは、当該実施例に関連して述べられる特定の特性、構造、特徴などが、本発明の原理の少なくとも1つの実施例に含まれるという意味である。従って、本明細書の様々な箇所に見られる「一実施例において」または「実施例において」という表現、あるいはそうした表現の変形表現は、その全てが必ずしも同じ実施例のことを指しているわけではない。

#### 【0025】

例えば「A / B」、「A および／または B」ならびに「A および B の少なくとも1つ」の場合など、「/」、「および／または」ならびに「の少なくとも1つ」の何れかを使用している場合、それは、最初に挙げた選択肢（A）のみを選択すること、2番目に挙げた選択肢（B）のみを選択すること、または両方の選択肢（A および B）を選択することを含むものであることを理解されたい。さらに別の例として、「A、B および／または C」ならびに「A、B および C の少なくとも1つ」の場合には、この表現は、最初に挙げた選択肢（A）のみを選択すること、2番目に挙げた選択肢（B）のみを選択すること、3番目に挙げた選択肢（C）のみを選択すること、最初と2番目の選択肢（A および B）のみを選択すること、最初と3番目の選択肢（A および C）のみを選択すること、2番目と3番目の選択肢（B および C）のみを選択すること、または3つ全ての選択肢（A および B および C）を選択することを含むものである。当技術分野および関連技術分野の当業者に

は容易に分かるように、このことは、列挙されている項目の数に応じて拡張することができる。

#### 【0026】

本発明の原理および従来技術を説明するために、本明細書では低ビット深度および高ビット深度という用語を使用する。これらの用語は、2つの異なるレベルのビット深度定義を定義するためのものである。高ビット深度は、低ビット深度より高いビット深度であることを特徴とするので、相対的な用語である。説明および例示のために、低ビット深度は8ビット、高ビット深度は10ビットであるものと仮定する。低ビット深度および高ビット深度という、これらの用語の相対的な性質から容易に分かるように、ここで求められる要件は、低ビット深度が高ビット深度未満であるということであり、それ以外の点に関しては、この用語は任意である。従って、例えば、低ビット深度は、4ビットでも6ビットでも、さらには12ビットでも良い。想定する高ビット深度が低ビット深度より大きいことが唯一の要件であるからである。従って、12ビットのビット深度を低ビット深度として定義すると仮定した場合には、高ビット深度は、14ビットや16ビットなど、12より大きいその他の任意のビット深度であると考えることができる。ここで、本発明の原理の説明および例示において低ビット深度が8ビットに等しいと仮定する場合には、高ビット深度の要件は、8ビットを超えていれば何ビットでも良いということになる（ここでは説明のために10ビットを仮定するが、12ビットや14ビットのビット深度など、8より大きいその他の任意のビット深度を含むことができる）。低ビット深度と高ビット深度の比較を説明する別 の方法は、ベース・レイヤ・ビット深度と、ベース・レイヤ・ビット深度より大きいエンハンスト・レイヤ・ビット深度である。従って、本発明の原理の1つまたは複数の実施例では10ビット・ピクチャを高ビット深度の例として使用するが、本発明の原理はこれに限定されるわけではなく、従って、本発明の原理で使用する高ビット深度は、12ビットや14ビットなど（ただしこれらに限定されない）を含む8より大きいその他の値（10以外の値）を取ることもできることを、理解されたい。

10

20

30

#### 【0027】

さらに、本明細書で使用する「ピクチャ」および「画像」という用語は入れ替えて使用しても良く、ビデオ・シーケンスに含まれる静止画像またはピクチャを指している。既知の通り、ピクチャは、フレームであってもフィールドであっても良い。

#### 【0028】

さらに、本明細書では、MPEG-4 AVC 標準のスケーラブル・ビデオ符号化（SVC）拡張に関する本発明の原理の1つまたは複数の実施例について述べるが、本発明の原理は、この拡張および／またはこの標準のみに限定されるわけではなく、従って、本発明の原理の趣旨を維持しながら、他のビデオ符号化標準および勧告、ならびにこれらの拡張について利用することもできる。

40

#### 【0029】

図1を参照すると、ビット深度スケーラビリティのためにインターレイヤ残差予測を用いた例示的なビデオ・エンコーダの全体が、参考番号100で示されている。ビデオ・エンコーダ100は、変換器110の入力部と信号通信する出力部を有する結合器105を含む。変換器110の出力部は、量子化器115の入力部に信号通信するように接続されている。量子化器115の出力部は、エントロピ符号化器120の第1の入力部および逆量子化器／逆変換器125の入力部に信号通信するように接続されている。逆量子化器／逆変換器125の出力部は、結合器130の第1の非反転入力部に信号通信するように接続されている。結合器130の出力部は、ループ・フィルタ135の入力部に信号通信するように接続されている。ループ・フィルタ135の出力は、インターレイヤ動き推定またはインターレイヤ動き予測決定を行う装置140の入力部に信号通信するように接続されている。装置140の出力部は、エントロピ符号化器120の第2の入力部および動き補償器145の入力部に信号通信するように接続されている。動き補償器145の出力部は、結合器130の第2の非反転入力部および結合器105の反転入力部に信号通信するように接続されている。装置140および動き補償器145は、装置133に含まれる。

50

リファレンス・プロバイダ(reference provider)222は、平滑リファレンス・プロバイダ150およびオリジナル・リファレンス・プロバイダ155を含む。オリジナル・リファレンス・プロバイダ155の出力部は、スイッチ160の第1の入力部に信号通信するように接続されている。平滑リファレンス・プロバイダ150の出力部は、スイッチ160の第2の入力部に信号通信するように接続されている。スイッチ160の出力部は装置133に信号通信するように接続されており、スイッチ160の出力は装置140および／または動き補償器145に供給されることが可能である。結合器105の非反転入力部は、高ビット深度信号を受信するための、ビデオ・エンコーダ100の入力部として利用することができる。エントロピ符号化器120の出力部は、高ビット深度ビット・ストリームを出力するための、ビデオ・エンコーダ100の出力部として利用することができる。

10

### 【0030】

図2を参照すると、ビット深度スケーラビリティのためにインターレイヤ残差予測を使用する例示的なビデオ・デコーダの全体が、参考番号200で示されている。ビデオ・デコーダ200は、逆変換器および逆量子化器210の入力部と信号通信するように接続されている第1の出力部を有するエントロピ・デコーダ205を含んでいる。逆変換器および逆量子化器210の出力部は、結合器215の第1の非反転入力部に信号通信するように接続されている。結合器215の出力部は、ループ・フィルタ220の入力部に信号通信するように接続されている。ループ・フィルタ220の第1の出力部は、リファレンス・プロバイダ222の入力部に信号通信するように接続されている。リファレンス・プロバイダ222は、オリジナル・リファレンス・プロバイダ230および平滑リファレンス・プロバイダ225を含んでいる。オリジナル・リファレンス・プロバイダ230の出力部は、スイッチ235の第1の入力部に信号通信するように接続されている。平滑リファレンス・プロバイダ225の出力部は、スイッチ235の第2の入力部に信号通信するように接続されている。スイッチの出力部は、動き補償器240の第1の入力部に接続されている。動き補償器240の出力部は、結合器215の第2の非反転入力部に信号連絡で接続されている。エントロピ・デコーダ205の第2の出力部は、動き補償器240の第2の入力部に信号通信するように接続されている。エントロピ・デコーダ205の入力部は、高ビット深度ビット・ストリームを受信するための、ビデオ・デコーダ200の入力部として利用することができる。ループ・フィルタ220の第2の出力部は、高ビット深度ピクチャを出力するための、ビデオ・デコーダ200の出力部として利用することができる。

20

### 【0031】

本発明の原理に従って、発明者等は、逆トーン・マッピングした平滑参照を動き補償の参考フレームとして使用することを提案する。一実施例では、発明者等は、逆トーン・マッピング問題を、インターレイヤ残差予測のために残差領域からピクセル領域に変換する。例示のために、本明細書では、ビット深度スケーラビリティのみを含み、単一ループ復号アーキテクチャを使用する1つまたは複数の実施例について説明する。しかし、本発明の原理はこれらに限定されるわけではなく、従って、本明細書に与える本発明の原理の教示があれば、当技術分野および関連技術分野の当業者なら、本発明の原理の趣旨を維持したまま、ビット深度スケーラビリティと空間的スケーラビリティなどのスケーラビリティの組合せ、および複数ループ復号アーキテクチャを含むように、本発明の原理を容易に拡張することができることを理解されたい。

30

### 【0032】

発明者等は、代替の平滑参照を動き補償に使用する符号化モードを追加することも提案する。この代替の平滑参照は、エンハンスマント・レイヤの参考フレーム、ならびにベース・レイヤの動きデータおよび残差データを用いて構築される。

40

### 【0033】

図3を参照すると、オリジナル・リファレンスおよびベース・レイヤ残差情報を用いた平滑リファレンスの作成の一例の全体が、参考番号300で示されている。オリジナル・

50

フレーム・バッファからのエンハンスメント・レイヤ予測  $p_e$  305 をトーン・マッピングして、 $p_b = T(p_e)$  310 を取得する。トーン・マッピング・フレーム  $p_b$  310 は、結合器 315 の第1の非反転入力部に入力される。ベース・レイヤ残差  $r_b$  320 は、結合器 315 の第2の非反転入力部に入力される。結合器 315 の出力は、平滑ベース・レイヤ・フレーム  $p_b + r_b$  325 を含む。平滑ベース・レイヤ・フレーム  $p_b + r_b$  325 を逆トーン・マッピングして、 $P_{e, smooth} = T^{-1}(p_b + r_b)$  330 を得る。

#### 【0034】

本発明の原理の一実施例によるビデオ符号化手順は、以下の通りである。

1. 以下のサブステップを用いて、各ブロックごとに代替の参照フレーム  $REF_{alt}$  10 を作成する。

a. 配列 (`collocated`) ベース・レイヤ・ブロックがイントラ符号化されている場合には、逆トーン・マッピング復号ブロックをコピーする。そうでない場合には、以下のサブステップ b または c の一方を実行する。

b. 一実施例では、10ビット・エンハンスメント・レイヤ・リファレンスピクチャおよびベース・レイヤ・アップサンプリング動きデータを使用して動き補償を実行して、予測ブロック  $P$  を作成する。次いで、 $P$  を8ビット・バージョン画像  $T(P)$  にトーン・マッピングする。

c. 他の実施例では、エンハンスメント・レイヤからの8ビット・トーン・マッピング参照ピクチャおよびベース・レイヤからのアップサンプリング動きデータを使用して動き補償を実行して、予測ブロック  $T(P)$  を形成する。 20

d. 対応するベース・レイヤ残差フレーム  $r_b$  を、 $U(r_b)$  まで空間的にアップサンプリングする。次いで、 $U(r_b)$  を  $T(P)$  に付加して、 $T(P) + U(r_b)$  を形成する。

e. フィルタを使用して、 $S(T(P) + U(r_b))$  を取得する。

f. 次いで、逆トーン・マッピングを適用して、 $T^{-1}(S(T(P) + U(r_b)))$  )を取得する。

2. 次いで、 $REF_{alt}$  を参照フレームとして使用して、動き推定を適用する。動きベクトル  $mv$  および残差  $r_e$  を符号化して伝送する。

#### 【0035】

マクロブロック (MB) レベル・シンタックスにおけるフラグ `smooth_ref_flag` は、この符号化モードを使用していることを示すために使用される。

#### 【0036】

他の実施例では、この符号化モードを `INTER` 符号化プロセスに埋め込み、代替のリファレンスを示すエントリが、エンハンスメント・レイヤのリファレンス・リストにもう1つ追加されるようにすることができる。この実施例では、この符号化モードを使用していることを示すフラグは必要ない。

#### 【0037】

図4を参照すると、ビデオ・エンコーダにおいてビット深度スケーラビリティのためのインターレイヤ残差予測を行う例示的な方法の全体が、参考番号400で示されている。この方法400は、機能ブロック415に制御をパスする開始ブロック405を含んでいる。機能ブロック415は、ベース・レイヤ動きベクトル ( $mv$ ) を使用し、制御を機能ブロック420にパスする。機能ブロック420は、ベース・レイヤ動きベクトルをアップサンプリングし、制御を機能ブロック425にパスする。機能ブロック425は、現在のブロックに対応する動き補償済みブロック  $P$  を取得し、制御を機能ブロック430にパスする。機能ブロック430は、動き補償済みブロックに対してトーン・マッピングを実行して低ビット深度予測  $T(P)$  を取得して、制御を機能ブロック435にパスする。機能ブロック435は、ベース・レイヤ・テクスチャ残差  $r_b$  を読み取り、制御を機能ブロック440にパスする。機能ブロック440は、ベース・レイヤ・テクスチャ残差  $r_b$  を低ビット深度予測  $T(P)$  に結合して、平滑参照ピクチャ、すなわち  $P' = T(P) + r_b$  40

10

20

30

40

50

$b$  を取得して、制御を決定ブロック 445 にパスする。決定ブロック 445 は、平滑参照を適用するか否かを判定する。適用する場合には、制御は機能ブロック 450 に移る。そうでない場合には、制御は機能ブロック 455 に移る。

#### 【0038】

機能ブロック 450 は、平滑参照ピクチャ  $P'$  に平滑フィルタを適用し、制御を機能ブロック 455 にパスする。

#### 【0039】

機能ブロック 455 は、 $P'$  に対して逆トーン・マッピングを実行して高ビット深度予測  $T^{-1}(P')$  を取得して、制御を機能ブロック 460 にパスする。機能ブロック 460 は、 $T'(P')$  をリファレンス(参照)として使用して動き推定を実行して動きベクトル( $m_v$ )およびエンハンスマント残差  $r_e$  を取得して、制御を終了ブロック 499 にパスする。

10

#### 【0040】

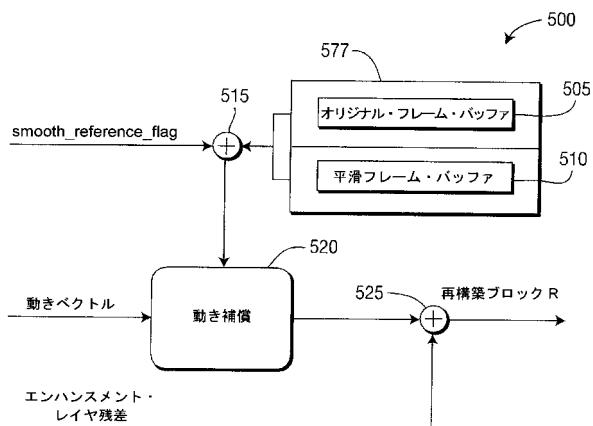

図 5 を参照すると、平滑参照復号の一例の全体が、参考番号 500 で示されている。オリジナル・フレーム・バッファ 505 の出力部および平滑フレーム・バッファ 510 の出力部が、結合器 515 の第 1 の非反転入力部に信号通信するように接続されている。結合器 515 の出力部は、動き補償器 520 の第 1 の入力部に信号通信するように接続されている。動き補償器 520 の出力部は、結合器 525 の第 1 の非反転入力部に信号通信するように接続されている。結合器 515 の第 2 の非反転入力部は、smooth\_ref\_f1ag を受信するための、平滑参照復号 500 の入力部として利用することができる。動き補償器 520 の第 2 の入力部は、動きベクトルを受信するための、平滑参照復号 500 の入力部として利用することができる。結合器 525 の第 2 の非反転入力部は、エンハンスマント・レイヤ残差を受信するための、平滑参照復号 500 の入力部として利用することができる。結合器 525 の出力部は、再構築ブロック R を出力するための、平滑参照復号 500 の出力部として利用することができる。オリジナル・フレーム・バッファ 505 および平滑フレーム・バッファ 510 は、メモリ 577 に含まれる。オリジナル・フレーム・バッファ 505 および平滑フレーム・バッファ 510 の両方を単一のメモリ 577 に関して示しているが、これらのバッファ 505 および 510 は、別個のメモリに記憶することもできる。このような変形形態およびその他の変形形態は、本発明の原理の趣旨に含まれる。

20

#### 【0041】

本発明の原理の一実施例によるビデオ復号手順は、以下の通りである。

1. 以下のサブステップを用いて、各ブロックごとに代替の参照フレーム  $REF_{alt}$  を作成する。

a. 配列ベース・レイヤ・ブロックがイントラ符号化されている場合には、逆トーン・マッピング復号ブロックをコピーする。そうでない場合には、以下のサブステップ b または c の一方を実行する。

b. 一実施例では、10ビット・エンハンスマント・レイヤ・リファレンスピクチャおよびベース・レイヤ・アップサンプリング動きデータを使用して動き補償を実行して、予測ブロック  $P$  を作成する。次いで、 $P$  を 8ビット・バージョン画像  $T(P)$  にトーン・マッピングする。

40

c. 他の実施例では、エンハンスマント・レイヤからの 8ビット・トーン・マッピング参照ピクチャおよびベース・レイヤからのアップサンプリング動きデータを使用して動き補償を実行して、予測ブロック  $T(P)$  を形成する。

d. 対応するベース・レイヤ残差フレーム  $r_b$  を、 $U(r_b)$  まで空間的にアップサンプリングする。次いで、 $U(r_b)$  を  $T(P)$  に付加して、 $T(P) + U(r_b)$  を形成する。

e. フィルタを使用して、 $S(T(P) + U(r_b))$  を取得する。

f. 次いで、逆トーン・マッピングを適用して、 $T^{-1}(S(T(P) + U(r_b)))$  を取得する。

50

2. 次いで、動き補償を適用して  $M C ( R E F_{a1t}, m v )$  を取得する。ここで、 $m v$  は動きベクトルである。

3. 直前のステップ(2)の結果にエンハンスメント・レイヤ残差ブロックを付加して、再構築ブロック  $R = M C ( R E F_{a1t}, m v ) + r_e$  を取得する。

#### 【0042】

図6を参照すると、ビデオ・デコーダにおいてビット深度スケーラビリティのためにインターレイヤ残差予測を行う例示的な方法の全体が、参考番号600で示されている。この方法600は、制御を機能ブロック615にパスする開始ブロック605を含んでいる。機能ブロック615は、ベース・レイヤ動きベクトル( $m v$ )を読み取り、エントロピ復号して、制御を機能ブロック620にパスする。機能ブロック620は、ベース・レイヤ動きベクトル( $m v$ )をアップサンプリングして、制御を機能ブロック625にパスする。機能ブロック625は、動き補償済みブロックPを取得して、制御を機能ブロック630にパスする。機能ブロック630は、Pに対してトーン・マッピングを実行して低ビット深度予測T(P)を取得して、制御を機能ブロック635にパスする。機能ブロック635は、ベース・レイヤ・テクスチャ残差 $r_b$ を読み取り、エントロピ復号し、制御を機能ブロック640にパスする。機能ブロック640は、ベース・レイヤ・テクスチャ残差 $r_b$ を低ビット深度予測T(P)に結合して平滑参照ピクチャすなわち $P' = T(P) + r_b$ を取得して、制御を決定ブロック645にパスする。決定ブロック645は、平滑参照フラグが真であるか否かを判定する。真である場合には、制御は機能ブロック650にパスされる。そうでない場合には、制御は機能ブロック655にパスされる。

10

20

#### 【0043】

機能ブロック650は、平滑参照ピクチャ $P'$ に平滑フィルタを適用し、制御を機能ブロック655にパスする。

#### 【0044】

機能ブロック655は、 $P'$ に逆トーン・マッピングを実行して高ビット深度予測 $T^{-1}(P')$ を取得して、制御を機能ブロック660にパスする。機能ブロック660は、動きベクトル( $m v$ )およびエンハンスメント・レイヤ残差 $r_e$ を読み取り、エントロピ復号し、制御を機能ブロック665にパスする。機能ブロック665は、動き補償を実行してブロック $R'$ を取得して、機能ブロック670に移行する。機能ブロック670は、高ビット深度予測 $T^{-1}(P')$ をエンハンスメント・レイヤ残差 $r_e$ に結合することによって得られた現在のブロックの再構築ブロックR、すなわち $R = T^{-1}(P') + r_e$ を生成し、制御を終了ブロック699にパスする。

30

#### 【0045】

一部については上記で述べたが、本発明に付属する多数の利点／特性の一部を次に説明する。例えば、1つの利点／特性は、ビット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分のインターレイヤ残差予測を生成することによってピクチャの当該部分のピクチャ・データを符号化するエンコーダを有する装置である。逆トーン・マッピング演算は、残差領域からピクセル領域にシフトされる。

40

#### 【0046】

他の利点／特性は、上述のエンコーダを有する装置であって、このエンコーダは、エンハンスメント・レイヤ・リファレンスを用いた動き補償を実行してエンハンスメント・レイヤ予測を生成し、エンハンスメント・レイヤ予測をベース・レイヤ・リファレンスにトーン・マッピングしてトーン・マッピング予測を生成し、上記部分のベース・レイヤ残差をトーン・マッピング予測に結合して平滑ベース・レイヤ・リファレンスを取得し、平滑ベース・レイヤ・リファレンスを逆トーン・マッピングして逆トーン・マッピング予測を生成することによって、上記インターレイヤ残差予測を生成する装置である。エンコーダは、逆トーン・マッピング予測を用いた動き推定および動き補償を実行して動きベクトルを取得し、動きベクトルならびに逆トーン・マッピング予測と入力ピクチャとの間の誤差を符号化して伝送する。

50

**【 0 0 4 7 】**

さらに他の利点 / 特性は、少なくとも上述のように動き補償を実行するエンコーダを有する装置であって、この動き補償をエンハンスメント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行してエンハンスメント・レイヤ予測を生成する装置である。このエンハンスメント・レイヤ・リファレンスはベース・レイヤ・リファレンスと同じビット深度を有する。

**【 0 0 4 8 】**

さらに他の利点 / 特性は、少なくとも上述のように動き補償を実行するエンコーダを有する装置であって、この動き補償をエンハンスメント・レイヤ・リファレンスおよびベース・レイヤ・アップサンプリング動きデータを用いて実行してエンハンスメント・レイヤ予測を生成する装置である。このエンハンスメント・レイヤ・リファレンスはベース・レイヤ・リファレンスより大きいビット深度を有する。

10

**【 0 0 4 9 】**

さらに、他の利点 / 特性は、少なくとも上述のように動き補償を実行するエンコーダを有する装置であって、ベース・レイヤ残差を空間的にアップサンプリングして、空間的にアップサンプリングされたベース・レイヤ残差を取得し、空間的にアップサンプリングされたベース・レイヤ残差をトーン・マッピング予測に結合して平滑ベース・レイヤ・リファレンスを取得する装置である。

**【 0 0 5 0 】**

さらに、他の利点 / 特性は、少なくとも上述のように動き補償を実行するエンコーダを有する装置であって、マクロブロック・レベル・シンタックスのフラグを使用して、インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを使用していることを示す装置である。

20

**【 0 0 5 1 】**

また、他の利点 / 特性は、少なくとも上述のように動き補償を実行するエンコーダを有する装置であって、平滑ベース・レイヤ・リファレンスを指すエントリがエンハンスメント・レイヤの既存のリファレンス・リストに追加されるように、インターレイヤ残差予測の生成に対応するインターレイヤ残差予測モードを既存のインター・モードに埋め込んだ状態で送信する装置である。

**【 0 0 5 2 】**

30

本発明の原理の上記その他の特性および利点は、本明細書の教示に基づいて、当業者であれば容易に確かめることができる。これらの本発明の原理の教示は、ハードウェア、ソフトウェア、ファームウェア、特殊目的プロセッサ、またはそれらの様々な組合せの形態で実施することができる。

**【 0 0 5 3 】**

本発明の原理の教示は、ハードウェアとソフトウェアの組合せとして実施されることが最も好ましい。さらに、ソフトウェアは、プログラム記憶装置に実装されたアプリケーション・プログラムとして実施することができる。アプリケーション・プログラムは、任意の適当なアーキテクチャを備える機械にアップロードして実行することができる。この機械は、1つまたは複数の中央処理装置(CPU)、ランダム・アクセス・メモリ(RAM)、および入出力(I/O)インターフェースなどのハードウェアを有するコンピュータ・プラットフォームで実施されることが好ましい。コンピュータ・プラットフォームは、オペレーティング・システムおよびマイクロ命令コードも備えることができる。本明細書に記載する様々なプロセスおよび機能は、CPUによって実行することができる、マイクロ命令コードの一部またはアプリケーション・プログラムの一部あるいはそれらの組合せの何れかにすることができる。さらに、追加のデータ記憶装置や印刷装置など、他の様々な周辺装置をコンピュータ・プラットフォームに接続することもできる。

40

**【 0 0 5 4 】**

さらに、添付の図面に示す構成要素となるシステム構成要素および方法の一部は、ソフトウェアで実施することが好ましいので、システム構成要素間またはプロセス機能プロッ

50

ク間の実際の接続は、本発明の原理をプログラミングする方法によって異なっていてもよいことも理解されたい。本明細書の教示があれば、当業者なら、本発明の原理の上記の実施態様または構成およびそれと同様の実施態様または構成を思いつくことができるであろう。

### 【 0 0 5 5 】

本明細書では、添付の図面を参照して例示的な実施例について述べたが、本発明の原理は、これらの具体的な実施例に限定されるわけではなく、当業者なら、本発明の原理の範囲または趣旨を逸脱することなく様々な変更および修正をそれらの実施例に加えることができることを理解されたい。そうした変更および修正は全て、添付の特許請求の範囲に記載する本発明の原理の範囲に含まれる。

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

【図6】

**【手続補正書】**

【提出日】平成28年4月20日(2016.4.20)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

ピット深度スケーラビリティのためにピクセル領域において実行される逆トーン・マッピング演算を用いてピクチャの少なくとも一部分に関するインターレイヤ残差予測を生成することによって前記部分のピクチャ・データを符号化するエンコーダを有する装置であって、

前記逆トーン・マッピング演算が残差領域から前記ピクセル領域にシフトされる、前記装置。

---

フロントページの続き

(72)発明者 マ , ジヤン

アメリカ合衆国 ニューヨーク州 フォレスト・ヒルズ アパートメント エー クライド・スト

リート 6841

(72)発明者 ルオ , ジアンコン

アメリカ合衆国 ニュージャージ州 ウエスト・ワインザー ワーウィック・ロード 65

(72)発明者 イン , ペン

アメリカ合衆国 ニューヨーク州 イサカ ジヨン・ストリート 6

【外国語明細書】

2016167828000001.pdf