(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5232773号

(P5232773)

(45) 発行日 平成25年7月10日(2013.7.10)

(24) 登録日 平成25年3月29日(2013.3.29)

|                  |                         |

|------------------|-------------------------|

| (51) Int.Cl.     | F 1                     |

| <b>H03F 3/24</b> | (2006.01) HO 3 F 3/24   |

| <b>H03F 1/02</b> | (2006.01) HO 3 F 1/02   |

| <b>H03F 1/32</b> | (2006.01) HO 3 F 1/32   |

| <b>H03F 3/68</b> | (2006.01) HO 3 F 3/68 Z |

| <b>H04B 1/04</b> | (2006.01) HO 4 B 1/04 R |

請求項の数 38 (全 157 頁) 最終頁に続く

|               |                               |           |                                                                                     |

|---------------|-------------------------------|-----------|-------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2009-507684 (P2009-507684)  | (73) 特許権者 | 500288603<br>パーカーヴィジョン インコーポレイテッド<br>アメリカ合衆国 32256 フロリダ州<br>ジャクソンビル ベイメドウズ ウエイ 7915 |

| (86) (22) 出願日 | 平成19年3月12日 (2007.3.12)        | (74) 代理人  | 100077481<br>弁理士 谷 義一                                                               |

| (65) 公表番号     | 特表2009-534988 (P2009-534988A) | (74) 代理人  | 100088915<br>弁理士 阿部 和夫                                                              |

| (43) 公表日      | 平成21年9月24日 (2009.9.24)        | (72) 発明者  | ディヴィッド エフ. ソレルス<br>アメリカ合衆国 32068 フロリダ州<br>ミドルバーグ ライドアウト レーン<br>3129                 |

| (86) 國際出願番号   | PCT/US2007/006197             |           |                                                                                     |

| (87) 國際公開番号   | W02007/133323                 |           |                                                                                     |

| (87) 國際公開日    | 平成19年11月22日 (2007.11.22)      |           |                                                                                     |

| 審査請求日         | 平成22年3月3日 (2010.3.3)          |           |                                                                                     |

| (31) 優先権主張番号  | 60/794,121                    |           |                                                                                     |

| (32) 優先日      | 平成18年4月24日 (2006.4.24)        |           |                                                                                     |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                                     |

| (31) 優先権主張番号  | 60/797,653                    |           |                                                                                     |

| (32) 優先日      | 平成18年5月5日 (2006.5.5)          |           |                                                                                     |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                                     |

最終頁に続く

(54) 【発明の名称】 RF電力伝送、変調および增幅のシステムおよび方法

## (57) 【特許請求の範囲】

## 【請求項1】

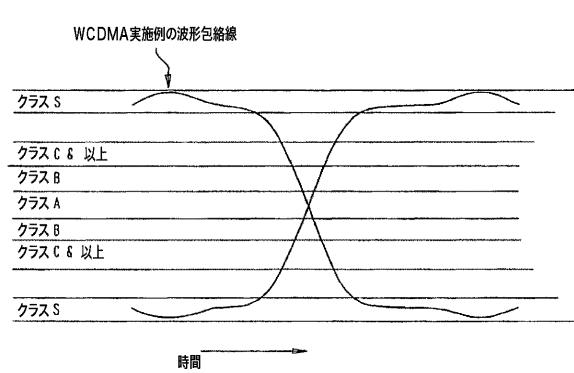

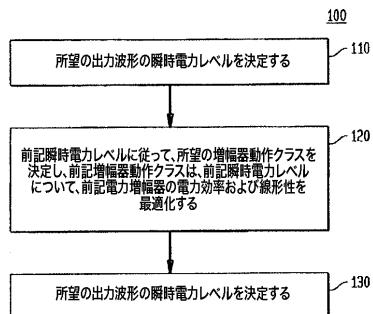

出力ステージにおけるリアルタイム出力ステージクラス制御のための方法であって、出力波形の電力レベルを決定するステップと、前記決定された電力レベルに従って、所望の出力ステージ動作クラスを決定するステップであって、前記所望の出力ステージ動作クラスは、前記決定された電力レベルのための前記出力ステージの電力効率および線形性のうち1つまたは複数を高めることであるステップと、

前記出力ステージ電力増幅器を、前記所望の出力ステージ動作クラスに従って動作するように制御するステップとを含むことを特徴とする方法。

## 【請求項2】

前記制御するステップは、前記出力ステージを、前記出力波形の前記決定された電力レベルに従って、複数の出力ステージ動作クラスの間で移行するように制御するステップを含むことを特徴とする請求項1に記載の方法。

## 【請求項3】

前記制御するステップは、前記出力ステージのバイアスを制御するステップを含むことを特徴とする請求項1に記載の方法。

## 【請求項4】

前記制御するステップは、前記出力ステージの入力信号の振幅を制御するステップを含むことを特徴とする請求項1に記載の方法。

## 【請求項 5】

前記制御するステップは、

前記出力ステージの入力信号の位相を制御するステップと、

前記出力ステージのバイアスを制御するステップと、

前記出力ステージの入力信号の振幅を制御するステップとのうち、1つまたは複数を含むことを特徴とする請求項1に記載の方法。

## 【請求項 6】

前記入力信号の位相を制御するステップと、前記出力ステージのバイアスを制御するステップと、前記出力ステージの入力信号の振幅を制御するステップとの使用は、前記出力波形の決定された制御領域、および、前記決定された電力レベルに基づくことを特徴とする請求項5に記載の方法。

10

## 【請求項 7】

前記制御領域の境界は、前記出力波形の相補累積密度関数 (Complementary Cumulative Density Function) (CCDF) およびサイドバンド性能基準に基づいて決定されることを特徴とする請求項6に記載の方法。

## 【請求項 8】

前記出力ステージの動作クラスを、前記出力波形の軌道における変化に従って制御するステップをさらに含むことを特徴とする請求項1に記載の方法。

## 【請求項 9】

前記出力ステージは、前記出力波形の複素包絡線が増大するにつれて、より高い動作クラスへスイッチすることを特徴とする請求項1に記載の方法。

20

## 【請求項 10】

前記出力ステージは、前記出力波形の複素包絡線が低減するにつれて、より低い動作クラスへスイッチすることを特徴とする請求項1に記載の方法。

## 【請求項 11】

前記出力波形の前記電力レベルが、決定されたしきい値を超えるとき、前記出力ステージの入力信号の位相を制御するステップをさらに含むことを特徴とする請求項1に記載の方法。

## 【請求項 12】

前記出力波形の前記決定された電力レベルが第1のしきい値を超えるが、第2のしきい値より低いとき、(a)前記出力ステージの入力信号の位相、(b)前記出力ステージのバイアス、および、(c)前記出力ステージの入力信号の振幅のうち、1つまたは複数を制御するステップをさらに含むことを特徴とする請求項1に記載の方法。

30

## 【請求項 13】

前記出力波形の前記決定された電力レベルが、決定されたしきい値より低いとき、(a)前記出力ステージのバイアス、および、(b)前記出力ステージの入力信号の振幅のうち、1つまたは複数を制御するステップをさらに含むことを特徴とする請求項1に記載の方法。

## 【請求項 14】

前記電力増幅器の出力電流を、前記出力波形の前記決定された電力レベルに従って制御するステップをさらに含むことを特徴とする請求項1に記載の方法。

40

## 【請求項 15】

電力増幅のための装置であって、

情報を受けし、複数の制御信号を前記受信された情報から生成するように構成される入力回路と、

前記入力回路に結合され、前記制御信号および周波数基準信号を受信し、前記周波数基準信号および前記制御信号を使用して、複数のほぼ一定の包絡線信号を生成するように構成されるペクトル変調回路と、

前記ほぼ一定の包絡線信号を受信し、前記ほぼ一定の包絡線信号を増幅かつ結合して、出力信号を生成するように構成される出力ステージと、

50

前記出力ステージを、前記出力信号の電力レベルに従って、1つまたは複数の出力ステージ動作クラスの間で移行するように制御する手段とを備えることを特徴とする装置。

【請求項16】

前記制御する手段は、前記出力ステージを、前記出力信号の波形軌道に従って、1つまたは複数の出力ステージ動作クラスの間で移行するように制御する手段とを備えることを特徴とする請求項15に記載の装置。

【請求項17】

前記制御する手段は、

前記出力ステージの入力信号の位相を制御する手段とを備えることを特徴とする請求項15に記載の装置。

10

【請求項18】

前記制御する手段は、

前記出力ステージのバイアスを制御する手段とを備えることを特徴とする請求項15に記載の装置。

【請求項19】

前記制御する手段は、

前記出力ステージの入力信号の振幅を制御する手段とを備えることを特徴とする請求項15に記載の装置。

【請求項20】

前記制御する手段は、

前記出力ステージを、前記出力信号の複素包絡線が増大するにつれて、より高い動作クラスへスイッチするように制御する手段とを備えることを特徴とする請求項15に記載の装置。

20

【請求項21】

前記制御する手段は、

前記出力ステージを、前記出力信号の複素包絡線が低減するにつれて、より低い動作クラスへスイッチするように制御する手段とを備えることを特徴とする請求項15に記載の装置。

【請求項22】

前記制御する手段は、

前記出力ステージの出力電流を、前記出力信号の前記電力レベルに従って制御する手段とを備えることを特徴とする請求項15に記載の装置。

30

【請求項23】

伝達関数に従い、IおよびQデータから振幅情報を生成するように構成される伝達関数モジュールと、

前記振幅情報に基づいて、ほぼ一定の包絡線信号を生成するように構成された複数のベクトル変調器と、

出力信号を生成するために、前記ほぼ一定の包絡線信号を増幅かつ結合する出力ステージと

を備え、

前記出力ステージは、前記出力信号の波形軌道に従い、1つまたは複数の動作クラスの間で移行するように制御されるように構成されることを特徴とする装置。

40

【請求項24】

前記出力ステージは、前記出力信号の波形包絡線がその最大値からゼロに向かって低減するにつれて、クラスS出力ステージからクラスA出力ステージにトラバースするように制御されるように構成されることを特徴とする請求項23に記載の装置。

【請求項25】

前記出力ステージは、前記出力信号の波形包絡線のゼロ交差で、クラスA出力ステージにトラバースするように制御されるように構成されることを特徴とする請求項23に記載の装置。

50

**【請求項 2 6】**

前記出力ステージは、前記出力信号の波形包絡線が、前記波形包絡線のゼロ交差から増加するについて、より高い動作クラスの出力ステージにトラバースするように制御されるように構成されることを特徴とする請求項 2 3 に記載の装置。

**【請求項 2 7】**

前記ほぼ一定の包絡線信号は、前記出力ステージに、前記 1 つまたは複数の動作クラスの間で移行させるように制御されることを特徴とする請求項 2 3 に記載の装置。

**【請求項 2 8】**

前記出力ステージへの入力信号の振幅は、前記出力ステージに、前記 1 つまたは複数の動作クラスの間で移行させるように制御されることを特徴とする請求項 2 3 に記載の装置

10

**【請求項 2 9】**

前記伝達関数は、前記出力ステージへの入力信号の振幅を制御し、前記出力ステージに、前記 1 つまたは複数の動作クラスの間で移行させるように構成されることを特徴とする請求項 2 3 に記載の装置。

**【請求項 3 0】**

前記出力ステージへの入力信号は、前記出力ステージに、前記 1 つまたは複数の動作クラスの間で移行させるようにバイアスがかけられることを特徴とする請求項 2 3 に記載の装置。

**【請求項 3 1】**

前記伝達関数は、前記出力ステージへの入力信号にバイアスをかけ、それにより、前記出力ステージに、前記 1 つまたは複数の動作クラスの間で移行させるように構成されることを特徴とする請求項 2 3 に記載の装置。

20

**【請求項 3 2】**

前記出力ステージは、前記出力ステージの駆動レベルおよびバイアスを制御することにより、クラス A 出力ステージへ移行し、その結果、出力電流導通角が 360 度に等しくなるように構成可能であることを特徴とする請求項 2 3 に記載の装置。

**【請求項 3 3】**

前記出力ステージは、前記出力ステージの駆動レベルおよびバイアスを制御することにより、クラス A B 出力ステージへ移行し、その結果、出力電流導通角が 180 度より大きく、360 度より小さくなるように構成可能であることを特徴とする請求項 2 3 に記載の装置。

30

**【請求項 3 4】**

前記出力ステージは、前記出力ステージの駆動レベルおよびバイアスを制御することにより、クラス B 出力ステージへ移行し、その結果、出力電流導通角が 180 度にほぼ等しくなるように構成可能であることを特徴とする請求項 2 3 に記載の装置。

**【請求項 3 5】**

前記出力ステージは、前記出力ステージの駆動レベルおよびバイアスを制御することにより、クラス C 出力ステージへ移行し、その結果、出力電流導通角が 180 度より小さくなるように構成可能であることを特徴とする請求項 2 3 に記載の装置。

40

**【請求項 3 6】**

前記出力ステージは、前記出力ステージの駆動レベルおよびバイアスを制御することにより、クラス D 出力ステージへ移行し、その結果、前記出力ステージがスイッチモードにおいて動作されるように構成可能であることを特徴とする請求項 2 3 に記載の装置。

**【請求項 3 7】**

前記出力ステージは、前記出力ステージをパルス幅変調された（ PWM ）出力信号を生成するように制御することにより、クラス S 出力ステージへ移行するように制御されるように構成可能であることを特徴とする請求項 2 3 に記載の装置。

**【請求項 3 8】**

前記出力ステージは、大きさ - 位相シフト変換のスペクトルの範囲内で変化する前記伝

50

達関数に追従して、前記1つまたは複数の動作クラスの間で移行させるように制御される

ように構成可能であることを特徴とする請求項23に記載の装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般に、RF電力伝送、変調および増幅に関する。より詳細には、本発明は、ベクトル結合 (vector combining) 電力増幅のための方法およびシステムに関する。

【背景技術】

【0002】

電力増幅器では、典型的には線形性と電力効率の間に複雑なトレードオフが存在する。

【0003】

線形性は、その入力を出力変数に関係付ける特性曲線における電力増幅器の動作範囲によって決定され、動作範囲がより線形であるほど、電力増幅器はより線形であると言われる。線形性は、電力増幅器の望ましい特性である。一態様では、例えば、電力増幅器は、変化する振幅、および/または位相、および/または周波数の信号を均一に増幅することが望ましい。したがって、線形性は、電力増幅器の出力信号品質を決定する重要なものである。

【0004】

電力効率を、増幅器に供給された総電力によって除算された、負荷に送達された総電力の関係を用いて計算することができる。理想的な増幅器では、電力効率は100%である。典型的には、電力増幅器は、増幅器の理論最大電力効率を決定するクラスに分割される。電力効率は、特に、電力増幅器が電力消費を大きく占める無線通信方式では、明らかに電力増幅器の望ましい特性である。

【0005】

残念ながら、電力増幅器における従来の線形性と効率の間のトレードオフは、電力増幅器がより線形であるほど、その電力効率が低いというものである。例えば、最も線形な増幅器は、増幅器の最も効率の低いクラスであるクラスA動作のためにバイアスされる。一方、クラスB、C、D、E、その他など、より高いクラスの増幅器はより電力効率がよいが、かなり非線形であり、スペクトル的に歪んだ出力信号の結果となる可能性がある。

【0006】

上述のトレードオフはさらに、典型的な無線通信信号によって強調される。例えば、OFDM、CDMAおよびW-CDMAなど、無線通信信号は一般に、それらのピーク対平均電力比によって特性化される。非線形な増幅器が採用されるとき、信号のピーク対平均比が大きいほど、より非線形な歪みが生じるようになる。

【0007】

アウトフェージング (out phasing) 増幅技術が、RF増幅器設計のために提案されている。いくつかの態様では、しかし、既存のアウトフェージング技術は、特に、例えば無線通信規格によって定義されるような、複素信号増幅要件を満たすことにおいて不十分である。

【0008】

一態様では、既存のアウトフェージング技術は、所望の出力信号の定包絡線成分 (constant envelope constituents) を結合するとき、絶縁および/または結合素子を採用する。例えば、成分信号を結合するために電力結合器が使用されることは、一般的なことである。しかし、この結合手法は典型的には、挿入損失およびバンド幅の制限による出力信号電力の低下、および、したがって電力効率の低減の結果となる。

【0009】

別の態様では、典型的に大きいサイズの結合素子は、モノリシックな増幅器設計に入れることは不可能である。

10

20

30

40

50

**【発明の開示】****【発明が解決しようとする課題】****【0010】**

したがって、必要とされるものは、既存の電力増幅技術の欠陥を解決しながら、電力効率を最大にし、非線形歪みを最小にする、電力増幅方法およびシステムである。さらに、従来の電力結合回路および技術の制限なしに実装することができる、電力増幅方法およびシステムが必要とされる。

**【課題を解決するための手段】****【0011】**

ベクトル結合電力増幅のための実施形態が、本明細書で開示される。

10

**【0012】**

一実施形態では、複数のほぼ一定の包絡線信号は個別に増幅され、次いで結合されて、所望の時変複素包絡線信号 (time-varying complex envelope envelope signal) が形成される。1つまたは複数のこれらの信号の位相および / または周波数特性は、所望の時変複素包絡線信号の所望の位相、周波数、および / または振幅特性を提供するように制御される。

**【0013】**

別の実施形態では、時変複素包絡線信号は、複数のほぼ一定の包絡線成分信号 (substantially constant envelope constituent signals) に分解される。これらの成分信号は増幅され、次いで再結合されて、元の時変包絡線信号の増幅されたバージョンが構成される。

20

**【0014】**

本発明の実施形態を、変調されたキャリア信号により、かつ、ベースバンド情報およびクロック信号により、実施することができる。本発明の実施形態はまた、周波数アップコンバージョンをも達成する。したがって、本発明の実施形態は、周波数アップコンバージョン、増幅および変調のための統合された解決法を表す。

**【0015】**

本発明の実施形態を、アナログおよび / またはデジタル制御により実装することができる。本発明を、アナログコンポーネントにより、あるいは、アナログコンポーネントおよびデジタルコンポーネントの組み合わせにより、実装することができる。後者の実施形態では、デジタル信号処理を、さらなるコスト節約のために、既存のベースバンドプロセッサにおいて実装することができる。

30

**【0016】**

本発明の追加の特徴および利点を、以下に続く説明において述べる。さらなる特徴および利点は、本明細書で述べる説明に基づいて、当業者には明らかになり、あるいは、本発明の実施により知ることができる。本発明の利点は、明細書およびこれの特許請求の範囲、ならびに添付の図面において特に指摘された構造および方法によって実現かつ達成されるであろう。

**【0017】**

前述の概要および以下の詳細な説明はいずれも例示的かつ説明のためのものであり、特許請求の範囲に記載された本発明の実施形態のさらなる説明を提供することを意図するものであることを理解されたい。

40

**【0018】**

本発明の実施形態を、添付の図面を参照して説明し、図面においては全体的に、類似の参照番号は、等しいかあるいは機能的に類似の要素を示す。また、全体的に、参照番号の一番左の数字は、関連する要素が最初に導入される図面を識別する。

**【0019】**

本発明を、添付の図面を参照して説明する。要素が最初に現れる図面は典型的には、対応する参照番号の一番左の数字によって示される。

**【発明を実施するための最良の形態】**

50

## 【0020】

## 目次

|                                                                           |    |

|---------------------------------------------------------------------------|----|

| 1. 序文                                                                     |    |

| 1.1. 時変複素包絡線入力信号の生成の実施例                                                   |    |

| 1.2. 定包絡線信号からの時変複素包絡線信号の生成の実施例                                            |    |

| 1.3. ベクトル電力増幅 (Vector Power Amplification)                                |    |

| n) 概観                                                                     |    |

| 2. 全体の数学的概観                                                               |    |

| 2.1. フェーザ信号表現                                                             |    |

| 2.2. 時変複素包絡線信号                                                            | 10 |

| 2.3. 時変包絡線信号の定包絡線分解                                                       |    |

| 3. ベクトル電力増幅 (VPA) 方法およびシステム                                               |    |

| 3.1. デカルト4分岐 (Cartesian 4-Branch) ベクトル電力増幅器                               |    |

| 3.2. デカルトポーラデカルトポーラ (Cartesian-Polar-Cartesian-Polar) (CPCP) 2分岐ベクトル電力増幅器 |    |

| 3.3. 直接デカルト (Direct Cartesian) 2分岐ベクトル電力増幅器                               |    |

| 3.4. IおよびQデータ - ベクトル変調器伝達関数                                               |    |

| 3.4.1. デカルト4分岐VPA伝達関数                                                     | 20 |

| 3.4.2. CP CP 2分岐VPA伝達関数                                                   |    |

| 3.4.3. 直接デカルト2分岐VPA伝達関数                                                   |    |

| 3.4.4. 大きさ - 位相シフト変換                                                      |    |

| 3.4.4.1. 正弦波信号のための大きさ - 位相シフト変換                                           |    |

| 3.4.4.2. 方形波信号のための大きさ - 位相シフト変換                                           |    |

| 3.4.5. 波形歪み補償                                                             |    |

| 3.5. 出力ステージ                                                               |    |

| 3.5.1. 出力ステージの実施形態                                                        |    |

| 3.5.2. 出力ステージ電流整形                                                         |    |

| 3.5.3. 出力ステージ保護                                                           | 30 |

| 3.6. 高調波制御 (Harmonic Control)                                             |    |

| 3.7. 電力制御                                                                 |    |

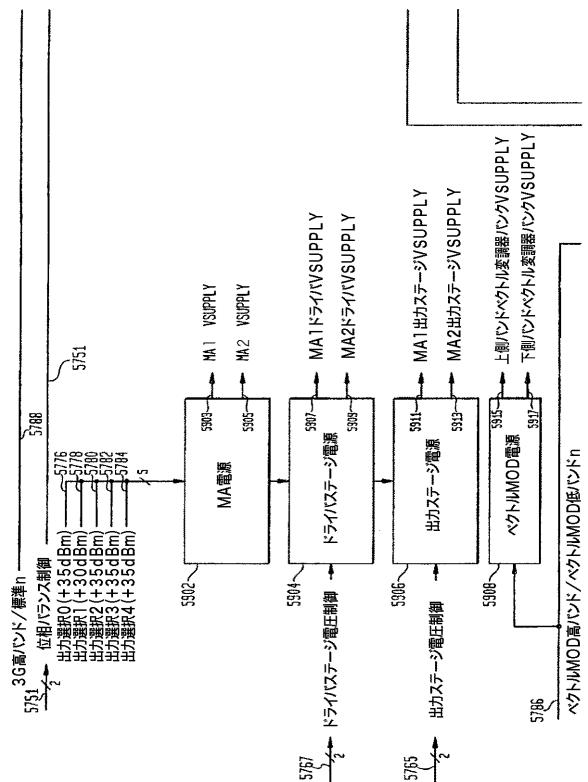

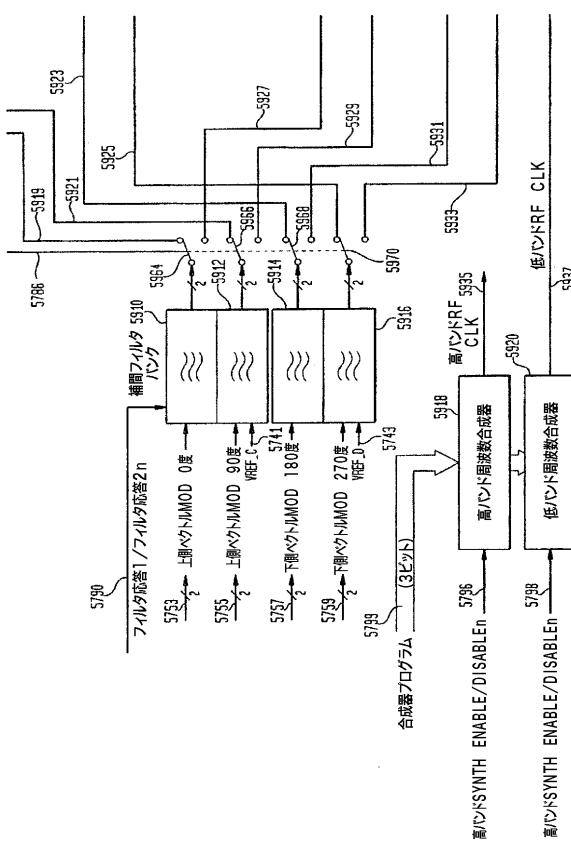

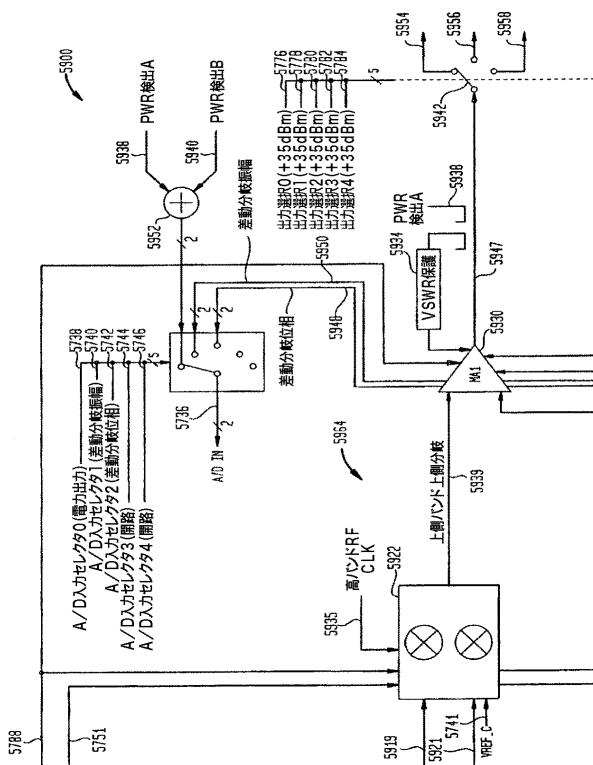

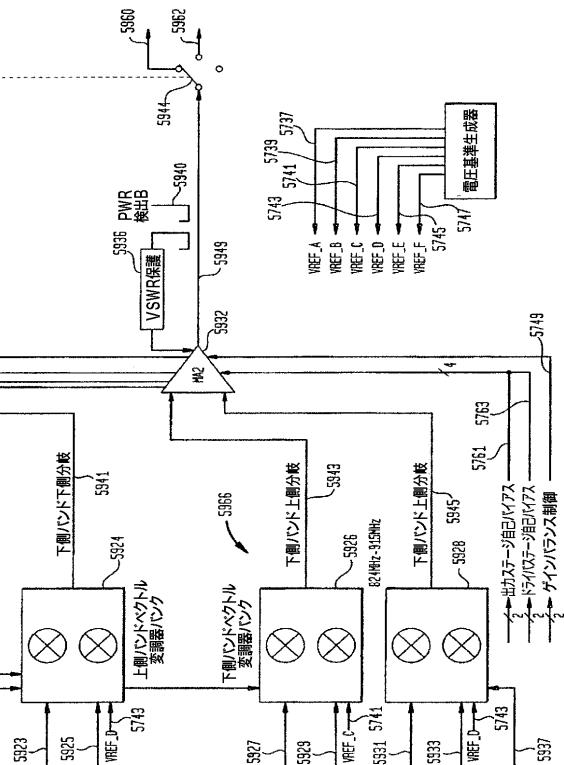

| 3.8. 例示的ベクトル電力増幅器の実施形態                                                    |    |

| 4. 追加の例示的実施形態および実装                                                        |    |

| 4.1. 概観                                                                   |    |

| 4.1.1. 出力電力および電力効率の制御                                                     |    |

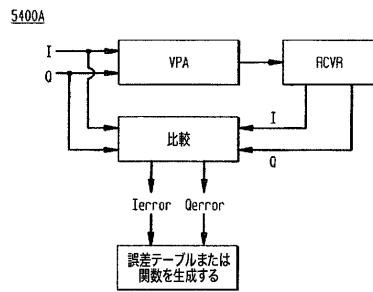

| 4.1.2. 誤差補償および／または訂正                                                      |    |

| 4.1.3. マルチバンドマルチモード動作                                                     |    |

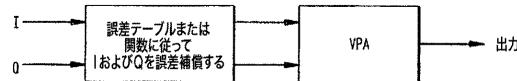

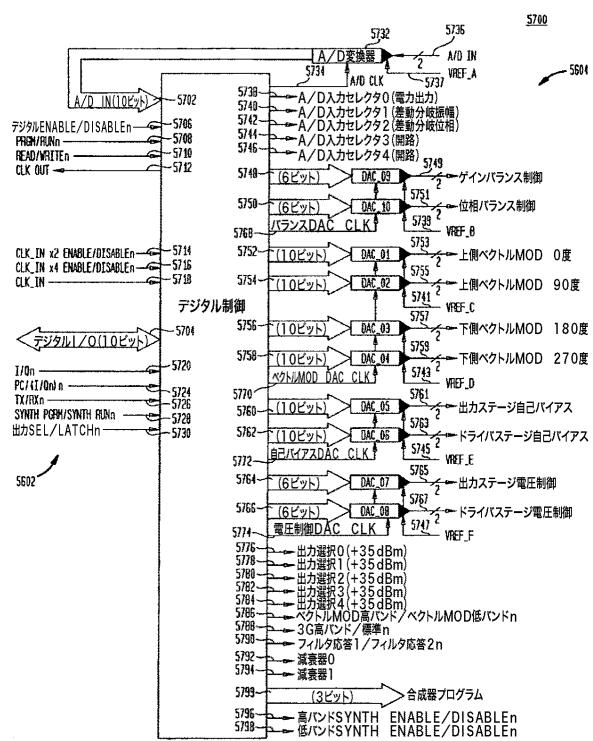

| 4.2. デジタル制御モジュール                                                          |    |

| 4.3. VPAアナログコア                                                            | 40 |

| 4.3.1. VPAアナログコア実装 A                                                      |    |

| 4.3.2. VPAアナログコア実装 B                                                      |    |

| 4.3.3. VPAアナログコア実装 C                                                      |    |

| 5. VPA出力ステージのリアルタイム増幅器クラス制御                                               |    |

| 6. 概要                                                                     |    |

| 7. 結論                                                                     |    |

| 【0021】                                                                    |    |

| 序文                                                                        |    |

| ベクトル結合電力増幅のための方法、装置およびシステムが、本明細書で開示される。                                   |    |

| 【0022】                                                                    | 50 |

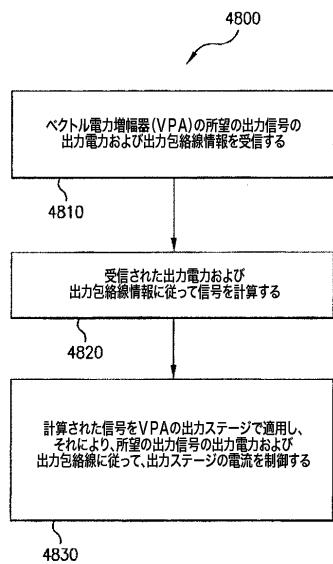

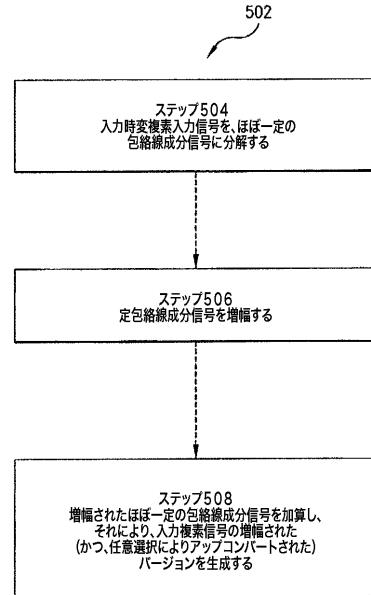

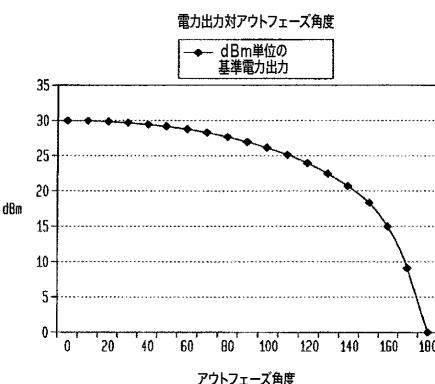

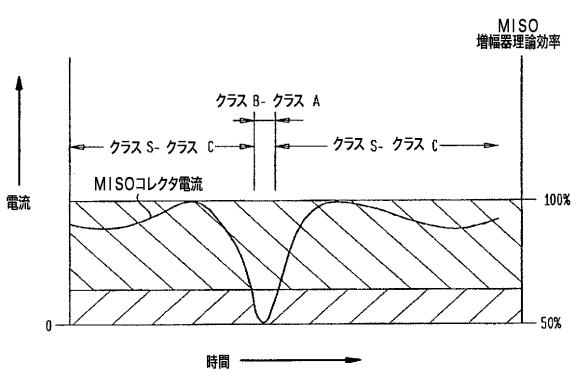

ベクトル結合電力増幅は、線形性および電力効率を同時に最適化するための手法である。一般的に言えば、また、図50の流れ図502を参照すると、ステップ504で、変化する振幅および位相を有する時変複素包絡線入力信号が、定包絡線成分信号に分解される。ステップ506で、定包絡線成分信号が増幅され、次いでステップ508で加算されて、入力複素包絡線信号の増幅されたバージョンが生成される。ほぼ一定の包絡線信号は、最小限の非線形歪みの懸念で増幅される可能性があるので、定包絡線信号を加算した結果は、最小の非線形歪みを受ける一方で、最適な効率をもたらす。

## 【0023】

したがって、ベクトル結合電力増幅は、最小の非線形歪みレベルを維持しながら、複素信号を効率的に増幅するために、非線形電力増幅器を使用することを可能にする。

10

## 【0024】

便宜上、限定ではなく、本発明の方法およびシステムは時として、本明細書で、ベクトル電力増幅(VPA)方法およびシステムと呼ばれる。

## 【0025】

本発明の実施形態によるVPA方法およびシステムの概要を、これから提供する。明確にするために、ある用語を最初に以下で定義する。このセクションで説明するこれらの定義は便宜上でのみ提供され、限定するものではない。これらの用語の意味は、本明細書で提供される教示の全体に基づいて、当業者には明らかになるであろう。これらの用語を、明細書全体でさらに詳細に論じる場合がある。

## 【0026】

20

信号包絡線という用語は、本明細書で使用されるとき、信号が時間領域において変動するときに、信号がその中に含まれる振幅境界を指す。直交変調信号を、 $r(t) = i(t) \cdot \cos(c \cdot t) + q(t) \cdot \sin(c \cdot t)$ によって記述することができ、ただし、 $i(t)$ および $q(t)$ は同相および直交信号を表し、信号包絡線 $e(t)$ は

## 【0027】

## 【数1】

$$e(t) = \sqrt{i(t)^2 + q(t)^2}$$

## 【0028】

30

に等しく、 $r(t)$ に関連付けられた位相角は逆正接( $q(t) / i(t)$ )に関係する。

## 【0029】

定包絡線信号という用語は、本明細書で使用されるとき、同相および直交信号を指し、ただし、

## 【0030】

## 【数2】

$$e(t) = \sqrt{i(t)^2 + q(t)^2}$$

## 【0031】

40

であり、 $e(t)$ は相対的にあるいはほぼ一定の値を有する。

## 【0032】

時変包絡線信号という用語は、本明細書で使用されるとき、時変信号包絡線を有する信号を指す。時変包絡線信号を、同相および直交信号に関して、

## 【0033】

## 【数3】

$$e(t) = \sqrt{i(t)^2 + q(t)^2}$$

## 【0034】

50

と記述することができ、 $e(t)$  は時変値を有する。

【0035】

位相シフトという用語は、本明細書で使用されるとき、基準位相に対して時変または定包絡線信号の位相成分を後退あるいは前進させることを指す。

【0036】

1.1) 複素包絡線時変入力信号の生成の実施例

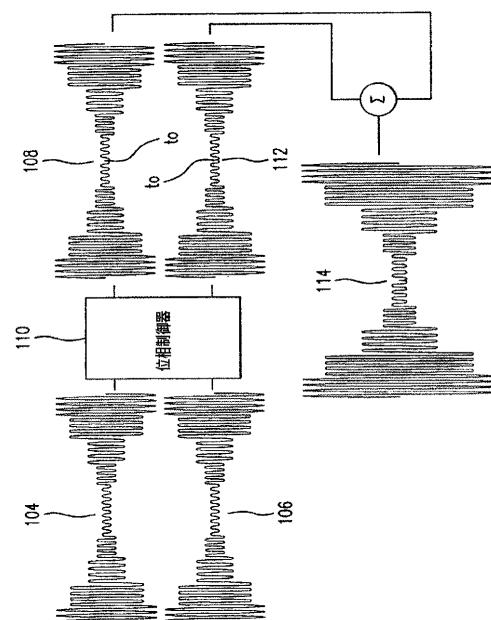

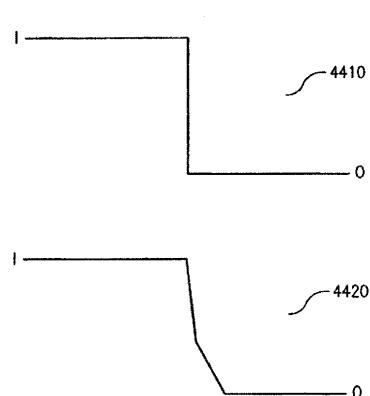

図1Aおよび1Bは、時変包絡線および位相複素入力信号の生成を例示する実施例である。図1Aで、時変包絡線キャリア信号104および106は、位相制御器110に入力される。位相制御器110は、信号104および106の位相成分を操作する。すなわち、位相制御器110は、信号104および106を位相シフトしてもよい。結果として生じる信号108および112を、したがって、信号104および106に対して位相シフトしてもよい。図1Aの実施例では、位相制御器110は、信号108および112を見ると分かるように、時刻 $t_0$ で、信号104および106において位相の反転(180度位相シフト)を引き起こす。信号108および112は、時変複素キャリア信号を表す。信号108および112は、時変包絡線および位相成分を共に有する。加算されるとき、信号108および112は信号114の結果となる。信号114もまた、時変複素信号を表す。信号114は、本発明のVPAの実施形態に対する一実施例の入力信号であってもよい(例えば、図50のステップ504への一実施例の入力)。

10

【0037】

時変複素信号をまた、図1Bに例示するように生成してもよい。図1Bで、信号116および118はベースバンド信号を表す。例えば、信号116および118は、信号の同相(I)および直交(Q)ベースバンド成分である場合がある。図1Bの実施例では、信号116および118は、+1から-1へ移行するときにゼロ交差を受ける。信号116および118は、信号120、または、90度位相シフトされた信号120で乗算される。信号116は、信号120の0度シフトされたバージョンで乗算される。信号118は、信号120の90度シフトされたバージョンで乗算される。結果として生じる信号122および124は、時変複素キャリア信号を表す。信号122および124は、信号116および118の時変振幅に従って変化する包絡線を有することに留意されたい。さらに、信号122および124は共に、信号116および118のゼロ交差で位相の反転を受ける。信号122および124は加算されて、信号126の結果となる。信号126は時変複素信号を表す。信号126は、本発明のVPAの実施形態に対する一実施例の入力信号を表す場合がある。加えて、信号116および118は、本発明のVPAの実施形態に対する実施例の入力信号を表す場合がある。

20

【0038】

1.2) 定包絡線信号からの時変複素包絡線信号の生成の実施例

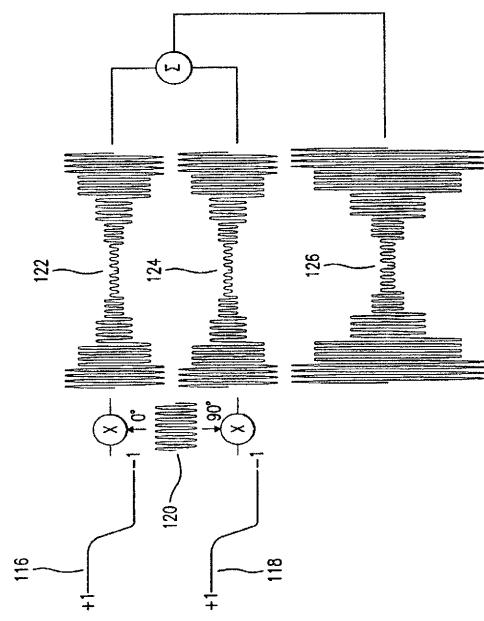

このセクションの説明は、全体的に図50のステップ508の動作に関係する。図1Cは、2つ以上のほぼ一定の包絡線信号の和からの時変複素信号の生成についての3つの実施例を例示する。しかし、本明細書で提供された教示に基づいて、図1Cの実施例において例示された概念を2つ以上の定包絡線信号の場合に同様に拡張することができることは、当業者には理解されよう。

30

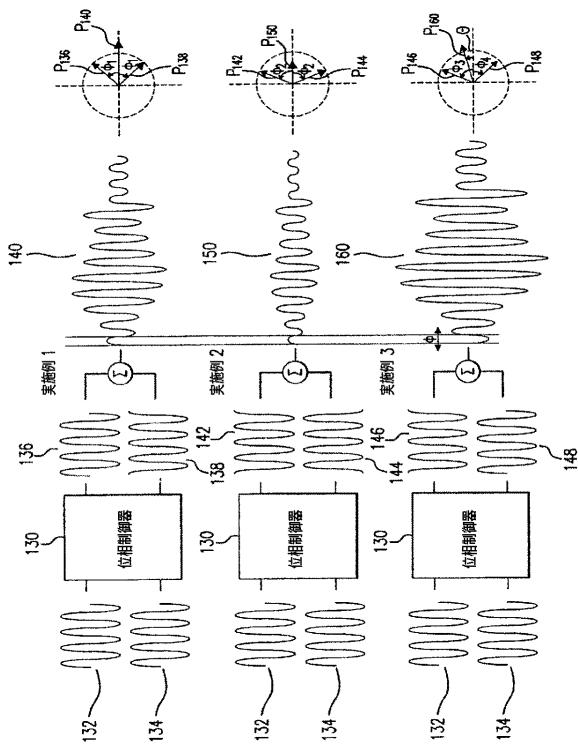

【0039】

図1Cの実施例1では、定包絡線信号132および134が位相制御器130に入力される。位相制御器130は、信号132および134の位相成分を操作して、信号136および138をそれぞれ生成する。信号136および138は、ほぼ一定の包絡線信号を表し、加算されて、信号140が生成される。実施例1に関連付けられた図1Cのフェーザ表現は、信号136および138をそれぞれフェーザ $P_{136}$ および $P_{138}$ として例示する。信号140は、フェーザ $P_{140}$ として例示される。実施例1では、 $P_{136}$ および $P_{138}$ は、フェーザ表現の実軸に整合されると仮定される基準信号に対して角度 $\alpha_1$ だけ対称的に位相シフトされる。対応して、時間領域信号136および138は、同量であるが、基準信号に対して逆方向に位相シフトされる。したがって、 $P_{136}$ および $P_{138}$ の和である $P_{140}$ は、

40

50

<sub>0</sub>は、基準信号と同相である。

【0040】

図1Cの実施例2では、ほぼ一定の包絡線信号132および134が位相制御器130に入力される。位相制御器130は、信号132および134の位相成分を操作して、信号142および144をそれぞれ生成する。信号142および144は、ほぼ一定の包絡線信号であり、加算されて信号150が生成される。実施例2に関連付けられたフェーザ表現は、信号142および144をそれぞれフェーザ $P_{142}$ および $P_{144}$ として例示する。信号150は、フェーザ $P_{150}$ として例示される。実施例2では、 $P_{142}$ および $P_{144}$ は、基準信号に対して対称的に位相シフトされる。したがって、 $P_{140}$ と同様に、 $P_{150}$ もまた基準信号と同相である。 $P_{142}$ および $P_{144}$ は、しかし、基準信号に対して、それにより<sub>2</sub>となる角度だけ位相シフトされる。 $P_{150}$ は、結果として、実施例1の $P_{140}$ とは異なる大きさを有する。時間領域表現では、信号140および150は同相であるが、互いに対しても異なる振幅を有することに留意されたい。

【0041】

図1Cの実施例3では、ほぼ一定の包絡線信号132および134が位相制御器130に入力される。位相制御器130は、信号132および134の位相成分を操作して、信号146および148をそれぞれ生成する。信号146および148は、ほぼ一定の包絡線信号であり、加算されて信号160が生成される。実施例3に関連付けられたフェーザ表現は、信号146および148をそれぞれフェーザ $P_{146}$ および $P_{148}$ として例示する。信号160は、フェーザ $P_{160}$ として例示される。実施例3では、 $P_{146}$ は、基準信号に対して角度<sub>3</sub>だけ位相シフトされる。 $P_{148}$ は、基準信号に対して角度<sub>4</sub>だけ位相シフトされる。<sub>3</sub>および<sub>4</sub>は、等しくても等しくなくてもよい。したがって、 $P_{146}$ および $P_{148}$ の和である $P_{160}$ は、もはや基準信号と同相ではない。 $P_{160}$ は、基準信号に対して角度だけ位相シフトされる。同様に、 $P_{160}$ は、実施例1および2の $P_{140}$ および $P_{150}$ に対してだけ位相シフトされる。 $P_{160}$ はまた、実施例3で例示するように、 $P_{140}$ に対して振幅において変化する場合もある。

【0042】

要約すると、図1Cの実施例は、時変振幅信号を、2つ以上のほぼ一定の包絡線信号の和によって得ることを実証する（実施例1）。さらに、時変信号は、2つ以上のほぼ一定の包絡線信号を逆方向に等しくシフトすることによって、振幅変化を有することができるが、それに与えられた位相変化を有することはできない（実施例2）。信号の2つ以上の定包絡線成分を同じ方向に等しくシフトすると、時変信号に位相変化を与えることはできるが、振幅変化を与えることはできない。いかなる時変振幅および位相信号も、2つ以上のほぼ一定の包絡線信号を使用して生成することができる（実施例3）。

【0043】

図1Cの実施例における信号は、例示のためにのみ正弦波形として図示されることに留意されたい。本明細書の教示に基づいて、他のタイプの波形もまた使用されている場合があることは、当業者には理解されよう。また、図1Cの実施例は、例示のためにのみ本明細書で提供され、本発明の特定の実施形態に対応する場合も対応しない場合もあることに留意されたい。

【0044】

1.3) ベクトル電力増幅概観

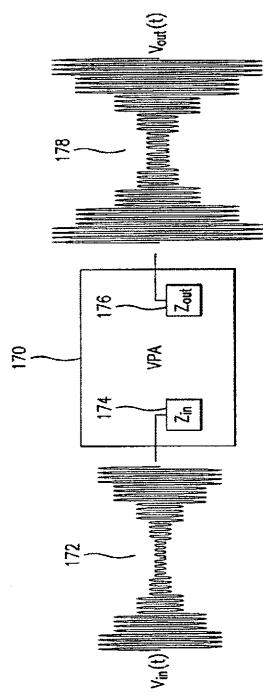

ベクトル電力増幅の大まかな概観をこれから提供する。図1Dは、例示的時変複素入力信号172の電力増幅を例示する。図1Aおよび1Bに例示するような信号114および126は、信号172の実施例である場合がある。さらに、信号172は、104および106（図1A）、108および112（図1A）、116および118（図1B）、ならびに、122および124（図1B）など、2つ以上の成分信号によって生成されるか、あるいはこれらからなる場合がある。

【0045】

図1Dの実施例では、VPA170は、本発明によるVPAシステムの実施形態を表す

10

20

30

40

50

。VPA170は、信号172を増幅して、増幅された出力信号178を生成する。出力信号178は、最小の歪みを有して効率的に増幅される。

【0046】

図1Dの実施例では、信号172および178は、電圧信号 $V_{in}(t)$ および $V_{out}(t)$ をそれぞれ表す。いかなる時刻でも、図1Dの実施例では、 $V_{in}(t)$ および $V_{out}(t)$ は $V_{out}(t) = K e_{V_{in}}(t + t')$ となるよう関係し、ただし、Kは倍率であり、 $t'$ は、VPAシステムにおいて存在する場合のある時間遅延を表す。電力の意味合いでは、

【0047】

【数4】

$$\frac{V_{out}^2(t)}{Z_{out}} > \frac{V_{in}^2(t)}{Z_{in}}$$

10

【0048】

であり、ただし、出力信号178は、入力信号172の電力増幅されたバージョンである。

【0049】

図1Dに例示するような、時変複素信号の線形（または、ほぼ線形）の電力増幅は、図1Eに示すような現在の実施形態によって達成される。

20

【0050】

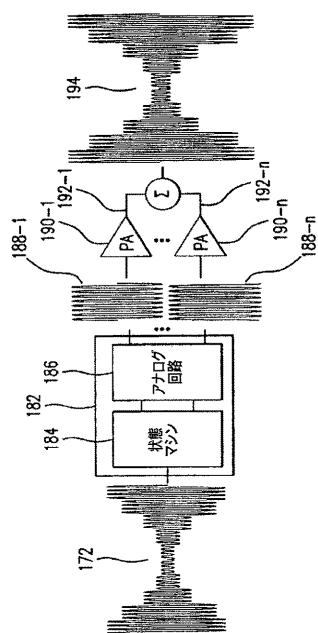

図1Eは、本発明の実施形態によるベクトル電力増幅の実施形態を概念的に例示する、一実施例のブロック図である。図1Eでは、入力信号172は時変複素信号を表す。例えば、入力信号172は、図1Aおよび1Bに例示するように生成されてもよい。実施形態では、信号172は、デジタル信号であってもアナログ信号であってもよい。さらに、信号172は、ベースバンド信号であってもキャリアベースの信号であってもよい。

【0051】

図1Eを参照すると、本発明の実施形態によれば、入力信号172またはその均等物がVPA182に入力される。図1Eの実施形態では、VPA182は、状態マシン184およびアナログ回路186を含む。状態マシン184は、デジタルおよび/またはアナログコンポーネントを含む場合がある。アナログ回路186は、アナログコンポーネントを含む。VPA182は、入力信号172を処理して、図1Eに例示するように、2つ以上の信号188 - {1, . . . , n}を生成する。図1Cにおける信号136、138、142、144および146、148に関して記載したように、信号188 - {1, . . . , n}は、異なる期間にわたって互いに対しても位相シフトされてもそうでなくてもよい。さらに、VPA182は、信号188 - {1, . . . , n}の和が、ある実施形態では、信号172の増幅されたバージョンである可能性のある信号194の結果となるように、信号188 - {1, . . . , n}を生成する。

30

【0052】

なお、図1Eを参照すると、信号188 - {1, . . . , n}は、ほぼ一定の包絡線信号である。したがって、前の段落の説明は、図50のステップ504に対応する。

40

【0053】

全体的に図50のステップ506に対応する図1Eの実施例では、定包絡線信号188 - {1, . . . , n}はそれぞれ、対応する電力増幅器（PA）190 - {1, . . . , n}によって独立して増幅されて、増幅された信号192 - {1, . . . , n}が生成される。実施形態では、PA190 - {1, . . . , n}は、各定包絡線信号188 - {1, . . . , n}をほぼ等しく増幅する。増幅された信号192 - {1, . . . , n}は、ほぼ一定の包絡線信号であり、ステップ508で加算されて、出力信号194が生成される。出力信号194は、入力信号172の線形的（あるいは、ほぼ線形的）増幅されたバージョンである可能性があることに留意されたい。出力信号194はまた、本明細書

50

に記載するように、入力信号 172 の周波数アップコンバートされたバージョンである場合もある。

【0054】

全体の数学的概観

2.1) フェーザ信号表現

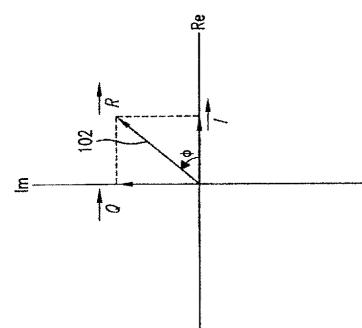

図1は、信号  $r(t)$  のフェーザ表現信号

【0055】

【数5】

$\overline{R}$

10

【0056】

102を例示する。信号のフェーザ表現は、信号の包絡線の大きさ、および、基準信号に対する信号の位相シフトを明示的に表す。本書では、便宜上、限定ではなく、基準信号は、フェーザ表現の直交空間の実 (Re) 軸に整合されるものとして定義される。本発明は、しかし、この実施形態に限定されない。信号の周波数情報は、この表現において暗示的であり、基準信号の周波数によって与えられる。例えば、図1を参照すると、また、実軸が  $\cos(t)$  基準信号に対応すると仮定すると、フェーザ

【0057】

【数6】

$\overline{R}$

20

【0058】

は、関数  $r(t) = R(t) \cos(t + \phi(t))$  に変換されるようになり、ただし、Rは、

【0059】

【数7】

$\overline{R}$

【0060】

の大きさである。

30

【0061】

なお、図1を参照すると、フェーザ

【0062】

【数8】

$\overline{R}$

【0063】

を、実部フェーザ

【0064】

【数9】

40

$\overline{I}$

【0065】

および虚部フェーザ

【0066】

【数10】

$\overline{Q}$

【0067】

に分解することができることに留意されたい。

50

【0068】

【数11】

$\tilde{I}$

【0069】

および

【0070】

【数12】

$\tilde{Q}$

10

【0071】

は、基準信号に対して

【0072】

【数13】

$\tilde{R}$

【0073】

の同相および直交フェーザ成分であると言われる。さらに、

20

【0074】

【数14】

$\tilde{I}$

【0075】

および

【0076】

【数15】

$\tilde{Q}$

30

【0077】

に対応する信号は、それぞれ、 $I(t) = R(t) \cdot \cos(\phi(t))$  および  $Q(t) = R(t) \cdot \sin(\phi(t))$  として、 $r(t)$  に関するに留意されたい。時間領域では、信号  $r(t)$  をまた、その同相および直交成分に関して、以下のように書くこともできる。

$$r(t) = I(t) \cdot \cos(\phi(t)) + Q(t) \cdot \sin(\phi(t)) = \\ R(t) \cdot \cos(\phi(t)) \cdot \cos(\phi(t)) + R(t) \cdot \sin(\phi(t)) \cdot \\ \sin(\phi(t)) \quad (1)$$

【0078】

図1の実施例では、 $R(t)$  が特定の時刻で例示されることに留意されたい。

40

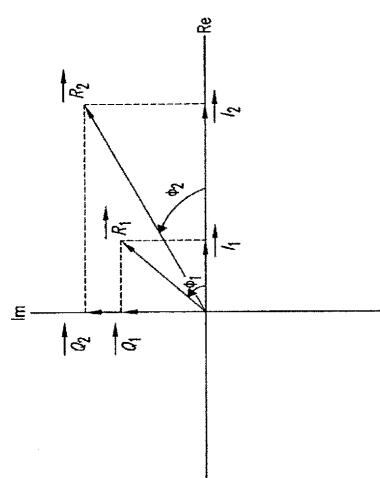

【0079】

2.2) 時変複素包絡線信号

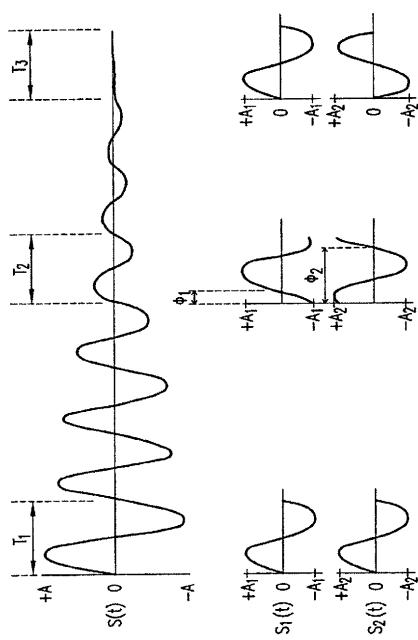

図2は、2つの異なる時刻  $t_1$  および  $t_2$  での信号  $r(t)$  のフェーザ表現を例示する。信号の包絡線の大きさを表す、フェーザの大きさ、ならびにその相対的な位相シフトは、共に時間  $t_1$  から  $t_2$  へと変化することに留意されたい。図2では、これは、フェーザ

【0080】

【数16】

$\tilde{R}_1$

50

【0081】

および

【0082】

【数17】

$\overrightarrow{R}_2$

【0083】

の変化する大きさ、および、それらの対応する位相シフト角 $\phi_1$ および $\phi_2$ によって例示される。信号 $r(t)$ は、したがって、時変複素包絡線信号である。

10

【0084】

さらに、図2から、信号 $r(t)$ の実および虚フェーザ成分もまた、振幅において時変であることに留意されたい。したがって、それらの対応する時間領域信号もまた、時変包絡線を有する。

【0085】

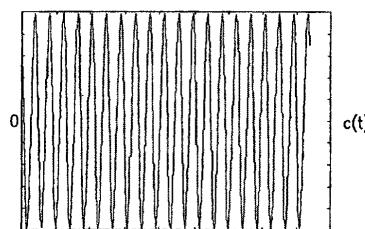

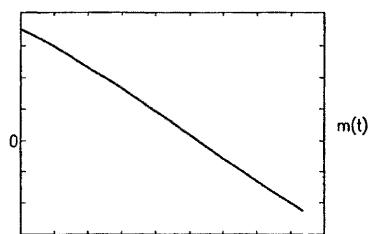

図3A～3Cは、時変複素包絡線信号を生成するための一実施例の変調を例示する。図3Aは、信号 $m(t)$ の図を例示する。図3Bは、キャリア信号 $c(t)$ の一部の図を例示する。図3Cは、信号 $m(t)$ および $c(t)$ の乗算の結果生じる信号 $r(t)$ を例示する。

20

【0086】

図3Aの実施例では、信号 $m(t)$ は、時変の大きさの信号である。 $m(t)$ はさらに、ゼロ交差を受ける。キャリア信号 $c(t)$ は、図3Bの実施例では、典型的には信号 $m(t)$ のものよりも高い、あるキャリア周波数で振動する。

【0087】

図3Cから、結果として生じる信号 $r(t)$ は時変包絡線を有することに留意されたい。さらに、図3Cから、 $r(t)$ は、変調信号 $m(t)$ がゼロに交差する瞬間に、位相の反転を受けることに留意されたい。一定でない包絡線および位相を共に有するので、 $r(t)$ は時変複素包絡線信号であると言われる。

【0088】

2.3) 時変包絡線信号の定包絡線分解

30

時変の大きさおよび位相のいかなるフェーザも、基準フェーザに対して適切に指定された位相シフトを有する2つ以上の一定の大きさのフェーザの和によって得ることができる。

【0089】

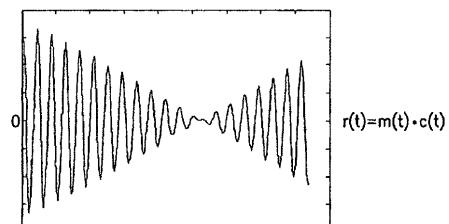

図3Dは、一実施例の時変包絡線および位相信号 $S(t)$ の図を例示する。例示を容易にするため、信号 $S(t)$ を、最大の包絡線の大きさ $A$ を有する正弦波信号であると仮定する。図3Dはさらに、いずれかの時刻に、2つの定包絡線信号 $S_1(t)$ および $S_2(t)$ の和によって、どのように信号 $S(t)$ を得ることができるかの一実施例を示す。一般に、 $S_1(t) = A_1 \sin(\omega_1 t + \phi_1(t))$  および  $S_2(t) = A_2 \sin(\omega_2 t + \phi_2(t))$  である。

40

【0090】

例示のため、図3Dにおいて、 $S(t)$ に対して信号 $S_1(t)$ および $S_2(t)$ を適切に位相整合することによって、どのように信号 $S_1(t)$ および $S_2(t)$ を加算して、 $S(t) = K(S_1(t) + S_2(t))$ 、ただし $K$ は定数となるようにすることができるかを例示する、3つの図が提供される。すなわち、信号 $S(t)$ を、いかなる時刻にも2つ以上の信号に分解することができる。図3Dから、期間 $T_1$ に渡って、 $S_1(t)$ および $S_2(t)$ は共に信号 $S(t)$ に対して同相であり、よって、和は信号 $S(t)$ の最大の包絡線の大きさ $A$ となる。しかし、期間 $T_3$ に渡って、信号 $S_1(t)$ および $S_2(t)$ は、互いに対して180度異相であり、よって、和は信号 $S(t)$ の最小の包絡線の大きさとなる。

50

## 【0091】

図3Dの実施例は、正弦波信号の場合を例示する。しかし、フーリエ級数またはフーリエ変換によって表すことができるキャリア信号を変調する、いかなる時変包絡線も、2つ以上のほぼ一定の包絡線信号に同様に分解することは、当業者には理解されよう。よって、複数のほぼ一定の包絡線信号の位相を制御することによって、いかなる時変複素包絡線信号を生成することもできる。

## 【0092】

## ベクトル電力増幅方法およびシステム

本発明の実施形態によるベクトル電力増幅方法およびシステムは、いかなる時変包絡線信号をも2つ以上のほぼ一定の包絡線成分信号に分解するため、または、このような成分信号を受信あるいは生成し、これらの成分信号を増幅し、次いで、増幅された信号を加算して、時変複素包絡線信号の増幅されたバージョンを生成するための、能力に依拠する。

10

## 【0093】

セクション3.1～3.3では、本発明のベクトル電力増幅（VPA）の実施形態が提供され、4分岐および2分岐の実施形態が含まれる。この説明では、各VPAの実施形態が最初に、実施形態の基本的概念の数学的導出を用いて概念的に提示される。VPAの実施形態の動作の方法の一実施形態が次いで提示され、その後に、VPAの実施形態の様々なシステムレベルの実施形態が続く。

## 【0094】

セクション3.4は、本発明の実施形態による制御モジュールの様々な実施形態を提示する。本発明の実施形態による制御モジュールは、本発明のあるVPAの実施形態を可能にするために使用される場合がある。いくつかの実施形態では、制御モジュールは、VPAの実施形態の入力ステージとVPAの実施形態の後続のベクトル変調ステージの間の中間物である。

20

## 【0095】

セクション3.5は、本発明の実施形態によるVPA出力ステージの実施形態を説明する。出力ステージの実施形態は、VPAの実施形態の出力信号を生成することを対象とする。

## 【0096】

セクション3.6は、本発明の実施形態による高調波制御を対象とする。本発明のある実施形態で高調波制御を実装して、VPAの実施形態の高調波における実および虚電力を操作し、よって、出力での基本周波数において存在する電力を増大させてもよい。

30

## 【0097】

セクション3.7は、本発明の実施形態による電力制御を対象とする。本発明のVPAの実施形態が採用される場合のある応用例の電力レベル要件を満たすために、本発明のある実施形態で電力制御を実装してもよい。

## 【0098】

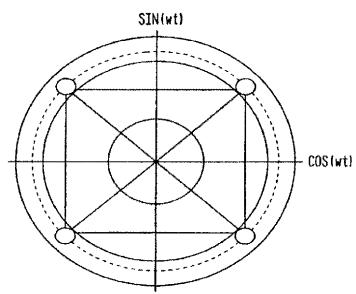

## 3.1) デカルト4分岐ベクトル電力増幅器

本明細書で、例示を容易にするため、限定ではなく、デカルト4分岐VPAの実施形態と呼ばれる本発明の一実施形態によれば、時変複素包絡線信号は、4つのほぼ一定の包絡線成分信号に分解される。これらの成分信号は、等しくあるいはほぼ等しく、個別に増幅され、次いで加算されて、元の時変複素包絡線信号の増幅されたバージョンが構成される。

40

## 【0099】

この実施形態では、例示のため、限定ではなく、4つの分岐が採用されることに留意されたい。本発明の範囲は、他の数の分岐の使用を含し、このような変形形態の実装は、本明細書に含まれた教示に基づいて、当業者には明らかになるであろう。

## 【0100】

一実施形態では、時変複素包絡線信号は最初に、その同相および直交ベクトル成分に分解される。フェーザ表現では、同相および直交ベクトル成分は、信号の実部および虚部フ

50

エーザにそれぞれに対応する。

【0101】

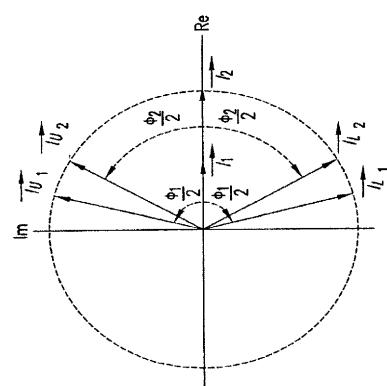

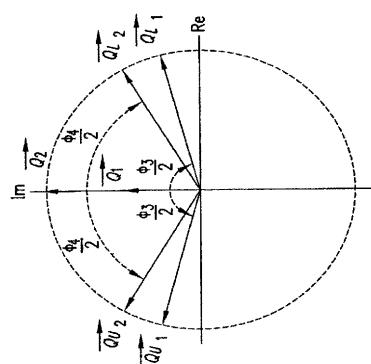

上述のように、信号の同相および直交ベクトル成分の大きさは、信号の大きさに比例して変化し、よって、信号が時変包絡線信号であるとき、定包絡線ではない。したがって、4分岐VPAの実施形態はさらに、信号の同相および直交ベクトル成分の各々を4つのほぼ一定の包絡線成分に分解し、2つは同相信号成分、2つは直交信号成分である。この概念を、フェーザ信号表現を用いて図4に例示する。

【0102】

図4の実施例では、フェーザ

【0103】

【数18】

$\vec{I}_1$

【0104】

および

【0105】

【数19】

$\vec{I}_2$

【0106】

は、2つの時刻  $t_1$  および  $t_2$  での例示的時変複素包絡線信号の実部フェーザにそれぞれ対応する。フェーザ

【0107】

【数20】

$\vec{I}_1$

【0108】

および

【0109】

【数21】

$\vec{I}_2$

【0110】

は、異なる大きさを有することに留意されたい。

【0111】

なお、図4を参照すると、瞬時  $t_1$  で、フェーザ

【0112】

【数22】

$\vec{I}_1$

【0113】

を、上側および下側フェーザ

【0114】

10

20

30

40

【数23】

$\overrightarrow{I_{U_1}}$

【0115】

および

【0116】

【数24】

$\overrightarrow{I_{L_1}}$

10

【0117】

の和によって得ることができる。同様に瞬時  $t_2$  で、フェーザ

【0118】

【数25】

$\overrightarrow{I_2}$

【0119】

を、上側および下側フェーザ

20

【0120】

【数26】

$\overrightarrow{I_{U_2}}$

【0121】

および

【0122】

【数27】

$\overrightarrow{I_{L_2}}$

30

【0123】

の和によって得ることができる。フェーザ

【0124】

【数28】

$\overrightarrow{I_{U_1}}$

【0125】

40

および

【0126】

【数29】

$\overrightarrow{I_{U_1}}$

【0127】

は、等しいかあるいはほぼ等しい大きさを有することに留意されたい。同様に、フェーザ

【0128】

【数30】

$$\overrightarrow{I}_{L_1}$$

【0129】

および

【0130】

【数31】

$$\overrightarrow{I}_{L_2}$$

10

【0131】

は、ほぼ等しい大きさを有する。したがって、時変包絡線信号の実部フェーザを、いずれかの時刻に、少なくとも2つのほぼ一定の包絡線成分の和によって得ることができる。

【0132】

フェーザ

【0133】

【数32】

$$\overrightarrow{I}_{U_1}$$

20

【0134】

および

【0135】

【数33】

$$\overrightarrow{I}_{L_1}$$

【0136】

の、

30

【0137】

【数34】

$$\overrightarrow{I}_1$$

【0138】

に対する位相シフト、ならびに、フェーザ

【0139】

【数35】

$$\overrightarrow{I}_{U_2}$$

40

【0140】

および

【0141】

【数36】

$$\overrightarrow{I}_{L_2}$$

【0142】

50

の、

【0 1 4 3】

【数37】

$\overrightarrow{I_2}$

【0 1 4 4】

に対する位相シフトはそれぞれ、フェーザ

【0 1 4 5】

【数38】

$\overrightarrow{I_1}$

10

【0 1 4 6】

および

【0 1 4 7】

【数39】

$\overrightarrow{I_2}$

【0 1 4 8】

の所望の大きさに従って設定される。ある場合には、上側および下側フェーザが等しい大きさを有するように選択されるとき、上側および下側フェーザは、そのフェーザに対して位相において対称的にシフトされる。これは図4の実施例において例示され、すべて等しい大きさを有する。

20

【0 1 4 9】

【数40】

$\overrightarrow{I_{U_1}}, \overrightarrow{I_{L_1}}, \overrightarrow{I_{U_2}}$

【0 1 5 0】

および

【0 1 5 1】

30

【数41】

$\overrightarrow{I_{L_2}}$

【0 1 5 2】

に対応する。第2の場合、上側および下側フェーザの位相シフトは、そのフェーザに対して位相においてほぼ対称的にシフトされる。本明細書の説明に基づいて、上側および下側フェーザの大きさおよび位相シフトの値は全く等しいものである必要はないことは、当業者には理解されよう。

【0 1 5 3】

40

一実施例として、さらに、図4に例示した場合では、図4の

【0 1 5 4】

【数42】

$\frac{\phi_1}{2}$

【0 1 5 5】

および

【0 1 5 6】

50

【数43】

$$\frac{\phi_2}{2}$$

【0157】

として例示された相対位相シフトは、以下のように、正規化されたフェーザ

【0158】

【数44】

$$\overrightarrow{I_1}$$

10

および

【0159】

【数45】

$$\overrightarrow{I_2}$$

【0160】

の大きさに関係することを検証することができる。

20

【0161】

【数46】

$$\frac{\phi_1}{2} = \cot^{-1} \left( \frac{I_1}{2\sqrt{1 - \frac{I_1^2}{4}}} \right); \text{ および} \quad (2)$$

30

$$\frac{\phi_2}{2} = \cot^{-1} \left( \frac{I_2}{2\sqrt{1 - \frac{I_2^2}{4}}} \right), \quad (3)$$

【0162】

ただし、 $I_1$ および $I_2$ はそれぞれ、フェーザ

【0163】

40

【数47】

$$\overrightarrow{I_1}$$

【0164】

【数48】

$$\overrightarrow{I_2}$$

【0165】

の正規化された大きさを表し、 $I_1$ および $I_2$ の領域は、方程式(2)および(3)が有効である領域に従って適切に制限される。方程式(2)および(3)は、相対位相シフトを

50

正規化された大きさに関係付けるための 1 つの表現であることに留意されたい。また、方程式 (2) および (3) の他の、解法、等価表現および / または簡約表現を採用してもよい。また、相対位相シフトを正規化された大きさに関係付けるルックアップテーブルを使用してもよい。

【0166】

上述の概念を、図 4 に例示するように、信号  $r(t)$  の虚フェーザまたは直交成分部に同様に適用することができる。したがって、いずれかの時刻  $t$  で、信号  $r(t)$  の虚フェーザ部

【0167】

【数 49】

10

【0168】

を、ほぼ等しくかつ一定の大きさの上側および下側フェーザ成分

【0169】

【数 50】

【0170】

20

および

【0171】

【数 51】

【0172】

を加算することによって、得ることができる。この実施例では、

【0173】

【数 52】

30

【0174】

および

【0175】

【数 53】

は、

【0176】

40

【数 54】

【0177】

に対して、時間  $t$  での

【0178】

【数 55】

50

【0179】

の大きさに従って設定された角度だけ、位相において対称的にシフトされる。

【0180】

【数56】

$\overline{\overrightarrow{Q}_U}$

【0181】

および

【0182】

【数57】

10

$\overline{\overrightarrow{Q}_L}$

【0183】

の、所望のフェーザ

【0184】

【数58】

$\overline{\overrightarrow{Q}}$

【0185】

20

に対する関係は、 $Q_U$ および $Q_L$ をそれぞれ $I_U$ および $I_L$ の代わりに用いることによって、方程式2および3に定義されたように関係付けられる。

【0186】

上記の考察から、フェーザ表現では、可変の大きさおよび位相のいずれかのフェーザ

【0187】

【数59】

$\overline{\overrightarrow{R}}$

【0188】

30

を、4つのほぼ一定の大きさのフェーザ成分の和によって構成することができるということになる。

【0189】

【数60】

$$\overline{\overrightarrow{R}} = \overline{\overrightarrow{I}_U} + \overline{\overrightarrow{I}_L} + \overline{\overrightarrow{Q}_U} + \overline{\overrightarrow{Q}_L};$$

$$\overline{\overrightarrow{I}_U} + \overline{\overrightarrow{I}_L} = \overline{\overrightarrow{I}};$$

$$\overline{\overrightarrow{Q}_U} + \overline{\overrightarrow{Q}_L} = \overline{\overrightarrow{Q}};$$

(4)

40

$$I_U = I_L = \text{定数} ;$$

$$Q_U = Q_L = \text{定数} ;$$

【0190】

ただし、 $I_U$ 、 $I_L$ 、 $Q_U$ および $Q_L$ はそれぞれ、フェーザ

【0191】

【数61】

$\overrightarrow{I_U}, \overrightarrow{I_L}, \overrightarrow{Q_U}$

【0192】

および

【0193】

【数62】

$\overrightarrow{Q_L}$

10

【0194】

の大きさを表す。

【0195】

対応して、時間領域では、時変複素包絡線正弦波信号  $r(t) = R(t) \cos(\phi(t))$  は、以下のように、4つの定包絡線信号の和によって構成される。

【0196】

【数63】

$$r(t) = I_U(t) + I_L(t) + Q_U(t) + Q_L(t);$$

20

$$I_U(t) = \text{sgn}(\overrightarrow{I}) \times I_U \times \cos\left(\frac{\phi_I}{2}\right) \times \cos(\omega t) + I_U \times \sin\left(\frac{\phi_I}{2}\right) \times \sin(\omega t);$$

$$I_L(t) = \text{sgn}(\overrightarrow{I}) \times I_L \times \cos\left(\frac{\phi_I}{2}\right) \times \cos(\omega t) - I_L \times \sin\left(\frac{\phi_I}{2}\right) \times \sin(\omega t); \quad (5)$$

$$Q_U(t) = -\text{sgn}(\overrightarrow{Q}) \times Q_U \times \cos\left(\frac{\phi_Q}{2}\right) \times \sin(\omega t) + Q_U \times \sin\left(\frac{\phi_Q}{2}\right) \times \cos(\omega t);$$

$$Q_L(t) = -\text{sgn}(\overrightarrow{Q}) \times Q_L \times \cos\left(\frac{\phi_Q}{2}\right) \times \sin(\omega t) - Q_L \times \sin\left(\frac{\phi_Q}{2}\right) \times \cos(\omega t). \quad (5)$$

30

【0197】

ただし、

【0198】

【数64】

$$\text{sgn}(\overrightarrow{I}) = \pm 1$$

【0199】

であり、

40

【0200】

【数65】

$\overrightarrow{I}$

【0201】

が正の実軸と同相であるか、180度異相であるかによって決まる。同様に、

【0202】

【数66】

$$\overline{\text{sgn}(\overline{Q})} = \pm 1$$

であり、

【0203】

【数67】

$$\overline{Q}$$

【0204】

10

が虚軸と同相であるか、180度異相であるかによって決まる。

【0205】

【数68】

$$\frac{\phi_I}{2}$$

【0206】

は、実軸に対する

【0207】

【数69】

20

$$\overline{I_U}$$

および

【0208】

【数70】

$$\overline{I_L}$$

【0209】

30

の位相シフトに対応する。同様に、

【0210】

【数71】

$$\frac{\phi_Q}{2}$$

【0211】

は、虚軸に対する

【0212】

【数72】

40

$$\overline{Q_U}$$

【0213】

および

【0214】

【数73】

$$\overline{Q_L}$$

50

【0215】

の位相シフトに対応する。

【0216】

【数74】

$$\frac{\phi_I}{2}$$

【0217】

および

【0218】

【数75】

$$\frac{\phi_Q}{2}$$

【0219】

を、(2)および(3)で与えられた方程式を用いて計算することができる。

【0220】

方程式(5)を、さらに以下のように簡約することができる。

【0221】

【数76】

$$r(t) = I_U(t) + I_L(t) + Q_U(t) + Q_L(t);$$

$$I_U(t) = \text{sgn}(\bar{I}) \times I_{UX} \times \cos(\omega t) + I_{UY} \times \sin(\omega t);$$

$$I_L(t) = \text{sgn}(\bar{I}) \times I_{UX} \times \cos(\omega t) - I_{UY} \times \sin(\omega t); \quad (6)$$

$$Q_U(t) = -Q_{UX} \times \cos(\omega t) + \text{sgn}(\bar{Q}) \times Q_{UY} \times \sin(\omega t);$$

$$Q_L(t) = Q_{UY} \times \cos(\omega t) - \text{sgn}(\bar{Q}) \times Q_{UX} \times \sin(\omega t).$$

10

【0222】

ただし、

【0223】

【数77】

$$I_{UX} = I_U \times \cos\left(\frac{\phi_I}{2}\right) = I_L \times \cos\left(\frac{\phi_I}{2}\right)$$

$$I_{UY} = I_U \times \sin\left(\frac{\phi_I}{2}\right) = I_L \times \sin\left(\frac{\phi_I}{2}\right)$$

$$Q_{UX} = Q_U \times \sin\left(\frac{\phi_Q}{2}\right) = Q_L \times \sin\left(\frac{\phi_Q}{2}\right) \quad , \quad \text{および} \quad Q_{UY} = Q_U \times \cos\left(\frac{\phi_Q}{2}\right) = Q_L \times \cos\left(\frac{\phi_Q}{2}\right)$$

40

【0224】

方程式(5)および(6)における時間領域表現は正弦波形の場合について提供されたが、等価表現を非正弦波形について、適切な基底関数を用いて展開することができることは、当業者には理解できよう。さらに、当業者には本明細書の教示に基づいて理解されるように、ほぼ一定の包絡線信号への上述の2次元分解を、適切に多次元分解に拡張することができる。

【0225】

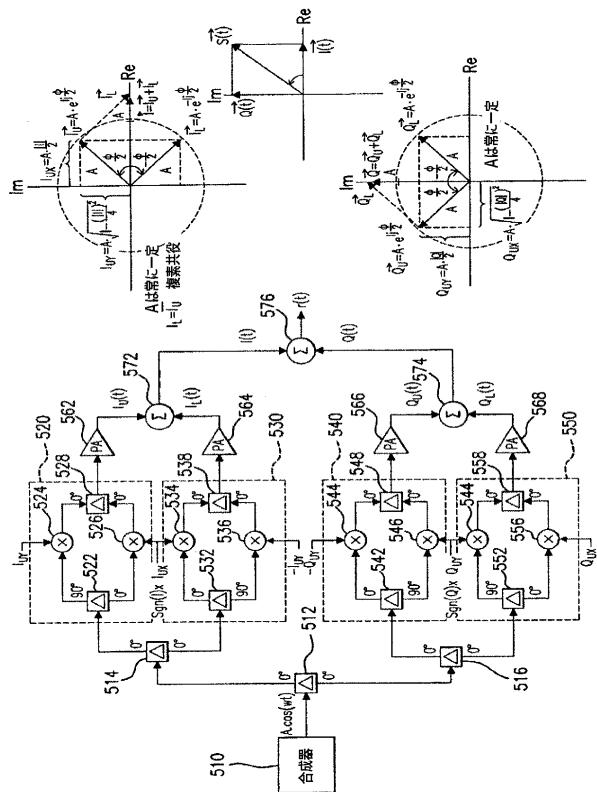

図5は、デカルト4分岐VPAの実施形態の一実施例のブロック図である。所望の電力レベルおよび周波数特性の出力信号r(t)578は、デカルト4分岐VPAの実施形態によるベースバンド同相および直交成分から生成される。

50

## 【0226】

図5の実施例では、合成器510など、周波数発生器は、出力信号 $r(t)578$ と同じ周波数を有する基準信号 $A * \cos(t)511$ を生成する。基準信号の選択が所望の出力信号に従って行われることは、当業者には理解できよう。例えば、所望の出力信号の所望の周波数が2.4GHzである場合、基準信号の周波数は2.4GHzに設定される。このように、本発明の実施形態は、周波数アップコンバージョンを達成する。

## 【0227】

図5を参照すると、1つまたは複数の分相器が、信号521、531、541および551を基準信号511に基づいて生成するために使用される。図5の実施例では、これは、分相器512、514および516を使用して、0度位相シフトを分相器の各々で適用することによって行われる。しかし、基準信号511の信号521、531、541および551を生成するために、様々な技術を使用してもよいことは、当業者には理解されよう。例えば、1:4分相器を、单一のステップで、あるいは図5の実施例の実施形態において、4つのレプリカ521、531、541および551を生成するために使用してもよく、信号511を、信号521、531、541、551に直結することができる。実施形態に応じて、様々な位相シフトを適用して、所望の信号521、531、541および551の結果となるようにしてもよい。

10

## 【0228】

なお、図5を参照すると、信号521、531、541および551がそれぞれ、対応するベクトル変調器520、530、540および550に、それぞれ提供される。ベクトル変調器520、530、540および550は、それらの適切な入力信号と共に、(6)で提供された方程式に従って、信号 $r(t)$ の4つの定包絡線成分を生成する。図5の実施例の実施形態では、ベクトル変調器520および530は、信号 $r(t)$ の $I_u(t)$ および $I_L(t)$ 成分をそれぞれ生成する。同様に、ベクトル変調器540および550は、信号 $r(t)$ の $Q_u(t)$ および $Q_L(t)$ 成分をそれぞれ生成する。

20

## 【0229】

ベクトル変調器520、530、540および550の各々の実際の実装は、変わるものがある。例えば、(6)における方程式に従って定包絡線成分を生成するために様々な技術が存在することは、当業者には理解されよう。

30

## 【0230】

図5の実施例の実施形態では、ベクトル変調器520、530、540、550の各々は、信号522、531、541、551を位相整合するための入力分相器(`input phase splitter`)522、532、542、552を含む。したがって、入力分相器522、532、542、552は、同相および直交成分またはそれらの各入力信号を生成するために使用される。

## 【0231】

各ベクトル変調器520、530、540、550では、同相および直交成分が振幅情報で乗算される。図5では、例えば、乗算器524は、信号521の直交成分を $I_u(t)$ の直交振幅情報 $I_{uY}$ で乗算する。並行して、乗算器526は、同相レプリカ信号を $I_u(t)$ の同相振幅情報 $sgn(I) \times I_{uX}$ で乗算する。

40

## 【0232】

$I_u(t)$ を生成するために、定包絡線成分信号525および527が、分相器528または代替加算技術を用いて加算される。結果として生じる信号529は、信号 $r(t)$ の $I_U(t)$ 成分に対応する。

## 【0233】

上述と類似の方法で、ベクトル変調器530、540および550は、信号 $r(t)$ の $I_L(t)$ 、 $Q_u(t)$ および $Q_L(t)$ 成分をそれぞれ生成する。 $I_L(t)$ 、 $Q_u(t)$ および $Q_L(t)$ は、図5の信号539、549および559にそれぞれ対応する。

## 【0234】

さらに、上述のように、信号529、539、549および559は、ほぼ等しくかつ

50

一定の大きさの包絡線を有することによって特性化される。したがって、信号 529、539、549 および 559 が対応する電力増幅器 (PA) 562、564、566 および 568 に入力されるとき、対応する増幅された信号 563、565、567 および 569 は、ほぼ一定の包絡線信号である。

## 【0235】

電力増幅器 562、564、566 および 568 は、信号 529、539、549、559 の各々をそれぞれ増幅する。一実施形態では、ほぼ等しい電力増幅が信号 529、539、549 および 559 の各々に適用される。一実施形態では、PA 562、564、566 および 568 の電力増幅レベルは、出力信号  $r(t)$  の所望の電力レベルに従って設定される。

10

## 【0236】

なお、図 5 を参照すると、増幅された信号 563 および 565 が、加算器 572 を使用して加算されて、信号  $r(t)$  の同相成分

## 【0237】

## 【数 78】

$\bar{I}(t)$

## 【0238】

の増幅されたバージョン 573 が生成される。同様に、増幅された信号 567 および 569 が、加算器 574 を使用して加算されて、信号  $r(t)$  の直交成分

20

## 【0239】

## 【数 79】

$\bar{Q}(t)$

## 【0240】

の増幅されたバージョン 575 が生成される。

## 【0241】

信号 573 および 575 が、図 5 に示すように、加算器 576 を使用して加算され、結果として生じる信号は所望の出力信号  $r(t)$  に対応する。

30

## 【0242】

図 5 の実施例では、加算器 572、574 および 576 は例示のためにのみ使用されていることに留意されたい。様々な技術を、増幅された信号 563、565、567 および 569 を加算するために使用してもよい。例えば、増幅された信号 563、565、567 および 569 をすべて 1 つのステップで加算して、信号 578 の結果としてもよい。実際には、本発明の様々な VPA の実施形態によれば、加算が増幅後に行われれば、十分である。本発明のある VPA の実施形態は、以下でさらに説明するように、ワイヤを介した直結など、損失が最低限の加算技術を使用する。別法として、ある VPA の実施形態は、従来の電力結合技術を使用する。他の実施形態では、以下でさらに説明するように、電力増幅器 562、564、566 および 568 を、多入力 1 出力の電力増幅器として実装することができる。

40

## 【0243】

デカルト 4 分岐 VPA の実施形態の動作を、図 6 のプロセス流れ図を参照してこれからさらに説明するものとする。このプロセスは、所望の出力信号のベースバンド表現を受信することを含む、ステップ 610 で開始する。一実施形態では、これは、所望の出力信号の同相 (I) および直交 (Q) 成分を受信することを含む。別の実施形態では、これは、所望の出力信号の大きさおよび位相を受信することを含む。デカルト 4 分岐 VPA の実施形態の一実施形態では、I および Q はベースバンド成分である。別の実施形態では、I および Q は RF 成分であり、ベースバンドへダウンコンバートされる。

## 【0244】

50

ステップ 620 は、所望の出力信号の所望の出力信号周波数に従って設定されたクロック信号を受信することを含む。図 5 の実施例では、ステップ 620 は、基準信号 511 を受信することによって達成される。

【0245】

ステップ 630 は、I 成分を処理して、出力信号周波数を有する第 1 および第 2 の信号を生成することを含む。第 1 および第 2 の信号は、ほぼ一定かつ等しい大きさの包絡線、および、I 成分に等しい和を有する。第 1 および第 2 の信号は、上述の  $I_U(t)$  および  $I_L(t)$  定包絡線成分に対応する。図 5 の実施例では、ステップ 630 は、ベクトル変調器 520 および 530 によって、それらの適切な入力信号と共に、達成される。

【0246】

ステップ 640 は、Q 成分を処理して、出力信号周波数を有する第 3 および第 4 の信号を生成することを含む。第 3 および第 4 の信号は、ほぼ一定かつ等しい大きさの包絡線、および、Q 成分に等しい和を有する。第 3 および第 4 の信号は、上述の  $Q_U(t)$  および  $Q_L(t)$  定包絡線成分に対応する。図 5 の実施例では、ステップ 630 は、ベクトル変調器 540 および 550 によって、それらの適切な入力信号と共に、達成される。

【0247】

ステップ 650 は、第 1、第 2、第 3 および第 4 の信号の各々を個別に増幅し、増幅された信号を加算して、所望の出力信号を生成することを含む。一実施形態では、第 1、第 2、第 3 および第 4 の信号の増幅はほぼ等しく、所望の出力信号の所望の電力レベルによるものである。図 5 の実施例では、ステップ 650 は、電力増幅器 562、564、566 および 568 が各信号 529、539、549 および 559 を増幅することによって、かつ、加算器 572、574 および 576 が、増幅された信号 563、565、567 および 569 を加算して、出力信号 578 を生成することによって達成される。

【0248】

図 7A は、図 6 のプロセス流れ図 600 を実装するベクトル電力増幅器 700 の例示的実施形態を例示するブロック図である。図 7A の実施例では、任意選択のコンポーネントが破線で例示される。他の実施形態では、追加のコンポーネントが任意選択であってもよい。

【0249】

ベクトル電力増幅器 700 は、同相 (I) 分岐 703 および直交 (Q) 分岐 705 を含む。I および Q 分岐の各々はさらに、第 1 の分岐および第 2 の分岐を備える。

【0250】

同相 (I) 情報信号 702 は、I データ伝達関数モジュール 710 によって受信される。一実施形態では、I 情報信号 702 は、デジタルベースバンド信号を含む。一実施形態では、I データ伝達関数モジュール 710 は、I 情報信号 702 をサンプルクロック 706 に従ってサンプルする。別の実施形態では、I 情報信号 702 はアナログベースバンド信号を含み、これが I データ伝達関数モジュール 710 に入力される前に、アナログ - デジタル変換器 (ADC) (図 7A に図示せず) を使用してデジタルに変換される。別の実施形態では、I 情報信号 702 は、I データ伝達関数モジュール 710 にアナログ形式で入力するアナログベースバンド信号を含み、I データ伝達関数モジュール 710 もまたアナログ回路を含む。別の実施形態では、I 情報信号 702 は、上述の実施形態のいずれかを使用して、I データ伝達関数モジュール 710 に入力される前にベースバンドにダウンコンバートされる、RF 信号を含む。

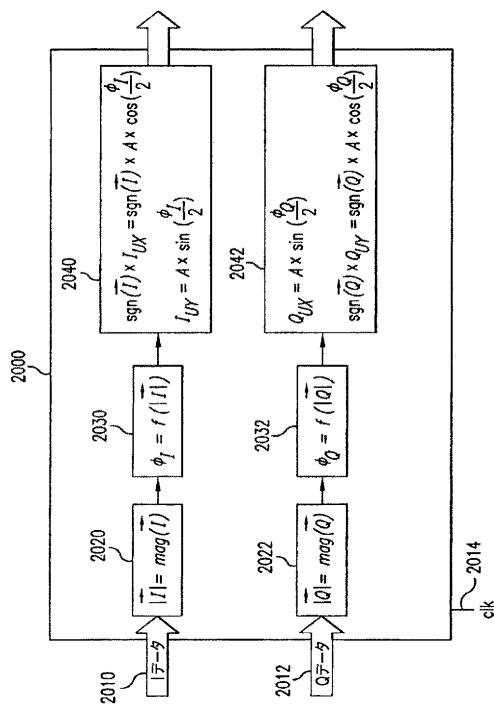

【0251】

I データ伝達関数モジュール 710 は、I 情報信号 702 を処理し、I 情報信号 702 の少なくとも 2 つの定包絡線成分信号の同相および直交振幅情報を決定する。図 5 を参照して上述したように、同相および直交ベクトル変調器入力振幅情報は、 $sgn(I) \times I_{UX}$  および  $I_{UY}$  にそれぞれ対応する。I データ伝達関数モジュール 710 の動作を、さらに以下でセクション 3.4 において説明する。

【0252】

10

20

30

40

50

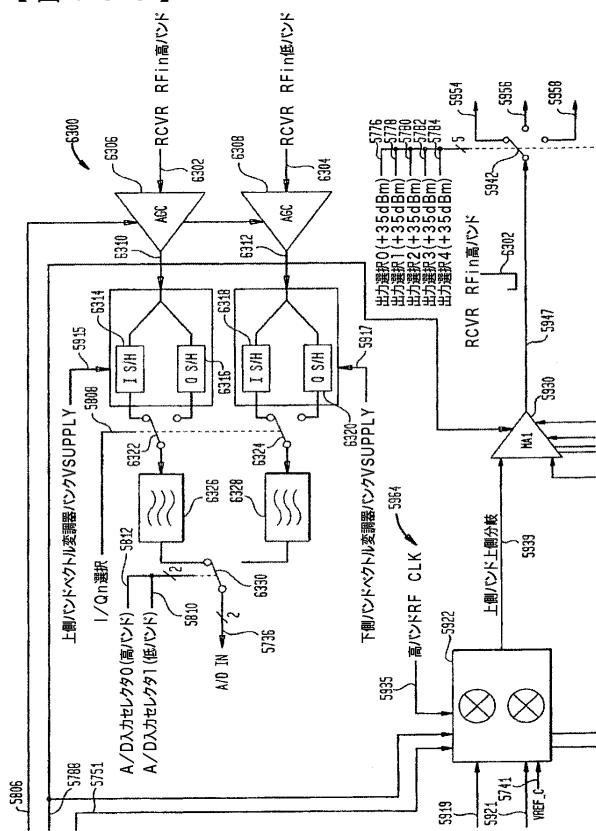

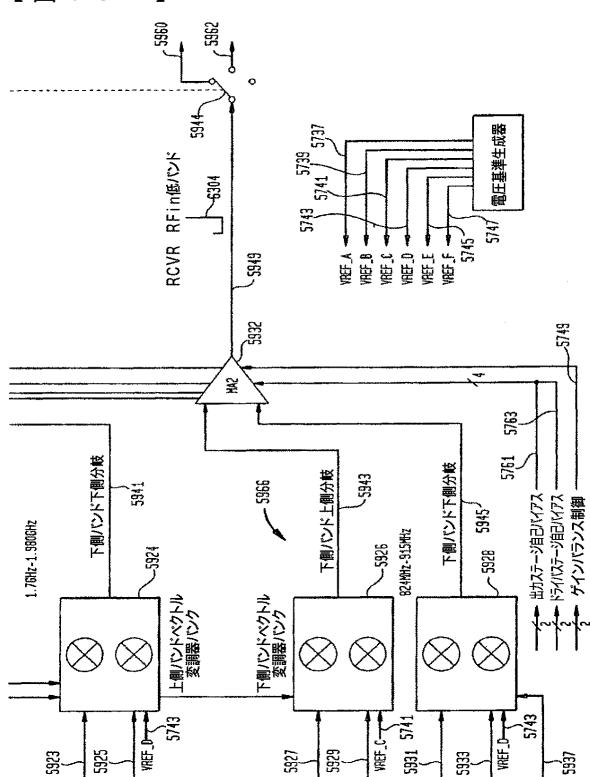

I データ伝達関数モジュール 710 は、ベクトル変調器 760 および 762 の同相および直交振幅成分を制御するために使用される、情報信号 702 および 724 を出力する。一実施形態では、信号 722 および 724 はデジタル信号である。したがって、信号 722 および 724 の各々は、対応するデジタル - アナログ変換器 (DAC) 730 および 732 にそれぞれ供給される。DAC 730 および 732 の分解能およびサンプルレートが、出力信号 782 の所望の I 成分を達成するために選択される。DAC 730 および 732 は、DAC クロック信号 723 および 725 によってそれぞれ制御される。DAC クロック信号 723 および 725 は、同じクロック信号から導出されてもよいし、独立であつてもよい。

## 【0253】

10

別の実施形態では、信号 722 および 724 はアナログ信号であり、DAC 730 および 732 は必要とされない。

## 【0254】

図 7A の例示的実施形態では、DAC 730 および 732 は、デジタル情報信号 722 および 724 を対応するアナログ信号に変換し、これらのアナログ信号を任意選択の補間フィルタ 731 および 733 にそれぞれ入力する。アンチエイリアスフィルタとしての機能も果たす補間フィルタ 731 および 733 は、DAC 出力を整形して、所望の出力波形を生成する。補間フィルタ 731 および 733 は、信号 740 および 742 をそれぞれ生成する。信号 741 は、信号 740 の逆を表す。信号 740 ~ 742 は、ベクトル変調器 760 および 762 に入力される。

20

## 【0255】

ベクトル変調器 760 および 762 は、信号 740 ~ 742 を、適切に位相整合されたクロック信号で乗算して、I 情報信号 702 の定包絡線成分を生成する。これらのクロック信号は、所望の出力信号周波数によるレートを有するチャネルクロック信号 708 から導出される。例えば、750 および 752 など、複数の分相器、および、ベクトル変調器乗算器に関連付けられたフェーザを、適切に位相整合されたクロック信号を生成するためには使用してもよい。

## 【0256】

図 7A の実施形態では、例えば、ベクトル変調器 760 は、直交振幅情報信号 740 により、90 度シフトされたチャネルクロック信号を変調する。並行して、ベクトル変調器 760 は、同相振幅情報信号 742 により、同相チャネルクロック信号を変調する。ベクトル変調器 760 は、2 つの変調された信号を結合して、I 情報信号 702 の第 1 の変調された定包絡線成分 761 を生成する。同様に、ベクトル変調器 762 は、I 情報信号 702 の第 2 の変調された定包絡線成分 763 を、信号 741 および 742 を使用して生成する。信号 761 および 763 はそれぞれ、図 5 を参照して説明した  $I_u(t)$  および  $I_L(t)$  定包絡線成分に対応する。

30

## 【0257】

並行して、かつ類似の方法で、ベクトル電力增幅器 700 の Q 分岐は、直交 (Q) 情報信号 704 の少なくとも 2 つの定包絡線成分信号を生成する。

## 【0258】

40

図 7A の実施形態では、例えば、ベクトル変調器 764 は、Q 情報信号 704 の第 1 の定包絡線成分 765 を、信号 744 および 746 を使用して生成する。同様に、ベクトル変調器 766 は、Q 情報信号 704 の第 2 の定包絡線成分 767 を、信号 745 および 746 を使用して生成する。

## 【0259】

図 5 に関して上述したように、成分信号 761、763、765 および 767 は、ほぼ等しくかつ一定の大きさの包絡線を有する。図 7A の例示的実施形態では、信号 761、763、765 および 767 は、対応する電力增幅器 (PA) 770、772、774 および 776 にそれぞれ入力される。PA 770、772、774 および 776 を、線形または非線形電力增幅器にすることができる。一実施形態では、PA 770、772、774

50

4 および 7 7 6 はスイッチング電力増幅器を含む。

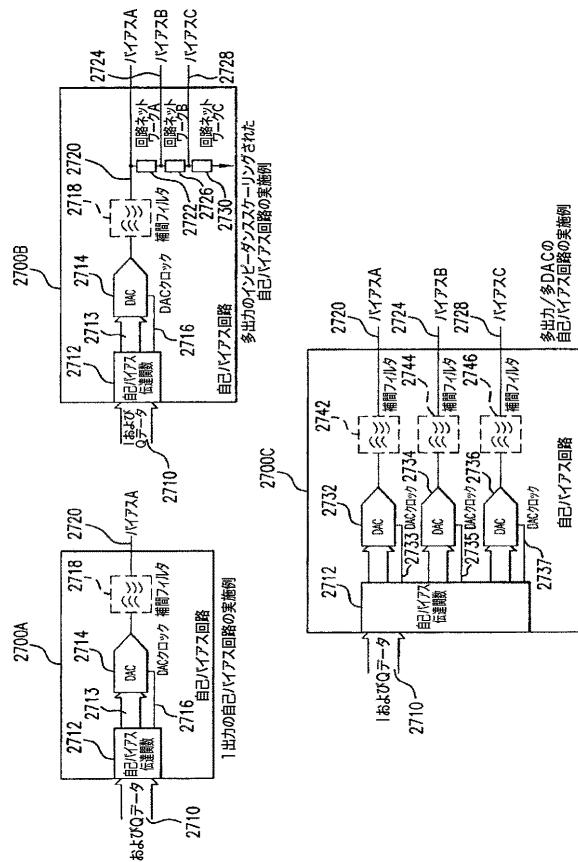

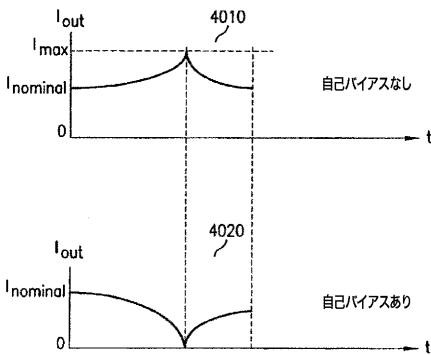

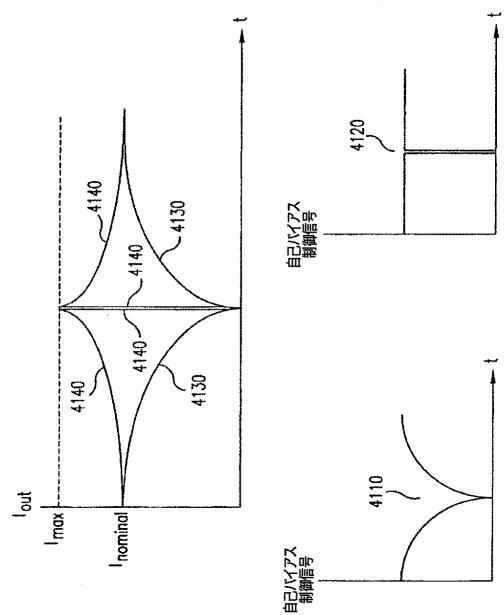

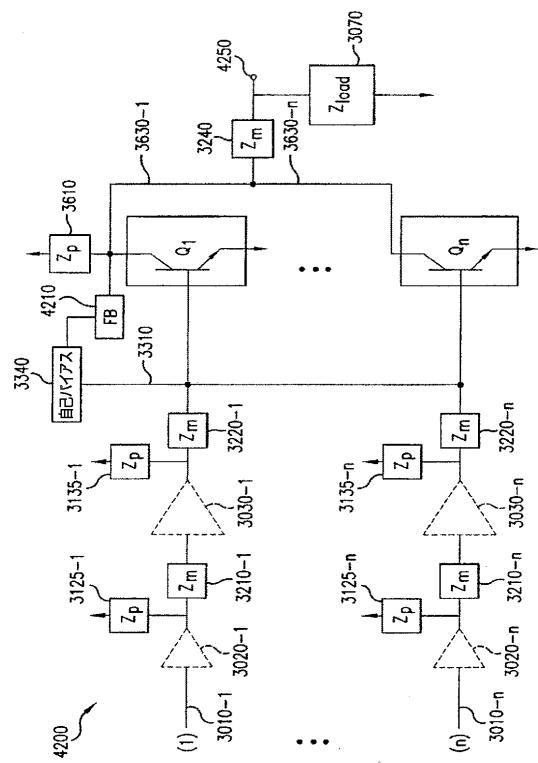

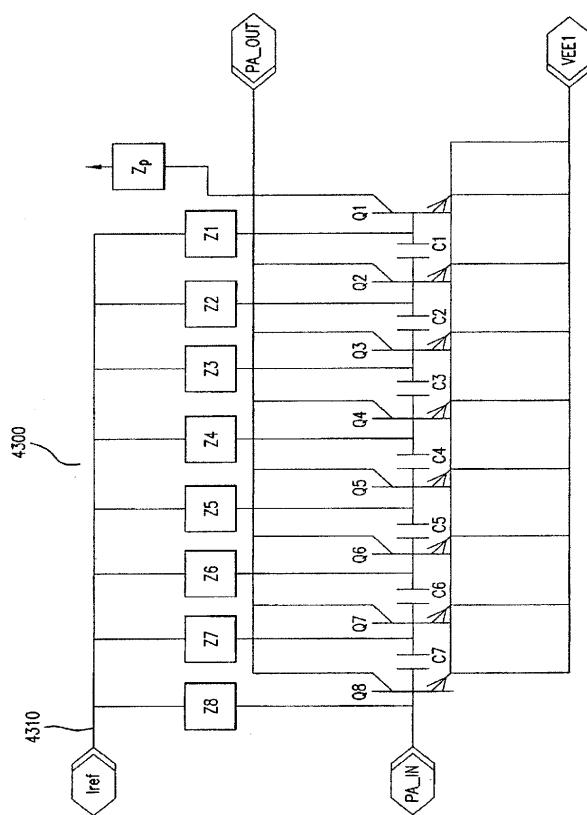

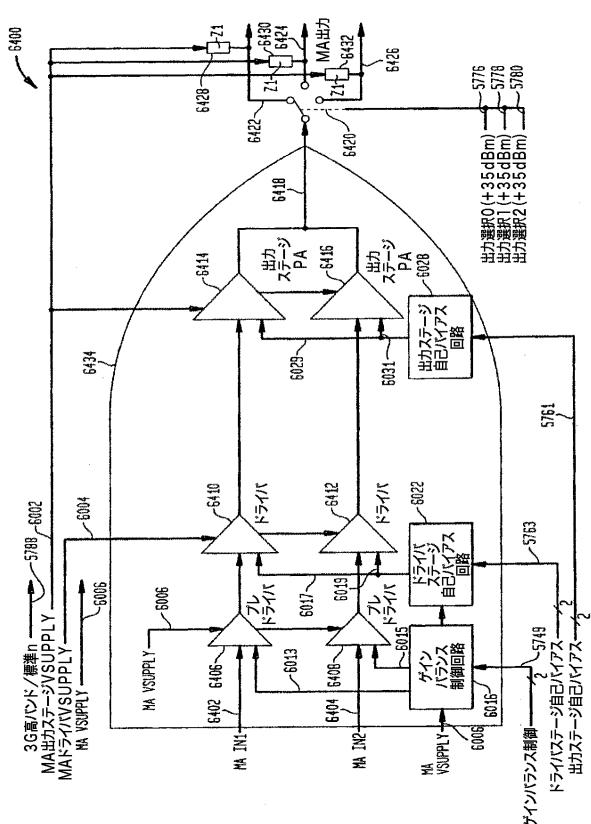

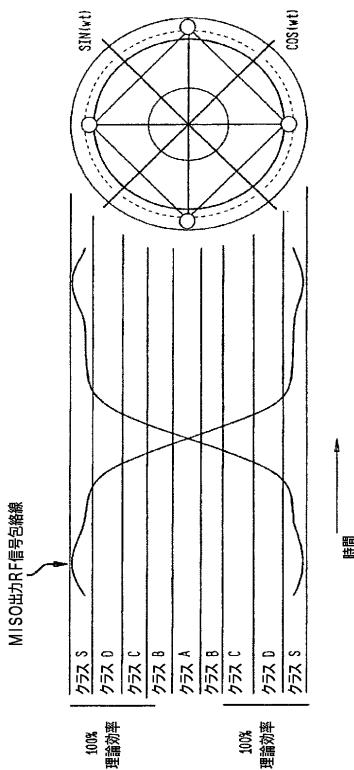

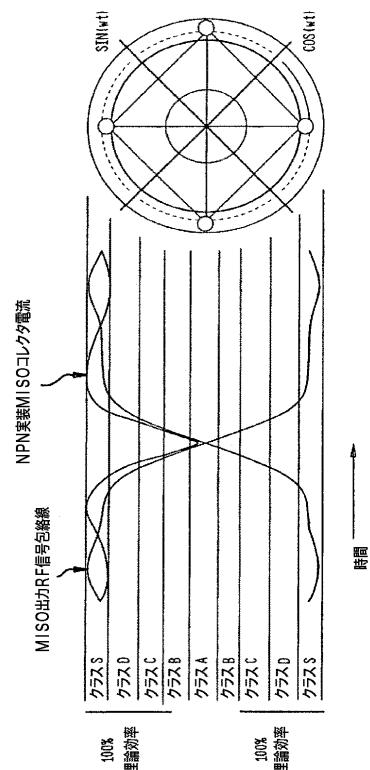

【0260】

回路 7 1 4 および 7 1 6 (本明細書で、参照を容易にするため、限定ではなく「自己バイアス回路」と称する)、および、この実施形態では、PA 7 7 0、7 7 2、7 7 4 および 7 7 6 のバイアスを、I および Q 情報信号 7 0 2 および 7 0 4 に従って制御する。図 7 A の実施形態では、自己バイアス回路 7 1 4 および 7 1 6 は、バイアス信号 7 1 5 および 7 1 7 をそれぞれ PA 7 7 0、7 7 2 および PA 7 7 4、7 7 6 に提供する。自己バイアス回路 7 1 4 および 7 1 6 を、さらに以下でセクション 3.5 において説明する。PA 7 7 0、7 7 2、7 7 4 および 7 7 6 の実施形態もまた、以下でセクション 3.5 において論じる。

10

【0261】

一実施形態では、PA 7 7 0、7 7 2、7 7 4 および 7 7 6 は、ほぼ等しい電力増幅をそれぞれのほぼ一定の包絡線信号 7 6 1、7 6 3、7 6 5 および 7 6 7 に適用する。他の実施形態では、PA ドライバが追加で採用されて、追加の電力増幅が提供される。図 7 A の実施形態では、PA ドライバ 7 9 4、7 9 5、7 9 6 および 7 9 7 が、ベクトル電力増幅器 7 0 0 の各分岐において、各ベクトル変調器 7 6 0、7 6 2、7 6 4、7 6 6 と各 PA 7 7 0、7 7 2、7 7 4 および 7 7 6 の間に、任意選択で追加される。

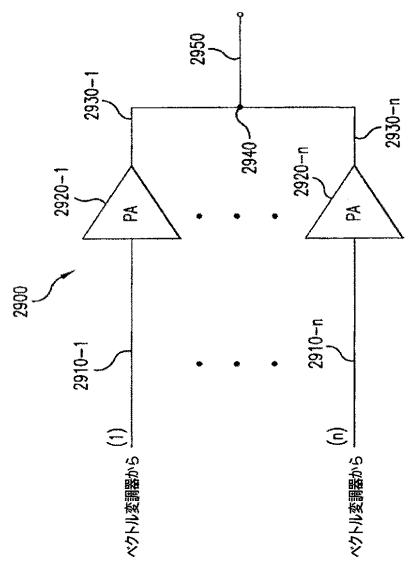

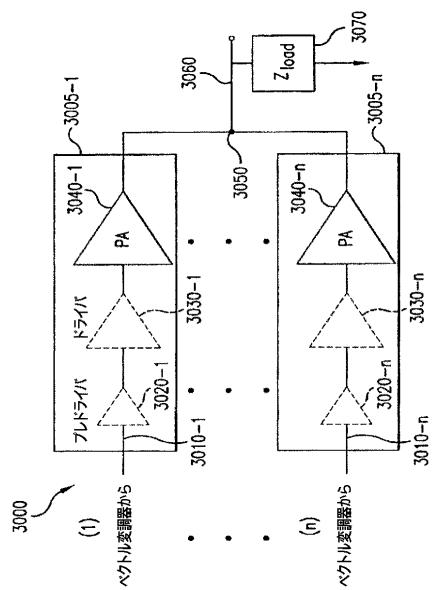

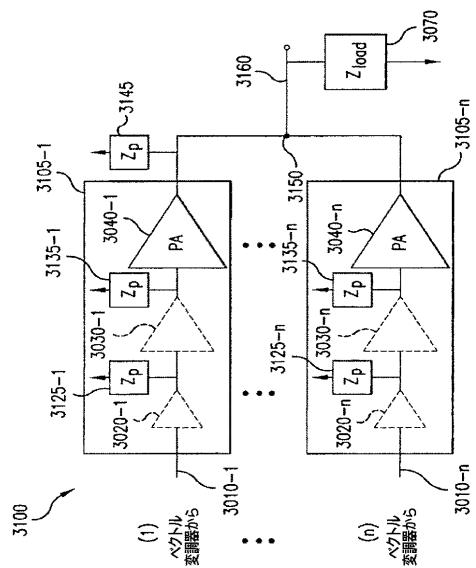

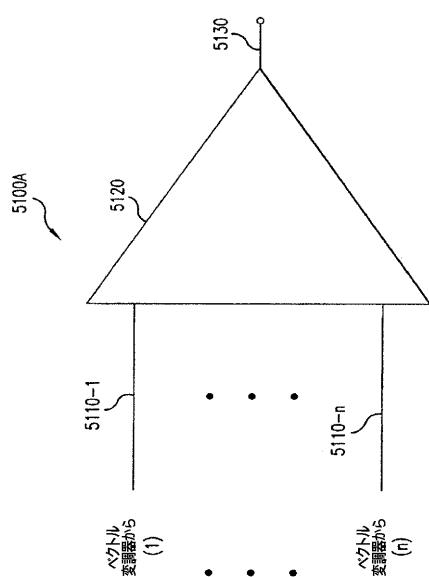

【0262】

PA 7 7 0、7 7 2、7 7 4 および 7 7 6 の出力が共に結合されて、ベクトル電力増幅器 7 0 0 の出力信号 7 8 2 が生成される。一実施形態では、ワイヤを使用して、PA 7 7 0、7 7 2、7 7 4 および 7 7 6 の出力が共に直結される。このような直結は、PA 7 7 0、7 7 2、7 7 4 および 7 7 6 の出力の間に抵抗性、誘導性または容量性の最小の絶縁があるか、あるいはないことを意味する。すなわち、PA 7 7 0、7 7 2、7 7 4 および 7 7 6 の出力は、介在するコンポーネントなしに共に結合される。別法として、一実施形態では、PA 7 7 0、7 7 2、7 7 4 および 7 7 6 の出力は、低または最小インピーダンス接続の結果となるインダクタンスおよび / またはキャパシタンス、および / または、最小の絶縁および最小の電力損失の結果となる接続を通じて、間接的に共に結合される。別法として、PA 7 7 0、7 7 2、7 7 4 および 7 7 6 の出力は、ウィルキンソン、ハイブリッド、変圧器、または既知のアクティブ結合器など、周知の結合技術を使用して結合される。一実施形態では、PA 7 7 0、7 7 2、7 7 4 および 7 7 6 は、統合された増幅および電力結合を单一の動作において提供する。一実施形態では、本明細書に記載した電力増幅器および / またはドライバの 1 つまたは複数は、多入力 1 出力の電力増幅技術を使用して実装され、その実施例を図 7 B および 5 1 A ~ H に図示する。

20

【0263】

出力信号 7 8 2 は、I および Q 情報信号 7 0 2 および 7 0 4 の I および Q 特性を含む。さらに、出力信号 7 8 2 は、その成分と同じ周波数、および、よって所望のアップコンバートされた出力周波数のものである。ベクトル電力増幅器 7 0 0 の実施形態では、プルアップインピーダンス (p u l l - u p i m p e d a n c e) 7 8 0 が、ベクトル増幅器 7 0 0 の出力と電源の間に結合される。本発明の電力増幅方法およびシステムによる出力ステージの実施形態を、さらに以下でセクション 3.5 において説明する。

30

【0264】

ベクトル電力増幅器 7 0 0 の他の実施形態では、プロセス検出器が採用されて、増幅器の回路におけるいかなるプロセス変動もが補償される。図 7 A の実施形態では、例えば、プロセス検出器 7 9 1 ~ 7 9 3 が任意選択で追加されて、PA ドライバ 7 9 4 ~ 7 9 7 および分相器 7 5 0 における変動が監視される。さらなる実施形態では、周波数補償回路 7 9 9 を採用して、周波数変動を補償してもよい。

40

【0265】

図 7 B は、ベクトル電力増幅器 7 0 0 の別の例示的実施形態を例示するブロック図である。任意選択のコンポーネントが破線で例示されるが、他の実施形態は、より多くのあるいはより少ない任意選択のコンポーネントを有してもよい。

50

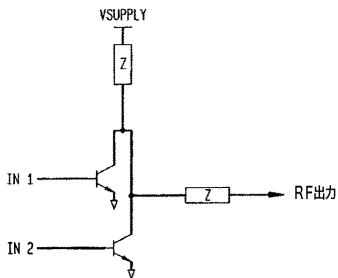

## 【0266】

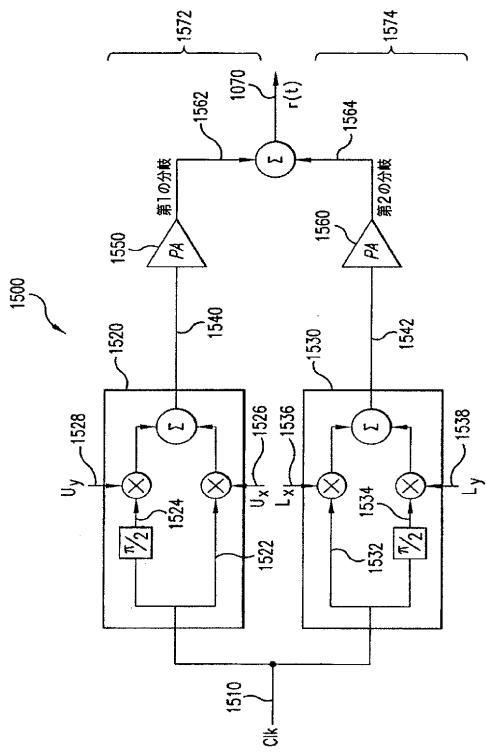

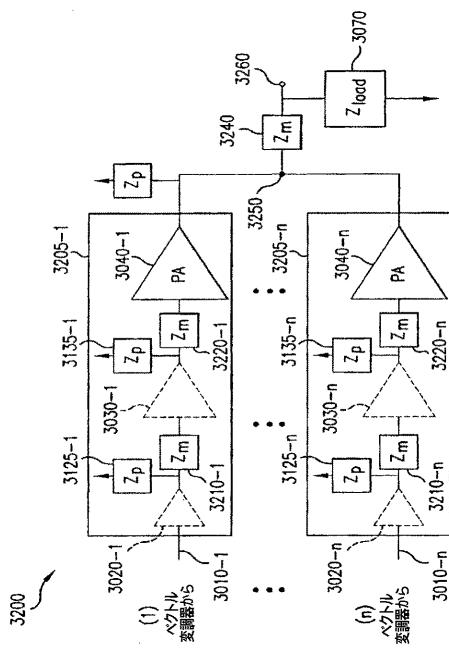

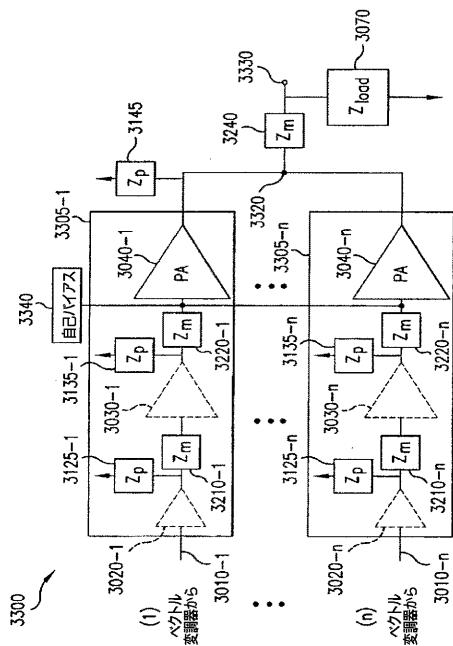

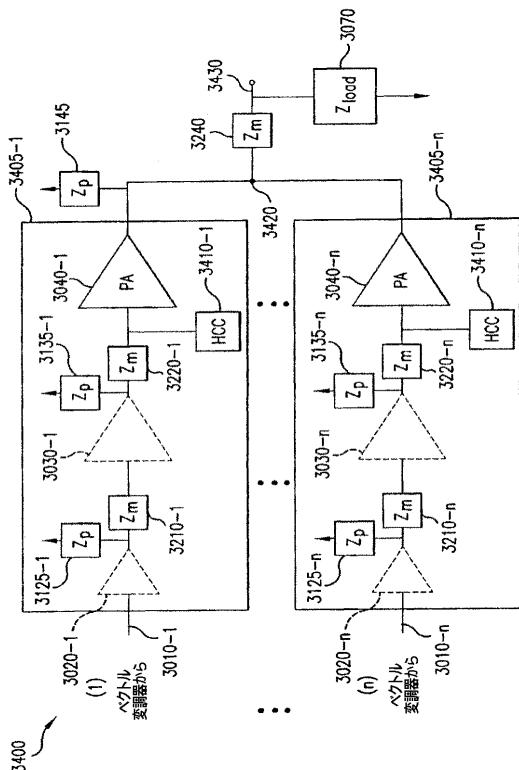

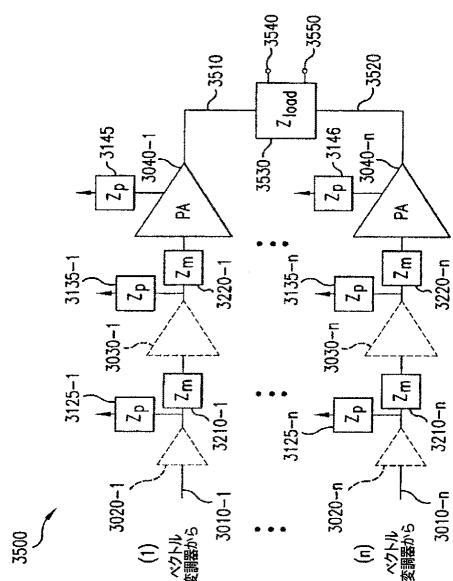

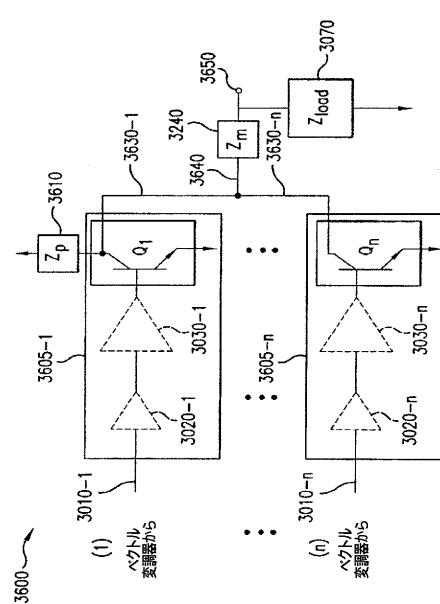

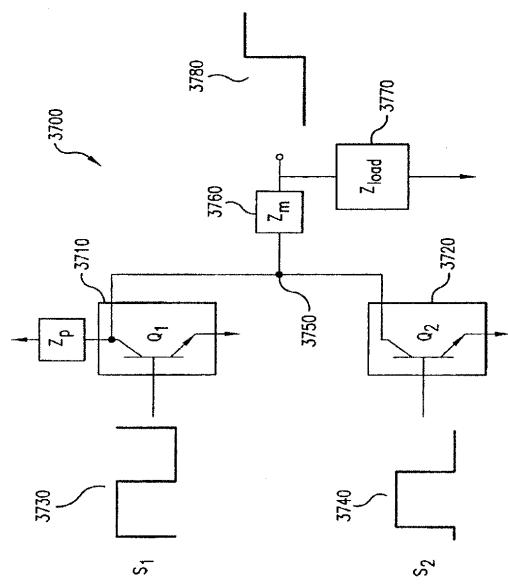

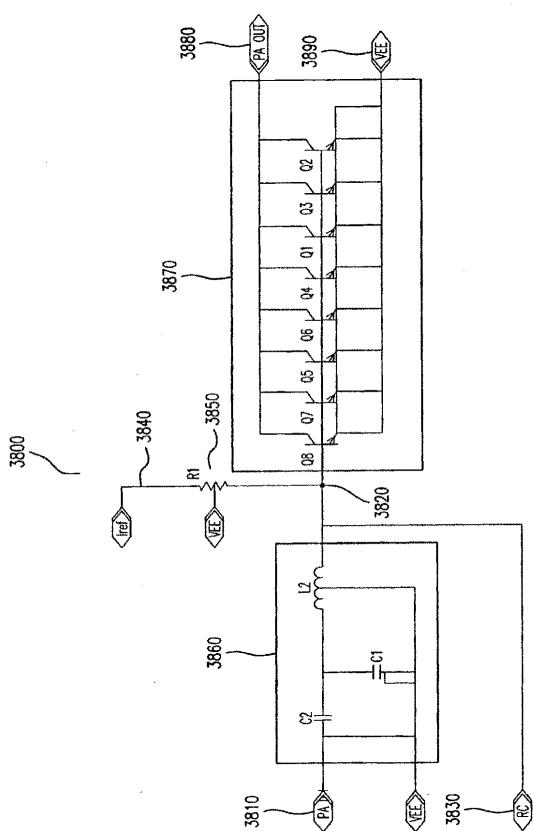

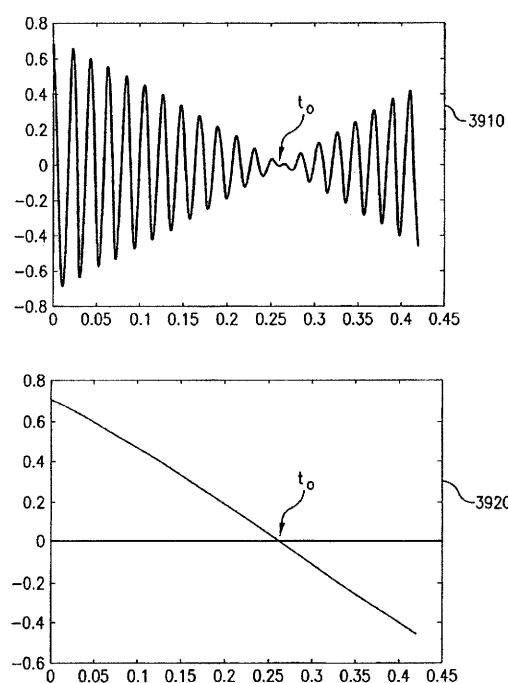

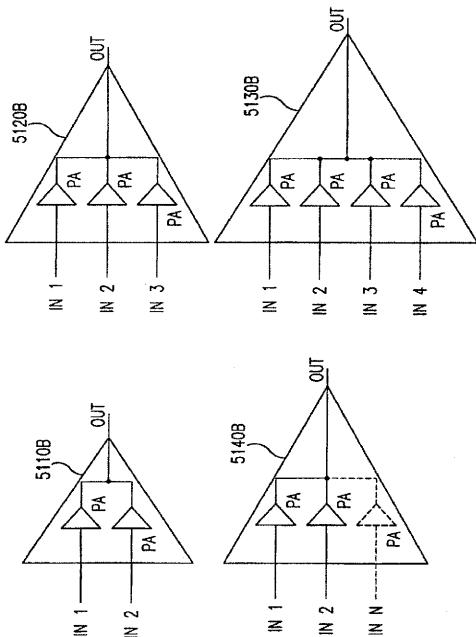

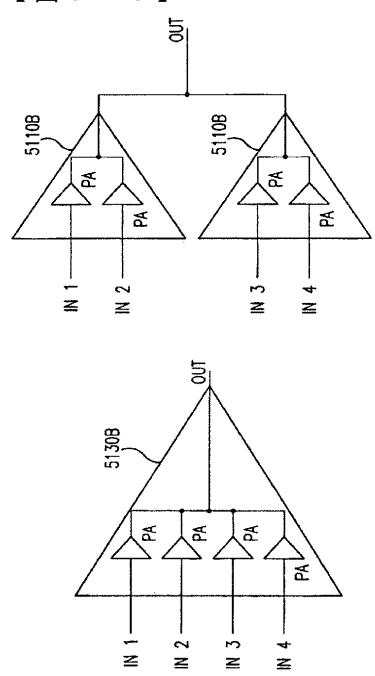

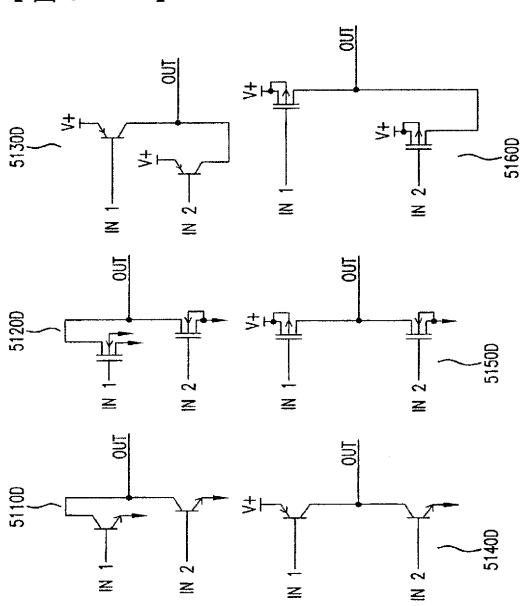

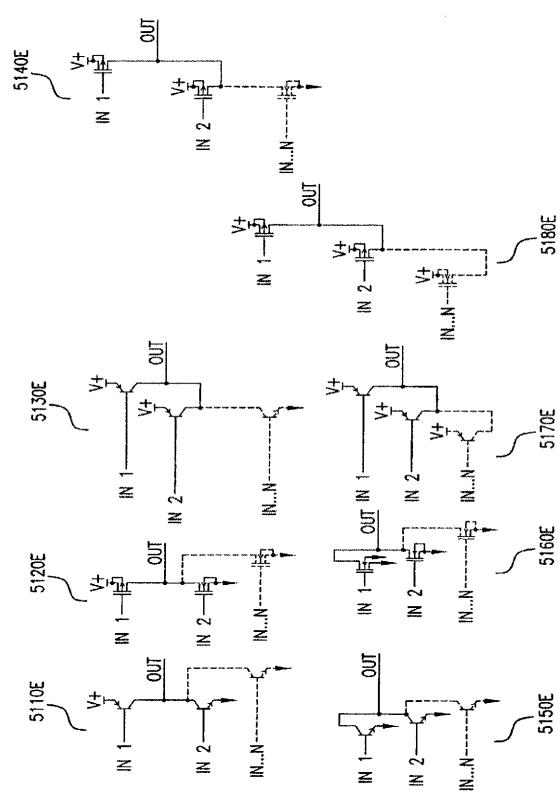

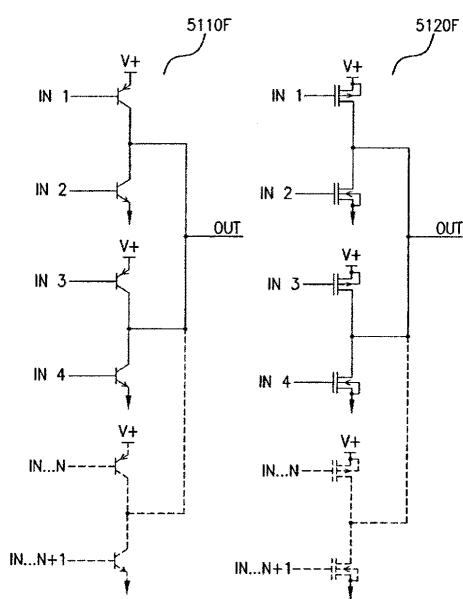

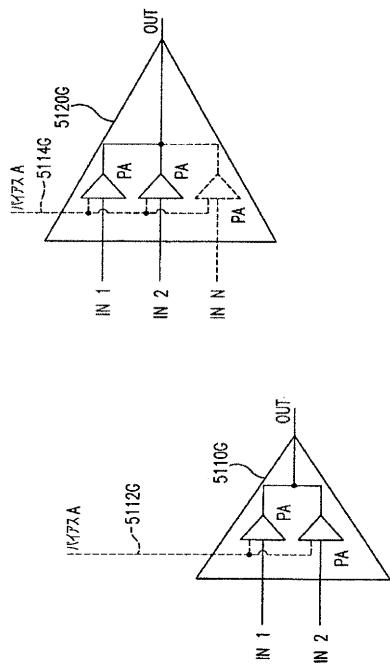

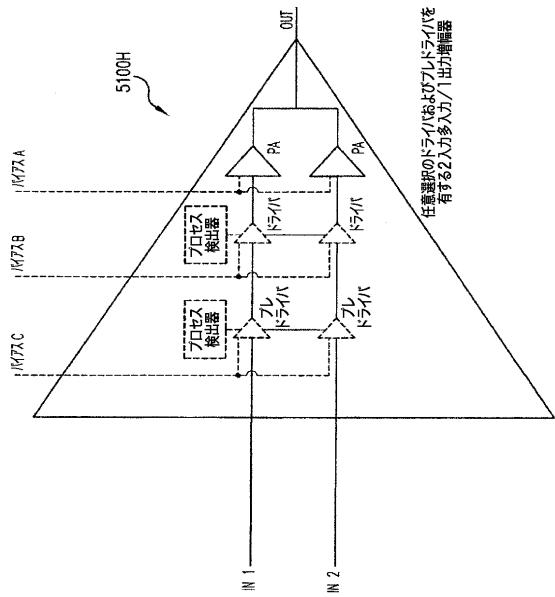

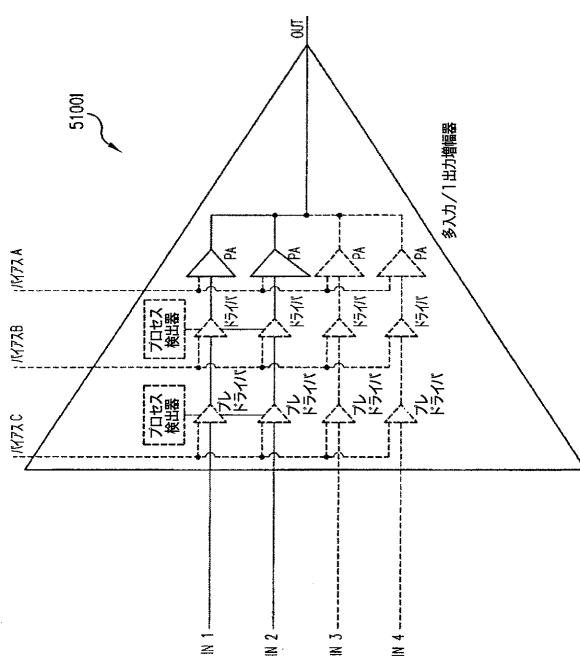

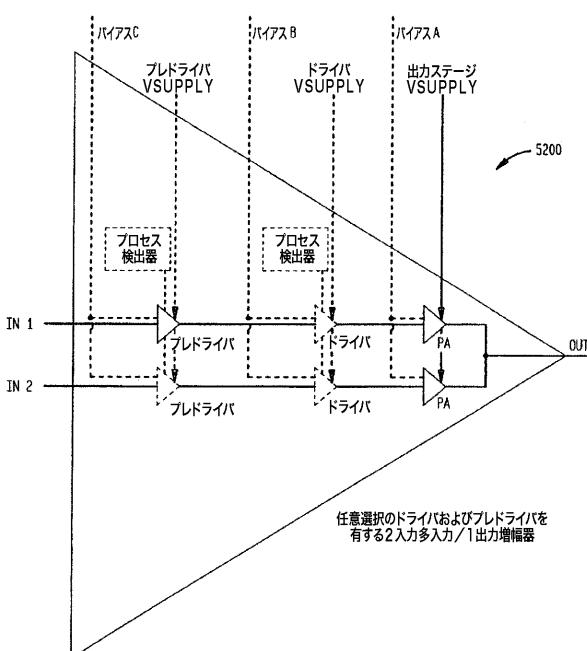

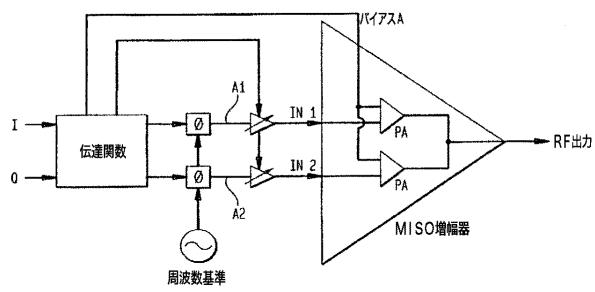

この実施形態は、図7Aの増幅器の多入力1出力(MISO)実装を例示する。図7Bの実施形態では、ベクトル変調器760、762、764および766から出力された、定包絡線信号761、763、765および767が、MISO PA784および786に入力される。MISO PA784および786は、2入力1出力の電力増幅器である。一実施形態では、MISO PA784および786は、図7Aの実施形態に示すような素子770、772、774、776、794～797、またはその機能的均等物を含む。別の実施形態では、MISO PA784および786は、任意選択のプレドライバおよび任意選択のプロセス検出回路など、他の素子を含んでもよい。さらに、MISO PA784および786は、図7Bに示すような2入力PAであることに限定されない。他の実施形態では、以下で図51A～Hを参照してさらに説明するように、PA784および786は、いかなる数の入力および出力を有することもできる。10

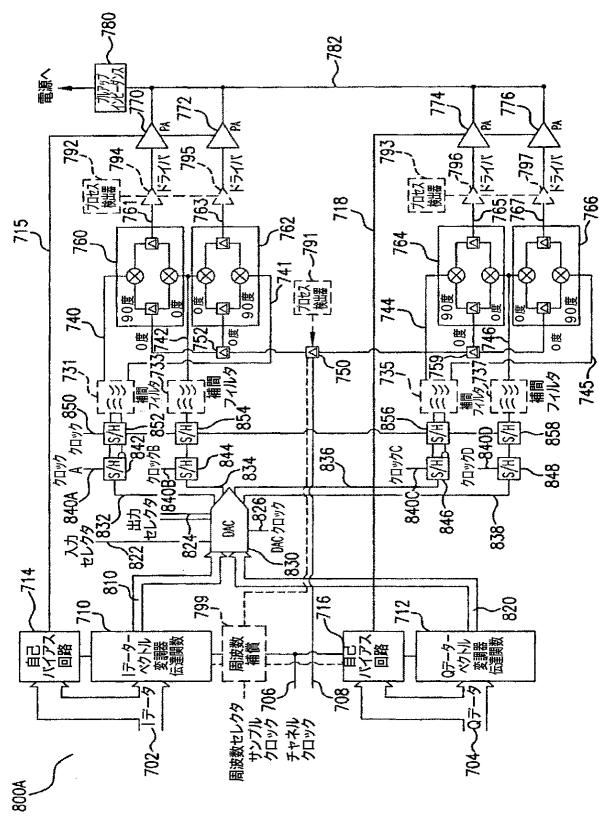

## 【0267】

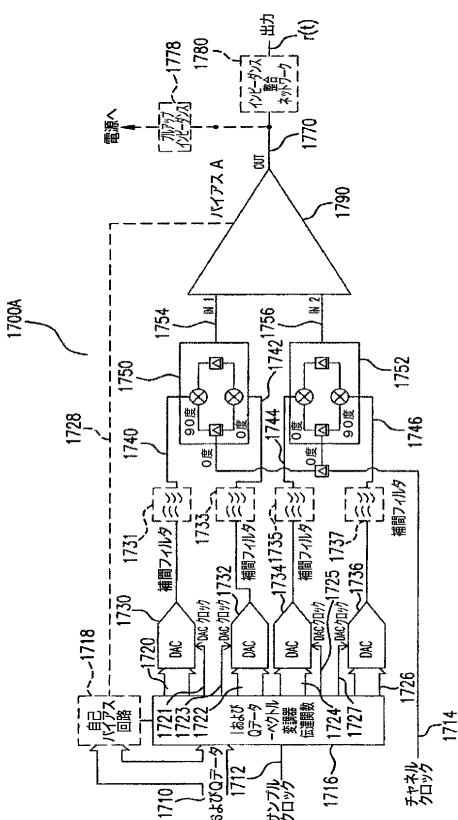

図8Aは、図6に示したデカルト4分岐VPA方法によるベクトル電力増幅器の別の例示的実施形態800Aを例示するブロック図である。任意選択のコンポーネントが破線で例示されるが、他の実施形態は、より多くのあるいはより少ない任意選択のコンポーネントを有してもよい。

## 【0268】

図8Aの実施形態では、十分な分解能およびサンプルレートのDAC830が、図7Aの実施形態のDAC730、732、734および736に取って代わる。DAC830のサンプルレートは、DACクロック信号826によって制御される。20

## 【0269】

DAC830は、同相および直交情報信号810および820を、Iデータ伝達関数モジュール710およびQデータ伝達関数モジュール712からそれぞれ上述のように受信する。一実施形態では、入力セレクタ822は、信号810および820がDAC830に入力される順序を選択する。

## 【0270】

DAC830は、一度に単一のアナログ信号を出力してもよい。一実施形態では、図8Aに示すように、サンプルホールドアーキテクチャを使用して、増幅器の4つの分岐に対する適切な信号タイミングを保証してもよい。30

## 【0271】

DAC830は、アナログ信号832、834、836、838を、第1のセットのサンプルホールド回路842、844、846および848へ、順次出力する。一実施形態では、DAC830は、図7Aの実施形態のDAC730、732、734および736の動作をエミュレートするために、十分なレートでクロックされる。出力セレクタ824は、出力信号832、834、836および838のうち、どれが出力のために選択されるべきであるかを決定する。

## 【0272】

DAC830のDACクロック信号826、出力セレクタ信号824、入力セレクタ822、および、サンプルホールドクロック840A～Dおよび850は、独立にするか、あるいは伝達関数モジュール710および/または712に統合することができる、制御モジュールによって制御される。40

## 【0273】

一実施形態では、サンプルホールド回路(S/H)842、844、846および848は、クロック信号840A～Dに従って、DAC830から、受信されたアナログ値をサンプルホールドする。サンプルホールド回路852、854、856および858は、サンプルホールド回路842、844、846および848からのアナログ値を、それぞれサンプルホールドする。同様に、サンプルホールド回路852、854、856および858は、受信されたアナログ値をホールドし、同時にこれらの値をベクトル変調器760、762、764および766へ、共通クロック信号850に従ってリリースする。別50

の実施形態では、サンプルホールド回路 852、854、856 および 858 は、これらの値を、同じくアンチエイリアスフィルタである任意選択の補間フィルタ 731、733、735 および 737 へリリースする。一実施形態では、共通クロック信号 850 は、S/H 852、854、856 および 858 の出力が時間的に整合されることを保証するために使用される。

#### 【0274】

ベクトル電力増幅器 800A の他の態様は、実質的には、ベクトル電力増幅器 700 に関して上述したものに対応する。

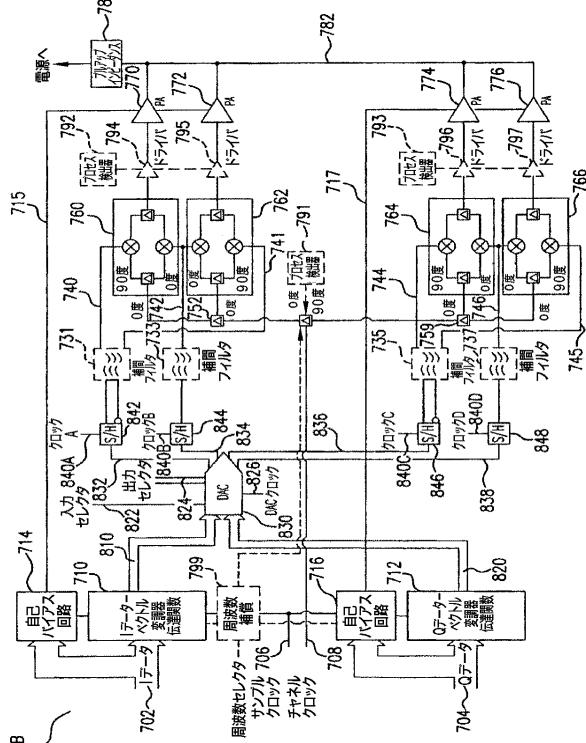

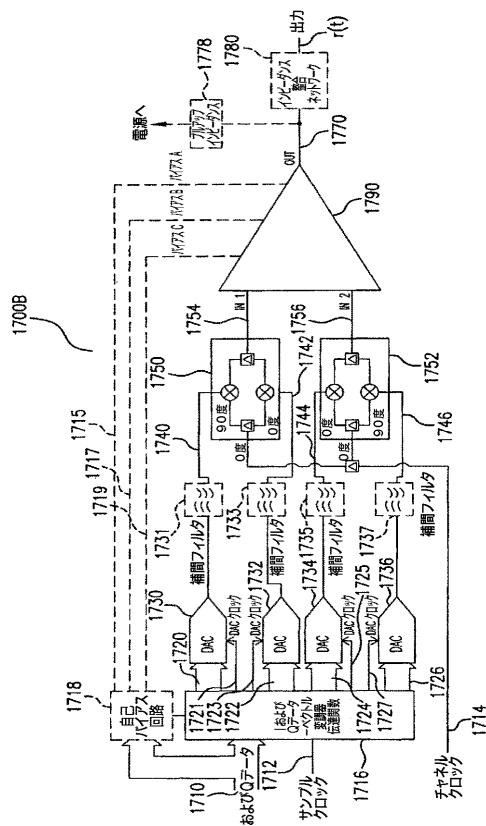

#### 【0275】

図 8B は、図 6 に示したデカルト 4 分岐 VPA 方法によるベクトル電力増幅器の別の例示的実施形態 800B を例示するブロック図である。任意選択のコンポーネントが破線で例示されるが、他の実施形態は、より多くのあるいはより少ない任意選択のコンポーネントを有してもよい。

#### 【0276】

実施形態 800B は、ベクトル電力増幅器の別の单一 DAC 実装を例示する。しかし、図 8A の実施形態とは対照的に、サンプルホールドアーキテクチャは単一のセットのサンプルホールド (S/H) 回路を含む。図 8B に示すように、S/H 842、844、846 および 848 は、信号 832、834、836 および 838 として例示した、DAC 830 からのアナログ値を受信する。S/H 回路 842、844、846 および 848 の各々は、図示のように異なるクロック 840A～D に従って、その受信された値をリリースする。信号 740、741、742、744、745 および 746 を生成するために使用されるアナログサンプルの間の時間差を、伝達関数 710 および 712 において補償することができる。図 8B の実施形態によれば、図 8A の実施形態と比較して S/H 回路の 1 レベルを除去し、それにより、増幅器のサイズおよび複雑性を低減することができる。

#### 【0277】

ベクトル電力増幅器 800B の他の態様は、実質的には、ベクトル電力増幅器 700 および 800A に関して上述したものに対応する。

#### 【0278】

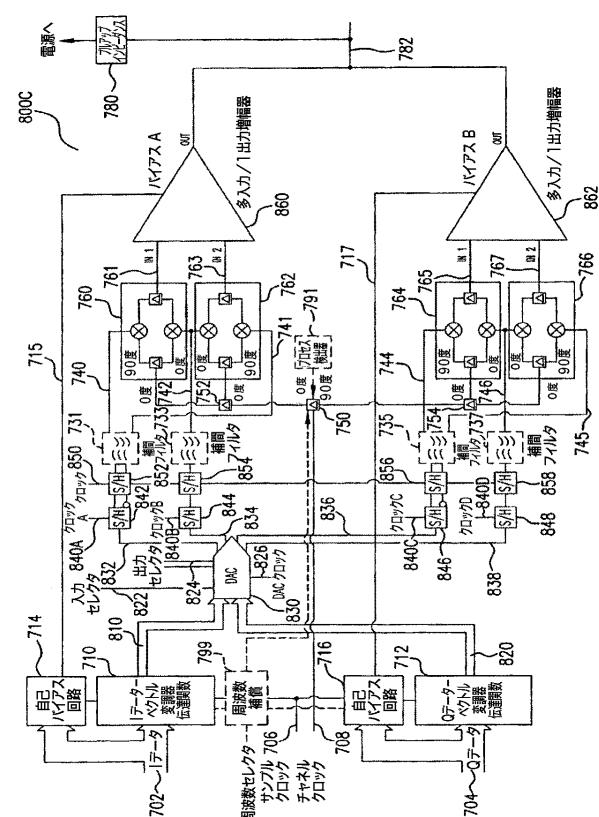

図 8C は、ベクトル電力増幅器 700 の別の例示的実施形態 800C を例示するブロック図である。任意選択のコンポーネントが破線で例示されるが、他の実施形態は、より多くのあるいはより少ない任意選択のコンポーネントを有してもよい。図 8C の実施形態は、図 8A の増幅器の多入力 1 出力 (MISO) 実装を例示する。図 8C の実施形態では、ベクトル変調器 760、762、764 および 766 から出力された、定包絡線信号 761、763、765 および 767 が、MISO PA 860 および 862 に入力される。MISO PA 860 および 862 は、2 入力 1 出力の電力増幅器である。一実施形態では、MISO PA 860 および 862 は、図 7A の実施形態に示すような素子 770、772、774、776、794～797、またはその機能的均等物を含む。別の実施形態では、MISO PA 860 および 862 は、任意選択のプレドライバおよび任意選択のプロセス検出回路など、他の素子を含んでもよい。別の実施形態では、MISO PA 860 および 862 は、図 7A の実施形態に図示されない、プレドライバなど、他の素子を含んでもよい。さらに、MISO PA 860 および 862 は、図 8C に示すような 2 入力 PA であることに限定されない。他の実施形態では、以下で図 51A～H を参照してさらに説明するように、PA 860 および 862 は、いかなる数の入力および出力を有することもできる。

#### 【0279】

ベクトル電力増幅器 800C の他の態様は、実質的には、ベクトル電力増幅器 700 および 800A に関して上述したものに対応する。

#### 【0280】

図 8D は、ベクトル電力増幅器 700 の別の例示的実施形態 800D を例示するブロック図である。任意選択のコンポーネントが破線で例示されるが、他の実施形態は、より多

10

20

30

40

50

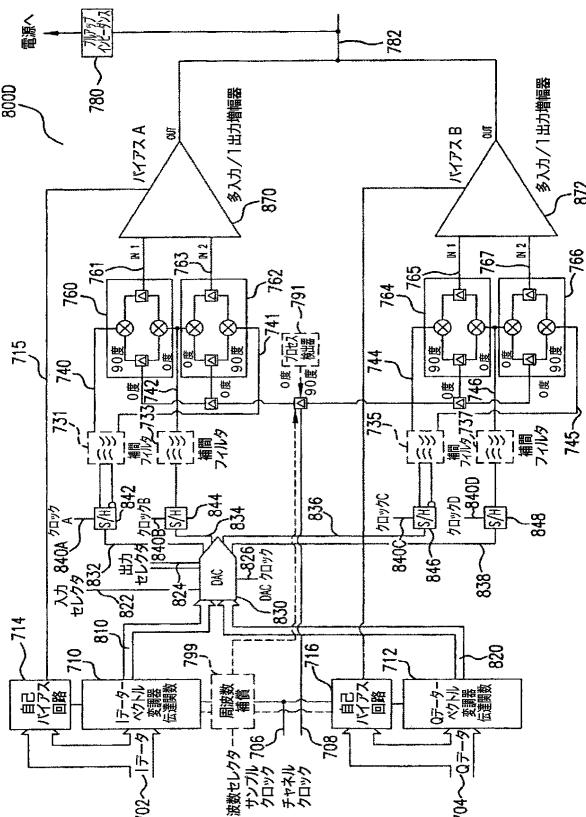

くのあるいはより少ない任意選択のコンポーネントを有してもよい。図 8 D の実施形態は、図 8 B の増幅器の多入力 1 出力 (MISO) 実装を例示する。図 8 D の実施形態では、ベクトル変調器 760、762、764 および 766 から出力された、定包絡線信号 761、763、765 および 767 が、MISO PA870 および 872 に入力される。MISO PA870 および 872 は、2 入力 1 出力の電力増幅器である。一実施形態では、MISO PA870 および 872 は、図 7 A の実施形態に示すような素子 770、772、774、776、794～797、またはその機能的均等物を含む。別の実施形態では、MISO PA870 および 872 は、任意選択のプレドライバおよび任意選択のプロセス検出回路など、他の素子を含んでもよい。別の実施形態では、MISO PA870 および 872 は、図 7 A の実施形態に図示されない、プレドライバなど、他の素子を含んでもよい。さらに、MISO PA870 および 872 は、図 8 D に示すような 2 入力 PA であることに限定されない。他の実施形態では、以下で図 51 A～H を参照してさらに説明するように、PA870 および 872 は、いかなる数の入力および出力を有することもできる。

10

## 【0281】

ベクトル電力増幅器 800D の他の態様は、実質的には、ベクトル電力増幅器 700 および 800B に関して上述したものに対応する。

## 【0282】

## 3.2) デカルトポーラデカルトポーラ 2 分岐ベクトル電力増幅器

デカルトポーラデカルトポーラ (CPCP) 2 分岐 VPA の実施形態をこれから説明するものとする (この実施形態の名称は、参照を容易にするために提供され、限定していない)。

20

## 【0283】

デカルトポーラデカルトポーラ (CPCP) 2 分岐 VPA 方法によれば、時変複素包絡線信号は、2 つのほぼ一定の包絡線成分信号に分解される。これらの成分信号は個別に増幅され、次いで加算されて、元の時変複素包絡線信号の増幅されたバージョンが構成される。加えて、時変複素包絡線信号の位相角が決定され、結果として生じる成分信号の加算が、適切な角度だけ位相シフトされる。

## 【0284】

CPCP 2 分岐 VPA 方法の一実施形態では、時変複素包絡線信号の大きさおよび位相角が、信号の同相および直交成分から計算される。大きさ情報が与えられると、2 つのほぼ一定の包絡線成分が、所望の時変包絡線信号の正規化されたバージョンから計算され、この正規化は、実装特有の位相および / または振幅の操作を含む。2 つのほぼ一定の包絡線成分は次いで、所望の時変包絡線信号の位相シフトに関係する適切な角度だけ位相シフトされる。ほぼ一定の包絡線成分は次いで、個別にほぼ等しく増幅され、加算されて、元の所望の時変包絡線信号の増幅されたバージョンが生成される。

30

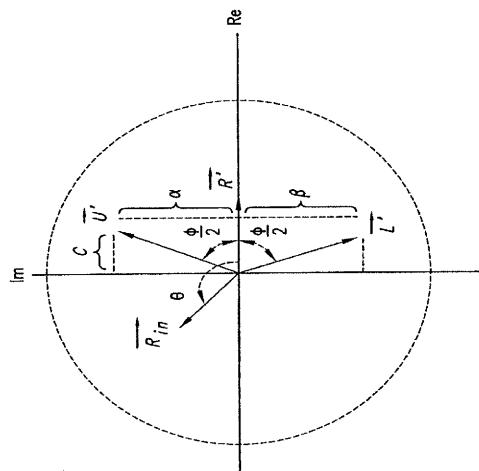

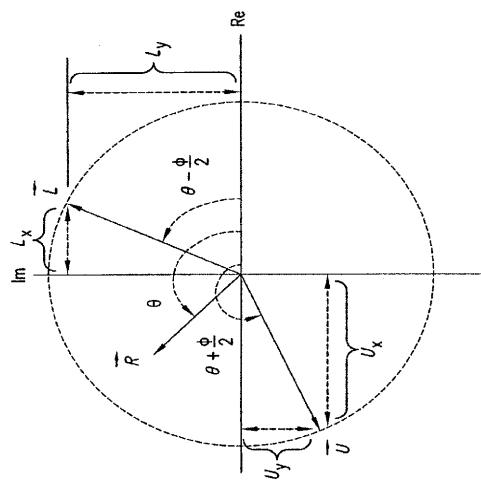

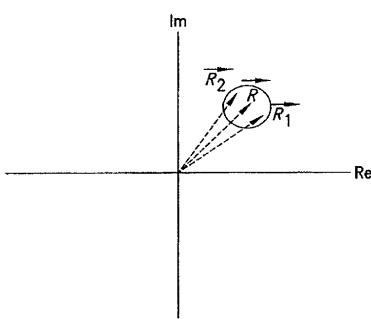

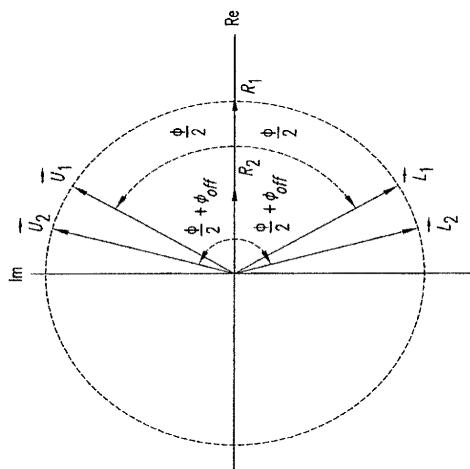

## 【0285】

図 9 A および 9 B は、フェーザ信号表現を使用した CPCP 2 分岐 VPA の実施形態を概念的に例示する。図 9 A では、フェーザ

## 【0286】

## 【数 80】

$\overline{R}_{in}$

## 【0287】

は、時変複素包絡線入力信号  $r(t)$  を表す。いずれかの時刻に

## 【0288】

10

20

30

40

【数 8 1】

$\overline{\overline{R}}_{in}$

【0 2 8 9】

は、信号  $r(t)$  の大きさおよび位相シフト角を反映する。図 9 A に示す実施例では、

【0 2 9 0】

【数 8 2】

$\overline{\overline{R}}_{in}$

10

【0 2 9 1】

は、大きさ  $R$  および位相シフト角  $\phi$  によって特徴化される。上述のように、位相シフト角は基準信号に対して測定される。

【0 2 9 2】

図 9 A を参照すると、

【0 2 9 3】

【数 8 3】

$\overline{\overline{R}}$

20

【0 2 9 4】

は、

【0 2 9 5】

【数 8 4】

$\overline{\overline{U}}$

【0 2 9 6】

および

【0 2 9 7】

【数 8 5】

$\overline{\overline{L}}$

30

【0 2 9 8】

によって生成された

【0 2 9 9】

【数 8 6】

$\overline{\overline{R}}_{in}$

【0 3 0 0】

の相対振幅成分を表す。

40

【0 3 0 1】

なお、図 9 A を参照すると、いずれかの時刻に、

【0 3 0 2】

【数 8 7】

$\overline{\overline{R}}$

【0 3 0 3】

を、上側フェーザ

【0 3 0 4】

50

【数 8 8】

【0 3 0 5】

および下側フェーザ

【0 3 0 6】

【数 8 9】

10

【0 3 0 7】

の和によって得ることができることに留意されたい。さらに、

【0 3 0 8】

【数 9 0】

および

【0 3 0 9】

【数 9 1】

20

【0 3 1 0】

を、ほぼ一定の大きさを有するように維持することができる。フェーザ

【0 3 1 1】

【数 9 2】

および

【0 3 1 2】

30

【数 9 3】

【0 3 1 3】

は、したがって、2つのほぼ一定の包絡線信号を表す。 $r'(t)$ を、よって、いずれかの時刻に、フェーザ

【0 3 1 4】

【数 9 4】

および

【0 3 1 5】

40

【数 9 5】

【0 3 1 6】

に対応する2つのほぼ一定の包絡線信号の和によって得ることができる。

【0 3 1 7】

【数96】

$\overline{R'}$

【0318】

に対するフェーザ

【0319】

【数97】

$\overline{U'}$

【0320】

および

【0321】

【数98】

$\overline{L'}$

【0322】

の位相シフトは、

【0323】

【数99】

$\overline{R'}$

【0324】

の所望の大きさ  $R$  に従って設定される。最も簡単な場合、上側および下側フェーザ

【0325】

【数100】

$\overrightarrow{U'}$

【0326】

および

【0327】

【数101】

$\overleftarrow{L'}$

【0328】

が等しい大きさを有するように選択されるとき、上側および下側フェーザ

【0329】

【数102】

$\overrightarrow{U'}$

【0330】

および

【0331】

【数103】

$\overleftarrow{L'}$

10

20

30

40

50

は、

【0 3 3 2】

【数1 0 4】

$\overrightarrow{R'}$

【0 3 3 3】

に対して、位相においてほぼ対称的にシフトされる。これは図9 A の実施例に例示される。それに限定されないが、「上側および下側」など、向きを指示あるいは示唆する用語および句は、参照を容易にするため、本明細書で使用され、機能的あるいは構造的に限定しないことに留意されたい。 10

【0 3 3 4】

図9 A に例示した場合では、

【0 3 3 5】

【数1 0 5】

$\overrightarrow{R'}$

【0 3 3 6】

に対する

【0 3 3 7】

【数1 0 6】

$\overrightarrow{U'}$

および

【0 3 3 8】

【数1 0 7】

$\overrightarrow{L'}$

【0 3 3 9】

の位相シフトは、図9 A では角度 30

【0 3 4 0】

【数1 0 8】

$\frac{\phi}{2}$

【0 3 4 1】

として例示され、以下のように

【0 3 4 2】

【数1 0 9】

$\overrightarrow{R'}$

【0 3 4 3】

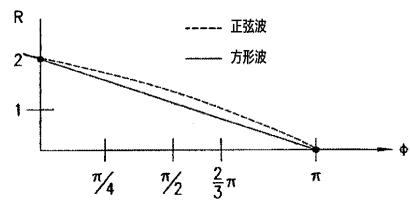

の大きさに関係することを検証することができる。 40

【0 3 4 4】

【数110】

$$\frac{\phi}{2} = \cot^{-1} \left( \frac{R}{2\sqrt{1 - \frac{R^2}{4}}} \right) \quad (7)$$

【0345】

ただし、Rは、フェーザ

10

【0346】

【数111】

$\overline{R}$

【0347】

の正規化された大きさを表す。

【0348】

方程式(7)を、さらに以下に約分することができる。

【0349】

【数112】

20

$$\frac{\phi}{2} = \cos^{-1} \left( \frac{R}{2} \right) \quad (7.10)$$

【0350】

ただし、Rは、フェーザ

【0351】

【数113】

$\overline{R}$

【0352】

の正規化された大きさを表す。

30

【0353】

別法として、いかなるほぼ等価な数学的方程式、または、ルックアップテーブルなど、他のほぼ等価な数学的技術も使用することができる。

【0354】

上記の考察から、フェーザ表現では、可変の大きさおよび位相のいかなるフェーザ

【0355】

【数114】

$\overline{R}$

【0356】

も、2つの一定の大きさのフェーザ成分の和によって構成することができるということになる。

40

【0357】

【数115】

$$\vec{R} = \vec{U} + \vec{L} \quad (8)$$

$$|\vec{U}| = |\vec{L}| = A = \text{定数}$$

【0358】

対応して、時間領域では、時変包絡線正弦波信号  $r'(t) = R(t) \times \cos(\omega t)$  は、以下のように、2つの定包絡線信号の和によって構成される。

【0359】

【数116】

$$r'(t) = U'(t) + L'(t);$$

$$U'(t) = A \times \cos(\omega t + \frac{\phi}{2}); \quad (9)$$

$$L'(t) = A \times \cos(\omega t - \frac{\phi}{2});$$

【0360】

ただし、Aは定数であり、

【0361】

【数117】

$$\frac{\phi}{2}$$

【0362】

は方程式(7)に示す通りである。

【0363】

図9Aから、さらに、方程式(9)を以下のように書き換えることができる事を検証することができる。

$$\begin{aligned} r'(t) &= U'(t) + L'(t), \\ U'(t) &= C \cos(\omega t) + \sin(\omega t), \quad (10) \\ L'(t) &= C \cos(\omega t) - \sin(\omega t), \end{aligned}$$

ただし、Cは、フェーザ

【0364】

【数118】

$$\vec{U}$$

および

【0365】

【数119】

$$\vec{L}$$

【0366】

の実部成分を示し、

【0367】

10

20

30

40

【数120】

$$\underline{A} \times \cos\left(\frac{\phi}{2}\right)$$

【0368】

に等しい。Cは、

【0369】

【数121】

$$\overrightarrow{U'}$$

【0370】

および

【0371】

【数122】

$$\overrightarrow{L'}$$

【0372】

の共通成分であることに留意されたい。およびは、フェーザ

【0373】

【数123】

$$\overrightarrow{U'}$$

【0374】

および

【0375】

【数124】

$$\overrightarrow{L'}$$

【0376】

の虚部成分をそれぞれ示す。

【0377】

【数125】

$$\alpha = \beta = A \times \sin\left(\frac{\phi}{2}\right)$$

【0378】

である。したがって、方程式(12)から、

【0379】

【数126】

$$r'(t) = 2C \times \cos(\omega t) = 2A \times \cos\left(\frac{\phi}{2}\right) \times \cos(\omega t)$$

【0380】

である。当業者には本明細書の教示に基づいて理解されるように、量A、BおよびCの上記表現の他の等価および/または簡約表現もまた使用してもよく、これには、例えば、ルックアップテーブルが含まれる。

10

20

30

40

50

【 0 3 8 1 】

【 数 1 2 7 】

$\overrightarrow{R_{in}}$

【 0 3 8 2 】

は、

【 0 3 8 3 】

【 数 1 2 8 】

$\overrightarrow{R'}$

10

【 0 3 8 4 】

に対して 一度だけシフトされることに留意されたい。したがって、方程式(8)を使用して、以下を推論することができる。

【 0 3 8 5 】

【 数 1 2 9 】

$$\overrightarrow{R_{in}} = \overrightarrow{R} e^{j\theta} = (\overrightarrow{U} + \overrightarrow{L}) e^{j\theta} = \overrightarrow{U} e^{j\theta} + \overrightarrow{L} e^{j\theta} \quad (11)$$

20

【 0 3 8 6 】

方程式(11)は、

【 0 3 8 7 】

【 数 1 3 0 】

$\overrightarrow{R_{in}}$

【 0 3 8 8 】

の表現を、一度だけシフトされた上記のフェーザ

【 0 3 8 9 】

【 数 1 3 1 】

$\overrightarrow{U'}$

および

【 0 3 9 0 】

【 数 1 3 2 】

$\overrightarrow{L'}$

【 0 3 9 1 】

を加算することによって、得ることができることを示唆する。さらに、

【 0 3 9 2 】

【 数 1 3 3 】

$\overrightarrow{R_{in}}$

40

【 0 3 9 3 】

の増幅された出力バージョン

【 0 3 9 4 】

【数 1 3 4】

$\overline{R}_{out}$

【0 3 9 5】

を、フェーザ

【0 3 9 6】

【数 1 3 5】

$\overline{U}$

および

【0 3 9 7】

【数 1 3 6】

$\overline{L}$

【0 3 9 8】

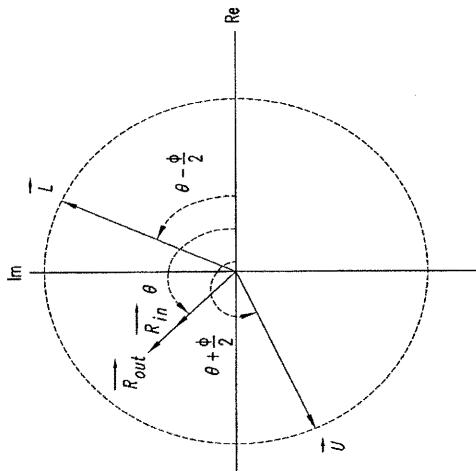

の度シフトされたバージョンの各々を別々にほぼ等しく増幅すること、および、それらを加算することによって、得ることができる。図9Bは、この概念を例示する。図9Bでは、フェーザ

10

【0 3 9 9】

【数 1 3 7】

$\overline{U}$

および

【0 4 0 0】

【数 1 3 8】

$\overline{L}$

【0 4 0 1】

は、フェーザ

【0 4 0 2】

【数 1 3 9】

$\overline{U}$

および

【0 4 0 3】

【数 1 4 0】

$\overline{L}$

【0 4 0 4】

の、度シフトされ、増幅されたバージョンを表す。

30

【0 4 0 5】

【数 1 4 1】

$\overline{U}$

【0 4 0 6】

および

【0 4 0 7】

40

【数142】

$\overline{L}$

【0408】

は一定の大きさのフェーザであるため、

【0409】

【数143】

$\overline{U}$

【0410】

および

【0411】

【数144】

$\overline{L}$

【0412】

もまた一定の大きさのフェーザであることに留意されたい。フェーザ

【0413】

【数145】

$\overline{U}$

【0414】

および

【0415】

【数146】

$\overline{L}$

【0416】

の和は、図9Bに示すように、フェーザ

【0417】

【数147】

$\overline{R}_{out}$

【0418】

となり、これは、入力信号

【0419】

【数148】

$\overline{R}_{in}$

【0420】

の電力増幅されたバージョンである。

【0421】

等価的に、時間領域では、以下であることが分かる。

$$r_{out}(t) = U(t) + L(t),$$

$$U(t) = K [ C \cos(\omega t + \phi) + S \sin(\omega t + \phi) ], \quad (12)$$

$$L(t) = K [ C \cos(\omega t + \phi) - S \sin(\omega t + \phi) ].$$

ただし、 $r_{out}(t)$ は、フェーザ

【0422】

10

20

30

40

50

【数149】

$\overline{R}_{out}$

【0423】

によって表現された時間領域信号に対応し、U(t)およびL(t)は、フェーザ

【0424】

【数150】

$\overline{U}$

【0425】

10

および

【0426】

【数151】

$\overline{L}$

【0427】

によって表現された時間領域信号に対応し、Kは電力増幅係数である。

【0428】

20

方程式(9)および(10)における時間領域表現は正弦波形の場合について提供されたが、等価表現を非正弦波形について、適切な基底関数を用いて展開することができるることは、当業者には理解されよう。

【0429】

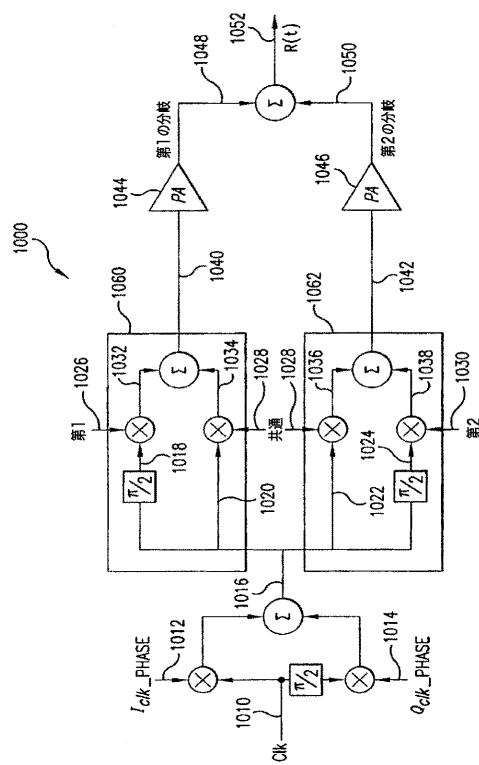

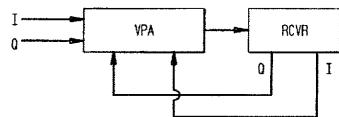

図10は、CP CP 2分岐VPAの実施形態の例示的実施形態1000を概念的に例示するブロック図である。所望の電力レベルおよび周波数特性の出力信号r(t)は、CP CP 2分岐VPAの実施形態によれば、同相および直交成分から生成される。

【0430】

図10の実施例では、クロック信号1010は、出力信号r(t)を生成するための基準信号を表す。クロック信号1010は、所望の出力信号r(t)と同じ周波数のものである。

30

【0431】

図10を参照すると、Ick\_phase信号1012およびQck\_phase信号1014は、C1k信号1010の同相および直交成分によって乗算され、ベースバンドIおよびQ信号から計算される、振幅アナログ値を表す。

【0432】

なお、図10を参照すると、クロック信号1010はIck\_phase信号1012で乗算される。並行して、クロック信号1010の90度シフトされたバージョンは、Qck\_phase信号1014で乗算される。この2つの乗算された信号が結合されて、Rck信号1016が生成される。Rck信号1016は、クロック信号1010と同じ周波数のものである。さらに、Rck信号1016は、Q(t)およびI(t)の比による位相シフト角によって特性化される。Rck信号1016の大きさは、 $R^2 c1k = I^2 c1k\_phase + Q^2 c1k\_phase$ のようになる。したがって、Rck信号1016は、所望の出力信号r(t)の位相特性を有するほぼ一定の包絡線信号を表す。

40

【0433】

なお、図10を参照すると、Rck信号1016は並行して、2つのベクトル変調器1060および1062に入力される。ベクトル変調器1060および1062は、(12)に記載したように、所望の出力信号のr(t)の、U(t)およびL(t)ほぼ一定の包絡線成分をそれぞれ生成する。ベクトル変調器1060では、共通信号1028で乗算された同相Rck信号1020は、第1の信号1026で乗算されたRck信号の

50

90度シフトされたバージョン1018と結合される。並行して、ベクトル変調器1062では、共通信号1028で乗算された同相Rc1k信号1022は、第2の信号1030で乗算されたRc1k信号の90度シフトされたバージョン1024と結合される。共通信号1028、第1の信号1026および第2の信号1030は、方程式(12)に記載された実部C、ならびに虚部 および にそれぞれ対応する。

#### 【0434】

各ベクトル変調器1060および1062の出力信号1040および1042は、入力信号r(t)のU(t)およびL(t)定包絡線成分にそれぞれ対応する。

#### 【0435】

上述のように、信号1040および1042は、ほぼ等しくかつ一定の大きさの包絡線を有することによって特性化される。したがって、信号1040および1042が対応する電力増幅器(PA)1044および1046に入力されるとき、対応する増幅された信号1048および1050は、ほぼ一定の包絡線信号である。

#### 【0436】

電力増幅器1044および1046は、ほぼ等しい電力増幅を信号1040および1042にそれぞれ適用する。一実施形態では、PA1044および1046の電力増幅レベルは、出力信号r(t)の所望の電力レベルに従って設定される。さらに、増幅された信号1048および1050は、互いに対しても同相である。したがって、共に加算されるとき、図10に示すように、結果として生じる信号1052は、所望の出力信号r(t)に対応する。

#### 【0437】

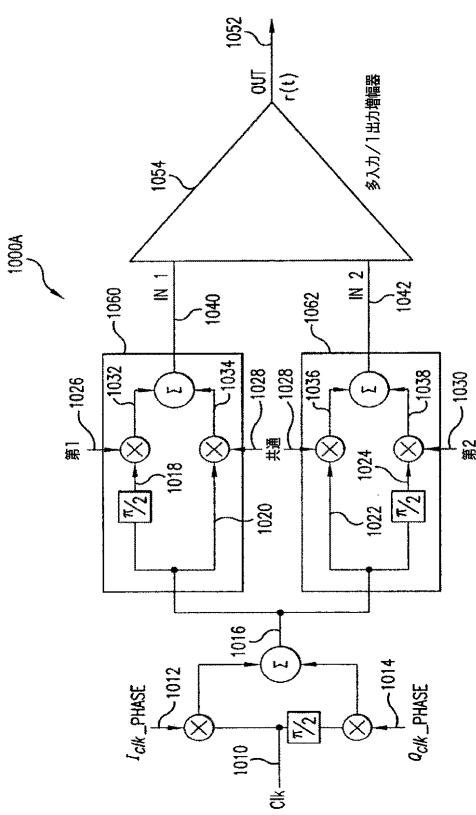

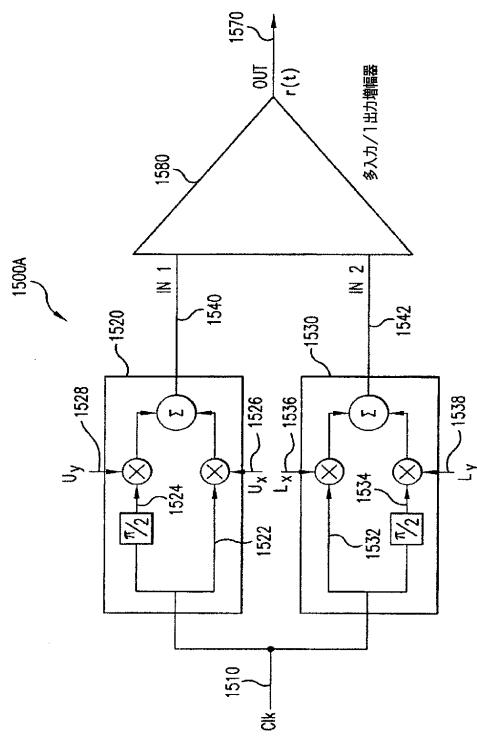

図10Aは、CPCP2分岐VPAの実施形態の別の例示的実施形態1000Aである。実施形態1000Aは、図10の実施形態1000の多入力1出力(MISO)実装を表す。

#### 【0438】

実施形態1000Aでは、ベクトル変調器1060および1062から出力された、定包絡線信号1040および1042は、MISO PA1054に入力される。MISO PA1054は、2入力1出力の電力増幅器である。一実施形態では、MISO PA1054は、例えば、プレドライバ、ドライバ、電力増幅器およびプロセス検出器(図10Aに図示せず)など、様々な素子を含んでよい。さらに、MISO PA1054は、図10Aに示すように、2入力PAであることに限定されない。他の実施形態では、以下で図51A～Hを参照してさらに説明するように、PA1054は、いかなる数の入力を有することもできる。

#### 【0439】

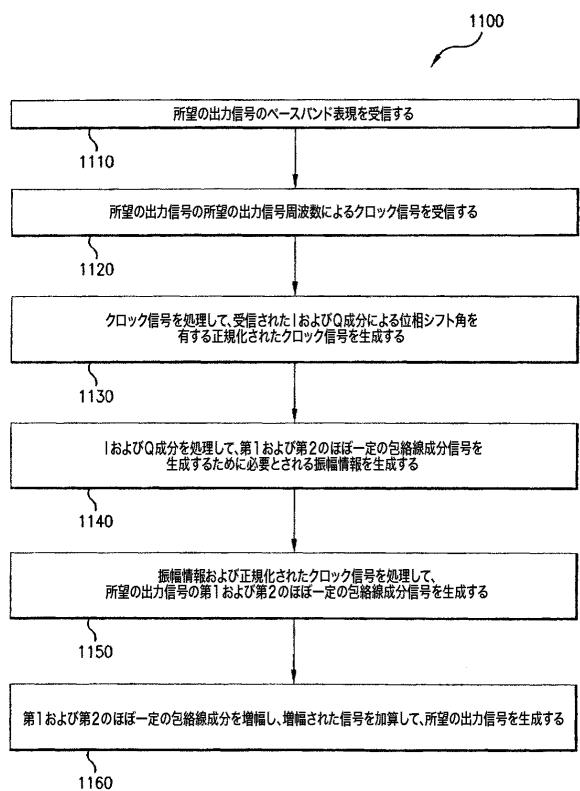

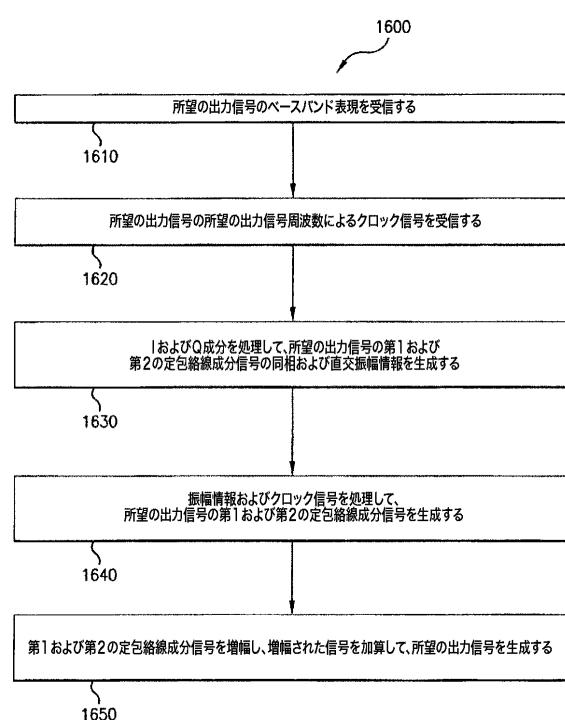

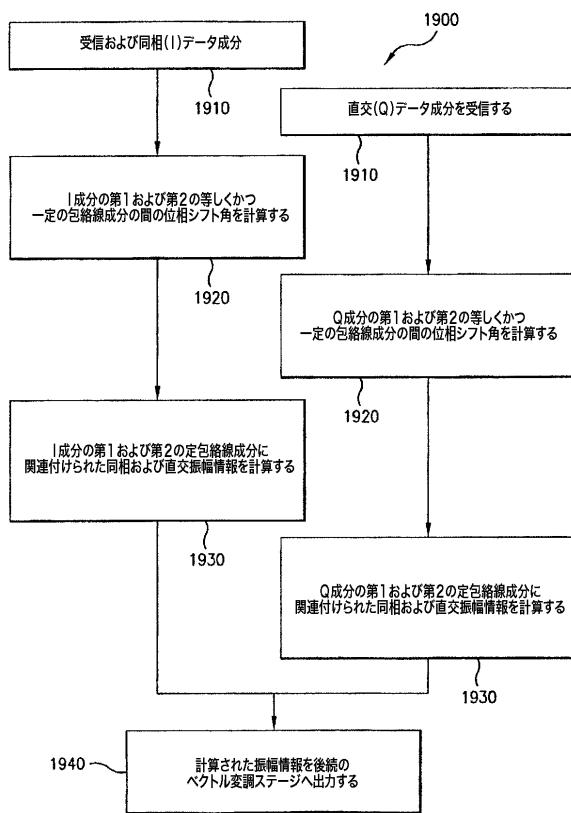

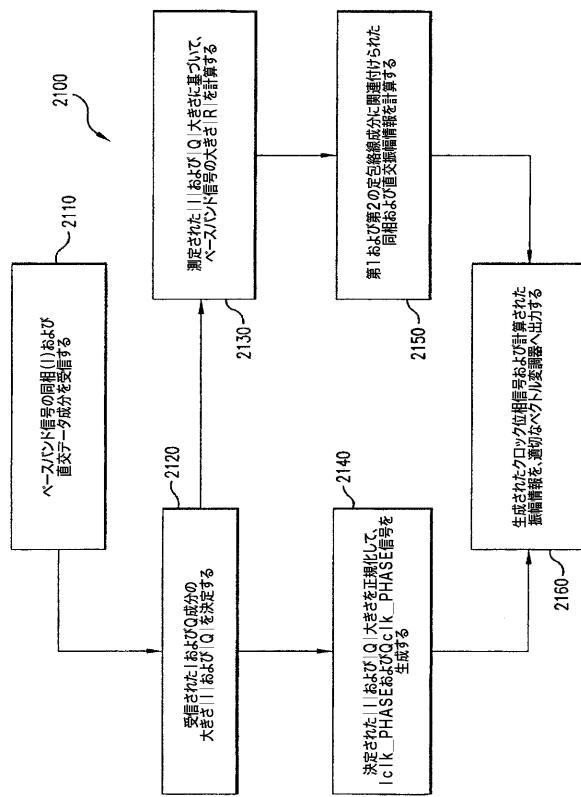

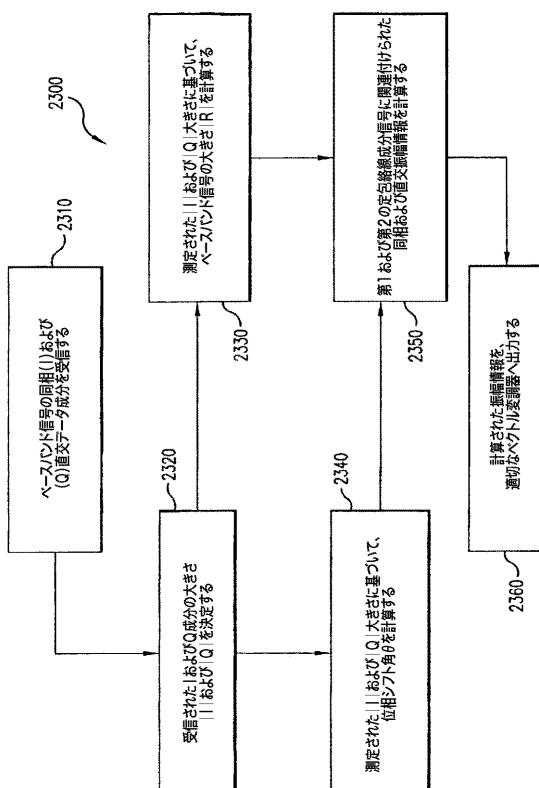

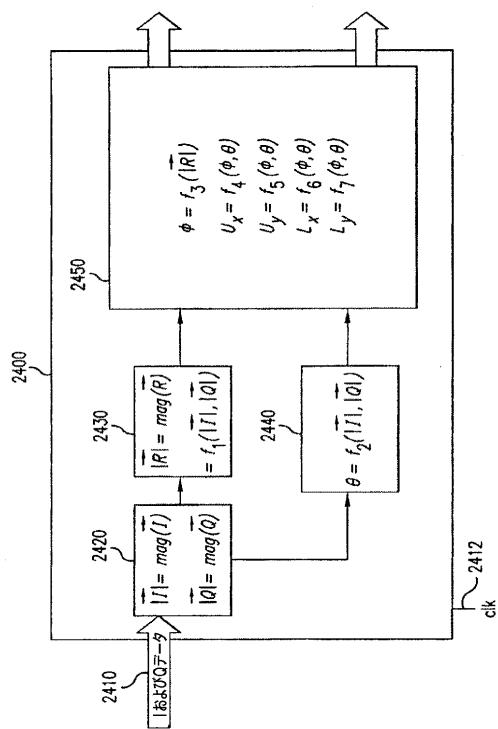

CPCP2分岐VPAの実施形態の動作を、図11のプロセス流れ図1100に示す。

#### 【0440】

このプロセスは、所望の出力信号のベースバンド表現を受信することを含む、ステップ1110で開始する。一実施形態では、これは、所望の出力信号の同相(I)および直交(Q)成分を受信することを含む。別の実施形態では、これは、所望の出力信号の大きさおよび位相を受信することを含む。

#### 【0441】

ステップ1120は、所望の出力信号の所望の出力信号周波数に従って設定されたクロック信号を受信することを含む。図10の実施例では、ステップ1120は、クロック信号1010を受信することによって達成される。

#### 【0442】

ステップ1130は、クロック信号を処理して、受信されたIおよびQ成分による位相シフト角を有する正規化されたクロック信号を生成することを含む。一実施形態では、正規化されたクロック信号は、IおよびQ成分の比による位相シフト角を有する定包絡線信号である。正規化されたクロックの位相シフト角は、元のクロック信号と相対的である。図10の実施例では、ステップ1130は、クロック信号1010の同相および直交成分

10

20

30

40

50

を  $I_{clk\_phase1012}$  および  $Q_{clk\_phase1014}$  信号で乗算し、次いで、乗算された信号を加算して、 $R_{clk}$  信号 1016 を生成することによって達成される。

#### 【0443】

ステップ 1140 は、I および Q 成分を処理して、第 1 および第 2 のほぼ一定の包絡線成分信号を生成するために必要とされる振幅情報を生成することを含む。

#### 【0444】

ステップ 1150 は、ステップ 1140 の振幅情報を正規化されたクロック信号  $R_{clk}$  を処理して、所望の出力信号の第 1 および第 2 の定包絡線成分を生成することを含む。一実施形態では、ステップ 1150 は、所望の出力信号の第 1 および第 2 の定包絡線成分を、正規化されたクロック信号の位相シフト角だけ位相シフトすることを含む。図 10 の実施例では、ステップ 1150 は、ベクトル変調器 1060 および 1062 が  $R_{clk}$  信号 1016 を第 1 の信号 1026、第 2 の信号 1030 および共通信号 1028 で変調して、信号 1040 および 1042 を生成することによって達成される。

10

#### 【0445】

ステップ 1160 は、第 1 および第 2 の定包絡線成分を個別に増幅し、増幅された信号を加算して、所望の出力信号を生成することを含む。一実施形態では、第 1 および第 2 の定包絡線成分の増幅はほぼ等しく、所望の出力信号の所望の電力レベルによるものである。図 10 の実施例では、ステップ 1160 は、PA1044 および 1046 が信号 1040 および 1042 を増幅して、増幅された信号 1048 および 1050 を生成することによって達成される。

20

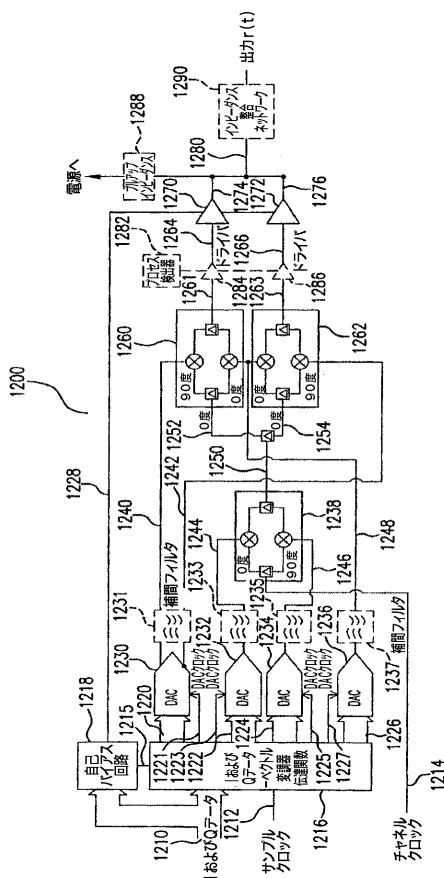

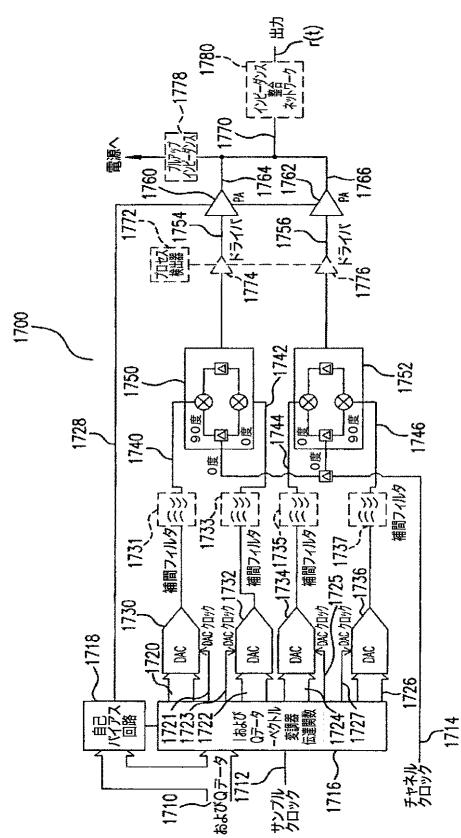

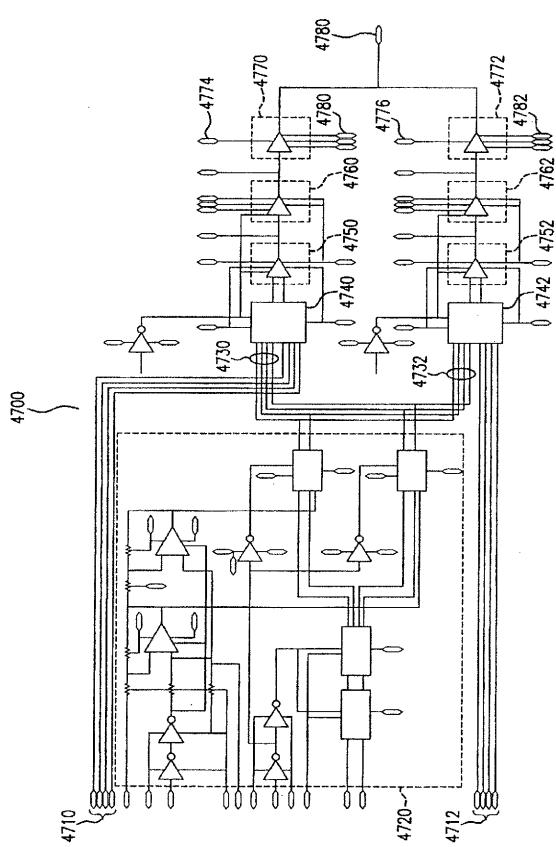

#### 【0446】

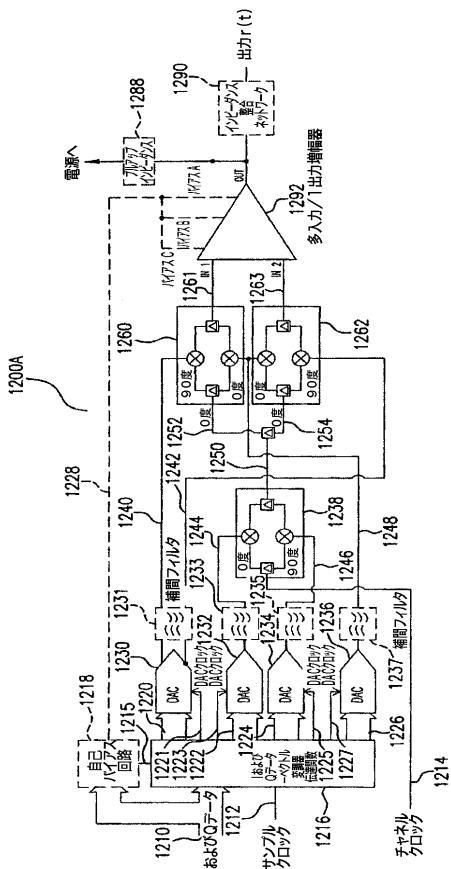

図 12 は、プロセス流れ図 1100 を実装するベクトル電力増幅器 1200 の例示的実施形態を例示するブロック図である。任意選択のコンポーネントが破線で例示されるが、他の実施形態では、より多くのあるいはより少ないコンポーネントが任意選択であってもよい。

20

#### 【0447】

図 12 を参照すると、同相 (I) および直交 (Q) 情報信号 1210 は、I および Q データ伝達関数モジュール 1216 によって受信される。一実施形態では、I および Q データ伝達関数 1216 は、信号 1210 をサンプルクロック 1212 に従ってサンプルする。I および Q 情報信号 1210 は、所望の出力信号  $r(t)$  のベースバンド I および Q 情報を含む。

30

#### 【0448】

一実施形態では、I および Q データ伝達関数モジュール 1216 は、情報信号 1210 を処理して、情報信号 1220、1222、1224 および 1226 を生成する。I および Q データ伝達関数モジュール 1216 の動作を、さらに以下でセクション 3.4 において説明する。

#### 【0449】

図 12 を参照すると、情報信号 1220 は、所望の出力信号  $r(t)$  のベースバンドバージョンの第 1 および第 2 の定包絡線成分の直交振幅情報を含む。図 9A を参照すると、例えば、情報信号 1220 は、および直交成分を含む。再度、図 12 を参照すると、情報信号 1226 は、信号  $r(t)$  のベースバンドバージョンの第 1 および第 2 の定包絡線成分の同相振幅情報を含む。図 9A を参照すると、例えば、情報信号 1226 は、共通 C 同相成分を含む。

40

#### 【0450】

なお、図 12 を参照すると、情報信号 1222 および 1224 は、正規化された同相  $I_{clk\_phase}$  および直交  $Q_{clk\_phase}$  信号をそれぞれ含む。 $I_{clk\_phase}$  および  $Q_{clk\_phase}$  は、信号 1210 に含まれた I および Q 情報信号の正規化されたバージョンである。一実施形態では、 $I_{clk\_phase}$  および  $Q_{clk\_phase}$  は、 $(I^2_{clk\_phase} + Q^2_{clk\_phase} = \text{定数})$  であるよう

50

に正規化される。信号 1250 の位相は、所望の出力信号の位相に対応し、I c l k \_ p h a s e および Q c l k \_ p h a s e から作成されることに留意されたい。図 9 B を参照すると、I c l k \_ p h a s e および Q c l k \_ p h a s e は、以下のように I および Q に関係する。

【0451】

【数152】

$$\theta = \tan^{-1}\left(\frac{Q}{I}\right) = \tan^{-1}\left(\frac{Q_{clk\_phase}}{I_{clk\_phase}}\right) \quad (12.1)$$

10

【0452】

ただし、 は、所望の出力信号の位相を表し、図 9 B において b フェーザ

【0453】

【数153】

$\overline{R_{out}}$

【0454】

を表した。ベースバンド I および Q 情報の符号情報は、4 つの象限すべてについての を計算するために考慮されなければならない。

20

【0455】

図 12 の例示的実施形態では、情報信号 1220、1222、1224 および 1226 はデジタル信号である。したがって、信号 1220、1222、1224 および 1226 の各々は、対応するデジタル - アナログ変換器 (D A C) 1230、1232、1234 および 1236 に供給される。D A C 1230、1232、1234 および 1236 の分解能およびサンプルレートは、特定の信号方式に従って選択される。D A C 1230、1232、1234 および 1236 は、D A C クロック信号 1221、1223、1225 および 1227 によって、それぞれ制御される。D A C クロック信号 1221、1223、1225 および 1227 は、同じクロック信号から導出されてもよいし、独立であってよい。

30

【0456】

他の実施形態では、情報信号 1220、1222、1224 および 1226 はアナログ形式で生成され、D A C は必要とされない。

【0457】

図 12 を参照すると、D A C 1230、1232、1234 および 1236 は、デジタル情報信号 1220、1222、1224 および 1226 を対応するアナログ信号に変換し、これらのアナログ信号を任意選択の補間フィルタ 1231、1233、1235 および 1237 にそれぞれ入力する。アンチエイリアスフィルタとしての機能も果たす補間フィルタ 1231、1233、1235 および 1237 は、D A C 出力信号を整形して、所望の出力波形を生成する。補間フィルタ 1231、1233、1235 および 1237 は、信号 1240、1244、1246 および 1248 をそれぞれ生成する。信号 1242 は、信号 1240 の逆を表す。

40

【0458】

なお、図 12 を参照すると、I c l k \_ p h a s e および Q c l k \_ p h a s e 情報を含む、信号 1244 および 1246 は、ベクトル変調器 1238 に入力される。ベクトル変調器 1238 は、信号 1244 をチャネルクロック信号 1214 で乗算する。チャネルクロック信号 1214 は、所望の出力信号周波数に従って選択される。並行して、ベクトル変調器 1238 は、信号 1246 を、チャネルクロック信号 1214 の 90 度シフトされたバージョンで乗算する。すなわち、ベクトル変調器 1238 は、I c l k \_ p h a s e の振幅を有する同相成分、および、Q c l k \_ p h a s e の振幅を有する直交成分を生

50

成する。

【0459】

ベクトル変調器1238は、2つの変調された信号を結合して、Rc1k信号1250を生成する。Rc1k信号1250は、所望の出力周波数、および、信号1210に含まれたIおよびQデータによる位相シフト角を有する、ほぼ一定の包絡線信号である。

【0460】

なお、図12を参照すると、信号1240、1242および1248は、信号 $r(t)$ の複素包絡線のU、Lおよび共通C振幅成分をそれぞれ含む。信号1240、1242および1248は、Rc1k信号1250と共に、ベクトル変調器1260および1262に入力される。

10

【0461】

ベクトル変調器1260は、Rc1k信号1250の90度シフトされたバージョンで乗算された信号1240、および、Rc1k信号1250の0度シフトされたバージョンで乗算された信号1248を結合して、出力信号1264を生成する。並行して、ベクトル変調器1262は、Rc1k信号1250の90度シフトされたバージョンで乗算された信号1242、および、Rc1k信号1250の0度シフトされたバージョンで変調された信号1248を結合して、出力信号1266を生成する。

【0462】

出力信号1264および1266は、ほぼ一定の包絡線信号を表す。さらに、Rc1k信号1250に対する出力信号1264および1266の位相シフトは、/Cおよび/Cの比にそれぞれ関連付けられた角度関係によって決定される。一実施形態では、 $= -$ であり、したがって、出力信号1264および1266は、Rc1k信号1250に対して対称的に位相整合される。図9Bを参照すると、例えば、出力信号1264および1266は、一定の大きさのフェーザ

20

【0463】

【数154】

$\overline{U}$

【0464】

および

30

【0465】

【数155】

$\overline{L}$

【0466】

にそれぞれ対応する。

【0467】

出力信号1264および1266の和は、ベースバンド信号 $r(t)$ のIおよびQ特性を有する、チャネルクロック変調された信号の結果となる。ベクトル電力増幅器1200の出力で所望の電力レベルを達成するために、しかし、信号1264および1266が増幅されて、増幅された出力信号が生成される。図12の実施形態では、信号1264および1266はそれぞれ電力増幅器(PA)1270および1272に入力され、増幅される。一実施形態では、PA1270および1272はスイッチング電力増幅器を含む。自己バイアス回路1218は、以下でセクション3.5.2においてさらに説明するよう PA1270および1272のバイアスを制御する。図12の実施形態では、例えば、自己バイアス回路1218は、バイアス電圧1228をPA1270および1272へ提供する。

40

【0468】

一実施形態では、PA1270および1272は、ほぼ等しい電力増幅を各定包絡線信号1264～1266に適用する。一実施形態では、この電力増幅は、所望の出力電力レ

50

ベルに従って設定される。ベクトル電力増幅器 1200 の他の実施形態では、PA ドライバおよび / またはプレドライバが追加で採用されて、追加の電力増幅能力が増幅器に提供される。図 12 の実施形態では、例えば、PA ドライバ 1284 および 1286 がそれぞれ、ベクトル変調器 1260 および 1262 と後続の PA 1270 および 1272 の間に、任意選択で追加される。

#### 【0469】

PA 1270 および 1272 の各出力信号 1274 および 1276 は、ほぼ一定の包絡線信号である。さらに、出力信号 1274 および 1276 が加算されるとき、結果として生じる信号は最小の非線形歪みを有する。図 12 の実施形態では、出力信号 1274 および 1276 が共に結合されて、ベクトル電力増幅器 1200 の出力信号 1280 が生成される。一実施形態では、PA 1270 および 1272 の出力の結合において絶縁が使用されない。したがって、結合によって最小の電力損失を受ける。一実施形態では、ワイヤを使用して、PA 1270 および 1272 の出力が共に直結される。このような直結は、PA 1270 および 1272 の出力の間に抵抗性、誘導性または容量性の最小の絶縁があるか、あるいはないことを意味する。すなわち、PA 1270 および 1272 の出力は、介在するコンポーネントなしに共に結合される。別法として、一実施形態では、PA 1270 および 1272 の出力は、低または最小インピーダンス接続の結果となるインダクタンスおよび / またはキャパシタンス、および / または、最小の絶縁および最小の電力損失の結果となる接続を通じて、間接的に共に結合される。別法として、PA 1270 および 1272 の出力は、ウィルキンソン、ハイブリッド結合器、変圧器、または既知のアクティブ結合器など、周知の結合技術を使用して結合される。一実施形態では、PA 1270 および 1272 は、統合された増幅および電力結合を单一の動作において提供する。一実施形態では、本明細書に記載した電力増幅器および / またはドライバの 1 つまたは複数は、多入力 1 出力の電力増幅技術を使用して実装され、その実施例を図 12A、12B および 51A～H に図示する。

#### 【0470】

出力信号 1280 は、ベースバンド信号  $r(t)$  の I および Q 特性、ならびに、所望の出力電力レベルおよび周波数を有する信号を表す。ベクトル電力増幅器 1200 の実施形態では、プルアップインピーダンス 1288 が、ベクトル電力増幅器 1200 の出力と電源の間に結合される。他の実施形態では、インピーダンス整合ネットワーク 1290 が、ベクトル電力増幅器 1200 の出力で結合される。本発明の電力増幅方法およびシステムによる出力ステージの実施形態を、さらに以下でセクション 3.5 において説明する。

#### 【0471】

ベクトル電力増幅器 1200 の他の実施形態では、プロセス検出器が採用されて、増幅器の回路におけるいかなるプロセス変動もが補償される。図 12 の例示的実施形態では、例えば、プロセス検出器 1282 が任意選択で追加されて、PA ドライバ 1284 および 1286 における変動が監視される。

#### 【0472】

図 12A は、プロセス流れ図 1100 を実装するベクトル電力増幅器 1200A の別の例示的実施形態を例示するブロック図である。任意選択のコンポーネントが破線で例示されるが、他の実施形態では、より多くのあるいはより少ないコンポーネントが任意選択であってもよい。

#### 【0473】

実施形態 1200A は、実施形態 1200 の多入力 1 出力 (MISO) 実装を例示する。実施形態 1200A では、ベクトル変調器 1260 および 1262 から出力された、定包絡線信号 1261 および 1263 が、MISO PA 1292 に入力される。MISO

PA 1292 は、2 入力 1 出力の電力増幅器である。一実施形態では、MISO PA 1292 は、図 12 の実施形態に示すような素子 1270、1272、1282、1284 および 1286 を含む。別の実施形態では、MISO PA 1292 は、図 12 の実施形態に図示されない、プレドライバなど、他の素子を含んでもよい。さらに、MISO

10

20

30

40

50

PA1292は、図12Aに示すような2入力PAであることに限定されない。他の実施形態では、以下で図51A～Hを参照してさらに説明するように、PA1292は、いかなる数の入力および出力を有することもできる。

【0474】

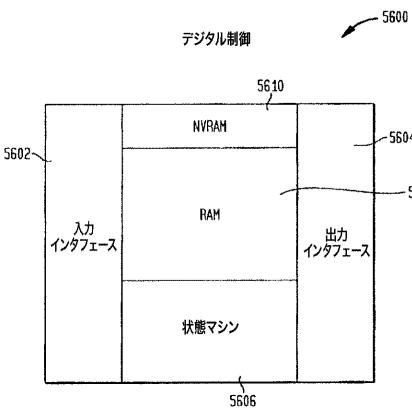

なお、図12Aを参照すると、実施形態1200Aは、自己バイアス信号をMISO PA1292へ送達するための一実装を例示する。図12Aの実施形態では、自己バイアス回路1218によって生成された自己バイアス信号1228は、MISO PA1292の異なるステージをバイアスするために、そこから送達された1つまたは複数の信号を有する。図12Aの実施例に示すように、3つのバイアス制御信号、バイアスA、バイアスBおよびバイアスCが自己バイアス信号1228から導出され、次いで、MISO PA1292の異なるステージに入力される。例えば、バイアスCは、MISO PA1292のプレドライバステージへのバイアス信号であってもよい。同様に、バイアスBおよびバイアスAは、MISO PA1292のドライバおよびPAステージへのバイアス信号であってもよい。

【0475】

図12Bの実施形態1200Bに示す別の実装では、自己バイアス回路1218は、バイアスA、バイアスBおよびバイアスCにそれぞれ対応する、別々の自己バイアス信号1295、1296および1297を生成する。信号1295、1296および1297は、自己バイアス回路1218内で別々に生成されてもそうでなくてもよいが、図示のように別々に出力される。さらに、信号1295、1296および1297は、MISO PA1292の異なるステージのバイアシングによって決定されるように関係付けられてもそうでなくてもよい。

【0476】

ベクトル電力増幅器1200Aおよび1200Bの他の態様は、実質的には、ベクトル電力増幅器1200に関して上述したものに対応する。

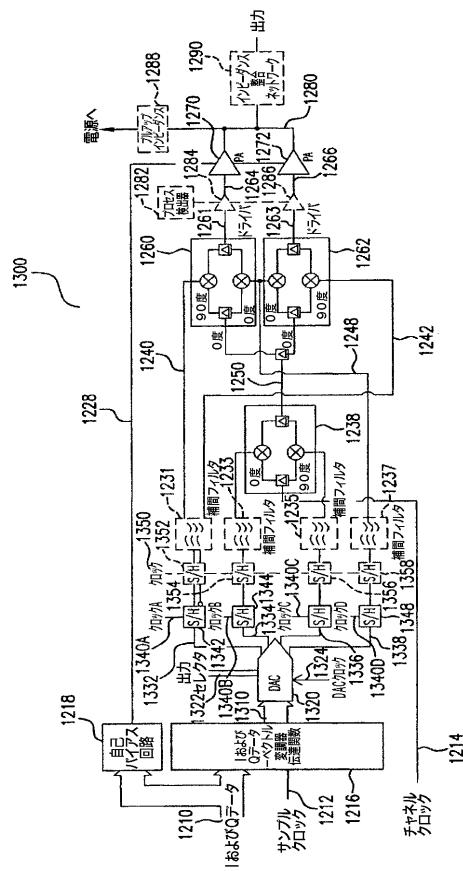

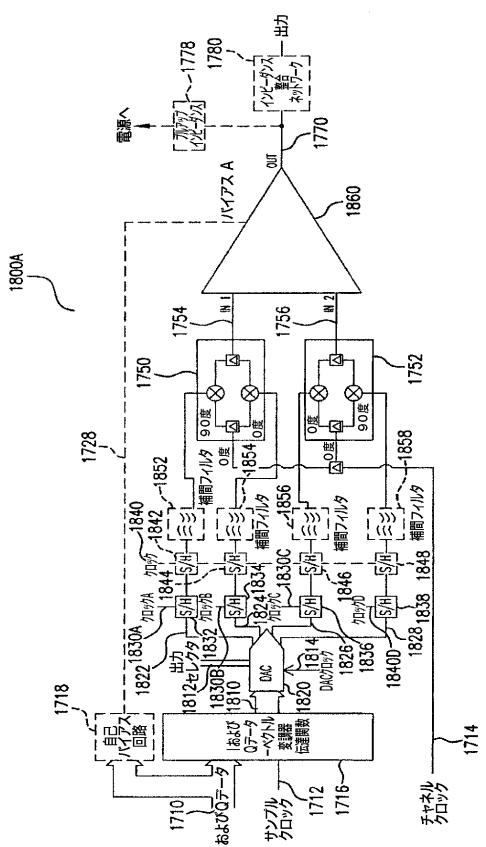

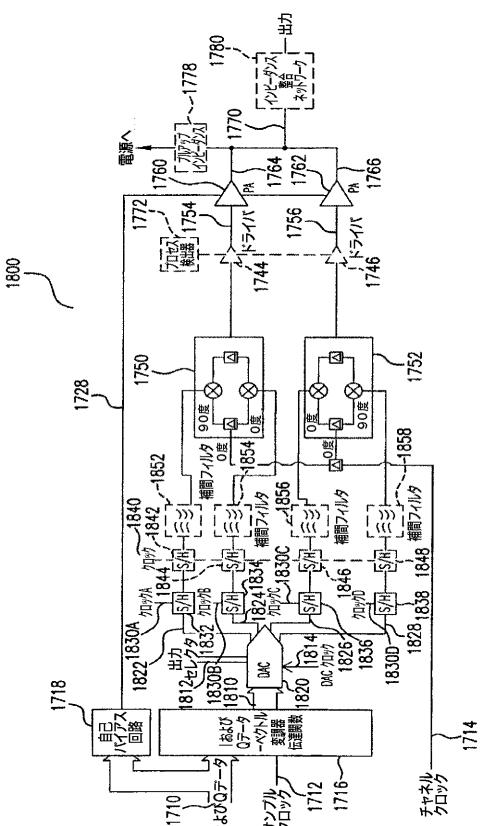

【0477】

図13は、CPCP2分岐VPAの実施形態によるベクトル電力増幅器の別の例示的実施形態1300を例示するブロック図である。任意選択のコンポーネントが破線で例示されるが、他の実施形態では、より多くのあるいはより少ないコンポーネントが任意選択であってもよい。

30

【0478】

図13の例示的実施形態では、十分な分解能およびサンプルレートのDAC1320が、図12の実施形態のDAC1230、1232、1234および1236に取って代わる。DAC1320は、DACクロック1324によって制御される。

【0479】

DAC1320は、情報信号1310をIおよびQデータ伝達関数モジュール1216から受信する。情報信号1310は、図12の実施形態における信号1220、1222、1224および1226と等しい情報内容を含む。

【0480】

DAC1320は、一度に単一のアナログ信号を出力してもよい。したがって、図13に示すように、サンプルホールドアーキテクチャを使用してもよい。

40

【0481】

DAC1320は、アナログ信号1332、1334、1336、1338を、第1のセットのサンプルホールド回路1342、1344、1346および1348へ、順次出力する。一実施形態では、DAC1320は、図12の実施形態のDAC1230、1232、1234および1236に取って代わるために、十分なレートでクロックされる。出力セレクタ1322は、出力信号1332、1334、1336および1338のうち、どれが出力のために選択されるべきであるかを決定する。

【0482】

DAC1320のDACクロック信号1324、出力セレクタ信号1322、およびサ

50

ンプルホールドクロック 1340A～D および 1350 は、独立にするか、あるいは伝達関数モジュール 1216 に統合することができる、制御モジュールによって制御される。

#### 【0483】

一実施形態では、サンプルホールド回路 (S/H) 1342、1344、1346 および 1348 は、受信されたアナログ値をホールドし、クロック信号 1340A～D に従って、これらの値を第 2 のセットのサンプルホールド回路 1352、1354、1356 および 1358 へリリースする。例えば、S/H 1342 はその値を S/H 1352 へ、受信されたクロック信号 1340A に従ってリリースする。同様に、サンプルホールド回路 1352、1354、1356 および 1358 は、受信されたアナログ値をホールドし、同時にこれらの値を補間フィルタ 1231、1233、1235 および 1237 へ、共通クロック信号 1350 に従ってリリースする。共通クロック信号 1350 は、S/H 1352、1354、1356 および 1358 の出力が時間的に整合されることを保証するために使用される。

#### 【0484】

別の実施形態では、S/H 1342、1344、1346 および 1348 を含む、単層の S/H 回路を採用することができる。したがって、S/H 回路 1342、1344、1346 および 1348 は、アナログ値を DAC 1320 から受信し、それぞれがその受信された値を、他のものから独立したクロックに従ってリリースする。例えば、S/H 1342 は、クロック 1340A によって制御され、クロック 1340A は、S/H 1344 を制御するクロック 1340B と同期化されていなくてもよい。S/H 回路 1342、1344、1346 および 1348 の出力が時間的に整合されることを保証するために、クロック 1340A～D の間の遅延が、増幅器の以前のステージにおいて事前補償される。例えば、クロック 1340A～D の間の時間差を補償するために、DAC 1320 は、信号 1332、1334、1336 および 1338 を、適切に選択された遅延を有して、S/H 回路 1342、1344、1346 および 1348 へ出力する。

#### 【0485】

ベクトル電力増幅器 1300 の他の態様は、実質的には、ベクトル電力増幅器 1200 に関して上述したものに相当する。

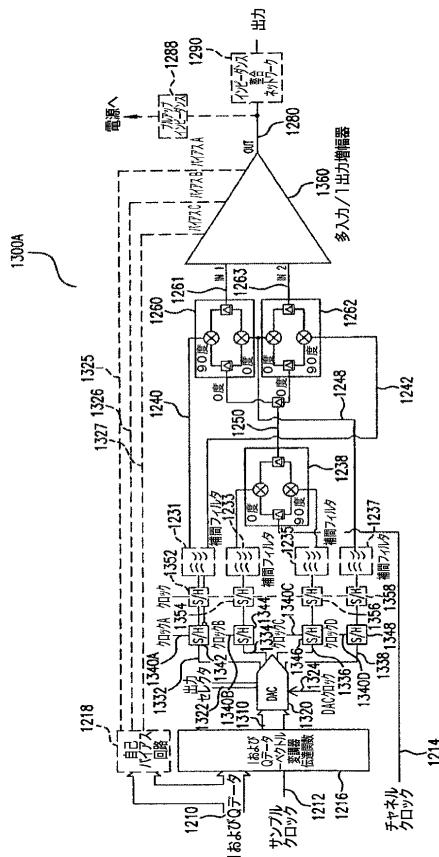

#### 【0486】

図 13A は、CPCP2 分岐 VPA の実施形態によるベクトル電力増幅器の別の例示的実施形態 1300A を例示するブロック図である。任意選択のコンポーネントが破線で表示されるが、他の実施形態では、より多くのあるいはより少ないコンポーネントが任意選択であってもよい。実施形態 1300A は、図 13 の実施形態 1300 の MISO 実装である。

#### 【0487】

図 13A の実施形態では、ベクトル変調器 1260 および 1262 から出力された、定包絡線信号 1261 および 1263 が、MISO PA 1360 に入力される。MISO PA 1360 は、2 入力 1 出力の電力増幅器である。一実施形態では、MISO PA 1360 は、図 13 の実施形態に示すような素子 1270、1272、1282、1284 および 1286 を含む。別の実施形態では、MISO PA 1360 は、図 13 の実施形態において図示されない、プレドライバなど、他の素子、またはその機能的均等物を含んでもよい。さらに、MISO PA 1360 は、図 13A に示すような 2 入力 PA であることに限定されない。他の実施形態では、以下で図 51A～H を参照してさらに説明するように、PA 1360 はいかなる数の入力を有することもできる。

#### 【0488】

図 13A の実施形態はさらに、図示のような单一または 2 つのレベルの S/H 回路を有する、2 つの異なるサンプルホールドアーキテクチャを例示する。この 2 つの実装は、図 13 に関して上述したものである。

#### 【0489】

実施形態 1300A はまた、任意選択のバイアス制御回路 1218、および、関連付け

10

20

30

40

50

られたバイアス制御信号 1325、1326 および 1327 をも例示する。信号 1325、1326 および 1327 を、ある実施形態において MISO PA1360 の異なるステージをバイアスするために使用してもよい。

【0490】

ベクトル電力増幅器 1300A の他の態様は、ベクトル電力増幅器 1200 および 1300 について上述したものに相当する。

【0491】

3.3) 直接デカルト 2 分岐ベクトル電力増幅器

直接デカルト 2 分岐 VPA の実施形態を、これから説明するものとする。この名称は参考のために本明細書で使用され、機能的あるいは構造的に限定しない。

10

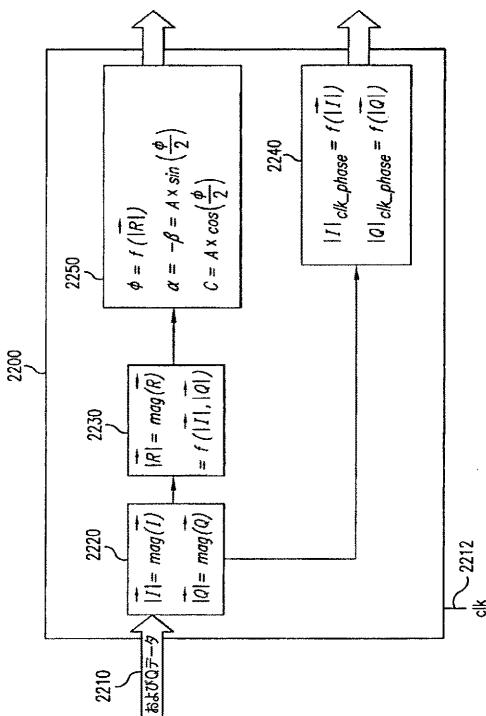

【0492】

直接デカルト 2 分岐 VPA の実施形態によれば、時変包絡線信号は 2 つの定包絡線成分信号に分解される。これらの成分信号は、個別に等しくあるいはほぼ等しく増幅され、次いで加算されて、元の時変包絡線信号の増幅されたバージョンが構成される。

【0493】

直接デカルト 2 分岐 VPA の実施形態の一実施形態では、時変包絡線信号の大きさおよび位相角は、入力信号の同相および直交成分から計算される。大きさおよび位相情報を使用して、同相および直交振幅成分が、時変包絡線信号の 2 つの定包絡線成分について計算される。2 つの定包絡線成分が次いで生成され、等しくあるいはほぼ等しく増幅され、加算されて、元の時変包絡線信号  $R_{in}$  の増幅されたバージョンが生成される。

20

【0494】

直接デカルト 2 分岐 VPA の概念を、これから図 9A および 14 を参照して説明する。

【0495】

図 9A について上記で説明し、検証したように、フェーザ

【0496】

【数 156】

$\overrightarrow{R'}$

【0497】

30

を、

【0498】

【数 157】

$\overline{\overrightarrow{R'}}$

【0499】

を生成するために適切に位相整合された上側フェーザ

【0500】

【数 158】

$\overrightarrow{U'}$

【0501】

および下側フェーザ

【0502】

【数 159】

$\overrightarrow{L'}$

【0503】

の和によって、得ることができる。

【0504】

40

50

【数160】

$\overrightarrow{R'}$

【0505】

は、大きさ  $R_{in}$  に比例するように計算される。さらに、

【0506】

【数161】

$\overrightarrow{U'}$

【0507】

および

【0508】

【数162】

$\overrightarrow{L'}$

【0509】

を、ほぼ一定の大きさを有するように維持することができる。時間領域では、

【0510】

【数163】

$\overrightarrow{U'}$

【0511】

および

【0512】

【数164】

$\overrightarrow{L'}$

【0513】

は、2つのほぼ一定の包絡線信号を表す。

【0514】

【数165】

$\overrightarrow{R'}$

【0515】

の時間領域等価物  $r'(t)$  を、よって、いずれかの時刻に、2つのほぼ一定の包絡線信号の和によって得ることができる。

【0516】

図9Aに例示した場合では、

【0517】

【数166】

$\overrightarrow{R'}$

に対する

【0518】

【数167】

$\overrightarrow{U'}$

【0519】

10

20

30

40

50

および

【0520】

【数168】

$\overrightarrow{L}$

【0521】

の位相シフトは、図9Aにおいて角度

【0522】

【数169】

$\frac{\phi}{2}$

【0523】

として例示され、以下のように

【0524】

【数170】

$\overrightarrow{R}$

【0525】

の大きさに関係する。

【0526】

【数171】

$$\frac{\phi}{2} = \cot^{-1} \left( \frac{R}{2\sqrt{1 - \frac{R^2}{4}}} \right)$$

10

【0527】

ただし、Rは、フェーザ

【0528】

【数172】

$\overrightarrow{R}$

【0529】

の正規化された大きさを表す。

【0530】

時間領域では、時変包絡線信号、例えば、 $r'(t) = R(t) \cos(\omega t)$ を、2つの定包絡線信号の和によって、以下のように構成することができる。

$$r'(t) = U'(t) + L'(t),$$

$$U'(t) = C \times \cos(\omega t) + S \times \sin(\omega t), \quad (14)$$

$$L'(t) = C \times \cos(\omega t) - S \times \sin(\omega t).$$

ただし、Cは、フェーザ

【0531】

【数173】

$\overrightarrow{U}$

【0532】

および

20

(13)

30

40

50

【 0 5 3 3 】

【 数 1 7 4 】

$\overline{L}$

【 0 5 3 4 】

の同相振幅成分を示し、

【 0 5 3 5 】

【 数 1 7 5 】

$$A \times \cos\left(\frac{\phi}{2}\right)$$

【 0 5 3 6 】

に等しいかあるいはほぼ等しい（Aは定数である）。およびは、フェーザ

【 0 5 3 7 】

【 数 1 7 6 】

$\overline{U}$

【 0 5 3 8 】

および

【 0 5 3 9 】

【 数 1 7 7 】

$\overline{L}$

【 0 5 4 0 】

の直交振幅成分をそれぞれ示す。

【 0 5 4 1 】

【 数 1 7 8 】

$$\alpha = \beta = A \times \sin\left(\frac{\phi}{2}\right)$$

【 0 5 4 2 】

である。基底関数を正弦から所望の関数に変更することによって、方程式（14）を非正弦波信号について修正することができることに留意されたい。

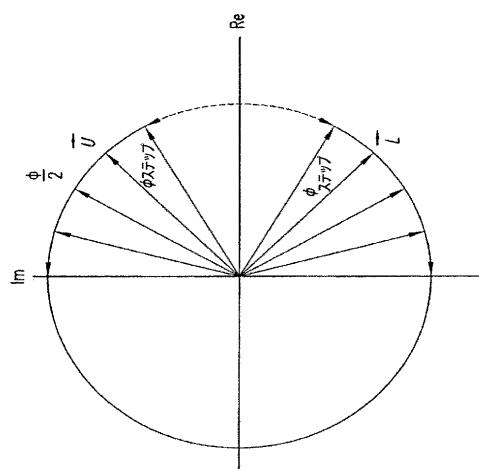

【 0 5 4 3 】

図14は、フェーザ

【 0 5 4 4 】

【 数 1 7 9 】

$\overline{R}$

【 0 5 4 5 】

、ならびに、その2つの一定の大きさの成分フェーザ

【 0 5 4 6 】

【 数 1 8 0 】

$\overline{U}$

【 0 5 4 7 】

および

【 0 5 4 8 】

10

20

30

40

【数181】

$\vec{L}$

【0549】

を例示する。

【0550】

【数182】

$\vec{R}$

【0551】

は、図9Aにおける

【0552】

【数183】

$\vec{R}'$

【0553】

に対して一度だけシフトされる。したがって、以下であることを検証することができる。

【0554】

【数184】

$$\vec{R} = \vec{R}' \times e^{j\theta} = (\vec{U}' + \vec{L}') \times e^{j\theta} = \vec{U}' + \vec{L};$$

$$\vec{U}' = \vec{U} \times e^{j\theta}; \quad (15)$$

$$\vec{L}' = \vec{L} \times e^{j\theta}.$$

【0555】

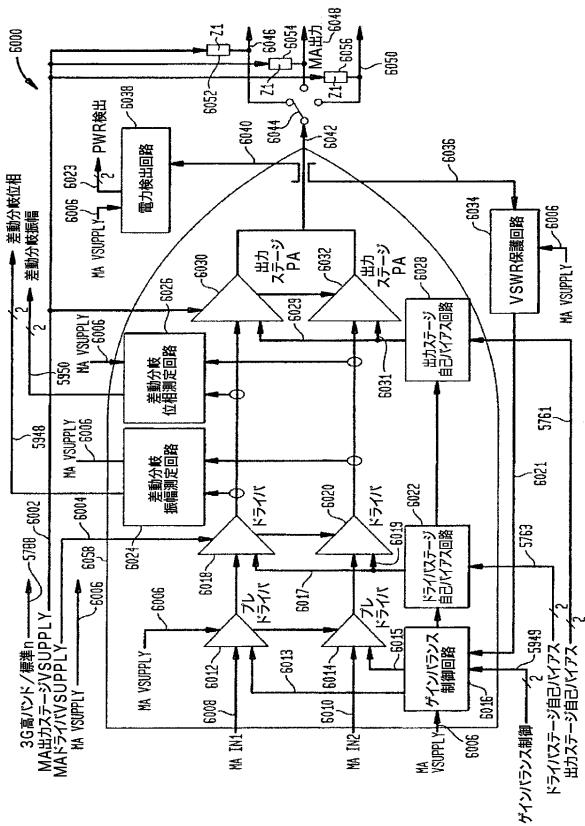

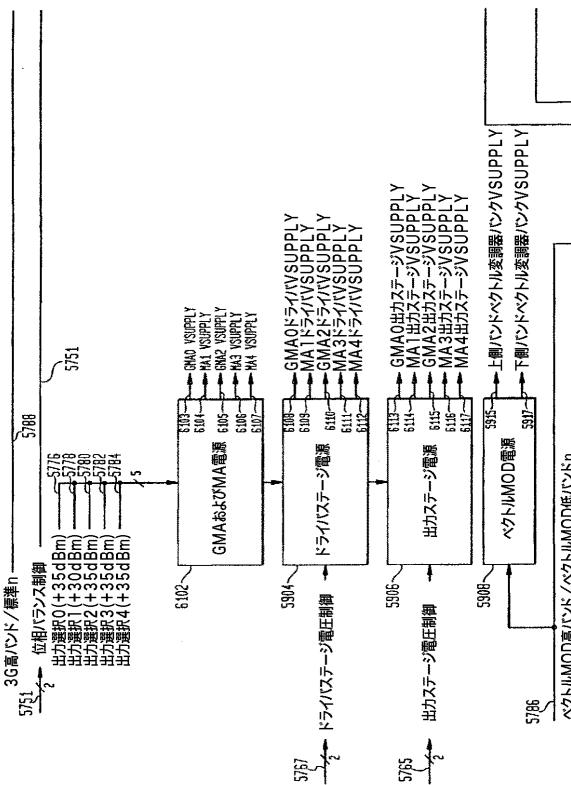

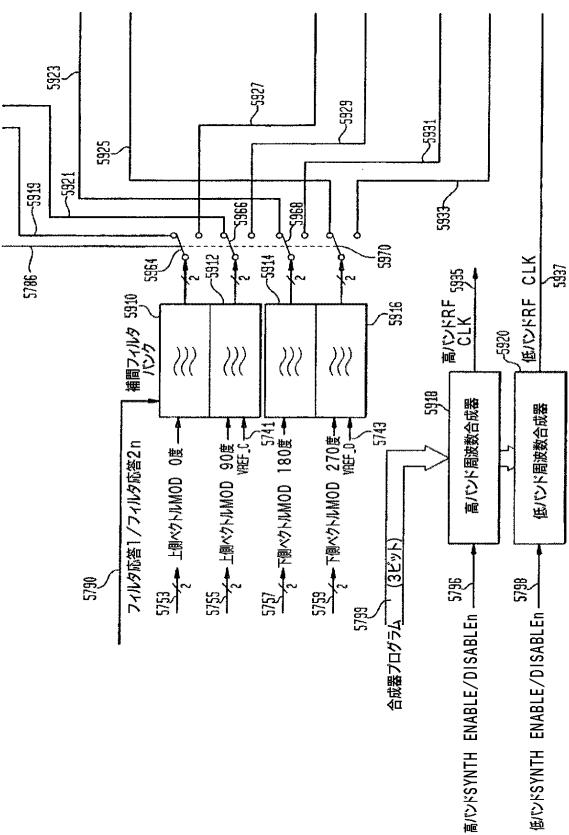

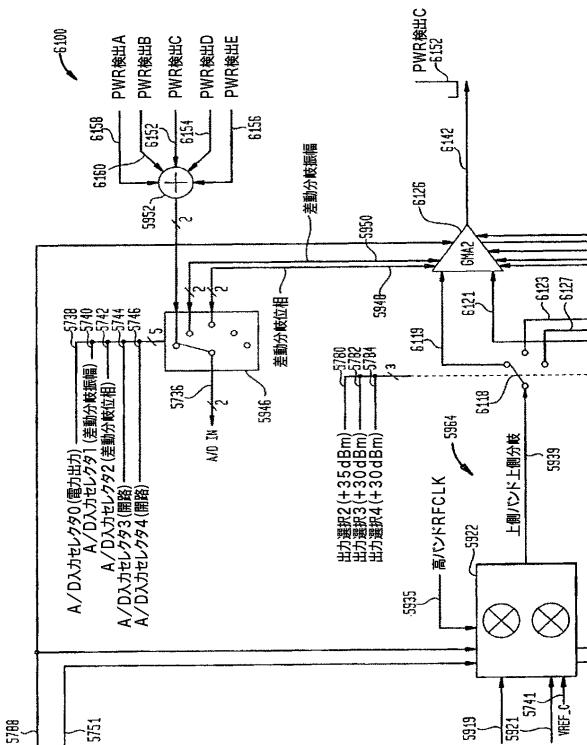

方程式(15)から、さらに以下であることが分かる。