(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3919378号

(P3919378)

(45) 発行日 平成19年5月23日(2007.5.23)

(24) 登録日 平成19年2月23日(2007.2.23)

(51) Int.CI.

F 1

HO 1 L 31/10 (2006.01)

HO 1 L 31/10

A

請求項の数 6 (全 16 頁)

(21) 出願番号 特願平11-89007

(22) 出願日 平成11年3月30日(1999.3.30)

(65) 公開番号 特開2000-286443(P2000-286443A)

(43) 公開日 平成12年10月13日(2000.10.13)

審査請求日 平成16年1月16日(2004.1.16)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100065385

弁理士 山下 横平

(72) 発明者 小塚 開

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 小泉 徹

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 吉野 三寛

最終頁に続く

(54) 【発明の名称】受光素子及びそれを用いた光電変換装置

## (57) 【特許請求の範囲】

## 【請求項1】

第1導電型の半導体基板上に設けられた第1導電型の第1エピタキシャル半導体領域と、

該第1エピタキシャル半導体領域に接し、且つ遮光層により規定される開口部に設けられた第2導電型の第2半導体領域と、

該第2半導体領域の主表面上に設けられた第1導電型の第3半導体領域と、

前記第2半導体領域に形成された電極領域である第2導電型の第4半導体領域と、

該電極領域に電気的に接続された配線手段と、

を有する受光素子であって、

前記半導体基板と前記第1エピタキシャル半導体領域との間に第1導電型の第5半導体領域を有し、

前記第5半導体領域の不純物濃度は前記半導体基板、及び前記第1エピタキシャル半導体領域よりも高いこと

を特徴とする受光素子。

## 【請求項2】

前記第2半導体領域は、不純物濃度が異なる領域を有していることを特徴とした請求項1の受光素子。

## 【請求項3】

前記第4半導体領域が前記遮光層で覆われていることを特徴とした請求項1の受光素子

10

20

。

**【請求項 4】**

第1導電型の半導体基板上に設けられた第1導電型の第1エピタキシャル半導体領域と、

該第1エピタキシャル半導体領域に接し、且つ遮光層により規定される開口部に設けられた第2導電型の第2半導体領域と、

該第2半導体領域の主表面上に設けられた第1導電型の第3半導体領域と、

前記第2半導体領域に形成された電極領域である第2導電型の第4半導体領域と、

該電極領域に電気的に接続された配線手段と、

を有する受光素子と、

該受光素子をリセットするリセット手段と、

前記受光素子に蓄積された電荷を電圧信号に変換する電荷-電圧変換手段と、

を有する光電変換装置であって、

前記半導体基板と前記第1エピタキシャル半導体領域との間に第1導電型の第5半導体領域を有し、

前記第5半導体領域の不純物濃度は前記半導体基板、及び前記第1エピタキシャル半導体領域よりも高く、

前記受光素子がリセットされた直後、及び飽和出力時において、上記第2半導体領域が略全域に渡って空乏化していること

を特徴とする光電変換装置。

10

20

**【請求項 5】**

前記第2半導体領域は、不純物濃度が異なる領域を有していることを特徴とした請求項4の光電変換装置。

**【請求項 6】**

前記第4半導体領域が前記遮光層で覆われていることを特徴とした請求項4の光電変換装置。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、イメージセンサやファクシミリ、複写機等の画像読み取りシステムに用いられるイメージセンサの受光素子構造及びこれを用いた光電変換装置に関わるものであり、特に、例えばカメラに用いられるオートフォーカスセンサのように画素の開口部が数十ミクロン以上の比較的大きい受光素子を有し、かつ赤、もしくは赤外感度が要求される光電変換装置に好適な受光素子構造に関わるものである。

30

**【0002】**

**【従来の技術】**

近年、一次元の光電変換装置の分野においては、縮小光学系を用いたCCDや、複数の半導体光センサチップをマルチ実装した、等倍系の密着型イメージセンサや、CCD、またはバイポーラトランジスタやCMOSトランジスタを用いたオートフォーカスセンサのように、比較的大きな開口部を有する受光素子の開発が積極的に行われている。これらの光電変換装置においては、受光素子は、半導体のPN接合から成るホトダイオードを用いるのが一般的である。

40

**【0003】**

**従来技術(1)**

たとえば、特開昭55-154784号公報にはPN接合が形成されていない基板表面部に、基板と同一導電型で、かつ基板より不純物濃度が高い領域を設け、基板表面で発生する暗電流を低減させた構造が提案されている。

**【0004】**

**従来技術(2)**

また、一次元の光電変換装置用の受光素子として、特開昭61-264758号公報に開

50

示されているように、P N接合が形成する接合容量を低減させたものが提案されている。

**【0005】**

従来技術(3)

さらに密着型イメージセンサに用いる感光部構造として、例えば、特開平1-303752号公報に開示されているように、チップ端部のスクライブに起因する暗電流の低減をはかったものが提案されている。

**【0006】**

従来技術(4)

また、CCDにおける受光素子構造としては、例えば特開昭60-145865号公報に開示されているように、N型基板/P型領域/N(N<sup>+</sup>)型領域/P<sup>+</sup>型領域という断面構造を有するホトダイオードが一般的に用いられている。

10

**【0007】**

従来技術(5)

一方、受光素子を用いた光電変換装置として、例えば特開平9-205588号公報には、ホトダイオードを受光素子とし、この受光素子の電荷をソースホロアアンプを用いて一括読み出しを行う光電変換装置が提案されている。

**【0008】**

**【発明が解決しようとする課題】**

しかしながら、上記従来技術(1)～(4)を用いて光生成キャリアをP N接合部に蓄積し、電荷・電圧変換手段を用いて信号電圧を読み出す増幅型の光電変換装置に適用した場合、高感度が得られないという問題が生ずる。

20

**【0009】**

また、上記従来技術(5)に示すような増幅型光電変換装置の場合、光出力は1式にて表わされる。

**【0010】**

$$V_p = Q_p / C_s \quad \dots \quad 1$$

ここで、Q<sub>p</sub>はP N接合部に蓄積される電荷量、C<sub>s</sub>は光電変換部の容量である。

**【0011】**

この光電変換部の容量C<sub>s</sub>は、例えば、ホトダイオード、MOSソースホロア、リセットMOSから成る増幅型光電変換装置の場合、

30

$$C_s = C_{pd} + C_a \quad \dots \quad 2$$

と表わすことができる。

**【0012】**

ここで、C<sub>pd</sub>は受光部のP NホトダイオードのP N接合容量、C<sub>a</sub>は光電変換部に接続されているその他の容量で、上記の場合、MOSソースホロアを形成するMOSトランジスタのゲート容量や、リセットMOSを形成するMOSトランジスタのソース／ウエルの接合容量、ソース／ゲート重なり容量、配線容量、等が含まれる。

**【0013】**

従って、高感度を実現するためには、光生成キャリアを有効に蓄積すること、キャリアが蓄積される光電変換部の容量をできるだけ小さくすることが必要となる。

40

**【0014】**

しかしながら、半導体基板中に反対導電型の領域を形成して得られるホトダイオードを受光部に用いた密着型イメージセンサにおいては、例えば、300dipiの解像度の場合、画素ピッチは約84.7ミクロンとなるため、光キャリアを有効に取り出すためには、開口部とほぼ同一面積のP N接合が必要となるが、2式におけるホトダイオード部のP N接合容量が増加する。

**【0015】**

一方、ホトダイオード部のP N接合容量を小さくするために、P N接合面積を小さくすると、P N接合により形成される空乏層領域が開口に対して過少となり、P N接合部に蓄積されるキャリアが減少する。

50

**【0016】**

上記従来技術(2)(特開昭61-264758号公報)には蓄積領域の接合容量を低減するために、蓄積部を環状、または一部分が切断された環状に形成することが開示されているが、上記従来技術(1)(特開昭55-154784号公報)に開示されているように、基板表面で発生する暗電流を抑制するために、基板と同一導電型でかつ基板よりも不純物濃度が高い領域を基板表面に設けた場合には、従来技術(1)に示されているように、接合部の周囲部で空乏層が狭くなり、PN接合容量の周囲長依存が大きくなる(特開昭61-264758号公報の図2)。

**【0017】**

従って、従来技術(2)に開示されている構造では、PN接合部の面積は減少しているものの、周囲長が増加するため、PN接合部の容量値を十分に小さくすることができず、高感度化が困難であった。

**【0018】**

また、上記従来技術(1)(特開昭55-154784号公報)に開示されているように、基板表面で発生する暗電流を抑制するために、基板と同一導電型でかつ基板よりも不純物濃度が高い領域を基板表面に設けた構造を開口部が比較的大きな光電変換装置に適用した場合、この表面部分は例えばALエッチング時やレジストのアッシング時にプラズマダメージにより基板表面部に欠陥が生成され、この欠陥部分から発生したキャリアが受光部に到達し暗電流の原因となる。

**【0019】****[発明の目的]**

本発明の目的は、ホトダイオード部のPN接合容量を極力低減し、かつ、光生成キャリアを有効に活用することが可能で、さらに暗電流を低減し、製造プロセスがばらついても高歩留まりが維持でき、また、高感度、特に赤色光から赤外光に対する感度が高く、例えばオートフォーカスシステム等に好適な受光素子の構造を提案し、高性能な光電変換装置、及びそれを用いた画像入力システム、位置検出システムを提供することにある。

**【0020】****【課題を解決するための手段】**

上記の課題を解決するために、本発明の受光素子は、第1導電型の半導体基板上に設けられた第1導電型の第1エピタキシャル半導体領域と、該第1エピタキシャル半導体領域に接し、且つ遮光層により規定される開口部に設けられた第2導電型の第2半導体領域と、該第2半導体領域の主表面上に設けられた第1導電型の第3半導体領域と、前記第2半導体領域に形成された電極領域である第2導電型の第4半導体領域と、該電極領域に電気的に接続された配線手段と、を有する受光素子であって、前記半導体基板と前記第1エピタキシャル半導体領域との間に第1導電型の第5半導体領域を有し、前記第5半導体領域の不純物濃度は前記半導体基板、及び前記第1エピタキシャル半導体領域よりも高いことを特徴とする。

**【0021】**

また、本発明の受光素子において、前記第2半導体領域は、不純物濃度が異なる領域を有していることを特徴とする。

**【0022】**

また、本発明の受光素子において、前記第4半導体領域が前記遮光層で覆われていることを特徴とする。

**【0023】**

また、本発明の光電変換装置は、第1導電型の半導体基板上に設けられた第1導電型の第1エピタキシャル半導体領域と、該第1エピタキシャル半導体領域に接し、且つ遮光層により規定される開口部に設けられた第2導電型の第2半導体領域と、該第2半導体領域の主表面上に設けられた第1導電型の第3半導体領域と、前記第2半導体領域に形成された電極領域である第2導電型の第4半導体領域と、該電極領域に電気的に接続された配線手段と、を有する受光素子と、該受光素子をリセットするリセット手段と、前記受光素子

10

20

30

40

50

に蓄積された電荷を電圧信号に変換する電荷 - 電圧変換手段と、を有する光電変換装置であって、前記半導体基板と前記第1エピタキシャル半導体領域との間に第1導電型の第5半導体領域を有し、前記第5半導体領域の不純物濃度は前記半導体基板、及び前記第1エピタキシャル半導体領域よりも高く、前記受光素子がリセットされた直後、及び飽和出力時において、上記第2半導体領域が略全域に渡って空乏化していることを特徴とする。

#### 【0024】

また、本発明の光電変換装置において、前記第2半導体領域は、不純物濃度が異なる領域を有していることを特徴とする。

#### 【0025】

また、本発明の光電変換装置において、前記第4半導体領域が前記遮光層で覆われていることを特徴とする。

10

#### 【0026】

以下実施態様例を用いて、本発明の構成、動作、および作用効果について説明する。

#### 【0027】

##### 【発明の実施の形態】

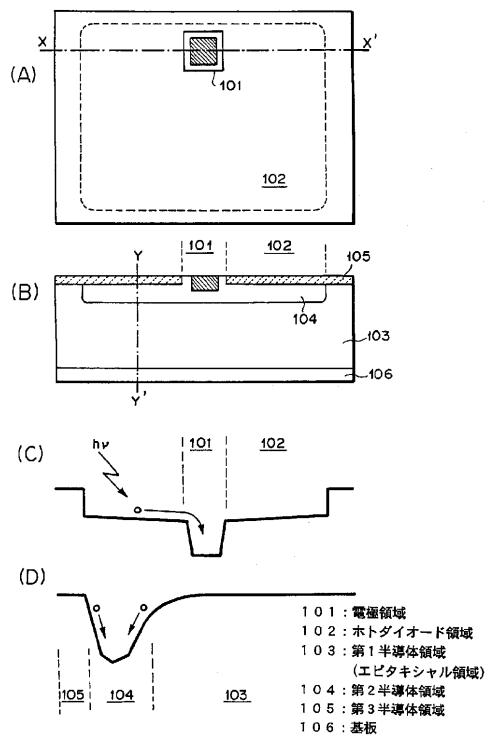

以下、図1、図2、図3を用いて本発明の実施態様例を説明する。

#### 【0028】

図1は、本発明の特徴を最もよく表した図面であり、

同図(A)は、本発明の受光素子部の平面図、

同図(B)は(A)の線分X-Xにおける断面構造図、

20

同図(C)は、線分X-Xにおけるポテンシャルプロファイル図、

同図(D)は、線分Y-Yにおけるポテンシャルプロファイル図、

である。

#### 【0029】

図中101は、前述の電極領域であり、具体的には、n型層とn型の高濃度不純物領域などからなる。

#### 【0030】

図中103、104、105は、それぞれ前述の第1半導体領域(エピタキシャル領域)、第2半導体領域、第3半導体領域である。

#### 【0031】

30

図中102が、前述の第1、第2、第3半導体領域からなる、ホトダイオード領域であり、この領域で光で発生したキャリアが電極領域101に捕獲される。

#### 【0032】

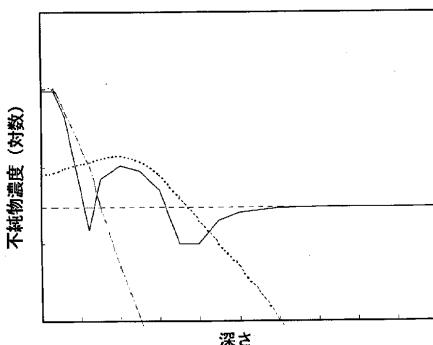

図2に線分Y-Yにおける、不純物プロファイルの具体例の一つを示す。

#### 【0033】

n型の半導体基板の表面にp型のエピタキシャル領域(103)、ついでn層を配し、n層を表面のp層とp型のエピタキシャル領域で挟む構造にする。この時、n層には、表面のp層とp型の半導体基板の両側に空乏層が形成され、図1(D)のようなポテンシャル構造が形成される。この結果、発生した電子・正孔対の電子はこのポテンシャルの溝に集められ、最終的には、最もポテンシャルの低い電極領域101に収集される。

40

#### 【0034】

このようなポテンシャル構造がない場合では、発生した電子は、拡散により、シリコン中を迷走し、電極101の形成する空乏層を通過した電子は、電極101に到達するが、ライフタイム以内に到達できなければ、正孔と再結合してしまう。

#### 【0035】

電極101の近傍で発生した電子は、電極に到達しやすいが、受光部の端で発生した電子は、例えば、約40μm(300dipi開口画素の中心部を仮定)離れた電極領域に到達する確立は極めて低く、結果として、感度が大きく損なわれる。

#### 【0036】

これに対し、本発明の構造では、少なくとも表面から約1μm以内に発生した電子は殆ど

50

収集することができる。特に、可視光センサで問題となる青色の感度については、青色光のその殆どがシリコン表面  $1 \mu m$  以内で吸収される。従って、前述の通り、本発明によれば、発生した電荷の殆どを収集することができる。

#### 【0037】

また、高エネルギーイオン注入などの技術を用い、レトログレードウェル構造などを用いたり、その逆にエピタキシャル領域 103 の濃度を下げ、空乏層を広げることでより深いところで発生した電子を収集することもできる。

#### 【0038】

さらに、基板表面に高濃度の不純物層を形成し、その上に低不純物濃度のエピタキシャル層を設け、本発明を適用することにより、長波長感度の高い受光部構造を得ることも可能である。10

#### 【0039】

また、本発明においては、エピタキシャル層中にホトダイオードを形成しているため、空乏層中の欠陥に起因する暗電流を抑制でき、特に密着型イメージセンサや、カメラの AF センサ等に用いられる、比較的大面積のホトダイオードを有する光電変換装置に好適である。

#### 【0041】

本発明の更なる特徴は、n 層 104 がほぼ全体にわたって空乏化するように、表面の p 層 105、エピタキシャル領域 103、n 層 104 の不純物濃度と接合深さ、及び電極 101 の電位が設定されている点である。その結果、n 層 104 は容量としては、殆ど寄与しなくなり、受光部容量の低減が可能となる。20

#### 【0042】

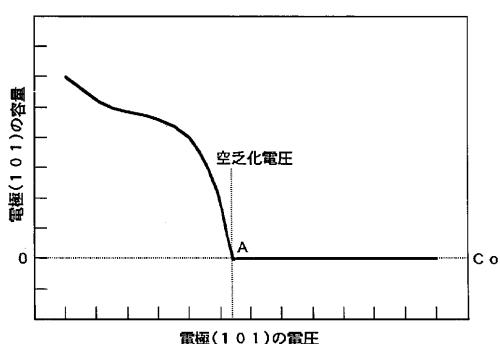

より詳細な説明のため、図 3 に電極 101 の電位とその時の容量の関係を示す。

#### 【0043】

電圧が低いときには、n 層 104 は空乏化しておらず、容量としては、n 層 104 と表面の p 層 105 間の空乏層容量と、n 層 104 と基板 103 間の空乏層容量が見える。ここで、電極 101 の電圧が上がるに従い、空乏層が広がるため、徐々に容量が減少するが、104 - 105 間、104 - 103 間の空乏層が接続されると、n 層がほぼ完全に空乏化し、容量が急激に減少する。その状態が図中 A 点であり、以下この電圧を空乏化電圧と称する。30

#### 【0044】

空乏化電圧は、表面の p 層 105、n 層 104、p 型エピタキシャル領域 103 の不純物濃度で決定されるため、

- ・受光素子をリセットした状態における電極 101 の電位、

- ・光電変換装置の光出力が飽和した状態の電極 101 の電位

を、この空乏化電圧以上に設定することで、n 層 104 の容量、即ち電極 101 部分における容量を、実質的に電極 101 の底部の接合容量  $C_0$  程度にまで小さくすることが可能となり、高感度が実現できる。

#### 【0045】

ここで、光により発生した電荷が電極 101 に蓄積されることにより、電極の電位は変化するが、動作点を空乏化電圧以上になるよう設計することにより、電極 101 部分の容量は線形性を有しているため、高感度かつ線形性の良好な光電変換特性を得ることができる。40

#### 【0046】

また、空乏化電圧を境に容量値は、 $C_0$  から、n 層 104 の面積で決定される容量値まで指數関数的に増加する。

#### 【0047】

例えば、電極 101 と n 層 104 の面積が各々、 $1.2 \mu m \times 1.2 \mu m$ 、及び  $80 \mu m \times 80 \mu m$  であった場合、その容量比は約 4400 倍となる。

#### 【0048】

10

30

40

50

この特徴を利用することにより、指數関数的な光電変換特性を有し、極めてダイナミックレンジが大きい光電変換装置を実現することも可能となる。

#### 【0049】

尚、説明を簡略化するために、103, 104, 105を、おののおのp型エピタキシャル領域、n層、p層として説明してきたが、本発明はこの導電型に限定されるものではなく、おののおのがn型エピタキシャル領域、p層、n層のように上記と反対の導電型でも良い。

#### 【0050】

また、電極101は、電極の機能を果たせばよいため、必ずしも高濃度不純物領域に限定されるものではなく、電圧を制御できる程度のオーミックコンタクトを得ることができれば金属を直接半導体領域に接続した構成でも構わない。

#### 【0051】

##### 【実施例】

以下、本発明の参考例と実施例を説明する。

#### 【0052】

##### 【参考例】

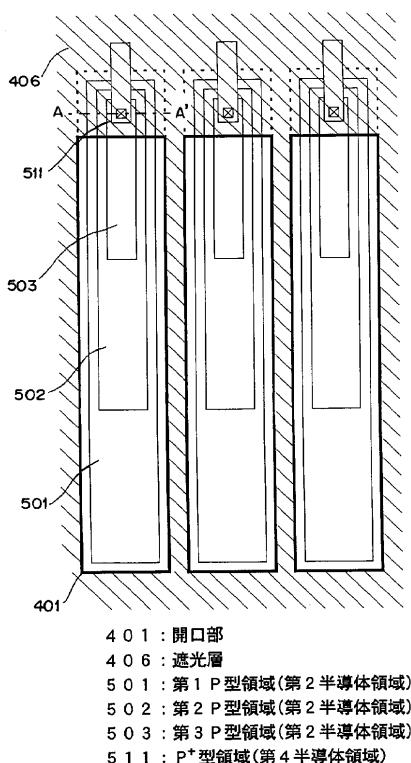

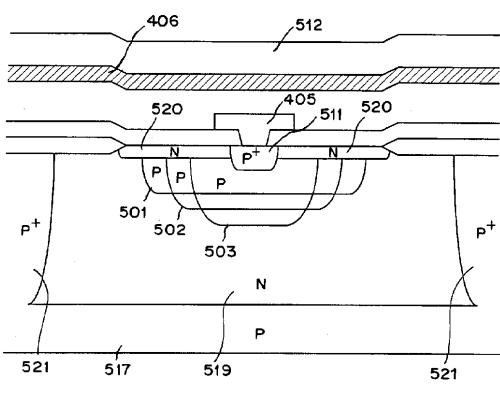

図4は本発明の参考例における3画素分の受光素子の平面構造図、図5は図4のA-A部における断面構造図である。

#### 【0053】

図4において、開口部401中に受光素子となるホトダイオードの第1p型領域501(第2半導体領域)、第2p型領域502(第2半導体領域)、第3p型領域503(第2半導体領域)が形成され、上記ホトダイオード中に形成されたp<sup>+</sup>型領域511(第4半導体領域(電極領域))は、第1AL層で形成される配線405により電気的に接続されている。また、受光素子の開口部401は第2AL層で形成される遮光層406により規定されている。ここで、開口部401の大きさは20μm×100μmである。

#### 【0054】

図5において、p型半導体基板517に設けられたn<sup>-</sup>型エピタキシャル領域519(第1エピタキシャル領域)の開口部401中に第1p型領域501、第2p型領域502、第3p型領域503が形成され、さらに第1p型領域501、第2p型領域502、第3p型領域503中にはp<sup>+</sup>型領域511が島状に設けられている。また、第1p型領域501、第2p型領域502、第3p型領域503の主表面には、n型表面領域520(第3半導体領域)が設けられ、n<sup>-</sup>型エピタキシャル領域519と電気的に接続されている。

#### 【0055】

従って、第1p型領域501、第2p型領域502、第3p型領域503とn<sup>-</sup>型エピタキシャル領域519、及びn型表面領域520とのpn接合によってホトダイオードが形成されており、ホトダイオードで光電変換された光キャリアはp<sup>+</sup>型領域511に収集され、第1AL層で形成される配線405の電位を変化せしめる。

#### 【0056】

また、おののおのの受光素子はp型半導体基板517と電気的に接続されたp<sup>+</sup>領域521(第5半導体領域)で素子分離されているが、要求される素子分離性能によっては、このp<sup>+</sup>領域521を除去することも可能である。

#### 【0057】

さらに、p型領域511は第1AL層で形成される配線405により電気的に接続され、第2AL層で形成される遮光層406の上部には保護膜512が設けられている。

#### 【0058】

図5において、おののおのの領域のおおよその表面濃度/接合深さを以下に示す。

#### 【0059】

P型基板517 : 約  $5 \times 10^{14}$  (cm<sup>-3</sup>)

n<sup>-</sup>型エピタキシャル領域519 : 約  $1 \times 10^{15}$  (cm<sup>-3</sup>) / 約 10.0 μm

|                          |                                                        |

|--------------------------|--------------------------------------------------------|

| 第 1 p 型領域 5 0 1          | : 約 $2 \times 10^{16}$ (cm <sup>-3</sup> ) / 約 0.50 μm |

| 第 2 p 型領域 5 0 2          | : 約 $3 \times 10^{16}$ (cm <sup>-3</sup> ) / 約 0.60 μm |

| 第 3 p 型領域 5 0 3          | : 約 $4 \times 10^{16}$ (cm <sup>-3</sup> ) / 約 0.70 μm |

| n 型表面領域 5 2 0            | : 約 $3 \times 10^{17}$ (cm <sup>-3</sup> ) / 約 0.30 μm |

| p <sup>+</sup> 型領域 5 1 1 | : 約 $3 \times 10^{19}$ (cm <sup>-3</sup> )             |

また、本参考例における第 1 p 型領域 5 0 1、第 2 p 型領域 5 0 2、第 3 p 型領域 5 0 3 のおののの空乏化電圧は、

|                            |

|----------------------------|

| 第 1 p 型領域 5 0 1 : 約 -1.0 V |

| 第 2 p 型領域 5 0 2 : 約 -1.5 V |

| 第 3 p 型領域 5 0 3 : 約 -2.0 V |

となっている。

#### 【0060】

従って、例えば、電源電圧 5 V 動作において n<sup>-</sup> 型エピタキシャル領域 5 1 9 を電源電圧に接続した場合には、p<sup>+</sup> 型領域 5 1 1 及び配線 4 0 5 の電位が 3 V 以下であれば、第 1 p 型領域 5 0 1、第 2 p 型領域 5 0 2、第 3 p 型領域 5 0 3 は空乏化することになる。

#### 【0061】

さらに、第 1 p 型領域 5 0 1、第 2 p 型領域 5 0 2、第 3 p 型領域 5 0 3 の空乏化電圧が p<sup>+</sup> 型領域 5 1 1 に向かって高くなっているため、光キャリアのポテンシャルの勾配が形成されるため、本参考例のように、開口部のアスペクト比が 5 というような細長い受光素子の場合でも、より効率良く光キャリアを p<sup>+</sup> 型領域 5 1 1 部分に収集することが可能となる。

#### 【0062】

尚、本参考例においては、第 1 p 型領域 5 0 1、第 2 p 型領域 5 0 2、第 3 p 型領域 5 0 3 はすべてイオン注入法により形成し、イオン注入時のドーズ量と加速エネルギーを変化させて図 5 に示すような領域を形成している。

#### 【0063】

また、図示していないが、本参考例においては p 型基板 5 1 7 から p<sup>+</sup> 型領域 5 1 1 方向に向かって n<sup>-</sup> 型エピタキシャル領域 5 1 9 の不純物濃度を減少させ、ポテンシャルの勾配を設けた構造となっているため、第 1 p 型領域 5 0 1、第 2 p 型領域 5 0 2、第 3 p 型領域 5 0 3 と、n<sup>-</sup> 型エピタキシャル領域 5 1 9 で形成される空乏層近傍で吸収された光による光キャリアのみならず、n<sup>-</sup> 型エピタキシャル領域 5 1 9 の中性領域で吸収された光による光キャリアも信号として p<sup>+</sup> 型領域 5 1 1 に効率良く収集される構成となっている。

#### 【0064】

一方、p 型基板 5 1 7 と n<sup>-</sup> 型エピタキシャル領域 5 1 9 で形成される空乏層近傍で吸収された光による光キャリアは光信号に寄与しない。

#### 【0065】

従って、本参考例の受光素子は、ある程度の赤感度が要求されるが、赤外感度をカットしたい場合等の用途に好適である。

#### 【0066】

また、ある画素に飽和以上の光キャリアが蓄積されても、あふれた光キャリアは周囲の p 型領域に吸収されるため、他の画素へ影響を与えることなく、にじみの少ない、高品質な信号を得ることができる。

#### 【0067】

加えて、本参考例においては、p 型基板 5 1 7 にて発生したキャリアは p 型基板 5 1 7 と n<sup>-</sup> 型エピタキシャル領域 5 1 9 との p n 接合により p<sup>+</sup> 型領域 5 1 1 へ混入することが無いため、高温時の暗電流特性も良好である。

#### 【0068】

さらに、本参考例においては、低濃度のエピタキシャル成長層中にホトダイオードを形成しているため、n 型表面領域 5 2 0 の不純物濃度を  $10^{17}$  (cm<sup>-3</sup>) 程度にしても空乏

10

20

30

40

50

化電圧が制御でき、かつ、n型表面領域520を受光部全面にイオン注入法を用いて形成してもp<sup>+</sup>型領域511とn型表面領域520の間に逆バイアスを印加してもブレークダウン等を引き起こさないため、アライメントズレ等による不具合を生じること無く、安定した受光部容量を得ることができ、感度バラツキ等の不具合を抑制することができる。

#### 【0069】

また、受光素子部において、シリコンと酸化膜の界面部に存在する空乏層はp<sup>+</sup>型領域511の周囲部のみで、かつp<sup>+</sup>型領域511を島状に形成しているため、キャリア収集効率が高く、低暗電流が実現できる。

#### 【0070】

##### [実施例]

本実施例は、本発明者らが特開平9-205588号公報に提案している光電変換装置に実施例に示した受光素子を適用し、この光電変換装置をカメラのオートフォーカスセンサに応用した例である。

#### 【0071】

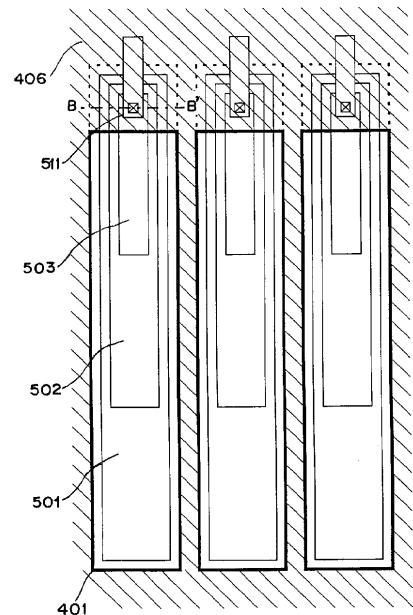

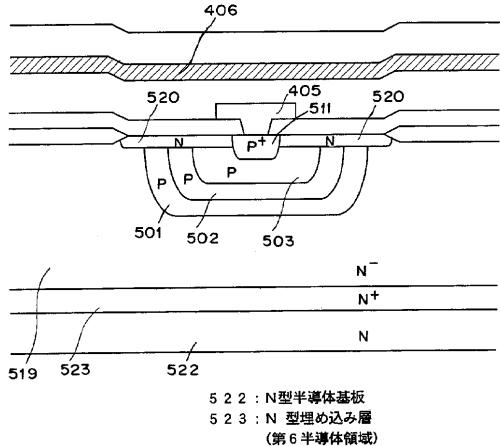

図6は本発明の実施例における3画素分の受光素子の平面構造図、図7は図6のB-B部における断面構造図、図8は本実施例における光電変換装置の1画素の等価回路図である。

#### 【0072】

図6において、開口部401中に受光素子となるホトダイオードの第1p型領域501(第2半導体領域)、第2p型領域502(第2半導体領域)、第3p型領域503(第2半導体領域)が形成され、上記ホトダイオード中に形成されたp<sup>+</sup>型領域511(第4半導体領域(電極領域))は、第1AL層で形成される配線405により電気的に接続されている。また、受光素子の開口部401は第2AL層で形成される遮光層406により規定されている。ここで、開口部401の大きさは18μm×100μm、画素ピッチは24μmである。

#### 【0073】

図7において、n型半導体基板522中にn<sup>+</sup>型埋込み層523(第6半導体領域)が形成され、さらに、その上部にエピタキシャル成長法を用いてn<sup>-</sup>型エピタキシャル領域519(第1エピタキシャル領域)が設けられている。

#### 【0074】

また、n<sup>-</sup>型エピタキシャル領域519の開口部401中には第1p型領域501、第2p型領域502、第3p型領域503が形成され、さらに第1p型領域501、第2p型領域502、第3p型領域503中にはp<sup>+</sup>型領域511が島状に設けられている。

#### 【0075】

また、第1p型領域501、第2p型領域502、第3p型領域503の主表面には、n型表面領域520(第3半導体領域)が設けられ、n<sup>-</sup>型エピタキシャル領域519(第1エピタキシャル領域)と電気的に接続されている。

#### 【0076】

従って、第1p型領域501、第2p型領域502、第3p型領域503とn<sup>-</sup>型エピタキシャル領域519、及びn型表面領域520とのpn接合によってホトダイオードが形成されており、ホトダイオードで光電変換された光キャリアはp<sup>+</sup>型領域511に収集され、第1AL層で形成される配線405の電位を変化せしめる。

#### 【0077】

さらに、p型領域511は第1AL層で形成される配線405により電気的に接続され、第2AL層で形成される遮光層406の上部には保護膜512が設けられている。

#### 【0078】

図7において、おのおのの領域のおおよその表面濃度/接合深さを以下に示す。

#### 【0079】

p型基板517 : 約5×10<sup>15</sup>(cm<sup>-3</sup>)

n<sup>-</sup>型エピタキシャル領域519 : 約3×10<sup>15</sup>(cm<sup>-3</sup>) / 約8.0μm

|                        |                                                                    |

|------------------------|--------------------------------------------------------------------|

| 第1 p型領域 501            | : 約 $2 \times 10^{16}$ ( $\text{cm}^{-3}$ ) / 約 0.80 $\mu\text{m}$ |

| 第2 p型領域 502            | : 約 $3 \times 10^{16}$ ( $\text{cm}^{-3}$ ) / 約 0.75 $\mu\text{m}$ |

| 第3 p型領域 503            | : 約 $4 \times 10^{16}$ ( $\text{cm}^{-3}$ ) / 約 0.70 $\mu\text{m}$ |

| n型表面領域 520             | : 約 $6 \times 10^{17}$ ( $\text{cm}^{-3}$ ) / 約 0.30 $\mu\text{m}$ |

| p <sup>+</sup> 型領域 511 | : 約 $3 \times 10^{19}$ ( $\text{cm}^{-3}$ )                        |

また、本実施例における第1 p型領域 501、第2 p型領域 502、第3 p型領域 503 のおののの空乏化電圧は、

|             |            |

|-------------|------------|

| 第1 p型領域 501 | : 約 -1.3 V |

| 第2 p型領域 502 | : 約 -1.8 V |

| 第3 p型領域 503 | : 約 -2.2 V |

となっている。

#### 【0080】

従って、例えば、電源電圧 5 V 動作において n<sup>-</sup> 型エピタキシャル領域 519 を電源電圧に接続した場合には、p<sup>+</sup> 型領域 511 及び配線 405 の電位が 3 V 以下であれば、第1 p型領域 501、第2 p型領域 502、第3 p型領域 503 は空乏化することになる。

#### 【0081】

さらに、第1 p型領域 501、第2 p型領域 502、第3 p型領域 503 の空乏化電圧が p<sup>+</sup> 型領域 511 に向かって高くなっているため、光キャリアのポテンシャルの勾配が形成されるため、本実施例のように、開口部のアスペクト比が 5 以上というような細長い受光素子の場合でも、より効率よく光キャリアを p<sup>+</sup> 型領域 511 部分に収集することができる。

#### 【0082】

尚、本実施例においては、第1 p型領域 501、第2 p型領域 502、第3 p型領域 503 はすべてイオン注入法により形成し、イオン注入時のドーズ量と加速エネルギーを変化させて図 7 に示すような不純物プロファイルを形成している。

#### 【0083】

また、本実施例においては、第1 p型領域 501、第2 p型領域 502、第3 p型領域 503 と、n<sup>-</sup> 型エピタキシャル領域 519 で形成される空乏層近傍で吸収された光のみならず、およそ n<sup>+</sup> 型埋込み層 523 の中央部までに吸収された光による光キャリアが信号として p<sup>+</sup> 型領域 511 に収集される構成となっている。また、隣接画素間の画素分離領域を積極的には設けていないため、画素間のクロストークはある程度発生するが、オートフォーカスセンサの場合にはこの画素間クロストークは許容できる。

#### 【0084】

従って、本発明の受光素子は、特に赤、及び赤外の感度、具体的には、波長 700 ~ 900 nm 程度の波長に対しての感度が要求される場合の用途に好適である。

#### 【0085】

加えて、本実施例においては、n<sup>+</sup> 型埋込み層 523 のポテンシャルバリアにより、n 型半導体基板 522 中にて発生した少数キャリアの p<sup>+</sup> 型領域 511 への混入を抑制しているため、高温時の暗電流特性も良好である。

#### 【0086】

さらに、本発明においては、低濃度のエピタキシャル成長層中にホトダイオードを形成しているため、n 型表面領域 520 の不純物濃度を  $10^{17}$  ( $\text{cm}^{-3}$ ) 程度にしても空乏化電圧が制御でき、かつ、n 型表面領域 520 を受光部全面にイオン注入法を用いて形成しても p<sup>+</sup> 型領域 511 と n 型表面領域 520 の間に逆バイアスを印加してもブレークダウン等を引き起こさないため、アライメントズレ等による不具合を生じること無く、安定した受光部容量を得ることができ、感度バラツキ等の不具合を抑制することができる。

#### 【0087】

また、受光素子部において、シリコンと酸化膜の界面部に存在する空乏層は p<sup>+</sup> 型領域 511 の周囲部のみで、かつ p<sup>+</sup> 型領域 511 を島状に形成しているため、キャリア収集効率が高く、低暗電流が実現でき、特に、カメラのオートフォーカスセンサのように比較的

長い蓄積時間で動作する応用の場合有効となる。

【0088】

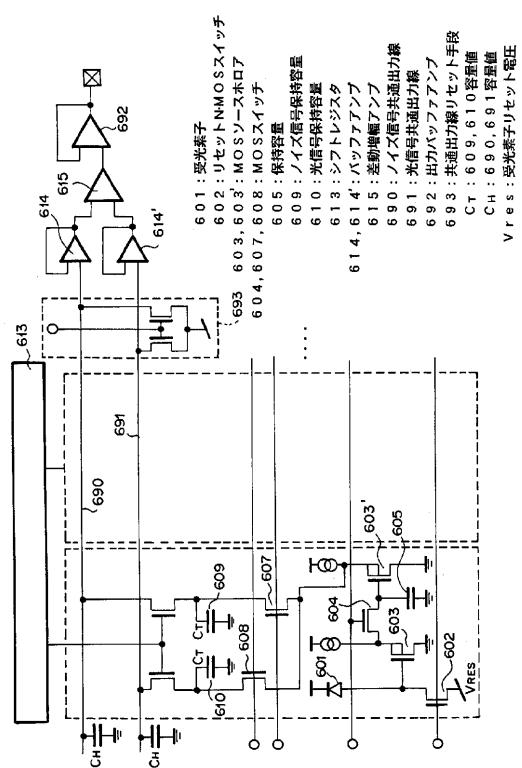

図8は本実施例における光電変換装置の1画素の等価回路図である。

【0089】

尚、図示していないが、本実施例においては40画素を一次元状に配置し、そのブロックを複数配置してオートフォーカス用センサを形成している。

【0090】

図8において、本実施例の画素部は、上記の実施例に示した受光素子601、受光素子601をリセットするためのリセットMOSスイッチ602、受光素子601の信号電荷を電圧信号に変換するための第1MOSソースホロワ603、受光素子601のリセット時のノイズ信号を蓄積期間中保持するためのMOSスイッチ604、及び保持容量605、保持容量605の信号をインピーダンス変換するための第2MOSソースホロワ603、リセット直後のノイズ信号電荷を読み出すためのMOSスイッチ607、及びノイズ信号保持容量609、光信号蓄積後の光信号電荷を読み出すためのMOSスイッチ608、及び光信号保持容量610、により構成される（同図の点線部分）。

【0091】

また、本実施例における光電変換装置には、おののの画素における、上記ノイズ信号保持容量609のノイズ信号、及び上記光信号保持容量610の光信号を、それぞれノイズ信号共通出力線690、及び光信号共通出力線691に順次読み出すためのシフトレジスタ613、ノイズ信号共通出力線690、及び光信号共通出力線691の電圧をインピーダンス変換するためのバッファアンプ614、614、上記ノイズ信号共通出力線690、及び光信号共通出力線691の電圧の差分信号を得、かつ信号を増幅するための差動増幅アンプ615、上記差動増幅アンプ615の出力をインピーダンス変換し、光電変換装置の外部に信号を出力する出力バッファアンプ692、が設けられており、さらに1画素読み出しごとにノイズ信号共通出力線690、及び光信号共通出力線691をリセットするための共通出力線リセット手段693が設けられている。

【0092】

図6に示した光電変換装置の光出力電圧は以下の式のようになる。

$$V_p = (Q_p / C_{PD}) \times G_{sf1} \times G_{sf2} \times (C_T / (C_T + C_H)) \times G_{amp} \dots$$

3

30

ここで、

$Q_p$  : 光信号電荷

$C_{PD}$  : 受光部容量

$G_{sf1}$  : 第1ソースホロアゲイン

$G_{sf2}$  : 第2ソースホロアゲイン

$C_T$  : ノイズ信号、及び光信号蓄積容量の容量値

$C_H$  : ノイズ信号及び光信号共通出力線容量の容量値

$G_{amp}$  : 差動増幅アンプゲイン

である。

【0093】

40

図6において、

$V_{1_{PD}}$  : 受光素子のリセット直後の受光素子部の電位、

$V_{2_{PD}}$  : 光電荷蓄積後の受光素子部の電位、

とすると、上記3式は次式のように表すことができる。

$$V_{2_{PD}} - V_{1_{PD}} = V_{PD} \left( Q_p / C_{PD} \right) = V_p / (G_{sf1} \times G_{sf2} \times (C_T / (C_T + C_H)) \times G_{amp}) \dots 4$$

ここで、 $V_{PD}$ は光電荷による受光素子部の電位変化である。

【0094】

従って、4式において、 $V_{1_{PD}}$ 及び $V_{2_{PD}}$ を受光素子部における空乏化領域内に設定することにより、高感度な光電変換装置を実現することができる。

50

## 【0095】

本実施例においては、上記 3、及び 4 式において、

$$G_{sf1} = G_{sf2} = 0.9$$

$$C_T / (C_T + C_H) = 0.5$$

$$G_{amp} = 20$$

光電変換装置の電源電圧：5V、

受光素子の空乏化電圧：-2.2V

光出力 ( $V_p$ ) の飽和出力：2V

受光素子のリセット電圧 ( $V_{reset}$ ) : 0.8V、

と設定した。

10

## 【0096】

従って、3、及び 4 式より、

- リセット直後の受光素子部の電位 ( $V_{1PD}$ ) : 約 0.50V

- 飽和出力時の受光素子部の電位 ( $V_{2PD}$ ) : 約 0.75V

となる。

## 【0097】

上記の電源電圧、空乏化電圧の値より、受光素子部の電位が 2.8V 以下であれば受光素子部は空乏化状態となることがわかる。

## 【0098】

ここで、本実施例においては、リセット直後の受光素子部の電位 ( $V_{1PD}$ )、及び飽和出力時の受光素子部の電位 ( $V_{2PD}$ ) は共に 2.8V 以下であるため、受光部容量が小さい範囲で使用でき、高感度化が実現できる。

20

## 【0099】

尚、本実施例における受光部容量を測定した結果、受光素子の  $p^+$  領域部の接合容量、ソースホロア MOS のゲート容量、リセットMOS のドレイン部の接合容量、その他、配線容量等の寄生容量等、すべての合計で、約 25 fF であった。

## 【0100】

また本実施例において、空乏化電圧のバラツキが -2.2V ± 2V 程度ある場合、受光素子部の空乏化領域は 0.8V ~ 4.8V となるが、本実施例における動作点は空乏化領域の最小値である 1V よりも小さいため、空乏化電圧が ± 2V 程度ばらついても高歩留まりが維持できる。

30

## 【0101】

尚、上記で、リセット直後の受光素子部の電位がリセット電圧 ( $V_{reset}$ ) より小さくなっているのは、リセットスイッチに NMOS を用いているため、リセットスイッチをオフする時に受光素子部の電位がマイナス側に振られることによるものである。

## 【0102】

以上示したオートフォーカスセンサをカメラに適用した結果、良好なオートフォーカス特性が得られた。

## 【0103】

尚、本実施例においてはオートフォーカスセンサへの適用を例に示したが、本発明はオートフォーカスセンサに限定されるものではなく、例えば視線検知センサ等のような検出センサへ応用することも可能である。

40

## 【0104】

## 【発明の効果】

以上説明したように、本発明によれば、エピタキシャル層中にホトダイオードを形成しているため、空乏層中の欠陥に起因する暗電流を抑制でき、このため、特に密着型イメージセンサや、カメラの AF センサ等に用いられる比較的大面積のホトダイオードを有する光電変換装置に好適である。

## 【0105】

また、赤色光から赤外光に対して高感度でかつ暗電流が低減可能な受光素子を得ることが

50

でき、さらに製造プロセスがばらついても高歩留まりが維持できる高性能な光電変換装置を実現することができる。

【図面の簡単な説明】

【図1】(A)：本発明の一実施形態の受光素子部の平面図

(B)：(A)の線分X-Xにおける断面構造図

(C)：線分X-Xにおけるポテンシャルプロファイル図

(D)：線分Y-Yにおけるポテンシャルプロファイル図

【図2】図1(D)の線分Y-Yにおける不純物プロファイルの具体例を示す図

【図3】電極101の電位と容量の関係を示す図

【図4】本発明の参考例における受光素子の平面構造図

10

【図5】図4のA-A部における断面構造図

【図6】本発明の実施例における受光素子の平面構造図

【図7】図6のB-B部における断面構造図

【図8】本発明の実施例における光電変換装置の1画素の等価回路図

【符号の説明】

101 電極領域

102 ホトダイオード領域

103 第1半導体領域

104 第2半導体領域

105 第3半導体領域

20

106 基板

401 開口部

406 遮光層

501 第1p型領域(第2半導体領域)

502 第2p型領域(第2半導体領域)

503 第3p型領域(第2半導体領域)

511 p<sup>+</sup>型領域(第4半導体領域(電極領域))

512 保護層

517 p型基板

519 n<sup>-</sup>型エピタキシャル領域(第1エピタキシャル領域)

30

520 n型領域(第3半導体領域)

521 p<sup>+</sup>型領域(第5半導体領域)

522 n型半導体基板

523 n<sup>+</sup>型埋め込み層(第6半導体領域)

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【 図 7 】

【 四 8 】

---

フロントページの続き

(56)参考文献 特開昭57-155784(JP,A)

特開平10-256587(JP,A)

特開平05-198835(JP,A)

特開昭61-016580(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 31/10-31/078