(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6577496号

(P6577496)

(45) 発行日 令和1年9月18日(2019.9.18)

(24) 登録日 令和1年8月30日(2019.8.30)

(51) Int.Cl.

G O 1 R 33/035 (2006.01)

F 1

G O 1 R 33/035 Z A A

請求項の数 11 (全 10 頁)

(21) 出願番号 特願2016-576033 (P2016-576033)

(86) (22) 出願日 平成27年6月25日 (2015.6.25)

(65) 公表番号 特表2017-527784 (P2017-527784A)

(43) 公表日 平成29年9月21日 (2017.9.21)

(86) 國際出願番号 PCT/CN2015/082289

(87) 國際公開番号 WO2016/008352

(87) 國際公開日 平成28年1月21日 (2016.1.21)

審査請求日 平成29年12月14日 (2017.12.14)

(31) 優先権主張番号 201410344300.1

(32) 優先日 平成26年7月18日 (2014.7.18)

(33) 優先権主張国・地域又は機関

中国(CN)

(73) 特許権者 517003716

シャンハイ インスティテュート オブ

マイクロシステム アンド インフォメー

ション テクノロジー, チャイニーズ ア

カデミー オブ サイエンシーズ

中華人民共和国 200050 上海 長

寧区 チャンニン・ロード ナンバー86

5

(73) 特許権者 503441780

フォルシュングスツェントルム ユーリッ

ヒ ゲーエムベーハー

ドイツ国 ユーリッヒ 52428 レオ

ーブラントーシュトラーセ

(74) 代理人 100082072

弁理士 清原 義博

最終頁に続く

(54) 【発明の名称】シングルオペアンプを用いる S Q U I D 磁気センサ

## (57) 【特許請求の範囲】

## 【請求項 1】

S Q U I D デバイスと第1のフィードバック抵抗とを含み、S Q U I D デバイスは、S Q U I D とフィードバックコイルとを含み、オフセット電流源によって供給されるオフセット電流は、S Q U I D に付与され、S Q U I D の他端は、グラウンドに接続される、シングルオペアンプを用いる S Q U I D 磁気センサであって、

回路にはオペアンプが直列に接続され、S Q U I D 電圧信号は、当該オペアンプの一方の入力端子に入力され、当該オペアンプの他方の入力端子には、オフセット電圧が入力され、当該オペアンプの出力端子は、第1のフィードバック抵抗の一端に接続され、当該フィードバック抵抗の他端は、フィードバックコイルに接続され、フィードバックコイルと S Q U I D とが相互誘導結合することによって、当該オペアンプの出力電圧は、フィードバック抵抗を駆動して電流を生じさせ、フィードバックコイルと S Q U I D の相互誘導によってフィードバック磁束を生じさせることにより、磁束ロックループを構成し、リセットスイッチの一端は、オペアンプの負入力端子に接続され、他端は、オペアンプの出力端子に接続されることを特徴とする S Q U I D 磁気センサ。

## 【請求項 2】

前記 S Q U I D 電圧信号は、オペアンプの正入力端子に入力され、オフセット電圧は、オペアンプの負入力端子に入力されることを特徴とする請求項 1 に記載の S Q U I D 磁気センサ。

## 【請求項 3】

10

20

S Q U I D 電圧信号は、オペアンプの負入力端子に入力され、オフセット電圧は、オペアンプの正入力端子に入力されることを特徴とする請求項 1 に記載の S Q U I D 磁気センサ。

#### 【請求項 4】

前記オフセット電流は、オフセット調整回路に供給され、当該オフセット調整回路は、三端子の変調抵抗によって構成される第 1 の変調電位器を含み、当該変調電位器の第 1 及び第 2 の端子は、一定抵抗値の抵抗であり、当該電位器の第 3 の端子は、変調抵抗タップであり、当該変調電位器の第 1 及び第 2 の端子は、それぞれ正電圧電源及び負電圧電源に接続され、当該変調電位器の第 3 の端子出力は、第 1 の分圧抵抗に入力され、当該分圧抵抗の他端は、S Q U I D に直列に接続されることを特徴とする請求項 1 ~ 3 のいずれか 1 つに記載の S Q U I D 磁気センサ。 10

#### 【請求項 5】

前記正電圧電源によって供給される電圧範囲は、+ 5 V ~ + 15 V の間であり、負電圧電源によって供給される電圧範囲は、- 5 V ~ - 15 V の間であり、第 1 の変調電位器の両端の間の抵抗値は、10 k ~ 100 k の間であることを特徴とする請求項 4 に記載の S Q U I D 磁気センサ。

#### 【請求項 6】

前記オフセット電圧は、オフセット電圧調整回路によって供給され、当該オフセット電圧調整回路は、三端子の変調抵抗によって構成される第 2 の変調電位器を含み、当該変調電位器の第 1 及び第 2 の端子は、固定端であり、それぞれ正電圧電源及び負電圧電源に接続され、当該第 2 の変調電位器の第 3 の端子は、タップ端子であり、当該タップ端子は、制限抵抗の一端に接続され、当該制限抵抗の他端は、第 2 の分圧抵抗に直列に接続され、当該第 2 の分圧抵抗は、グラウンドに接続されることにより、当該制限抵抗と第 2 の分圧抵抗の接続端に生じる抵抗分圧を引き出し、オフセット電圧信号を構成することを特徴とする請求項 4 に記載の S Q U I D 磁気センサ。 20

#### 【請求項 7】

前記オフセット電圧の調整範囲は、± 100  $\mu$  V であり、グラウンドに接続される一端の第 2 の分圧抵抗値は、1 ~ 10 の間であり、直列に接続される制限抵抗の抵抗値範囲は、10 k ~ 100 k の間であることを特徴とする請求項 6 に記載の S Q U I D 磁気センサ。 30

#### 【請求項 8】

前記オペアンプは、バイポーラによって電力供給される低ノイズオペアンプであることを特徴とする請求項 1 に記載の S Q U I D 磁気センサ。

#### 【請求項 9】

前記オペアンプの電圧ノイズは、1 nV / Hz であり、開ループゲインは、> 120 dB であり、帯域幅ゲイン積は、10 MHz より大きいこと特徴とする請求項 8 に記載の S Q U I D 磁気センサ。

#### 【請求項 10】

第 2 のフィードバック抵抗と S P D T スイッチとを含み、当該 S P D T スイッチは、固定接続端、第 1 の接点接続端及び第 2 の接点接続端を有し、前記固定接続端は、オペアンプの出力端子に接続され、第 1 の接点接続端は、第 2 のフィードバック抵抗の一端に接続され、当該第 2 のフィードバック抵抗の他端は、オペアンプの負入力端子に接続され、第 2 の接点接続端は、第 1 のフィードバック抵抗に接続されることを特徴とする請求項 1 に記載の S Q U I D 磁気センサ。 40

#### 【請求項 11】

前記第 1 のフィードバック抵抗又は前記第 2 のフィードバック抵抗の抵抗値は、いずれも 100 ~ 10 k の間であることを特徴とする請求項 10 に記載の S Q U I D 磁気センサ。

#### 【発明の詳細な説明】

#### 【技術分野】

50

## 【0001】

本発明は、シングルオペアンプを用いるSQUID磁気センサに関し、より詳しくは、SQUID読み出し回路に関し、回路技術領域に属する。

## 【背景技術】

## 【0002】

超伝導量子干渉素子(Superconducting Quantum Interference Device、以下、SQUIDと略称する)を用いて構成される磁気センサは、現在知られている最も感度が高い磁気センサである。生物磁場、地球磁場異常、低磁場NMR等の微弱磁場検出応用領域によく用いられており、その磁場検出感度は、 $fT(10^{-15}$  テスラ)レベルに達している。それは、微弱磁場検出及び研究における重要な磁気センサである。10

## 【0003】

直流SQUID(以下、dc SQUIDと称する)は、2つの超電導ジョセフソン接合の並列によって形成される超電導ループである。ジョセフソン接合の両端には、配線が引き出されることにより、両端子素子が形成される。SQUID両端には、一定のオフセット電流が付与されると、超電導量子化効果とジョセフソン効果に基づいて、SQUID両端に発生した電圧が超電導ループ誘導外磁束の大きさにしたがって変化する。SQUID出力電圧は、検出磁束とは、非線形関数となるから、SQUID両端電圧を計測することによって、直接に検出される磁束の大きさが得られない。したがって、実際適用されるSQUID磁気センサは、SQUIDデバイスとアンプ回路により構成される磁束ロックループ(Flux-Locked Loop、以下FLLと称する)によって実現される。当該磁束ロックループは、SQUID読み出し回路と称される。20

## 【0004】

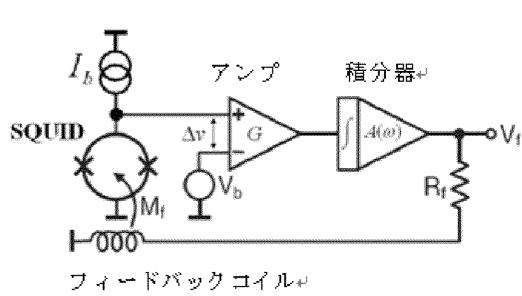

文献[D. Drung and M. Muck, The SQUID Handbook, vol. I, J. Clarke and A. I. Braginski, Ed. Weinheim: Wiley - VCH, pp. 128 - 155, 2006.]には、図1に示すように、典型的なSQUID磁束ロックループが開示されている。まず、SQUIDに一定のオフセット電流 $I_b$ を付与することにより、最大の磁束電圧伝送率が得られる。SQUID電圧信号をプリアンプに入力させて増幅する。同時にオフセット電圧 $V_b$ を調整することにより、SQUIDは、最大磁束電圧伝送率を有する際に出力される電圧の直流量がゼロとなる。このとき、SQUID現状のオフセット電流 $I_b$ 、オフセット電圧 $V_b$ 及び付与される磁束 $\phi_a$ の値状態を動作箇所と称する。プリアンプの出力を積分器に入力して積分し、積分器の出力は、フィードバック抵抗を駆動してフィードバックコイルにフィードバック電流を流动させ、フィードバックコイルとSQUIDの相互誘導によって発生されるフィードバック磁束は、SQUIDに結合される。30

## 【0005】

磁束ロックループの動作原理は以下の通りである。磁束ロックループは、SQUID動作箇所の安定を保持する際に、検出される磁束には変化量 $\phi$ が発生し、SQUID端に作動箇所からずれる電圧変化 $v$ が発生し、プリアンプを経由した後に、積分器に入力して積分し、積分器の出力電圧を調整する。フィードバック抵抗、フィードコイルによってフィードバック磁束を調整して前記外部入力の磁束変換量を打ち消して、SQUIDが動作箇所で入力する積分器の電圧をゼロとし、積分器は、積分を停止し、ループは安定を回復する。動作箇所の安定状態を読み出し回路ロックと称する。ロック状態において、磁束ロックループが出力する電圧 $V_f$ は、SQUIDが誘導する外磁束変化量と正比例となり、[D. Drung "High-Tc and low-Tc dc SQUID electronics" Supercond. Sci. Technol. 16 1320 - 1336 (2003).]、即ち、 $V_f = \cdot R_f / M_f$ 、 $\cdot$ は、SQUIDが検出する磁束変化量であり、 $R_f$ は、フィードバック抵抗であり、 $M_f$ は、フィードバックコイルとSQUIDの相互誘導である。40

## 【0006】

回路実現にあたって、従来 S Q U I D 磁束ロックループは、通常プリアンプを使用し、S Q U I D 微弱電圧信号を低ノイズ増幅し、増幅される信号を積分器に入力して積分フィードバックを行う。したがって、従来の S Q U I D 磁束ロックループは、少なくとも 1 つのプリアンプ回路と 1 つの積分器のカスケード回路をフィードバック抵抗、フィードバックコイルに再接続させて構成される。実際の適用において、用いられる積分器の S Q U I D 磁束ロックループは、以下の問題を有する。

1 ) 帯域幅の規制：積分器を用いる読み出し回路は、少なくとも二次以上のアンプ回路を使用し、ループ信号の遅延を増大させることにより、高周波数信号の伝送に位相シフトを生じさせ、ループ発振を作り出し [ D . Drung and M . Muck , The S Q U I D Handbook , vol . I , J . Clarke and A . I . Braginski , Ed . Weinheim : Wiley - V C H , pp . 128 - 155 , 2006 . ] 。したがって、積分容量を増大する必要があり、発振を打ち消し、磁束ロックループの安定動作を実現し、積分容量の増大は、磁束ロックループの帯域幅を低減する。

2 ) スルーレート規制：積分回路の出力は、入力信号が時間を積分する結果であり、検出信号が急激に変化し、積分器が迅速に応答できなくなり、これによって、センサ電圧出力のスルーレートが規制される。高いスルーレート磁場検出の要求を満足し難くなる。

3 ) 少なくとも 2 つ以上のオペアンプ及び外周回路を使用し、回路が複雑で、電力の消費が大きい。

#### 【先行技術文献】

20

#### 【非特許文献】

#### 【0007】

【非特許文献 1】 D . Drung and M . Muck , The S Q U I D Handbook , vol . I , J . Clarke and A . I . Braginski , Ed . Weinheim : Wiley - V C H , pp . 128 - 155 , 2006 .

#### 【0008】

【非特許文献 2】 D . Drung " High - Tc and low - Tc dc S Q U I D electronics " Supercond . Sci . Technol . 16 1320 - 1336 ( 2003 ) .

#### 【発明の概要】

30

#### 【発明が解決しようとする課題】

#### 【0009】

S Q U I D デバイスの信号応答は、直流 ( 0 H z ) から G H z へ変化可能であり、高速 S Q U I D チップは、マイクロ電子技術によって製造され、小さい体積、集積化の独特なメリットを有し、マルチチャネル、高分解率検出システム、例えば S Q U I D の 64 チャネル M C G デバイス、200 超チャネルの M E G デバイスによく用いられている。マルチチャネルシステムは、S Q U I D 磁気センサの小型化に対し、より高い要求を求めていている。したがって、簡易化 S Q U I D 読み出し回路設計は、S Q U I D マルチチャネル適用に重要な意義と実用価値を有する。本発明は、これらの問題を解決するためになされたものである。

40

#### 【0010】

本発明は、シングルオペアンプを用いる S Q U I D 磁気センサを提供することを目的とする。本発明は、マルチチャネル高度集積の S Q U I D システムに対し、より簡易化の読み出し回路を設計し、S Q U I D 磁気センサを構築する。

#### 【課題を解決するための手段】

#### 【0011】

S Q U I D は、半導体アンプよりも高い応答速度を有し、アンプとの組み合わせによって安定な負フィードバック回路が実現される。したがって、本発明の思想は、開ループで低ノイズのオペアンプを 1 つのみ用いることにより、S Q U I D 電圧信号を増幅し、シングルオペアンプの開ループ出力によりフィードバック抵抗及びフィードバックコイルを直接

50

駆動することにより、従来磁束ロックループにおけるプリアンプと積分器とを代替え、簡易な S Q U I D 磁束ロックループの構築が実現される。シングルオペアンプを用いる S Q U I D 磁束ロックループは、以下の配線方式を含む。

#### 【 0 0 1 2 】

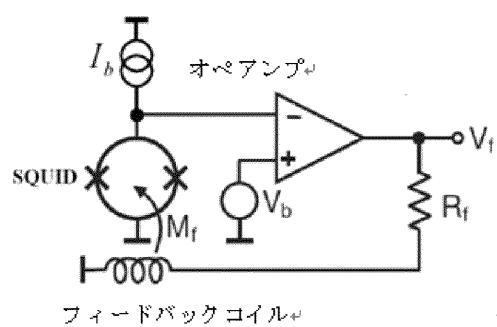

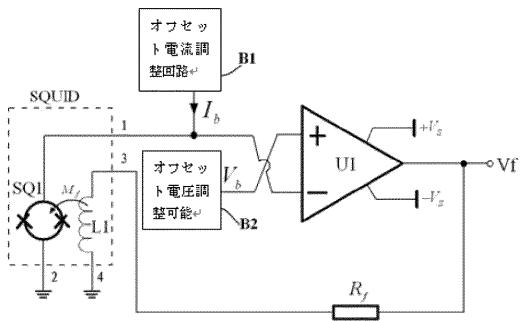

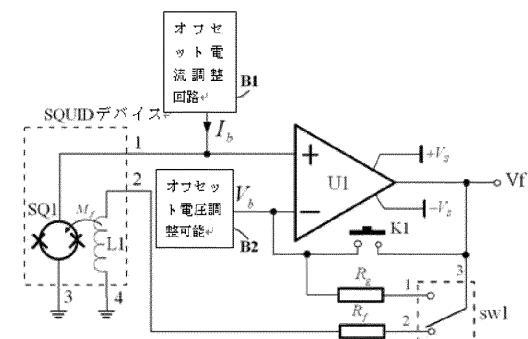

1 ) 正端子配線方式は、図 2 に示すように、オフセット電流  $I_b$  が S Q U I D に付与され、S Q U I D 電圧信号がオペアンプの正入力端子に入力される。オフセット電圧  $V_b$  がオペアンプの負入力端子に入力される。オペアンプの出力端子がフィードバック抵抗  $R_f$  の一端に接続され、フィードバック抵抗の他端がフィードバックコイルに接続され、フィードバックコイルと S Q U I D とが相互誘導によって結合され、オペアンプが電圧を出力し、フィードバック抵抗  $R_f$  を駆動することにより電流を発生させ、フィードバックコイルと S Q U I D との相互誘導  $M_f$  によって、フィードバック磁束を発生させ、磁束ロックループが構成される。

10

#### 【 0 0 1 3 】

前記正端子入力配線方式は、実施形態 1 、 3 および 5 ( 即ち、 A 、 B 及び C ) のうちの一つである ( 詳しくは、詳細な実施形態を参照 ) 。

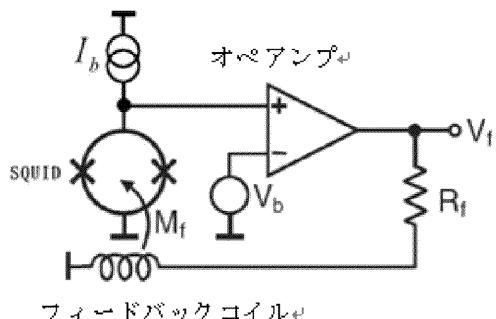

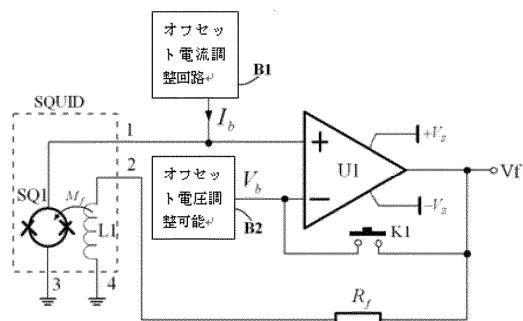

2 ) 負端子配線方式は、図 3 に示すように、オフセット電流  $I_b$  が S Q U I D に付与され、S Q U I D 電圧信号がオペアンプの負入力端子に入力され、オフセット電圧  $V_b$  がオペアンプの正入力端子に入力される。オペアンプの出力端子がフィードバック抵抗  $R_f$  の一端に接続され、フィードバック抵抗の他端がフィードバックコイルに接続され、フィードバックコイルと S Q U I D とが相互誘導によって結合され、オペアンプが電圧を出力し、フィードバック抵抗  $R_f$  を駆動することにより電流を発生させ、フィードバックコイルと S Q U I D との相互誘導  $M_f$  によって、フィードバック磁束を発生させ、磁束ロックループが構成される。

20

前記負端子入力配線方式は、実施形態 2 、 4 および 6 ( 即ち、 D 、 E 及び F ) のうちの一つである ( 詳しくは、詳細な実施形態を参照 ) 。

#### 【 発明の効果 】

#### 【 0 0 1 4 】

本発明は、オペアンプを 1 つのみ用いることにより S Q U I D 磁束ロックループを実現し、回路が簡単になる。従来回路における積分器の使用を回避し、ループ遅延を減少し、より広い帯域幅の磁束ロックループを実現する。オペアンプは、直接に出力してフィードバック抵抗とフィードバックコイルを駆動することにより、積分容量の影響を回避し、磁束ロックループがより高いスルーレートを実現できる。また、前記回路は、シングルオペアンプと数少ない外周回路によって構成されることで、回路の体積が小さく、電力消費が低く、マルチチャネル S Q U I D センサ集積の全体の体積と電力消費を大幅に減少し、 S Q U I D マルチチャネルの適用には、重要な意義がある。

30

#### 【 図面の簡単な説明 】

#### 【 0 0 1 5 】

【 図 1 】 典型的な直読式読み出し回路原理図である。

【 図 2 】 S Q U I D 正端子入力のシングルオペアンプ磁束ロックループ原理図である。

【 図 3 】 S Q U I D 負端子入力のシングルオペアンプ磁束ロックループ原理図である。

40

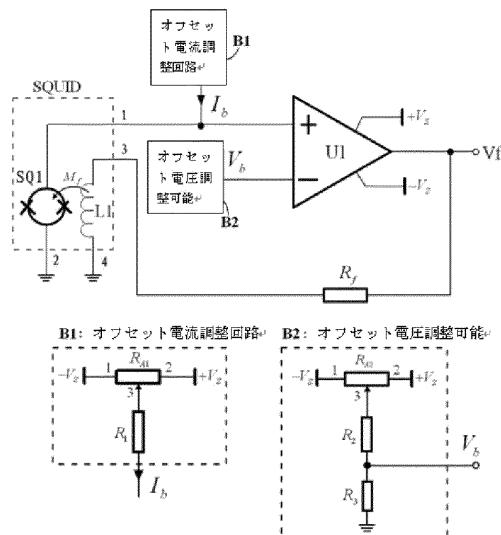

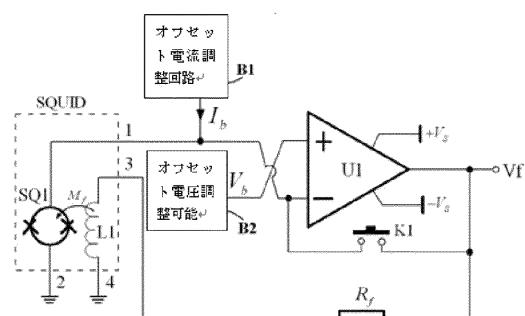

【 図 4 】 シングルオペアンプ S Q U I D 磁束ロックループの詳細な実施形態 1 であり、図 1 における B 1 、 B 2 はそれぞれオフセット電流或いはオフセット電圧調整回路である。

【 図 5 】 シングルオペアンプ S Q U I D 磁束ロックループの詳細な実施形態 2 である。

【 図 6 】 シングルオペアンプ S Q U I D 磁束ロックループの詳細な実施形態 3 である。

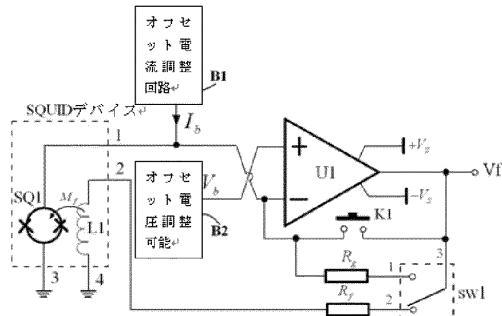

【 図 7 】 シングルオペアンプ S Q U I D 磁束ロックループの詳細な実施形態 4 である。

【 図 8 】 シングルオペアンプ S Q U I D 磁束ロックループの詳細な実施形態 5 である。

【 図 9 】 シングルオペアンプ S Q U I D 磁束ロックループの詳細な実施形態 6 である。

#### 【 発明を実施するための形態 】

#### 【 0 0 1 6 】

以下の六つの詳細な実施形態を有する。

1 ) 詳細な実施形態 1 は、図 4 に示すように、即ち、正端子入力配線方式 A :

1 . 電力供給電源 + V<sub>s</sub> と - V<sub>s</sub> : 回路がバイポーラ電源によって電力供給され、即ち正電源端子 + V<sub>s</sub> に正電圧電源が接続され、負電源端子 - V<sub>s</sub> に負電圧電源が接続される。正電源 + V<sub>s</sub> の電力供給範囲は、+ 5 V ~ + 15 V であり、対応する負電源 - V<sub>s</sub> の電力供給範囲は、- 5 V ~ - 15 V である。

#### 【 0 0 1 7 】

2 . S Q U I D オフセット電流調整回路 B 1 : その機能は、S Q U I D に S Q U I D に向けて流れる 2 つのジョセフソン接合のオフセット電流が付与され、電流の大きさを調整可能である。S Q U I D に付与されるオフセット電流の大きさを調整することにより、S Q U I D に最適の磁束電圧変換特性が得られる。調整可能なオフセット電流回路の詳細な実施例は、図 3 における B 1 モジュールに示すように、調整可能な電位器 R<sub>A1</sub> は、3 端子の調整可能な抵抗であり、電位器の 1 と 2 の両端子は、固定抵抗値の抵抗であり、その抵抗値は、10 k ~ 100 k であることが最も好ましい。電位器の 3 端子は、調整可能な抵抗タップである。電位器 R<sub>A1</sub> の 1 と 2 の両端子は、それぞれ正電源 + V<sub>s</sub> と負電源 - V<sub>s</sub> に接続される。電位器 R<sub>A1</sub> の 3 端子は、電位器抵抗分圧を出力し、電位器タップ位置を調整することにより調整可能な電圧を発生させる。当該電圧出力は抵抗 R<sub>1</sub> に入力され、抵抗 R<sub>1</sub> の他端は、S Q U I D に直列に接続される。抵抗 R<sub>1</sub> の値は、50 k ~ 200 k である。調整可能な電位器 R<sub>A1</sub> を調整することにより、± 100 μA 範囲の直流オフセット電流を発生させる。

#### 【 0 0 1 8 】

3 . S Q U I D オフセット電圧調整回路 B 2 : その機能は、調整可能な直流電圧が発生され、オペアンプの負入力端子に入力されることである。当該電圧と S Q U I D 動作箇所の直流電圧とが同じであるように調整することにより、動作箇所のゼロ調整を実現する。調整可能な電圧回路の詳細な実施例は、図 3 における B 2 モジュールに示すように、調整可能な電位器 R<sub>A2</sub> は、3 端子の調整可能な抵抗であり、電位器の 1 と 2 の両端子は、固定端子であり、その抵抗値は、10 k ~ 100 k であることが最も好ましい。電位器 R<sub>A2</sub> の 1 と 2 の端子は、それぞれ正電源 + V<sub>s</sub> と負電源 - V<sub>s</sub> に接続され、調整可能な抵抗は、タップ端を引き出し、3 端子は、抵抗分圧を出力し、当該電圧は、抵抗 R<sub>3</sub> の一端に入力され、抵抗 R<sub>3</sub> の他端は、R<sub>2</sub> に直列に接続され、R<sub>2</sub> の他端は、グラウンドに接続される。R<sub>2</sub> と R<sub>3</sub> の接続端は、発生した抵抗分圧をオフセット電圧信号 V<sub>b</sub> として引き出す。当該オフセット電圧の調整範囲は、± 100 μV である。オペアンプの入力端子に引き入れられる熱ノイズを低減するように、抵抗 R<sub>3</sub> の値は、通常 1 ~ 10 である。抵抗 R<sub>2</sub> の値範囲は、10 k ~ 100 k である。

#### 【 0 0 1 9 】

4 . S Q U I D デバイス S Q 1 : S Q 1 は、(4 . 2 K の液体ヘリウム温度で動作する) 低温直流 S Q U I D 、或いは (77 K の液体窒素温度で動作する) 高温直流 S Q U I D を使用しており、両端子のデバイスでもある。S Q 1 の一端は、オペアンプの正入力端子に接続されるとともに、オフセット電流回路 B 1 の電流出力端子と接続される。S Q 1 の他端は、グラウンドに接続される。

#### 【 0 0 2 0 】

5 . フィードバックコイル L 1 : フィードバックコイル L 1 は、S Q U I D と相互誘導結合を有するコイルであり、その相互誘導の値は、M<sub>f</sub> である。フィードバックコイルは、フィードバック回路で発生される電流をフィードバック磁束に変換して S Q U I D に結合させて打ち消す磁束を形成する。フィードバックコイル L 1 の一端は、フィードバック抵抗 R<sub>f</sub> に接続され、その他端は、グラウンドに接続される。

#### 【 0 0 2 1 】

6 . オペアンプ U 1 : オペアンプ U 1 は、バイポーラによって電力供給される低ノイズオペアンプを用いて、正入力端子と負入力端子の 2 つの電圧信号入力端子を有し、1 つの電圧信号は、出力端子を増幅させている。図のオペアンプの正入力端子には、S Q U I D 電圧出力が入力され、オペアンプの負入力端子には、オフセット電圧出力が入力され、ア

10

20

30

40

50

ンプ出力は、磁束ロックループの出力であり、センサ全体の出力である。同時にフィードバック抵抗  $R_f$  に入力される。SQUID電圧信号の低ノイズアンプと磁束ロックループ高線形度の出力を実現するために、本発明のオペアンプは、低入力電圧ノイズと高い帯域幅、高い開ループゲイン特性のデバイスであることが好ましく、アンプ電圧ノイズは、1 nV / Hz であり、開ループゲイン > 120 dB、帯域幅ゲイン積は、10 MHz より大きい。通常の低ノイズオペアンプは、米国ADI社のAD797或いはリニア・テクノロジー(Linear Technology)社のLT1028である

#### 【0022】

7. フィードバック抵抗  $R_f$  : フィードバック抵抗  $R_f$  の一端には、オペアンプ U1 の出力が入力され、他端は、フィードバックコイル L1 に接続される。フィードバック抵抗  $R_f$  は、アンプが出力した電圧をフィードバック電流に変換してフィードバックコイルに入力することにより、フィードバック磁束を発生させる。 $R_f$  の値は、100 ~ 10 k である。

#### 【0023】

2) 詳細な実施形態 2 は、図 5 に示すように、即ち、正端子入力配線方式 D :

実施形態 1 のうちの SQUID 電圧信号は、オペアンプ U1 の負入力端子に入力され、オフセット電圧信号は、オペアンプの正入力端子に入力され、その他の配線は、実施形態 1 と同じである。

#### 【0024】

3) 詳細な実施形態 3 は、図 6 に示すように、即ち、正端子入力配線方式 B :

磁束ロックループは、外部干渉を受けてアンロックを生じさせ、出力の漏洩をもたらす。リセットスイッチによって磁束ロックループをロックに回復させることができる。本実施形態 3 は、実施形態 1 を基にして、リセットスイッチ K1 を増加することによりリセット機能を実現する。K1 の一端は、オペアンプ U1 の負入力端子に接続され、K1 の他端は、オペアンプ U1 の出力端子に接続される。リセットスイッチをオンにすると、オペアンプ U1 の出力端子と負入力端子とが等電位となる。オペアンプが開ループ高ゲインアンプから単位ゲインのアンプになり、出力が迅速に減少し、回路はリセットを実現する。リセットスイッチをオフにすると、回路が再びロックされる。

#### 【0025】

4) 詳細な実施形態 4 は、図 7 に示すように、即ち、正端子入力配線方式 E :

実施形態 3 のうちの SQUID 電圧信号は、オペアンプ U1 の負入力端子に入力され、オフセット電圧信号は、オペアンプの正入力端子に入力され、その他の配線は、実施形態 3 と同じである。

#### 【0026】

5) 詳細な実施形態 5 は、図 8 に示すように、即ち、正端子入力配線方式 C :

SQUID 磁気センサは、電力使用状態において、オフセット電流とオフセット電圧を調整し直すことにより、SQUID に最適な動作箇所を取得させる必要がある。本実施形態 5 は、実施形態 3 を基にして、フィードバック抵抗  $R_g$  と SPDT スイッチ SW1 を増加することにより磁束ロックループに動作箇所調整機能を具備させる。SPDT スイッチ SW1 は、配線端子を三つ有し、端子 3 を SP 固定配線端子と定義し、端子 1 を第 1 接点配線端子と定義し、端子 2 を第 2 接点配線端子と定義する。SPDT スイッチ SW1 の SP 固定配線端子は、オペアンプ U1 の出力端子に接続される。SW1 の端子 1 は、抵抗  $R_g$  の一端に接続され、抵抗  $R_g$  の他端は、オペアンプ U1 の負入力端子と接続され、SW1 の端子 2 は、フィードバック抵抗  $R_f$  に接続され、フィードバック抵抗  $R_f$  の他端は、フィードバックコイル L1 に接続される。SW1 の SP スイッチは、第 2 接点とオフにして、第 1 接点とオンにして、抵抗  $R_g$  は、オペアンプ U1 の出力端子に接続される。このとき、磁束ロックループが稼働し、オペアンプ U1 が比率増幅モードで動作することにより、SQUID 電圧信号の比率増幅を実現する。オペアンプの出力電圧  $V_f$  を検出し、磁束電圧伝送特性曲線を観測し、SQUID 動作箇所を補助し、オフセット電流とオフセット電圧の調整を行う。最適のオフセット電圧、オフセット電流の調整を完了させた後に、

10

20

30

40

50

S W 1 の S P スイッチは、第 1 接点とオフにして、第 2 接点とオンにして、オペアンプ U 1 の出力端子は、フィードバック抵抗  $R_f$  に接続され、このとき、磁束ロックループは、閉ループでロック出力を実現する。

【 0 0 2 7 】

6 ) 詳細な実施形態 6 は、図 9 に示すように、即ち、正端子入力配線方式 F :

実施形態 5 のうちの S Q U I D 電圧信号は、オペアンプ U 1 の負入力端子に入力され、オフセット電圧信号は、オペアンプの正入力端子に入力され、その他の配線は、実施形態 5 と同じである。

【 図 1 】

【 図 3 】

【 図 2 】

【図4】

【図5】

【図6】

【図7】

【図9】

【図8】

---

フロントページの続き

(72)発明者 ワン , ヨンリアン

中華人民共和国 200050 上海 長寧区 チャンニン・ロード ナンバー865

(72)発明者 チャン , イー

ドイツ ユーリッヒ 52425

(72)発明者 チャン , カイ

中華人民共和国 200050 上海 長寧区 チャンニン・ロード ナンバー865

(72)発明者 クラウス , ハンス - ヨアヒム

ドイツ ユーリッヒ 52425

(72)発明者 シュ , シャオフェン

中華人民共和国 200050 上海 長寧区 チャンニン・ロード ナンバー865

(72)発明者 チウ , ヤン

中華人民共和国 200050 上海 長寧区 チャンニン・ロード ナンバー865

審査官 永井 皓喜

(56)参考文献 米国特許出願公開第2011/0285393(US, A1)

特表2005-501264(JP, A)

特開昭60-41311(JP, A)

特開2000-321343(JP, A)

特開2007-124494(JP, A)

ANALOG DEVICES, INC., Ultralow Distortion,Ultralow Noise Op Amp AD797 Data Sheet , AD797 Data Sheet , 米国 , ANALOG DEVICES, INC. , 2015年

(58)調査した分野(Int.Cl. , DB名)

G01R 33/035

H01L 27/18