(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6517845号

(P6517845)

(45) 発行日 令和1年5月22日(2019.5.22)

(24) 登録日 平成31年4月26日(2019.4.26)

(51) Int.Cl.

F 1

|             |           |             |   |

|-------------|-----------|-------------|---|

| H01L 21/677 | (2006.01) | H01L 21/68  | A |

| G05B 19/418 | (2006.01) | G05B 19/418 | Z |

| H01L 21/02  | (2006.01) | H01L 21/02  | Z |

請求項の数 9 (全 20 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2017-5729 (P2017-5729)      |

| (22) 出願日  | 平成29年1月17日 (2017.1.17)        |

| (65) 公開番号 | 特開2018-117000 (P2018-117000A) |

| (43) 公開日  | 平成30年7月26日 (2018.7.26)        |

| 審査請求日     | 平成30年10月31日 (2018.10.31)      |

早期審査対象出願

|           |                                                  |

|-----------|--------------------------------------------------|

| (73) 特許権者 | 000000239<br>株式会社荏原製作所<br>東京都大田区羽田旭町11番1号        |

| (74) 代理人  | 100140109<br>弁理士 小野 新次郎                          |

| (74) 代理人  | 100106208<br>弁理士 宮前 徹                            |

| (74) 代理人  | 100146710<br>弁理士 鐘ヶ江 幸男                          |

| (74) 代理人  | 100186613<br>弁理士 渡邊 誠                            |

| (72) 発明者  | 野々部 宏司<br>東京都千代田区富士見2丁目17番1号<br>学校法人法政大学デザイン工学部内 |

最終頁に続く

(54) 【発明の名称】スケジューラ、基板処理装置、及び基板搬送方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板の処理を行う複数の基板処理部と、前記基板を搬送する搬送部と、前記搬送部と前記基板処理部を制御する制御部を備えた基板処理装置の前記制御部に内蔵され、基板搬送スケジュールを計算するスケジューラであって、

前記基板処理装置の処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、グラフ・ネットワークを作成し、各ノードへの最長経路長の計算を行うモデル化部と、

前記最長経路長に基づいて前記基板搬送スケジュールを計算する計算部と、を有し、

前記基板処理部は、基板ホルダに保持された前記基板にめっき処理するめっき処理部を有し、

前記搬送部は、前記基板を収容する基板収納容器と前記基板を前記基板ホルダに対して着脱するフィキシングステーションとの間で基板を搬送する前段搬送部と、前記フィキシングステーションと前記めっき処理部との間で基板を搬送する後段搬送部とを有し、

前記基板処理装置は、前記前段搬送部を含む装置前段部と、前記めっき処理部及び前記後段搬送部を含む装置後段部とを有し、

前記モデル化部は、前記装置前段部及び前記装置後段部の処理条件、処理時間、及び制約条件をそれぞれモデル化し、前記装置前段部における前段側グラフ・ネットワークと、前記装置後段部における後段側グラフ・ネットワークとを別々に作成し、

前記スケジューラは、さらに、前記前段側グラフ・ネットワークと、前記後段側グラフ

・ネットワークとを結合する処理を行い、各ノードへの最長経路長の計算を行う結合部を有し、

前記計算部は、前記結合部で算出された前記各ノードへの最長経路長に基づいて、前記基板搬送スケジュールを計算する、スケジューラ。

**【請求項 2】**

請求項1に記載されたスケジューラにおいて、

指定された前記基板の処理枚数を任意の枚数のミニバッチに分割し、

前記モデル化部は、前記ミニバッチ分の前記前段側グラフ・ネットワークと、前記ミニバッチ分の前記後段側グラフ・ネットワークを作成し、

前記結合部は、前記ミニバッチ分の前記前段側グラフ・ネットワークと、前記ミニバッチ分の前記後段側グラフ・ネットワークとを結合し、10

指定された処理枚数分まで前記ミニバッチ分の前記前段側グラフ・ネットワークと前記ミニバッチ分の前記後段側グラフ・ネットワークとの作成及び結合を繰り返す、スケジューラ。

**【請求項 3】**

請求項1又は2に記載されたスケジューラにおいて、

前記基板処理装置が非定常状態に移行したか否かを検知する検知部を有し、

前記モデル化部は、前記基板処理装置が非定常状態に移行したことを前記検知部が検知したとき、前記非定常状態における前記基板処理装置の処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、グラフ・ネットワークを作成し、各ノードへの最長経路長の計算を行い、20

前記計算部は、前記非定常状態における前記各ノードへの最長経路長に基づいて、前記基板搬送スケジュールを計算するように構成される、スケジューラ。

**【請求項 4】**

請求項3に記載されたスケジューラにおいて、

前記非定常状態は、前記基板処理装置の故障時の状態、基板ホルダのメンテナンス時の状態、又はアノードホルダのメンテナンス時の状態を含む、スケジューラ。

**【請求項 5】**

請求項1から4のいずれか一項に記載されたスケジューラを内蔵する前記制御部を備えた、基板処理装置であって、30

前記制御部は、計算された前記基板搬送スケジュールに基づいて前記搬送部を制御するように構成される、基板処理装置。

**【請求項 6】**

基板の処理を行う複数の基板処理部と、前記基板を搬送する搬送部と、前記搬送部と前記基板処理部を制御する制御部を備えた基板処理装置を用いた基板搬送方法であって、

前記基板処理装置の処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、グラフ・ネットワークを作成し、各ノードへの最長経路長の計算を行うモデル化工程と、

前記最長経路長に基づいて基板搬送スケジュールを計算する計算工程と、

前記基板搬送スケジュールに基づいて前記基板を搬送する工程と、を有し、40

前記基板処理部は、基板ホルダに保持された前記基板にめっき処理するめっき処理部を有し、

前記搬送部は、前記基板を収容する基板収納容器と前記基板を前記基板ホルダに対して着脱するフィキシングステーションとの間で基板を搬送する前段搬送部と、前記フィキシングステーションと前記めっき処理部との間で基板を搬送する後段搬送部とを有し、

前記基板処理装置は、前記前段搬送部を含む装置前段部と、前記めっき処理部及び前記後段搬送部を含む装置後段部とを有し、

前記モデル化工程は、前記装置前段部及び前記装置後段部の処理条件、処理時間、及び制約条件をそれぞれモデル化し、前記装置前段部における前段側グラフ・ネットワークと、前記装置後段部における後段側グラフ・ネットワークとを別々に作成し、50

前記基板搬送方法は、さらに、前記前段側グラフ・ネットワークと、前記後段側グラフ・ネットワークとを結合する処理を行い、各ノードへの最長経路長の計算を行う結合工程を有し、

前記計算工程は、前記結合工程で算出された前記最長経路長に基づいて基板搬送スケジュールを計算する、基板搬送方法。

#### 【請求項 7】

請求項6に記載された基板搬送方法において、

指定された前記基板の処理枚数を任意の枚数のミニバッチに分割する工程を有し、

前記モデル化工程は、前記ミニバッチ分の前記前段側グラフ・ネットワークと、前記ミニバッチ分の前記後段側グラフ・ネットワークを作成し、10

前記結合工程は、前記ミニバッチ分の前記前段側グラフ・ネットワークと、前記ミニバッチ分の前記後段側グラフ・ネットワークとを結合し、

前記基板搬送方法は、さらに、指定された処理枚数分まで前記ミニバッチ分の前記前段側グラフ・ネットワークと前記ミニバッチ分の前記後段側グラフ・ネットワークとの作成及び結合を繰り返す工程を有する、基板搬送方法。

#### 【請求項 8】

請求項6又は7に記載された基板搬送方法において、

前記基板処理装置が非定常状態に移行したか否かを検知する工程を有し、

前記モデル化工程は、前記基板処理装置が非定常状態に移行したことを検知したとき、前記非定常状態における前記基板処理装置の処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、グラフ・ネットワークを作成し、前記各ノードへの最長経路長の計算を行う工程を含み、20

前記計算工程は、前記非定常状態の前記各ノードへの最長経路長に基づいて、前記基板搬送スケジュールを計算する工程を含む、基板搬送方法。

#### 【請求項 9】

請求項8に記載された基板搬送方法において、

前記非定常状態は、前記基板処理装置の故障時の状態、前記基板ホルダのメンテナンス時の状態、又はアノードホルダのメンテナンス時の状態を含む、基板搬送方法。

#### 【発明の詳細な説明】

##### 【技術分野】

30

##### 【0001】

本発明は、スケジューラ、基板処理装置、及び基板搬送方法に関する。

##### 【背景技術】

##### 【0002】

基板処理装置には種々の構成のものが存在する。例えば、一般に、複数枚の基板を収容する基板収納容器と、複数の搬送機と、複数の処理部を有する基板処理装置が知られている。この基板処理装置では、複数枚の基板が基板収納容器から装置内に順次投入され、複数の搬送機により複数の処理部間を搬送されて並列的に処理され、処理後の基板が基板収納容器に回収される。また、複数の基板収納容器を有し、これらを交換可能とした基板処理装置も知られている。このような基板処理装置では、処理済の基板が装填された基板収納容器を未処理の基板が装填された基板収納容器に適宜交換することによって、連続的に基板処理装置の運転を行うことができる。40

##### 【0003】

上記の基板処理装置の一例として、例えば、バンプ形成、T S V形成、再配線めっきを行いうめっき処理装置が知られている。このような基板処理装置では、厳しいプロセス制約条件（あるプロセスが開始してから次のプロセスを開始するまでの所定のプロセス時間間隔）を満たしながら、高いスループットを実現することが求められる。この厳しい要求を満たすため、めっき処理装置の基板搬送制御には最適な基板の搬送計画を立てる様々なスケジューリング手法が考えられてきた。このスケジューリング手法として、シミュレーション法を用いて基板搬送スケジュールを計算する基板処理装置が知られている（特許文献50

1)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第5620680号

【発明の概要】

【発明が解決しようとする課題】

【0005】

シミュレーション法を用いて基板搬送スケジュールを計算する場合、良好なスループットを得るために、予め与えられた処理条件及び制約条件に基づいて、スケジューリングに関連する多数のパラメータの組み合わせについてそれぞれシミュレーション計算を行うので、計算量が膨大となり、基板処理装置としての実際の運用には適さないという問題がある。この解決策として、設計時点において想定されるプロセスレシピ条件に対してスループット値が最大となるようなパラメータ設定を検索して、最適と想定されるパラメータ範囲に絞りこむことが考えられる。実際の基板処理実行時にはこれらの各々のパラメータに対して基板搬送シミュレーションを行い、スループットの評価値を計測し、その中から最大スループット値となるパラメータを選択する。このように、数多く存在するパラメータ群の中から最適と想定されるパラメータ範囲を事前に絞り込むことで、実際の運用時におけるシミュレーション計算時間を短縮させ、基板の処理開始に支障が出ないようにする必要がある。10

20

【0006】

しかしながら、装置に搭載したときのシミュレーション計算時間が実運用に支障のない計算時間に収まる範囲で、かつ最適と想定されるパラメータ範囲を予め用意するためには、長時間（例えば5時間）の事前の計算処理が必要となる。また、事前に用意された最適と想定されるパラメータ範囲は、想定されるプロセスレシピ条件に基づいて決定されたものであるので、想定されるプロセスレシピ以外の条件が与えられた場合や基板処理装置が故障等の非定常状態にある場合には、良好なスループットを達成することができないという問題がある。

【0007】

本発明は上述の点に鑑みてなされたものである。その目的は、基板搬送スケジュールのための計算量及び計算時間を削減し、あらゆる条件において良好なスループットを得ることである。30

【課題を解決するための手段】

【0008】

本発明の一形態によれば、基板の処理を行う複数の基板処理部と、前記基板を搬送する搬送部と、前記搬送部と前記基板処理部を制御する制御部を備えた基板処理装置の前記制御部に内蔵され、基板搬送スケジュールを計算するスケジューラが提供される。このスケジューラは、前記基板処理装置の処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、グラフ・ネットワークを作成し、各ノードへの最長経路長の計算を行うモデル化部と、前記最長経路長に基づいて前記基板搬送スケジュールを計算する計算部と、を有する。40

【0009】

この一形態によれば、基板搬送スケジュールが、グラフ・ネットワーク理論を用いてモデル化された各ノードへの最長経路長に基づいて計算される。したがって、従来多くの計算時間を要していたパラメータ範囲の絞りこみのための事前の計算処理を行うことなく、基板搬送スケジュールを計算することができる。また、最適なスループットを得るためのパラメータ（処理条件）を予め制限する必要もないので、想定されるプロセスレシピ以外の条件が与えられた場合でも良好なスループットを達成し得る基板搬送スケジュールを計算することができる。

【0010】

50

本発明の一形態において、前記基板処理部は、基板ホルダに保持された前記基板にめっき処理するめっき処理部を有する。前記搬送部は、前記基板を収容する基板収納容器と前記基板を前記基板ホルダに対して着脱するフィキシングステーションとの間で基板を搬送する前段搬送部と、前記フィキシングステーションと前記めっき処理部との間で基板を搬送する後段搬送部とを有する。前記基板処理装置は、前記前段搬送部を含む装置前段部と、前記めっき処理部及び前記後段搬送部を含む装置後段部とを有する。前記モデル化部は、前記装置前段部及び前記装置後段部の処理条件、処理時間、及び制約条件をそれぞれモデル化し、前記装置前段部における前段側グラフ・ネットワークと、前記装置後段部における後段側グラフ・ネットワークとを別々に作成する。前記スケジューラは、さらに、前記前段側グラフ・ネットワークと、前記後段側グラフ・ネットワークとを結合する処理を行い、各ノードへの最長経路長の計算を行う結合部を有する。前記計算部は、前記結合部で算出された前記各ノードへの最長経路長を元に、前記基板搬送スケジュールを計算する。

#### 【0011】

この一形態によれば、装置前段部及び装置後段部の処理条件、処理時間、及び制約条件をそれぞれモデル化し、装置前段部における前段側グラフ・ネットワークと、装置後段部における後段側グラフ・ネットワークとを別々に作成した後、それぞれのネットワークを結合する処理を行う。装置前段部と装置後段部のネットワークをエッジで結合するノード数はネットワーク全体のノード数に比較して少ないため、装置全体のグラフ・ネットワークをまとめて計算する場合に比べて、計算が単純化され、計算量及び計算時間を削減することができる。

#### 【0012】

本発明の一形態において、スケジューラは、指定された前記基板の処理枚数を任意の枚数のミニバッチに分割する。前記モデル化部は、前記ミニバッチ分の前記前段側グラフ・ネットワークと、前記ミニバッチ分の前記後段側グラフ・ネットワークを作成する。前記結合部は、前記ミニバッチ分の前記前段側グラフ・ネットワークと、前記ミニバッチ分の前記後段側グラフ・ネットワークとを結合する。スケジューラは、指定された処理枚数分まで前記ミニバッチ分の前記前段側グラフ・ネットワークと前記ミニバッチ分の前記後段側グラフ・ネットワークとの作成及び結合を繰り返す。

#### 【0013】

この一形態によれば、指定された全処理枚数について、前段部と後段部のグラフ・ネットワークを作成した後に結合する場合に比べ、結合時の計算処理を低減することができる。また、処理条件によってミニバッチの枚数を任意に変えることで、計算時間の短い条件を選ぶことができる。

#### 【0014】

本発明の一形態において、前記基板処理装置が非定常状態に移行したか否かを検知する検知部を有し、前記モデル化部は、前記基板処理装置が非定常状態に移行したことを前記検知部が検知したとき、前記非定常状態における前記基板処理装置の処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、グラフ・ネットワークを作成し、各ノードへの最長経路長の計算を行い、前記計算部は、前記非定常状態における前記各ノードへの最長経路長に基づいて、前記基板搬送スケジュールを計算するように構成される。

#### 【0015】

この一形態によれば、基板処理装置が非定常状態に移行したときであっても、非定常状態における各ノードへの最長経路長に基づいて基板搬送スケジュールを計算するので、非定常状態において適切な基板搬送スケジュールを計算することができる。

#### 【0016】

本発明の一形態において、前記非定常状態は、前記基板処理装置の故障時の状態、基板ホルダのメンテナンス時の状態、又はアノードホルダのメンテナンス時の状態を含む。

#### 【0017】

10

20

30

40

50

この一形態によれば、基板処理装置の故障のような突発的な非定常状態における適切な基板搬送スケジュールを計算することができる。また、基板ホルダ及びアノードホルダは、長時間使用されることにより洗浄や点検が必要になる場合があり、基板処理装置から取り出されて、もしくは基板処理装置内で定期的にメンテナンス（洗浄又は点検）される。この一形態によれば、メンテナンスのような定期的に発生する非定常状態においても、適切な基板搬送スケジュールを計算することができる。

#### 【0018】

本発明の一形態によれば、上記いずれかのスケジューラを内蔵する前記制御部を備えた、基板処理装置が提供される。この基板処理装置において、前記制御部は、計算された前記基板搬送スケジュールに基づいて前記搬送部を制御するように構成される。

10

#### 【0019】

この一形態によれば、計算された基板搬送スケジュールに基づいて、基板を適切に搬送することができる。

#### 【0020】

本発明の一形態によれば、基板の処理を行う複数の基板処理部と、前記基板を搬送する搬送部と、前記搬送部と前記基板処理部を制御する制御部を備えた基板処理装置を用いた前記基板搬送方法が提供される。この基板搬送方法は、前記基板処理装置の処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、グラフ・ネットワークを作成し、各ノードへの最長経路長の計算を行うモデル化工程と、前記最長経路長に基づいて基板搬送スケジュールを計算する計算工程と、前記基板搬送スケジュールに基づいて前記基板を搬送する工程と、を有する。

20

#### 【0021】

この一形態によれば、基板搬送スケジュールが、グラフ・ネットワーク理論を用いてモデル化された各ノードへの最長経路長に基づいて計算される。したがって、従来多くの計算時間を要していたパラメータ範囲の絞りこみのための事前の計算処理を行うことなく、基板搬送スケジュールを計算することができるので、計算量及び計算時間を低減することができる。また、最適なスループットを得るためのパラメータ（処理条件）を予め制限する必要もないで、想定されるプロセスレシピ以外の条件が与えられた場合でも良好なスループットを達成し得る基板搬送スケジュールを計算することができる。

#### 【0022】

本発明の一形態において、前記基板処理部は、基板ホルダに保持された前記基板にめっき処理するめっき処理部を有し、前記搬送部は、前記基板を収容する基板収納容器と前記基板を前記基板ホルダに対して着脱するフィキシングステーションとの間で基板を搬送する前段搬送部と、前記フィキシングステーションと前記めっき処理部との間で基板を搬送する後段搬送部とを有し、前記基板処理装置は、前記前段搬送部を含む装置前段部と、前記めっき処理部及び前記後段搬送部を含む装置後段部とを有する。前記モデル化工程は、前記装置前段部及び前記装置後段部の処理条件、処理時間、及び制約条件をそれぞれモデル化し、前記装置前段部における前段側グラフ・ネットワークと、前記装置後段部における後段側グラフ・ネットワークとを別々に作成する。前記基板搬送方法は、さらに、前記前段側グラフ・ネットワークと、前記後段側グラフ・ネットワークとを結合する処理を行い、各ノードへの最長経路長の計算を行う結合工程を有する。前記計算工程は、前記結合工程で算出された前記最長経路長に基づいて基板搬送スケジュールを計算する。

30

#### 【0023】

この一形態によれば、装置前段部及び装置後段部の処理条件、処理時間、及び制約条件をそれぞれモデル化し、装置前段部における前段側グラフ・ネットワークと、装置後段部における後段側グラフ・ネットワークとを別々に計算し、その後それぞれのネットワークを結合する。前段部と後段部のネットワークをエッジで結合するノードはネットワーク全体のノード数に比較して少ないため、装置全体の基板搬送スケジュールを計算する場合に比べて、計算が単純化され、計算量及び計算時間を削減することができる。

#### 【0024】

40

50

本発明の一形態において、基板搬送方法は、指定された前記基板の処理枚数を任意の枚数のミニバッチに分割する工程を有し、前記モデル化工程は、前記ミニバッチ分の前記前段側グラフ・ネットワークと、前記ミニバッチ分の前記後段側グラフ・ネットワークを作成し、前記結合工程は、前記ミニバッチ分の前記前段側グラフ・ネットワークと、前記ミニバッチ分の前記後段側グラフ・ネットワークとを結合し、前記基板搬送方法は、さらに、指定された処理枚数分まで前記ミニバッチ分の前記前段側グラフ・ネットワークと前記ミニバッチ分の前記後段側グラフ・ネットワークとの作成及び結合を繰り返す工程を有する。

#### 【0025】

この一形態によれば、指定された全処理枚数について、前段部と後段部のグラフ・ネットワークを作成した後に結合する場合に比べ、結合時の計算処理を低減することができる。また、処理条件によってミニバッチの枚数を任意に変えることで、計算時間の短い条件を選ぶことができる。

#### 【0026】

本発明の一形態において、前記基板処理装置が非定常状態に移行したか否かを検知する工程を有し、前記モデル化工程は、前記基板処理装置が非定常状態に移行したことを検知したとき、前記非定常状態における前記基板処理装置の処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、グラフ・ネットワークを作成し、前記各ノードへの最長経路長の計算を行う工程を含み、前記計算工程は、前記非定常状態の前記各ノードへの最長経路長に基づいて、前記基板搬送スケジュールを計算する工程を含む。

#### 【0027】

この一形態によれば、基板処理装置が非定常状態に移行したときであっても、その処理条件、処理時間、及び制約条件に基づいて基板搬送スケジュールを計算するので、非定常状態において適切な基板搬送スケジュールを計算することができる。

#### 【発明の効果】

#### 【0028】

本発明の一つによれば、基板搬送スケジュールのための計算量及び計算時間を削減することができる。

#### 【図面の簡単な説明】

#### 【0029】

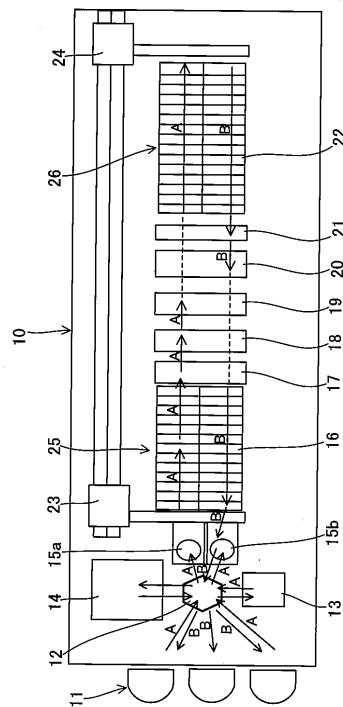

【図1】本発明の実施形態に係るめっき処理装置の構成例を示す模式図である。

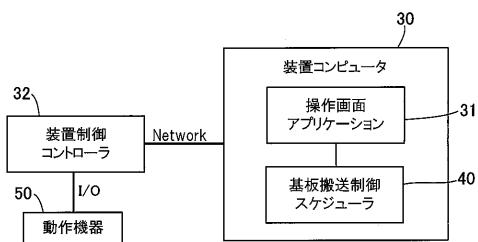

【図2】制御部の構成の一例を示すブロック図である。

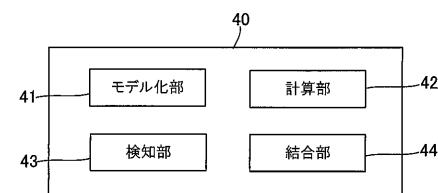

【図3】図2に示した基板搬送制御スケジューラのブロック図である。

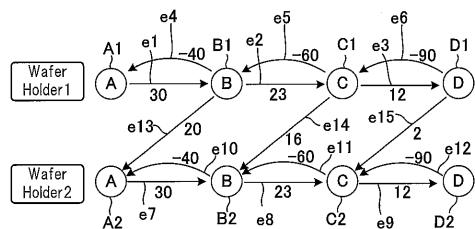

【図4】図3に示したモデル化部によりモデル化されたグラフ・ネットワークの一例を示す図である。

【図5】各ノードへの最長経路長を付記した図4に示したグラフ・ネットワーク図である。

【図6】図5に示したグラフ・ネットワーク図に、搬送機の競合を避けるためのエッジを追加した図である。

【図7】各ノードへの最長経路長を付記した図6に示したグラフ・ネットワーク図である。

【図8】基板搬送スケジュールの一部を示す図である。

【図9】基板搬送制御スケジューラに設定されるロードロボットの搬送処理時間の一例を示す図である。

【図10】基板搬送制御スケジューラに設定される搬送機の搬送処理時間の一例を示す図である。

【図11】基板搬送制御スケジューラに設定される搬送機の搬送処理時間の一例を示す図である。

【図12】基板搬送制御スケジューラに設定される制約条件の一例を示す図である。

10

20

30

40

50

【図13】基板搬送制御スケジューラに設定される全体レシピの一例を示す図である。

【図14】基板搬送制御スケジューラに設定されるプロセスレシピの一例を示す図である。

【図15】本実施形態に係る基板処理方法を示すフロー図である。

【図16】ステップS105のサブルーチンを示すフロー図である。

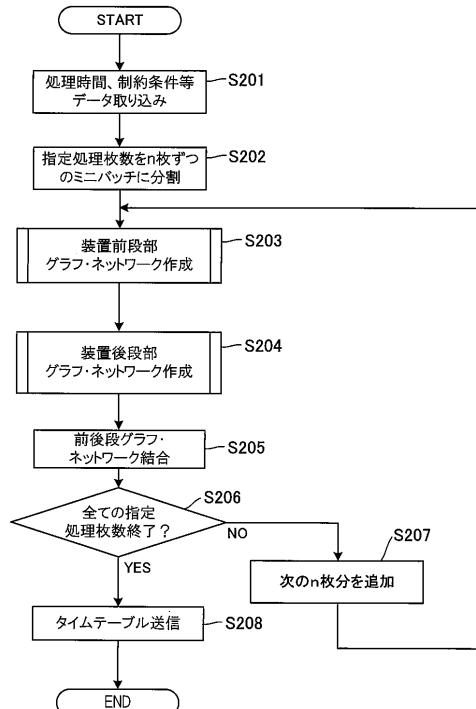

【図17】ステップS202のサブルーチンを示すフロー図である。

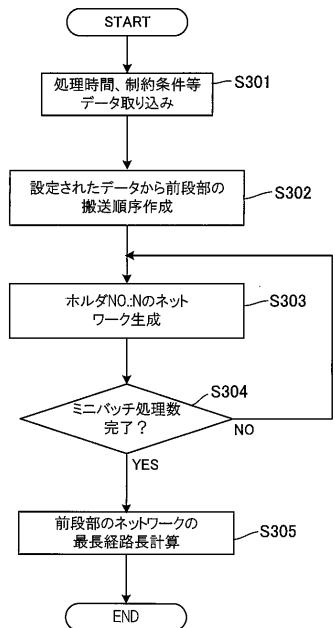

【図18】ステップS203のサブルーチンを示すフロー図である。

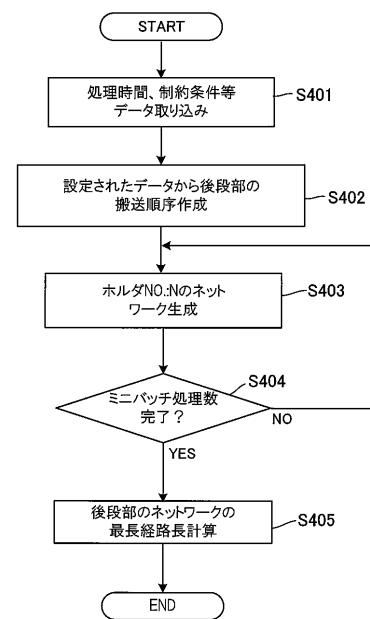

【発明を実施するための形態】

#### 【0030】

以下、本発明の実施形態について図面を参照して説明する。以下で説明する図面において、同一の又は相当する構成要素には、同一の符号を付して重複した説明を省略する。本実施形態では、基板処理装置として半導体基板にめっき処理を行うめっき装置を例に説明するが、本発明に係る基板処理装置はこれに限らず、例えば、ガラス基板に対してLCD製造用の処理を行う基板処理装置等、各種の基板処理装置に適用できる。

10

#### 【0031】

図1は、本発明の実施形態に係るめっき処理装置の構成例を示す模式図である。本めっき処理装置10は、ロードポート11、ロードロボット12、アライナ13、スピンドライヤ(SRD)14、フィキシングステーション15a, 15b、複数のストッカ16を備えた基板ホルダ貯留領域25、前水洗槽17、前処理槽18、水洗槽19、粗乾燥槽(ブローカー)20、水洗槽21、複数のめっき槽22を備えためっき領域26(めっき処理部の一例に相当する)、2台の搬送機23, 24を有する。スピンドライヤ14、前水洗槽17、前処理槽18、水洗槽19、ブローカー20、水洗槽21、及びめっき槽22は、基板に所定の処理を行う基板処理部として機能する。また、ロードロボット12及び搬送機23, 24は、基板を搬送する搬送部として機能する。

20

#### 【0032】

図1において、矢印Aは基板のロード移送行程を、矢印Bは基板のアンロードの移送行程を示す。ロードポート11には複数枚の未処理基板及び複数枚の処理済基板を収納した基板収納容器(FOUP:Front Opening Unified Pod)が載置されるようになっている。

30

#### 【0033】

このめっき処理装置10において、ロードロボット12はロードポート11に載置された基板収納容器から未処理の基板を取り出し、アライナ13に載置する。アライナ13は、ノッチ、オリフラ(オリエンテーションフラット)等を基準に基板の位置決めを行う。次にロードロボット12は基板をフィキシングステーション15a, 15bに移送し、フィキシングステーション15a, 15bは、ストッカ16から取り出した基板ホルダに基板を装着する。このめっき処理装置10は、2台のフィキシングステーション15a, 15bでそれぞれの基板ホルダに基板を装着し、2つの基板ホルダを1組として搬送するよう構成される。基板ホルダに装着された基板は搬送機23により、前水洗槽17に移送され前水洗槽17で前水洗処理された後、前処理槽18に移送される。前処理槽18で前処理された基板は、更に水洗槽19に移送され、水洗槽19で水洗処理される。

40

#### 【0034】

水洗槽19で水洗処理された基板は、搬送機24でめっき領域26のいずれかのめっき槽22に移送され、めっき液に浸漬される。ここでめっき処理が施され基板に金属膜が形成される。金属膜が形成された基板は搬送機24により水洗槽21に移送され、水洗槽21で水洗処理される。続いて、基板は、搬送機24によりブローカー20に移送されて粗乾燥処理を施された後、搬送機23によりフィキシングステーション15a, 15bに移送され、基板ホルダから取り外される。基板ホルダから取り外された基板は、ロードロボット12でスピンドライヤ14に移送され、洗浄・乾燥処理を施された後、ロードポート11に載置されている基板収納容器の所定位置に収納される。

#### 【0035】

50

本実施形態に係るめっき処理装置10は、便宜上、ロードポート11とフィキシングステーション15a, 15bとの間で基板を搬送するロードロボット12（前段搬送部の一例に相当する）を含む装置前段部と、フィキシングステーション15a, 15bとめっき領域26との間で基板を搬送する搬送機23, 24（後段搬送部の一例に相当する）を含む装置後段部とに分けられる。本実施形態に係るめっき処理装置10においては、後述するように、装置前段部における前段側グラフ・ネットワークと、装置後段部における後段側グラフ・ネットワークとを別々に計算する。

#### 【0036】

続いて、図1に示しためっき処理装置10を制御する制御部について説明する。図2は、制御部の構成の一例を示すブロック図である。図1に示したロードロボット12、搬送機23、及び搬送機24による矢印Aに示す基板のロード移送行程の搬送制御、及び矢印Bに示す基板のアンロードの移送行程の搬送制御は、制御部の制御により行われる。

10

#### 【0037】

めっき処理装置10の制御部は、装置コンピュータ30と装置制御コントローラ32を有する。装置コンピュータ30は、主に計算やデータ処理等を行い、装置制御コントローラ32は主に図1に示しためっき処理装置10の各部を制御するように構成される。本実施形態では、装置コンピュータ30と装置制御コントローラ32とが別々に構成されるが、これに限らず、これらを一体の制御部として構成してもよい。

#### 【0038】

装置コンピュータ30は、図示しない表示部に操作画面を表示させる操作画面アプリケーション31と、基板搬送制御スケジュールを生成するための基板搬送制御スケジューラ40と、を有する。装置コンピュータ30は、この他、操作画面アプリケーション31及び基板搬送制御スケジューラ40を実現するために必要なCPU(Central Processing Unit)、ROM(Read Only Memory)、メモリ、ハードディスク等のハードウェアを有する。

20

#### 【0039】

装置制御コントローラ32は、装置コンピュータ30とネットワーク接続されており、装置コンピュータ30から、基板搬送制御スケジューラ40が生成した基板搬送制御スケジュールを受信するように構成される。装置制御コントローラ32は、図1に示した搬送部及び基板処理部を含む動作機器50と、入出力インターフェースを介して通信可能に接続される。装置制御コントローラ32は、装置コンピュータ30から受信した基板搬送制御スケジュールに従って、動作機器50を制御する。

30

#### 【0040】

図3は、図2に示した基板搬送制御スケジューラ40のブロック図である。図示のように、基板搬送制御スケジューラ40は、モデル化部41と、計算部42と、検知部43と、結合部44とを有する。本実施形態に係る基板搬送制御スケジューラ40は、基板搬送スケジュールを計算するために、後述するグラフ・ネットワーク理論を用いて、めっき処理装置10の処理条件、処理時間、及び制約条件をノード及びエッジにモデル化する。ここで処理条件とは、処理の種類及び順序、並びに処理の優先度等を含む。処理時間とは、各プロセスの開始時間、搬送開始時間、プロセスに要する時間、及び搬送に要する時間等を含む。また、制約条件とは、ある処理の開始から次の処理を開始するまでにかかる時間を制約する条件等をいう。なお、スケジューラとは、外部から信号情報を受信し、これに基づいて基板搬送スケジュールを計算する一連の演算処理を行うためのソフトウェアが記録された記憶媒体を少なくとも有する演算処理装置のことという。なお、このスケジューラは、処理時間、制約条件、及びプロセスレシピ(処理条件)等のデータ情報を記憶するための記憶部をさらに有するようにし、この記憶部に保存された情報を参照しながら、上記の演算処理を行うように構成される。

40

#### 【0041】

モデル化部41は、めっき処理装置10の処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジで表されるグラフ・ネットワークにモデ

50

ル化し、各ノードへの最長経路長の計算を行う。計算部42は、モデル化された各ノードへの最長経路長に基づいて基板搬送スケジュールを計算する。検知部43は、図2に示した装置制御コントローラ32からの信号を受信し、めっき処理装置10が非定常状態に移行したか否かを検知する。ここで、非定常状態とは、例えば、めっき処理装置10の故障時の状態、基板ホルダのメンテナンス時の状態、又はアノードホルダのメンテナンス時の状態等を含む。

#### 【0042】

また、本実施形態では、結合部44は、装置前段部における前段側グラフ・ネットワークと、装置後段部における後段側グラフ・ネットワークとを別々に計算し、前段側グラフ・ネットワークと後段側グラフ・ネットワークとを結合して、めっき処理装置10全体に係るグラフ・ネットワークを計算する。

10

#### 【0043】

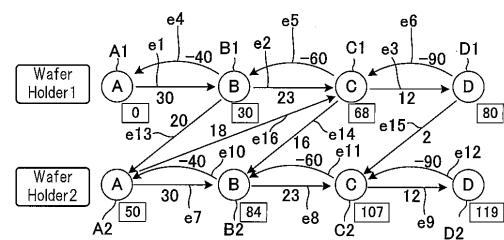

次に、図3に示した基板搬送制御スケジューラ40により基板搬送スケジュールを計算する具体例について説明する。図4は、図3に示したモデル化部41によりモデル化されたグラフ・ネットワークの一例を示す図である。このグラフ・ネットワークは、説明のために簡素化されたものである。

#### 【0044】

このグラフ・ネットワークをモデル化するための前提を以下の通りとした。即ち、処理対象となる基板を保持した基板ホルダは2つ使用される。ここでは、それぞれの基板ホルダを第1基板ホルダ(Wafer Holder 1)と第2基板ホルダ(Wafer Holder 2)と呼ぶ。この例におけるめっき処理装置10は、4つのユニットA、ユニットB、ユニットC、ユニットDを有し、2つ基板ホルダはそれぞれ別のユニットAに収納された状態から処理が開始される。ユニットB、Cについては、基板ホルダは1つしか存在できない。基板ホルダの各々には、図4においてノードとなる処理A-Dが実施される。基板ホルダの各々に実施される処理A-Dの考えられる順番はプロセスレシピに基づいて予め定められており、この順番は、図4に示されるエッジe1-e16の矢印で示される。処理Aは、ユニットAからの基板ホルダの取り出し処理である。処理Bは、ユニットBからの基板ホルダの取り出し処理である。処理Cは、ユニットCからの基板ホルダの取り出し処理である。処理A、B、Cについてはそれぞれ、基板ホルダの取り出し、次のユニットへの移動、次のユニットへの収納の一連の処理を連続して実行するものとする。処理Dは、ユニットDへの基板ホルダの収納処理である。処理A-Cの取り出し処理時間は、それぞれ5秒とする。処理Dは、終了処理であり、取り出し処理時間は0である。基板ホルダの各々は、一つの搬送機により一つずつ搬送される。例えば、ユニットBとユニットC間の搬送機の移動時間は3秒とする。ユニットB間、及びユニットC間の搬送機の移動時間は1秒とする。ユニットBに収納された基板ホルダには、15秒間の処理が行われ、ユニットCに収納された基板ホルダには、10秒間の処理が行われる。また、制約条件として、処理Aが開始されてから処理Bが開始されるまでの時間を40秒以内、処理Bが開始されてから処理Cが開始されるまでの時間を60秒等とする。これらの前提条件の一覧を以下の表1に示す。

20

#### 【0045】

30

40

【表1】

| 処理一覧 |  | 処理内容         |

|------|--|--------------|

| A    |  | ユニットAから取出し開始 |

| B    |  | ユニットBから取出し開始 |

| C    |  | ユニットCから取出し開始 |

| D    |  | ユニットDに収納(完了) |

| ユニット間移動時間<br>(s) | 移動先 |   |   |   |

|------------------|-----|---|---|---|

|                  | A   | B | C | D |

| 移動元              | A   | 1 | 5 | 7 |

|                  | B   | 5 | 1 | 3 |

|                  | C   | 7 | 3 | 1 |

|                  | D   | 8 | 4 | 2 |

| 取出し処理時間(s) |   |

|------------|---|

| ユニットA      | 5 |

| ユニットB      | 5 |

| ユニットC      | 5 |

| ユニットD      | 0 |

| 収納処理時間(s) |   |

|-----------|---|

| ユニットA     | 0 |

| ユニットB     | 5 |

| ユニットC     | 5 |

| ユニットD     | 5 |

| レシピ処理時間(s) |    |

|------------|----|

| ユニットA      | 0  |

| ユニットB      | 15 |

| ユニットC      | 10 |

| ユニットD      | 0  |

| 制約上限時間(s) |    |

|-----------|----|

| A→B       | 40 |

| B→C       | 60 |

| C→D       | 90 |

## 【0046】

図4に示すように、第1基板ホルダに関して処理Aから処理Bへの所要時間は、ユニットAからの取り出し処理時間である5秒と、ユニットAからユニットBへの搬送機の移動時間の5秒と、ユニットBへの収納処理時間の5秒と、ユニットBでのレシピ処理時間の15秒とで、30秒となる。よってエッジe1は30秒となる。また、ユニットA,B間の処理の制約条件である40秒が、エッジe4となる。ここでの制約条件は負数で表される。ユニットB,C間、ユニットC,D間についても同様である。第1基板ホルダに関して、処理Bから処理Cへの所要時間は、ユニットBからの取り出し処理時間である5秒と、ユニットBからユニットCへの搬送機の移動時間3秒と、ユニットCにおける収納処理時間である5秒と、ユニットCでのレシピ処理時間の10秒であり、エッジe2は23秒となる。

10

## 【0047】

続いて、第1基板ホルダに関して処理Cから処理Dへの所要時間は、ユニットCからの取り出し処理時間である5秒と、ユニットCからユニットDへの搬送機の移動時間の2秒と、ユニットDへの収納処理時間の5秒で、12秒となる。よってエッジe3は12秒となる。第2基板ホルダに関して、処理A-Dまでのそれぞれの所要時間は、第1基板ホルダと同様である。

30

## 【0048】

第1基板ホルダの処理Bから第2基板ホルダの処理Aへ移行する場合、第2基板ホルダが処理A(ユニットAから取り出し、ユニットBへ移動、収納)を開始するためには、ユニットBが空いている必要がある。このため、まず第1基板ホルダの処理Bが実行される必要がある。すなわちユニットBからの取出し時間の5秒と、ユニットBからユニットCへの移動時間の3秒と、ユニットCへの収納処理時間の5秒が必要となる。また、処理Bの最後はユニットCで行われ、処理AがユニットAで行われるので、搬送機がユニットCからユニットAへ移動する時間の7秒が必要となる。したがって、第1基板ホルダの処理Bから第2基板ホルダの処理Aへの所要時間は、20秒となる。よってエッジe13は20秒となる。エッジe14についても同様に算出され、16秒となる。エッジe15はユニットDのレシピ処理時間は0秒なので、ユニットDからユニットCまでの移動時間の2秒となる。

40

## 【0049】

50

以上のようにして図3に示したモデル化部41によって生成されたグラフ・ネットワーク図において、各ノードへの最長経路長を算出する。ここで、モデル化部41は、最長経路長を算出するために、最短経路問題解決手法を用いる。具体的には、モデル化部41は、各エッジの所要時間の値を正負反転し、ベルマン・フォード法等の公知の最短経路問題解決手法により、各ノードへの最短経路を算出する。ここでは、例えば第1基板ホルダの処理Aから第1基板ホルダの処理Cへの最短経路は、第1基板ホルダの処理A、第1基板ホルダの処理B、第1基板ホルダの処理Cを順次実施する場合が最短経路（値が最小）となり、その所要時間の値は「-53」となる。モデル化部41は、このようにして各ノードへの最短経路長の値を計算し、その値を再度正負反転する。この値が、各ノードへの最長経路長を示す値となる。この値は、各処理の実行可能な最速の処理開始時刻を示す。なお、ベルマン・フォード法の他、例えばダイクストラ法等を用いて、各ノードへの最長経路長を計算してもよい。

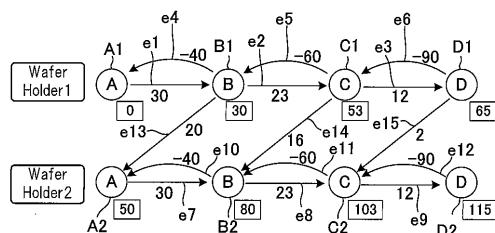

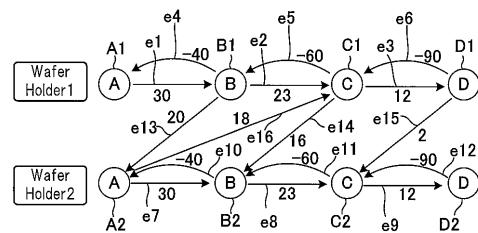

#### 【0050】

図5は、各ノードへの最長経路長を付記した図4に示したグラフ・ネットワーク図である。ここで、第1基板ホルダの処理Cの開始時刻53秒と、第2基板ホルダの処理Aの開始時刻50秒について確認する。開始時刻の早い第2基板ホルダの処理Aを開始すると、取出し処理の5秒と、ユニットAからユニットBへの移動処理の5秒と、ユニットBへの収納処理の5秒が経過するまでは搬送機が使用できないため、第1基板ホルダの処理Cは実行できない。加えて、処理Aの最後のユニットBから処理Cの開始位置のユニットCまでの移動時間の3秒を経過しないと第1基板ホルダの処理Cは開始できない。このように搬送機の競合を避けるため、図6に示すように新たに、例えばエッジe16を追加する必要がある。このエッジe16は上記から18秒となる。図7はエッジe16を加えた後で再度各ノードへの最長経路長を計算し、更新したグラフ・ネットワーク図である。なお、このエッジe16に相当するエッジの向きは逆でも構わず、その場合、エッジ長は20秒となる。

#### 【0051】

グラフ・ネットワーク図において、エッジの追加によって長さが正の閉路が生成される場合、実行不可能（制約条件を守れない）となるため、追加したエッジを削除し、別のエッジを追加する必要がある。図7の例では、第1基板ホルダの処理Bと、第2基板ホルダの処理Aと、第1基板ホルダの処理Cの間で閉路が存在するが、長さの合計は $20 + 18 - 60 = -22$ となるので問題はない。

#### 【0052】

図7に示す各ノードへの最長経路長は、各処理の実行可能な最速の処理開始時刻を示す。したがって、最長経路長の値が示す時刻に各処理を実行すれば、スループットが高い基板搬送処理を行うことができる。

#### 【0053】

計算部42は、図7に示す最長経路長の値に基づいて、各基板ホルダを搬送するタイムテーブル、即ち基板搬送スケジュールを作成する。図8は、基板搬送スケジュールの一部を示す図である。基板搬送制御スケジューラ40は、このようにして作成された基板搬送スケジュールを、図2に示した装置制御コントローラ32に送信する。装置制御コントローラ32は、この基板搬送スケジュールに基づいて、基板処理部及び搬送部を制御する。

#### 【0054】

このように、本実施形態に係る基板搬送制御スケジューラ40によれば、基板搬送スケジュールが、グラフ・ネットワーク理論を用いてモデル化されたノード及びエッジについて、各ノードへの最長経路長に基づいて計算される。したがって、パラメータ範囲の絞りこみのための事前の計算処理を行うことなく、基板搬送スケジュールを計算することができるので、計算量及び計算時間を低減することができる。また、最適なスループットを得るためにパラメータ（処理条件）を制限する必要もないので、想定されるプロセスレシピ以外の条件が与えられた場合でも良好なスループットを達成し得る基板搬送スケジュールを計算することができる。

**【0055】**

次に、基板搬送制御スケジューラ40に設定される、めっき処理装置10の処理条件、処理時間、及び制約条件の具体例について説明する。図9は、基板搬送制御スケジューラ40に設定されるロードロボット12の搬送処理時間の一例を示す図である。この図には、一の基板収納容器(FOUP1)、他の基板収納容器(FOUP2)、及びスピンドライヤ14等の間で、ロードロボット12が基板を搬送するために要する時間(秒)が例示される。例えば、FOUP1からFOUP2にロードロボット12が基板を搬送するには、1秒の処理時間を要する。図9に示すそれぞれの所要時間として、予め測定された値が基板搬送制御スケジューラ40に設定される。

**【0056】**

10

図10は、基板搬送制御スケジューラ40に設定される搬送機23の搬送処理時間の一例を示す図であり、図11は、基板搬送制御スケジューラ40に設定される搬送機24の搬送処理時間の一例を示す図である。図10には、フィギングステーション15a, 15b、前処理槽18(Pre-wet)、水洗槽19(Presoak)、及びブロー槽20(Blow)等の間で、搬送機23が基板を搬送するために要する時間(秒)が示される。また、図11には、ブロー槽20、一のめっき槽22、及び他のめっき槽22等の間で、搬送機24が基板を搬送するために要する時間(秒)が示される。図9ないし図11に示す各搬送部の移動所要時間は、処理時間として予め基板搬送制御スケジューラ40に設定される。

**【0057】**

20

続いて、基板搬送制御スケジューラ40に設定される制約条件について説明する。図12は、基板搬送制御スケジューラ40に設定される制約条件の一例を示す図である。図示のように、この例では、前処理槽18(Pre-wet)、水洗槽19(Presoak)、一のめっき槽22(Plating A)、及び他のめっき槽22(Plating B)等の制約条件(秒)が示される。図12に示す制約条件に従えば、例えば、搬送機23は、前処理が終了してから30秒以内に前処理槽18に収納された基板を取り出さなくてはならない。

**【0058】**

次に、基板搬送制御スケジューラ40に設定されるプロセスレシピ及びプロセス処理時間について説明する。図13は、基板搬送制御スケジューラ40に設定される全体レシピの一例を示す図である。図13に示すように、基板搬送制御スケジューラ40には、複数のプロセスレシピが設定される。図示の例では、レシピID「ABC」と「XYZ」が設定されている。それぞれのレシピIDにおいては、ユニットレシピを選択することができる。図示の例ではレシピID「ABC」において、前処理槽18(Pre-wet)における処理、他のめっき槽22(Plating B)における処理、ブロー槽20(Blow)における処理、及びスピンドライヤ14(SRD)における処理が、通常条件(STD:Standard)で行われるように設定されている。また、レシピID「XYZ」では、図示の各処理が試験条件(TEST)で行われるように設定されている。

30

**【0059】**

図14は、基板搬送制御スケジューラ40に設定されるプロセスレシピの一例を示す図である。図14に示すように、前処理槽18(Pre-wet)、水洗槽19(Presoak)、一のめっき槽22(Plating A)、他のめっき槽22(Plating B)、ブロー槽20(Blow)、及びスピンドライヤ14(SRD)における、通常条件(STD)と試験条件(TEST)の処理時間がそれぞれ設定される。図13に示した通常条件と試験条件は、図14に示された処理時間に従う。

40

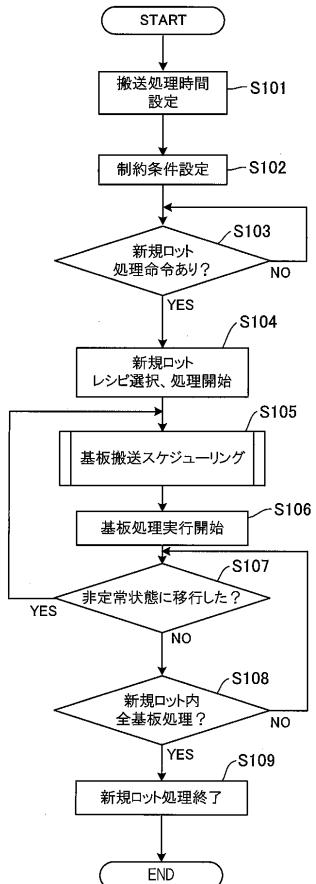

**【0060】**

次に、本実施形態に係るめっき処理装置10による基板処理方法について説明する。図15は、本実施形態に係る基板処理方法を示すフロー図である。図15に示すように、まず、オペレータは、めっき処理装置10の装置コンピュータ30が有する図示しない入力部を介して、図9から図11に示した基板の搬送処理時間と、図12に示した制約条件を

50

めっき処理装置 10 に設定する（ステップ S101、ステップ S102）。後述する非定常状態における処理時間及び制約条件は、故障の種類など非定常状態の状況に応じて、あらかじめめっき処理装置 10 に規定されている。

#### 【0061】

続いて、新規ロット処理の命令、即ち新たな基板処理の命令があったか否かを判定する（ステップ S103）。新規ロット処理の命令があったとき（ステップ S103、YES）、図 13 に示したプロセスレシピ（処理条件）のいずれかが選択され、処理が開始される（ステップ S104）。なお、このプロセスレシピの選択は、オペレータが装置コンピュータ 30 の入力部を介して入力してもよいし、装置コンピュータ 30 とネットワーク接続された図示しないホストコンピュータから入力してもよい。

10

#### 【0062】

次に、基板搬送制御スケジューラ 40 の計算部 42 は、基板搬送スケジュールを計算する（ステップ S105）。ステップ S105 の詳細なプロセスは後述する。ステップ S105 によって基板搬送スケジュール、即ちタイムテーブルが決定されると、装置制御コントローラ 32 は、基板処理を実行する（ステップ S106）。

#### 【0063】

基板処理の実行中に、めっき処理装置 10 が非定常状態に移行したか否かを検知部 43 が検知する（ステップ S107）。ここで、非定常状態とは、めっき処理装置 10 の故障時の状態、基板ホルダのメンテナンス時の状態、又はアノードホルダのメンテナンス時の状態等を含む。めっき処理装置 10 では、例えめっき槽 22 の整流器等が突発的に故障することがあり、この場合めっき槽 22 の一つが使用不可になる。また、基板ホルダ及びアノードホルダは、長時間使用されることにより洗浄や点検が必要になる場合があり、めっき処理装置 10 から取り出されて、もしくは基板処理装置内で定期的にメンテナンス（洗浄又は点検）される。この場合、使用可能な基板ホルダ及び基板ホルダの数が変更され、めっき処理装置 10 のスループットに影響が出る。そこで、めっき処理装置 10 が非定常状態に移行したと判定した場合（ステップ S107、YES）、ステップ S105 に戻り、非定常状態における処理条件、処理時間、及び制約条件に基づいて基板搬送スケジュールを再び計算する。

20

#### 【0064】

めっき処理装置 10 が非定常状態に移行していないと判定した場合（ステップ S107、NO）、新規ロット内の全ての基板が処理されたか否かが判定される（ステップ S108）。処理されるべき基板が残っている場合は（ステップ S108、NO）、ステップ S107 に戻り、めっき処理装置 10 が非定常状態に移行したか否かが検知される。新規ロット内の全ての基板が処理されると（ステップ S108、YES）、新規ロットの処理を終了する（S109）。

30

#### 【0065】

図 15 に示したステップ S105 の基板搬送スケジュールの具体的な計算手順について説明する。図 16 は、ステップ S105 のサブルーチンを示すフロー図である。図示のように、基板搬送スケジュールを計算するためには、まず、図 9 ないし図 11 及び図 14 に示した処理時間、図 12 に示した制約条件、及び図 13 に示したプロセスレシピ（処理条件）等のデータを基板搬送制御スケジューラ 40 に取り込む（ステップ S201）。なお、図 15 のステップ S107 においてめっき処理装置 10 が非定常状態に移行したことが検知された場合には、ステップ S201 においては、非定常状態のめっき処理装置 10 の処理条件、処理時間、及び制約条件等のデータが基板搬送制御スケジューラ 40 に取り込まれる。

40

#### 【0066】

続いて、基板搬送制御スケジューラ 40 は、まず指定された基板の処理枚数を n 枚毎（n は 1 以上の任意の数字）のいくつかのミニバッチに分割する（ステップ S202）。その後、基板搬送制御スケジューラ 40 は、装置前段部のグラフ・ネットワークを計算する（ステップ S203）。その後、基板搬送制御スケジューラ 40 は、装置後段部のグラフ

50

・ネットワークを計算する（ステップS204）。

#### 【0067】

結合部44は、ステップS203で計算した装置前段部のグラフ・ネットワークと、ステップS204で計算した装置後段部のグラフ・ネットワークとを関係するノード間にに対してエッジを追加することにより、装置全体としてのグラフ・ネットワークとして結合する（ステップS205）。次に、全ての指定処理枚数について計算が終了したか確認し、指定処理枚数に達していない場合（ステップS206、NO）、次のn枚分を追加し（ステップS207）、ステップS203の処理に戻る。指定処理枚数に達した場合（ステップS206、YES）、計算部42は、この装置全体のグラフ・ネットワークの各ノードへの最長経路長に基づいて基板搬送スケジュールを計算し、基板搬送タイムテーブルとして、図2に示した装置制御コントローラ32に送信する（ステップS208）。装置制御コントローラ32は、この基板搬送タイムテーブルに基づいて、基板を搬送するように、めっき処理装置10の搬送部を制御する。

10

#### 【0068】

続いて、図16に示したステップS203の装置前段部の基板搬送スケジュールの具体的な計算手順について説明する。図17は、ステップS203のサブルーチンを示すフロー図である。図示のように、装置前段部の基板搬送スケジュールを計算するためには、まず、装置前段部に関連する処理時間、制約条件、及びプロセスレスレシピ（処理条件）等のデータを基板搬送制御スケジューラ40に取り込む（ステップS301）。取り込んだこれらのデータから、装置前段部の搬送順序が作成される（ステップS302）。この搬送順序は、特にプロセスレスレシピ（処理条件）に基づいて作成される。

20

#### 【0069】

続いて、モデル化部41が、処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、図4に示したような各基板ホルダに対するグラフ・ネットワークを生成する（ステップS303）。図16に示したステップS202で与えられたミニバッチ処理数の基板ホルダについてのグラフ・ネットワークが追加生成されると（ステップS304、YES）、生成されたグラフ・ネットワークに基づいて、各ノードへの最長経路長を算出する（ステップS305）。

#### 【0070】

次に、図18に示したステップS204の装置後段部の基板搬送スケジュールの具体的な計算手順について説明する。図18は、ステップS204のサブルーチンを示すフロー図である。図示のように、装置後段部の基板搬送スケジュールを計算するためには、まず、装置後段部に関連する処理時間、制約条件、及びプロセスレスレシピ（処理条件）等のデータを基板搬送制御スケジューラ40が取得する（ステップS401）。取り込んだこれらのデータから、装置後段部の搬送順序が作成される（ステップS402）。この搬送順序は、特にプロセスレスレシピ（処理条件）に基づいて作成される。

30

#### 【0071】

続いて、モデル化部41が、処理条件、処理時間、及び制約条件を、グラフ・ネットワーク理論を用いてノード及びエッジにモデル化し、図4に示したような各基板ホルダに対するグラフ・ネットワークを生成する（ステップS403）。図16に示したステップS202で与えられたミニバッチ処理数の基板ホルダについてのグラフ・ネットワークが追加生成されると（ステップS404、YES）、生成されたグラフ・ネットワークに基づいて、各ノードへの最長経路長を算出する（ステップS405）。

40

#### 【0072】

図16で説明したように、本実施形態では、装置前段部及び装置後段部の処理条件、処理時間、及び制約条件をそれぞれモデル化し、装置前段部における前段側基板搬送スケジュールと、装置後段部における後段側基板搬送スケジュールとを別々に計算する。このため、装置全体の基板搬送スケジュールを計算する場合に比べて、計算が単純化され、計算量及び計算時間を削減することができる。なお、装置前段部と装置後段部とをまとめて一度に基板搬送スケジュールを計算してもよい。

50

**【 0 0 7 3 】**

また、本実施形態によれば、図15に示したように、めっき処理装置10が非定常状態に移行したときであっても、その処理条件、処理時間、及び制約条件に基づいて基板搬送スケジュールを計算するので、非定常状態において適切な基板搬送スケジュールを計算することができる。具体的には、めっき処理装置10の故障のような突発的な非定常状態において適切な基板搬送スケジュールを計算することができる。また、基板ホルダ及びアノードホルダのメンテナンスのような定期的に発生する非定常状態においても、適切な基板搬送スケジュールを計算することができる。

**【 0 0 7 4 】**

以上、本発明の実施形態について説明したが、上述した発明の実施の形態は、本発明の理解を容易にするためのものであり、本発明を限定するものではない。本発明は、その趣旨を逸脱することなく、変更、改良され得るとともに、本発明にはその等価物が含まれることはもちろんである。また、上述した課題の少なくとも一部を解決できる範囲、または、効果の少なくとも一部を奏する範囲において、特許請求の範囲及び明細書に記載された各構成要素の任意の組み合わせ、又は省略が可能である。

10

**【 符号の説明 】****【 0 0 7 5 】**

|                             |    |

|-----------------------------|----|

| 1 0 ...めっき処理装置              |    |

| 1 1 ...ロードポート               |    |

| 1 2 ...ロードロボット              | 20 |

| 1 4 ...スピニングスドライヤ           |    |

| 1 5 a、1 5 b ...フィキシングステーション |    |

| 2 3 ...搬送機                  |    |

| 2 4 ...搬送機                  |    |

| 2 6 ...めっき領域                |    |

| 3 0 ...装置コンピュータ             |    |

| 3 1 ...操作画面アプリケーション         |    |

| 3 2 ...装置制御コントローラ           |    |

| 4 0 ...基板搬送制御スケジューラ         |    |

| 4 1 ...モデル化部                | 30 |

| 4 2 ...計算部                  |    |

| 4 3 ...検知部                  |    |

| 4 4 ...判定部                  |    |

| 4 5 ...パラメータ調整部             |    |

【図1】

【図2】

【図3】

( 4 )

〔 四 7 〕

〔 図 5 〕

〔四八〕

| 開始時刻 | 対象  | 処理 |

|------|-----|----|

| 0    | WH1 | A  |

| 30   | WH1 | B  |

| 50   | WH2 | A  |

| 68   | WH1 | C  |

| 80   | WH1 | D  |

| 84   | WH2 | B  |

| 107  | WH2 | C  |

| 119  | WH2 | D  |

【 四 6 】

【図9】

| Load Robot<br>移動元 | F0UP1 | F0UP2 | SRD | ... |

|-------------------|-------|-------|-----|-----|

| F0UP1             | 0     | 1     | 3   |     |

| F0UP2             | 1     | 0     | 2   |     |

| SRD               | 3     | 2     | 0   |     |

| ...               |       |       |     |     |

【図10】

| 搬送機23<br>移動元   | Fixing Station | Prewet | Presoak | Blow | ... |

|----------------|----------------|--------|---------|------|-----|

| Fixing Station | 0              | 1      | 2       | 4    |     |

| Prewet         | 1              | 0      | 1       | 3    |     |

| Presoak        | 2              | 1      | 0       | 2    |     |

| Blow           | 4              | 3      | 2       | 0    |     |

| ...            |                |        |         |      |     |

【図11】

| 搬送機24<br>移動元 | Blow | PlatingA | PlatingB | ... | ... |

|--------------|------|----------|----------|-----|-----|

| Blow         | 0    | 2        | 4        |     |     |

| PlatingA     | 2    | 0        | 2        |     |     |

| PlatingB     | 4    | 2        | 0        |     |     |

| ...          |      |          |          |     |     |

| ...          |      |          |          |     |     |

【図12】

|          | 処理後取出待ち上限 |

|----------|-----------|

| Prewet   | 30        |

| Presoak  | 30        |

| PlatingA | 5         |

| PlatingB | 5         |

【図13】

| No. | レシピID | ユニットレシピ選択 |         |          |          |      |      |

|-----|-------|-----------|---------|----------|----------|------|------|

|     |       | Prewet    | Presoak | PlatingA | PlatingB | Blow | SRD  |

| 1   | ABC   | STD       | —       | —        | STD      | STD  | STD  |

| 2   | XYZ   | TEST      | TEST    | TEST     | —        | TEST | TEST |

| ~   |       |           |         |          |          |      |      |

【図14】

| レシピID  | 処理時間 |

|--------|------|

| Prewet | STD  |

|        | TEST |

| レシピID   | 処理時間 |

|---------|------|

| Presoak | STD  |

|         | TEST |

| レシピID    | 処理時間 |

|----------|------|

| PlatingA | 500s |

|          | TEST |

| レシピID    | 処理時間 |

|----------|------|

| PlatingB | 500s |

|          | TEST |

| レシピID | 処理時間 |

|-------|------|

| Blow  | 30s  |

|       | TEST |

| レシピID | 処理時間 |

|-------|------|

| SRD   | 30s  |

|       | TEST |

【図15】

【図16】

【図17】

【図18】

---

フロントページの続き

(72)発明者 三ツ谷 隆

東京都大田区羽田旭町11番1号 株式会社荏原製作所内

(72)発明者 小泉 竜也

東京都大田区羽田旭町11番1号 株式会社荏原製作所内

(72)発明者 大石 邦夫

東京都大田区羽田旭町11番1号 株式会社荏原製作所内

審査官 内田 正和

(56)参考文献 特開平10-031504(JP,A)

特開2011-243812(JP,A)

特開2015-060566(JP,A)

特開2015-005085(JP,A)

特開2011-146448(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/677

G05B 19/418

H01L 21/02