(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4141581号

(P4141581)

(45) 発行日 平成20年8月27日(2008.8.27)

(24) 登録日 平成20年6月20日(2008.6.20)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G06F 12/00 560A

請求項の数 8 (全 25 頁)

(21) 出願番号 特願平11-98019

(22) 出願日 平成11年4月5日(1999.4.5)

(65) 公開番号 特開2000-293427(P2000-293427A)

(43) 公開日 平成12年10月20日(2000.10.20)

審査請求日 平成17年8月11日(2005.8.11)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 將行

最終頁に続く

(54) 【発明の名称】 フラッシュメモリを搭載する記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ホストシステムから外部書込アドレス信号と外部書込データとを受けてデータ記憶を行う書込モードを備える記憶装置であって、

外部書込データ容量より容量の大きい内部書込データ容量を単位として複数のデータの書込がなされるフラッシュメモリを備え、

前記フラッシュメモリは、前記書込モードにおいて、内部書込アドレス信号を受けて、内部書込データに含まれる複数のデータを取り込み保持し、

前記書込モードにおいて、前記外部書込アドレス信号を受けて前記内部書込アドレス信号を発生し、前記外部書込データを受けて保持して前記外部書込データと前記外部書込アドレス信号とに基づいて前記内部書込データを出力するデータ入出力部をさらに備え、

前記データ入出力部は、

前記書込モードにおいて、前記ホストシステムから前記外部書込データおよび前記外部書込アドレス信号を受ける第1のインターフェイス部と、

前記外部書込データ容量以上で、かつ、前記内部書込データ容量より小さい記憶容量を有し、前記書込モードにおいて前記第1のインターフェイス部から前記外部書込データを受け取る、バッファメモリと、

前記書込モードにおいて、前記第1のインターフェイス部から前記外部書込アドレス信号を受けて前記内部書込アドレス信号を発生し、前記バッファメモリから読出した前記外部書込データに、前記フラッシュメモリを構成するメモリセルの消去状態に対応するデータ

10

20

を加えて前記内部書込データを発生する、第2のインターフェイス部とを含む、フラッシュメモリを搭載する記憶装置。

【請求項2】

前記フラッシュメモリは、前記内部書込アドレス信号に対応し、前記内部書込データ容量と同じ容量を持つメモリ領域単位を有し、前記メモリ領域単位はオフセット信号に対応する複数の領域を含み、

前記第2のインターフェイス部は、前記外部書込アドレス信号に含まれる前記オフセット信号を出力し、前記外部書込データに対応する前記内部書込データを前記メモリ領域単位の前記オフセット信号に対応する領域に書き込む、請求項1に記載のフラッシュメモリを搭載する記憶装置。

10

【請求項3】

前記第2のインターフェイス部は、前記メモリ領域単位の前記外部書込データに対応する前記内部書込データを書き込んだ残りの領域に、前記フラッシュメモリを構成するメモリセルの消去状態に対応するデータを書き込む、請求項2に記載のフラッシュメモリを搭載する記憶装置。

【請求項4】

前記内部書込データ容量は、前記外部書込データ容量の整数倍である、請求項3に記載のフラッシュメモリを搭載する記憶装置。

【請求項5】

前記フラッシュメモリは、クロックに同期して前記内部書込データを順次読み込み、

20

前記第2のインターフェイス部は、

前記バッファメモリに対する読み出制御信号を発生して前記バッファメモリから前記外部書込データを受けて前記内部書込データを発生し、前記外部書込アドレス信号から前記内部書込アドレス信号を発生する、データ転送制御部を有し、

前記データ転送制御部は、

前記フラッシュメモリに前記内部書込データの書き込みが開始されるときに、前記クロックのカウントを開始するカウンタと、

前記外部書込アドレス信号に含まれるオフセット信号と前記カウンタのカウント値の上位から所定数ビットとが一致した時に一致信号を出力する比較器と、

前記バッファメモリが前記クロックに同期して前記外部書込データを出力するように前記一致信号に応じて読み出制御信号を前記バッファメモリに与えるゲート回路と、

30

前記一致信号が非活性化されている時は、前記フラッシュメモリを構成するメモリセルの消去状態に対応するデータを前記フラッシュメモリに与え、前記一致信号が活性化した時は前記バッファメモリから読み出された前記外部書込データを前記フラッシュメモリに与える選択回路とを有する、請求項2に記載のフラッシュメモリを搭載する記憶装置。

【請求項6】

前記記憶装置は、前記ホストシステムから外部読み出アドレス信号を受けて前記ホストシステムに外部読み出データを出力する読み出モードをさらに備え、

前記データ入出力部は、前記読み出モード時に、前記外部読み出アドレス信号を受けて内部読み出アドレス信号を発生して前記フラッシュメモリに与え、前記フラッシュメモリから読み出される内部読み出データの一部を選択して前記外部読み出データとして保持した後、前記ホストシステムに対して前記外部読み出データを出力し、

40

前記第1のインターフェイス部は、前記読み出モード時に、前記ホストシステムから受けた前記外部読み出アドレス信号に応じた前記外部読み出データを前記ホストシステムに出力し、

前記バッファメモリは、前記外部読み出データ容量以上で、かつ、前記内部読み出データ容量より小さい記憶容量を有し、前記読み出モード時に、前記第1のインターフェイス部に対して保持していた前記外部読み出データを出力し、

前記第2のインターフェイス部は、前記読み出モード時に、前記第1のインターフェイス部から前記外部読み出アドレス信号を受けて前記内部読み出アドレス信号を発生して前記フラッシュメモリに与えて前記フラッシュメモリから前記内部読み出データが含む複数のデータを読

50

出し、前記内部読み出しデータの一部を前記外部読み出データとしてバッファメモリに送出する、請求項1に記載のフラッシュメモリを搭載する記憶装置。

#### 【請求項7】

前記フラッシュメモリは、クロックに同期して前記内部読み出データを順次出力し、

前記第2のインターフェイス部は、

前記外部読み出アドレス信号から前記内部読み出アドレス信号を発生し、前記内部読み出データの一部を選択して前記外部読み出データとして前記バッファメモリが格納するように前記バッファメモリへ書き込み制御信号を発生する、データ転送制御部を有し、

前記データ転送制御部は、

前記フラッシュメモリから前記内部読み出データの読み出しが開始されるときに、前記クロックのカウントを開始するカウンタと、

前記外部書き込みアドレス信号に含まれるオフセット信号と前記カウンタのカウント値の上位から所定数ビットとが一致した時に一致信号を出力する比較器と、

前記バッファメモリが前記クロックに同期して前記内部読み出データの一部を前記外部読み出データとして格納するように前記一致信号に応じて前記書き込み制御信号を前記バッファメモリに与えるゲート回路とを有する、請求項6に記載のフラッシュメモリを搭載する記憶装置。

#### 【請求項8】

フラッシュメモリと、

ホストシステムから入力される外部アドレスに対応する内部主アドレスおよび内部副アドレスを発生し、前記ホストシステムから入力される外部データを前記フラッシュメモリに出力、または前記フラッシュメモリから入力されるデータを前記外部データとしてホストシステムへ出力する、データ入出力部とを備え、

前記データ入出力部は、

前記内部主アドレスによって前記フラッシュメモリの前記外部データの容量より大きい容量を持つメモリ領域単位を選択し、前記内部副アドレスによって前記メモリ領域単位内のデータ入出力開始位置を指定し、前記データ入出力開始位置から前記フラッシュメモリのデータ読み出しが、または前記データ入出力開始位置から前記フラッシュメモリへのデータの書き込みを行い、

前記データ入出力部は、

前記ホストシステムと前記フラッシュメモリとの間のタイミング調整のために前記外部データを一時的に保持するバッファメモリを含み、

前記バッファメモリの記憶容量は、前記外部データの容量以上で、前記メモリ領域単位の容量より小さい、フラッシュメモリを搭載する記憶装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、記憶装置に関し、より特定的には、フラッシュメモリを搭載する記憶装置に関する。

##### 【0002】

##### 【従来の技術】

近年、半導体製造技術の進歩に伴い、フラッシュメモリの記憶容量も大きくなっている。この大容量化に伴い、小型でかつ低消費電力である特性を生かして特に携帯機器の分野においては記録メディアとしてフラッシュメモリを搭載した記憶装置が使用されるようになってきた。

##### 【0003】

##### 【発明が解決しようとする課題】

フラッシュメモリは、不揮発性で、一括消去後再書きができる半導体記憶装置である。フラッシュメモリは、高密度に記憶素子を集積し、かつ、高速にデータ授受をするため、セクタアドレスを指定して一定量のデータをセクタ単位で読み出、消去、書き込み（プログラム）

10

20

30

40

50

を一括して行う。フラッシュメモリの大容量化に伴い、フラッシュメモリが一括してデータを読出す単位であるセクタ容量も増加する傾向にあり、たとえば、256MビットのAND型フラッシュメモリではこのセクタ容量は2048バイトになっている。

【0004】

一方、パーソナルコンピュータを初めとする情報機器がハードディスクやメモリカード等の記憶装置とデータ授受を行なう際の単位のデータ容量（本明細書中では以降メディアセクタ容量と称する）は、たとえば、標準的には512バイトであり、このメディアセクタ容量は特に増加する傾向は見られない。

【0005】

このような、セクタ構造を持ったフラッシュメモリを搭載する記憶装置では、フラッシュメモリのセクタデータを一時的に格納し、ホストシステムとのデータ転送を行なうためのタイミングおよび容量の調整を行なうためのバッファメモリを記憶装置の内部に搭載する必要がある。このバッファメモリは通常SRAM（Static Random Access Memory）等が用いられる。

10

【0006】

ホストシステムとのデータ転送の容量、すなわちメディアセクタ容量が、フラッシュメモリのセクタ容量よりも小容量である場合でも、バッファメモリの容量は、フラッシュメモリのセクタ容量と同容量もしくはそれ以上の容量にする必要があった。

【0007】

しかしながら、フラッシュメモリのセクタ容量が年々大容量化しつつあり、このような場合には、バッファメモリとして大容量のSRAMを搭載する必要があり、コスト的にデメリットが生じていた。

20

【0008】

本発明は、このような問題点を解決するようになされたもので、その目的は、メディアセクタ容量に相当する小容量のバッファメモリを搭載することを可能にし、コストダウンを図ったフラッシュメモリを搭載する記憶装置を提供することである。

【0009】

【課題を解決するための手段】

この発明は、ある局面においては、ホストシステムから外部書込アドレス信号と外部書込データとを受けてデータ記憶を行う書込モードを備える記憶装置であって、外部書込データ容量より容量の大きい内部書込データ容量を単位として複数のデータの書込がなされるフラッシュメモリを備え、フラッシュメモリは、書込モードにおいて、内部書込アドレス信号を受けて、内部書込データに含まれる複数のデータを取り込み保持し、書込モードにおいて、外部書込アドレス信号を受けて内部書込アドレス信号を発生し、外部書込データを受けて保持して外部書込データと外部書込アドレス信号とに基づいて内部書込データを出力するデータ入出力部をさらに備え、データ入出力部は、書込モードにおいて、ホストシステムから外部書込データおよび外部書込アドレス信号を受ける第1のインターフェイス部と、外部書込データ容量以上で、かつ、内部書込データ容量より小さい記憶容量を有し、書込モードにおいて第1のインターフェイス部から外部書込データを受け取る、バッファメモリと、書込モードにおいて、第1のインターフェイス部から外部書込アドレス信号を受けて内部書込アドレス信号を発生し、バッファメモリから読出した外部書込データに、フラッシュメモリを構成するメモリセルの消去状態に対応するデータを加えて内部書込データを発生する、第2のインターフェイス部とを含む。

30

【0010】

好ましくは、フラッシュメモリは、内部書込アドレス信号に対応し、内部書込データ容量と同じ容量を持つメモリ領域単位を有し、メモリ領域単位はオフセット信号に対応する複数の領域を含み、第2のインターフェイス部は、外部書込アドレス信号に含まれるオフセット信号を出力し、外部書込データに対応する内部書込データをメモリ領域単位のオフセット信号に対応する領域に書き込む。

40

【0011】

50

より好ましくは、第2のインターフェイス部は、メモリ領域単位の外部書込データに対応する内部書込データを書き込んだ残りの領域に、フラッシュメモリを構成するメモリセルの消去状態に対応するデータを書き込む。

【0012】

さらに好ましくは、内部書込データ容量は、外部書込データ容量の整数倍である。

【0013】

より好ましくは、フラッシュメモリは、クロックに同期して内部書込データを順次取込み、第2のインターフェイス部は、バッファメモリに対する読出制御信号を発生してバッファメモリから外部書込データを受けて内部書込データを発生し、外部書込アドレス信号から内部書込アドレス信号を発生する、データ転送制御部を有し、データ転送制御部は、フラッシュメモリに内部書込データの書き込みが開始されるときに、クロックのカウントを開始するカウンタと、外部書込アドレス信号に含まれるオフセット信号とカウンタのカウント値の上位から所定数ビットとが一致した時に一致信号を出力する比較器と、バッファメモリがクロックに同期して外部書込データを出力するように一致信号に応じて読出制御信号をバッファメモリに与えるゲート回路と、一致信号が活性化されている時は、フラッシュメモリを構成するメモリセルの消去状態に対応するデータをフラッシュメモリに与え、一致信号が活性化した時はバッファメモリから読出された外部書込データをフラッシュメモリに与える選択回路とを有する。

10

【0014】

好ましくは、記憶装置は、ホストシステムから外部読出アドレス信号を受けてホストシステムに外部読出データを出力する読出モードをさらに備え、データ入出力部は、読出モード時に、外部読出アドレス信号を受けて内部読出アドレス信号を発生してフラッシュメモリに与え、フラッシュメモリから読出される内部読出データの一部を選択して外部読出データとして保持した後、ホストシステムに対して外部読出データを出力し、第1のインターフェイス部は、読出モード時に、ホストシステムから受けた外部読出アドレス信号に応じた外部読出データをホストシステムに出力し、バッファメモリは、外部読出データ容量以上で、かつ、内部読出データ容量より小さい記憶容量を有し、読出モード時に、第1のインターフェイス部に対して保持していた外部読出データを出力し、第2のインターフェイス部は、読出モード時に、第1のインターフェイス部から外部読出アドレス信号を受けて内部読出アドレス信号を発生してフラッシュメモリに与えてフラッシュメモリから内部読出データが含む複数のデータを読み出し、内部読出しデータの一部を外部読出データとしてバッファメモリに送出する。

20

【0018】

好ましくは、フラッシュメモリは、クロックに同期して内部読出データを順次出力し、第2のインターフェイス部は、外部読出アドレス信号から内部読出アドレス信号を発生し、内部読出データの一部を選択して外部読出データとしてバッファメモリが格納するようにバッファメモリへ書き込み制御信号を発生する、データ転送制御部を有し、データ転送制御部は、フラッシュメモリから内部読出データの読み出しが開始されるときに、クロックのカウントを開始するカウンタと、外部書込アドレス信号に含まれるオフセット信号とカウンタのカウント値の上位から所定数ビットとが一致した時に一致信号を出力する比較器と、バッファメモリがクロックに同期して内部読出データの一部を外部読出データとして格納するように一致信号に応じて書き込み制御信号をバッファメモリに与えるゲート回路とを有する。

30

【0019】

この発明は他の局面では、フラッシュメモリを搭載する記憶装置であって、フラッシュメモリと、ホストシステムから入力される外部アドレスに対応する内部主アドレスおよび内部副アドレスを発生し、ホストシステムから入力される外部データをフラッシュメモリに出力、またはフラッシュメモリから入力されるデータを外部データとしてホストシステムへ出力する、データ入出力部とを備え、データ入出力部は、内部主アドレスによってフラッシュメモリの外部データの容量より大きい容量を持つメモリ領域単位を選択し、内部副アドレスによってメモリ領域単位内のデータ入出力開始位置を指定し、データ入出力開

40

50

始位置からフラッシュメモリのデータ読出、またはデータ入出力開始位置からフラッシュメモリへのデータの書き込みを行う。

【0020】

好ましくは、データ入出力部は、ホストシステムとフラッシュメモリとの間のタイミング調整のために外部データを一時的に保持するバッファメモリを含み、バッファメモリの記憶容量は、外部データの容量以上で、メモリ領域単位の容量より小さい。

【0021】

【発明の実施の形態】

以下図面を参照しつつ、本発明の実施の形態について詳しく説明する。なお、図中同一符号は、同一または相当部分を示す。

10

【0022】

[実施の形態1]

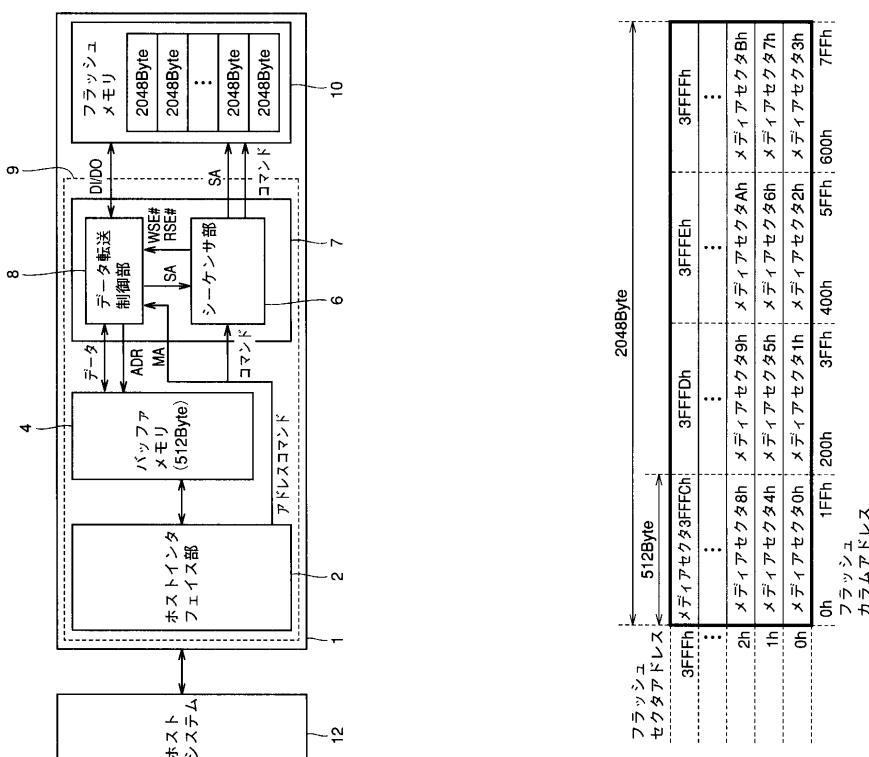

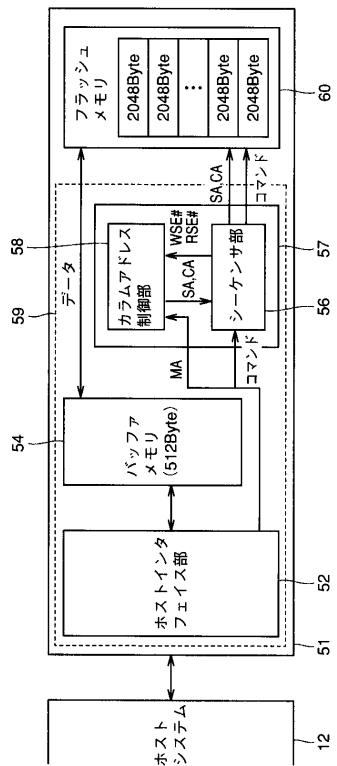

図1は、フラッシュメモリを搭載した記憶装置1の概略構成を示すブロック図である。

【0023】

図1を参照して、記憶装置1は、ホストシステム12と記憶する外部データの授受を行うためのものであり、ホストシステムからメディアアドレスを受けてアドレス変換を行い、ホストシステムとの間で外部データを授受するためにデータ変換を行うデータ入出力部9と、データ入出力部9が変換したアドレス信号に応じてデータ授受を行うフラッシュメモリ10とを含む。データ入出力部9はフラッシュメモリ10が入出力するデータと外部データとの間のデータの変換を行う。

20

【0024】

データ入出力部9は、ホストシステムとデータ転送を行なうホストインターフェイス部2と、ホストインターフェイス部2がホストシステム12とデータ転送を行なうためにフラッシュメモリのセクタデータの一部を一時的に格納する512バイトの容量を持つバッファメモリ4と、ホストインターフェイス部2からの指令に応じてバッファメモリ4とフラッシュメモリとのデータ授受のコントロールを行なうフラッシュインターフェイス部7と、記憶装置1が記憶すべきデータを保持する半導体装置であるフラッシュメモリ10とを含む。

【0025】

フラッシュインターフェイス部7は、フラッシュメモリの仕様にあわせたシーケンスで、読み出や書き込み等の動作を設定するコマンドや、読み出や書き込み時にメモリ領域を指定するためのアドレスをフラッシュメモリに送出するシーケンサ部6と、ホストシステム12から与えられたメディアセクタアドレスからフラッシュメモリのセクタアドレスおよびカラムアドレスオフセットを生成するデータ転送制御部8とを含む。

30

【0026】

フラッシュメモリ10は、各々が2048バイトの容量を持つ複数のセクタを有する。フラッシュメモリ10は、セクタアドレスが指定されると、指定されたセクタに記憶されている2048バイトのデータをシリアルに出力することができる。

【0027】

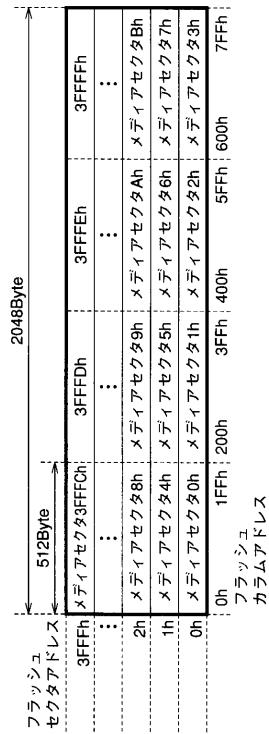

図2は、実施の形態1におけるフラッシュメモリとバッファメモリとのアドレスの対応関係を示すメモリマップである。

40

【0028】

図2を参照して、メディアセクタ容量、すなわち記憶装置1が一括してデータ授受を行なうセクタ容量が512バイト、フラッシュメモリ10の1セクタが2048バイトである場合のメモリアップであり、フラッシュメモリ10の1/4セクタをメディアセクタとして割当てている。

【0029】

たとえば、メディアセクタアドレス0hは、フラッシュセクタアドレス0hのフラッシュカラムアドレス0h~1FFhに相当する。メディアセクタアドレス1hは、フラッシュセクタアドレス0hのフラッシュカラムアドレス200h~3FFhに相当する。同様に、メディアセクタアドレス2hは、フラッシュセクタアドレス0hのフラッシュカラムア

50

ドレス 400h ~ 5FFh に相当する。メディアセクタアドレス 3h は、フラッシュセクタアドレス 0h のフラッシュカラムアドレス 600h ~ 7FFh に相当する。つまり、各フラッシュセクタアドレスはそれぞれ 4 分割され、メディアセクタアドレスに割当てられている。

【0030】

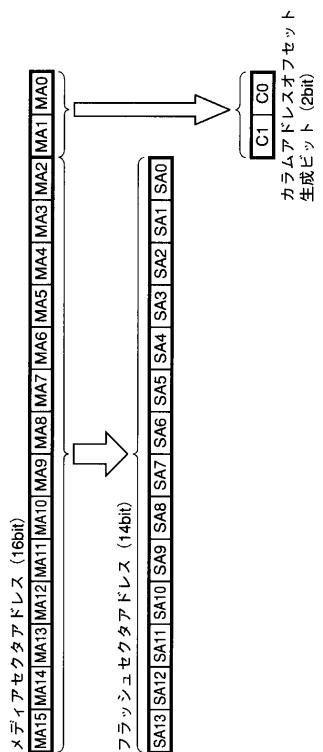

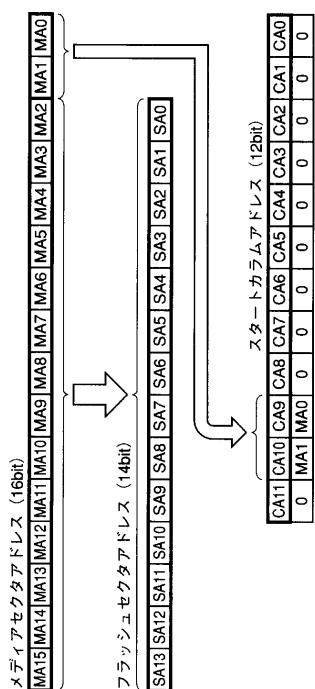

図3は、メディアセクタアドレスをフラッシュセクタアドレスとカラムアドレスオフセット生成ビットとに変換する説明をするための図である。

【0031】

図3を参照して、メディアセクタアドレス MA15 ~ MA0 の上位 14 ビットは、フラッシュセクタアドレス SA13 ~ SA0 として使用される。また、メディアセクタアドレスのうち下位 2 ビットである MA1、MA0 は、カラムアドレスオフセット生成ビット C1、C0 として使用され、このカラムアドレスオフセット生成ビットから後に説明するスタートフラッシュカラムアドレスオフセットを発生する。

10

【0032】

図4は、スタートフラッシュカラムアドレスオフセットとメディアセクタアドレスの下位 2 ビットとの関係を示す図である。

【0033】

図4を参照して、MA1、MA0 がともに 0 であるときは、スタートフラッシュカラムアドレスオフセットは 0h に設定され、メディアセクタ容量である 512 バイトのデータの授受がバッファメモリとフラッシュメモリとの間で行なわれる。

20

【0034】

MA1、MA0 がそれぞれ、0、1 であるときは、スタートフラッシュカラムアドレスオフセットは 200h に設定され、バッファメモリとフラッシュメモリとの間のデータ授受が行なわれる。

【0035】

MA1、MA0 がそれぞれ 1、0 の場合には、スタートフラッシュカラムアドレスオフセットは 400h に設定され、バッファメモリとフラッシュメモリとの間でデータ授受が行なわれる。

【0036】

MA1、MA0 がともに 1 であるときは、スタートフラッシュカラムアドレスオフセットは 600h に設定され、バッファメモリとフラッシュメモリとの間のデータ授受が行なわれる。

30

【0037】

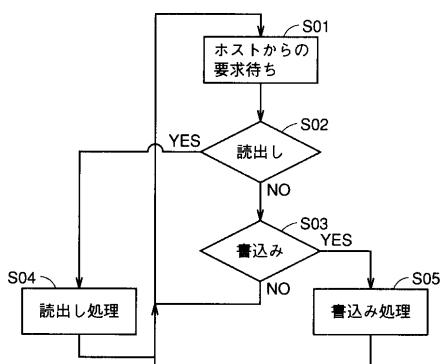

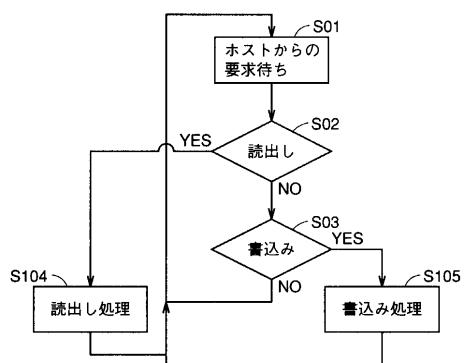

図5は、実施の形態1の記憶装置の処理のメインフローを示す図である。

図5を参照して、ステップ S01 は、ホストシステムからの要求待ちのステップである。続いて、ステップ S02 において、読み出の要求があったか否かが判断される。読み出要求があった場合には、ステップ S04 に移り、読み出処理が行なわれる。読み出処理が完了すると、再び、ステップ S01 に戻りホストシステムからの要求待ち状態となる。

【0038】

ステップ S02 において、読み出要求が行なわれていない場合には、ステップ S03 に進む。ステップ S03 では、ホストシステムから書き込み要求が行なわれていないかどうかが判断される。書き込み要求があった場合には、ステップ S05 に進み、書き込み処理が行なわれる。書き込み処理が完了すると、再び、ステップ S01 に進みホストシステムからの要求待ち状態となる。

40

【0039】

ステップ S03 において、書き込み要求が行なわれなかった場合には、再び、ステップ S01 に戻り、ホストシステムからの要求待ち状態となる。

【0040】

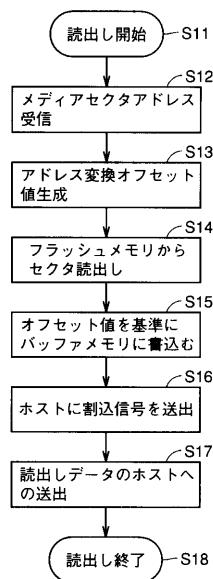

図6は、図5に示したステップ S04 の読み出処理の詳細を示すフローチャートである。

【0041】

50

図6を参照して、ステップS11において、読み出しが開始される。

次いで、ステップS12において、メディアセクタアドレスがホストシステムから受信される。続いて、受信したメディアセクタアドレスをもとにアドレス変換が行なわれ、図4で示したスタートフラッシュカラムアドレスオフセットの値が生成される。

【0042】

続いてステップS14において、フラッシュメモリからセクタ読み出しが行なわれる。そして読み出されたデータは、ステップS15において、オフセット値に基づきバッファメモリに書込まれる。続いてステップS16において、ホストシステムに割込み信号を送出し、ステップS17において、バッファメモリに書込まれたデータをホストシステムに対して読み出しだとして送出する。そしてステップS18において、読み出しが終了する。

10

【0043】

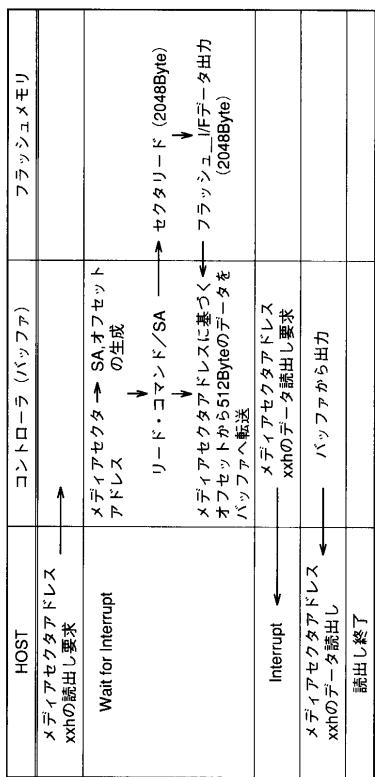

図7は、図6に示した読み出しが記憶装置内のどのブロックで実施されているかを示す図である。

【0044】

図7を参照して、まずホストシステムからコントローラやバッファメモリに対してメディアセクタアドレスの読み出しが発信される。コントローラというのは、図1におけるホストインターフェイス部2およびフラッシュインターフェイスシーケンサ部6に該当する。

【0045】

これを受けて、コントローラではメディアセクタアドレスからフラッシュメモリのセクタアドレスSAとオフセット値の生成がされる。そして、フラッシュメモリに対してリードコマンドとセクタアドレスSAが発信される。応じて、フラッシュメモリではセクタリードが行なわれ2048バイトのデータが順次フラッシュインターフェイスデータ出力としてコントローラに送出される。これを受けてコントローラではメディアセクタアドレスに基づくオフセットに対応する512バイトのデータを抜き出してバッファメモリへと転送する。

20

【0046】

そしてバッファメモリへのデータの格納が終了すると、コントローラはホストシステムに対してメディアセクタアドレスのデータ読み出しが行なわれないホストシステムは割込みを受ける。続いて、コントローラはバッファメモリからデータを出力しこれによりメディアセクタアドレスのデータ読み出しが行なわれる。そして読み出しが終了する。

30

【0047】

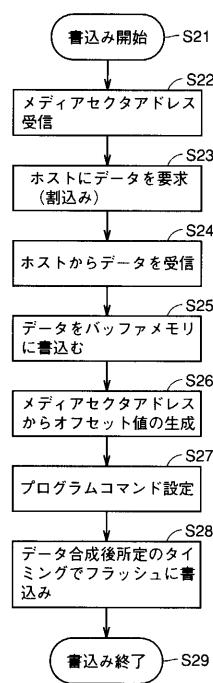

図8は、図5に示したステップS05における書き込み処理の詳細を示すフローチャートである。

【0048】

図8を参照して、まず、ステップS21において書き込みが開始される。

続いて、ステップS22においてホストシステムから発信されたメディアセクタアドレスが受信される。

【0049】

続いて、ステップS23において、記憶装置がホストシステムに対してデータを要求する。そして、ステップS24において、記憶装置がホストシステムからデータを受信する。このデータはステップS25において、バッファメモリに書き込まれる。

40

【0050】

そして、ステップS26において、ステップS22で受信したメディアセクタアドレスからオフセット値の生成がされる。その後、ステップS27においてフラッシュメモリに対するプログラムコマンドの設定がされる。続いて、ステップS28において、バッファメモリからのデータを初期値データと合成し所定のタイミングでフラッシュメモリに書きが行なわれる。

【0051】

そして、ステップS29において書き込みが終了する。

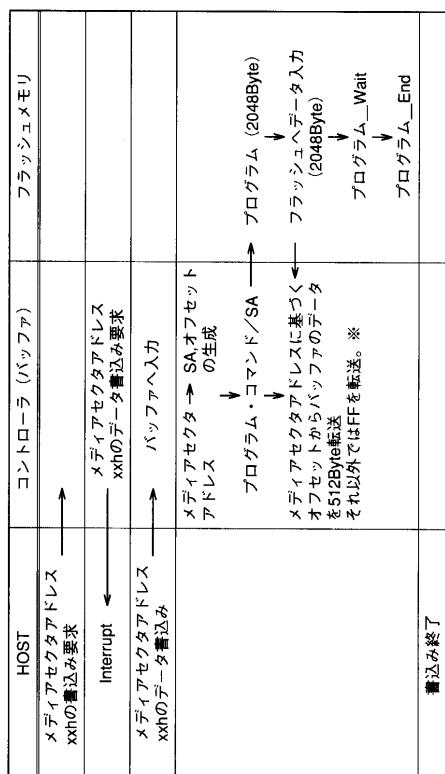

図9は、図8に示した書き込み処理の各ステップがホストシステムとコントローラおよびバッ

50

ファムモリとフラッシュメモリとの間でどのように行なわれるかを示す図である。

【0052】

図9を参照して、まずホストシステムからメディアセクタアドレスの書込要求がコントローラに向けて発信される。続いて、コントローラはこれを受けてメディアセクタアドレスへのデータ書込要求をホストシステムに対して行なう。応じてホストシステムはメディアセクタアドレスに対するデータの書込を行なう。このデータはコントローラを経由してバッファムモリに入力される。

【0053】

続いて、コントローラでは受信していたメディアセクタアドレスからフラッシュメモリのセクタアドレスおよびオフセット値の生成がされる。そして、フラッシュメモリに対するプログラムコマンドおよびセクタアドレスの発信がされる。

10

【0054】

これを受け、フラッシュメモリはデータ書込可能状態となる。そして、コントローラからの所定の信号に基づきバッファムモリからはオフセット値に基づいて格納されていた512バイトのデータが転送される。フラッシュメモリへの書込データが転送されている期間のうち、バッファムモリに格納されていたデータが転送される期間以外の書込データとしては“FFh”が転送される。フラッシュメモリへバッファムモリのデータを含む書込データが入力されると、その後、所定のウエイト時間経過後書込が終了する。

【0055】

ここで、書込みデータ“FFh”について説明する。

20

フラッシュメモリの各メモリセルは、フローティングゲートを有するMOSトランジスタで構成されている。各メモリセルはMOSトランジスタのしきい値電圧の状態でデータ“1”、“0”を保持している。一般に、メモリセルの消去直後の状態は、保持データ“1”に対応する。データ“0”的書込動作がされるとしきい値電圧が変化し、変化後のしきい値電圧を有するメモリセルの状態が保持データ“0”に対応する。一方、データ“1”的書込動作ではしきい値電圧は変化しない。このため、初期状態としてデータ“0”を保持しているメモリセルに対してデータ“1”的書込動作が行われても、保持データは変化しない。

【0056】

つまり、通常は、メモリセルデータの消去が行なわれてからデータの書込が行なわれるが、実施の形態1では、消去動作を行わずデータとして“FFh”を書込む。“FFh”はビットがすべて“1”的1バイトのデータであるため、フラッシュメモリは書込む直前のデータを保持するのである。

30

【0057】

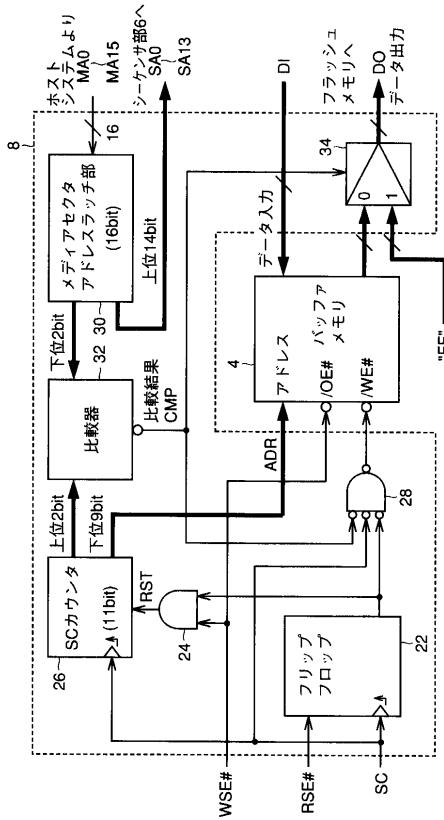

図10は、図1に示したデータ転送制御部8の詳細を示すブロック図である。図10を参照して、データ転送制御部8は、記憶装置内部で生成されるリードセクタネーブル信号RSEをクロック信号SCの立上がりに同期してラッチするフリップフロップ22と、フリップフロップ22の出力と記憶装置内部で生成されるライトセクタネーブル信号WSEとの論理和をリセット信号RSTとして出力するAND回路24と、リセット信号RSTによってリセットされその後クロック信号SCの立上がりに応答してカウントアップを開始するSCカウンタ26と、ホストシステムより16ビットのメディアセクタアドレスをラッチして上位14ビットをシーケンサ部6へセクタアドレスSA0～SA15として出力するメディアセクタアドレスラッチ部30と、SCカウンタ26の出力である11ビットの計数値のうち上位2ビットとメディアセクタアドレスラッチ部30がラッチしたメディアセクタアドレスの下位2ビットとを比較する比較器32とを含む。

40

【0058】

比較器32は、SCカウンタ26からの2ビットのデータとメディアセクタアドレスラッチ部30からの2ビットのデータとが一致したときにLレベルとなる比較結果信号をCMPを出力する。

【0059】

50

データ転送制御部 8 は、さらに、フリップフロップ 22 の出力とクロック信号 S C と結果信号 C M P を受けてライトイネーブル信号 / W E を出力するゲート回路 28 と、バッファメモリ 4 からの出力と固定データ “ F F h ” とを受けて比較結果信号 C M P に応じてフラッシュメモリに対して出力するセレクタ 34 とを含む。セレクタ 34 は、比較信号 C M P が L のときはバッファメモリからの出力をフラッシュメモリに対して出力し、比較信号 C M P が H のときは固定データ “ F F h ” をフラッシュメモリに対して出力する。

#### 【 0 0 6 0 】

尚、説明の便宜のため、図 10 にはバッファメモリ 4 が記載されている。バッファメモリ 4 は、S C カウンタ 26 の 11 ビットの計数値のうちの下位 9 ビットをアドレス信号 A D R として受け、ライトセクタイネーブル信号 W S E をアウトプットイネーブル信号 / O E として受け、ゲート回路 28 の出力をライトイネーブル信号 / W E として受けこれらに応答してフラッシュメモリからのデータ入力 D I を受けて保持し、またはセレクタ 34 を介してフラッシュメモリへデータ出力 D O を送出する。

#### 【 0 0 6 1 】

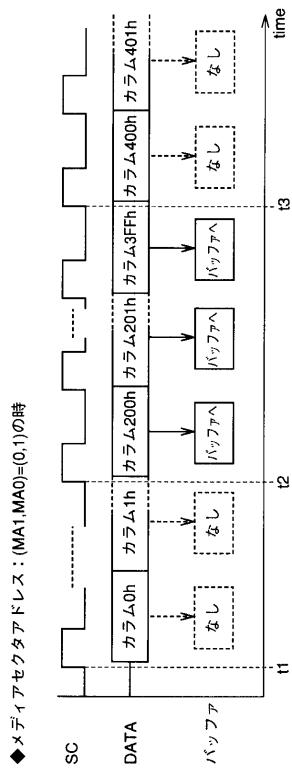

図 11 は、フラッシュメモリからバッファメモリへのデータ転送の様子を示すタイミング図である。

#### 【 0 0 6 2 】

図 11 を参照して、時刻 t 1 からクロック信号 S C に応じてデータ信号 D A T A がフラッシュメモリから読出される。この読出は、セクタ単位で行なわれるため、通常は 2048 データが連続して以後読出される。

#### 【 0 0 6 3 】

ここで、ホストシステムから指定されたメディアセクタアドレスのうち最下位の 2 ビットである ( M A 1 , M A 0 ) が ( 0 , 1 ) のときには時刻 t 1 ~ t 2 においては、フラッシュメモリから読出されたデータはバッファメモリへは転送されない。

#### 【 0 0 6 4 】

そして、時刻 t 2 ~ t 3 において、カラムアドレス 200 h ~ 3 F F h に相当するデータがフラッシュメモリから読出されている間は、これらのデータはバッファメモリへと転送されて保持される。この保持されるデータは、フラッシュメモリから読出されるセクタ容量 2048 バイトのうちの 512 バイトであり、セクタ容量の 4 分の 1 である。

#### 【 0 0 6 5 】

時刻 t 3 以降は、カラムアドレス 400 h 以降のデータが順次読出されるが、これらはバッファメモリへは保持されることはない。

#### 【 0 0 6 6 】

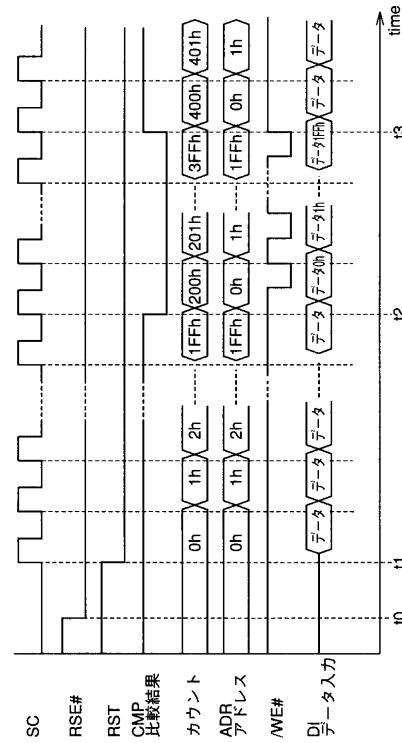

図 12 は、図 11 に示したバッファメモリへのデータ書き込み動作をより詳細に示した動作波形図である。

#### 【 0 0 6 7 】

図 10 、図 12 を参照して、時刻 t 0 において、ホストシステムから読出要求が行なわれたことに応じて、リードセクタイネーブル信号 R S E が H レベルから L レベルへと立下がる。続いて、時刻 t 1 においてリセット信号 R S T が H レベルから L レベルへと立下がり、S C カウンタ 26 のリセットが解除される。以降、時刻 t 1 ~ t 2 において、クロック信号 S C の入力に応じて S C カウンタ 26 は 11 ビットのカウント値を 0 h から 1 F F h までカウントアップする。カウント値の下位 9 ビットであるバッファメモリに入力されるアドレス信号 A D R は、同様に 0 h から 1 F F h まで変化する。このとき、比較器 32 に入力されるカウント値の上位 2 ビットは ( 0 , 0 ) であり、メディアセクタアドレスラッチ部 30 からの 2 ビットの入力は ( 0 , 1 ) であるため、比較結果信号 C M P は不一致を示す H レベルである。そのため、データ入力信号 D I の内容は、時刻 t 1 ~ t 2 においては、バッファメモリ 4 に書き込まれることはない。

#### 【 0 0 6 8 】

時刻 t 2 において、S C カウンタ 26 のカウント値が 200 h になり、カウント値の上位 2 ビットがメディアセクタアドレスラッチ部 30 から入力される 2 ビットの信号と一致す

10

20

30

40

50

る。応じて、比較結果信号 C M P が H から L レベルへと立下がる。すなわち、そして、比較結果信号 C M P は、カウント値が 2 0 0 h ~ 3 F F h である間 L レベルとなる。この比較結果信号 C M P の変化に応じて、ゲート回路 2 8 がクロック信号 S C をライトイネーブル信号 / W E としてバッファメモリに対して出力する。バッファメモリ 4 は、ライトイネーブル信号 / W E が入力されるため、ライトイネーブル信号 / W E の立上がりエッジにおけるアドレス信号 A D R が示すアドレスにデータ入力であるデータ 0 h ~ データ 1 F F h が書込まれる。

【 0 0 6 9 】

時刻 t 3 以降においては、 S C カウンタ 2 6 のカウント値が 4 0 0 h 以上となるため、比較結果信号 C M P は再び H レベルになり、以降入力されるデータはバッファメモリへは書込まれない。

10

【 0 0 7 0 】

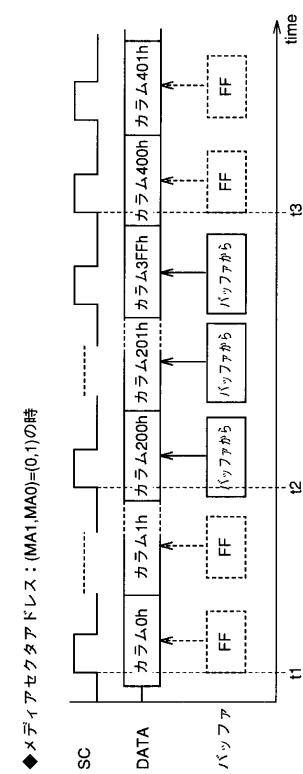

図 1 3 は、バッファメモリからフラッシュメモリへのデータ転送の様子を示すタイミング図である。

【 0 0 7 1 】

図 1 3 を参照して、メディアセクタアドレス ( M A 1 , M A 0 ) が ( 0 , 1 ) のときには、時刻 t 1 ~ t 2 において、フラッシュメモリのカラムアドレス 0 h ~ 1 F F h には、ダミーデータである “ F F h ” が書込まれる。このダミーデータは、フラッシュメモリの消去直後の初期値に対応するデータであり、一般に、フラッシュメモリはこの初期値データを書込む動作を行なっても既に内部に保持されているデータが破壊されることはない。

20

【 0 0 7 2 】

したがって、実施の形態 1 の記憶装置は、一括消去され、その後逐次データを追加していくような用途、例えば、デジタルカメラの画像の一時保存や、携帯型デジタルオーディオ機器の音響信号の保存等に好適に用いられる。

【 0 0 7 3 】

時刻 t 2 ~ t 3 において、フラッシュメモリのカラムアドレス 2 0 0 h ~ 3 F F h には、バッファメモリからデータが順次書込まれる。このデータはフラッシュメモリのセクタ容量の 1 / 4 に相当する 5 1 2 バイトのデータである。

30

【 0 0 7 4 】

時刻 t 3 以降は、時刻 t 1 ~ t 2 と同様に、ダミーデータである “ F F h ” が書込まれる。

【 0 0 7 5 】

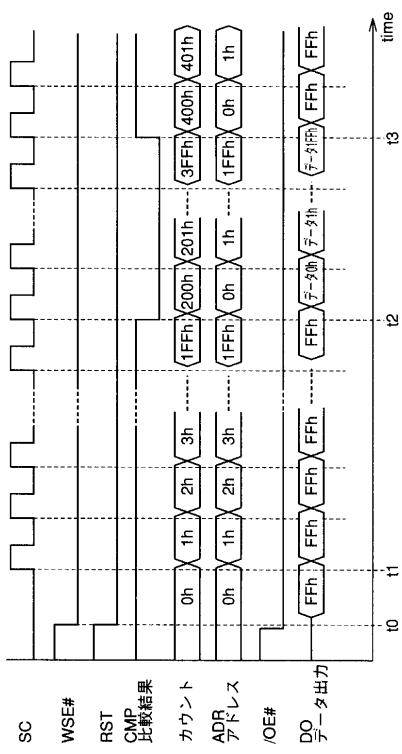

図 1 4 は、図 1 3 に示したバッファメモリからフラッシュメモリへのデータ転送の様子をさらに詳しく説明するための動作波形図である。

【 0 0 7 6 】

図 1 0 、図 1 4 を参照して、時刻 t 0 において、ホストシステムからの書込要求に応じてライトセクタイネーブル信号 W S E が H レベルから L レベルへと立下がる。応じて、リセット信号 R S T が H レベルから L レベルへと立下がり、 S C カウンタ 2 6 のリセットが解除される。また、バッファメモリのアウトプットイネーブル入力信号 / O E は H レベルから L レベルへと立下がり、バッファメモリ 4 は、アクセス可能な状態となる。

40

【 0 0 7 7 】

時刻 t 1 ~ t 2 において、クロック信号 S C の立上がりに同期して、セレクタ 3 4 が出力するデータ出力信号がフラッシュメモリへ書込まれる。そのときの書込カラムアドレスに対応するカウント値が S C カウンタ 2 6 によってカウントアップされる。時刻 t 1 ~ t 2 においてはメディアセクタアドレス ( M A 1 , M A 0 ) が S C カウンタ 2 6 の上位 2 ビットと一致しないので、データ出力信号 D O はセレクタ 3 4 の “ 1 ” 側の入力ノードに入力されている固定データ “ F F h ” である。

【 0 0 7 8 】

時刻 t 2 において、カウント値の変化に従って、比較結果信号 C M P は H レベルから L レベルへと立下がり、アドレス信号 A D R に指定されるアドレスのデータはバッファメモリ

50

4から読み出され、セレクタ34を介してデータ出力信号D0としてフラッシュメモリへと転送される。以降時刻t3に至るまでの間バッファメモリからフラッシュメモリへとデータ転送が行なわれる。

【0079】

データ0h～データ1Fhの512バイトのデータの転送が終了すると、時刻t3において、カウント値の変化に従い比較結果信号CMPがLレベルからHレベルへと立上がるため、再びデータ出力信号はセレクタ34の“1”側の入力ノードに入力されている固定値“FFh”となる。

【0080】

以上説明したように、実施の形態1の記憶装置は、一括消去され、その後逐次データを追加していくような用途、例えば、デジタルカメラの画像の一時保存や、携帯型デジタルオーディオ機器の音響信号の保存等に好適に用いられる。

10

【0081】

そして、使用するフラッシュメモリの1セクタの容量よりもホストシステムとのデータ転送の単位容量であるメディアセクタ容量が小さい場合に、一時的なデータ格納を行なうバッファメモリの容量をメディアセクタ容量に合わせて小さくすることができるため、ハードウェアを構成する上でコスト的に有利な記憶装置を提供することができる。

【0082】

【実施の形態2】

図15は、実施の形態2の記憶装置51の概略構成を示すブロック図である。

20

【0083】

図15を参照して、記憶装置51は、ホストシステム12と記憶する外部データの授受を行なうためのものであり、ホストシステムからメディアアドレスを受けてアドレス変換を行い、ホストシステムの間で外部データを授受するためにデータ変換を行うデータ入出力部59と、データ入出力部59が変換したアドレス信号に応じてデータ授受を行うフラッシュメモリ60とを含む。データ入出力部59はフラッシュメモリ60が入出力するデータと外部データとの間のデータの変換を行う。

【0084】

データ入出力部59は、ホストシステム12とデータ転送を行なうホストインターフェイス部52と、ホストインターフェイス部52がホストシステム12とデータ転送を行なうために記憶データを一時的に格納する512バイトの容量を持つバッファメモリ54と、ホストインターフェイス部52からの指令に応じてバッファメモリ54とフラッシュメモリ60とのデータ授受のコントロールを行なうフラッシュインターフェイス部57とを含む。

30

【0085】

フラッシュインターフェイス部57は、フラッシュメモリの仕様にあわせたシーケンスで、読み出や書き込等の動作を設定するコマンドや、読み出や書き込時にメモリ領域を指定するためのアドレスをフラッシュメモリに送出するシーケンサ部56と、ホストシステム12から与えられたメディアセクタアドレスからフラッシュメモリのセクタアドレスとセクタアドレスで指定されたカラムの読み出開始位置を指定するスタートカラムアドレスとを生成するカラムアドレス制御部58とを含む。

40

【0086】

図15において、フラッシュメモリ60は、データのリードおよびプログラムをセクタの任意のカラムアドレスから読み出や書き込開始をできる分割リード/プログラム機能を有する。

【0087】

フラッシュメモリ60は、各々が2048バイトの容量を持つ複数のセクタを有する。フラッシュメモリは、セクタアドレスが指定されると、指定されたセクタ容量分だけのデータをクロック信号に同期してシリアルに出力することができる。そして、スタートカラムアドレスがさらに指定されると、指定されたセクタのカラムアドレスに該当するデータからセクタの最終アドレスに該当するデータまでをクロック信号に同期してシリアルに出力

50

することができる。

【0088】

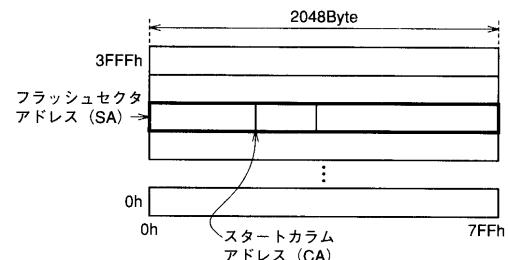

図16は、実施の形態2におけるフラッシュメモリとバッファメモリとの対応関係を示すメモリマップである。

【0089】

図16に示されるメモリマップは、図2に示した実施の形態1に用いられるメモリマップと同様の割付を示しているため説明は繰返さない。

【0090】

図17は、メディアセクタアドレスがフラッシュセクタアドレスとスタートカラムアドレスとに変換されることを説明するための図である。

10

【0091】

図17を参照して、メディアセクタアドレスMA15～MA0の上位14ビットは、フラッシュセクタアドレスSA13～SA0として使用される。また、メディアセクタアドレスのうち下位2ビットであるMA1、MA0は、スタートカラムアドレスのうちそれぞれCA10、CA9として使用される。また、スタートカラムアドレスの他のビットであるCA11、CA8～CA0はすべて“0h”に設定される。

【0092】

図18は、フラッシュメモリのスタートカラムアドレスとメディアセクタアドレスの下位2ビットとの関係を示す図である。

20

【0093】

図18を参照して、MA1、MA0がともに0であるときは、スタートカラムアドレスは0hに設定され、MA1、MA0がそれぞれ0、1であるときは、スタートカラムアドレスは200hに設定される。

【0094】

MA1、MA0がそれぞれ1、0であるときは、スタートカラムアドレスは400hに設定され、MA1、MA0がともに1であるときは、スタートカラムアドレスは600hに設定される。このアドレス変換は図15のカラムアドレス制御部58で行われるが、図18に対応する配線の接続をするだけで容易に実現できる。

【0095】

図19は、スタートカラムアドレスの説明をするための概念図である。

30

図19を参照して、1セクタが2048バイトであるときは、フラッシュセクタアドレスSAに対応して0h～7FFhのカラムアドレスが存在する。スタートカラムアドレスCAを設定すると、設定したフラッシュセクタアドレスSA中のスタートカラムアドレスに対応するカラムのデータからクロック信号に同期して読出が開始される。

【0096】

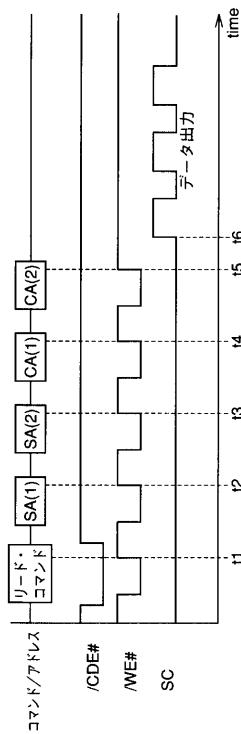

図20は、分割リード／プログラム機能を有するフラッシュメモリからデータを読出す際のコマンド設定とアドレス設定とを説明するための動作波形図である。

【0097】

図20を参照して、時刻t1において、コマンドデータイネーブル信号/CDEがLレベルのときに、ライトイネーブル信号/WEの立上がりが検出されると、そのタイミングにおいて、リードコマンドがフラッシュメモリに取込まれる。

40

【0098】

時刻t2において、ライトイネーブル信号/WEの立上がりエッジにおいて、セクタアドレスの下位8ビットであるSA(1)が取込まれる。次いで時刻t3において、ライトイネーブル信号/WEの立上がりエッジにおいて、セクタアドレスの上位6ビットであるSA(2)がフラッシュメモリに取込まれる。

【0099】

次いで、時刻t4において、ライトイネーブル信号/WEの立上がりエッジでスタートカラムアドレスCAの下位8ビットであるCA(1)がフラッシュメモリに取込まれる。

続いて、時刻t5において、ライトイネーブル信号/WEの立上がりエッジでスタート

50

カラムアドレスの上位 4 ビットである C A ( 2 ) が取込まれる。

【 0 1 0 0 】

時刻  $t_6$  以降は、クロック信号 S C に同期してアドレス / データ入出力端子から指定されたスタートカラムアドレスのデータを先頭にしてフラッシュメモリからデータが出力される。

【 0 1 0 1 】

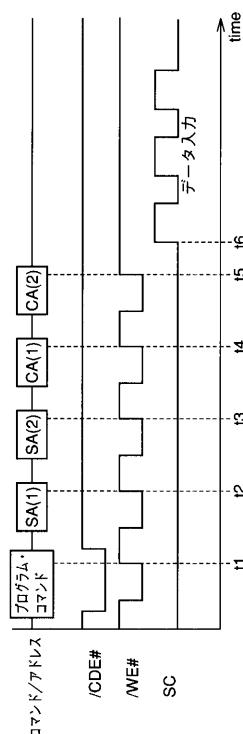

図 2 1 は、実施の形態 2 においてフラッシュメモリにデータを書込む入力波形を示す図である。

【 0 1 0 2 】

図 2 1 を参照して、時刻  $t_1$  において、コマンドデータイネーブル入力 / C D E が L レベルのときに、ライトイネーブル信号 / W E の立上がりエッジが検出されると、プログラムコマンドがフラッシュメモリに読み込まれる。 10

【 0 1 0 3 】

続いて、時刻  $t_2$  において、ライトイネーブル信号 / W E の立上がりエッジでセクタアドレスの下位 8 ビットである S A ( 1 ) がフラッシュメモリに取込まれる。続いて、時刻  $t_3$  において、ライトイネーブル信号 / W E の立上がりエッジでセクタアドレスの上位 6 ビットである S A ( 2 ) がフラッシュメモリに取込まれる。

【 0 1 0 4 】

時刻  $t_4$  において、ライトイネーブル信号 / W E の立上がりエッジでスタートカラムアドレスの下位 8 ビットである C A ( 1 ) がフラッシュメモリに取込まれる。続いて、時刻  $t_5$  において、ライトイネーブル信号 / W E の立上がりエッジでスタートカラムアドレスの上位 4 ビットである C A ( 2 ) がフラッシュメモリに取込まれる。以上でアドレス設定が終了する。 20

【 0 1 0 5 】

時刻  $t_6$  以降は、設定されたセクタアドレスのスタートカラムアドレスに対応するデータを先頭としてクロック信号 S C に同期してシリアルにデータ入力がされ対応するアドレスにデータが書込まれる。

【 0 1 0 6 】

図 2 0 、図 2 1 で示したフラッシュメモリに対するコマンドやアドレス信号を与える制御は、図 1 5 におけるフラッシュインタフェイスシーケンサ部 5 6 で行なわれる。 30

【 0 1 0 7 】

図 2 2 は、実施の形態 2 の記憶装置の処理のメインフローを示す図である。

図 2 2 を参照して、実施の形態 2 の記憶装置の処理のメインフローは、図 5 に示した実施の形態 1 の読み出し処理ステップ S 0 4 に代えてステップ S 1 0 4 を含み、書き込み処理ステップ S 0 5 に代えてステップ S 1 0 5 を含む点が図 5 で示したフローと異なる。他の部分は図 5 で示したフローと同様であるので説明は繰返さない。

【 0 1 0 8 】

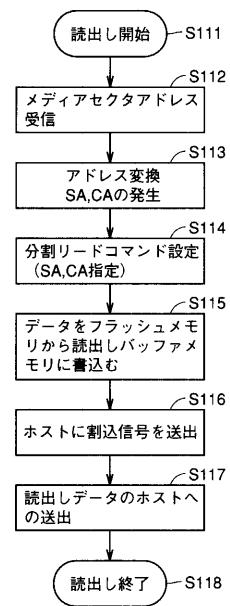

図 2 3 は、図 2 2 に示したステップ S 1 0 4 の読み出し処理の詳細を示すフローチャートである。

【 0 1 0 9 】

図 2 3 を参照して、ステップ S 1 1 1 において、読み出しが開始される。 40

次いで、ステップ S 1 1 2 において、メディアセクタアドレスがホストシステムから受信される。続いて、ステップ S 1 1 3 において、受信したメディアセクタアドレスを変換してフラッシュメモリのセクタアドレス S A およびスタートカラムアドレス C A が発生される。続いて、ステップ S 1 1 4 において、フラッシュメモリの分割リードコマンドが設定されセクタアドレス S A およびスタートカラムアドレス C A も指定される。そして、ステップ S 1 1 5 において、データがフラッシュメモリから読み出され、バッファメモリに書き込まれる。

【 0 1 1 0 】

バッファメモリへの書き込みが終了すると、ステップ S 1 1 6 においてホストシステムに対し 50

て割込信号が送出される。

【0111】

続いて、ステップS117において、バッファメモリに書込まれたデータはホストシステムに対して読み出データとして送出される。そして、ステップS118において、読み出しが終了する。

【0112】

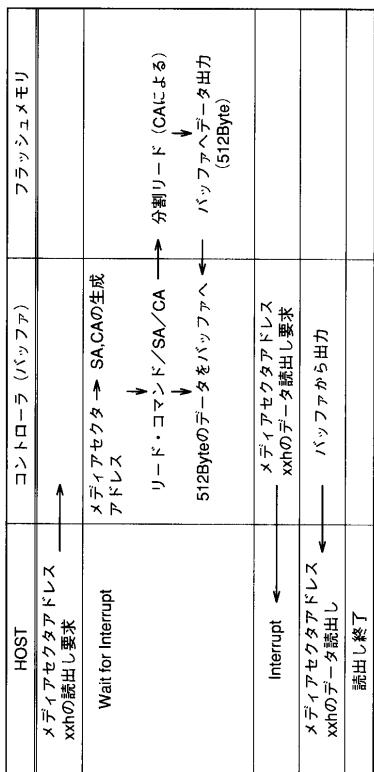

図24は、図23で示した読み出しが記憶装置内のどのブロックで実施されているかを示す図である。

【0113】

図24を参照して、まずホストシステムからコントローラやバッファメモリに対してメディアセクタアドレスの読み出しが発信される。コントローラというのは、図15におけるホストインターフェイス部52およびフラッシュインターフェイスシーケンサ部56に該当する。

10

【0114】

これを受けてコントローラではメディアセクタアドレスからフラッシュメモリのセクタアドレスSAとスタートカラムアドレスCAとが生成される。そしてコントローラからはリードコマンドとセクタアドレスおよびスタートカラムアドレスとがフラッシュメモリに送出される。応じて、フラッシュメモリでは、分割リード動作が行なわれ、512バイトのデータがバッファメモリへと出力される。バッファメモリへのデータ書き込みが終了すると、コントローラは指定されたメディアセクタアドレスのデータ読み出しがホストシステムに対して要求する。そして、バッファメモリからはホストシステムに対してデータの読み出しが行なわれ、読み出しが終了する。

20

【0115】

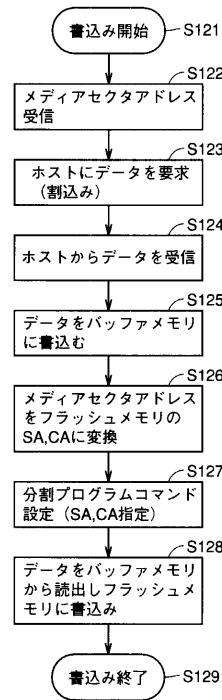

図25は、図22に示したステップS105における書き込み処理の詳細を示すフローチャートである。

【0116】

図25を参照して、まずステップS121において書き込みが開始される。

続いてステップS122においてホストシステムから発信されたメディアセクタアドレスが受信される。

30

【0117】

続いて、ステップS123において、記憶装置がホストシステムに対してデータを要求する。そして、ステップS124においてホストシステムからデータを受信する。このデータは、ステップS125においてバッファメモリに書き込まれる。

【0118】

そして、ステップS126において、ステップS122で受信したメディアセクタアドレスからフラッシュメモリのセクタアドレスSAおよびスタートカラムアドレスCAが生成される。続いてステップS127において、フラッシュメモリに対して分割プログラムコマンドが設定され、続いてセクタアドレスSAおよびスタートカラムアドレスCAの指定がされる。

40

【0119】

そして、ステップS128において、データが、バッファメモリから読み出されフラッシュメモリに書き込まれる。そしてステップS129において、データの書き込みが終了する。

【0120】

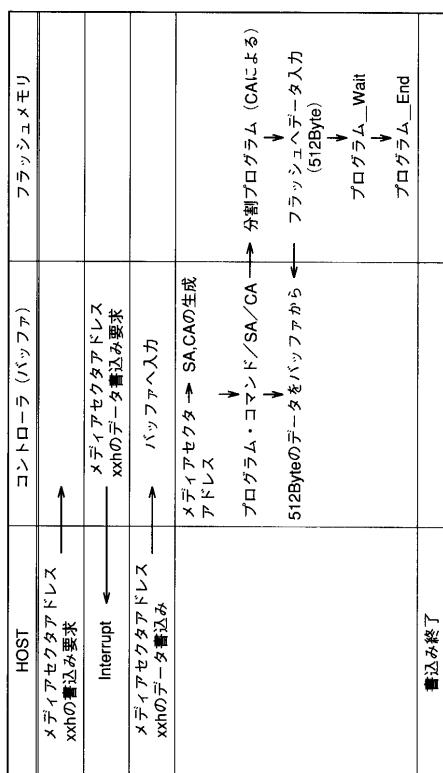

図26は、図25に示した書き込み処理の各ステップがホストシステムとコントローラおよびバッファメモリとフラッシュメモリとの間でどのように行なわれるかを示す図である。

【0121】

図26を参照して、まずホストシステムからメディアセクタアドレスの書き込み要求がコントローラに向けて発信される。続いて、コントローラはこれを受けてメディアセクタアドレスのデータ書き込み要求をホストシステムに対して行なう。応じてホストシステムはメディアセクタアドレスに対するデータの書き込みを行なう。このデータはコントローラを経由してバ

50

バッファメモリに入力される。

【0122】

続いて、コントローラでは、受信していたメディアセクタアドレスからフラッシュメモリのセクタアドレスSAおよびスタートカラムアドレスCAが生成される。そして、コントローラがフラッシュメモリに対してプログラムコマンドとセクタアドレス/SAおよびスタートカラムアドレス/CAの設定を行なう。応じて、フラッシュメモリは、分割プログラム動作を行なう。そしてバッファから512バイトのデータがフラッシュメモリに対して入力され、所定のカラムアドレスを先頭にしてデータ書き込みが行なわれる。フラッシュメモリへバッファメモリから512バイトの書き込みデータが入力されると、その後、所定のウェイト時間経過後書き込みが終了する。

10

【0123】

実施の形態2においては、バッファメモリのアドレス制御およびメディアセクタアドレスからフラッシュメモリに与えるアドレス信号の生成は図15におけるカラムアドレス制御部58で行なわれる。

【0124】

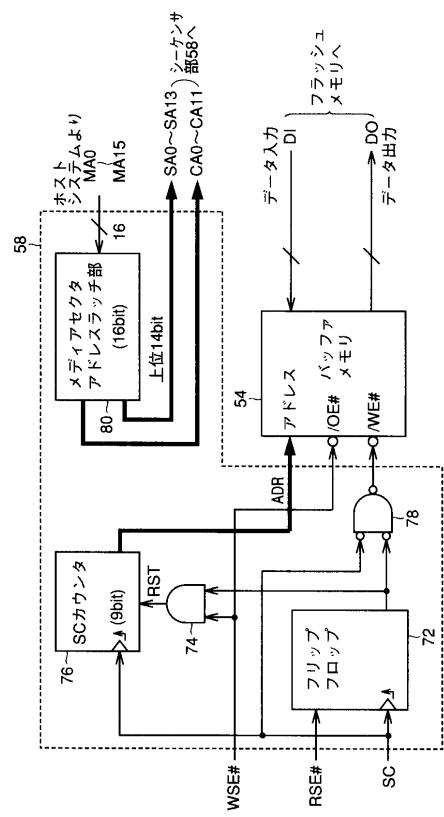

図27は、図15におけるカラムアドレス制御部58の詳細を示すブロック図である。

【0125】

図27を参照して、カラムアドレス制御部58は、記憶装置内部で生成されるリードセクタイネーブル信号RSEをクロック信号SCの立上がりに同期してラッチするフリップフロップ72と、フリップフロップ72の出力と記憶装置内部で生成されるライトセクタイネーブル信号WSEとの論理和をリセット信号RSTとして出力するAND回路74と、リセット信号RSTによってリセットされその後クロック信号SCの立上がりに応答してカウントアップを開始する9ビットのSCカウンタ76と、ホストシステムより16ビットのメディアセクタアドレスをラッチして上位14ビット、下位2ビットをそれぞれセクタアドレスSA0～SA15、スタートカラムアドレスCA0～1としてシーケンサ部6へ出力するメディアセクタアドレスラッチ部30と、フリップフロップ72の出力とクロック信号SCとを受けてライトイネーブル信号/WEを出力するゲート回路78とを含む。

20

【0126】

尚、説明の便宜のため、図27にはバッファメモリ54が記載されている。バッファメモリ54は、SCカウンタ76の計数値9ビットをアドレス信号ADRとして受け、ライトセクタイネーブル信号WSEをアウトプットイネーブル信号/OEとして受け、ゲート回路78の出力をライトイネーブル信号/WEとして受けこれらに応答してフラッシュメモリからのデータ入力DIを受けて保持し、またはフラッシュメモリへデータ出力DOを送出する。

30

【0127】

以上説明したように、実施の形態2においては、ホストインターフェイス部がホストシステムとデータ転送を行なうときにデータを一時的に格納するバッファメモリの容量をフラッシュメモリの1セクタの容量よりも小さくできるため、コストメリットのある記憶装置を提供することができる。さらに、分割リード/プログラム可能なフラッシュメモリを搭載し使用することで、メディアセクタ単位で読み出および再書き込みが可能である。

40

【0128】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなく特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0129】

【発明の効果】

本発明のある局面に従うフラッシュメモリを搭載する記憶装置は、セクタ読み出をするフラッシュメモリを記憶用半導体装置として用いる場合小容量のバッファメモリを搭載する

50

のでコスト的に有利である。

【0130】

本発明の他のフラッシュメモリを搭載する記憶装置は、ダミーデータとしてフラッシュメモリが消去された直後のデータと同じデータを書込むため、既にデータ保持が行なわれた部分のデータが失われることはない。

【0131】

本発明のさらに他のフラッシュメモリを搭載する記憶装置は、フラッシュメモリのセクタ容量を外部のメディアセクタ容量で区切って使用することができ、効率的にフラッシュメモリを使用することができる。

【0132】

本発明のさらに他のフラッシュメモリを搭載する記憶装置は、セクタデータの読み出をする際にも小容量のバッファメモリを使用することができる。

【0133】

本発明のさらに他のフラッシュメモリを搭載する記憶装置は、フラッシュメモリのセクタ容量を外部のメディアセクタ容量で区切って使用することができ、効率的にフラッシュメモリを使用することができる。

【0134】

本発明のさらに他のフラッシュメモリを搭載する記憶装置は、小容量のバッファメモリを搭載するのでコスト的に有利であり、さらに、メディアセクタ単位でデータの再書き込みが可能である。

【図面の簡単な説明】

【図1】 フラッシュメモリを搭載した記憶装置1の概略構成を示すブロック図である。

【図2】 実施の形態1におけるフラッシュメモリとバッファメモリとのアドレスの対応関係を示すメモリマップである。

【図3】 メディアセクタアドレスをフラッシュセクタアドレスとカラムアドレスオフセット生成ビットとに変換する説明をするための図である。

【図4】 スタートフラッシュカラムアドレスオフセットとメディアセクタアドレスの下位2ビットとの関係を示す図である。

【図5】 実施の形態1の記憶装置の処理のメインフローを示す図である。

【図6】 図5に示したステップS04の読み出し処理の詳細を示すフローチャートである。

【図7】 図6に示した読み出し処理の各ステップが記憶装置内のどのブロックで実施されているかを示す図である。

【図8】 図5に示したステップS05における書き込み処理の詳細を示すフローチャートである。

【図9】 図8に示した書き込み処理の各ステップがホストシステムとコントローラおよびバッファメモリとフラッシュメモリとの間でどのように行なわれるかを示す図である。

【図10】 図1に示したデータ転送制御部8の詳細を示すブロック図である。

【図11】 フラッシュメモリからバッファメモリへのデータ転送の様子を示すタイミング図である。

【図12】 図11に示したバッファメモリへのデータ書き込み動作をより詳細に示した動作波形図である。

【図13】 バッファメモリからフラッシュメモリへのデータ転送の様子を示すタイミング図である。

【図14】 図13に示したバッファメモリからフラッシュメモリへのデータ転送の様子をさらに詳しく説明するための動作波形図である。

【図15】 実施の形態2の記憶装置51の概略構成を示すブロック図である。

【図16】 実施の形態2におけるフラッシュメモリとバッファメモリとの対応関係を示すメモリマップである。

【図17】 メディアセクタアドレスをフラッシュセクタアドレスとスタートカラムアドレスとに変換を説明するための図である。

10

20

30

40

50

【図18】 スタートカラムアドレスとメディアセクタアドレスの下位2ビットとの関係を示す図である。

【図19】 スタートカラムアドレスの説明をするための概念図である。

【図20】 分割リード／プログラム機能を有するフラッシュメモリからデータを読出す際のコマンド設定とアドレス設定とを説明するための動作波形図である。

【図21】 実施の形態2においてフラッシュメモリにデータを書込む入力波形を示す図である。

【図22】 実施の形態2の記憶装置の処理のメインフローを示す図である。

【図23】 図22に示したステップS104の読み出し処理の詳細を示すフロー・チャートである。

【図24】 図23で示した読み出し処理の各ステップが記憶装置内のどのブロックで実施されているかを示す図である。

【図25】 図22に示したステップS105における書込処理の詳細を示すフローチャートである。

【図26】 図25に示した書込処理の各ステップがホストシステムとコントローラおよびバッファメモリとフラッシュメモリとの間でどのように行なわれるかを示す図である。

【図27】図15におけるカラムアドレス制御部58の詳細を示すブロック図である。

## 【符号の説明】

1, 51 記憶装置、2, 52 ホストインターフェイス部、4, 54 バッファメモリ、

6, 56 フラッシュインターフェイスシーケンサ、8 データ転送制御部、10, 60

フラッシュメモリ、58 カラムアドレス制御部、22 フリップフロップ、24 AN

D回路、26 S Cカウンタ、28 ゲート回路、30 メディアセクタアドレスラッ奇

部、32 比較器、34 セレクタ。

〔 1 〕

【 2 】

【図3】

【図4】

| ◆メディアセクタアドレス (下位 2bit) |     |                                                                   |

|------------------------|-----|-------------------------------------------------------------------|

| MA1                    | MA0 | 動作                                                                |

| 0                      | 0   | スタートフラッシュカラムアドレスオフセットを0nとし、512Byteのデータをバッファメモリへ(バッファメモリから)転送する。   |

| 0                      | 1   | スタートフラッシュカラムアドレスオフセットを200nとし、512Byteのデータをバッファメモリへ(バッファメモリから)転送する。 |

| 1                      | 0   | スタートフラッシュカラムアドレスオフセットを400nとし、512Byteのデータをバッファメモリへ(バッファメモリから)転送する。 |

| 1                      | 1   | スタートフラッシュカラムアドレスオフセットを600nとし、512Byteのデータをバッファメモリへ(バッファメモリから)転送する。 |

【図5】

【図6】

【図7】

【図8】

【図9】

※フラッシュメモリのイレース状態がFFである場合。

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

【図17】

【図18】

◆メディアセクタアドレス (下位 2bit)

| MA1 | MA0 | スタートカラムアドレス        |

|-----|-----|--------------------|

| 0   | 0   | スタートカラムアドレス : 0h   |

| 0   | 1   | スタートカラムアドレス : 200h |

| 1   | 0   | スタートカラムアドレス : 400h |

| 1   | 1   | スタートカラムアドレス : 600h |

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【 図 25 】

【 図 2 6 】

【 図 27 】

---

フロントページの続き

(72)発明者 福住 知也

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 田中 秀人

(56)参考文献 特開平01-237861 (JP, A)

特開平07-141247 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 12/00 - 12/06