(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6262519号

(P6262519)

(45) 発行日 平成30年1月17日(2018.1.17)

(24) 登録日 平成29年12月22日(2017.12.22)

(51) Int.Cl.

F 1

|                    |                  |             |      |

|--------------------|------------------|-------------|------|

| <b>H01L 29/786</b> | <b>(2006.01)</b> | H01L 29/78  | 612B |

| <b>G02F 1/1368</b> | <b>(2006.01)</b> | G02F 1/1368 |      |

| <b>H01L 21/336</b> | <b>(2006.01)</b> | H01L 29/78  | 618B |

| <b>G09F 9/30</b>   | <b>(2006.01)</b> | H01L 29/78  | 619A |

|                    |                  | G09F 9/30   | 338  |

請求項の数 3 (全 72 頁) 最終頁に続く

(21) 出願番号

特願2013-268881 (P2013-268881)

(22) 出願日

平成25年12月26日 (2013.12.26)

(65) 公開番号

特開2014-199913 (P2014-199913A)

(43) 公開日

平成26年10月23日 (2014.10.23)

審査請求日

平成28年12月22日 (2016.12.22)

(31) 優先権主張番号

特願2012-288973 (P2012-288973)

(32) 優先日

平成24年12月28日 (2012.12.28)

(33) 優先権主張国

日本国 (JP)

(31) 優先権主張番号

特願2013-49261 (P2013-49261)

(32) 優先日

平成25年3月12日 (2013.3.12)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 遠藤 佑太

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】半導体装置、および半導体装置の作製方法

(57) 【特許請求の範囲】

【請求項 1】

トランジスタと容量素子を有し、前記トランジスタは、第1の絶縁膜上の第1の酸化物半導体層と、前記第1の酸化物半導体層と接する領域を有するソース電極層およびドレイン電極層と、前記ソース電極層および前記ドレイン電極層および第1の酸化物半導体層の上方の第2の絶縁膜と、

前記第2の絶縁膜を介して前記第1の酸化物半導体層と重なるゲート電極層と、

前記第2の絶縁膜および前記ゲート電極層の上方の第3の絶縁膜と、

前記第3の絶縁膜の上方の第4の絶縁膜と、を有し、

前記容量素子は、

前記第1の絶縁膜の上方の第2の酸化物半導体層と、

前記第2の酸化物半導体層と接する領域を有する配線と、

前記第2の酸化物半導体層および前記配線の上方の第5の絶縁膜と、

前記第5の絶縁膜の上方の透光性導電膜と、を有し、

前記第5の絶縁膜は、前記第3および前記第4の絶縁膜を有し、

前記第3の絶縁膜は、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa-Zn系金属酸化物のうち、いずれか一つを有し、

10

20

前記第4の絶縁膜は、窒化酸化シリコン、窒化シリコン、窒化アルミニウム、窒化酸化アルミニウムのうち、いずれか一つを有することを特徴とする半導体装置。

**【請求項2】**

請求項1において、

前記第2の絶縁膜は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはG a - Z n系金属酸化物のうち、いずれか一つを有することを特徴とする半導体装置。

**【請求項3】**

請求項1または請求項2において、

前記第1の絶縁膜は、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはG a - Z n系金属酸化物のうち、いずれか一つを有することを特徴とする半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、物、方法、または、製造方法に関する。または、本発明は、プロセス、マシン、マニュファクチャ、または、組成物（コンポジション・オブ・マター）に関する。特に、本発明は、例えば、半導体装置、表示装置、発光装置、それらの駆動方法、または、それらの作製方法に関する。特に、本発明は、例えば、酸化物半導体を有する半導体装置、表示装置、または、発光装置、およびその作製方法に関する。

20

**【背景技術】**

**【0002】**

近年、液晶ディスプレイ（L C D）などのフラットパネルディスプレイが広く普及している。フラットパネルディスプレイなどの表示装置において、行方向および列方向に配設された画素内には、スイッチング素子であるトランジスタと、当該トランジスタと電気的に接続された液晶素子と、当該液晶素子と並列に接続された容量素子とが設けられている。

**【0003】**

当該トランジスタの半導体膜を構成する半導体材料としては、アモルファス（非晶質）シリコンまたはポリ（多結晶）シリコンなどのシリコン半導体が汎用されている。

30

**【0004】**

また、半導体特性を示す金属酸化物（以下、酸化物半導体と記す）は、トランジスタの半導体膜に適用できる半導体材料である。例えば、酸化亜鉛またはI n - G a - Z n系酸化物半導体を用いて、トランジスタを作製する技術が開示されている（特許文献1および特許文献2を参照）。

**【先行技術文献】**

**【特許文献】**

**【0005】**

**【特許文献1】**特開2007-123861号公報

**【特許文献2】**特開2007-96055号公報

40

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

容量素子は一対の電極の間に誘電体膜が設けられており、一対の電極のうち、少なくとも一方の電極は、トランジスタを構成するゲート電極、ソース電極またはドレイン電極などと同一材料で形成されるため、金属などの遮光性を有する導電膜で形成されていることが多い。

**【0007】**

また、容量素子の容量値を大きくするほど、電界を加えた状況において、液晶素子の液晶分子の配向を一定に保つことができる期間を長くすることができる。静止画を表示させる

50

ことのできる表示装置において、当該期間を長くできることは、画像データを書き換える回数を低減することができ、消費電力の低減が望める。

#### 【0008】

容量素子の電荷容量を大きくするためには、画素内における容量素子の占有面積を大きくする、具体的には一対の電極が重畳している面積を大きくするという手段がある。しかしながら、上記表示装置において、一対の電極が重畳している面積を大きくするために遮光性を有する導電膜の面積を大きくすると、画素の開口率が低減し、画像の表示品位が低下する。

#### 【0009】

そこで、上記課題に鑑みて、本発明の一態様は、開口率が高い半導体装置などを提供することを目的の一つとする。または、電荷容量を増大させることができ可能な容量素子を有する半導体装置などを提供することを目的の一つとする。または、フォトリソグラフィ工程のマスク枚数を削減することのできる半導体装置などを提供することを目的の一つとする。または、オフ電流の低い半導体装置などを提供することを目的の一つとする。または、消費電力を低減した半導体装置などを提供することを目的の一つとする。または、透明な半導体層を用いた半導体装置などを提供することを目的の一つとする。または、信頼性の高い半導体装置などを提供することを目的の一つとする。または、目にやさしい半導体装置などを提供することを目的の一つとする。または、新規な半導体装置などを提供することを目的の一つとする。または、新規な半導体装置などの作製方法を提供することを目的の一つとする。

10

#### 【0010】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。なお、本発明の一態様は、これらの課題の全てを解決する必要はないものとする。なお、これら以外の課題は、明細書、図面、請求項などの記載から、自ずと明らかとなるものであり、明細書、図面、請求項などの記載から、これら以外の課題を抽出することが可能である。

20

#### 【課題を解決するための手段】

#### 【0011】

本発明の一態様は、酸化物半導体層を一方の電極とし、透光性導電膜を他方の電極とする透光性を有する容量素子を含む半導体装置に関する。

#### 【0012】

本発明の一態様は、トランジスタを有する半導体装置であって、第1の絶縁膜上に形成された第1の酸化物半導体層および第2の酸化物半導体層と、第1の酸化物半導体層と電気的に接続されたソース電極層およびドレイン電極層と、第2の酸化物半導体層と電気的に接続された配線と、第1の絶縁膜、第1の酸化物半導体層、第2の酸化物半導体層、ソース電極層、ドレイン電極層、および配線上に形成された第2の絶縁膜と、第2の絶縁膜を介して第1の酸化物半導体層と重なるゲート電極層と、第2の絶縁膜、およびゲート電極層上に形成された第3の絶縁膜と、第3の絶縁膜上に形成された第4の絶縁膜と、第2の酸化物半導体層上において、第4の絶縁膜上に形成された透光性導電膜と、を有し、誘電体を含み、第2の酸化物半導体層の少なくとも一部を第1の電極とし、透光性導電膜の少なくとも一部を第2の電極とした容量素子を有することを特徴とする半導体装置である。

30

#### 【0013】

第1の酸化物半導体層および第2の酸化物半導体層は同じ材料で形成されていることが好みしい。

#### 【0014】

また、第1の酸化物半導体層および第2の酸化物半導体層は、エネルギーギャップが2.0 eV以上であることが好みしい。

#### 【0015】

第2の酸化物半導体層に水素、ホウ素、窒素、フッ素、アルミニウム、リン、ヒ素、インジウム、スズ、アンチモンおよび希ガス元素から選ばれた一種以上のドーパントが添加されていてもよい。

40

50

## 【0016】

誘電体は第2の絶縁膜、第3の絶縁膜および第4の絶縁膜で形成することができる。

## 【0017】

また、誘電体を第3の絶縁膜および第4の絶縁膜で形成してもよい。

## 【0018】

また、誘電体を第4の絶縁膜で形成してもよい。

## 【0019】

また、第3の絶縁膜は、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa-Zn系金属酸化物から選ばれた酸化絶縁材料の単層構造または積層構造で形成することが好ましい。

10

## 【0020】

また、第4の絶縁膜は、窒化酸化シリコン、窒化シリコン、窒化アルミニウム、窒化酸化アルミニウムから選ばれた窒化絶縁材料の単層構造または積層構造で形成することが好ましい。

## 【0021】

また、第1の絶縁膜と第2の酸化物半導体層との間に水素を含む窒化絶縁膜が形成されていてもよい。

## 【0022】

また、ソース電極層、ドレイン電極層、および配線は同一の絶縁表面上に形成された構成とすることができる。

20

## 【0023】

また、ソース電極層、ドレイン電極層、および配線は同じ材料で形成された構成とすることができる。

## 【0024】

また、透光性導電膜はソース電極またはドレイン電極の一方と電気的に接続されている構成とすることができる。

## 【0025】

また、本発明の他の一態様は、第1の絶縁膜上に第1の酸化物半導体層および第2の酸化物半導体層を形成し、第1の酸化物半導体層と電気的に接続するソース電極層およびドレイン電極層、ならびに、第2の酸化物半導体層と電気的に接続する配線を形成し、第1の絶縁膜、第1の酸化物半導体層、第2の酸化物半導体層、ソース電極層、ドレイン電極層、および配線上に第2の絶縁膜を形成し、第2の絶縁膜上に第1の酸化物半導体層と重畳するゲート電極層を形成し、第2の絶縁膜およびゲート電極層上に第3の絶縁膜を形成し、第3の絶縁膜上に第4の絶縁膜を形成し、第2の絶縁膜、第3の絶縁膜、および第4の絶縁膜にソース電極層またはドレイン電極層に通じる開口部を形成し、第4の絶縁膜上に開口部でソース電極層またはドレイン電極層と電気的に接続する透光性導電膜を形成し、トランジスタと、第1の電極として少なくとも第2の酸化物半導体層の一部、第2の電極として透光性導電膜の少なくとも一部、誘電体層を有する容量素子と、を形成することを特徴とする半導体装置の作製方法である。

30

## 【0026】

第1の酸化物半導体層および第2の酸化物半導体層は同じ材料で形成することが好ましい。

## 【0027】

また、第1の酸化物半導体層および第2の酸化物半導体層は、エネルギーギャップが2.0eV以上の材料で形成することが好ましい。

## 【0028】

また、第2の酸化物半導体層に水素、ホウ素、窒素、フッ素、アルミニウム、リン、ヒ素、インジウム、スズ、アンチモンおよび希ガス元素から選ばれた一種以上のドーパントを添加してもよい。

## 【0029】

50

誘電体は第2の絶縁膜、第3の絶縁膜および第4の絶縁膜で形成することができる。

**【0030】**

また、第2の酸化物半導体層上の第2の絶縁膜をエッティングし、誘電体を第3の絶縁膜および第4の絶縁膜で形成してもよい。

**【0031】**

また、第2の酸化物半導体層上の第2の絶縁膜および第3の絶縁膜をエッティングし、誘電体を第4の絶縁膜で形成してもよい。

**【0032】**

また、第3の絶縁膜を、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa-Zn系金属酸化物から選ばれた酸化絶縁材料の単層構造または積層構造で形成することが好ましい。10

**【0033】**

また、第4の絶縁膜を、窒化酸化シリコン、窒化シリコン、窒化アルミニウム、窒化酸化アルミニウムから選ばれた窒化絶縁材料の単層構造または積層構造で形成することが好ましい。

**【0034】**

また、第1の絶縁膜と第2の酸化物半導体層との間に水素を含む窒化絶縁膜を形成してもよい。

**【0035】**

また、ソース電極層、ドレイン電極層、および配線と同じ材料で形成することが好ましい。20

**【0036】**

また、ソース電極層、前記ドレイン電極層、および前記配線を同一の絶縁表面上に形成することが好ましい。

**【発明の効果】**

**【0037】**

本発明の一態様より、開口率が高い半導体装置などを提供することができる。または、電荷容量を増大させることができた容量素子を有する半導体装置などを提供することができる。または、フォトリソグラフィ工程のマスク枚数を削減することのできる半導体装置などを提供することができる。または、オフ電流の低い半導体装置などを提供することができる。または、消費電力を低減した半導体装置などを提供することができる。または、透明な半導体層を用いた半導体装置などを提供することができる。または、信頼性の高い半導体装置などを提供することができる。または、目にやさしい半導体装置を提供することができる。または、半導体装置の作製方法を提供することができる。30

**【図面の簡単な説明】**

**【0038】**

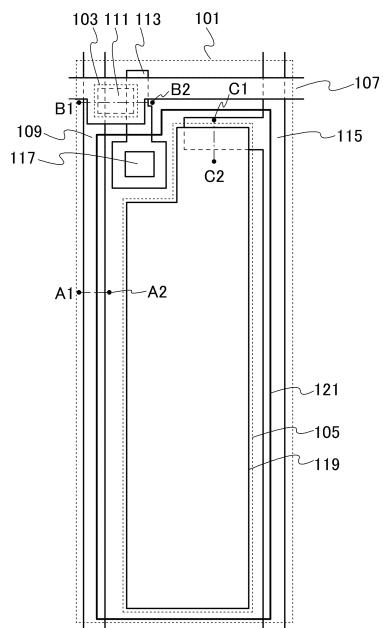

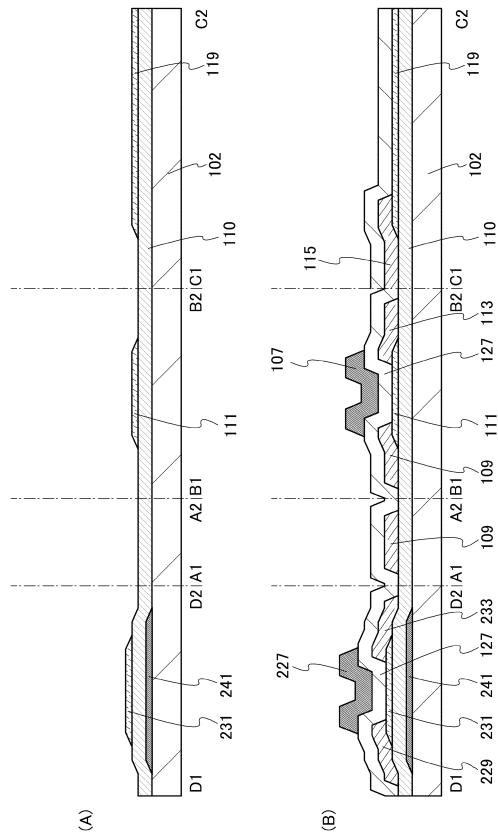

【図1】半導体装置を説明する上面図。

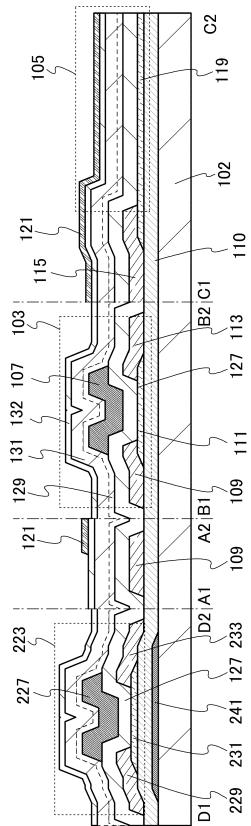

【図2】半導体装置を説明する断面図。

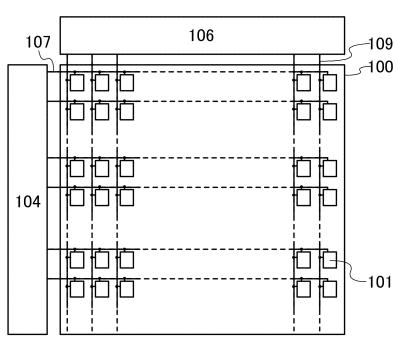

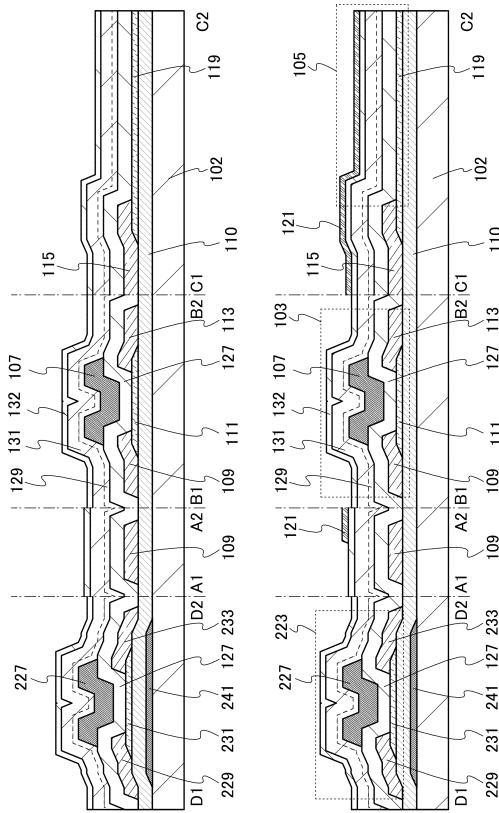

【図3】半導体装置を説明する図。

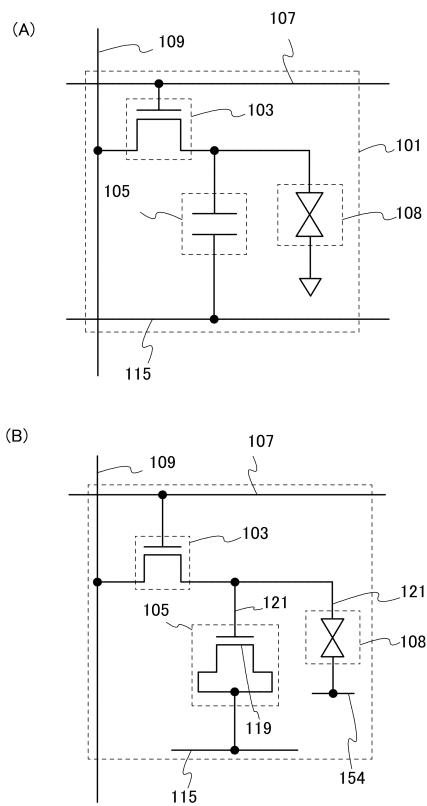

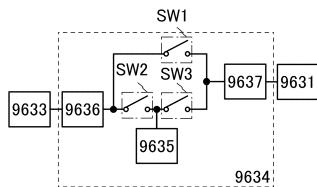

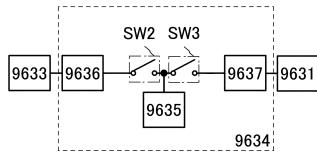

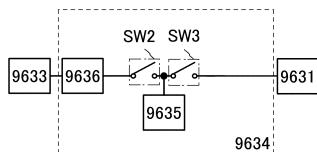

【図4】半導体装置の画素を説明する回路図。

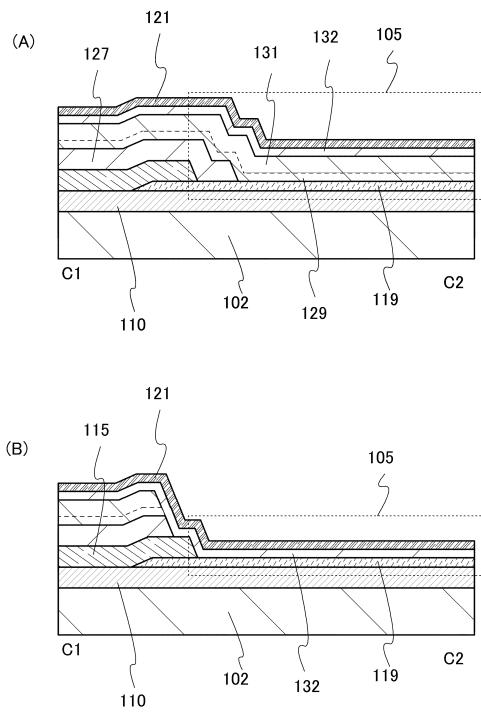

【図5】半導体装置の作製方法を説明する断面図。

【図6】半導体装置の作製方法を説明する断面図。

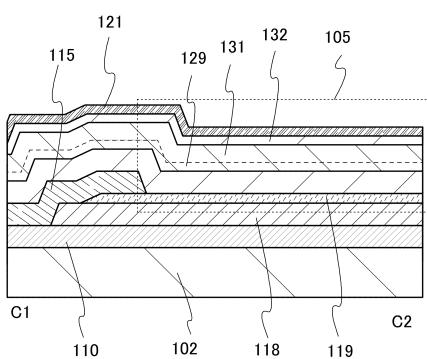

【図7】半導体装置の容量素子を説明する断面図。

【図8】半導体装置を説明する断面図。

【図9】半導体装置を説明する断面図。

【図10】酸化物半導体膜の極微電子線回折パターンを示す図。

【図11】酸化物半導体膜のCPM測定結果を示す図。

【図12】CAC-O<sub>2</sub>膜のCPM測定結果を示す図。

【図13】酸化物半導体膜の断面TEM像および極微電子線回折パターン。

【図14】酸化物半導体膜の平面TEM像および制限視野電子線回折パターン。40

50

- 【図15】電子線回折強度分布の概念図。

- 【図16】石英ガラス基板の極微電子線回折パターン。

- 【図17】酸化物半導体膜の極微電子線回折パターン。

- 【図18】酸化物半導体膜の断面TEM像。

- 【図19】酸化物半導体膜のX線回折分析結果。

- 【図20】CAAC-OS膜の断面TEM像。

- 【図21】CAAC-OS膜の電子線回折パターン。

- 【図22】CAAC-OS膜の断面TEM像。

- 【図23】CAAC-OS膜の断面TEM像およびX線回折スペクトル。

- 【図24】CAAC-OS膜の電子線回折パターン。 10

- 【図25】CAAC-OS膜の断面TEM像およびX線回折スペクトル。

- 【図26】CAAC-OS膜の電子線回折パターン。

- 【図27】CAAC-OS膜の断面TEM像およびX線回折スペクトル。

- 【図28】CAAC-OS膜の電子線回折パターン。

【図29】半導体装置を説明する上面図。

【図30】半導体装置を説明する断面図。

【図31】半導体装置を説明する断面図および上面図。

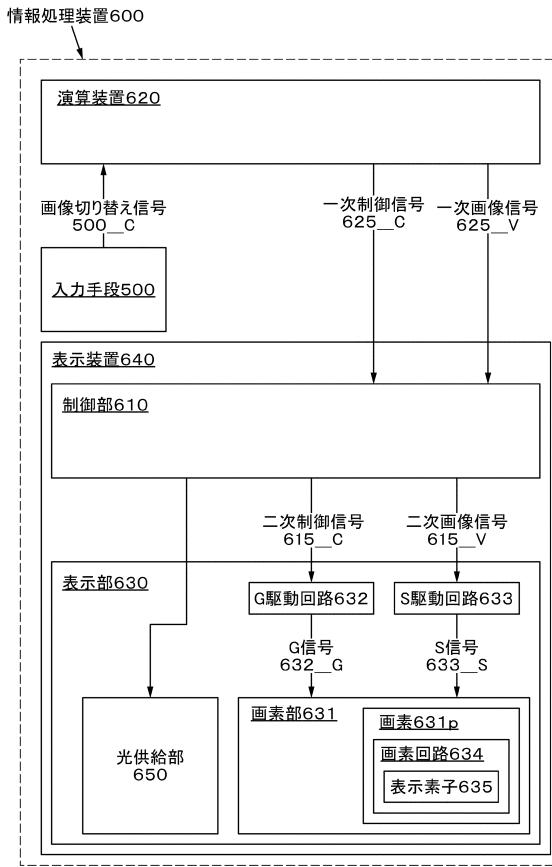

【図32】表示機能を有する情報処理装置の構成を説明するブロック図。

【図33】情報処理装置の表示部の構成を説明するブロック図および回路図。

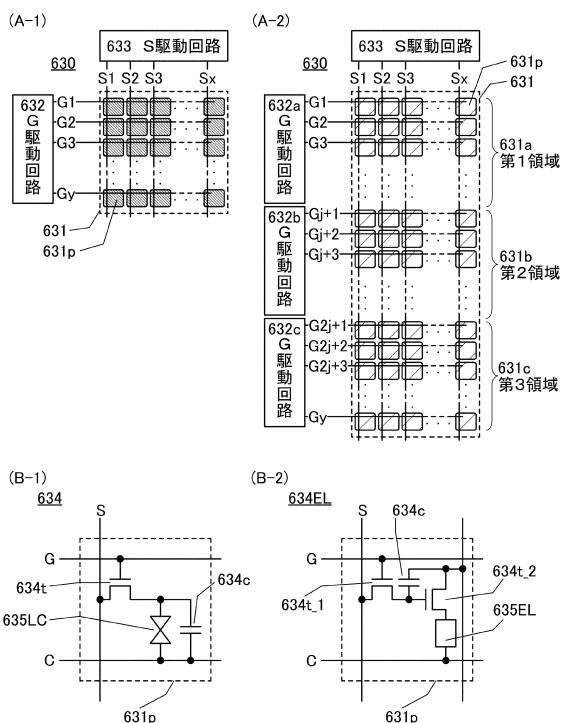

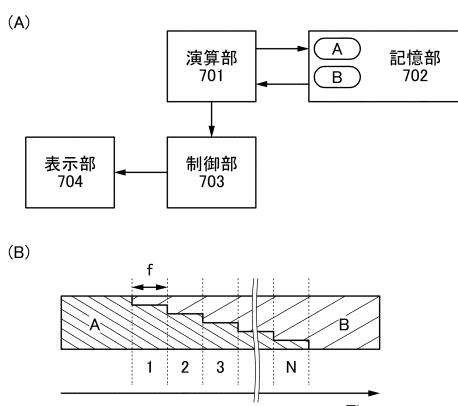

【図34】情報処理装置の構成を説明するブロック図および画像データを説明するための模式図。 20

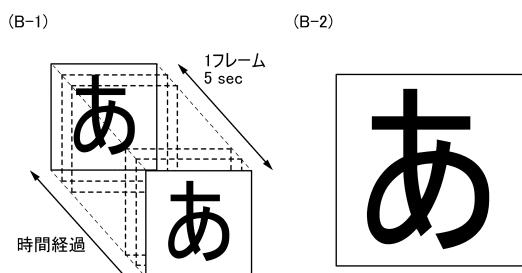

【図35】情報処理装置の効果を説明する図。

【図36】情報処理装置を説明するブロック図。

【図37】半導体装置を用いた電子機器を説明する図。

【図38】半導体装置を用いた電子機器を説明する図。

【図39】半導体装置を用いた電子機器を説明する図。

【発明を実施するための形態】

【0039】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。 30

【0040】

以下に説明する本発明の構成において、同一部分または同様の機能を有する部分には同一の符号を異なる図面間で共通して用い、その繰り返しの説明は省略する。また、同様の機能を有する部分を指す場合には、ハッチパターンを同じくし、特に符号を付さない場合がある。

【0041】

本明細書で説明する各図において、各構成の大きさ、膜の厚さ、または領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。 40

【0042】

本明細書などにおいて、第1、第2等として付される序数詞は便宜上用いるものであり、工程順または積層順を示すものではない。また、本明細書等において発明を特定するための事項として固有の名称を示すものではない。

【0043】

また、電圧とは2点間における電位差のことをいい、電位とはある一点における静電場の中に単位電荷が持つ静電エネルギー（電気的な位置エネルギー）のことをいう。ただし、一般的に、ある一点における電位と基準となる電位（例えば接地電位）との電位差のことを、単に電位もしくは電圧と呼び、電位と電圧が同義語として用いられることが多い。このため、本明細書では特に指定する場合を除き、電位を電圧と読み替えてよいし、 50

電圧を電位と読み替えてよいこととする。

【0044】

本明細書において、フォトリソグラフィ処理を行った後にエッチング処理を行う場合は、フォトリソグラフィ処理で形成したレジストマスクは除去するものとする。

【0045】

(実施の形態1)

本実施の形態では、本発明の一態様である半導体装置について、図面を用いて説明する。なお、本実施の形態では、液晶表示装置を例にして本発明の一態様である半導体装置を説明する。なお、本発明の一態様である半導体装置は、他の表示装置にも適用することができる。

10

【0046】

図3は、本発明の一態様の半導体装置を説明する図である。図3に示す半導体装置は、画素部100と、第1の駆動回路104と、第2の駆動回路106と、各々が平行または略平行に配設され、且つ第1の駆動回路104によって電位が制御されるm本の走査線107と、各々が平行または略平行に配設され、且つ第2の駆動回路106によって電位が制御されるn本の信号線109と、を有する。さらに、画素部100はマトリクス状に配設された複数の画素101を有する。また、当該半導体装置は容量線115(図3に図示せず)を有する。容量線115は、走査線107に沿って各々が平行または略平行に配設、または信号線109に沿って各々が平行または略平行に配設されている。

【0047】

各走査線107は、画素部100においてm行n列に配設された画素101のうち、いずれかの行に配設されたn個の画素101と電気的に接続される。また、各信号線109は、m行n列に配設された画素101のうち、いずれかの列に配設されたm個の画素101に電気的に接続される。m、nは、ともに1以上の整数である。また、各容量線115は、m行n列に配設された画素101のうち、いずれかの行に配設されたn個の画素101と電気的に接続される。なお、容量線115が、信号線109に沿って、各々が平行または略平行に配設されている場合は、m行n列に配設された画素101のうち、いずれかの列に配設されたm個の画素101に電気的に接続される。

20

【0048】

なお、第1の駆動回路104は、走査線107に接続されたトランジスタをスイッチングする信号を供給する機能、例えば、走査線駆動回路としての機能を有することができる。また、第2の駆動回路106は、信号線109に接続されたトランジスタに映像信号を供給する機能、例えば、信号線駆動回路としての機能を有することができる。なお、これに限らず、第1の駆動回路104および第2の駆動回路106は、別の信号を供給することも可能である。

30

【0049】

また、本実施の形態では、液晶表示装置を例として説明するため、便宜上、第1の駆動回路104に接続された配線を走査線107、容量線115と称し、第2の駆動回路106に接続された配線を信号線109と称するが、その名称によって機能を限定するものではない。

40

【0050】

図1は、上記半導体装置に含まれる画素101の一例の構成を説明する上面図である。なお、図1においては、液晶層および液晶素子が有する一対の電極のうち、一つを省略する。

【0051】

図1に示す画素101において、走査線107は、信号線109に略直交する方向(行方向)に延伸して設けられている。信号線109は、走査線107に略直交する方向(列方向)に延伸して設けられている。容量線115は、信号線109と平行方向に延伸して設けられている。なお、走査線107は、第1の駆動回路104(図3参照)と電気的に接続されており、信号線109は、第2の駆動回路106(図3参照)に電気的に接続され

50

ている。

**【0052】**

トランジスタ103は、走査線107および信号線109が交差する領域近傍に設けられている。トランジスタ103は、少なくとも、チャネル形成領域を有する半導体膜111、ゲート電極、ゲート絶縁膜(図1に図示せず)、ソース電極、およびドレイン電極を含む。なお、走査線107において、半導体膜111と重畠する領域はトランジスタ103のゲート電極として機能する。信号線109において、半導体膜111と重畠する領域はトランジスタ103のソース電極またはドレイン電極の一方として機能する。導電膜113において、半導体膜111と重畠する領域はトランジスタ103のソース電極またはドレイン電極の他方として機能する。このため、ゲート電極、ソース電極、ドレイン電極をそれぞれ、走査線107、信号線109、導電膜113と示す場合がある。また、図1において、走査線107は、上面形状において端部が半導体膜111の端部より外側に位置する。このため、走査線107は外部からの光を遮る遮光膜として機能する。この結果、トランジスタに含まれる半導体膜111に光が照射されず、トランジスタの電気特性の変動を抑制することができる。

10

**【0053】**

また、本発明の一態様では半導体膜111に酸化物半導体を用いることが好ましい。酸化物半導体を用いたトランジスタは、適切な条件にて作製することでオフ電流を極めて小さくすることができる。したがって、半導体装置の消費電力を低減することができる。

20

**【0054】**

本発明の一態様において、酸化物半導体を用いたトランジスタはnチャネル型トランジスタである。また、酸化物半導体に含まれる酸素欠損はキャリアを生成することがあり、トランジスタの電気特性および信頼性を低下させる恐れがある。例えば、トランジスタのしきい値電圧がマイナス方向に変動し、ゲート電圧が0Vのときにドレイン電流が流れてしまうことがある。このように、ゲート電圧が0Vの場合にドレイン電流が流れてしまうことをノーマリーオン特性という。なお、ゲート電圧が0Vの場合にドレイン電流が流れていないとみなすことができるトランジスタをノーマリーオフ特性という。

**【0055】**

そのため、半導体膜111に酸化物半導体を用いる際、半導体膜111である酸化物半導体膜に含まれる欠陥(代表的には酸素欠損)は、できる限り低減されていることが好ましい。例えば、磁場の向きを膜面に対して平行に印加した電子スピン共鳴法によるg値=1.93のスピンド 密度(酸化物半導体膜に含まれる欠陥密度に相当する)は、測定器の検出下限以下まで低減されていることが好ましい。酸化物半導体膜に含まれる欠陥をできる限り低減することで、トランジスタ103がノーマリーオン特性となることを抑制することができ、半導体装置の電気特性および信頼性を向上させることができる。

30

**【0056】**

トランジスタのしきい値電圧のマイナス方向への変動は酸素欠損だけではなく、酸化物半導体に含まれる水素(水などの水素化合物を含む)によっても引き起こされることがある。酸化物半導体に含まれる水素の一部はドナー準位の形成に寄与し、キャリアである電子を生成してしまう。したがって、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。

40

**【0057】**

そこで、半導体膜111に酸化物半導体を用いる際、半導体膜111である酸化物半導体膜は水素ができる限り低減されていることが好ましい。具体的には、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により得られる水素濃度を $5 \times 10^{18}$ atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{18}$ atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$ atoms/cm<sup>3</sup>以下、さらに好ましくは $1 \times 10^{16}$ atoms/cm<sup>3</sup>以下とする領域を有するように半導体膜111を形成する。

**【0058】**

50

また、二次イオン質量分析法により得られるアルカリ金属またはアルカリ土類金属の濃度を $1 \times 10^{-8}$  atoms/cm<sup>3</sup>以下、好ましくは $2 \times 10^{-6}$  atoms/cm<sup>3</sup>以下とする領域を有するように半導体膜111を形成することが好ましい。アルカリ金属およびアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタ103のオフ電流を増大させことがある。

#### 【0059】

また、半導体膜111である酸化物半導体膜に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。したがって、当該酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、窒素濃度は、 $5 \times 10^{-8}$  atoms/cm<sup>3</sup>以下とする領域を有するように半導体膜111を形成することが好ましい。10

#### 【0060】

このように、不純物（水素、窒素、アルカリ金属またはアルカリ土類金属など）をできる限り低減させ、高純度化させた酸化物半導体膜を半導体膜111として、トランジスタ103がノーマリーオン特性となることを抑制でき、トランジスタ103のオフ電流を極めて低減することができる。したがって、良好な電気特性に有する半導体装置を作製できる。また、信頼性を向上させた半導体装置を作製することができる。

#### 【0061】

なお、高純度化された酸化物半導体膜を用いたトランジスタのオフ電流が低いことは、いろいろな実験により証明できる。例えば、チャネル幅が $1 \times 10^6$  μmでチャネル長Lが $10$  μmの素子であっても、ソース電極とドレイン電極間の電圧（ドレイン電圧）が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}$  A以下という特性を得ることができる。この場合、トランジスタのチャネル幅で除した数値に相当するオフ電流は、 $100$  zA/μm以下であることが分かる。また、容量素子とトランジスタとを接続して、容量素子に流入または容量素子から流出する電荷を当該トランジスタで制御する回路を用いて、オフ電流の測定を行った。当該測定では、上記トランジスタに高純度化された酸化物半導体膜をチャネル形成領域に用い、容量素子の単位時間あたりの電荷量の推移から当該トランジスタのオフ電流を測定した。その結果、トランジスタのソース電極とドレイン電極間の電圧が3Vの場合に、数十yA/μmという、極めて低いオフ電流が得られることが分かった。したがって、高純度化された酸化物半導体膜を用いたトランジスタは、オフ電流が著しく小さいことができる。2030

#### 【0062】

図1において、導電膜113は、開口117を通じて透光性を有する導電膜で形成される液晶素子の一方の電極である画素電極121と電気的に接続されている。

#### 【0063】

容量素子105は、透光性を有する酸化物半導体で形成される半導体膜119を一方の電極とし、透光性を有する画素電極121を他方の電極とし、トランジスタ103に含まれ、透光性を有する絶縁膜（図1に図示せず）を誘電体膜として構成されている。すなわち、容量素子105は透光性を有する。また、容量素子105の一方の電極である半導体膜119は、容量線115と電気的に接続されている。40

#### 【0064】

このように、容量素子105は透光性を有するため、液晶素子との重畠領域においても光を透過させることができる。したがって、画素101内に容量素子105を大きく（大面積に）形成しても開口率を例えば55%以上、さらには60%以上と高くすることが可能となる。また、容量素子における電荷容量を増大させた半導体装置を得ることができる。

#### 【0065】

例えば、解像度の高い液晶表示装置においては、画素全体の面積が縮小されるが、容量素子においては必要な電荷容量を確保しなければならず、面積の縮小には限度がある。この50

ため、解像度の高い液晶表示装置においては、開口率が小さくなってしまう。一方、本実施の形態に示す容量素子105は透光性を有するため、当該容量素子を画素に設けることで、各画素において十分な電荷容量を得つつ、開口率を高めることができる。代表的には、画素密度が200ppi以上、さらには300ppi以上である高解像度の液晶表示装置に用いることが好適である。また、本発明の一態様は、開口率を高めることができたため、バックライトなどの光源の光を効率よく利用することができ、表示装置の消費電力を低減することができる。

#### 【0066】

次いで、図1に示す一点鎖線A1-A2間、一点鎖線B1-B2間、一点鎖線C1-C2間の断面図、および図3に示す第1の駆動回路104に用いられるトランジスタの断面図を図2に示す。なお、第1の駆動回路104の上面図を省略すると共に、図2においては、第1の駆動回路104の断面図をD1-D2として示す。また、第1の駆動回路104に用いられるトランジスタは、第2の駆動回路106に用いることもできる。

10

#### 【0067】

はじめに、画素101の一点鎖線A1-A2間、一点鎖線B1-B2間、および一点鎖線C1-C2間の断面構造について説明する。

#### 【0068】

基板102上には下地絶縁膜110が設けられ、当該下地絶縁膜上に半導体膜111、半導体膜119が設けられている。半導体膜111上には、トランジスタ103のソース電極またはドレイン電極の一方を含む信号線109、およびトランジスタ103のソース電極またはドレイン電極の他方を含む導電膜113が設けられ、半導体膜119上には、容量線115が設けられている。半導体膜111、半導体膜119、信号線109、導電膜113、容量線115上には、ゲート絶縁膜127が設けられており、当該ゲート絶縁膜の半導体膜111と重畠する領域上に走査線107が設けられている。ゲート絶縁膜127上、信号線109上、半導体膜111上、導電膜113上、半導体膜119上には、トランジスタ103の保護絶縁膜として機能する絶縁膜129、絶縁膜131、および絶縁膜132が設けられている。絶縁膜129、絶縁膜131、および絶縁膜132には導電膜113に達する開口117(図1参照)が設けられており、当該開口を覆うように画素電極121(図1参照)が設けられている。

20

#### 【0069】

30

本実施の形態に示す容量素子105は、一対の電極のうち一方の電極が下地絶縁膜110上において半導体膜111と同様に形成された半導体膜119であり、一対の電極のうち他方の電極が画素電極121であり、一対の電極の間に設けられた誘電体膜が絶縁膜129、絶縁膜131、および絶縁膜132である。

#### 【0070】

なお、半導体膜119にはドーパントが添加されていてもよい。半導体膜119が酸化物半導体である場合、例えば、水素、ホウ素、窒素、フッ素、アルミニウム、リン、ヒ素、インジウム、スズ、アンチモンおよび希ガス元素から選ばれた一種以上のドーパントを添加することで、酸化物半導体層をn型化させ、導電率を高めることができる。したがって、半導体膜119は導電膜ということもでき、容量素子の一方の電極として作用させることができる。

40

#### 【0071】

なお、導電膜として作用する半導体膜119は、半導体膜111より水素濃度が高いことが好ましい。半導体膜119において、二次イオン質量分析法(SIMS: Second ary Ion Mass Spectrometry)により得られる水素濃度は、 $8 \times 10^{19}$  atoms/cm<sup>3</sup>以上、好ましくは $1 \times 10^{20}$  atoms/cm<sup>3</sup>以上、より好ましくは $5 \times 10^{20}$  atoms/cm<sup>3</sup>以上である。半導体膜111において、二次イオン質量分析法により得られる水素濃度は、 $5 \times 10^{19}$  atoms/cm<sup>3</sup>以下、好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>以下、より好ましくは $5 \times 10^{17}$  atoms/cm<sup>3</sup>以下、さらに好まし

50

くは  $1 \times 10^{-6}$  atoms/cm<sup>3</sup> 以下である。

**【0072】**

また、導電膜として作用する半導体膜 119 は、半導体膜 111 より抵抗率が低い。半導体膜 119 の抵抗率が、半導体膜 111 の抵抗率の  $1 \times 10^{-8}$  倍以上  $1 \times 10^{-1}$  倍以下であることが好ましく、代表的には  $1 \times 10^{-3}$  cm 以上  $1 \times 10^{-4}$  cm 未満、さらに好ましくは、抵抗率が  $1 \times 10^{-3}$  cm 以上  $1 \times 10^{-1}$  cm 未満であるとよい。

**【0073】**

なお、半導体膜 119 は、半導体膜 111 または、半導体膜 231 とは、異なる材料を用いて形成することも可能である。つまり、半導体膜 119 は、半導体膜 111 または、半導体膜 231 とは異なる工程を用いて形成することも可能である。10

**【0074】**

なお、半導体膜 119 と同様に半導体膜を形成し、その半導体膜を用いて、抵抗素子を構成することも可能である。そして、その抵抗素子を用いて、保護回路を構成することも可能である。保護回路を設けることにより、静電気などからの破壊を低減することが出来る。

**【0075】**

次に、第 1 の駆動回路 104 に設けられるトランジスタの構造について説明する。

**【0076】**

基板 102 上に導電膜 241 が設けられ、当該基板上および当該導電膜上には下地絶縁膜 110 が設けられている。下地絶縁膜 110 上の導電膜 241 と重畠する領域には、半導体膜 231 が設けられている。半導体膜 231 上には、トランジスタ 223 のソース電極またはドレイン電極の一方を含む配線 229、およびトランジスタ 223 のソース電極またはドレイン電極の他方を含む配線 233 が設けられている。半導体膜 231、配線 229、配線 233 上には、ゲート絶縁膜 127 が設けられており、当該ゲート絶縁膜の半導体膜 231 と重畠する領域上にゲート電極 227 が設けられている。ゲート絶縁膜 127 上、ゲート電極 227 上には、トランジスタ 223 の保護絶縁膜として機能する絶縁膜 129、絶縁膜 131、および絶縁膜 132 が設けられている。なお、第 1 の駆動回路 104 に設けられるトランジスタは、導電膜 241 を設けない構成であってもよい。

**【0077】**

トランジスタ 223 において、半導体膜 231 を介して、ゲート電極 227 と重なる導電膜 241 を設けることで、異なるドレイン電圧において、オン電流の立ち上がりゲート電圧のばらつきを低減することができる。また、導電膜 241 と対向する半導体膜 231 の面において、配線 229 および配線 233 の間に流れる電流を制御することが可能であり、トランジスタ間ににおける電気特性のばらつきを低減することができる。また、導電膜 241 を設けることで、周囲の電界の変化が半導体膜 231 へ与える影響を軽減し、トランジスタの信頼性を向上させることができる。さらには、導電膜 241 の電位を、駆動回路の最低電位 (Vss、例えば配線 229 の電位を基準とする場合、配線 229 の電位) と同電位またはそれと同等電位とすることで、トランジスタのしきい値電圧の変動を低減することができ、トランジスタの信頼性を高めることができる。30

**【0078】**

なお、ゲート絶縁膜 127、走査線 107、ゲート電極 227 上に設けられる絶縁膜は、上述した 3 層の構成に限らず、1 層、2 層、または 4 層以上であってもよい。

**【0079】**

次に、上記構造の構成要素について詳細を説明する。

**【0080】**

基板 102 の材質などに大きな制限はないが、少なくとも、半導体装置の作製工程において行う熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、プラスチック基板などがあり、ガラス基板としては、バリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス若しくはアルミニケイ酸ガラス等の無アルカリガラス

20

30

40

50

基板を用いるとよい。また、ステンレス合金などの透光性を有していない基板を用いることもできる。その場合は、基板表面に絶縁膜を設けることが好ましい。なお、基板 102 として石英基板、サファイア基板、単結晶半導体基板、多結晶半導体基板、化合物半導体基板、SOI (Silicon On Insulator) 基板などを用いることもできる。

#### 【0081】

下地絶縁膜 110 は、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたは Ga - Zn 系金属酸化物などの絶縁材料を用い、単層構造または積層構造で形成することができる。下地絶縁膜 110 の一領域の厚さは、30 nm 以上 500 nm 以下、好ましくは 150 nm 以上 10 400 nm 以下とする。

#### 【0082】

半導体膜 111、半導体膜 119、および半導体膜 231 には酸化物半導体膜を用いることが好ましい。当該酸化物半導体膜は、非晶質構造、単結晶構造、または多結晶構造とすることができる。また、半導体膜 111 の一領域の厚さは、1 nm 以上 100 nm 以下、好ましくは 1 nm 以上 50 nm 以下、更に好ましくは 1 nm 以上 30 nm 以下、最も好ましくは 3 nm 以上 20 nm 以下とする。

#### 【0083】

なお、下地絶縁膜 110 の下に、半導体膜 111 のチャネル領域を隠すように、遮光膜を配置することも可能である。遮光膜としては、例えば、導電膜 241 と同時に形成してもよい。

#### 【0084】

半導体膜 111、半導体膜 119、および半導体膜 231 に適用可能な半導体として、エネルギーギャップが 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上であって、3.9 eV 未満、好ましくは 3.7 eV 未満、より好ましくは 3.5 eV 未満の酸化物半導体が挙げられる。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタ 103 のオフ電流を低減することができる。また、当該酸化物半導体は可視光に対する透過率が高く、容量素子 105 の一方の電極に用いることで、透光性を有する容量素子を形成することができ、液晶表示装置等の画素の開口率を向上させることができる。

#### 【0085】

なお、酸化物半導体膜を n 型化することで、酸化物半導体膜の光学バンドギャップは、2.4 eV 以上 3.1 eV 以下、または 2.6 eV 以上 3.0 eV 以下とすることができる。

また、例えば、半導体膜 119 として用いる酸化物半導体膜を原子数比が In : Ga : Zn = 1 : 1 : 1 の In - Ga - Zn 系金属酸化物とした場合、その光学バンドギャップは 3.15 eV である。また、画素電極 121 などに用いられるインジウム錫酸化物の光学バンドギャップは 3.7 eV ~ 3.9 eV である。したがって、画素電極 121 では透過してしまう可視光線の中で最もエネルギーの高い波長を含む光および紫外光を半導体膜 119 では吸収することができる。当該エネルギーの高い波長を含む光および紫外光による目への害が懸念されており、画素 101 に透光性を有する容量素子 105 を用いた半導体装置は、目にやさしいということができる。なお、容量素子 105 が、画素 101 の全ての領域と重ならなくてもよい。少なくとも、容量素子 105 が画素 101 の一部と重なることで、可視光線の中でもエネルギーの高い波長を含む光および紫外光を吸収することができる。

#### 【0086】

半導体膜 111、半導体膜 119、および半導体膜 231 に適用可能な酸化物半導体は、少なくともインジウム (In) 若しくは亜鉛 (Zn) を含むことが好ましい。または、In と Zn の双方を含むことが好ましい。また、当該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすため、それらと共にスタビライザーの一つ、または複数を有

10

20

30

40

50

することが好ましい。

**【0087】**

スタビライザーとしては、ガリウム(Ga)、スズ(Sn)、ハフニウム(Hf)、アルミニウム(Al)、またはジルコニウム(Zr)等がある。また、他のスタビライザーとしては、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)などがある。

**【0088】**

半導体膜111、半導体膜119、および半導体膜231に適用できる酸化物半導体としては、例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二種類の金属を含む酸化物であるIn-Zn系酸化物、Sn-Zn系酸化物、Al-Zn系酸化物、Zn-Mg系酸化物、Sn-Mg系酸化物、In-Mg系酸化物、In-Ga系酸化物、三種類の金属を含む酸化物であるIn-Ga-Zn系酸化物(IGZOとも表記する)、In-Al-Zn系酸化物、In-Sn-Zn系酸化物、Sn-Ga-Zn系酸化物、Al-Ga-Zn系酸化物、Sn-Al-Zn系酸化物、In-Hf-Zn系酸化物、In-Zr-Zn系酸化物、In-Ti-Zn系酸化物、In-Sc-Zn系酸化物、In-Y-Zn系酸化物、In-La-Zn系酸化物、In-Ce-Zn系酸化物、In-Pr-Zn系酸化物、In-Nd-Zn系酸化物、In-Sm-Zn系酸化物、In-Eu-Zn系酸化物、In-Gd-Zn系酸化物、In-Tb-Zn系酸化物、In-Dy-Zn系酸化物、In-Ho-Zn系酸化物、In-Er-Zn系酸化物、In-Tm-Zn系酸化物、In-Yb-Zn系酸化物、In-Lu-Zn系酸化物、四種類の金属を含む酸化物であるIn-Sn-Ga-Zn系酸化物、In-Hf-Ga-Zn系酸化物、In-Al-Ga-Zn系酸化物、In-Sn-Al-Zn系酸化物、In-Sn-Hf-Zn系酸化物、In-Hf-Al-Zn系酸化物を用いることができる。

**【0089】**

ここで、In-Ga-Zn系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

**【0090】**

また、酸化物半導体として、 $InMO_3 (ZnO)_m$  ( $m > 0$ ) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、MnおよびCoから選ばれた一の金属元素または複数の金属元素、若しくは上記のスタビライザーとしての元素を示す。

**【0091】**

例えば、 $In : Ga : Zn = 1 : 1 : 1$  (= 1 / 3 : 1 / 3 : 1 / 3)、 $In : Ga : Zn = 2 : 2 : 1$  (= 2 / 5 : 2 / 5 : 1 / 5)、あるいは $In : Ga : Zn = 3 : 1 : 2$  (= 1 / 2 : 1 / 6 : 1 / 3) の原子数比のIn-Ga-Zn系金属酸化物を用いることができる。あるいは、 $In : Sn : Zn = 1 : 1 : 1$  (= 1 / 3 : 1 / 3 : 1 / 3)、 $In : Sn : Zn = 2 : 1 : 3$  (= 1 / 3 : 1 / 6 : 1 / 2) あるいは $In : Sn : Zn = 2 : 1 : 5$  (= 1 / 4 : 1 / 8 : 5 / 8) の原子数比のIn-Sn-Zn系金属酸化物を用いるとよい。なお、金属酸化物の原子数比は、誤差として上記の原子数比のプラスマイナス 20 % の変動を含む。

**【0092】**

しかし、これらに限られず、必要とする半導体特性および電気特性(電界効果移動度、しきい値電圧等)に応じて適切な原子数比のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。例えば、In-Sn-Zn系酸化物では比較的容易に高い電界効果移動度が得られる。しかしながら、In-Ga-Zn系酸化物でも、バルク内欠陥密度を低くすることにより、電界効果移動度を上げることが

10

20

30

40

50

できる。

**【0093】**

信号線109、導電膜113、容量線115、配線229、および配線233は、抵抗損失を低減するため、抵抗の低い金属膜で形成することが好ましい。例えば、モリブデン(Mo)、チタン(Ti)、タングステン(W)タンタル(Ta)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジム(Nd)、スカンジウム(Sc)などの金属材料またはこれらを主成分とする合金材料を用い、単層構造または積層構造で形成することができる。

**【0094】**

信号線109、導電膜113、容量線115、配線229、および配線233の一例としては、シリコンを含むアルミニウムを用いた単層構造、アルミニウム上にチタンを積層する二層構造、窒化チタン上にチタンを積層する二層構造、窒化チタン上にタングステンを積層する二層構造、窒化タンタル上にタングステンを積層する二層構造、銅-マグネシウム-アルミニウム合金上に銅を積層する二層構造、窒化チタン上に銅を積層し、さらにその上にタングステンを形成する三層構造などがある。

10

**【0095】**

例えば、信号線109、導電膜113、容量線115、配線229、および配線233には、低抵抗材料であるアルミニウムや銅を用いることが好ましい。アルミニウムや銅を用いることで、信号遅延を低減し、表示品位を高めることができる。なお、アルミニウムは耐熱性が低く、ヒロック、ウィスカー、あるいはマイグレーションによる不良が発生しやすい。アルミニウムのマイグレーションを防ぐため、アルミニウムに、モリブデン、チタン、タングステンなどの、アルミニウムよりも融点の高い金属材料を積層することが好ましい。また、銅を用いる場合も、マイグレーションによる不良や銅元素の拡散を防ぐため、モリブデン、チタン、タングステンなどの、銅よりも融点の高い金属材料を積層することが好ましい。

20

**【0096】**

また、信号線109、導電膜113、容量線115、配線229、および配線233の材料として、画素電極121に適用可能な透光性を有する導電材料を用いることができる。なお、本発明の一態様である半導体装置を反射型の表示装置とする場合、画素電極121または基板102に透光性を有していない導電性材料を用いることができる。

30

**【0097】**

ゲート絶縁膜127は、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたはGa-Zn系金属酸化物などの絶縁材料を用い、単層構造または積層構造で形成することができる。なお、半導体膜111である酸化物半導体膜との界面特性を向上させるため、ゲート絶縁膜127において少なくとも半導体膜111と接する領域は、酸素を含む絶縁膜で形成することが好ましい。

**【0098】**

また、ゲート絶縁膜127に、酸素、水素、水などに対するバリア性を有する絶縁膜を用いることで、半導体膜111である酸化物半導体膜からの酸素の外部への拡散と、外部から当該酸化物半導体膜への水素、水等の侵入を防ぐことができる。酸素、水素、水等などに対するバリア性を有する絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム、窒化シリコンなどがある。

40

**【0099】**

また、ゲート絶縁膜127として、ハフニウムシリケート(HfSiO<sub>x</sub>)、窒素を有するハフニウムシリケート(HfSi<sub>x</sub>O<sub>y</sub>N<sub>z</sub>)、窒素を有するハフニウムアルミネート(HfAl<sub>x</sub>O<sub>y</sub>N<sub>z</sub>)、酸化ハフニウム、酸化イットリウムなどのhigh-k材料を用いることでトランジスタ103のゲートリーオフを低減できる。

**【0100】**

50

また、ゲート絶縁膜 127 は、ゲート電極側から以下の積層構造とすることが好ましい。第1の窒化シリコン膜として、欠陥量が少ない窒化シリコン膜を設け、第1の窒化シリコン膜上に第2の窒化シリコン膜として、水素脱離量およびアンモニア脱離量の少ない窒化シリコン膜を設け、第2の窒化シリコン膜上に、上記ゲート絶縁膜 127 として用いることのできる酸素を含む絶縁膜のいずれかを設けることが好ましい。

#### 【0101】

第2の窒化シリコン膜としては、昇温脱離ガス分析法において、水素分子の脱離量が  $5 \times 10^{21}$  分子 /  $\text{cm}^3$  未満、好ましくは  $3 \times 10^{21}$  分子 /  $\text{cm}^3$  以下、さらに好ましくは  $1 \times 10^{21}$  分子 /  $\text{cm}^3$  以下であり、アンモニア分子の脱離量が  $1 \times 10^{22}$  分子 /  $\text{cm}^3$  未満、好ましくは  $5 \times 10^{21}$  分子 /  $\text{cm}^3$  以下、さらに好ましくは  $1 \times 10^{21}$  分子 /  $\text{cm}^3$  以下である窒化シリコン膜を用いることが好ましい。10 上記第1の窒化シリコン膜および第2の窒化シリコン膜をゲート絶縁膜 127 の一部として用いることで、ゲート絶縁膜 127 として、欠陥量が少なく、且つ水素およびアンモニアの脱離量の少ないゲート絶縁膜を形成することができる。したがって、ゲート絶縁膜 127 に含まれる水素および窒素の半導体膜 111 への拡散量を低減することが可能となる。

#### 【0102】

酸化物半導体を用いたトランジスタにおいて、酸化物半導体膜およびゲート絶縁膜の界面またはゲート絶縁膜に捕獲準位（界面準位ともいう）が存在すると、トランジスタのしきい値電圧の変動、代表的にはしきい値電圧のマイナス方向への変動が起こりやすくなる。20 また当該捕獲準位は、トランジスタがオン状態となるときにドレイン電流が一桁変化するのに必要なゲート電圧を示すサブスレッシュルド係数（S値）の増大の原因ともなる。また、上記電気特性の変化は一様ではなく、トランジスタごとに電気特性がばらつくという問題がある。このため、ゲート絶縁膜として、欠陥量の少ない窒化シリコン膜を用いること、また、半導体膜 111 と接する領域に酸素を含む絶縁膜を設けることで、しきい値電圧のマイナスシフトを低減すると共に、S値の増大を抑制することができる。

#### 【0103】

ゲート絶縁膜 127 の一領域の厚さは、 $5 \text{ nm}$  以上  $400 \text{ nm}$  以下、より好ましくは  $10 \text{ nm}$  以上  $300 \text{ nm}$  以下、より好ましくは  $50 \text{ nm}$  以上  $250 \text{ nm}$  以下とする。

#### 【0104】

走査線 107、ゲート電極 227 および導電膜 241 は、信号線 109、導電膜 113、容量線 115、配線 229、および配線 233 に適用できる材料を用い、単層構造または積層構造で形成することができる。30

#### 【0105】

さらに、走査線 107、ゲート電極 227 および導電膜 241 の一部の材料として、窒素を含む金属酸化物、具体的には、窒素を含む In - Ga - Zn 系酸化物や、窒素を含む In - Sn 系酸化物や、窒素を含む In - Ga 系酸化物や、窒素を含む In - Zn 系酸化物や、窒素を含む Sn 系酸化物や、窒素を含む In 系酸化物や、金属窒化膜（InN、SnNなど）を用いることができる。これらの材料は  $5 \text{ eV}$ （電子ボルト）以上の仕事関数を有する。トランジスタ 103 の半導体膜 111 に酸化物半導体を用いる場合、走査線 107（トランジスタ 103 のゲート電極）として窒素を含む金属酸化物を用いることで、トランジスタ 103 のしきい値電圧をプラス方向に変動させることができ、所謂ノーマリーオフ特性を有するトランジスタを実現できる。例えば、窒素を含む In - Ga - Zn 系酸化物を用いる場合、少なくとも半導体膜 111 の酸化物半導体膜より高い窒素濃度、具体的には窒素濃度が 7 原子% 以上の In - Ga - Zn 系酸化物を用いることができる。40

#### 【0106】

絶縁膜 129 および絶縁膜 131 は、例えば、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたは Ga - Zn 系金属酸化物などの酸化絶縁材料を用い、単層構造または積層構造で形成することができる。

#### 【0107】

絶縁膜 129 の一領域の厚さは、 $5 \text{ nm}$  以上  $150 \text{ nm}$  以下、好ましくは  $5 \text{ nm}$  以上  $50 \text{ nm}$ 50

n m 以下、より好ましくは 1 0 n m 以上 3 0 n m 以下とする。また、絶縁膜 1 3 1 の一領域の厚さは、3 0 n m 以上 5 0 0 n m 以下、好ましくは 1 5 0 n m 以上 4 0 0 n m 以下とする。

#### 【 0 1 0 8 】

絶縁膜 1 2 9 および絶縁膜 1 3 1 の一方または双方は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜であることが好ましい。このようにすることで、当該酸化物半導体膜からの酸素の脱離を防止するとともに、酸素過剰領域に含まれる酸素をゲート絶縁膜 1 2 7 を介して酸化物半導体膜に拡散させ、酸素欠損を補填することが可能となる。例えば、昇温脱離ガス分析（以下、T D S 分析とする）によって測定される、1 0 0 以上 7 0 0 以下、好ましくは 1 0 0 以上 5 0 0 以下の加熱処理における酸素分子の放出量が、 $1 . 0 \times 1 0 ^ { 1 8 }$  分子 / c m <sup>3</sup> 以上ある酸化絶縁膜を用いることで、当該酸化物半導体膜に含まれる酸素欠損を補填することができる。なお、絶縁膜 1 2 9 および絶縁膜 1 3 1 の一方または双方において、化学量論的組成よりも過剰に酸素を含む領域（酸素過剰領域）が部分的に存在している酸化絶縁膜であってもよく、少なくとも半導体膜 1 1 1 と重畳する領域に酸素過剰領域が存在することで、当該酸化物半導体膜からの酸素の脱離を防止するとともに、酸素過剰領域に含まれる酸素を酸化物半導体膜に拡散させ、酸素欠損を補填することが可能となる。

#### 【 0 1 0 9 】

絶縁膜 1 3 1 が化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜である場合、絶縁膜 1 2 9 は、酸素を透過する酸化絶縁膜とすることが好ましい。なお、絶縁膜 1 2 9 において、外部から絶縁膜 1 2 9 に入った酸素は、全て絶縁膜 1 2 9 を通過して拡散せず、絶縁膜 1 2 9 にとどまる酸素もある。また、あらかじめ絶縁膜 1 2 9 に含まれており、絶縁膜 1 2 9 から外部に拡散する酸素もある。そこで、絶縁膜 1 2 9 は酸素の拡散係数が大きい酸化絶縁膜であることが好ましい。

#### 【 0 1 1 0 】

また、絶縁膜 1 2 9 および絶縁膜 1 3 1 の一方または双方が窒素に対するバリア性を有する絶縁膜であることが好ましい。例えば、緻密な酸化絶縁膜とすることで窒素に対するバリア性を有することができ、具体的には、2 5 において 0 . 5 重量 % のフッ化水素酸を用いた場合のエッチング速度が 1 0 n m / 分以下である酸化絶縁膜とすることが好ましい。

#### 【 0 1 1 1 】

なお、絶縁膜 1 2 9 および絶縁膜 1 3 1 の一方または双方を、酸化窒化シリコンまたは窒化酸化シリコンなど、窒素を含む酸化絶縁膜とする場合、S I M S より得られる窒素濃度は、S I M S 検出下限以上  $3 \times 1 0 ^ { 2 0 }$  atoms / c m <sup>3</sup> 未満、好ましくは  $1 \times 1 0 ^ { 1 8 }$  atoms / c m <sup>3</sup> 以上  $1 \times 1 0 ^ { 2 0 }$  atoms / c m <sup>3</sup> 以下とする領域を有するように形成することが好ましい。このようにすることで、トランジスタ 1 0 3 に含まれる半導体膜 1 1 1 への窒素の移動量を少なくすることができる。また、このようにすることで、窒素を含む酸化絶縁膜自体の欠陥量を少なくすることができる。

#### 【 0 1 1 2 】

また、絶縁膜 1 3 2 は、例えば窒化酸化シリコン、窒化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化絶縁材料を用い、単層構造または積層構造で形成することができる。

#### 【 0 1 1 3 】

絶縁膜 1 3 2 として、水素含有量が少ない窒化絶縁膜を設けてもよい。当該窒化絶縁膜としては、例えば、膜の表面温度が 1 0 0 以上 7 0 0 以下、好ましくは 1 0 0 以上 5 0 0 以下の加熱処理で行われるT D S 分析によって測定される水素分子の放出量が、 $5 . 0 \times 1 0 ^ { 2 1 }$  分子 / c m <sup>3</sup> 未満であり、好ましくは  $3 . 0 \times 1 0 ^ { 2 1 }$  分子 / c m <sup>3</sup> 未満であり、さらに好ましくは  $1 . 0 \times 1 0 ^ { 2 1 }$  分子 / c m <sup>3</sup> 未満である窒化絶縁膜を用いることができる。

#### 【 0 1 1 4 】

10

20

30

40

50

絶縁膜 132 の一領域は、外部から水素や水などの不純物の侵入を抑制する機能を発揮できる厚さとすることが好ましい。例えば、50 nm 以上 200 nm 以下、好ましくは 50 nm 以上 150 nm 以下、さらに好ましくは 50 nm 以上 100 nm 以下とする。絶縁膜 132 を設けることで、炭素等の不純物が絶縁膜 132 でプロッキングされ、トランジスタ 103 およびトランジスタ 223 の半導体膜 111 および半導体膜 231 への不純物の外部からの移動が低減されるため、トランジスタの電気特性のばらつきを低減することが可能である。

#### 【 0115 】

なお、ゲート絶縁膜 127、走査線 107、ゲート電極 227 上に設けられる絶縁膜が 1 層である場合は、絶縁膜 131 を設けることが好ましい。また、絶縁膜が 2 層である場合は、当該半導体膜側から絶縁膜 131、絶縁膜 132 の順で設けることが好ましい。

10

#### 【 0116 】

また、ゲート絶縁膜 127、走査線 107、ゲート電極 227 と、画素電極 121、導電膜 241 およびそれらと同時に形成することのできる配線等との間に形成される絶縁膜としては、有機シランガスを用いた CVD 法（化学気相成長法）により形成した酸化絶縁膜、代表的には酸化シリコン膜が含まれていてもよい。

#### 【 0117 】

当該酸化シリコン膜は 300 nm 以上 600 nm 以下で設けることができる。有機シランガスとしては、珪酸エチル（TEOS：化学式 Si(O<sub>2</sub>H<sub>5</sub>)<sub>4</sub>）、テトラメチルシリラン（TMS：化学式 Si(CH<sub>3</sub>)<sub>4</sub>）、テトラメチルシクロテトラシロキサン（TMCTS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（SiH(O<sub>2</sub>H<sub>5</sub>)<sub>3</sub>）、トリスジメチルアミノシラン（SiH(N(CH<sub>3</sub>)<sub>2</sub>)<sub>3</sub>）などのシリコン含有化合物を用いることができる。

20

#### 【 0118 】

当該酸化シリコン膜を有機シランガスを用いた CVD 法により形成することで、基板 102 上に形成される素子部表面の平坦性を高めることができる。この結果、有機樹脂で形成される平坦化膜を設けなくとも、液晶の配向乱れを低減し、光漏れの低減ができると共に、コントラストを高めることができる。もちろん、当該酸化シリコン膜の代わりに有機樹脂を用いてもよいし、当該酸化シリコン膜と有機樹脂を含む積層を用いてもよい。

30

#### 【 0119 】

画素電極 121 は、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電材料で形成することができる。

#### 【 0120 】

次に、本実施の形態に示す画素 101 に含まれる各構成要素について説明する。

#### 【 0121 】

図 4 (A) は、上述した画素 101 の回路図の一例である。画素 101 は、トランジスタ 103、容量素子 105、および液晶素子 108 を有する。トランジスタ 103 のゲート電極は走査線 107 に電気的に接続され、ソース電極またはドレイン電極の一方は信号線 109 と電気的に接続され、ソース電極またはドレイン電極の他方は容量素子 105 の一方の電極および液晶素子 108 の一方の電極（画素電極）と電気的に接続される。また、容量素子 105 の他方の電極は容量線 115 に電気的に接続され、液晶素子 108 の他方の電極（対向電極）は、対向電極に対向電位を供給する配線に電気的に接続される。

40

#### 【 0122 】

液晶素子 108 は、トランジスタ 103 および画素電極が形成される基板と、対向する基板（例えば、対向電極が形成される基板）とで挟持される液晶の光学的変調作用によって、光の透過または非透過を制御する素子である。なお、液晶の光学的変調作用は、液晶に

50

かかる電界（縦方向の電界または斜め方向の電界を含む）によって制御される。なお、画素電極および対向電極（共通電極ともいう）が一方の基板側に形成される場合は、液晶にかかる電界は横方向の電界となる。

#### 【0123】

また、図4(B)は、画素101の詳細な回路図の一例である。図4(B)および図2に示すように、トランジスタ103は、ゲート電極を含む走査線107と、ソース電極またはドレイン電極の一方を含む信号線109と、ソース電極またはドレイン電極の他方を含む導電膜113とを有する。

#### 【0124】

容量素子105においては、容量線115と接続する半導体膜119が一方の電極として機能する。また、ソース電極またはドレイン電極の他方を含む導電膜113に接続する画素電極121が他方の電極として機能する。また、半導体膜119および画素電極121の間に設けられる、絶縁膜129、絶縁膜131、絶縁膜132が誘電体膜として機能する。

#### 【0125】

液晶素子108は、画素電極121、対向電極154、並びに画素電極121および対向電極154の間に設けられる液晶層で構成される。

#### 【0126】

容量素子105において、半導体膜119は、半導体膜111と同様に高抵抗であっても、容量素子105の電極として機能する。なぜなら、画素電極121をゲート電極、絶縁膜129、絶縁膜131、および絶縁膜132をゲート絶縁膜、容量線115をソース電極またはドレイン電極と機能させることができ、この結果、容量素子105をトランジスタと同様に動作させ、半導体膜119を導通状態にすることができるからである。したがって、半導体膜119を容量素子105の一方の電極として機能させることができる。

#### 【0127】

次に、図1および図2に示す半導体装置の作製方法について、図5、図6を用いて説明する。

#### 【0128】

まず、基板102上に導電膜241を形成し、当該導電膜を覆うように下地絶縁膜110を形成する。

#### 【0129】

導電膜241は、前述した材料を用いて導電膜を形成し、当該導電膜上にマスクを形成し、当該マスクを用いて加工することにより形成できる。当該導電膜は、蒸着法、CVD法、スパッタリング法、スピノコート法などの各種成膜方法を用いることができる。なお、当該導電膜の厚さは特に限定されず、形成する時間や所望の抵抗率などを考慮して決めることができる。当該マスクは、例えばフォトリソグラフィ工程によって形成したレジストマスクとすることができます。また、当該導電膜の加工はドライエッチングおよびウェットエッチングの一方または双方によって行うことができる。

#### 【0130】

下地絶縁膜110は、前述した材料を用いて形成することができる。当該下地絶縁膜は、蒸着法、CVD法、スパッタリング法、スピノコート法などの各種成膜方法を用いることができる。

#### 【0131】

次に、半導体膜111、半導体膜119、および半導体膜231を形成する（図1参照）。半導体膜111、半導体膜119、および半導体膜231は、前述した酸化物半導体を用いて酸化物半導体膜を形成し、当該酸化物半導体膜上にマスクを形成し、当該マスクを用いて加工することにより形成できる。当該酸化物半導体膜は、スパッタリング法、塗布法、パルスレーザー蒸着法、レーザーアブレーション法などを用いて形成することができる。印刷法を用いることで、素子分離された半導体膜111および半導体膜119を下地

10

20

30

40

50

絶縁膜 110 上に直接形成することができる。スパッタリング法で当該酸化物半導体膜を形成する場合、プラズマを発生させるための電源装置は、RF 電源装置、AC 電源装置またはDC 電源装置などを適宜用いることができる。スパッタリングガスは、希ガス（代表的にはアルゴン）、酸素、希ガスおよび酸素の混合ガスを適宜用いる。なお、希ガスおよび酸素の混合ガスの場合、希ガスに対して酸素のガス比を高めることが好ましい。また、ターゲットは、形成する酸化物半導体膜の組成にあわせて、適宜選択すればよい。なお、当該マスクは、例えばフォトリソグラフィ工程によって形成したレジストマスクとすることができる。また、当該酸化物半導体膜の加工はドライエッチングおよびウェットエッチングの一方または双方によって行うことができる。所望の形状にエッチングできるよう、材料に合わせてエッティング条件（エッティングガスやエッティング液、エッティング時間、温度など）を適宜設定する。

#### 【0132】

また、上記酸化物半導体膜は、CVD 法により形成してもよい。CVD 法としては MOCVD (Metal Organic Chemical Vapor Deposition) 法や ALD (Atomic Layer Deposition) 法などの熱 CVD 法を用いても良い。

#### 【0133】

熱 CVD 法は、プラズマを使わない成膜方法のため、プラズマダメージにより欠陥が生成されることが無いという利点を有する。

#### 【0134】

熱 CVD 法は、原料ガスと酸化剤を同時にチャンバー内に送り、チャンバー内を大気圧または減圧下とし、基板近傍または基板上で反応させて基板上に堆積させることで成膜を行ってもよい。

#### 【0135】

また、ALD 法は、チャンバー内を大気圧または減圧下とし、反応のための原料ガスが順次にチャンバーに導入され、そのガス導入の順序を繰り返すことで成膜を行ってもよい。例えば、それぞれのスイッチングバルブ（高速バルブとも呼ぶ）を切り替えて 2 種類以上の原料ガスを順番にチャンバーに供給し、複数種の原料ガスが混ざらないように第 1 の原料ガスと同時またはその後に不活性ガス（アルゴン、或いは窒素など）などを導入し、第 2 の原料ガスを導入する。なお、同時に不活性ガスを導入する場合には、不活性ガスはキヤリアガスとなり、また、第 2 の原料ガスの導入時にも同時に不活性ガスを導入してもよい。また、不活性ガスを導入する代わりに真空排気によって第 1 の原料ガスを排出した後、第 2 の原料ガスを導入してもよい。第 1 の原料ガスが基板の表面に吸着して第 1 の層を成膜し、後から導入される第 2 の原料ガスと反応して、第 2 の層が第 1 の層上に積層されて薄膜が形成される。このガス導入順序を制御しつつ所望の厚さになるまで複数回繰り返すことで、段差被覆性に優れた薄膜を形成することができる。薄膜の厚さは、ガス導入順序を繰り返す回数によって調節することができるため、精密な膜厚調節が可能であり、微細なトランジスタを作製する場合に適している。

#### 【0136】

例えば、In - Ga - Zn - O 膜を成膜する場合には、トリメチルインジウム、トリメチルガリウム、およびジメチル亜鉛を用いる。なお、トリメチルインジウムの化学式は、In (CH<sub>3</sub>)<sub>3</sub> である。また、トリメチルガリウムの化学式は、Ga (CH<sub>3</sub>)<sub>3</sub> である。また、ジメチル亜鉛の化学式は、Zn (CH<sub>3</sub>)<sub>2</sub> である。また、これらの組み合わせに限定されず、トリメチルガリウムに代えてトリエチルガリウム（化学式 Ga (C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>）を用いることもでき、ジメチル亜鉛に代えてジエチル亜鉛（化学式 Zn (C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>）を用いることもできる。

#### 【0137】

In - Ga - Zn - O 膜を ALD 法で成膜する場合には、In (CH<sub>3</sub>)<sub>3</sub> ガスと O<sub>3</sub> ガスを順次繰り返し導入して InO<sub>2</sub> 層を形成し、その後、Ga (CH<sub>3</sub>)<sub>3</sub> ガスと O<sub>3</sub> ガスを同時に導入して GaO 層を形成し、更にその後 Zn (CH<sub>3</sub>)<sub>2</sub> と O<sub>3</sub> ガスを同時に

10

20

30

40

50

導入してZnO層を形成する。なお、これらの層の順番はこの例に限らない。また、これらのガスを混ぜてIn-Ga-O層やIn-Zn-O層、Ga-In-O層、Zn-In-O層、Ga-Zn-O層などの混合化合物層を形成しても良い。なお、O<sub>3</sub>ガスに変えてAr等の不活性ガスでバーピングして得られたH<sub>2</sub>Oガスを用いても良いが、Hを含まないO<sub>3</sub>ガスを用いる方が好ましい。また、In(CH<sub>3</sub>)<sub>3</sub>ガスにかえて、In(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いても良い。また、Ga(CH<sub>3</sub>)<sub>3</sub>ガスにかえて、Ga(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いても良い。また、In(CH<sub>3</sub>)<sub>3</sub>ガスにかえて、In(C<sub>2</sub>H<sub>5</sub>)<sub>3</sub>ガスを用いても良い。また、Zn(CH<sub>3</sub>)<sub>2</sub>ガスを用いても良い。

#### 【0138】

半導体膜111、半導体膜119、および半導体膜231を形成した後に加熱処理をし、半導体膜111、半導体膜119、および半導体膜231である酸化物半導体膜の脱水素化または脱水化をすることが好ましい。当該加熱処理の温度は、代表的には、150以上基板歪み点未満、好ましくは200以上450以下、更に好ましくは300以上450以下とする。なお、当該加熱処理は半導体膜111、半導体膜119、および半導体膜231に加工する前の酸化物半導体膜に行ってもよい。

10

#### 【0139】

当該加熱処理において、加熱処理装置は電気炉に限らず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置であっても良い。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて加熱処理を行う装置である。

20

#### 【0140】

当該加熱処理は、窒素、酸素、超乾燥空気(水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、または希ガス(アルゴン、ヘリウム等)の雰囲気下で行えばよい。なお、上記窒素、酸素、超乾燥空気、または希ガスに水素、水などが含まれないことが好ましい。不活性ガス雰囲気で加熱した後、酸素雰囲気で加熱してもよい。なお、処理時間は3分~24時間とすることが好ましい。

30

#### 【0141】

ここで、半導体膜119にはドーパントを添加してもよい。半導体膜119にドーパントを添加する方法は、半導体膜119以外の領域にマスクを設けて、当該マスクを用いて、水素、ホウ素、窒素、フッ素、アルミニウム、リン、ヒ素、インジウム、スズ、アンチモンおよび希ガス元素から選ばれた一種以上のドーパントをイオン注入法またはイオンドーピング法などで添加する。また、イオン注入法またはイオンドーピング法の代わりに当該ドーパントの含むプラズマに半導体膜119を曝すことで、当該ドーパントを添加してもよい。なお、ドーパントを添加した後、加熱処理をおこなってもよい。当該加熱処理は、半導体膜111および半導体膜119の脱水素化または脱水化を行う加熱処理の詳細を参照して適宜行うことができる。

40

#### 【0142】

次に、信号線109、導電膜113、容量線115、配線229、および配線233を形成する。信号線109、導電膜113、容量線115、配線229、および配線233は、前述した材料を用いて導電膜を形成し、当該導電膜上にマスクを形成し、当該マスクを用いて加工することにより形成できる。当該マスクおよび当該加工は、導電膜241と同じようにして行うことができる。

#### 【0143】

次に、下地絶縁膜110、半導体膜111、半導体膜119、半導体膜231、信号線109、導電膜113、容量線115、配線229、および配線233を覆うようにゲート

50

絶縁膜 127 を形成する。

**【0144】**

ゲート絶縁膜 127 は、前述した材料を用いて、CVD 法またはスパッタリング法などの各種成膜方法を用いて形成することができる。また、ゲート絶縁膜 127 に酸化ガリウムを適用する場合は、MOCVD (Metal Organic Chemical Vapor Deposition) 法を用いて形成することができる。

**【0145】**

次に、ゲート絶縁膜 127 上の半導体膜 111 と重畳する領域に走査線 107 を形成し、半導体膜 231 と重畳する領域にゲート電極 227 を形成する（図 5 (B) 参照）。

**【0146】**

走査線 107、およびゲート電極 227 は、前述した材料を用いて導電膜を形成し、当該導電膜上にマスクを形成し、当該マスクを用いて加工することにより形成できる。当該マスクおよび当該加工は、導電膜 241 と同じようにして行うことができる。

**【0147】**

次に、ゲート絶縁膜 127、走査線 107、およびゲート電極 227 上に絶縁膜 129、絶縁膜 131、および絶縁膜 132 を形成する（図 6 (A) 参照）。なお、絶縁膜 129、絶縁膜 131 および絶縁膜 132 は、連続して形成することが好ましい。連続して形成することで、絶縁膜 129、絶縁膜 131 および絶縁膜 132 のそれぞれの界面に不純物が混入することを抑制できる。

**【0148】**

絶縁膜 129、絶縁膜 131、および絶縁膜 132 は、前述した材料を用いて、CVD 法またはスパッタリング法などの各種成膜方法により形成することができる。

**【0149】**

絶縁膜 129 は、例えば、前述した酸化絶縁膜を用いて形成することができる。なお、ここでは当該酸化絶縁膜として、酸化シリコン膜または酸化窒化シリコン膜を形成する場合について記載する。当該形成条件は、プラズマ CVD 装置の真空排気された処理室内に載置された基板を 180 以上 400 以下、さらに好ましくは 200 以上 370 以下に保持し、処理室に原料ガスのシリコンを含む堆積性気体および酸化性気体を導入して処理室内における圧力を 20 Pa 以上 250 Pa 以下、さらに好ましくは 40 Pa 以上 200 Pa 以下とし、処理室内に設けられた電極に高周波電力を供給する条件である。

**【0150】**

シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シランなどがある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素などがある。

**【0151】**

なお、シリコンを含む堆積性気体に対する酸化性気体量を 100 倍以上とすることで、絶縁膜 129 に含まれる水素含有量を低減することができると共に、絶縁膜 129 に含まれるダングリングボンドを低減することができる。絶縁膜 131 から拡散する酸素は、絶縁膜 129 に含まれるダングリングボンドによって捕獲される場合があるため、絶縁膜 129 に含まれるダングリングボンドが低減されていると、絶縁膜 131 に含まれる酸素を効率よくゲート絶縁膜 127 を介して半導体膜 111 および半導体膜 231 へ拡散させ、半導体膜 111 および半導体膜 231 である酸化物半導体膜に含まれる酸素欠損を補填することができる。この結果、当該酸化物半導体膜に混入する水素量を低減できると共に酸化物半導体膜に含まれる酸素欠損を低減させることができる。

**【0152】**

絶縁膜 131 を上記の酸素過剰領域を含む酸化絶縁膜または化学量論的組成を満たす酸素よりも多くの酸素を含む酸化絶縁膜とする場合、以下の形成条件を用いて形成することができる。なお、ここでは当該酸化絶縁膜として、酸化シリコン膜または酸化窒化シリコン膜を形成する場合について記載する。当該形成条件としては、プラズマ CVD 装置の真空排気された処理室内に載置された基板を 180 以上 260 以下、さらに好ましくは 1

10

20

30

40

50

80 以上230 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下、さらに好ましくは100Pa以上200Pa以下とし、処理室内に設けられた電極に0.17W/cm<sup>2</sup>以上0.5W/cm<sup>2</sup>以下、さらに好ましくは0.25W/cm<sup>2</sup>以上0.35W/cm<sup>2</sup>以下の高周波電力を供給する条件が一例として挙げられる。

#### 【0153】

絶縁膜131の原料ガスは、絶縁膜129に適用できる原料ガスとすることができます。

#### 【0154】

絶縁膜131の形成条件として、上記圧力の反応室において上記パワー密度の高周波電力を供給することで、プラズマ中で原料ガスの分解効率が高まり、酸素ラジカルが増加し、原料ガスの酸化が進むため、絶縁膜131中における酸素含有量が化学量論的組成よりも多くなる。しかしながら、基板温度が上記形成条件の温度であると、シリコンと酸素の結合力が弱いため、加熱により酸素の一部が脱離する。この結果、化学量論的組成を満たす酸素よりも多くの酸素を含み、加熱により酸素の一部が脱離する酸化絶縁膜を形成することができる。

10

#### 【0155】

また、絶縁膜131は膜厚を厚くすることで加熱によって脱離する酸素の量を多くすることができます。絶縁膜131は絶縁膜129より厚く設けることが好ましい。絶縁膜129を設けることで絶縁膜131を厚く設ける場合でも被覆性を良好にすることができます。

20

#### 【0156】

絶縁膜132を水素含有量が少ない窒化絶縁膜で設ける場合、以下の形成条件を用いて形成できる。なお、ここでは当該窒化絶縁膜として、窒化シリコン膜を形成する場合について記載する。当該形成条件の一例としては、プラズマCVD装置の真空排気された処理室内に載置された基板を80 以上400 以下、さらに好ましくは200 以上370 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下とし、好ましくは100Pa以上200Pa以下とし、処理室内に設けられた電極に高周波電力を供給する条件が挙げられる。

#### 【0157】

絶縁膜132の原料ガスとしては、シリコンを含む堆積性気体、窒素、およびアンモニアを用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シランなどがある。また、窒素の流量は、アンモニアの流量に対して5倍以上50倍以下、好ましくは10倍以上50倍以下とすることが好ましい。なお、原料ガスとしてアンモニアを用いることで、シリコンを含む堆積性気体および窒素の分解を促すことができる。これは、アンモニアがプラズマエネルギーや熱エネルギーによって解離し、解離することで生じるエネルギーが、シリコンを含む堆積性気体分子の結合および窒素分子の結合の分解に寄与するためである。このようにすることで、水素含有量が少なく、外部から水素や水などの不純物の侵入を抑制することが可能な窒化シリコン膜を形成することができる。

30

#### 【0158】

少なくとも絶縁膜131を形成した後に加熱処理を行い、絶縁膜129または絶縁膜131に含まれる過剰酸素をゲート絶縁膜127を介して半導体膜111および半導体膜231に拡散させ、半導体膜111および半導体膜231である酸化物半導体膜の酸素欠損を補填することが好ましい。なお、当該加熱処理は、半導体膜111および半導体膜231の脱水素化または脱水化を行う加熱処理の詳細を参照して適宜行うことができる。

40

#### 【0159】

次に、絶縁膜129、絶縁膜131、および絶縁膜132の導電膜113と重畳する領域に、導電膜113に達する開口117(図1参照)を形成する。

#### 【0160】

次に、画素電極121を形成することで、図1、図2に示す半導体装置を作製することができます。

50

できる（図6（B）参照）。画素電極121は、前述した材料を用い、開口117を通じて導電膜113に接する導電膜を形成し、当該導電膜上にマスクを形成し、当該マスクを用いて加工することにより形成できる。なお、当該マスクおよび当該加工は、導電膜241と同じようにして行うことができる。

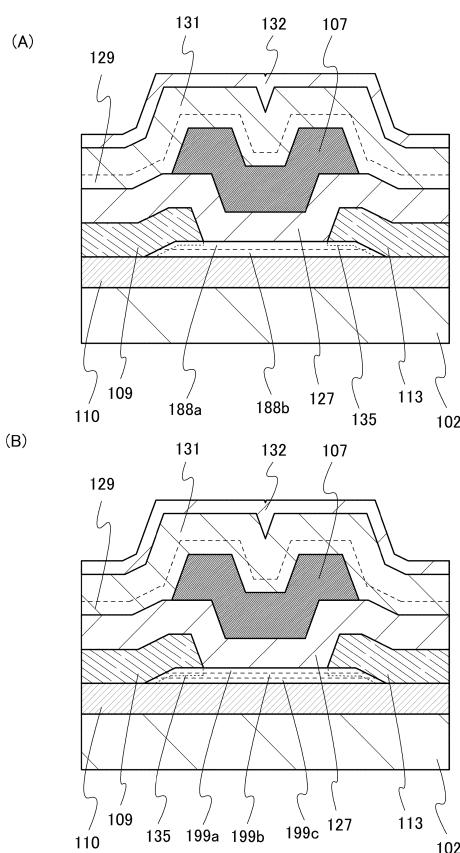

#### 【0161】

なお、本発明の一態様である半導体装置においては、容量素子の構成を適宜変更することができる。例えば、図7（A）に示す容量素子105の断面図のように、容量素子105の誘電体部分からゲート絶縁膜127を取り除いてもよい。このようにすることで、誘電体部分の膜厚を薄くすることができ、容量素子105の電荷容量を向上させることができる。なお、ゲート絶縁膜127を部分的に取り除くには、当該ゲート絶縁膜上にマスクを形成し、当該マスクを用いて加工することにより形成できる。なお、当該マスクおよび当該加工は、導電膜241と同じようにして行うことができる。なお、ハーフトーンマスクを用いて、ゲート電極227を形成する際に、ゲート絶縁膜127の一部を除去してもよい。この場合、フォトリソグラフィ工程を減らすことができる。また、加えて、絶縁膜129または絶縁膜131のどちらか一方を取り除く構成としてもよい。

10

#### 【0162】

また、図7（B）に示す容量素子105の断面図のように、容量素子105の誘電体部分からゲート絶縁膜127、絶縁膜129、および絶縁膜131を取り除いてもよい。このようにすることで、さらに誘電体部分の膜厚が薄くなり、容量素子105の電荷容量を向上させることができる。

20

#### 【0163】

また、図7（B）に示す容量素子105では、半導体膜119と絶縁膜132が接する構成となる。絶縁膜132は、前述したように窒化絶縁膜とすることが好ましい。窒化絶縁膜には窒素および水素が多量に含まれており、それらを半導体膜119に拡散させることができ。半導体膜119として酸化物半導体を用いる場合、酸化物半導体内に取り込まれた窒素および水素の一部はキャリアを生成するドナー準位の形成に寄与するため、酸化物半導体層をn型化することができる。したがって、半導体膜119の導電率を向上させることができ、半導体膜119への不純物のドーピング工程などを省くことができる。

#### 【0164】

また、図8に示すように、容量素子105の一方の電極である半導体膜119と下地絶縁膜110との間に窒化絶縁膜118を設ける構成であってもよい。このような構成では、図7（B）と同様に、窒化絶縁膜118から半導体膜119に窒素および水素を拡散させることができ、半導体膜119の導電率を向上させることができる。なお、窒化絶縁膜118を形成するには、絶縁膜132として適用できる膜を形成し、当該膜上にマスクを形成し、当該マスクを用いて加工することにより形成できる。なお、当該マスクおよび当該加工は、導電膜241と同じようにして行うことができる。また、当該容量素子に、図7（A）または（B）に示す容量素子の構成を組み合わせてもよい。

30

#### 【0165】

また、本発明の一態様である半導体装置においては、画素内に設けられるトランジスタの形状は図1および図2に示したトランジスタの形状に限定されず、適宜変更することができる。例えば、トランジスタにおいて、信号線109に含まれるソース電極またはドレイン電極の一方がU字型（C字型、コの字型、または馬蹄型）とし、ソース電極またはドレイン電極の他方を含む導電膜を囲む形状のトランジスタであってもよい。このような形状とすることで、トランジスタの面積が小さくても、十分なチャネル幅を確保することができとなり、トランジスタの導通時に流れるドレイン電流（オン電流ともいう）の量を増やすことが可能となる。

40

#### 【0166】

また、上記に示す画素101において、トランジスタとして、1つのゲート電極を有するトランジスタを示したが、半導体膜111を介して対向する2つのゲート電極を有するトランジスタを用いることができる。なお、2つのゲート電極を有するトランジスタの構成

50

としては、例えば、図2に示すゲート電極227、および導電膜241を有する第1の駆動回路104に用いられるトランジスタを参照することができる。

#### 【0167】

上記2つのゲート電極を有するトランジスタは、本実施の形態で説明したトランジスタ103の下地絶縁膜110の下に導電膜を有する。導電膜は、少なくとも半導体膜111のチャネル形成領域と重なる。導電膜を半導体膜111のチャネル形成領域と重なる位置に設けることによって、導電膜の電位は、信号線109に入力されるビデオ信号の最低電位とすることが好ましい。この結果、導電膜と対向する半導体膜111の面において、ソース電極およびドレイン電極の間に流れる電流を制御することが可能であり、トランジスタの電気特性のばらつきを低減することができる。また、導電膜を設けることで、周囲の電界の変化が半導体膜111へ与える影響を軽減し、トランジスタの信頼性を向上させることができる。10

#### 【0168】

なお、上記導電膜は、導電膜241、走査線107、信号線109、画素電極121などと同様の材料および方法により形成することができる。

#### 【0169】

以上より、容量素子の一方の電極として、トランジスタに含まれる半導体膜と同じ形成工程で形成される半導体膜を用いることで、開口率を高めつつ、電荷容量を増大させた容量素子を有する半導体装置を作製することができる。この結果、表示品位の優れた半導体装置を得ることができる。20

#### 【0170】

また、容量素子の一方の電極として、トランジスタに含まれる半導体膜と同じ形成工程で形成される半導体膜を用いることでフォトリソグラフィ工程に必要なマスク枚数を増加させることなく、開口率が高く、電荷容量が大きい容量素子を有する半導体装置を作製することができる。

#### 【0171】

また、トランジスタに含まれる半導体膜である酸化物半導体膜は酸素欠損が低減され、水素などの不純物が低減されていることから、本発明の一態様である半導体装置は、良好な電気特性を有する半導体装置となる。

#### 【0172】

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせすることができる。30

#### 【0173】

##### (実施の形態2)

本実施の形態では、上記実施の形態で説明した半導体装置に含まれているトランジスタおよび容量素子において、半導体膜として用いられる酸化物半導体膜に適用可能な一態様について説明する。

#### 【0174】

酸化物半導体は、非単結晶を有してもよい。非単結晶は、例えば、CAAC(C Axis Aligned Crystal)、多結晶、微結晶、非晶質部を有する。40

#### 【0175】

酸化物半導体は、CAACを有してもよい。なお、CAACを有する酸化物半導体を、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)と呼ぶ。

#### 【0176】

CAAC-OSは、透過型電子顕微鏡(TEM: Transmission Electron Microscope)による観察像で、結晶部を確認することができる場合がある。CAAC-OSに含まれる結晶部は、TEMによる観察像で、一辺100nmの立方体内に収まる大きさであることが多い。また、CAAC-OSは、TEMによる観察像で、結晶部と結晶部との境界を明確に確認できない場合がある。また、CAAC-OSは50

、TEMによる観察像で、粒界（グレインバウンダリーともいう。）を明確に確認できない場合がある。CAAC-OSは、明確な粒界を有さないため、不純物が偏析することが少ない。また、CAAC-OSは、明確な粒界を有さないため、欠陥準位密度が高くなることが少ない。また、CAAC-OSは、明確な粒界を有さないため、電子移動度の低下が小さい。

#### 【0177】

CAAC-OSは、複数の結晶部を有し、当該複数の結晶部においてc軸が被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃っている場合がある。そのため、CAAC-OSは、X線回折(XRD:X-Ray Diffraction)装置を用い、out-of-plane法による分析を行うと、 $2\theta$ が $31^\circ$ 近傍のピークが現れる場合がある。 $2\theta$ が $31^\circ$ 近傍のピークは、InGaZnO<sub>4</sub>の結晶であれば、(009)面に配向していることを示す。また、CAAC-OSは、 $2\theta$ が $36^\circ$ 近傍のピークが現れる場合がある。 $2\theta$ が $36^\circ$ 近傍のピークは、ZnGa<sub>2</sub>O<sub>4</sub>の結晶であれば、(222)面に配向していることを示す。CAAC-OSは、好ましくは、 $2\theta$ が $31^\circ$ 近傍にピークが現れ、 $2\theta$ が $36^\circ$ 近傍にピークが現れない。

#### 【0178】

また、CAAC-OSは、異なる結晶部間で、それぞれa軸およびb軸の向きが揃っていない場合がある。InGaZnO<sub>4</sub>の結晶を有するCAAC-OSであれば、XRD装置を用い、c軸に垂直な方向からX線を入射させるin-plane法による分析を行うと、 $2\theta$ が $56^\circ$ 近傍のピークが現れる場合がある。 $2\theta$ が $56^\circ$ 近傍のピークは、InGaZnO<sub>4</sub>の結晶の(110)面を示す。ここで、 $2\theta$ を $56^\circ$ 近傍で固定し、表面の法線ベクトルを軸( c 軸)として試料を回転させて分析( スキャン )を行うと、a軸およびb軸の向きが揃っている単結晶酸化物半導体の場合は6つの対称性のピークが現れるが、CAAC-OSの場合は明瞭なピークが現れない。

#### 【0179】

このように、CAAC-OSは、c軸配向し、a軸またはb軸はマクロに揃っていない場合がある。

#### 【0180】

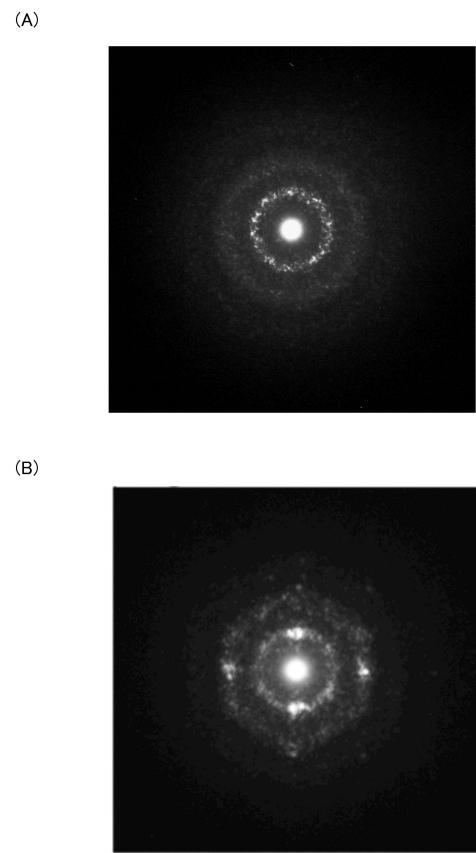

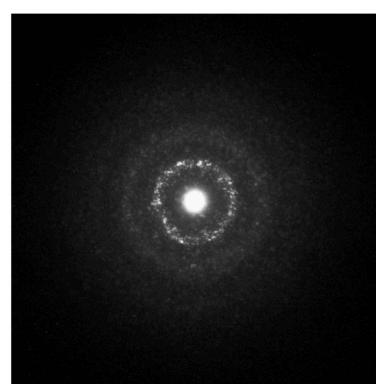

また、CAAC-OSは、電子線回折パターンで、スポット(輝点)が観測される場合がある。なお、特に、ビーム径が $10\text{ nm}$ 以下、または $5\text{ nm}$ 以下の電子線を用いて得られる電子線回折パターンを、極微電子線回折パターンと呼ぶ。

#### 【0181】

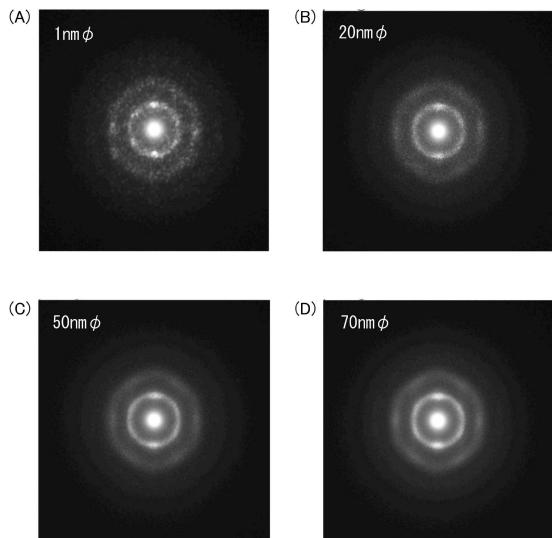

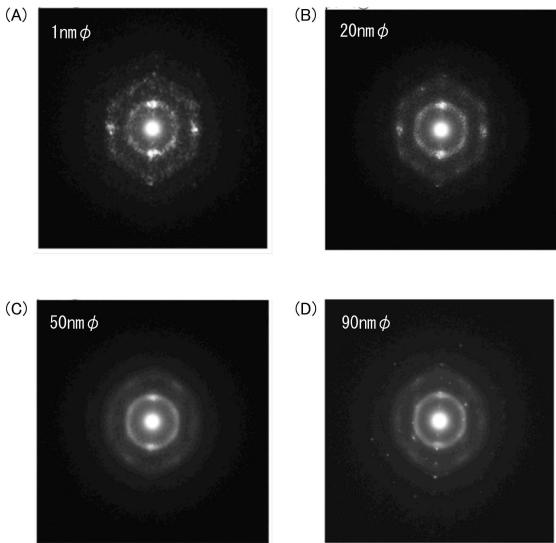

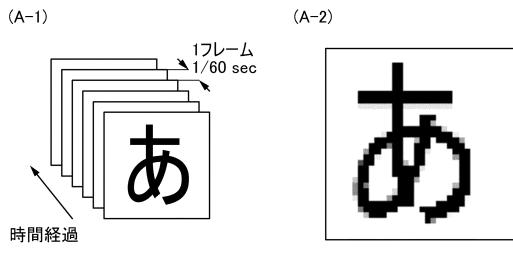

図10(A)は、CAAC-OSを有する試料の極微電子線回折パターンの一例である。ここでは、試料を、CAAC-OSの被形成面に垂直な方向に切断し、厚さが $40\text{ nm}$ 程度となるように薄片化する。また、ここでは、ビーム径が $1\text{ nm}$ の電子線を、試料の切断面に垂直な方向から入射させる。図10(A)より、CAAC-OSの極微電子線回折パターンは、スポットが観測されることがわかる。

#### 【0182】

CAAC-OSに含まれる結晶部は、c軸がCAAC-OSの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃い、かつab面に垂直な方向から見て金属原子が三角形状または六角形状に配列し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、 $80^\circ$ 以上 $100^\circ$ 以下、好ましくは $85^\circ$ 以上 $95^\circ$ 以下の範囲も含まれることとする。また、単に平行と記載する場合、 $-10^\circ$ 以上 $10^\circ$ 以下、好ましくは $-5^\circ$ 以上 $5^\circ$ 以下の範囲も含まれることとする。

#### 【0183】

CAAC-OSに含まれる結晶部のc軸は、CAAC-OSの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃うため、CAAC-OSの形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある

10

20

30

40

50

。また、結晶部は、成膜したとき、または成膜後に加熱処理などの結晶化処理を行ったときに形成される。したがって、結晶部のc軸は、CAC-O<sub>S</sub>が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向になるように揃う。

#### 【0184】

CAC-O<sub>S</sub>は、不純物濃度を低減することで形成することができる場合がある。ここで、不純物は、水素、炭素、シリコン、遷移金属元素などの酸化物半導体の主成分以外の元素である。特に、シリコンなどの元素は、酸化物半導体を構成する金属元素よりも酸素との結合力が強い。したがって、当該元素が酸化物半導体から酸素を奪う場合、酸化物半導体の原子配列を乱し、結晶性を低下させことがある。また、鉄やニッケルなどの重金属、アルゴン、二酸化炭素などは、原子半径（または分子半径）が大きいため、酸化物半導体の原子配列を乱し、酸化物半導体の結晶性を低下させことがある。したがって、CAC-O<sub>S</sub>は、不純物濃度の低い酸化物半導体である。また、酸化物半導体に含まれる不純物は、キャリア発生源となる場合がある。10

#### 【0185】

なお、CAC-O<sub>S</sub>において、結晶部の分布が一様でなくてもよい。例えば、CAC-O<sub>S</sub>の形成過程において、酸化物半導体の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAC-O<sub>S</sub>に不純物が混入することにより、当該不純物混入領域において結晶部の結晶性が低下することがある。

#### 【0186】

また、CAC-O<sub>S</sub>は、欠陥準位密度を低減することで形成することができる。酸化物半導体において、酸素欠損は欠陥準位である。酸素欠損は、トラップ準位となることや、水素を捕獲することによってキャリア発生源となることがある。CAC-O<sub>S</sub>を形成するためには、酸化物半導体に酸素欠損を生じさせないことが重要となる。したがって、CAC-O<sub>S</sub>は、欠陥準位密度の低い酸化物半導体である。または、CAC-O<sub>S</sub>は、酸素欠損の少ない酸化物半導体である。20

#### 【0187】

不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）ことを高純度真性または実質的に高純度真性と呼ぶ。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる場合がある。したがって、当該酸化物半導体をチャネル形成領域に用いたトランジスタは、しきい値電圧がマイナスとなる電気特性（ノーマリーオンともいう。）になることが少ないのである。また、高純度真性または実質的に高純度真性である酸化物半導体は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。したがって、当該酸化物半導体をチャネル形成領域に用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる場合がある。なお、酸化物半導体のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体をチャネル形成領域に用いたトランジスタは、電気特性が不安定となる場合がある。30

#### 【0188】

また、高純度真性または実質的に高純度真性であるCAC-O<sub>S</sub>を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。

#### 【0189】

CAC-O<sub>S</sub>は、例えば、DC電源を用いたスパッタリング法によって形成することができる。

#### 【0190】

酸化物半導体は、多結晶を有してもよい。なお、多結晶を有する酸化物半導体を、多結晶酸化物半導体と呼ぶ。多結晶酸化物半導体は複数の結晶粒を含む。

#### 【0191】

多結晶酸化物半導体は、TEMによる観察像で、結晶粒を確認することができる場合があ50

る。多結晶酸化物半導体に含まれる結晶粒は、TEMによる観察像で、2 nm以上300 nm以下、3 nm以上100 nm以下または5 nm以上50 nm以下の粒径であることが多い。また、多結晶酸化物半導体は、TEMによる観察像で、結晶粒と結晶粒との境界を確認できる場合がある。また、多結晶酸化物半導体は、例えば、TEMによる観察像で、粒界を確認できる場合がある。

#### 【0192】

多結晶酸化物半導体は、複数の結晶粒を有し、当該複数の結晶粒において方位が異なっている場合がある。また、多結晶酸化物半導体は、XRD装置を用い、out-of-plane法による分析を行うと、配向を示す2θが31°近傍のピーク、または複数種の配向を示すピークが現れる場合がある。また、多結晶酸化物半導体は、電子線回折パターンで、スポットが観測される場合がある。10

#### 【0193】

多結晶酸化物半導体は、高い結晶性を有するため、高い電子移動度を有する場合がある。したがって、多結晶酸化物半導体をチャネル形成領域に用いたトランジスタは、高い電界効果移動度を有する。ただし、多結晶酸化物半導体は、粒界に不純物が偏析する場合がある。また、多結晶酸化物半導体の粒界は欠陥準位となる。多結晶酸化物半導体は、粒界がキャリア発生源、トラップ準位となる場合があるため、多結晶酸化物半導体をチャネル形成領域に用いたトランジスタは、CAAC-O<sub>S</sub>をチャネル形成領域に用いたトランジスタと比べて、電気特性の変動が大きく、信頼性の低いトランジスタとなる場合がある。20

#### 【0194】

多結晶酸化物半導体は、高温での加熱処理、またはレーザ光処理によって形成することができる。20

#### 【0195】

酸化物半導体は、微結晶を有してもよい。なお、微結晶を有する酸化物半導体を、微結晶酸化物半導体と呼ぶ。

#### 【0196】

微結晶酸化物半導体は、TEMによる観察像では、明確に結晶部を確認することができない場合がある。微結晶酸化物半導体に含まれる結晶部は、1 nm以上100 nm以下、または1 nm以上10 nm以下の大きさであることが多い。特に、1 nm以上10 nm以下の微結晶をナノ結晶(nc: nanocrystalline)と呼ぶ。ナノ結晶を有する酸化物半導体を、nc-O<sub>S</sub>(nanocrystalline Oxide Semiconductor)と呼ぶ。また、nc-O<sub>S</sub>は、TEMによる観察像では、結晶部と結晶部との境界を明確に確認できない場合がある。また、nc-O<sub>S</sub>は、TEMによる観察像では、明確な粒界を有さないため、不純物が偏析することが少ない。また、nc-O<sub>S</sub>は、明確な粒界を有さないため、欠陥準位密度が高くなることが少ない。また、nc-O<sub>S</sub>は、明確な粒界を有さないため、電子移動度の低下が小さい。30

#### 【0197】

nc-O<sub>S</sub>は、微小な領域(例えば、1 nm以上10 nm以下の領域)において原子配列に周期性を有する場合がある。また、nc-O<sub>S</sub>は、結晶部と結晶部との間で規則性がないため、巨視的には原子配列に周期性が見られない場合、または長距離秩序が見られない場合がある。したがって、nc-O<sub>S</sub>は、分析方法によっては、非晶質酸化物半導体と区別が付かない場合がある。nc-O<sub>S</sub>は、例えば、XRD装置を用い、結晶部よりも大きいビーム径のX線でout-of-plane法による分析を行うと、配向を示すピークが検出されない場合がある。また、nc-O<sub>S</sub>は、結晶部よりも大きいビーム径(例えば、20 nm以上、または50 nm以上)の電子線を用いる電子線回折パターンでは、ハローパターンが観測される場合がある。また、nc-O<sub>S</sub>は、結晶部と同じか結晶部より小さいビーム径(例えば、10 nm以下、または5 nm以下)の電子線を用いる極微電子線回折パターンでは、スポットが観測される場合がある。また、nc-O<sub>S</sub>の極微電子線回折パターンは、円を描くように輝度の高い領域が観測される場合がある。また、nc-O<sub>S</sub>の極微電子線回折パターンは、当該領域内に複数のスポットが観測される場合4050

がある。

**【0198】**

図10(B)は、n c - O Sを有する試料の極微電子線回折パターンの一例である。ここでは、試料を、n c - O Sの被形成面に垂直な方向に切断し、厚さが40 nm程度となるように薄片化する。また、ここでは、ビーム径が1 nmの電子線を、試料の切断面に垂直な方向から入射させる。図10(B)より、n c - O Sの極微電子線回折パターンは、円を描くように輝度の高い領域が観測され、かつ当該領域内に複数のスポットが観測されることがわかる。

**【0199】**

n c - O Sは、微小な領域において原子配列に周期性を有する場合があるため、非晶質酸化物半導体よりも欠陥準位密度が低くなる。ただし、n c - O Sは、結晶部と結晶部との間で規則性がないため、C AAC - O Sと比べて欠陥準位密度が高くなる。

**【0200】**

したがって、n c - O Sは、C AAC - O Sと比べて、キャリア密度が高くなる場合がある。キャリア密度が高い酸化物半導体は、電子移動度が高くなる場合がある。したがって、n c - O Sをチャネル形成領域に用いたトランジスタは、高い電界効果移動度を有する場合がある。しかしながら、n c - O Sは、C AAC - O Sと比べて、欠陥準位密度が高いため、トラップ準位密度も高くなる場合がある。したがって、n c - O Sをチャネル形成領域に用いたトランジスタは、C AAC - O Sをチャネル形成領域に用いたトランジスタと比べて、電気特性の変動が大きく、信頼性の低いトランジスタとなる場合がある。ただし、n c - O Sは、比較的不純物が多く含まれても形成することができるため、C AAC - O Sよりも形成が容易となり、用途によっては好適に用いることができる場合がある。なお、AC電源を用いたスパッタリング法などの成膜方法によってn c - O Sを形成してもよい。AC電源を用いたスパッタリング法は、大型基板へ均一性高く成膜することが可能であるため、n c - O Sをチャネル形成領域に用いたトランジスタを有する半導体装置は生産性高く作製することができる。

**【0201】**

酸化物半導体は、非晶質部を有してもよい。なお、非晶質部を有する酸化物半導体を、非晶質酸化物半導体と呼ぶ。非晶質酸化物半導体は、原子配列が無秩序であり、結晶部を有さない。または、非晶質酸化物半導体は、石英のような無定形状態を有し、原子配列に規則性が見られない。

**【0202】**

非晶質酸化物半導体は、TEMによる観察像で、結晶部を確認することができない場合がある。

**【0203】**

非晶質酸化物半導体は、XRD装置を用い、out-of-plane法による分析を行うと、配向を示すピークが検出されない場合がある。また、非晶質酸化物半導体は、電子線回折パターンでハローパターンが観測される場合がある。また、非晶質酸化物半導体は、極微電子線回折パターンでスポットを観測することができず、ハローパターンが観測される場合がある。

**【0204】**

非晶質酸化物半導体は、水素などの不純物を高い濃度で含ませることにより形成することができる場合がある。したがって、非晶質酸化物半導体は、不純物を高い濃度で含む酸化物半導体である。

**【0205】**

酸化物半導体に不純物が高い濃度で含まれると、酸化物半導体に酸素欠損などの欠陥準位を形成する場合がある。したがって、不純物濃度の高い非晶質酸化物半導体は、欠陥準位密度が高い。また、非晶質酸化物半導体は、結晶性が低いためC AAC - O Sやn c - O Sと比べて欠陥準位密度が高い。

**【0206】**

10

20

30

40

50

したがって、非晶質酸化物半導体は、 $n_c - OS$ と比べて、さらにキャリア密度が高くなる場合がある。そのため、非晶質酸化物半導体をチャネル形成領域に用いたトランジスタは、ノーマリーオンの電気特性になる場合がある。したがって、ノーマリーオンの電気特性が求められるトランジスタに好適に用いることができる場合がある。非晶質酸化物半導体は、欠陥準位密度が高いため、トラップ準位密度も高くなる場合がある。したがって、非晶質酸化物半導体をチャネル形成領域に用いたトランジスタは、 $CAAC - OS$ や $n_c - OS$ をチャネル形成領域に用いたトランジスタと比べて、電気特性の変動が大きく、信頼性の低いトランジスタとなる場合がある。ただし、非晶質酸化物半導体は、比較的不純物が多く含まれてしまう成膜方法によっても形成することができるため、形成が容易となり、用途によっては好適に用いることができる場合がある。例えば、スピンコート法、ゾル・ゲル法、浸漬法、スプレー法、スクリーン印刷法、コンタクトプリント法、インクジェット印刷法、ロールコート法、ミスト $CVD$ 法などの成膜方法によって非晶質酸化物半導体を形成してもよい。したがって、非晶質酸化物半導体をチャネル形成領域に用いたトランジスタを有する半導体装置は生産性高く作製することができる。

#### 【0207】

なお、酸化物半導体が、 $CAAC - OS$ 、多結晶酸化物半導体、微結晶酸化物半導体、非晶質酸化物半導体の二種以上を有する混合膜であってもよい。混合膜は、例えば、非晶質酸化物半導体の領域、微結晶酸化物半導体の領域、多結晶酸化物半導体の領域、 $CAAC - OS$ の領域、のいずれか二種以上の領域を有する場合がある。また、混合膜は、例えば、非晶質酸化物半導体の領域、微結晶酸化物半導体の領域、多結晶酸化物半導体の領域、 $CAAC - OS$ の領域、のいずれか二種以上の領域の積層構造を有する場合がある。

#### 【0208】

酸化物半導体は、例えば、単結晶を有してもよい。なお、単結晶を有する酸化物半導体を、単結晶酸化物半導体と呼ぶ。

#### 【0209】

単結晶酸化物半導体は、例えば、不純物濃度が低く、欠陥準位密度が低い（酸素欠損が少ない）ため、キャリア密度を低くすることができます。したがって、単結晶酸化物半導体をチャネル形成領域に用いたトランジスタは、ノーマリーオンの電気特性になることが少ない場合がある。また、単結晶酸化物半導体は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。したがって、単結晶酸化物半導体をチャネル形成領域に用いたトランジスタは、電気特性の変動が小さく、信頼性の高いトランジスタとなる場合がある。

#### 【0210】

酸化物半導体は、欠陥が少ないと密度が高くなることがある。また、酸化物半導体は、結晶性が高いと密度が高くなることがある。また、酸化物半導体は、例えば、水素などの不純物濃度が低いと密度が高くなる。また、単結晶酸化物半導体は、 $CAAC - OS$ よりも密度が高い場合がある。また、 $CAAC - OS$ は、微結晶酸化物半導体よりも密度が高い場合がある。また、多結晶酸化物半導体は、微結晶酸化物半導体よりも密度が高い場合がある。また、微結晶酸化物半導体は、非晶質酸化物半導体よりも密度が高い場合がある。

#### 【0211】

また、 $CAAC - OS$ を成膜するために、以下の条件を適用することが好ましい。

#### 【0212】

成膜時の不純物混入を低減することで、不純物によって結晶状態が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素および窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が-80℃以下、好ましくは-100℃以下である成膜ガスを用いる。

#### 【0213】

また、成膜時の被成膜面の加熱温度（例えば基板加熱温度）を高めることで、被成膜面に到達後にスパッタリング粒子のマイグレーションが起こる。具体的には、被成膜面の温度を100℃以上740℃以下、好ましくは150℃以上500℃以下として成膜する。

10

20

30

40

50

## 【0214】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージを軽減すると好ましい。成膜ガス中の酸素割合は、30体積%以上、好ましくは100体積%とする。

## 【0215】

スペッタリング用ターゲットの一例として、In-Ga-Zn-O化合物ターゲットについて以下に示す。

## 【0216】

InO<sub>x</sub>粉末、GaO<sub>y</sub>粉末およびZnO<sub>z</sub>粉末を所定のmol数で混合し、加圧処理後、1000以上1500以下の温度で加熱処理をすることで多結晶であるIn-Ga-Zn系金属酸化物ターゲットとする。なお、当該加圧処理は、冷却（または放冷）しながら行ってもよいし、加熱しながら行ってもよい。なお、X、YおよびZは任意の正数である。ここで、所定のmol数比は、例えば、InO<sub>x</sub>粉末、GaO<sub>y</sub>粉末およびZnO<sub>z</sub>粉末が、2:2:1、8:4:3、3:1:1、1:1:1、4:2:3、または3:1:2などがある。なお、粉末の種類、およびその混合するmol数比は、作製するスペッタリング用ターゲットによって適宜変更すればよい。

## 【0217】

ここで、結晶状態における酸化物半導体(OSと示す。)およびシリコン(Siと示す。)の対比を表1に示す。

## 【0218】

## 【表1】

|    | 非晶質            | 微結晶                 | 多結晶         | 連続結晶    | 単結晶      |

|----|----------------|---------------------|-------------|---------|----------|

| OS | a-OS<br>a-OS:H | nc-OS<br>$\mu$ c-OS | 多結晶OS       | CAAC-OS | 単結晶OS    |

|    | 極微電子線回折        | ハロー                 | リング+スポット    | スポット    | スポット     |

|    | 結晶部            | —                   | nm~ $\mu$ m | 不連続     | 連続的につながる |

|    | DOS            | 高い                  | やや低い        | —       | 低い       |

|    | 密度             | 低い                  | 中程度         | —       | 高い       |

|    |                |                     |       |        |       |

|----|----------------|---------------------|-------|--------|-------|

| Si | a-Si<br>a-Si:H | nc-Si<br>$\mu$ c-Si | 多結晶Si | CGシリコン | 単結晶Si |

|----|----------------|---------------------|-------|--------|-------|

## 【0219】

酸化物半導体の結晶状態には、例えば、表1に示すように、非晶質酸化物半導体(a-OS、a-OS:H)、微結晶酸化物半導体(nc-OS、 $\mu$ c-OS)、多結晶酸化物半導体(多結晶OS)、連続結晶酸化物半導体(CAAC-OS)、単結晶酸化物半導体(単結晶OS)などがある。なお、シリコンの結晶状態には、例えば、表1に示すように、非晶質シリコン(a-Siやa-Si:H)、微結晶シリコン(nc-Si、 $\mu$ c-Si)、多結晶シリコン(多結晶Si)、連続結晶シリコン(CG(Continuous Grain)シリコン)、単結晶シリコン(単結晶Si)などがある。

## 【0220】

各結晶状態における酸化物半導体に対し、ビーム径を10nm以下に収束させた電子線を用いる電子線回折(極微電子線回折)を行うと、以下のような電子線回折パターン(極微電子線回折パターン)が観測される。非晶質酸化物半導体では、ハローパターン(ハロ

10

20

30

40

50

ーリングまたはハローとも言われる。)が観測される。微結晶酸化物半導体では、スポットまたは/およびリングパターンが観測される。多結晶酸化物半導体では、スポットが観測される。連続結晶酸化物半導体では、スポットが観測される。単結晶酸化物半導体では、スポットが観測される。

#### 【0221】

なお、極微電子線回折パターンより、微結晶酸化物半導体は、結晶部がナノメートル(nm)からマイクロメートル(μm)の径であることがわかる。多結晶酸化物半導体は、結晶部と結晶部との間に粒界を有し、境界が不連続であることがわかる。連続結晶酸化物半導体は、結晶部と結晶部との間に境界が観測されず、連続的に繋がることがわかる。

#### 【0222】

各結晶状態における酸化物半導体の密度について説明する。非晶質酸化物半導体の密度は低い。微結晶酸化物半導体の密度は中程度である。連続結晶酸化物半導体の密度は高い。即ち、連続結晶酸化物半導体の密度は微結晶酸化物半導体の密度より高く、微結晶酸化物半導体の密度は非晶質酸化物半導体の密度より高い。

10

#### 【0223】

各結晶状態における酸化物半導体に存在する状態密度(DOS)の特徴を説明する。非晶質酸化物半導体はDOSが高い。微結晶酸化物半導体はDOSがやや低い。連続結晶酸化物半導体はDOSが低い。単結晶酸化物半導体はDOSが極めて低い。即ち、単結晶酸化物半導体は連続結晶酸化物半導体よりDOSが低く、連続結晶酸化物半導体は微結晶酸化物半導体よりDOSが低く、微結晶酸化物半導体は非晶質酸化物半導体よりDOSが低い。

20

#### 【0224】

また、酸化物半導体膜は、複数の酸化物半導体膜が積層された構造でもよい。例えば、図9(A)に示すトランジスタのように、半導体膜を第1の酸化物半導体膜188aと第2の酸化物半導体膜188bの積層とすることができる。第1の酸化物半導体膜188aと第2の酸化物半導体膜188bに、異なる原子数比の金属酸化物を用いてもよい。例えば、一方の酸化物半導体膜に二種類の金属を含む酸化物、三種類の金属を含む酸化物、四種類の金属を含む酸化物のうち一つを用い、他方の酸化物半導体膜に一方の酸化物半導体膜と異なる二種類の金属を含む酸化物、三種類の金属を含む酸化物、四種類の金属を含む酸化物を用いてもよい。

30

#### 【0225】

また、第1の酸化物半導体膜188aと第2の酸化物半導体膜188bの構成元素を同一とし、両者の原子数比を異ならせててもよい。例えば、一方の酸化物半導体膜の原子数比をIn:Ga:Zn=3:1:2とし、他方の酸化物半導体膜の原子数比をIn:Ga:Zn=1:1:1としてもよい。また、一方の酸化物半導体膜の原子数比をIn:Ga:Zn=2:1:3とし、他方の酸化物半導体膜の原子数比をIn:Ga:Zn=1:3:2としてもよい。また、一方の酸化物半導体膜の原子数比をIn:Ga:Zn=1:1:1とし、他方の酸化物半導体膜の原子数比をIn:Ga:Zn=1:3:2としてもよい。また、一方の酸化物半導体膜の原子数比をIn:Ga:Zn=1:1:1とし、他方の酸化物半導体膜の原子数比をIn:Ga:Zn=1:6:4としてもよい。また、一方の酸化物半導体膜の原子数比をIn:Ga:Zn=1:1:1とし、他方の酸化物半導体膜の原子数比をIn:Ga:Zn=1:9:6としてもよい。なお、各酸化物半導体膜の原子数比は、誤差として上記の原子数比のプラスマイナス20%の変動を含む。

40

#### 【0226】

このとき、一方の酸化物半導体膜と他方の酸化物半導体膜のうち、ゲート電極に近い側(チャネル側)の酸化物半導体膜のInとGaの原子数比をIn>Gaとし、ゲート電極から遠い側(バックチャネル側)の酸化物半導体膜のInとGaの原子数比をIn<Gaとすることで、電界効果移動度の高いトランジスタを作製することができる。一方、チャネル側の酸化物半導体膜のInとGaの原子数比をIn<Gaとし、バックチャネル側の酸化物半導体膜のInとGaの原子数比をIn>Gaとすることで、トランジスタの経時変

50

化や信頼性試験によるしきい値電圧の変動量を低減することができる。

【0227】

また、トランジスタの半導体膜を第1の酸化物半導体膜乃至第3の酸化物半導体膜からなる3層構造としてもよい。このとき、第1の酸化物半導体膜乃至第3の酸化物半導体膜の構成元素を同一とし、且つそれぞれの原子数比を異ならせててもよい。半導体膜を3層構造とするトランジスタの構成について、図9(B)を用いて説明する。

【0228】

図9(B)に示すトランジスタは、第1の酸化物半導体膜199a、第2の酸化物半導体膜199b、および第3の酸化物半導体膜199cがゲート絶縁膜127側から順に積層されている。第1の酸化物半導体膜199aおよび第3の酸化物半導体膜199cを構成する材料は、 $InM_{1-x}Zn_yO_z$ ( $x < 1$ 、 $y > 0$ 、 $M_1 = Ga, Hf$ 等)で表記できる材料を用いる。ただし、第1の酸化物半導体膜199aおよび第3の酸化物半導体膜199cを構成する材料にGaを含ませる場合、含ませるGaの割合が多い、具体的には $InM_{1-x}Zn_yO_z$ で表記できる材料で $x = 1.0$ を超えると成膜時に粉が発生する恐れがあり、不適である。10

【0229】

また、第2の酸化物半導体膜199bを構成する材料は、 $InM_{2-x}Zn_yO_z$ ( $x < 1$ 、 $y < x$ 、 $z > 0$ 、 $M_2 = Ga, Sn$ 等)で表記できる材料を用いる。

【0230】

第1の酸化物半導体膜199aの伝導帯下端および第3の酸化物半導体膜199cの伝導帯下端に比べて第2の酸化物半導体膜199bの伝導帯下端が真空準位から最も深くなるような井戸型構造を構成するように、第1、第2、および第3の酸化物半導体膜の材料を適宜選択する。20

【0231】

なお、酸化物半導体膜において第14族元素の一つであるシリコンや炭素はドナー準位の形成に寄与することがある。このため、シリコンや炭素が酸化物半導体膜に含まれると、酸化物半導体膜はn型化してしまう。したがって、シリコンおよび炭素のそれぞれの濃度は $3 \times 10^{18} / cm^3$ 以下、好ましくは $3 \times 10^{17} / cm^3$ とする領域を有するように各酸化物半導体膜を形成することが好ましい。特に、第2の酸化物半導体膜199bに第14族元素が多く混入しないように、第1の酸化物半導体膜199aおよび第3の酸化物半導体膜199cで、キャリアパスとなる第2の酸化物半導体膜199bを挟む、または囲む構成とすることが好ましい。すなわち、第1の酸化物半導体膜199aおよび第3の酸化物半導体膜199cは、シリコン、炭素等の第14族元素が第2の酸化物半導体膜199bに混入することを防ぐバリア膜とも呼べる。30

【0232】

例えば、第1の酸化物半導体膜199aおよび第3の酸化物半導体膜199cを原子数比が $In : Ga : Zn = 1 : 3 : 2$ 、または $1 : 6 : 4$ 、または $1 : 9 : 6$ である酸化物半導体膜で形成し、第2の酸化物半導体膜199bの原子数比が $In : Ga : Zn = 1 : 1 : 1$ 、または $3 : 1 : 2$ である酸化物半導体膜で形成することができる。

【0233】

または、第1の酸化物半導体膜199aを原子数比が $In : Ga : Zn = 1 : 3 : 2$ である酸化物半導体膜で形成し、第2の酸化物半導体膜199bを原子数比が $In : Ga : Zn = 1 : 1 : 1$ または $In : Ga : Zn = 3 : 1 : 2$ である酸化物半導体膜で形成し、第3の酸化物半導体膜199cを原子数比が $In : Ga : Zn = 1 : 6 : 4$ 、または $1 : 9 : 6$ である酸化物半導体膜で形成してもよい。40

【0234】

第1の酸化物半導体膜199a乃至第3の酸化物半導体膜199cの構成元素は同一であるため、第2の酸化物半導体膜199bは、第1の酸化物半導体膜199aとの界面における欠陥準位(トラップ準位)が少ない。詳細には、当該欠陥準位(トラップ準位)は、ゲート絶縁膜127と第1の酸化物半導体膜199aとの界面における欠陥準位よりも少50

ない。このため、上記のように酸化物半導体膜が積層されていることで、トランジスタの経時変化や信頼性試験によるしきい値電圧の変動量を低減することができる。

**【0235】**

また、第1の酸化物半導体膜199aの伝導帯下端および第3の酸化物半導体膜199cの伝導帯下端に比べて第2の酸化物半導体膜199bの伝導帯下端が真空準位から最も深くなるような井戸型構造を構成するように、第1、第2、および第3の酸化物半導体膜の材料を適宜選択することで、トランジスタの電界効果移動度を高めることができると共に、トランジスタの経時変化や信頼性試験によるしきい値電圧の変動量を低減することができる。

**【0236】**

また、第1の酸化物半導体膜199a乃至第3の酸化物半導体膜199cに、結晶性の異なる酸化物半導体を適用してもよい。すなわち、単結晶酸化物半導体、多結晶酸化物半導体、微結晶(ナノ結晶)酸化物半導体、非晶質酸化物半導体、およびCAC-O<sub>S</sub>膜を適宜組み合わせた構成としてもよい。また、第1の酸化物半導体膜199a乃至第3の酸化物半導体膜199cのいずれか一つに非晶質酸化物半導体を適用すると、酸化物半導体膜の内部応力や外部からの応力を緩和し、トランジスタの特性ばらつきが低減され、またトランジスタの経時変化や信頼性試験によるしきい値電圧の変動量を低減することができる。

**【0237】**

また、少なくともチャネル形成領域となりうる第2の酸化物半導体膜199bはCAC-O<sub>S</sub>膜であることが好ましい。

**【0238】**

なお、酸素と結合し易い導電材料(例えば、ソース電極またはドレイン電極に用いられる金属)と酸化物半導体膜を接触させると、酸化物半導体膜中の酸素が、酸素と結合し易い導電材料側に拡散する現象が起こる。当該現象は、温度が高いほど顕著に起こる。トランジスタの作製工程には、いくつかの加熱工程があることから、上記現象により、酸化物半導体層のソース電極またはドレイン電極と接触した近傍の領域に酸素欠損が発生し、当該領域はn型化する。したがって、n型化した当該領域はトランジスタのソースまたはドレインとして作用させることができる。

**【0239】**

上記n型化した領域は、図9(A)、(B)に例示される。半導体膜中に点線で示される境界135は、真性半導体領域とn型半導体領域の境界であり、酸化物半導体におけるソース電極またはドレイン電極と接触した近傍の領域がn型化した領域となる。なお、境界135は模式的に示したものであり、実際には明瞭ではない場合がある。また、境界135の位置も図示した位置とは異なる場合がある。

**【0240】**

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせることができる。

**【0241】**

(実施の形態3)

本実施の形態では、本発明の一態様に用いることのできるナノ結晶酸化物半導体膜の電子線回折パターン、および局在準位について説明する。

**【0242】**

ナノ結晶酸化物半導体膜は、ビーム径が10nm以下とした電子線回折(極微電子線回折)を用いた電子線回折パターンにおいて、非晶質状態を示すハローパターンとも、特定の面に配向した結晶状態を示す規則性を有するスポットとも異なり、方向性を持たないスポットが観察される酸化物半導体膜である。

**【0243】**

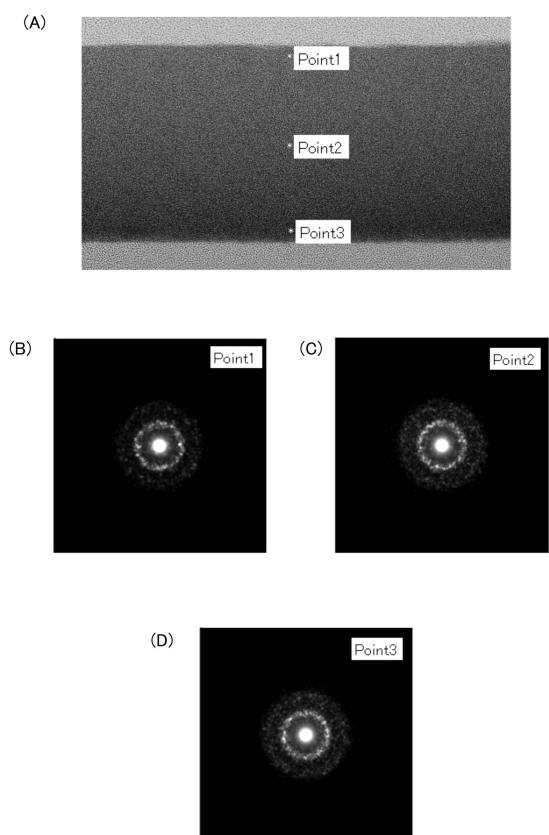

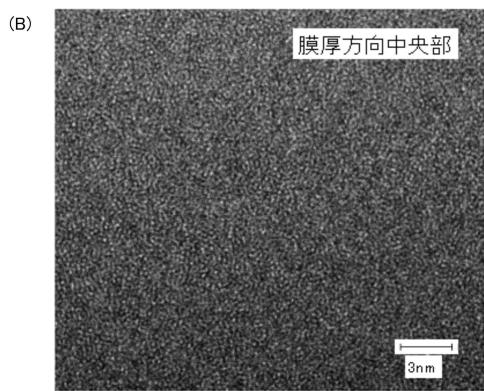

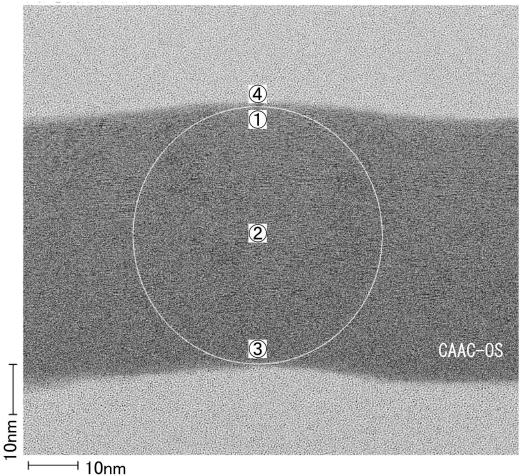

図13(A)にナノ結晶酸化物半導体膜の断面TEM(Transmission Electron Microscope(透過型電子顕微鏡))像を示す。また、図13(

10

20

30

40

50

B)に図13(A)のポイント1において極微電子線回折を用いて測定した電子線回折パターンを、図13(C)に図13(A)のポイント2において極微電子線回折を用いて測定した電子線回折パターンを、図13(D)に図13(A)のポイント3において極微電子線回折を用いて測定した電子線回折パターンをそれぞれ示す。

#### 【0244】

図13では、ナノ結晶酸化物半導体膜の一例として、In-Ga-Zn系酸化物膜を石英ガラス基板上に膜厚50nmで成膜した試料を用いる。図13に示すナノ微結晶酸化物半導体膜の成膜条件は、In:Ga:Zn=1:1:1(原子数比)である酸化物ターゲットを用いて、酸素雰囲気下(流量45sccm)、圧力0.4Pa、直流(DC)電源0.5kW、基板温度を室温とした。そして、成膜したナノ結晶酸化物半導体膜を100nm以下(例えば、40nm±10nm)の幅に薄片化し、断面TEM像および極微電子線回折による電子線回折パターンを得た。

#### 【0245】

図13(A)は、透過型電子顕微鏡(日立ハイテクノロジーズ製「H-9000NAR」)を用い、加速電圧を300kV、倍率200万倍として撮影したナノ結晶酸化物半導体膜の断面TEM像である。また、図13(B)乃至図13(D)は、透過型電子顕微鏡(日立ハイテクノロジーズ製「HF-2000」)を用い、加速電圧を200kV、ビーム径を約1nmとして極微電子線回折によって得られた電子線回折パターンである。なお、ビーム径を約1nmとした場合の極微電子線回折での測定範囲は、5nm以上10nm以下である。

#### 【0246】

図13(B)に示すように、ナノ結晶酸化物半導体膜は、極微電子線回折を用いた電子線回折パターンにおいて、円周状に配置された複数のスポット(輝点)が観察される。換言すると、ナノ結晶酸化物半導体膜では、円周状(同心円状)に分布した複数のスポットが観察されるともいえる。または、円周状に分布した複数のスポットが複数の同心円を形成するともいえる。

#### 【0247】

また、石英ガラス基板との界面近傍である図13(D)および、ナノ結晶酸化物半導体膜の膜厚方向中央部の図13(C)においても図13(B)と同様に円周状に分布した複数のスポットが観察される。図13(C)において、メインスポットから円周状のスポットまでの距離は、3.88/nmから4.93/nmであった。面間隔に換算すると、0.203nmから0.257nmである。

#### 【0248】

図13の極微電子線回折パターンより、ナノ結晶酸化物半導体膜は、面方位が不規則であって且つ大きさの異なる結晶部が複数混在する膜であることがわかる。

#### 【0249】

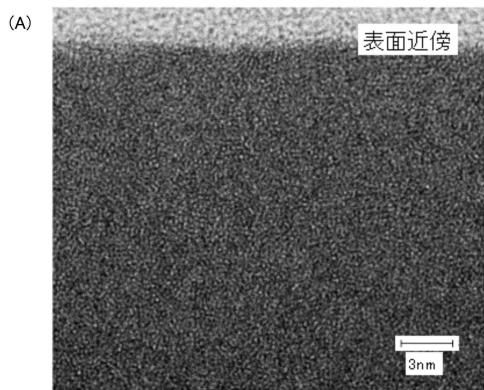

次いで、図14(A)にナノ結晶酸化物半導体膜の平面TEM像を示す。また、図14(B)に図14(A)において円で囲んだ領域を、制限視野電子線回折を用いて測定した電子線回折パターンを示す。

#### 【0250】

図14では、ナノ結晶酸化物半導体膜の一例として、In-Ga-Zn系酸化物膜を石英ガラス基板上に膜厚30nmで成膜した試料を用いる。図14に示すナノ結晶酸化物半導体膜の成膜条件は、In:Ga:Zn=1:1:1(原子数比)である酸化物ターゲットを用いて、酸素雰囲気下(流量45sccm)、圧力0.4Pa、直流(DC)電源0.5kW、基板温度を室温とした。そして、試料を薄片化し、ナノ結晶酸化物半導体膜の平面TEM像および電子線回折による電子線回折パターンを得た。

#### 【0251】

図14(A)は、透過型電子顕微鏡(日立ハイテクノロジーズ製「H-9000NAR」)を用い、加速電圧を300kV、倍率50万倍として撮影したナノ結晶酸化物半導体膜の平面TEM写真である。また、図14(B)は、制限視野を300nmとして電子線

10

20

30

40

50

回折によって得られた電子線回折パターンである。なお、電子線の広がりを考慮すると、測定範囲は、300 nm 以上である。

**【0252】**

図14(B)に示すように、ナノ結晶酸化物半導体膜は、極微電子線回折よりも測定範囲の広い制限視野電子線回折を用いた電子線回折パターンでは、極微電子線回折によって観察された複数のスポットがみられず、ハローパターンが観察される。

**【0253】**

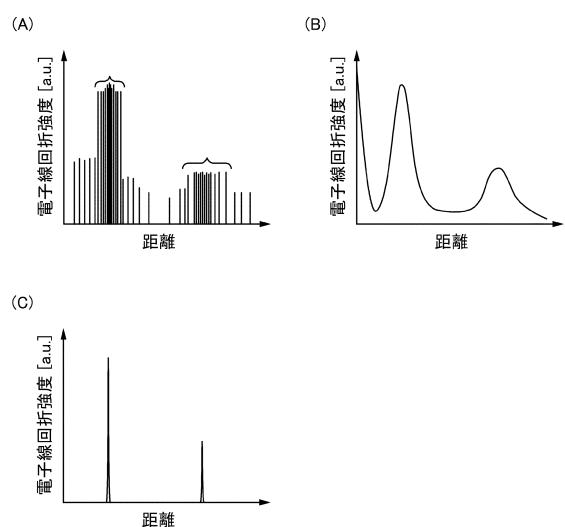

次に、図15に、図13および図14の電子線回折パターンにおける回折強度の分布を概念的に示す。図15(A)は、図13(B)乃至図13(D)に示す極微電子線回折パターンにおける回折強度の分布の概念図である。また、図15(B)は、図14(B)に示す制限視野電子線回折パターンにおける回折強度の分布の概念図である。また、図15(C)は単結晶構造または多結晶構造の電子線回折パターンにおける回折強度の分布の概念図である。

**【0254】**

図15において、縦軸はスポットなどの分布を表す電子線回折強度(任意単位)、横軸はメインスポットからの距離を示す。

**【0255】**

図15(C)に示す単結晶構造または多結晶構造においては、結晶部が配向する面の面間隔(d値)に応じた、メインスポットからの特定の距離にスポットがみられる。

**【0256】**

一方、図13に示すようにナノ結晶酸化物半導体膜の極微電子線回折パターンで観察される複数のスポットは、比較的大きい幅を有する。よって、図15(A)は、離散的な強度分布を示す。また、極微電子線回折パターンにおいて、同心円状の領域間に明確なスポットとならないものの輝度の高い領域が存在することがわかる。

**【0257】**

また、図15(B)に示すように、ナノ結晶酸化物半導体膜の制限視野電子線回折パターンにおける電子線回折強度分布は、連続的な強度分布を示す。図15(B)は、図15(A)に示す電子線回折強度分布を広範囲で観察した結果と近似可能であるため、図15(A)に示す複数のスポットが重なってつながり、連続的な強度分布が得られたものと考察できる。

**【0258】**

図15(A)乃至図15(C)に示すように、ナノ結晶酸化物半導体膜は、面方位が不規則であって且つ大きさの異なる結晶部が複数混在する膜であり、且つ、その結晶部は、制限視野電子線回折パターンにおいてはスポットが観察されない程度に、極微細であることが示唆される。

**【0259】**

複数のスポットが観察された図13において、ナノ結晶酸化物半導体膜は50 nm以下に薄片化されている。また電子線のビーム径は1 nm に収束されているため、その測定範囲は5 nm以上10 nm以下である。よって、ナノ結晶酸化物半導体膜に含まれる結晶部は、少なくとも50 nm以下であり、例えば、10 nm以下、または5 nm以下であることが推測される。

**【0260】**

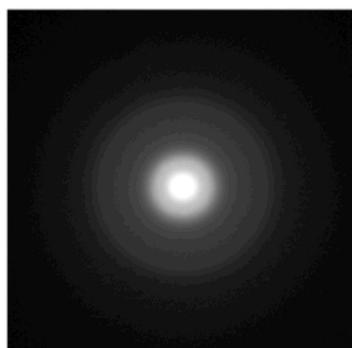

ここで、図16に、石英ガラス基板における極微電子線回折パターンを示す。図16の測定条件は、図13(B)乃至図13(D)と同様とした。

**【0261】**

図16に示すように、非晶質構造を有する石英ガラス基板では、特定のスポットを有さずメインスポットから輝度が連続的に変化するハローパターンが観測される。このように、非晶質構造を有する膜においては、極微小な領域の電子線回折を行ったとしても、ナノ結晶酸化物半導体膜で観察されるような円周状に分布した複数のスポットが観察されない。したがって、図13(B)乃至図13(D)で観察される円周状に分布した複数のスポット

10

20

30

40

50

トは、ナノ結晶酸化物半導体膜に特有のものであることが確認される。

**【0262】**

また、図17に、図13(A)に示すポイント2にビーム径を約1nmに収束した電子線を1分間照射した後に、測定を行った電子線回折パターンを示す。

**【0263】**

図17に示す電子線回折パターンは、図13(C)に示す電子線回折パターンと同様に、円周状に分布した複数のスポットが観察され、両者の測定結果に特段の相違点は確認されない。このことは、図13(C)の電子線回折パターンで確認された結晶部は、ナノ結晶酸化物半導体膜の成膜時から存在していることを意味しており、収束電子線を照射したことで結晶部が形成されたものではないことを意味する。

10

**【0264】**

次に、図18に、図13(A)に示す断面TEM像の部分拡大図を示す。図18(A)は、図13(A)のポイント1近傍(ナノ結晶酸化物半導体膜表面)を、倍率800万倍で観察した断面TEM像である。また、図18(B)は、図13(A)のポイント2近傍(ナノ結晶酸化物半導体膜の膜厚方向中央部)を、倍率800万倍で観察した断面TEM像である。

**【0265】**

図18に示す断面TEM像からは、ナノ結晶酸化物半導体膜において結晶構造が明確には確認できない。

**【0266】**

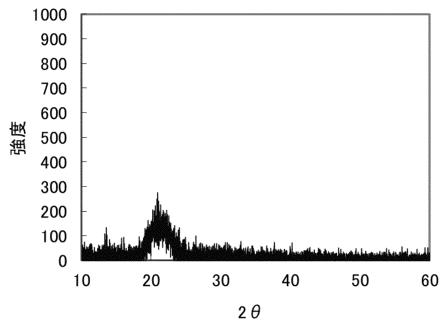

また、図13および図14の観察に用いた、石英ガラス基板上に本実施の形態のナノ結晶酸化物半導体膜が成膜された試料をX線回折(XRD:X-Ray Diffraction)を用いて分析した。図19にout-of-plane法を用いてXRDスペクトルを測定した結果を示す。

20

**【0267】**

図19において、縦軸はX線回折強度(任意単位)であり、横軸は回折角 $2\theta$ (deg.)である。なお、XRDスペクトルの測定は、Bruker AXS社製X線回折装置D-8 ADVANCEを用いた。

**【0268】**

図19に示すように、 $2\theta = 20 \sim 23^\circ$ 近傍に石英に起因するピークが観察されるものの、ナノ結晶酸化物半導体膜に含まれる結晶部に起因するピークは確認できない。

30

**【0269】**

図18および図19の結果からも、ナノ結晶酸化物半導体膜に含まれる結晶部は、極微細な結晶部であることが示唆される。

**【0270】**

以上示したように、本実施の形態のナノ結晶酸化物半導体膜では、測定範囲の広いX線回折(XRD:X-ray diffraction)による分析では配向を示すピークが検出されず、また、測定範囲の広い制限視野電子線回折によって得られる電子線回折パターンでは、ハローパターンが観測される。よって、本実施の形態のナノ結晶酸化物半導体膜は、巨視的には無秩序な原子配列を有する膜と同等であるといえる。しかしながら、電子線のビーム径が十分に小さい径(例えば、10nm以下)の極微電子線回折によってナノ結晶酸化物半導体膜を測定することで、得られる極微電子線回折パターンではスポット(輝点)を観測することができる。よって、本実施の形態のナノ結晶酸化物半導体膜は、面方位の不規則な極微な結晶部(例えば、粒径が10nm以下、または5nm以下、または3nm以下の結晶部)が凝集して形成された膜と推測できる。また、極微細な結晶部を含有するナノ結晶領域は、ナノ結晶酸化物半導体膜の膜厚方向の全領域において含まれる。

40

**【0271】**

ここで、ナノ結晶酸化物半導体膜の局在準位について説明する。ここでは、ナノ結晶酸化物半導体膜をCPM(Constant photocurrent method)測

50

定で評価した結果について説明する。

**【0272】**

まず、測定試料の構造について説明する。

**【0273】**

測定試料は、ガラス基板上に設けられた酸化物半導体膜と、該酸化物半導体膜に接する一对の電極と、酸化物半導体膜および一対の電極を覆う絶縁膜と、を有する。

**【0274】**

次に、測定試料に含まれる酸化物半導体膜の形成方法について説明する。

**【0275】**

In-Ga-Zn酸化物 (In : Ga : Zn = 1 : 1 : 1 [原子数比]) であるターゲットを用い、成膜ガスとしてアルゴンガスを30 sccm、酸素ガスを15 sccm用い、圧力を0.4 Paとし、基板温度を室温とし、DC電力を0.5 kW印加する条件を用いたスパッタリング法により、第1の酸化物半導体膜を形成した。なお、第1の酸化物半導体膜はナノ結晶酸化物半導体膜である。10

**【0276】**

また、第1の酸化物半導体膜を、450 の窒素雰囲気で1時間加熱した後、450 の酸素雰囲気で1時間加熱することで、第1の酸化物半導体膜に含まれる水素を脱離させる処理および第1の酸化物半導体膜に酸素を供給する処理を行い、第2の酸化物半導体膜を形成した。なお、第2の酸化物半導体膜はナノ結晶酸化物半導体膜である。

**【0277】**

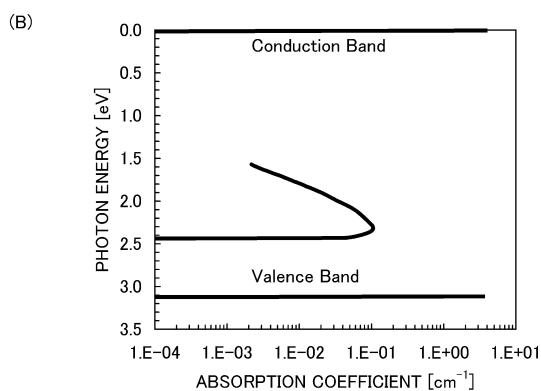

次に、第1の酸化物半導体膜を有する測定試料、および第2の酸化物半導体膜を有する測定試料についてCPM測定を行った。具体的には、酸化物半導体膜に接して設けた一对の電極間に電圧を印加した状態で光電流値が一定となるように端子間の測定試料面に照射する光量を調整し、所望の波長の範囲において照射光量から吸収係数を導出した。20

**【0278】**

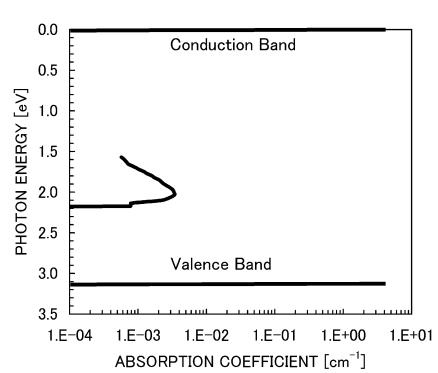

各測定試料をCPM測定して得られた吸収係数からバンドテイル起因の吸収係数を除いた吸収係数、即ち欠陥に起因する吸収係数を図11に示す。図11において、横軸は吸収係数を表し、縦軸は光エネルギーを表す。なお、図11の縦軸において、酸化物半導体膜の伝導帯の下端を0 eVとし、価電子帯の上端を3.15 eVとする。また、図11において、各曲線は吸収係数と光エネルギーの関係を示す曲線であり、欠陥準位に相当する。30

**【0279】**

図11(A)は、第1の酸化物半導体膜を有する測定試料の測定結果であり、欠陥準位による吸収係数は、 $5.28 \times 10^{-1} \text{ cm}^{-1}$ であった。図11(B)は、第2の酸化物半導体膜を有する測定試料の測定結果であり、欠陥準位による吸収係数は、 $1.75 \times 10^{-2} \text{ cm}^{-1}$ であった。

**【0280】**

したがって、加熱処理により、酸化物半導体膜に含まれる欠陥を低減することができる。

**【0281】**

なお、第1の酸化物半導体膜および第2の酸化物半導体膜に関し、X線反射率法(XRR)(X-ray Reflectometry)を用いた膜密度の測定を行った。第1の酸化物半導体膜の膜密度は、 $5.9 \text{ g/cm}^3$ であり、第2の酸化物半導体膜の膜密度は $6.1 \text{ g/cm}^3$ であった。40

**【0282】**

したがって、加熱処理により、酸化物半導体膜の膜密度を高めることができる。

**【0283】**

即ち、酸化物半導体膜において、膜密度が高い程、膜中に含まれる欠陥が少ないことがわかる。

**【0284】**

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。50

**【0285】**

(実施の形態4)

本実施の形態では、本発明の一態様に用いることのできるC A A C - O S 膜について、電子線回折パターン、および局在準位について説明する。

**【0286】**

本実施の形態に用いるC A A C - O S 膜は、In - Ga - Zn酸化物 (In : Ga : Zn = 1 : 1 : 1 [原子数比]) であるターゲット、および酸素を含む成膜ガスを用いたスパッタリング法で形成したIn - Ga - Zn系酸化物膜である。当該C A A C - O S 膜の作製方法等の詳細な説明は、実施の形態1、2を参照することができる。

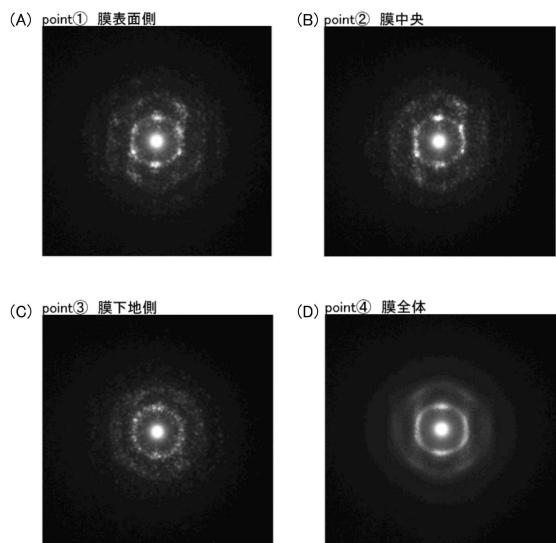

**【0287】**

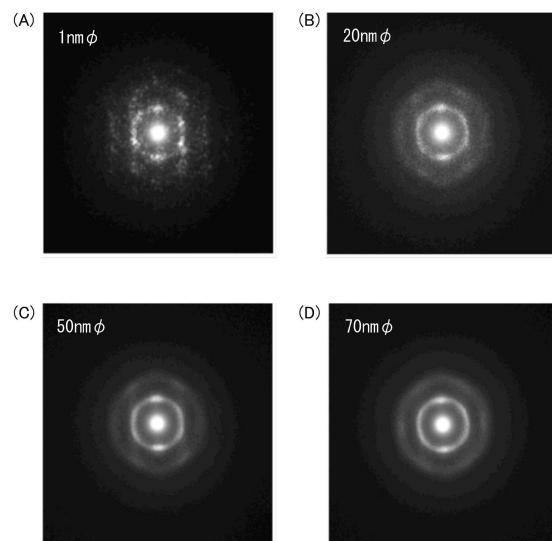

図20にC A A C - O S 膜の断面TEM (Transmission Electron Microscope (透過型電子顕微鏡)) 像を示す。また、図21に図20のポイント1乃至ポイント4において電子線回折を用いて測定した電子線回折パターンを示す。

**【0288】**

図20に示す断面TEM画像は、透過型電子顕微鏡 (日立ハイテクノロジーズ製「H-9000NAR」) を用い、加速電圧を300kV、倍率200万倍で撮影した画像である。また、図21に示す電子線回折パターンは、透過型電子顕微鏡 (日立ハイテクノロジーズ製「HF-2000」) を用い、加速電圧を200kV、ビーム径を約1nm または約50nm とした電子線回折パターンである。なお、ビーム径が10nm 以下とした電子線回折を、特に極微電子線回折と呼ぶことがある。また、ビーム径を約1nm とした場合の電子線回折での測定範囲は、5nm 以上10nm 以下である。

**【0289】**

図20に示すポイント1 (膜表面側)、ポイント2 (膜中央)、ポイント3 (膜下地側) における電子線回折パターンが図21 (A)、(B)、(C) にそれぞれ対応しており、電子ビーム径を約1nm とした電子線回折パターンである。また、図20に示すポイント4 (膜全体) における電子線回折パターンが図21 (D) であり、電子ビーム径を約50nm とした電子線回折パターンである。

**【0290】**

ポイント1 (膜表面側) およびポイント2 (膜中央) の電子線回折パターンは、スポット (輝点) によるパターンの形成が確認できるが、ポイント3 (膜下地側) では、ややパターンが崩れている。これは、C A A C - O S 膜の膜厚方向において、結晶状態が異なることを示唆している。なお、ポイント4 (膜全体) においては、スポット (輝点) によるパターンの形成が確認できることから、膜全体としてはC A A C - O S 膜である、または、C A A C - O S 膜を含む膜であることができる。

**【0291】**

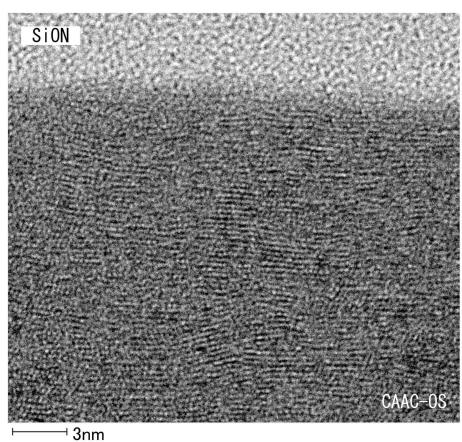

図22は、図20におけるポイント1 (膜表面側) の近傍の拡大写真である。層間絶縁膜である酸化窒化珪素膜との界面までC A A C - O S 膜の配向性を示す明瞭な格子像を確認することができる。

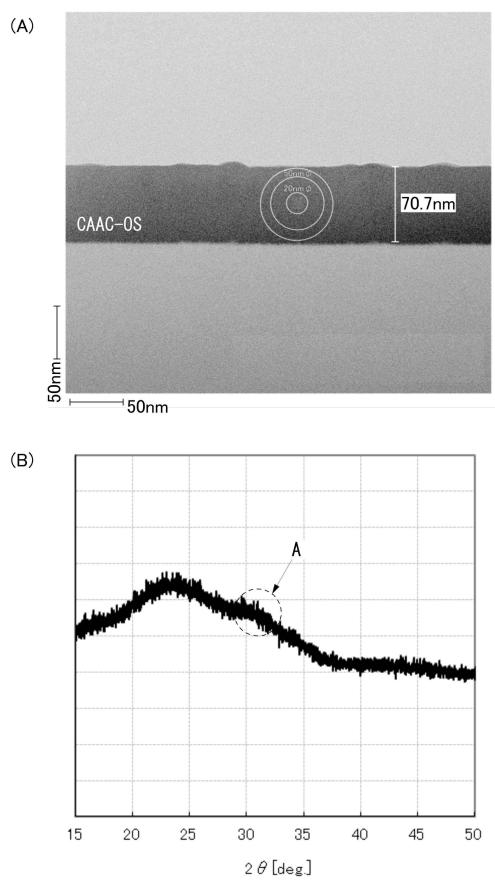

**【0292】**

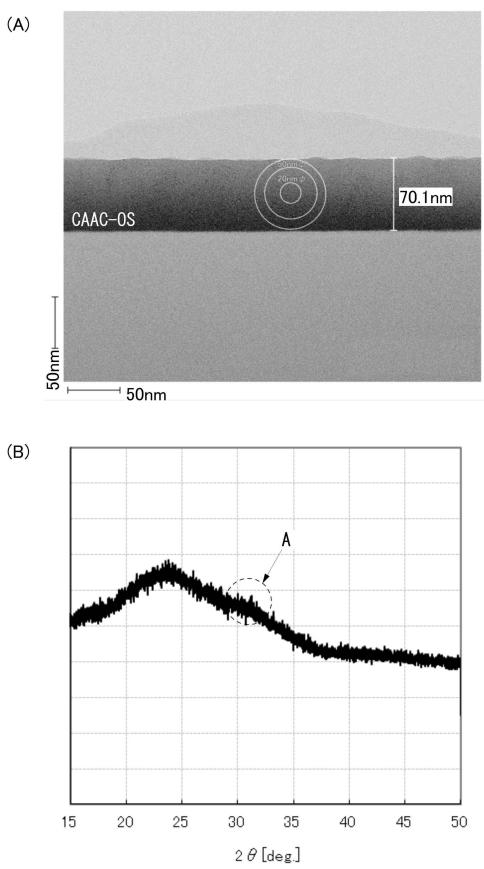

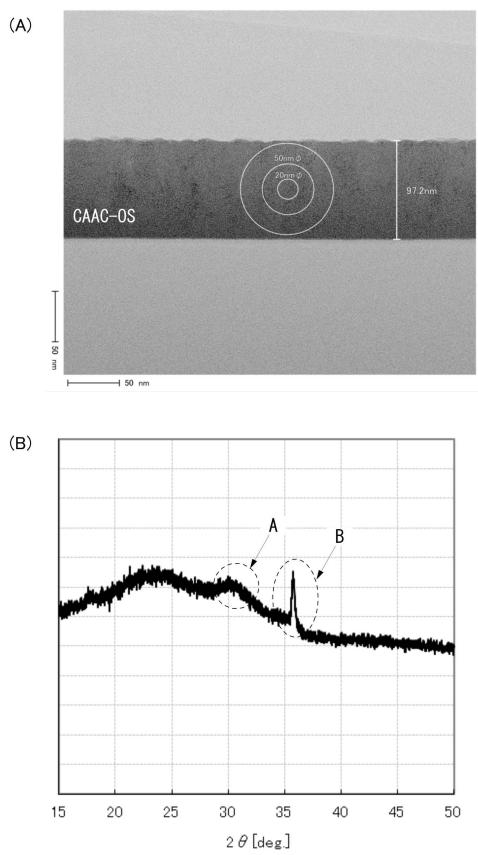

図23 (A)、(B) は、図20の断面TEM観察に用いたC A A C - O S 膜とは異なるC A A C - O S 膜の断面TEM写真とX線回折スペクトルである。C A A C - O S 膜は様々な形態があり、図23 (B) に示すような $2\theta = 31^\circ$  近傍に結晶成分を示すピークAが現れる。なお、当該ピークは明瞭に現れない場合もある。

**【0293】**

図23 (A) のC A A C - O S 膜に同心円で示す領域において、電子線のビーム径を1nm、20nm、50nm、70nm として、電子線回折を行った結果を図24 (A)、(B)、(C)、(D) に示す。電子線のビーム径が1nm においては、図21 (A)、(B) と同様に明瞭なスポット (輝点) によるパターンの形成を確認することができる。電子線のビーム径を大きくしていくとスポット (輝点) がやや不明瞭になるが、回折パターンは確認することができ、膜全体としてはC A A C - O S 膜である、またはC

10

20

30

40

50

A A C - O S 膜を含む膜であるということができる。

**【 0 2 9 4 】**

図 25 (A)、(B) は、図 23 (A) の断面 TEM 觀察に用いた C A A C - O S 膜を 450 °でアニールした後の断面 TEM 写真と X 線回折スペクトルである。

**【 0 2 9 5 】**

図 25 (A) の C A A C - O S 膜に同心円で示す領域において、電子線のビーム径を 1 nm、20 nm、50 nm、70 nm として、電子線回折を行った結果を図 26 (A)、(B)、(C)、(D) に示す。図 24 に示した結果と同様に、電子線のビーム径が 1 nm においては、明瞭なスポット（輝点）によるパターンの形成を確認することができる。また、電子線のビーム径を大きくしていくとスポット（輝点）がやや不明瞭になるが、回折パターンは確認することができ、膜全体としては C A A C - O S 膜である、または C A A C - O S 膜を含む膜であるといふことができる。

10

**【 0 2 9 6 】**

図 27 (A)、(B) は、図 20 の断面 TEM 写真に用いた C A A C - O S 膜、および図 23 (A) の断面 TEM 觀察に用いた C A A C - O S 膜とは異なる C A A C - O S 膜の断面 TEM 写真と X 線回折スペクトルである。C A A C - O S 膜は様々な形態があり、図 27 (B) に示すように 2 = 31 °近傍に結晶成分を示すピーク A が現れるとともに、スピネル結晶構造に由来するピーク B が現れる場合もある。

**【 0 2 9 7 】**

図 27 (A) の C A A C - O S 膜に同心円で示す領域において、電子線のビーム径を 1 nm、20 nm、50 nm、90 nm として、電子線回折を行った結果を図 28 (A)、(B)、(C)、(D) に示す。電子線のビーム径が 1 nm においては、明瞭なスポット（輝点）によるパターンの形成を確認することができる。また、電子線のビーム径を大きくしていくとスポット（輝点）がやや不明瞭になるが、回折パターンは確認することができる。また、ビーム径 90 nm では、より明瞭なスポット（輝点）を確認することができる。したがって、膜全体としては C A A C - O S 膜である、または C A A C - O S 膜を含む膜であるといふことができる。

20

**【 0 2 9 8 】**

ここで、C A A C - O S 膜の局在準位について説明する。ここでは、C A A C - O S 膜を C P M (Constant photocurrent method) 測定で評価した結果について説明する。

30

**【 0 2 9 9 】**

まず、C P M 測定した試料の構造について説明する。

**【 0 3 0 0 】**

測定試料は、ガラス基板上に設けられた酸化物半導体膜と、該酸化物半導体膜に接する一対の電極と、酸化物半導体膜および一対の電極を覆う絶縁膜と、を有する。

**【 0 3 0 1 】**

次に、測定試料に含まれる酸化物半導体膜の形成方法について説明する。

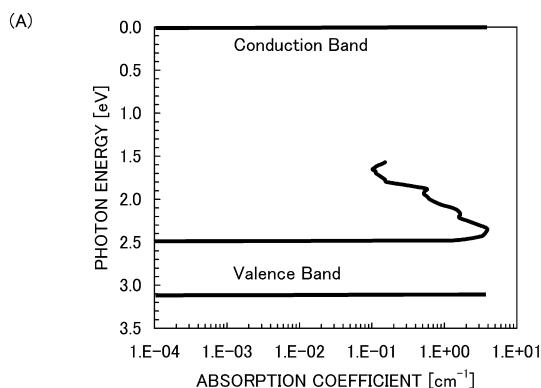

**【 0 3 0 2 】**

I n - G a - Z n 酸化物 (I n : G a : Z n = 1 : 1 : 1 [原子数比]) であるターゲットを用い、成膜ガスとしてアルゴンガスを 30 s c c m、酸素ガスを 15 s c c m 用い、圧力を 0.4 Pa とし、基板温度を 400 °とし、DC 電力を 0.5 kW 印加する条件を用いたスパッタリング法により、酸化物半導体膜を形成した。次に、450 °の窒素雰囲気で 1 時間加熱した後、450 °の酸素雰囲気で 1 時間加熱して、酸化物半導体膜に含まれる水素を脱離させる処理および酸化物半導体膜に酸素を供給する処理を行った。なお、当該酸化物半導体膜は C A A C - O S 膜である。

40

**【 0 3 0 3 】**

次に、酸化物半導体膜を有する測定試料について C P M 測定を行った。具体的には、酸化物半導体膜に接して設けた一対の電極間に電圧を印加した状態で光電流値が一定となるように端子間の試料面に照射する光量を調整し、所望の波長の範囲において照射光量から吸

50

吸収係数を導出した。

**【0304】**

各測定試料を CPM 測定して得られた吸収係数からバンドテイル起因の吸収係数を除いた吸収係数、即ち欠陥に起因する吸収係数を図 12 に示す。図 12 において、横軸は吸収係数を表し、縦軸は光エネルギーを表す。なお、図 12 の縦軸において、酸化物半導体膜の伝導帯の下端を 0 eV とし、価電子帯の上端を 3.15 eV とする。また、図 12 において、曲線は吸収係数と光エネルギーの関係を示し、欠陥準位に相当する。

**【0305】**

図 12 に示す曲線において、欠陥準位による吸収係数は、 $5.86 \times 10^{-4} \text{ cm}^{-1}$  であった。即ち、CAC-O<sub>S</sub> 膜は、欠陥準位による吸収係数が  $1 \times 10^{-3} / \text{cm}$  未満、好ましくは  $1 \times 10^{-4} / \text{cm}$  未満であり、欠陥準位密度の低い膜である。

10

**【0306】**

なお、酸化物半導体膜に関し、X線反射率法(XRR(X-ray Reflectometry))を用いた膜密度の測定を行った。酸化物半導体膜の膜密度は、 $6.3 \text{ g/cm}^3$  であった。即ち、CAC-O<sub>S</sub> 膜は、膜密度の高い膜である。

**【0307】**

なお、本実施の形態は、本明細書で示す他の実施の形態と適宜組み合わせができる。

。

**【0308】**

(実施の形態 5 )

20

上記実施の形態で一例を示したトランジスタおよび容量素子を用いて表示機能を有する半導体装置(表示装置)を作製することができる。また、トランジスタを含む駆動回路の一部または全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。本実施の形態では、上記実施の形態で一例を示したトランジスタを用いた表示装置の例について、図 29 乃至図 31 を用いて説明する。なお、図 30 は、図 29 (B) 中で M-N の一点鎖線で示した部位の断面構成を示す断面図である。なお、図 30 において、画素部の構造は一部のみ記載している。

**【0309】**

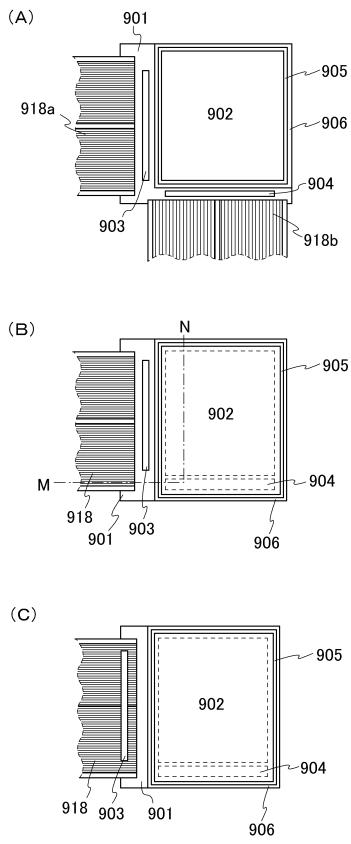

図 29 (A)において、第 1 の基板 901 上に設けられた画素部 902 を囲むようにして、シール材 905 が設けられ、第 2 の基板 906 によって封止されている。図 29 (A)においては、第 1 の基板 901 上のシール材 905 によって囲まれている領域とは異なる領域に、別途用意された基板上に単結晶半導体または多結晶半導体で形成された第 2 の駆動回路 903、および第 1 の駆動回路 904 が実装されている。また、第 2 の駆動回路 903、第 1 の駆動回路 904、または画素部 902 に与えられる各種信号および電位は、FPC(Flexible printed circuit) 918a、FPC 918b から供給されている。

30

**【0310】**

なお、第 1 の駆動回路 904 は、走査線駆動回路としての機能を有する。また、第 2 の駆動回路 903 は、信号線駆動回路としての機能を有する。

**【0311】**

図 29 (B) および図 29 (C) において、第 1 の基板 901 上に設けられた画素部 902 と、第 1 の駆動回路 904 とを囲むようにして、シール材 905 が設けられている。また画素部 902 と、第 1 の駆動回路 904 の上に第 2 の基板 906 が設けられている。よって画素部 902 と、第 1 の駆動回路 904 とは、第 1 の基板 901 とシール材 905 と第 2 の基板 906 とによって、表示素子と共に封止されている。図 29 (B) および図 29 (C) においては、第 1 の基板 901 上のシール材 905 によって囲まれている領域とは異なる領域に、別途用意された単結晶半導体または多結晶半導体で形成された第 2 の駆動回路 903 が実装されている。図 29 (B) および図 29 (C) においては、第 2 の駆動回路 903、第 1 の駆動回路 904、または画素部 902 に与えられる各種信号および電位は、FPC 918 から供給されている。

40

50

## 【0312】

また、図29(B)および図29(C)においては、第2の駆動回路903を別途形成し、第1の基板901に実装している例を示しているが、この構成に限定されない。第1の駆動回路を別途形成して実装しても良いし、第2の駆動回路の一部または第1の駆動回路の一部のみを別途形成して実装しても良い。

## 【0313】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG(Chip On Glass)法、ワイヤボンディング法、或いはTCP(Tape Carrier Package)などを実装する方法を用いることができる。図29(A)は、COG方法により第2の駆動回路903、第1の駆動回路904を実装する例であり、図29(B)は、COG方法により第2の駆動回路903を実装する例であり、図29(C)は、第2の駆動回路903をTCPとして実装する例である。10

## 【0314】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含むIC等を実装した状態にあるモジュールとを含む。

## 【0315】

なお、本明細書における表示装置とは、画像表示デバイスまたは表示デバイスを指す。また、表示装置の代わりに光源(照明装置含む)として機能させることができる。また、コネクター、例えばFPCもしくはTCPが取り付けられたモジュール、TCPの先にプリント配線板が設けられたモジュール、または表示素子にCOG方式によりIC(集積回路)が直接実装されたモジュールも全て表示装置に含むものとする。20

## 【0316】

また、第1の基板上に設けられた画素部および第1の駆動回路は、トランジスタを複数有しており、上記実施の形態で示したトランジスタを適用することができる。

## 【0317】

表示装置に設けられる表示素子としては液晶素子、発光素子などを用いることができる。液晶素子の一例としては、液晶の光学的変調作用によって光の透過または非透過を制御する素子がある。その素子は一对の電極と液晶層により構造されることが可能である。なお、液晶の光学的変調作用は、液晶にかかる電界(横方向の電界、縦方向の電界または斜め方向の電界を含む)によって制御される。なお、具体的には、液晶素子の一例としては、ネマチック液晶、コレステリック液晶、スマートチック液晶、ディスコチック液晶、サーモトロピック液晶、リオトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶(PDLA)、強誘電液晶、反強誘電液晶、主鎖型液晶、側鎖型高分子液晶、バナナ型液晶などを挙げることができる。また液晶の駆動方法としては、TN(Twisted Nematic)モード、STN(Super Twisted Nematic)モード、IPS(In-Plane-Switching)モード、FFS(Fringe Field Switching)モード、MVA(Multi-domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASV(Advanced Super View)モード、ASM(Axially Symmetric aligned Micro-cell)モード、OCB(Optically Compensated Birefringence)モード、ECB(Electrically Controlled Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(Antiferroelectric Liquid Crystal)モード、PDLC(Polymer Dispersed Liquid Crystal)モード、PNLC(Polymer Network Liquid Crystal)モード、ゲストホストモード、ブルー相(Blue Phase)モードなどがある。ただし、これに限定されず、液晶素子およびその駆動方式として様々なものを用いることができる。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL(Electro Luminescence)モードなどがある。

30

40

50

escence) 素子、有機EL素子等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。図30に、表示素子として液晶素子を用いた液晶表示装置の例を示す。

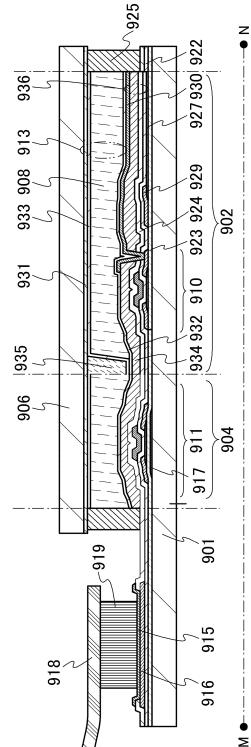

#### 【0318】

図30は、縦電界方式の液晶表示装置の断面図である。当該液晶表示装置は、接続端子電極915および端子電極916を有しており、接続端子電極915および端子電極916はFPC918が有する端子と異方性導電剤919を介して、電気的に接続されている。

#### 【0319】

接続端子電極915は、第1の電極930と同じ導電膜から形成され、端子電極916は、トランジスタ910、911のソース電極およびドレイン電極と同じ導電膜で形成されている。

#### 【0320】

また、第1の基板901上に設けられた画素部902と、第1の駆動回路904は、トランジスタを複数有しており画素部902に含まれるトランジスタ910と、第1の駆動回路904に含まれるトランジスタ911とを例示している。トランジスタ910およびトランジスタ911上には実施の形態1に示す絶縁膜129、絶縁膜131、および絶縁膜132に相当する絶縁膜924が設けられている。また、絶縁膜924上には平坦性を高めるための絶縁膜934が設けられている。また、絶縁膜923は窒化絶縁膜である。

#### 【0321】

本実施の形態では、トランジスタ910として、上記実施の形態1で示した画素101に設けられるトランジスタを適用することができる。また、トランジスタ911として、上記実施の形態1で示した第1の駆動回路104に設けられるトランジスタを適用することができる。なお、トランジスタ911は、導電膜917を設けた構成を例示しているが、導電膜917を設けない構成であってもよい。

#### 【0322】

また、酸化物半導体膜927、絶縁膜924、絶縁膜934、および第1の電極930を用いて、容量素子936を構成する。なお、酸化物半導体膜927は、容量線929と電気的に接続する。容量線929は、トランジスタ910、トランジスタ911のゲート電極と同じ導電膜から形成される。なお、ここでは、容量素子936として実施の形態1に示した容量素子を図示したが、適宜他の実施の形態に示した容量素子を用いることができる。

#### 【0323】

画素部902に設けられたトランジスタ910は表示素子と電気的に接続し、表示パネルを構成する。表示素子は表示を行うことができれば特に限定されず、様々な表示素子を用いることができる。

#### 【0324】

表示素子である液晶素子913は、第1の電極930、第2の電極931、および液晶層908を含む。なお、液晶層908を挟持するように配向膜として機能する絶縁膜932および絶縁膜933が設けられている。また、第2の電極931は第2の基板906側に設けられ、第1の電極930と第2の電極931とは液晶層908を介して重なる構成となっている。

#### 【0325】

表示素子に電圧を印加するために設けられる第1の電極930および第2の電極931(画素電極、共通電極、対向電極などともいう)においては、取り出す光の方向、電極が設けられる場所、および電極のパターン構造によって透光性、反射性を選択することができる。

#### 【0326】

第1の電極930および第2の電極931は、実施の形態1に示す画素電極121と同様の材料を適宜用いることができる。

#### 【0327】

10

20

30

40

50

また、スペーサ 935 は絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、第1の電極 930 と第2の電極 931 との間隔（セルギャップ）を制御するために設けられている。なお、球状のスペーサを用いていてもよい。

#### 【0328】

表示素子として、液晶素子を用いる場合、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料は、条件により、コレステリック相、スマートチック相、キュービック相、カイラルネマチック相、等方相等を示す。

#### 【0329】

また、配向膜を用いないブルー相を示す液晶を用いててもよい。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は狭い温度範囲でしか発現しないため、温度範囲を改善するためにカイラル剤を混合させた液晶組成物を用いて液晶層に用いる。なお、配向膜は有機樹脂で構成されており、有機樹脂は水素または水などを含むことから、本発明の一態様である半導体装置のトランジスタの電気特性を低下させるおそれがある。そこで、液晶層として、ブルー相を用いることで、有機樹脂を用いずに本発明の一態様である半導体装置を作製することができ、信頼性の高い半導体装置を得ることができる。

#### 【0330】

第1の基板 901 および第2の基板 906 はシール材 925 によって固定されている。シール材 925 は、熱硬化樹脂、光硬化樹脂などの有機樹脂を用いることができる。また、シール材 925 は、絶縁膜 924 と接している。なお、シール材 925 は図 29 に示すシール材 905 に相当する。

#### 【0331】

シール材 925 は、絶縁膜 924 上に設けられている。また、絶縁膜 934 は、シール材 925 の内側に設けられている。絶縁膜 924 の最上層は窒化絶縁膜であり、外部から水素や水などの不純物の侵入を抑制することが可能である。一方、絶縁膜 934 は、透湿性が高い。このため、絶縁膜 934 をシール材 925 の内側に設け、絶縁膜 924 上にシール材 925 を設けることで、外部から水素や水などの不純物の侵入を抑制し、トランジスタ 910 およびトランジスタ 911 の電気特性の変動を抑制することができる。

#### 【0332】

また、液晶表示装置において、ブラックマトリクス（遮光膜）、偏光部材、位相差部材、反射防止部材などの光学部材（光学基板）などは適宜設ける。例えば、偏光基板および位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライトなどを用いてもよい。

#### 【0333】

また、トランジスタは静電気などにより破壊されやすいため、駆動回路保護用の保護回路を設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

#### 【0334】

図 31 に、図 30 に示す液晶表示装置において、基板 906 に設けられた第2の電極 931 と電気的に接続するための共通接続部（パッド部）を、基板 901 上に形成する例を示す。

#### 【0335】

共通接続部は、基板 901 と基板 906 とを接着するためのシール材と重なる位置に配置され、シール材に含まれる導電性粒子を介して第2の電極 931 と電気的に接続される。または、シール材と重ならない箇所（但し、画素部を除く）に共通接続部を設け、共通接続部に重なるように導電性粒子を含むペーストをシール材とは別途設けて第2の電極 931 と電気的に接続してもよい。

#### 【0336】

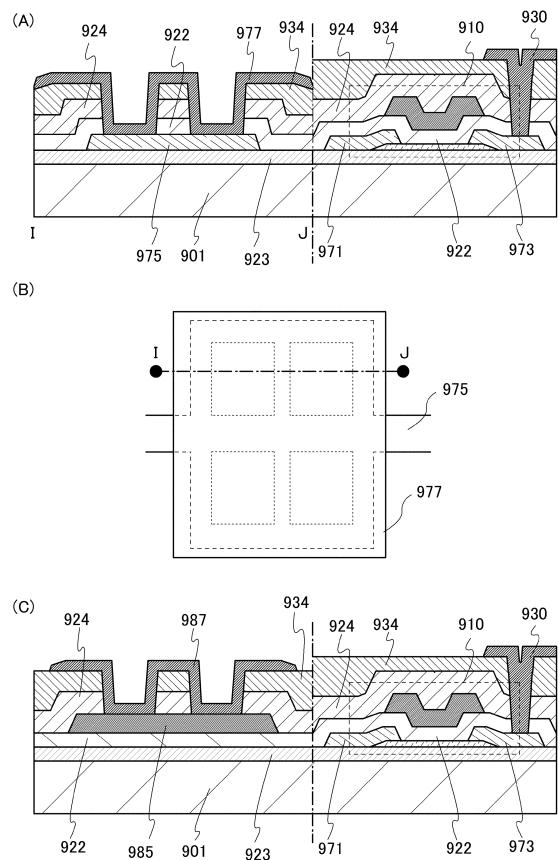

図 31 (A) の右側は、画素部に設けられるトランジスタ 910 の断面図であり、図 31 (A) の左側は、当該トランジスタと同じ工程を利用して形成することのできる共通接続

10

20

30

40

50

部の断面図である。図31(A)に示す共通接続部は、図31(B)に示す共通接続部の上面図におけるI-Jの断面に相当する。

【0337】

共通電位線975は、ゲート絶縁膜922上に設けられ、トランジスタ910のソース電極971またはドレイン電極973と同じ材料および同じ工程を利用して作製される。

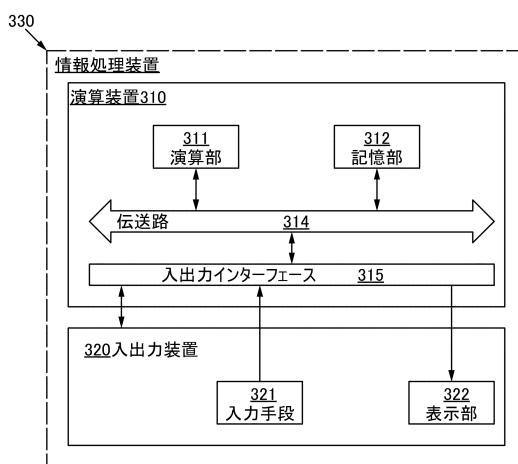

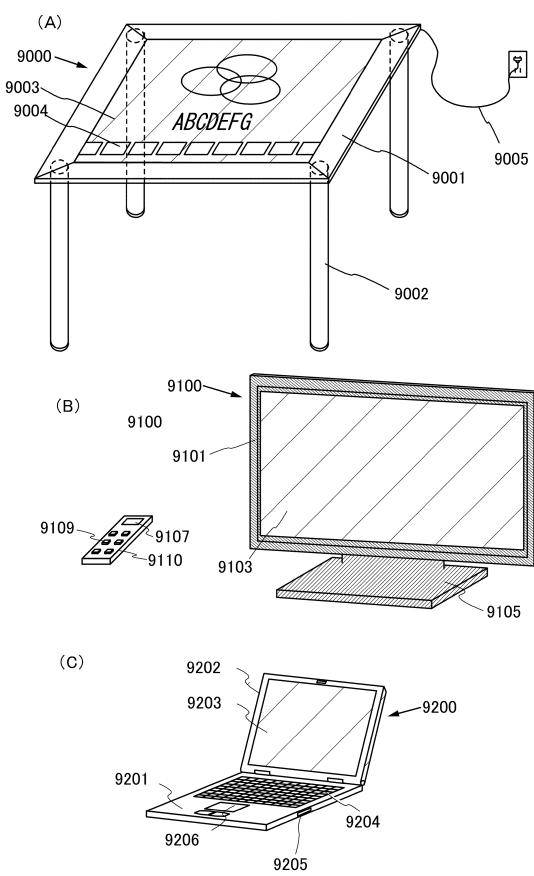

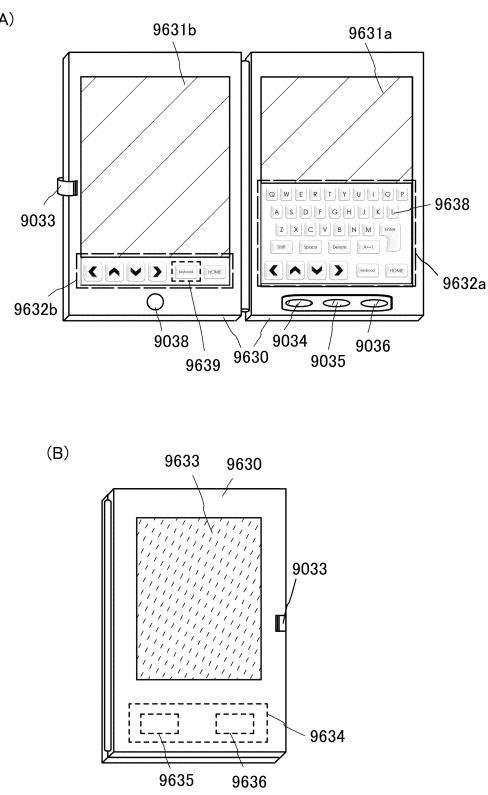

【0338】