#### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2009-238819 (P2009-238819A)

(43) 公開日 平成21年10月15日(2009, 10, 15)

| (51) Int.Cl. |               |           | F 1  |       |   | テーマコード (参考) |

|--------------|---------------|-----------|------|-------|---|-------------|

| HO1L 2       | 27/146        | (2006.01) | HO1L | 27/14 | A | 2H095       |

| GO3F         | 1/08          | (2006.01) | GO3F | 1/08  | A | 4M118       |

| HO4N         | <i>5/33</i> 5 | (2006.01) | HO4N | 5/335 | E | 5CO24       |

#### 審査譜求 未譜求 譜求項の数 12 〇1 (全 16 頁)

|                       |                                                      | 田旦明小                                        | 小明小                                                                                                 | 明小块以                               | ノ女X 14               | OL                   | \±                   | 10 貝/                |  |

|-----------------------|------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------|----------------------|----------------------|----------------------|----------------------|--|

| (21) 出願番号<br>(22) 出願日 | 特願2008-80008 (P2008-80008)<br>平成20年3月26日 (2008.3.26) | (71) 出願人<br>(74) 代理人<br>(72) 発明者<br>Fターム (参 | ソニー株式会社<br>東京都港区港南1丁目7番1号<br>代理人 100086298<br>弁理士 船橋 國則<br>発明者 馬渕 圭司<br>東京都港区港南1丁目7番1号 ソニー株<br>式会社内 |                                    |                      |                      |                      |                      |  |

|                       |                                                      |                                             | 4M1                                                                                                 | 18 AB01<br>CA32<br>GD04<br>24 AX01 | BA14<br>FA33<br>GD07 | CA03<br>GA02<br>GX24 | CA04<br>GC07<br>GY31 | CA18<br>GD03<br>JX36 |  |

(54) 【発明の名称】 リソグラフィー用マスクの作成方法、リソグラフィー用マスクデータの作成方法、裏面入射型固体撮像装置の製造方法、裏面入射型固体撮像装置および電子機器

### (57)【要約】

【課題】裏面入射型であっても表面入射型と区別せずに 扱うことができるようにする。

【解決手段】裏面入射型CMOSイメージセンサのチップの設計データ(A)については、裏面入射による撮像画像(C)の左右反転を意識することなく、通常のCMOSプロセスのIPを用いて、表面入射型と同様に設計する。端子図面であるI/O図面(B)も、信号図面も撮像画像(C)の左右反転を意識することなく、そのまま作る。そして、チップ全体のレイアウトデータまで組み上げた後、このレイアウトデータ(A)を製造のためのフォトリソグラフィー用のマスクに転写する前に、チップ全体で左右反転し、反転マスクデータ(E)を新たに作成する。そして、この反転マスクデータ(E)を用いてマスクを作成し、当該作成したマスクを用いて裏面入射型CMOSイメージセンサを作る。

【選択図】図4

#### 【特許請求の範囲】

### 【請求項1】

光電変換素子が形成される素子形成部の配線が形成される面側と反対側の面側から入射光を取り込む裏面入射型固体撮像装置の製造に用いるリソグラフィー用のマスクの作成に際して、

少なくとも出力端子の一部の位置を反転した反転データを用いて前記マスクを作成する リソグラフィー用マスクの作成方法。

### 【請求項2】

前記固体撮像装置のチップのレイアウトデータを作成し、

次いで、前記レイアウトデータをチップ全体で左右反転して前記反転データを作成し、 しかる後、前記反転データを用いて前記マスクを作成する

請求項1記載のリソグラフィー用マスクの作成方法。

### 【請求項3】

前記チップ上に配置するマークを前記レイアウトデータと別のデータとして作成し、当該別のデータを前記反転データと重ね合わせて前記反転データとする

請求項2記載のリソグラフィー用マスクの作成方法。

### 【請求項4】

前記マークは、リソグラフィー用の合わせに使うためのマーク、製造工程での検査に使うためのマーク、チップを特定するためのマーク、または製造工程での検査のときの座標の基準に使うためのマークである

請求項3記載のリソグラフィー用マスクの作成方法。

#### 【請求項5】

反転操作をしない枠に前記前記反転データを嵌め込んで前記マスクを作成する 請求項2記載のリソグラフィー用マスクの作成方法。

#### 【請求項6】

前記裏面入射型固体撮像装置は、

出力段が差動出力構成の出力回路部と、

前記出力回路部から出力される正相の信号と逆相の信号とをチップの外部に出力する正相の出力端子および逆相の出力端子とを有し、

前記反転データを作成する際に、前記正相の出力端子と前記逆相の出力端子との位置を 交換する

請求項1記載のリソグラフィー用マスクの作成方法。

#### 【請求項7】

前記正相の出力端子と前記逆相の出力端子との位置を交換したライブラリを作成しておき、当該ライブラリを用いて前記反転データを作成する

請求項6記載のリソグラフィー用マスクの作成方法。

#### 【請求項8】

光電変換素子が形成される素子形成部の配線が形成される面側と反対側の面側から入射光を取り込む裏面入射型固体撮像装置の製造に用いるリソグラフィー用のマスクデータの作成に際して、

前記固体撮像装置のチップのレイアウトデータを作成し、

次いで、前記レイアウトデータをチップ全体で左右反転した反転データを作成して当該 反転データを前記マスクデータとする

リソグラフィー用マスクデータの作成方法。

#### 【請求項9】

光電変換素子が形成される素子形成部の配線が形成される面側と反対側の面側から入射 光を取り込む裏面入射型固体撮像装置のチップのレイアウトデータを作成し、

次いで、前記レイアウトデータをチップ全体で左右反転した反転データを作成し、

次いで、前記反転データを用いて前記マスクを作成し、

しかる後、当該作成したマスクを用いて前記固体撮像装置を製造する

20

10

30

40

裏面入射型固体撮像装置の製造方法。

#### 【請求項10】

前記作成したマスクを用いて前記固体撮像装置を製造する際に、半導体基板に対するイオン注入の向きを前記レイアウトデータの反転に合わせて左右反転する

請求項9記載の裏面入射型固体撮像装置の製造方法。

### 【請求項11】

チップのレイアウトデータをチップ全体で左右反転した反転データをリソグラフィー用のマスクデータとし、当該マスクデータを用いて作成されたマスクを使用して製造された 裏面入射型固体撮像装置。

### 【請求項12】

チップのレイアウトデータをチップ全体で左右反転した反転データをリソグラフィー用のマスクデータとし、当該マスクデータを用いて作成されたマスクを使用して製造された 裏面入射型固体撮像装置を搭載した

電子機器。

【発明の詳細な説明】

### 【技術分野】

#### [00001]

本発明は、リソグラフィー用マスクの作成方法、リソグラフィー用マスクデータの作成方法、裏面入射型固体撮像装置の製造方法、裏面入射型固体撮像装置および電子機器に関する。

【背景技術】

### [0002]

固体撮像装置の一つとして、光電変換素子が形成される素子形成部の配線部が形成される面(表面)とは反対側の面(裏面)側から入射光を取り込む、いわゆる裏面入射型CMOSイメージセンサがある(例えば、特許文献 1 参照)。このように、裏面側から入射光を取り込む構造を採ることで、受光面を考慮して配線層の各金属配線を配設する必要がないため、配線の自由度が高くなる。その結果、画素の微細化および高開口率化を図ることができる。

### [0003]

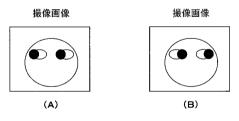

裏面入射型CMOSイメージセンサでは、チップを裏向きにマウントするため、表面入射型CMOSイメージセンサに対して撮像画像が左右反転して出てくる。例えば、表面入射型の撮像画像が図9(A)に示す画像であるとすると、裏面入射型の撮像画像は、図9(B)に示すように、表面入射型の撮像画像に対して左右が反転する。この場合、裏面入射型の撮像画像を表面入射型の撮像画像と左右関係を同じにするには、後段の信号処理ICにラインメモリ等を用いた左右反転機能をつけなければならない。

[0004]

【特許文献 1 】特開 2 0 0 3 - 3 1 7 8 5 号公報

### 【発明の開示】

【発明が解決しようとする課題】

#### [0005]

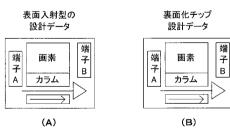

上述したことに加えて、裏面入射型 C M O S イメージセンサでは、撮像画像が表面入射型の撮像画像に対して左右が反転することで、次のような不具合が発生する。図 1 0 に、一例として、表面入射型(A)および裏面入射型(B)の C M O S イメージセンサのチップの設計データを示す。

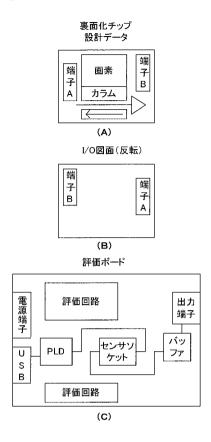

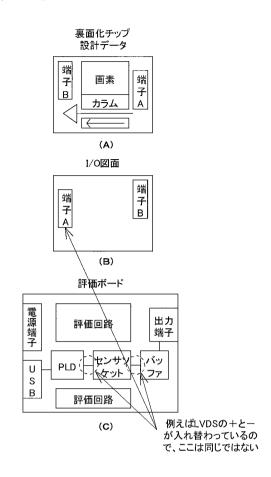

#### [0006]

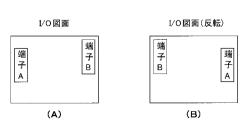

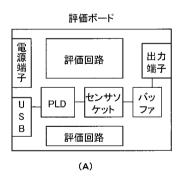

先ず、図11に示すように、CMOSイメージセンサの端子位置を規定したI/O図面(端子図面)が反転する。図11において、(A)が表面入射型の場合を、(B)が裏面入射型の場合をそれぞれ示している。このように、端子位置を規定したI/O図面が反転すると、図12に示すように、評価時あるいは製品でセンサを搭載するボードも左右反転して設計しなおさなければならない。

10

20

30

40

#### [0007]

図12において、(A)が表面入射型の場合を、(B)が裏面入射型の場合をそれぞれ示している。また、評価回路とは、レギュレータ、各種のチェック端子などを含む回路のことを言う。

### [0008]

しかしながら、以下の理由から、単純にボードを左右反転して設計しなおせばよいという訳ではない。その理由の1つは、信号の入る向きや出る向き、電源端子の位置などは通常使い勝手のよい位置にだいたい決められているので、それらの位置を左右反転するのは好ましくない。

### [0009]

別の1つは、センサの電源端子などの端子位置は反転しても、他のPLD(Programmab le Logic Device)などの端子位置は反転している訳ではないので、それらの間の配線は左右反転では済まないことである。具体的には、図12(B)に示すように、CMOSイメージセンサへの配線について、入出力関係を逆にするように引きまわした形にすることになる。

#### [0010]

このような配線の引き回しについては、ボード上の配線で引き回しても対応してもよいし、センサパッケージとソケットの間の変換コネクタで対応してもよい。ただし、どちらの対応策を採ったとしても数十本以上の配線を交差させることになるため、かなり無理があり、またノイズが乗りやすくなる。特に、変換コネクタについてはセンサのボード面からの高さが変わるため、この点もイメージセンサとして問題である。

#### [ 0 0 1 1 ]

もちろん、裏面入射型CMOSイメージセンサが単独に存在するのであれば、信号や端子位置の反転の問題はなく、それに合わせて、評価系、後段の信号処理IC、システム、カメラなど全てを作れば良いことになる。しかしながら、現実には、コストと性能のトレードオフなどの都合から、表面入射型CMOSイメージセンサと共存することになる。その場合、信号の左右や、入出力端子の位置などが大きく変わることは望ましくない。

#### [0012]

上記の不具合に対して、従来は、以下のような対応策を採っていた。最も簡単には、図13に示すように、チップの設計データ(A)を、水平走査方向を反転走査するように設計する。この場合、図9(A)に示すように、撮像画像は正常になる。したがって、後段の処理系としては従来のものがそのまま使える。

#### [0013]

但し、端子位置については、図13(B)に示すように、チップを裏返すことで反転してしまうので、センサを実装するボード(C)の問題は残る。たとえ、すでにある表面入射型のチップを裏面化したとしても、ボードについては作り直しとなる。ウェーハ状態でのテストでも、左右反転したプローブを作り直し、ソフトも左右反転対応させる煩雑さとコストがかかる。

## [0014]

根本的には、図14(B)に示すように、端子位置も左右逆に置くように、最初から設計することになる。最初から設計するので問題無さそうに思えるが、実際にはやはり問題がある。СMOSイメージセンサもIP(Intellectual Property)を使って設計される。 裏面入射型も一般のСMOSライブラリのIP、当然表面入射型でも使っているものを用いて設計する。

# [0015]

ここで、例えば、CMOSイメージセンサの出力段を差動出力構成とする場合などの差動入出力端子を見ると、正極性の端子と負極性の端子が入れ替わる。その結果、通常ではCMOSイメージセンサに限らずCMOSLSI全般で共通な仕様が、裏面入射型では異なってしまい、測定やカメラ実装のときにいちいち対応しなければならないなどの不都合が生ずる。

10

20

30

40

#### [0016]

特に、表面入射型とコンパチブルなものを作るときは、内部ブロックでもIPの端子の 出る向きは変わってないので、先のセンサ実装ボードの例と同様に、全体的なブロック配 置 や 配 線 の 再 構 成 が 必 要 で あ る 。 し た が っ て 、 表 面 入 射 型 で 最 適 化 し て 無 駄 の 少 な い レ イ アウトになっているものが、裏面入射型ではそもそもそのサイズに収まるかどうかも不確 実である。

#### [0017]

そこで、本発明は、裏面入射型であっても表面入射型と区別せずに扱うことができるよ うにするリソグラフィー用マスクの作成方法、リソグラフィー用マスクデータの作成方法 、 裏 面 入 射 型 固 体 撮 像 装 置 の 製 造 方 法 、 裏 面 入 射 型 固 体 撮 像 装 置 お よ び 電 子 機 器 を 提 供 す ることを目的とする。

【課題を解決するための手段】

### [ 0 0 1 8 ]

上記目的を達成するために、本発明は、

光電変換素子が形成される素子形成部の配線が形成される面側と反対側の面側から入射 光 を 取 り 込 む 裏 面 入 射 型 固 体 撮 像 装 置 の 製 造 に 用 い る リ ソ グ ラ フ ィ ー 用 の マ ス ク デ ー タ の 作成に際して、

少 な く と も 出 力 端 子 の 一 部 の 位 置 を 反 転 し た 反 転 デ ー タ を リ ソ グ ラ フ ィ ー 用 の マ ス ク デ ータとし、当該マスクデータ用いて前記マスクを作成する。

### [0019]

少なくとも出力端子の一部の位置を反転した反転データを用いてマスクを作成すること で、裏面入射型であっても表面入射型と区別せずに扱うことができる固体撮像装置を製造 することができる。このようにして製造された裏面入射型固体撮像装置を、画像取込部( 光電変換部)に固体撮像装置を用いる電子機器において、当該固体撮像装置として搭載し て用いることができる。

### 【発明の効果】

### [0020]

本発明によれば、裏面入射型であっても表面入射型と区別せずに扱うことができるため に、裏面入射型固体撮像装置を搭載する評価ボードや後段の信号処理ICに特別な仕様を 要求したり、コストをかけたりしなくて済む。

【発明を実施するための最良の形態】

## [0021]

以下、本発明の実施の形態について図面を参照して詳細に説明する。

### [0022]

### [固体撮像装置]

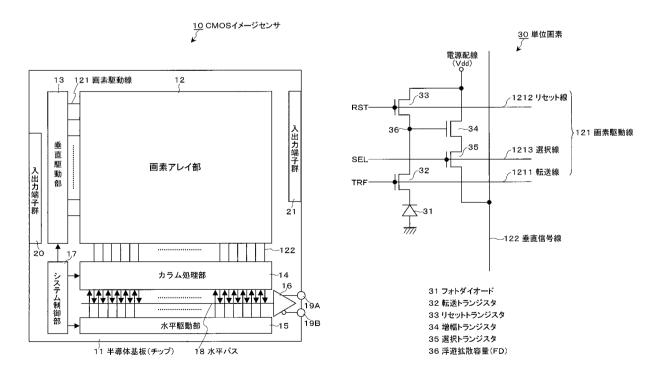

図1は、本発明が適用される裏面入射型固体撮像装置、例えば裏面入射型СМОSイメ ージセンサのシステム構成の概略を示すシステム構成図である。

### [0023]

図1に示すように、本適用例に係るCMOSイメージセンサ10は、半導体基板(チッ プ)11上に形成された画素アレイ部12と、当該画素アレイ部12と同じチップ11上 に集積された周辺回路部とを有する構成となっている。周辺回路部として、例えば、垂直 駆 動 部 1 3 、 カ ラ ム 処 理 部 1 4 、 水 平 駆 動 部 1 5 、 出 力 回 路 部 1 6 お よ び シ ス テ ム 制 御 部 17が設けられている。

# [ 0 0 2 4 ]

画素アレイ部12には、入射光量に応じた電荷量の光電荷を発生して内部に蓄積する光 電変換素子を有する単位画素(以下、単に「画素」と記述する場合もある)が行列状に2 次元配置されている。単位画素の具体的な構成については後述する。

画素アレイ部12にはさらに、行列状の画素配列に対して行ごとに画素駆動線121が 予行方向/行方向(画素行の画素の配列方向)に沿って配線され、列ごとに垂直信号線1

10

20

30

40

10

20

30

40

50

22が縦方向/列方向(画素列の画素の配列方向)に沿って配線されている。図1では、画素駆動線121について1本として示しているが、1本に限られるものではない。画素駆動線121の一端は、垂直駆動部13の各行に対応した出力端に接続されている。

#### [0026]

垂直駆動部13は、シフトレジスタやアドレスデコーダなどによって構成され、画素アレイ部12の各画素を、全画素同時あるいは行単位等で駆動する画素駆動部である。この垂直駆動部13はその具体的な構成については図示を省略するが、一般的に、読出し走査系と掃出し走査系の2つの走査系を有する構成となっている。

### [0027]

読出し走査系は、単位画素から信号を読み出すために、画素アレイ部12の単位画素を行単位で順に選択走査する。掃出し走査系は、読出し走査系によって読出し走査が行われる読出し行に対して、その読出し走査よりもシャッタスピードの時間分だけ先行して掃出し走査を行う。

### [0028]

この掃出し走査系による掃出し走査により、読出し行の単位画素の光電変換素子から不要な電荷が掃き出される(リセットされる)。そして、この掃出し走査系による不要電荷の掃き出し(リセット)により、いわゆる電子シャッタ動作が行われる。ここで、電子シャッタ動作とは、光電変換素子の光電荷を捨てて、新たに露光を開始する(光電荷の蓄積を開始する)動作のことを言う。

### [0029]

読出し走査系による読出し動作によって読み出される信号は、その直前の読出し動作または電子シャッタ動作以降に入射した光量に対応するものである。そして、直前の読出し動作による読出しタイミングまたは電子シャッタ動作による掃出しタイミングから、今回の読出し動作による読出しタイミングまでの期間が、単位画素における光電荷の蓄積時間(露光時間)となる。

### [0030]

垂直駆動部13によって選択走査された画素行の各単位画素から出力される信号は、垂直信号線122の各々を通してカラム処理部14に供給される。カラム処理部14は、画素アレイ部12の画素列ごとに、選択行の各単位画素から垂直信号線122を通して出力される信号に対して所定の信号処理を行うとともに、信号処理後の画素信号を一時的に保持する。

# [0031]

具体的には、カラム処理部14は、各単位画素の信号を受けて当該信号に対して、例えばCDS(Correlated Double Sampling;相関二重サンプリング)によるノイズ除去や、信号増幅や、AD(アナログ・デジタル)変換などの信号処理を行う。ノイズ除去処理により、リセットノイズや増幅トランジスタの閾値ばらつき等の画素固有の固定パターンノイズが除去される。なお、ここで例示した信号処理は一例に過ぎず、信号処理としてはこれらに限られるものではない。

### [0032]

水平駆動部15は、シフトレジスタやアドレスデコーダなどによって構成され、カラム処理部14の画素列に対応する単位回路を順番に選択する。この水平駆動部15による選択走査により、カラム処理部14で信号処理された画素信号が順番に水平バス18に出力され、当該水平バス18によって出力回路部16に伝送される。

### [0033]

出力回路部16は、水平バス18によって伝送される信号を処理して出力する。出力回路部16での処理としては、バッファリングだけの処理の場合もあるし、バッファリングの前に黒レベルを調整したり、列ごとのばらつきを補正したりするなど、各種のデジタル信号処理が挙げられる。

### [0034]

出力回路部16は、例えば、その出力段が差動の信号を出力する差動出力構成となって

いる。すなわち、出力回路部16の出力段は、水平バス18によって伝送される信号を処理して正相の信号として出力するとともに、その極性を反転して逆相の信号として出力する。この出力回路部16の出力段には、例えば、LVDS(Low Voltage Differential Signal)回路が用いられる。

### [0035]

正相の信号は正相の出力端子19Aを介してチップ11の外部に出力され、逆相の信号は逆相の出力端子19Bを介してチップ11の外部に出力される。出力回路部16の出力段を差動出力構成とした場合、チップ11の外部に設けられる信号処理部、例えば信号処理ICは、差動回路構成の入力段で正相および逆相の信号を受けることになる。

### [0036]

このように、出力回路部16の出力段を差動出力構成とし、信号処理ICの入力段を差動回路構成とすることで、出力回路部16の出力段と信号処理ICの入力段との間で電流によって情報を伝達することができる。これにより、出力回路部16の出力段と信号処理ICの入力段との間の伝送経路が長くなっても当該伝送経路での充放電が小さくなるためにシステムの高速化を実現できる。

#### [0037]

システム制御部17は、チップ11の外部から与えられるクロックや、動作モードを指令するデータなどを受け取り、また、本CMOSイメージセンサ10の内部情報などのデータを出力する。システム制御部17はさらには、各種のタイミング信号を生成するタイミングジェネレータを有し、当該タイミングジェネレータで生成された各種のタイミング信号を基に垂直駆動部13、カラム処理部14および水平駆動部15などの周辺回路部の駆動制御を行う。

### [0038]

チップ11の周縁部には、電源端子を含む入出力端子群20,21の各端子が設けられている。入出力端子群20,21は、チップ11の内部と外部との間で電源電圧や信号のやり取りを行う。入出力端子群20,21の配設位置としては、信号の入る向きや出る向きなどを考慮して使い勝手のよい位置に決められる。

#### [0039]

## (画素回路)

図 2 は、単位画素 3 0 の回路構成の一例を示す回路図である。本回路例に係る単位画素 3 0 は、光電変換素子であるフォトダイオード 3 1 と、例えば転送トランジスタ 3 2 、リセットトランジスタ 3 3 、増幅トランジスタ 3 4 および選択トランジスタ 3 5 の 4 つのトランジスタとを有する構成となっている。ここでは、これらトランジスタ 3 2 ~ 3 5 として、例えば N チャネルの M O S トランジスタを用いているが、これに限られるものではない。

### [0040]

転送トランジスタ32、リセットトランジスタ33および選択トランジスタ35の駆動制御のために、先述した画素駆動線121として、転送制御線1211、リセット制御線1212および選択制御線1213が行ごとに配線されている。

#### [0041]

転送トランジスタ32は、フォトダイオード31のカソード電極と浮遊拡散容量(FD)36との間に接続されており、フォトダイオード31で光電変換され、その内部に蓄積された光電荷(ここでは、電子)を、転送制御線1211を介してゲート電極に転送パルスTRGが与えられることによって浮遊拡散容量36に転送する。浮遊拡散容量36は、光電荷を電圧信号に変換する電荷電圧変換部として機能する

# [0042]

リセットトランジスタ33は、電源電圧Vddの画素電源にドレイン電極が、浮遊拡散容量36にソース電極がそれぞれ接続されており、フォトダイオード31から浮遊拡散容量36への光電荷の転送に先立って、リセット制御線1212を介してゲート電極にリセットパルスRSTが与えられることによって浮遊拡散容量36の電位をリセットする。

10

20

30

40

#### [0043]

増幅トランジスタ34は、浮遊拡散容量36にゲート電極が、電源電圧Vddの画素電源にドレイン電極がそれぞれ接続されており、リセットトランジスタ33によってリセットされた後の浮遊拡散容量36の電位をリセットレベルとして出力し、さらに転送トランジスタ32によって光電荷が転送された後の浮遊拡散容量36の電位を信号レベルとして出力する。

#### [0044]

選択トランジスタ35は、ドレイン電極が増幅トランジスタ34のソース電極に、ソース電極が垂直信号線122にそれぞれ接続されており、選択制御線1213を介してゲート電極に選択パルスSELが与えられることによってオン状態となり、画素30を選択状態として増幅トランジスタ34から出力される信号を垂直信号線122に出力する。選択トランジスタ35については、画素電源(Vdd)と増幅トランジスタ34のドレイン電極との間に接続した構成を採ることも可能である。

### [0045]

なお、ここでは、転送トランジスタ32、リセットトランジスタ33、増幅トランジスタ34および選択トランジスタ35を含む4トランジスタ構成の単位画素30を例に挙げたが、これは一例に過ぎない。すなわち、単位画素30としては、4トランジスタ構成の画素構成に限られるものではない。

# [0046]

# (裏面入射型の画素構造)

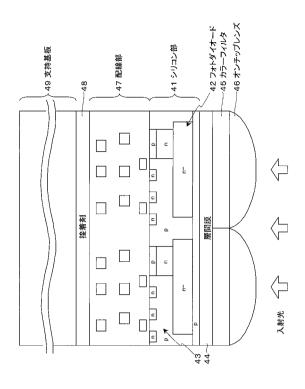

図3は、裏面入射型の画素構造の一例を示す断面図である。ここでは、2画素分の断面構造を示している。

### [0047]

図3において、シリコン部41には、フォトダイオード42や画素トランジスタ43が 形成される。すなわち、シリコン部41は素子形成部である。ここで、フォトダイオード 42は図2のフォトダイオード31に相当する。また、画素トランジスタ43は図2のト ランジスタ32~35に相当する。

#### [0048]

シリコン部 4 1 の一方の面側には、層間膜 4 4 を介してカラーフィルタ 4 5 およびオンチップレンズ 4 6 が作り込まれる。これにより、シリコン部 4 1 の一方の面側から入射する光は、オンチップレンズ 4 6 およびカラーフィルタ 4 5 を経由してフォトダイオード 4 2 の受光面に導かれる。

#### [0049]

シリコン部41の他方の面側には、画素トランジスタ43のゲート電極や金属配線が配線される配線部47が形成される。配線部47のシリコン部41と反対側の面には、接着剤48によって支持基板49が貼り付けられる。

# [0050]

上記の画素構造において、フォトダイオード42や画素トランジスタ43が形成されるシリコン部41の配線部47側を表面側と呼び、シリコン部41の配線部47と反対側を裏面側と呼ぶこととする。このような定義の下に、本画素構造は、シリコン部41の裏面側から入射光を取り込むことになるため裏面入射型の画素構造となる。

#### [0051]

以下では、裏面入射型の画素構造において、シリコン部 4 1 の表面側に画素トランジスタ 4 3 を作り込んだり、配線部 4 7 に金属配線を形成したりする工程を表面工程と呼ぶこととする。また、シリコン部 4 1 の裏面側にカラーフィルタ 4 5 およびオンチップレンズ 4 6 を造り込む工程を裏面工程と呼ぶこととする。

#### [0052]

### 「裏面入射型 С М О S イメージセンサの設計 1

以下に、裏面入射型 C M O S イメージセンサ 1 0 を設計するに当たっての具体的な実施例について説明する。

10

20

30

40

10

20

30

40

50

#### [ 0 0 5 3 ]

#### (実施例1)

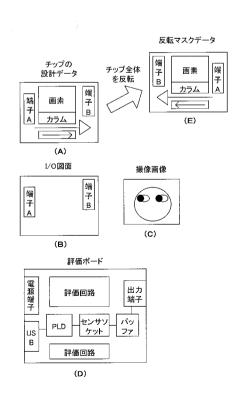

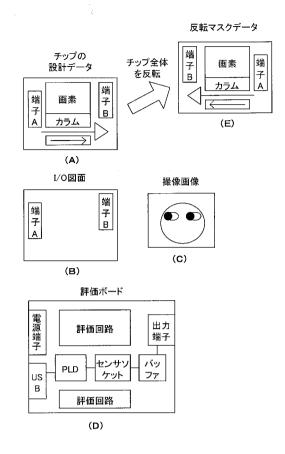

図4に示すように、裏面入射型CMOSイメージセンサ10のチップのレイアウトデータである設計データ(A)については、裏面入射による撮像画像(C)の左右反転を意識することなく、通常のCMOSプロセスのIPを用いて、表面入射型と同様に設計する。ここに、IP(Intellectual Property;知的所有権)とは、既に開発済みの知的財産(機能別ブロック)のことを言う。

### [0054]

端子図面である I / O 図面(B)も、信号図面も撮像画像(C)の左右反転を意識することなく、そのまま作る。そして、チップ全体のレイアウトデータまで組み上げた後、本実施例 1 では、このレイアウトデータ、即ちチップの設計データ(A)を製造のためのフォトリソグラフィー用のマスクに転写する前に、チップ全体で左右反転し、反転マスクデータ(E)を新たに作成する。

### [0055]

反転マスクデータ(E)の作成は、元データであるチップの設計データ(A)の×座標の符号を全て入れ替えることによって容易に実現できる。裏面入射型CMOSイメージセンサ10の製造については、この反転マスクデータ(E)に基づくレイアウトが焼き付けられたリソグラフィー用のマスクを用いて行う。

### [0056]

このようにして製造された C M O S イメージセンサ 1 0 は全体が反転しているが、それを裏面側から見ると、反転の反転で、端子位置も、出てくる撮像画像も、正転となっている。図 1 に示す出力回路部 1 6 の差動出力についても、正極性の端子と負極性の端子が入れ替わったりしていない。

#### [0057]

表面入射型チップとコンパチブルな裏面入射型チップを作る場合も、従来のような全体的な再設計の必要はない。例えば、チップ内ブロック間の配線をやり直す必要は無い。表面入射型のレイアウトデータを流用して、裏面側に関係する工程の部分のみ入れ替えまたは変更するだけで、端子位置、信号データとも同じものを作ることができる。

### [0058]

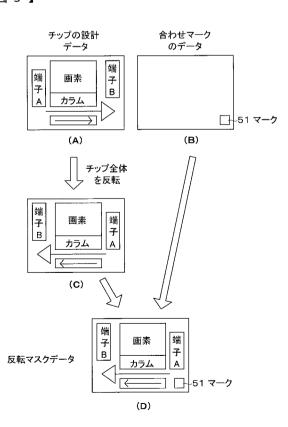

反転マスクデータ(E)を作成する際には以下のようにすることが重要である。すなわち、図5に示すように、表面側のマークのうち、チップに配置するマーク51を、チップのレイアウトデータ(A)と別のデータ(層)、即ち合わせマークのデータ(B)として持つ。マスク作成に進む前に、チップの設計データ(A)については反転させて反転設計データ(C)とする。合わせマークのデータ(B)については反転しない。そして、反転設計データ(C)と合わせマークのデータ(B)を重ね合わせたものを反転マスクデータ(D)とする。

# [0059]

ここで、チップに配置するマーク 5 1 としては、リソグラフィー用の合わせに使うためのマーク、線幅や膜厚など製造工程での検査に使うためのマーク、チップを特定するためのマーク、または製造工程での検査のときの座標の基準に使うためのマークなどが挙げられる。すなわち、マーク 5 1 とは、チップの動作に関係しない、マークとして認識可能なすべての「しるし」をいう。

### [0060]

チップに配置するマーク51をレイアウトデータ(A)と別のデータとして持ち、チップの設計データ(A)は反転させ、合わせマークのデータ(B)はそのままにして重ね合わせて反転マスクデータ(D)とすることで、次のような効果を得ることができる。すなわち、製造工程上でリソグラフィーの合わせや、製造工程での検査に伴う問題が起こるのを防止できる。裏面側のマークについては、チップの設計データ(A)とともに反転させるので、当該設計データ(A)と同一の層に置いてよい。また、表面工程では、左右対称なマークや、形状が決められていないマークについては設計データ(A)と同一の層にお

いてもよい。

### [0061]

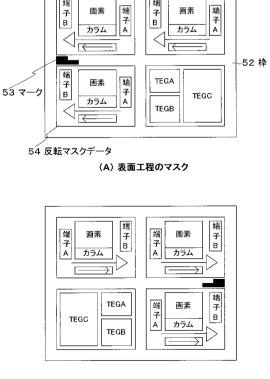

このようにして出来上がったチップデータ(即ち、反転マスクデータ)は、図6に示すように、枠52に収められてマスクになる。ここでは、1チップはTEG(Test Element Group)を入れる例としている。枠52にも、マスクの番号など、さまざまなマーク類53が存在するが、枠52の作り方については従来と同じにする。その詳細についてはここでは説明を省略する。

### [0062]

図6に示すように、従来と同じ枠、即ち反転操作をしていない枠52に、従来は行われていなかった反転工程を経た反転マスクデータ54を嵌め込む。この全体データから、表面工程の各リソグラフィーマスク(A)を形成する。裏面工程のマスク(B)については、枠とそこに収められたチップ全体をまるごと左右反転したデータからつくる。この枠も含めた丸ごと反転については、従来の裏面入射型CMOSイメージセンサでもやっていたことであり、本実施例1の特徴ではない。ここでは、従来の枠も含めた丸ごと反転と、本実施例1の表面工程でも影響あるチップのみの反転が異なることを明示するために記述している。

### [0063]

そして、製造工程においては、ウェーハ(半導体基板)に対するイオン注入について注意する。通常は、チップデータ(反転マスクデータ)に基づいて、イオン注入のウェーハに対する傾きを決定する(例えば、特開2000-223687号公報参照)。本実施例1では、マスクにする前にチップデータが反転されるので、イオン注入の向きを気にする工程では、これも合わせて左右反転することが好ましい。例えば、通常ウェーハの左から8度の角度でイオン注入する場合、ここでは右から8度の角度でイオン注入する。

#### [0064]

以上説明した実施例1によれば、開発や設計に当たっても、裏面入射による撮像画像の左右反転を意識しないでよいので、設計者、製造業者の両者にメリットが有る。特に、表面入射型チップとコンパチブルな裏面入射型チップを作る場合は、従来のような全体的な再設計の必要なく、表面入射型のレイアウトデータを流用して、端子位置、信号データとも同じものを作ることができる。

### [0065]

### (実施例2)

一部のIPについて、裏面入射用のライブラリを別に用意する。ここに、ライブラリとは、特定の機能を持ったプログラムを他のプログラムから利用できるように、設計の単位となる基本論理ゲートや論理回路ブロック、セルなどをまとめたデータベースのことをいう。

### [0066]

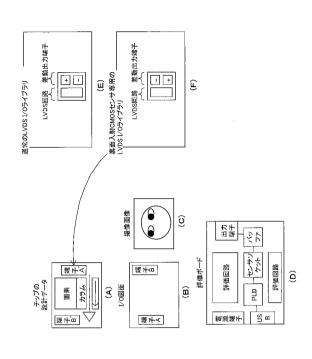

図 7 に示すように、差動入出力端子、即ち正相の信号の端子と逆相の信号の端子の位置を反転させた I / O セルを裏面入射用ライブラリ内に持つ。インターフェイス部分にこの I / O セルを用いてチップの設計データ(A)を設計する。図 7 (A)では、端子 A や端子 B と表示している。

# [0067]

図7において、(E)は通常のLVDSI/Oライブラリを、(F)は裏面入射型CMOSイメージセンサ10のLVDSI/Oライブラリをそれぞれ示している。LVDS回路は、先述したように、図1に示す出力回路部16において、差動の信号、即ち正相の信号と逆相の信号とを出力する出力段の回路部分として用いられる。

## [0068]

あとは、図14に示した従来技術2の場合のように、全体が逆になるように設計する。 端子図面であるI/O図面(B)は、チップの設計データ(A)に対して左右反転したも のになる。撮像画像(C)は正転である。マスクにするデータは、チップ全体を反転する ことなく、そのまま用いる。これにより、インターフェイス部分の不都合を解消する。 10

20

30

40

#### [0069]

表面入射型チップのものとコンパチブルな裏面入射型チップを作るときは、全体を再設計しないといけないとか、同じチップサイズで作れないかもしれないなどについては、図14に示した従来技術2の場合と同じである。そのため、製造者にとっては効率が落ちることになるものの、チップの内部がブラックボックスでよい使用者にとっては、使い勝手が変わらないことになる。

#### [0070]

裏面入射型 C M O S イメージセンサ 1 0 を表面入射型と無関係につくるときは、上記の効率の低下はない。但し、表面入射型とライブラリや各種図面の管理が異なることの手間や、撮像画像の左右反転を意識して設計しなければならない煩雑さやミス誘発の可能性は残る。

### [0071]

(実施例1,2による作用効果)

実施例1,2に係る設計によって裏面入射型CMOSイメージセンサ10を製造することで、裏面入射型であっても表面入射型と区別せずに扱うことができる。そのため、裏面入射型CMOSイメージセンサ10を搭載する評価ボード(E)や後段の信号処理ICに特別な仕様を要求したり、コストをかけたりしなくて済む。

### [0072]

また、裏面入射型CMOSイメージセンサ10を従来の表面入射型CMOSイメージセンサと同じ感覚で使用できるため、当該CMOSイメージセンサ10を搭載する電子機器にとっては、次のようなメリットがある。すなわち、表面入射型チップとコンパチブルな裏面入射型チップを作る場合は、従来のような全体的な再設計の必要なく、表面入射型のレイアウトデータを流用できるため、早期に商品を投入できるとともに、低コスト化を図ることができる。また、予期せぬ不具合の可能性を低減できる。

#### [0073]

ここでは、可視光の光量に応じた信号電荷を物理量として検知する単位画素が行列状に配置されてなるCMOSイメージセンサに適用した場合を例に挙げて説明したが、本発明はCMOSイメージセンサへの適用に限られるものではなく、裏面入射型の固体撮像装置全般に対して適用可能である。

### [0074]

なお、固体撮像装置はワンチップとして形成された形態であってもよいし、撮像部と、信号処理部または光学系とがまとめてパッケージングされた撮像機能を有するモジュール 状の形態であってもよい。

# [0075]

### [適用例]

本発明に係る裏面入射型固体撮像装置は、画像取込部(光電変換部)に固体撮像装置を用いる電子機器全般に搭載して用いることができる。電子機器としては、デジタルスチルカメラやビデオカメラ等の撮像装置や、携帯電話機などの撮像機能を有する携帯端末装置や、画像読取部に固体撮像装置を用いる複写機などが挙げられる。なお、電子機器に搭載される上記モジュール状の形態、即ちカメラモジュールを撮像装置とする場合もある。

# [0076]

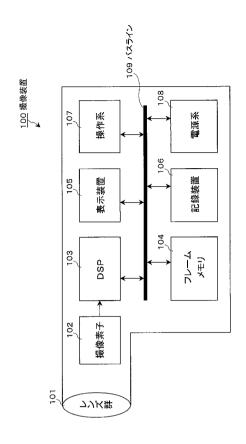

#### (撮像装置)

図8は、本発明に係る電子機器の一つである例えば撮像装置の構成の一例を示すブロック図である。図8に示すように、本発明に係る撮像装置100は、レンズ群101等を含む光学系、撮像素子(撮像デバイス)102、カメラ信号処理回路であるDSP回路103、フレームメモリ104、表示装置105、記録装置106、操作系107および電源系108等を有し、DSP回路103、フレームメモリ104、表示装置105、記録装置106、操作系107および電源系108がバスライン109を介して相互に接続された構成となっている。

## [0077]

30

10

20

レンズ群 1 0 1 は、被写体からの入射光(像光)を取り込んで撮像素子 1 0 2 の撮像面上に結像する。撮像素子 1 0 2 は、レンズ群 1 0 1 によって撮像面上に結像された入射光の光量を画素単位で電気信号に変換して画素信号として出力する。この撮像素子 1 0 2 として、先述した適用例に係る C M O S イメージセンサ 1 0 等の裏面入射型固体撮像装置を用いることができる。

[0078]

表示装置 1 0 5 は、液晶表示装置や有機 E L (electro luminescence)表示装置等のパネル型表示装置からなり、撮像素子 1 0 2 で撮像された動画または静止画を表示する。記録装置 1 0 6 は、撮像素子 1 0 2 で撮像された動画または静止画を、ビデオテープや D V D (Digital Versatile Disk)等の記録媒体に記録する。

[0079]

操作系107は、ユーザによる操作の下に、本撮像装置が持つ様々な機能について操作指令を発する。電源系108は、DSP回路103、フレームメモリ104、表示装置105、記録装置106および操作系107の動作電源となる各種の電源を、これら供給対象に対して適宜供給する。

[0800]

上述したように、ビデオカメラやデジタルスチルカメラ、さらには携帯電話機等のモバイル機器向けカメラモジュールなどの撮像装置において、その撮像素子52として先述した実施形態に係る裏面入射型CMOSイメージセンサ10を用いることで、次のような作用効果を得ることができる。すなわち、先述した実施形態に係る裏面入射型CMOSイメージセンサ10を従来の表面入射型CMOSイメージセンサと同じ感覚で使用できるために、早期に商品を投入できるとともに低コスト化を図ることができ、また予期せぬ不具合の可能性を低減できる。

【図面の簡単な説明】

[ 0 0 8 1 ]

【図1】本発明が適用される裏面入射型 C M O S イメージセンサのシステム構成の概略を示すシステム構成図である。

- 【図2】単位画素の回路構成の一例を示す回路図である。

- 【図3】裏面入射型の画素構造の一例を示す断面図である。

- 【 図 4 】 実 施 例 1 に 係 る 裏 面 入 射 型 C M O S イ メ ー ジ セ ン サ の 設 計 の 概 念 図 で あ る 。

- 【図5】反転マスクデータを作成する手順を示す概念図である。

- 【図 6 】マスク構成の例を示す図であり、(A)は表面工程のマスク、(B)は裏面工程のマスクをそれぞれ示している。

- 【図7】実施例2に係る裏面入射型СМОSイメージセンサの設計の概念図である。

- 【図8】本発明に係る撮像装置の構成の一例を示すブロック図である。

- 【図9】表面入射型(A)と裏面入射型(B)の撮像画像を示す図である。

- 【 図 1 0 】表面入射型および裏面入射型の C M O S イメージセンサのチップの設計データを示す図である。

- 【図11】CMOSイメージセンサの端子位置を規定したI/O図面(端子図面)を示す図であり、(A)が表面入射型の場合を、(B)が裏面入射型の場合をそれぞれ示している。

【図12】評価時あるいは製品でセンサを搭載するボードを示す図であり、(A)が表面入射型の場合を、(B)が裏面入射型の場合をそれぞれ示している。

- 【図13】従来技術1についての説明図である。

- 【図14】従来技術2についての説明図である。

【符号の説明】

[0082]

10…裏面入射型 C M O S イメージセンサ、11…半導体基板(チップ)、12…画素アレイ部、13…垂直駆動部、14…カラム処理部、15…水平駆動部、16…出力回路部、17…システム制御部、18…水平バス、19A…正相の出力端子、19B…逆相の

10

20

30

40

出力端子、20,21…入出力端子群、30…単位画素、31…フォトダイオード、32 …転送トランジスタ、33…リセットトランジスタ、34…増幅トランジスタ、35…選択トランジスタ、36…浮遊拡散容量(FD)、41…シリコン部(素子形成部)、45 …カラーフィルタ、46…オンチップレンズ、47…配線部

# 【図1】

【図3】

【図4】

【図5】

【図6】

端 子 B

画素

端 子 B

端 子 A

画素

(B) 裏面工程のマスク

【図7】

【図8】

【図9】

【図12】

【図11】

# 【図13】

【図14】