(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-158810

(P2009-158810A)

(43) 公開日 平成21年7月16日(2009.7.16)

(51) Int.Cl.

H01L 21/304 (2006.01)

B24B 37/00 (2006.01)

C09K 3/14 (2006.01)

F 1

H01L 21/304 622D

B24B 37/00 H

C09K 3/14 550Z

C09K 3/14 550D

テーマコード(参考)

3C058

審査請求 未請求 請求項の数 5 O L (全 16 頁)

(21) 出願番号

特願2007-337248 (P2007-337248)

(22) 出願日

平成19年12月27日 (2007.12.27)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100089118

弁理士 酒井 宏明

(72) 発明者 南幅 学

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 倉嶋 延行

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 重田 厚

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

(54) 【発明の名称】 化学的機械的研磨用スラリーおよび半導体装置の製造方法

## (57) 【要約】

【課題】半導体装置の製造工程におけるC M P工程において、良好な被研磨面を得ることができ、ひいては、半導体装置の製造におけるスループットの改善と歩留り向上を実現することのできるC M P用スラリーと、該スラリーを用いた半導体装置の製造方法を提供する。

【解決手段】本発明の一態様のC M P用スラリーは、重量平均分子量が100万以上100万以下のポリアクリル酸、ポリメタクリル酸、及びそれらの塩からなる群より選ばれる一種または二種以上からなる水溶性高分子と、-シクロデキストリンと、コロイダルシリカと、水を含有することを特徴とする。また、本発明の一態様の半導体装置の製造方法は、タッチアップ研磨工程に本発明の一態様のC M Pスラリーを用いることを特徴とする。

【選択図】 なし

## 【特許請求の範囲】

## 【請求項 1】

重量平均分子量が100万以上1000万以下のポリアクリル酸、ポリメタクリル酸、及びそれらの塩からなる群より選ばれる少なくとも一種の水溶性高分子と、-シクロデキストリンと、コロイダルシリカと、水とを含有することを特徴とする化学的機械的研磨用スラリー。

## 【請求項 2】

前記水溶性高分子の含有量が0.0001～0.5質量%であり、前記-シクロデキストリンの含有量が0.001～0.5重量%であることを特徴とする化学的機械的研磨用スラリー。

10

## 【請求項 3】

pH調整剤を含有し、アルカリ性であることを特徴とする請求項1または2に記載の化学的機械的研磨用スラリー。

## 【請求項 4】

半導体基板上に第1の絶縁膜を形成する第1の絶縁膜形成工程と、

前記第1の絶縁膜上に該第1の絶縁膜より誘電率が高い第2の絶縁膜を形成する第2の絶縁膜形成工程と、

前記第2の絶縁膜から第1の絶縁膜にかけて配線用の凹部を形成する凹部形成工程と、

前記凹部の内面と前記第2の絶縁膜の表面にバリアメタル膜を形成するバリアメタル膜形成工程と、

前記バリアメタル膜で覆われた凹部を埋め込むように銅または銅合金を前記バリアメタル膜上に堆積して配線材料堆積層を形成する配線材料堆積工程と、

前記配線材料堆積層を前記バリアメタル膜が露出するまで化学的機械的研磨により平坦に研磨して除去する第1の化学的機械的研磨工程と、

前記第1の化学的機械的研磨工程の後、前記第1の絶縁膜が露出するまでバリアメタル膜と第2の絶縁膜を化学的機械的研磨により平坦に研磨して除去する第2の化学的機械的研磨工程とを有し、

前記第2の化学的機械的研磨工程における研磨を、請求項1に記載の化学的機械的研磨用スラリーを用いて行うことを特徴とする半導体装置の製造方法。

## 【請求項 5】

前記第1の化学的機械的研磨工程と第2の化学的機械的研磨工程とを、同一研磨テーブル上で連続的に行うことの特徴とする請求項4に記載の半導体装置の製造方法。

30

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、化学的機械的研磨用スラリーおよび該スラリーを用いた半導体装置の製造方法に関する。

## 【背景技術】

## 【0002】

近年、半導体装置の高密度化に伴い、形成される配線の微細化が進んでいる。この配線の更なる微細化を達成することができる技術として、ダマシン法と呼ばれる技術が知られている。このダマシン法は、半導体基板上に設けた絶縁膜に配線用の凹部をR I E (R e a c t i v e I o n E t c h i n g)などにより形成し、この凹部に配線材料を埋め込んだ後、凹部以外の部分に堆積した余剰な配線材料を化学的機械的研磨 (C h e m i c a l M e c h a n i c a l P o l i s h i n g、以下、C M Pと略記する)により除去することによって、絶縁膜中にCuなどの配線を形成する方法である。

## 【0003】

配線材料にCuまたはCu合金を用いる場合、Cu原子の絶縁膜中のマイグレーションを避けるため、CuまたはCu合金と絶縁膜との界面に、通常、Ta、TaN、Ti、TiN、Ru等を材料とするバリアメタル膜を形成する。

40

50

## 【0004】

上述のような配線材料やバリアメタル膜のCMPに用いることのできるCMP用スラリーとしては、研磨砥粒、金属酸化剤、酸化金属溶解剤、防食剤、界面活性剤、水溶性高分子などを成分とするものが種々提案されている。例えば、特許文献1には、研磨砥粒、酸化剤、有機酸、防食剤、界面活性剤、およびpH調整剤を含有し、pHが5～10であるCMP用研磨組成物が開示されている。また、特許文献2には、研磨砥粒0.1～10質量%、過硫酸アンモニウム0.01～10質量%、シュウ酸0.01～5質量%、ベンゾトリアゾール0.0001～5質量%、ドデシルベンゼンスルホン酸および/またはドデシルベンゼンスルホン酸の塩0.001～10質量%、ポリビニルピロリドン0.001～10質量%および水溶性塩基性化合物であるpH調整剤を含有し、pHが8～12の範囲にあるCMP用研磨組成物が開示されている。なお、これら従来のCMP用スラリーには、任意成分として、シクロデキストリンの使用も可能であることが開示されている。

10

## 【0005】

ところで最近は、前記絶縁膜に低誘電率の材料を用いることが進められているが、この低誘電率の絶縁膜（第1の絶縁膜）は、凹部を形成するためのRIE加工を直接作用させると、RIE加工用のマスク除去時などにダメージを被りやすい。そのため、第1の絶縁膜上に第2の絶縁膜（キャップ絶縁膜）としてSiO<sub>2</sub>膜などの比較的誘電率の高い絶縁膜を堆積し、この第2の絶縁膜から第1の絶縁膜にかけて凹部を形成する。

20

## 【0006】

前記第2の絶縁膜は誘電率が高いため、凹部に形成した配線を囲む層間絶縁膜として残すと、配線の電気的特性を損なうので、前述の余剰に堆積した配線材料のCMPによる除去に引き続いてCMP処理により完全に除去することが望まれる。

20

## 【0007】

この場合、前記CMPにより除去する積層膜は、配線材料の余剰堆積膜、キャップ絶縁膜として用いた第2の絶縁膜、そしてバリアメタル膜の3種類の膜である。CMPの最終段階では、凹部間の第1の絶縁膜の表面を露出させることになるため、研磨開始から研磨終了までの間でCMPの対象となる膜は、第1の絶縁膜を含め、4種類となる。CMPの初期段階では、CuまたはCu合金からなる配線材料の余剰堆積膜のみを研磨することになり、次の段階では、バリアメタル膜と第2の絶縁膜、そして第1の絶縁膜の表面を順次に研磨することになる。

30

## 【0008】

同一の研磨剤を用いた場合、CuまたはCu合金からなる膜と、SiO<sub>2</sub>からなる第2の絶縁膜と、Taなどの金属からなるバリアメタル膜と、SiOCなどの低誘電体材料からなる第1の絶縁膜のそれぞれの研磨速度は、大きく異なる。そのため、通常、CMPは、CuまたはCu合金からなる配線材料の余剰堆積膜を除去する第1の化学的機械的研磨工程（以下、第1のCMP工程と略記する）と、残りの第2の絶縁膜とバリアメタル膜を除去する第2の化学的機械的研磨工程（以下、第2のCMP工程と略記する）との2段階研磨により対処している。

30

## 【0009】

上記第2のCMP工程では、バリアメタル膜と第2の絶縁膜、そして第1の絶縁膜の表面を順次に研磨することになるので、研磨に用いる化学的機械的研磨用スラリー（以下、CMP用スラリーと略記する）としては、いずれの膜に対しても良好な研磨性を有することが求められる。特に、第2のCMP工程の最終段階では、第2の絶縁膜の露出表面と、凹部側壁に沿って形成されているバリアメタル膜の露出面と、凹部内の配線材料層の露出面とを同時に研磨して、半導体ウェハーの全面が平坦となるように仕上げる必要がある。

40

## 【0010】

【特許文献1】特開2006-66874号公報

【特許文献2】特開2007-13059号公報

## 【発明の開示】

## 【発明が解決しようとする課題】

50

## 【0011】

本発明は、上記従来の事情に鑑みてなされたもので、その課題は、半導体装置の製造工程におけるCMP工程において、より良好な被研磨面を得ることができ、それにより半導体装置の製造におけるスループットの改善を実現することのできるCMP用スラリーと、該スラリーを用いた半導体装置の製造方法を提供することにある。

## 【課題を解決するための手段】

## 【0012】

前記課題を解決するために、本発明の一態様によれば、重量平均分子量が100万以上1000万以下のポリアクリル酸、ポリメタクリル酸、及びそれらの塩からなる群より選ばれる少なくとも一種の水溶性高分子と、-シクロデキストリンと、コロイダルシリカと、水とを含有することを特徴とするCMP用スラリーが提供される。

10

## 【0013】

また、本発明の他の態様によれば、半導体基板上に第1の絶縁膜を形成する第1の絶縁膜形成工程と、前記第1の絶縁膜上に該第1の絶縁膜より誘電率が高い第2の絶縁膜を形成する第2の絶縁膜形成工程と、前記第2の絶縁膜から前記第1の絶縁膜にかけて配線用の凹部を形成する凹部形成工程と、前記凹部の内面と前記第2の絶縁膜の表面にバリアメタル膜を形成するバリアメタル膜形成工程と、前記バリアメタル膜で覆われた凹部を埋め込むように銅または銅合金を前記バリアメタル膜上に堆積して配線材料堆積層を形成する配線材料堆積工程と、前記配線材料堆積層を前記バリアメタル膜が露出するまで化学的機械的研磨により平坦に研磨して除去する第1の化学的機械的研磨工程と、前記第1の化学的機械的研磨工程の後、前記第1の絶縁膜が露出するまでバリアメタル膜と第2の絶縁膜を化学的機械的研磨により平坦に研磨して除去する第2の化学的機械的研磨工程とを有し、前記第2の化学的機械的研磨工程における研磨を、前記本発明の一態様の化学的機械的研磨用スラリーを用いて行うことを特徴とする半導体装置の製造方法が提供される。

20

## 【発明の効果】

## 【0014】

本発明の一態様のCMP用スラリーは、半導体装置の製造工程におけるCMP工程において、良好な被研磨面を得ることができ、それにより、半導体装置の製造におけるスループットの改善と歩留り向上を実現することができる。また、本発明の一態様の半導体装置の製造方法によれば、信頼性に優れた半導体装置を効率よく製造することができる。

30

## 【発明を実施するための最良の形態】

## 【0015】

低誘電率の層間絶縁膜中にCMPにより配線を形成する際に、CMPによる被研磨面を良好とするための障害となる主な問題点は、(i)第1のCMP工程において用いられるCMP用スラリー中の有機酸が、低誘電率の層間絶縁膜(第1の絶縁膜)に通常堆積されるキャップ絶縁膜(第2の絶縁膜)であるSiO<sub>2</sub>膜に吸着することにより生じると推定されるSiO<sub>2</sub>膜の研磨摩擦の低下と、(ii)疎水性の低誘電体材料からなる第1の絶縁膜の露出面面積が広い領域の端部に生じやすい「ファング」と呼称される過剰研磨部位の発生と、(iii)配線層の表面が局部的に削り取られた状態(「スクラッチ」と呼称される)の発生である。これら問題点は、特に、第1のCMP工程と第2のCMP工程を同一の研磨テーブルを用いて連続して行う場合に顕著となるため、半導体装置の製造におけるスループットを向上するためのネックとなってしまう。

40

上記問題点は、以下に詳述する本発明の一態様により解決することができる。

## 【0016】

本発明の一態様のCMP用スラリーは、半導体装置の製造方法において、半導体基板上の絶縁膜中にダマシン法により配線層を形成する際に実施される第1および第2のCMP工程の内、特に第2のCMP工程に用いて好適な研磨組成物である。

## 【0017】

前述のように、本発明の一態様のCMP用スラリーは、前記第2のCMP工程に用いて好適な研磨組成物(以下、便宜的に第2のCMP用スラリーと記す)であり、前記第1の

50

CMP工程に用いられるCMP用スラリー（以下、便宜的に第1のCMP用スラリーと記す）を構成する研磨砥粒等の基本的要素材料を同様に有するとともに、更に必須成分として、重量平均分子量が100万以上1000万以下のポリアクリル酸、ポリメタクリル酸、及びそれらの塩からなる群から選ばれる一種または二種以上からなる水溶性高分子と、-シクロデキストリンとを含有させた組成を有する。

従って、以下に、まず、第1のCMP用スラリーの組成の一例の詳細を説明し、続いて、第2のCMP用スラリー（本発明の一態様のCMP用スラリー）の必須成分の詳細について説明する。

#### 【0018】

本発明の一態様の半導体装置の製造方法において、第1のCMP工程に用いられる第1のCMP用スラリーは、特に限定されるものではなく、従来、第1のCMP工程に用いられていたCMP用スラリーを使用することができる。例えば、以下の組成からなる研磨組成物を第1のCMP用スラリーとして用いる。

#### 【0019】

##### [第1のCMP用スラリー]

第1のCMP用スラリーは、CuまたはCu合金からなる配線材料堆積膜の不要部分を除去する第1のCMP工程で使用するに適したもので、水と、Cu水不溶性錯体形成剤と、Cu水可溶性錯体形成剤と、酸化剤、界面活性剤、コロイダルシリカ、およびpH調整剤が含まれる。

#### 【0020】

##### (Cu水不溶性錯体形成剤)

Cuなどの金属と水に不溶性または難溶性の錯体を形成する錯体形成剤としては、例えば、少なくとも1個のN原子を含む複素六員環、複素五員環からなるヘテロ環化合物が挙げられる。より具体的には、キナルジン酸、キノリン酸、ベンゾトリアゾール、ベンゾイミダゾール、7-ヒドリキシ-5-メチル-1,3,4-トリアザインドリジン、ニコチニ酸、およびピコリン酸などを挙げることができる。このCu水不溶性錯体形成剤の含有量は、CMP用スラリーの総量の0.0005質量%以上2.0質量%以下が好ましい。このCu水不溶性錯体形成剤の含有量が0.0005質量%以上2.0質量%以下であれば、研磨される配線層表面のディッシングが抑えられるとともに、良好なCu研磨速度を得ることができる。このCu水不溶性錯体形成剤の含有量は、より好ましくは、第1のCMP用スラリーの総量の0.0075質量%以上1.5質量%以下である。

#### 【0021】

##### (Cu水可溶性錯体形成剤)

Cuなどの金属と水に可溶性の錯体を形成する錯体形成剤は、研磨加速剤の役割を果たし、例えば、例えば、ギ酸、コハク酸、乳酸、酢酸、酒石酸、フマル酸、グリコール酸、フタル酸、マレイン酸、シュウ酸、クエン酸、リンゴ酸、マロン酸、およびグルタル酸などが挙げられる。さらに、アンモニア、エチレンジアミン、およびTMAH（テトラメチルアンモニウムハイドロオキサイド）などの塩基性塩を用いてもよい。また、中性アミノ酸のグリシン、アラニンなどを添加してもよい。このCu水可溶性錯体形成剤の含有量は、第1のCMP用スラリーの総量の0.0005質量%以上2.0質量%以下が好ましい。この含有量が0.0005質量%以上2.0質量%以下であれば、大きな速度でCuを研磨することができるとともに、研磨による配線層表面のディッシングやコロージョンを抑制することができる。このCu水可溶性錯体形成剤のより好ましい含有量は、CuあるいはCu合金における組成の違いにより異なるが、第1のCMP用スラリーの総量の0.0075質量%以上1.5質量%以下である。

#### 【0022】

##### (酸化剤)

酸化剤としては、例えば、過硫酸塩、過酸化水素、等が挙げられる。過硫酸塩としては、過硫酸アンモニウム、過硫酸カリウムなどが挙げられる。好ましい濃度は、第1のCMP用スラリーの総量の0.001~2質量%であり、より好ましくは0.01~2質量%

10

20

30

40

50

であり、さらに好ましくは0.05～1.5質量%である。酸化剤をこの範囲の配合量とすることにより、Cu又はCu合金膜とバリアメタル膜に対する研磨速度を適度な範囲に設定することができる。

【0023】

(界面活性剤)

非イオン性界面活性剤としては、例えば、ポリビニルピロリドン(PVP)、アセチレングリコール、それらのエチレンオキサイド付加物、アセチレンアルコール、シリコーン系界面活性剤、ポリビニルアルコール、ポリビニルメチルエーテル、ヒドロキシエチルセルロースなどを用いてもよい。さらに、アニオン界面活性剤またはカチオン界面活性剤を含んでもよい。アニオン界面活性剤としては、ドデシルベンゼンスルホン酸塩、高分子のポリアクリル酸塩などが挙げられ、カチオン界面活性剤としては、例えば、脂肪族アミン塩および脂肪族アンモニウム塩などが挙げられる。上述したような界面活性剤は、単独でも2種以上を組み合わせて用いてもよい。この界面活性剤の含有量は、第1のCMP用スラリーの総量の0.001質量%以上0.5質量%以下が好ましい。この範囲内に設定することにより配線層表面の研磨によるディッシングを十分に抑制することができる。この界面活性剤のより好ましい含有量は、第1のCMP用スラリーの総量の0.05質量%以上0.3質量%以下である。

10

【0024】

(コロイダルシリカ)

コロイダルシリカは、例えば $\text{Si}(\text{OC}_2\text{H}_5)_4$ 、 $\text{Si}(\text{sec}-\text{OC}_4\text{H}_9)_4$ 、 $\text{Si}(\text{OC}_3)_4$ 、および $\text{Si}(\text{OC}_4\text{H}_9)_4$ のようなシリコンアルコキシド化合物をゾルゲル法により加水分解することにより得ることができる。コロイダルシリカの粒子径は、好ましくは5～500nmであり、より好ましくは10～100nmであり、更に好ましくは20～50nmである。この範囲の平均分散粒径のコロイダルシリカを使用することにより、適度な研磨速度を達成することができる。

20

【0025】

このコロイダルシリカの好ましい含有量は、第1のCMP用スラリーの総量中1～10質量%であり、より好ましくは2～5質量%である。コロイダルシリカが10質量%より多い場合、研磨速度を上げることができるが、コストの面で好ましくない。一方、1質量%より少ない場合、研磨速度が小さいため、半導体生産のスループットが小さくなるので好ましくない。

30

【0026】

(第1のCMP用スラリーのpH)

第1のCMP用スラリーのpHは、好ましくは7を超える13以下であり、8～11であることがより好ましい。この範囲のpHとすることにより、適度な研磨速度を達成することができる。pH調整剤としては、例えば、有機塩基、無機塩基、無機酸が挙げられる。有機塩基としては、例えば、テトラメチルアンモニウムヒドロキシド(TMAH)、トリエチルアミン等が挙げられる。無機塩基としては、例えば、アンモニア、水酸化カリウム、水酸化ナトリウム等が挙げられる。無機酸としては、例えば、硝酸、硫酸等が挙げられる。

40

【0027】

[第2のCMP用スラリー(本発明の一態様のCMP用スラリー)]

本発明の一態様の半導体装置の製造方法において、バリアメタル膜、CuまたはCu合金膜、第2の絶縁膜を除去する第2のCMP工程で使用する第2のCMP用スラリーは、先に述べたように、前記第1のCMP用スラリーに用いられている研磨砥粒等の基本的要素材料は共通して含有し、それ以外の必須組成として、重量平均分子量が100万以上1000万以下の特定の水溶性高分子と、-シクロデキストリンを含む。なお、この第2のCMP用スラリーにおいて、前記第1のCMP用スラリーの成分を同様に含有する場合のそれらの含有量は、第1のCMP用スラリーでの含有量とほぼ同様であって良い。また、好適なpH値の範囲も同様であり、第1のCMP用スラリーの場合と同様のpH調整

50

剤を配合してアルカリ性に設定されることが好ましい。

【0028】

(水溶性高分子)

水溶性高分子としては、例えば、ポリアクリル酸、ポリアクリル酸塩、ポリメタクリル酸、ポリメタクリル酸塩、アクリル酸-メタクリル酸ポリマー、およびアクリル酸-メタクリル酸ポリマーの塩などが挙げられる。本発明の一態様のCMP用スラリーに用いられる水溶性高分子は、前記の群から選ばれる一種を単独で用いても良いし、二種以上を混合して用いても良く、その重量平均分子量が100万以上1000万以下であることが重要である。100万以上とすることにより、被研磨面に生じやすいファングの抑制効果が発揮され、スクラッチ数の低減効果も得ることができ、配線層表面のティッキングも抑制することができる。また、重量平均分子量を1000万以下とすることにより、第2のCMP用スラリー中のコロイダルシリカの凝集が防止され、それに伴って、被研磨面のスクラッチ数を減少させることができる。また、重量平均分子量を100万以上1000万以下とすることにより、第2のCMP用スラリーの粘度を、コロイダルシリカの凝集を防止しつつ、コロイダルシリカを均一に保持可能な範囲に調整可能であり、かつ、研磨テーブルに滴下可能な範囲に抑えることができる、など取り扱いを良好とすることができます。また、上記水溶性高分子は、いわば、大きなアニオン群であるため、pH配合剤が配合された場合は、その周囲にpH調整剤由来のカチオンを引きつけ、このカチオン群がさらにコロイダルシリカを引きつけることにより、研磨砥粒であるコロイダルシリカの均一保持が可能になり、良好な研磨特性が得られるものと考えられる。

10

20

30

40

50

【0029】

この水溶性高分子の好ましい濃度は、第2のCMP用スラリーの総量中0.0001~0.5質量%であり、より好ましくは0.01~0.1質量%である。0.5質量%以下とすることにより、コストを抑えることができると共に、取り扱い上良好な粘度を実現することができる。一方、0.0001質量%以上とすることにより、第2の絶縁膜(SiO<sub>2</sub>膜)の研磨速度の低下を防止でき、被研磨面に生じやすいファングの抑制効果、さらに被研磨面のスクラッチ数の低減効果も十分に得ることができる。

【0030】

(-シクロデキストリン)

シクロデキストリンは、-、-、-型の3種類のうち-シクロデキストリンが用いられる。この-シクロデキストリンは、SiOC膜などの低誘電体材料への作用が特に強く、疎水性の低誘電体材料膜に直接または第2のCMP用スラリー中の他の成分との相互作用を通じて接触し、膜表面の疎水性の度合いを低減して親水性方向にシフトさせ、ひいてはファングの抑制効果を発揮するものと考えられる。また、この-シクロデキストリンはコロイダルシリカに接触して、コロイダルシリカを電気的に中性化し、コロイダルシリカの凝集防止に寄与するものと推定される。

【0031】

この-シクロデキストリンの好ましい濃度は、第2のCMP用スラリーの総量中0.001~0.5質量%であり、より好ましくは0.01~0.1質量%である。0.001質量%以上とすることにより、第2の絶縁膜の特に良好な研磨速度が実現され、それに伴って、半導体装置の製造におけるスループットを向上させることができる。また、0.5質量%を超えて研磨速度の向上効果は大きくないので、コストの面から、上限値として0.5質量%を設定することが好ましい。

【0032】

(洗浄液)

半導体装置の製造方法においては、前記第2のCMP工程の後に、連続して洗浄工程を設けることが好ましい。その洗浄工程に用いる洗浄液としては、クエン酸、シュウ酸ベースの酸性液や、TMAHのようなアルカリ性の溶液などCu錯体、Cu酸化物を溶解するものを用いることができる。

【0033】

## (半導体装置の製造方法)

本発明の一態様の半導体装置の製造方法は、先に述べたように、半導体基板上に第1の絶縁膜を形成する第1の絶縁膜形成工程と、前記第1の絶縁膜上に該第1の絶縁膜より誘電率が高い第2の絶縁膜を形成する第2の絶縁膜形成工程と、前記第2の絶縁膜から前記第1の絶縁膜にかけて配線用の凹部を形成する凹部形成工程と、前記凹部の内面と前記第2の絶縁膜の表面にバリアメタル膜を形成するバリアメタル膜形成工程と、前記バリアメタル膜で覆われた凹部を埋め込むように銅または銅合金を前記バリアメタル膜上に堆積して配線材料堆積層を形成する配線材料堆積工程と、前記配線材料堆積層を前記バリアメタル膜が露出するまで化学的機械的研磨により平坦に研磨して除去する第1の化学的機械的研磨工程と、前記第1の化学的機械的研磨工程の後、前記第1の絶縁膜が露出するまでバリアメタル膜と第2の絶縁膜を化学的機械的研磨により平坦に研磨して除去する第2の化学的機械的研磨工程とを有し、前記第2の化学的機械的研磨工程における研磨を、前記本発明の一態様のCMP用スラリーを用いて行うことを特徴とする。

以下に図面を用いて、上記第1のCMP用スラリーおよび第2のCMP用スラリーを用いて行われる半導体装置の製造方法を説明する。

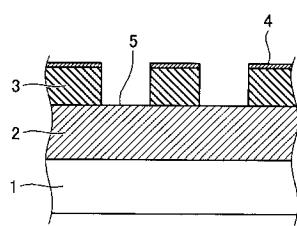

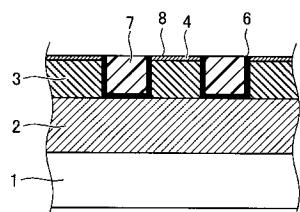

## 【0034】

まず、図1に示すように、不図示の半導体素子が形成された半導体基板1上にSiO<sub>2</sub>からなる絶縁層2を形成する。この絶縁層2の上に、CVD法、回転塗布法等により第1の絶縁膜3を形成する。この第1の絶縁膜3を構成する材料は、例えば、SOG(spin on glass)法やCVD法等で形成されたSiOCなどの低誘電体材料が主に用いられる。第1の絶縁膜3の上にキャップ絶縁膜としてSiO<sub>2</sub>などからなる第2の絶縁膜4を形成し、この第2の絶縁膜4から第1の絶縁膜3にかけて凹部(配線溝)5を形成する。

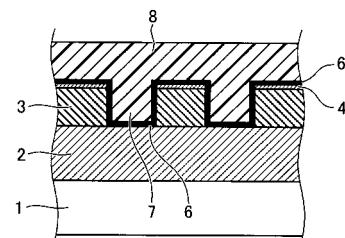

## 【0035】

次に、前述のように凹部5を形成した第1の絶縁膜3の表面に、図2に示すように、バリアメタルを堆積させることによって、凹部5の内面にバリアメタル膜6を形成する。この時バリアメタル膜6は前記第2の絶縁膜4の上にも形成される。このバリアメタル膜6は、凹部5内に埋め込むことになる銅または銅合金が第1の絶縁膜3中へ拡散することを防止するためのバリア膜である。

## 【0036】

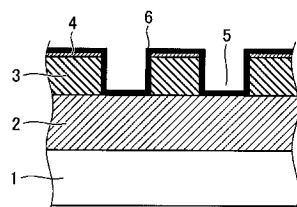

その後、図3に示すように、凹部5内に、下層配線層7を形成するための銅または銅合金を、電解メッキなどを用いて堆積する。この場合の銅または銅合金の堆積は、凹部5内にのみ行うことは製造上困難であるため、堆積の結果、図3に示すように、凹部5およびバリアメタル膜6の全面を覆うように銅または銅合金からなる配線材料堆積層8が形成される。

## 【0037】

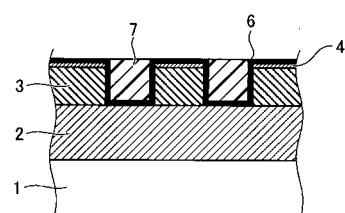

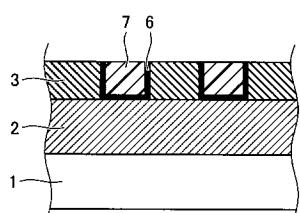

上記配線材料堆積層8およびバリアメタル膜6の内、凹部5内以外の部分は、余剰であるので、その余剰部分を除去し、積層膜の表面を平坦にする必要がある。そのためにCMPを施す。このCMPは、第1のCMP工程と、第2のCMP工程とに分けて行われる。第1のCMP工程は、図3～図4に示すように、配線材料堆積層8のほとんどを除去する粗研磨工程である。また、第2のCMP工程は、図4～図6に示すように、残りの配線材料堆積層8とバリアメタル膜6と第2の絶縁膜4とを除去し、第1の絶縁膜3を露出させるとともに、ウェハーの全面を平坦にする仕上げ研磨工程である。この第2のCMP工程は、タッチアップ研磨とも呼称されている。

## 【0038】

前記第1のCMP工程では、先に述べた組成の第1のCMP用スラリーを用い、その後の第2のCMP工程では、先に述べた組成の第2のCMP用スラリーを用いる。

## 【0039】

前記第2のCMP工程に、本発明の一態様のCMP用スラリー(第2のCMP用スラリー)を用いることにより、図4から図6への研磨工程(第2のCMP工程)において、SiO<sub>2</sub>からなる第2の絶縁膜4の研磨も良好に行うことができる。また、本発明の一態様

のC M P用スラリーを用いることにより、第1の絶縁膜3が露出する時点で発生しやすいファンギングを抑制することができ、各配線層7に生じやすいスクラッチ数も低減することができる。

【実施例】

【0040】

以下、本発明の実施例を説明する。以下に示す実施例は、本発明を説明するための例示であり、何ら本発明を限定するものではない。

【0041】

(実施例1～5)

第1のC M P工程に用いる第1のC M P用スラリーを、下記表1に示す成分及び組成割合に従って、調製し、この第1のC M P用スラリーを、実施例1～5における第1のC M P用スラリーとして共通して用いた。

【0042】

【表1】

(表1)第1のC M P用スラリーの組成

| 組成分         | 含有量(質量%)          |          |

|-------------|-------------------|----------|

| 水           | 残部                |          |

| Cu水不溶性錯体形成剤 | キナルジン酸            | 0.3      |

|             | キノリン酸             | 0.3      |

| Cu水可溶性錯体形成剤 | アラニン              | 0.3      |

|             | シュウ酸              | 0.1      |

| 酸化剤         | 過硫酸アンモニウム         | 2.5      |

| 界面活性剤       | ドデシルベンゼンスルホン酸カリウム | 0.03     |

|             | ポリビニルピロリドン        | 0.03     |

| 研磨砥粒        | コロイダルシリカ          | 0.75     |

| pH調整剤       | KOH               | (pH9に調整) |

【0043】

また、各実施例1～5の第2のC M P工程に用いる第2のC M P用スラリーを、下記表2に示す成分及び組成割合に従って、調製した。

【0044】

(比較例1～4)

第1のC M P工程に用いる第1のC M P用スラリーは、実施例1～5と同様に、上記表1に示す成分及び組成割合に従って調製したものを共通して用いた。

【0045】

各比較例1～4の第2のC M P工程に用いる第2のC M P用スラリーを、下記表3に示す成分及び組成割合に従って、調製した。

【0046】

前記実施例1～5、および比較例1～4のそれぞれのC M P用スラリーを用いて、それぞれ以下のようにして、半導体装置の製造を行った。

【0047】

以下の製造プロセスは、図1～6を参照しつつ説明する。半導体素子(図示せず)が形成された半導体基板1上に、SiO<sub>2</sub>からなる絶縁層2を設けた。この絶縁層2の上に、第1の絶縁膜3として低誘電率絶縁膜と、キャップ絶縁膜として第2の絶縁膜4を順次形成して、積層絶縁膜を形成した。前記第1の絶縁膜3として、比誘電率が2.8未満のS

10

20

30

40

50

iO<sub>C</sub>膜を180nm厚に形成した。

【0048】

前記第2の絶縁膜4として30nm厚のSiO<sub>2</sub>膜を形成した。この第2の絶縁膜4から第1の絶縁膜3にかけて配線用の凹部(配線溝)5を形成した。その後、全面に常法によりバリアメタル膜6としてのTa膜を5nm厚に堆積させた。その後、バリアメタル膜6を覆うようにしてCu膜8を550nm堆積させた。

【0049】

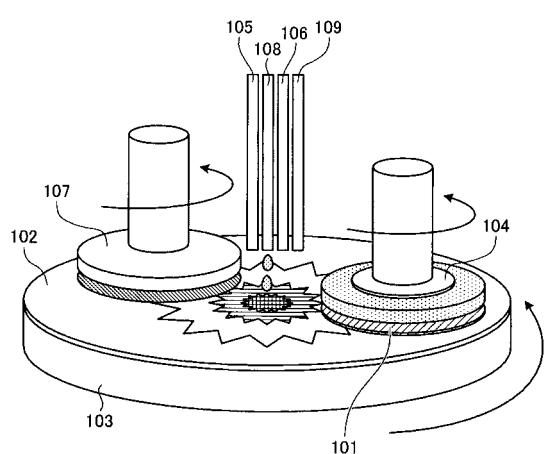

次に、図7に示すように、上述のようにしてCu膜を堆積させた直径300mmの半導体基板101を用意し、この半導体基板101を同一研磨テーブル上で、第1のCMP工程と第2のCMP工程とを連続して研磨処理した。すなわち、半導体基板101のCu膜を研磨布102に密着させた状態でCu膜の余剰堆積部分を除去する第1の工程と、バリアメタル膜、Cu膜、第2の絶縁膜を除去する第2の工程と、さらに研磨後の半導体基板101を洗浄する第3の工程を順次行った。その際、研磨布102としてニッタハース社製の「IC1000(商品名)」を貼付したターンテーブル103を80rpmで回転させつつ、各サンプルの半導体基板101を保持したトップリング104を200g/cm<sup>2</sup>の研磨荷重で当接させた。

【0050】

前記トップリング104の回転数は81rpmとし、研磨布102上には、第1の研磨液供給ノズル105から300cc/minの流量で、Cu膜の余剰堆積部分を除去する前記第1のCMP用スラリーを供給し、余剰のCu膜がなくなるまで研磨を行なった。その後、研磨液供給ノズル105の供給をストップし、連続的に各サンプルの半導体基板101を研磨布102に当接させたまま純水供給ノズル106から300cc/minの流量で純水を供給し、10秒間摺動させた。そのままの状態でダイヤモンドドレッサー107で研磨布102のコンディショニングを行い、純水供給ノズル106からの供給をストップした。

【0051】

続いて、第2の研磨液供給ノズル108から300cc/minの流量で、前記各例の第2のCMP用スラリーを供給し、バリアメタル膜6下の第2の絶縁膜4がなくなるまで研磨を行なった。その後、第2の研磨液供給ノズル108からの第2のCMP用スラリーの供給をストップし、連続的に半導体基板101を研磨布102と摺動させたまま純水供給ノズル106から300cc/minの流量で純水を供給した。そして、そのままの状態でダイヤモンドドレッサー107で研磨布102のコンディショニングを行なった。続いて、純水供給ノズル106からの供給をストップし、第3の研磨液供給ノズル109から300cc/minの流量で、洗浄工程用洗浄液としてTMABベースのアルカリ洗浄液を供給しつつ、トップリング104に保持した半導体基板101を200g/cm<sup>2</sup>の研磨荷重で30秒間研磨パッド102と摺動させた。その後、各サンプルの半導体基板101を不図示の洗浄ユニットを通過させ、IPA(イソプロピルアルコール)による乾燥を行なった。

【0052】

また、上記プロセスによる半導体装置の製造に加えて、上記半導体装置の製造方法において、第1のCMP工程と第2のCMP工程とを、別々の研磨テーブルを用いて行ったこと以外、同様にして、実施例1~5および比較例1~4の各CMP用スラリーを用いて、半導体装置を製造した。

以下、上記第1のCMP工程と第2のCMP工程を同一の研磨テーブルを用いて連続して行った場合を連続研磨処理と記し、上記第1のCMP工程と第2のCMP工程とを別々の研磨テーブルを用いて行った場合を不連続研磨処理と記す。

【0053】

(CMP用スラリーの評価)

各例のCMP用スラリーの研磨特性の評価は、配線幅0.06μm、配線間隔0.06μm(配線被覆率50%)の配線パターンを形成した各基板サンプルについて行った。フ

10

20

30

40

50

アングの大きさ(幅寸法( nm ))は、配線パターンに隣接したフィールド領域における低誘電率絶縁膜(第1の絶縁膜)の端部をAFM(Atomic Force Microscope:原子間力顕微鏡)で評価した。発生スクラッチ数は、300mm径の半導体基板の研磨面を全面に亘って日立ハイテクノロジー社製の欠陥評価装置(商品名「IS2700」)により評価した。また、SiO<sub>2</sub>膜(第2の絶縁膜)の研磨速度は、別途、半導体基板上の全面にSiO<sub>2</sub>膜を形成し、このSiO<sub>2</sub>膜に対して研磨処理を行うことにより、測定した。SiO<sub>2</sub>膜の研磨速度については、不連続研磨処理と、連続研磨処理でのそれれにおいて、測定した。それらの測定結果を、表2および表3に併記した。

【0054】

【表2】

10

(表2)第2のCMP用スラリー(実施例)

| 実施例                                  |                 | 1    | 2    | 3    | 4    | 5    |

|--------------------------------------|-----------------|------|------|------|------|------|

| (質量%)                                | 水               | 残部   | 残部   | 残部   | 残部   | 残部   |

|                                      | キナルジン酸          | —    | —    | —    | —    | 0.05 |

|                                      | マレイン酸           | 0.8  | 0.8  | 0.8  | 0.8  | 0.8  |

|                                      | 過酸化水素(酸化剤)      | 0.2  | 0.2  | 0.2  | 0.2  | 0.2  |

|                                      | コロイダルシリカ        | 4    | 4    | 4    | 4    | 4    |

|                                      | ポリアクリル酸 mw:100万 | 0.01 | 0.1  | —    | —    | 0.1  |

|                                      | mw:1000万        | —    | —    | 0.1  | 0.1  | —    |

| $\beta$ -シクロデキストリン                   |                 | 0.1  | 0.1  | 0.1  | 0.01 | 0.1  |

| pH(pH調整剤:KOH)                        |                 | 10   | 10   | 10   | 10   | 10   |

| アング(nm)*                             |                 | 15   | 12   | 10   | 16   | 18   |

| スクラッチ数(個)*                           |                 | 12   | 10   | 8    | 25   | 8    |

| SiO <sub>2</sub> 研磨速度(不連続研磨処理)nm/min |                 | 58.2 | 60.6 | 68.2 | 52.5 | 50.7 |

| SiO <sub>2</sub> 研磨速度(連続研磨処理)nm/min  |                 | 54.2 | 57.1 | 63   | 47.3 | 46.1 |

\*連続研磨処理時の測定値

20

30

【0055】

【表3】

(表3) 第2のCMP用スラリー(比較例)

| 比較例                                  |                | 1    | 2    | 3         | 4   |

|--------------------------------------|----------------|------|------|-----------|-----|

| (質量%)                                | 水              | 残部   | 残部   | 残部        | 残部  |

|                                      | キナルジン酸         | —    | —    | —         | —   |

|                                      | マレイン酸          | 0.8  | 0.8  | 0.8       | 0.8 |

|                                      | 過酸化水素(酸化剤)     | 0.2  | 0.2  | 0.2       | 0.2 |

|                                      | コロイダルシリカ       | 4    | 4    | 4         | 4   |

|                                      | ポリアクリル酸 mw:10万 | —    | —    | —         | 0.1 |

|                                      | mw:1000万       | —    | —    | 0.1       | —   |

|                                      | β-シクロデキストリン    | —    | 0.1  | セルロース 0.1 | 0.1 |

|                                      | pH(pH調整剤:KOH)  | 10   | 10   | 10        | 10  |

|                                      | ファング(nm)*      | 53   | 18   | 35        | 50  |

| スクラッチ数(個)*                           |                | 255  | 35   | 40        | 102 |

| SiO <sub>2</sub> 研磨速度(不連続研磨処理)nm/min |                | 29.9 | 32   | 25        | 38  |

| SiO <sub>2</sub> 研磨速度(連続研磨処理)nm/min  |                | 24   | 29.1 | 21.25     | 35  |

\*連続研磨処理時の測定値

## 【0056】

上記表2に見るように、実施例1のCMP用スラリーの組成上の特徴は、重量平均分子量(mw)が100万のポリアクリル酸0.01質量%と、-シクロデキストリン0.1質量%とを同時に含有している点にある。この実施例1に対して、実施例2のCMP用スラリーでは、重量平均分子量(mw)が100万のポリアクリル酸の含有量が0.1質量%に増加している点が異なっている。このポリアクリル酸の含有量の増加により、ファング抑制効果、スクラッチ数の低減効果、およびSiO<sub>2</sub>研磨速度の向上効果のそれぞれにおいて、向上が認められる。

上記実施例2に対して、実施例3では、ポリアクリル酸の含有量は0.1質量%と同一であるが、その重量平均分子量(mw)が1000万とより高分子量のポリアクリル酸を使用している点が異なっている。この重量平均分子量の増加によって、ファング抑制効果、スクラッチ数の低減効果、およびSiO<sub>2</sub>研磨速度の向上効果の全てにおいて、向上が認められ、特にスクラッチ数の低減効果における改善が顕著となっている。

上記実施例3に対して、実施例4では、-シクロデキストリンの含有量が0.01質量%に低減している点が異なっている。この-シクロデキストリンの含有量の減少によって、ファング抑制効果、スクラッチ数の低減効果、およびSiO<sub>2</sub>研磨速度の向上効果の全てが実施例3の場合より低減しており、特にスクラッチ数の低減効果が弱まる傾向となっている。

実施例5は、上記実施例2に対して、キナルジン酸が0.05質量%添加されている点のみが異なっている。このキナルジン酸は有機酸であり、余剰のCu膜を研磨する第1のCMP用スラリーに配合されているCu水不溶性錯体形成剤である。この有機酸がSiO<sub>2</sub>膜に接触すると、SiO<sub>2</sub>に吸着し、SiO<sub>2</sub>膜の研磨摩擦が低下すると推定されている。実施例2の各評価結果と比べると、スクラッチ数の低減効果以外の評価結果が低下しており、特にSiO<sub>2</sub>膜の研磨速度が低下傾向となっていることが分かる。しかし、その低下傾向もごく小さな範囲にあることから、本発明の一態様のCMP用スラリーは、有機酸の影響を抑制する効果を有することが確認できる。

10

20

30

40

50

## 【0057】

一方、表3に見るように、比較例1では、ポリアクリル酸も - シクロデキストリンも含有されていない。その結果、実施例に比べて、全ての評価結果が大きく低下しており、特にスクラッチ数の増加が顕著となることが分かる。

比較例2では、ポリアクリル酸の含有がなく、 - シクロデキストリンが0.1質量%含有されている。この - シクロデキストリンの含有によって、ファング抑制効果およびスクラッチ数の低減効果が幾分か良好となる傾向にあるが、十分なものでなく、SiO<sub>2</sub>膜の研磨速度の向上効果はほとんど得られない。

比較例3では、重量平均分子量が1000万のポリアクリル酸が0.1質量%含有されているが、このポリアクリル酸の含有によって、 - シクロデキストリンのみの含有の場合と同様に、ファング抑制効果およびスクラッチ数の低減効果が幾分か良好となる傾向にあるが、十分なものでなく、SiO<sub>2</sub>膜の研磨速度の向上効果は得られない。

比較例4では、ポリアクリル酸および - シクロデキストリンが共に含有されているが、ポリアクリル酸の重量平均分子量が10万と大変小さい。その結果、全ての評価結果が低く、特にスクラッチ数が増加傾向となることが分かる。

## 【0058】

このように、実施例1～6のCMP用スラリーは、比較例1～4のCMP用スラリーに対し、ファングの抑制効果およびスクラッチ数の低減効果に優れ、かつSiO<sub>2</sub>膜（第2の絶縁膜）の研磨速度の向上効果、すなわちSiO<sub>2</sub>膜を確実に削りきり、SiOC膜（第1の絶縁膜）を露出させる能力が高まっている。これは重量平均分子量が100万以上1000万以下のポリアクリル酸（水溶性高分子）と、 - シクロデキストリンとを同時に用いることによって初めて得られる相乗的効果である。

## 【0059】

以上のように、本発明の一態様のCMP用スラリーは、半導体装置の製造工程におけるCMP工程において、被研磨面に生じやすいファングを抑制するとともに、スクラッチ数を低下させ、第2の絶縁膜（SiO<sub>2</sub>膜）の研磨速度の低下を防止することができ、それにより、半導体装置の製造におけるスループットの改善を実現することができる。また、本発明の一態様の半導体装置の製造方法によれば、信頼性に優れた半導体装置を効率よく製造することができる。したがって、本発明の一態様によれば、品質の優れた半導体装置を安価に製造することができ、半導体製造分野への寄与が大である。

## 【図面の簡単な説明】

## 【0060】

【図1】本発明の一態様の半導体装置の製造方法を説明するための図であって、半導体基板上に形成された絶縁層の上に積層された第1の絶縁膜と第2の絶縁膜に配線形成用の凹部が形成された状態を示す断面構成図である。

【図2】本発明の一態様の半導体装置の製造方法を説明するための図であって、凹部が形成された第1の絶縁膜の全面にバリアメタル膜が積層された状態を示す断面構成図である。

【図3】本発明の一態様の半導体装置の製造方法を説明するための図であって、凹部内に配線材料を埋め込むためにバリアメタル膜の全面に配線材料が堆積された状態を示す断面構成図である。

【図4】本発明の一態様の半導体装置の製造方法を説明するための図であって、第1のCMP工程により配線材料堆積層の余剰部分が研磨された状態を示す断面構成図である。

【図5】本発明の一態様の半導体装置の製造方法を説明するための図であって、第2のCMP工程が開始され、バリアメタル膜が平坦に研磨され、その下の第2の絶縁膜が露出した状態を示す断面構成図である。

【図6】本発明の一態様の半導体装置の製造方法を説明するための図であって、第2のCMP工程によりバリアメタル膜とその下の第2の絶縁膜が平坦に研磨され、第1の絶縁膜が露出した状態を示す断面構成図である。

【図7】本発明の一態様の半導体装置の製造方法に用いられる研磨装置の模式図である。

10

20

30

40

50

## 【符号の説明】

## 【0061】

- 1 半導体基板

- 2 絶縁層

- 3 第1の絶縁膜

- 4 第2の絶縁膜

- 5 凹部(配線溝)

- 6 バリアメタル膜

- 7 下層配線層

- 8 配線材料堆積層

10

101 Cu膜を堆積させた半導体基板

102 研磨布

103 ターンテーブル

104 トップリング

105 第1の研磨液供給ノズル

106 純水供給ノズル

107 ダイヤモンドドレッサー

108 第2の研磨液供給ノズル

109 第3の研磨液供給ノズル

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 穂山 佳邦

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 矢野 博之

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターム(参考) 3C058 AA07 CB01 CB03 CB10 DA02 DA12 DA17