(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7581367号**

**(P7581367)**

(45)発行日 令和6年11月12日(2024.11.12)

(24)登録日 令和6年11月1日(2024.11.1)

(51)国際特許分類

|         |                 |     |         |       |       |

|---------|-----------------|-----|---------|-------|-------|

| G 0 9 F | 9/30 (2006.01)  | F I | G 0 9 F | 9/30  | 3 3 8 |

| G 0 9 F | 9/33 (2006.01)  |     | G 0 9 F | 9/33  |       |

| H 0 1 L | 33/62 (2010.01) |     | H 0 1 L | 33/62 |       |

請求項の数 20 (全27頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2022-560993(P2022-560993) |

| (86)(22)出願日       | 令和3年4月6日(2021.4.6)          |

| (65)公表番号          | 特表2023-522583(P2023-522583) |

|                   | A)                          |

| (43)公表日           | 令和5年5月31日(2023.5.31)        |

| (86)国際出願番号        | PCT/US2021/025881           |

| (87)国際公開番号        | WO2021/207129               |

| (87)国際公開日         | 令和3年10月14日(2021.10.14)      |

| 審査請求日             | 令和5年2月7日(2023.2.7)          |

| (31)優先権主張番号       | 63/005,731                  |

| (32)優先日           | 令和2年4月6日(2020.4.6)          |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |

|          |                                                                                                                                                                                                                                                                                                                                      |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73)特許権者 | 502208397<br>グーグル エルエルシー<br>G o o g l e L L C<br>アメリカ合衆国 カリフォルニア州 9 4<br>0 4 3 マウンテン ピュー アンフィシ<br>アター パークウェイ 1 6 0 0<br>1 6 0 0 Amphitheatre P<br>arkway 9 4 0 4 3 Mounta<br>in View, C A U . S . A .<br>110001195<br>弁理士法人深見特許事務所<br>アーチャー,メリッサ<br>アメリカ合衆国、9 4 5 3 9 カリフォ<br>ルニア州、フリーモント、リライアンス<br>・ウェイ、1 2 5 0 、ラキシウム・イン<br>最終頁に続く |

| (74)代理人  |                                                                                                                                                                                                                                                                                                                                      |

| (72)発明者  |                                                                                                                                                                                                                                                                                                                                      |

(54)【発明の名称】 バックプレーン及びディスプレイアセンブリ

**(57)【特許請求の範囲】****【請求項1】**

ディスプレイを制御するためのバックプレーンであって、前記バックプレーンは、

前記バックプレーンの周囲上にある電気コネクタと、

前記バックプレーン上においてタイルアレイに形成された複数のタイルとを備え、前記複

数のタイルは、前記タイルアレイの周囲上にあるとともに前記電気コネクタに接続されて

いるタイルを含み、

前記タイル上においてダイアレイに配置されている複数のバックプレーンダイを備え、前

記複数のバックプレーンダイは、

前記ダイアレイの周囲上にある縁部を有する第1バックプレーンダイと、

前記第1バックプレーンダイに隣り合っており、かつ、前記ダイアレイの前記周囲上に縁

部を有しない第2バックプレーンダイとを含み、前記第2バックプレーンダイは、前記第

1バックプレーンダイを経由して前記電気コネクタに接続されている、バックプレーン。

**【請求項2】**

前記複数のバックプレーンダイのうちのバックプレーンダイは、前記ディスプレイの発光素子を駆動するための電気信号を生成する相補型金属酸化膜半導体(CMOS)集積回路を含む、請求項1に記載のバックプレーン。

**【請求項3】**

前記複数のバックプレーンダイのうちのバックプレーンダイは、前記ディスプレイの光反射素子への電気信号を生成するための相補型金属酸化膜半導体(CMOS)集積回路を含

む、請求項 1 に記載のバックプレーン。

**【請求項 4】**

前記複数のタイルが  $2 \times 2$  タイルアレイとして形成されている場合、各タイルは 2 つの縁部を有し、各縁部は前記タイルアレイの前記周囲に位置する電気接続を有する、請求項 1 から請求項 3 のいずれか一項に記載のバックプレーン。

**【請求項 5】**

前記複数のバックプレーンダイのうちの前記第 1 バックプレーンダイは、前記タイル上の前記ダイアレイにおけるの残りのバックプレーンダイへの外部電気接続を提供する、請求項 1 から請求項 4 のいずれか一項に記載のバックプレーン。

**【請求項 6】**

前記複数のバックプレーンダイは、長方形または正方形のダイアレイに配置され、前記複数のバックプレーンダイのうちのバックプレーンダイは、電気再分配層 (RDL) を介して、前記ディスプレイの LED アレイに電気的に接続された複数のピラーを含む、請求項 1 に記載のバックプレーン。

**【請求項 7】**

前記タイルは、前記複数のバックプレーンダイ間のギャップを充填し、かつ、前記複数のバックプレーンダイを共に保持するように構成されているオーバーモールドを含む、請求項 1 から請求項 6 のいずれか一項に記載のバックプレーン。

**【請求項 8】**

前記オーバーモールドは、シリカ材料、アルミナ材料、グラファイト材料、セラミック材料、またはポリマー材料の少なくとも一つから形成される、請求項 7 に記載のバックプレーン。

20

**【請求項 9】**

前記タイルは、前記複数のバックプレーンダイを確実に支持するための基板を含む、請求項 1 から請求項 8 のいずれか一項に記載のバックプレーン。

**【請求項 10】**

前記基板は、剛性であり、かつ、前記複数のバックプレーンダイのうちの少なくとも 1 つへの電気接続を提供する複数のシリコン貫通ビア (TSV) を含む、請求項 9 に記載のバックプレーン。

**【請求項 11】**

バックプレーンを備え、前記バックプレーンは、

前記バックプレーンの周囲上にある電気コネクタと、

タイルのアレイとを含み、前記タイルのアレイは、前記タイルのアレイの周囲上にあるとともに前記電気コネクタに接続されているタイルを含み、

前記タイル上においてダイアレイに配置されている、電気的に結合された複数のバックプレーンダイを含み、前記複数のバックプレーンダイは、

前記ダイアレイの周囲上にある縁部を有する第 1 バックプレーンダイと、

前記第 1 バックプレーンダイに隣り合っており、かつ、前記ダイアレイの前記周囲上に縁部を有しない第 2 バックプレーンダイとを含み、前記第 2 バックプレーンダイは、前記第 1 バックプレーンダイを経由して前記電気コネクタに接続されており、

前記タイルに電気的に結合された発光ダイオード (LED) アレイを備える、ディスプレイヤセンブリ。

**【請求項 12】**

前記タイルは、前記第 1 バックプレーンダイまたは前記第 2 バックプレーンダイの少なくとも 1 つのピラーを前記 LED アレイに電気的に接続するために、前記第 1 バックプレーンダイ及び前記第 2 バックプレーンダイの各々の少なくとも一部に配置された電気再分配層を含む、請求項 11 に記載のディスプレイヤセンブリ。

**【請求項 13】**

前記 LED アレイからの光を屈折させるように構成された少なくとも 1 つのマイクロレンズアレイをさらに備える、請求項 11 または請求項 12 に記載のディスプレイヤセンブリ

50

り。

#### 【請求項 14】

前記少なくとも 1 つのマイクロレンズアレイは、前記タイルのアレイを覆う単一のマイクロレンズアレイを含む、請求項 13 に記載のディスプレイアセンブリ。

#### 【請求項 15】

前記少なくとも 1 つのマイクロレンズアレイは、複数のマイクロレンズアレイを含み、前記複数のマイクロレンズアレイの各々は、前記タイルのアレイの異なるタイルを覆う、請求項 13 に記載のディスプレイアセンブリ。

#### 【請求項 16】

前記少なくとも 1 つのマイクロレンズアレイは、複数のマイクロレンズアレイを含み、前記複数のマイクロレンズアレイの各々は、前記複数のバックプレーンダイのうちの単一のバックプレーンダイを覆う、請求項 13 に記載のディスプレイアセンブリ。 10

#### 【請求項 17】

前記タイルは、前記複数のバックプレーンダイを強固に支持する基板を含む、請求項 1 から請求項 16 のいずれか一項に記載のディスプレイアセンブリ。

#### 【請求項 18】

前記基板は、前記複数のバックプレーンダイのうちの少なくとも 1 つへの電気接続を提供する複数のシリコン貫通ビア (TSV) をさらに含む、請求項 17 に記載のディスプレイアセンブリ。

#### 【請求項 19】

前記タイルは、前記複数のバックプレーンダイ間のギャップを充填し、かつ、前記複数のバックプレーンダイを強固に支持するように構成されたオーバーモールドを含む、請求項 11 から請求項 18 のいずれか一項に記載のディスプレイアセンブリ。 20

#### 【請求項 20】

前記オーバーモールドは、シリカ材料、アルミナ材料、グラファイト材料、セラミック材料、またはポリマー材料の少なくとも一つから形成される、請求項 19 に記載のディスプレイアセンブリ。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

###### 関連出願

本願は、2020年4月6日に提出された U.S 特許出願第 63 / 005731 号の優先権を主張し、その全体が参照により本明細書に組み込まれる。

##### 【0002】

###### 背景

本開示の態様は、一般的に、異なるアセンブリに関し、より具体的には、バックプレーンを含むアセンブリ、およびバックプレーンと、ディスプレイを形成するための他の素子のアレイとを含むアセンブリに関する。

##### 【背景技術】

##### 【0003】

多くのディスプレイにおいて見落とされている一側面は、主ディスプレイパネル（例えば、個々の画素および / または光学素子からなるアレイ）の画素を駆動するために使用されるバックプレーン技術である。バックプレーンは、ディスプレイパネル内の個々の画素をオンおよびオフにすることに関与し、したがって、ディスプレイ全体の解像度、リフレッシュ速度、および電力消費において重要な役割を果たす、様々な回路および / またはトランジスタの設計、組み立て、または配列である。 40

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

現在の課題は、高度に集積され、発光素子（例えば、発光ダイオードまたは LED）ま

10

20

30

40

50

たは光反射素子ならびに光学素子と共に組み立てられ得るまたはパッケージされ得るバックプレーンを作製することである。集積化された光学素子および電子素子のためのパッケージング技術は、従来のパッケージング技術から進化し続けている。例えば、ウエハレベルチップスケールパッケージング（W L C S P）技術およびファンアウトウエハレベルパッケージング技術が改善されている。また、パッケージング寸法も改善され、さらに高密度の解決策を可能にしている。パッケージングは、パッケージ当たり1つのチップが存在する1次元（1 D）パッケージングから、2 Dパッケージング（例えば、パッケージ当たり複数のチップ）、インターポーラを含む2 . 5 Dパッケージング、およびチップスタッキングを含む3 Dパッケージングまで進んで来た。これらの技術によって提供された全ての改善点があっても、ライトフィールドディスプレイを含む高解像度ディスプレイにおいて必要とされる種類のアセンブリの要件を満たすことができない場合がある。

10

#### 【0005】

したがって、バックプレーンを有するアセンブリ、およびバックプレーンと、ディスプレイを形成する他の素子のアレイとの組み合わせを有するアセンブリの設計および製作を可能にする新しい技法が望ましい。

#### 【課題を解決するための手段】

#### 【0006】

##### 開示の概要

本開示の1つ以上の態様についての基礎知識を提供するために、これらの態様の概要を、以下に簡潔に示す。以下の概要是、意図される全ての態様の全体像を広く示すものではなく、全ての態様の重要なまたは不可欠な要素を特定するものでもなく、任意のまたは全ての態様の範囲を詳細に叙述するものでもない。以下の概要の目的は、1つ以上の態様のいくつかの概念を簡潔に提示して、その後に続く詳細な説明の序文とすることである。

20

#### 【0007】

本開示の一態様において、ディスプレイによって提供された光を制御するためのバックプレーンが説明される。バックプレーンは、アレイに形成された複数のタイルを備え、各タイルは、複数の相補型金属酸化膜半導体（C M O S）バックプレーンダイを含み、アレイの外周を形成するタイルの縁部は、C M O Sバックプレーンダイのうちの少なくとも1つに電気信号を導く電気コネクタを含む。

30

#### 【0008】

本開示の別の態様において、ディスプレイアセンブリが説明される。ディスプレイアセンブリは、タイルのアレイを含むバックプレーンを備え、各タイルは、電気的に結合された複数のC M O Sバックプレーンダイを含む。アレイの外周を形成するタイルの縁部は、複数のC M O Sバックプレーンダイのうちの1つ以上に電気信号を導く電気接続を含む。ディスプレイアセンブリは、少なくとも1つのタイルに電気的に結合された少なくとも1つの発光ダイオード（L E D）アレイをさらに備える。

#### 【0009】

添付の図面は、一部の実装形態のみを示し、したがって、範囲を限定するものとして見なされるべきではない。

40

#### 【図面の簡単な説明】

#### 【0010】

【図1】本開示の態様に従って、ディスプレイとディスプレイ用のコンテンツソースとの一例を示す図である。

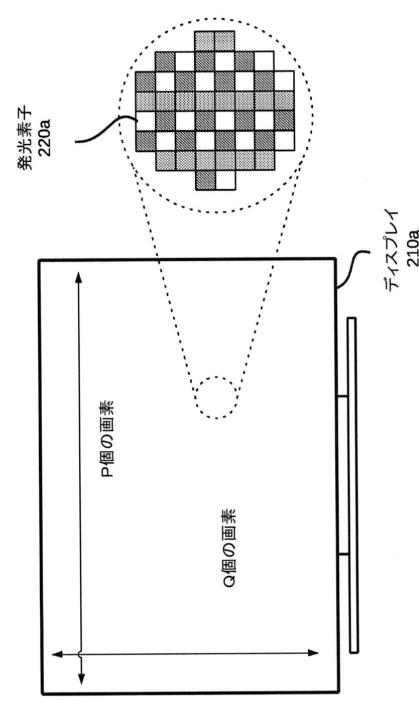

【図2 A】本開示の態様に従って、複数の画素を有するディスプレイの一例を示す図である。

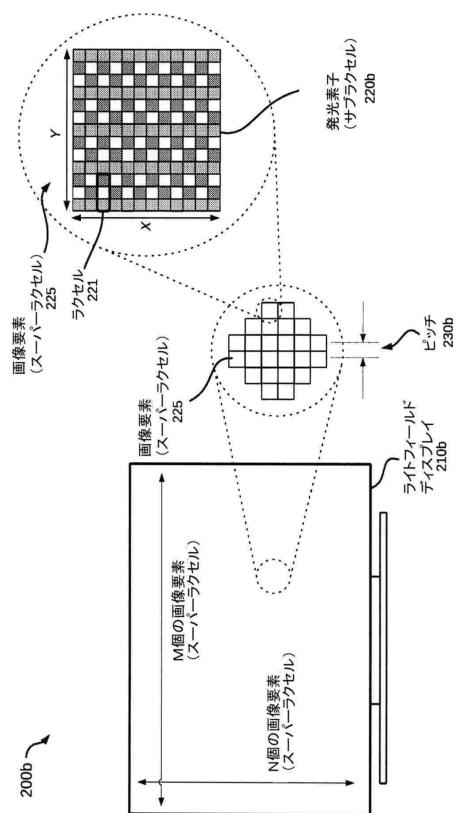

【図2 B】本開示の態様に従って、複数の画像要素を有するライトフィールドディスプレイの一例を示す図である。

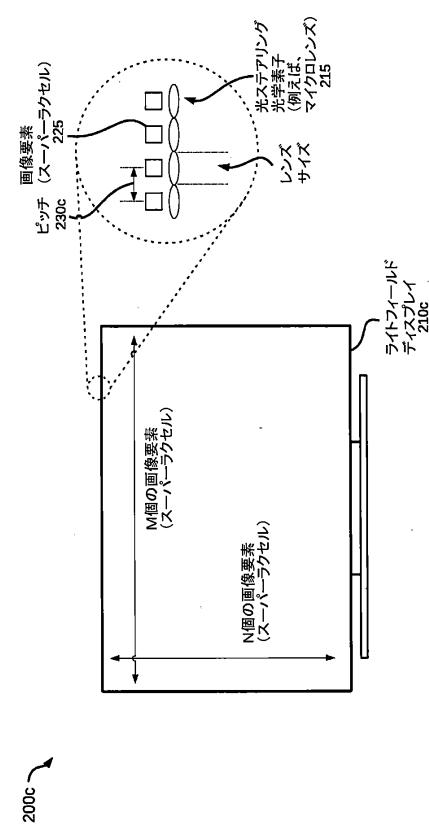

【図2 C】本開示の態様に従って、複数の画像要素を有するライトフィールドディスプレイの一例を示す図である。

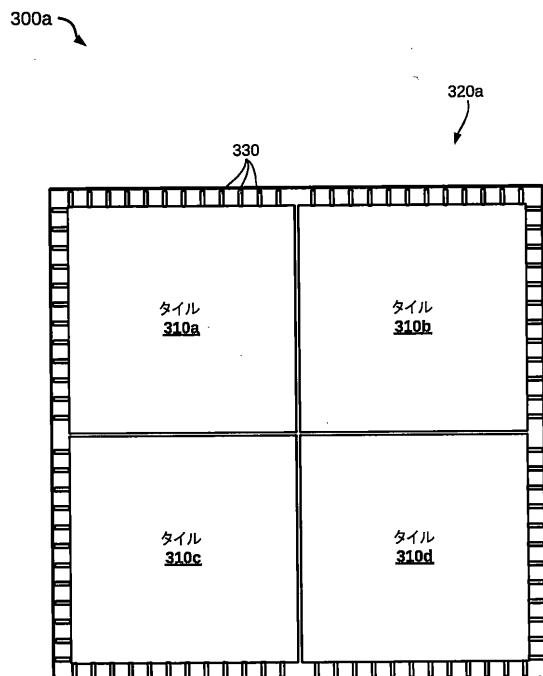

#### 【図3 A】本開示の態様に従って、複数のタイルによって形成されたバックプレーンの一

50

例を示す図である。

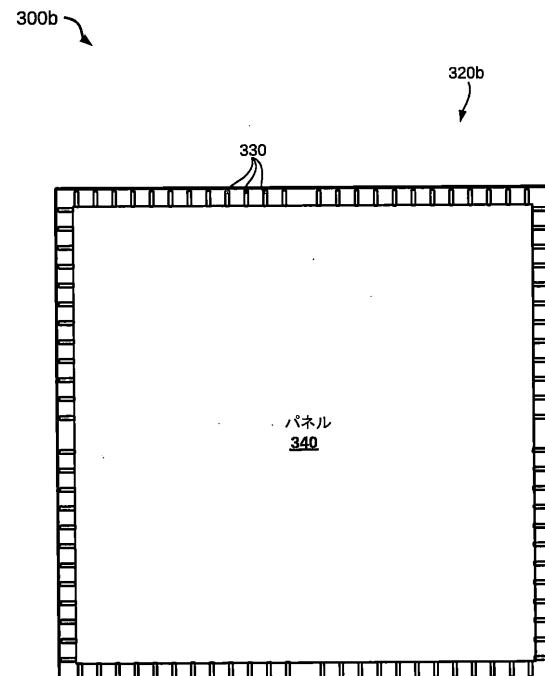

【図3B】本開示の態様に従って、単一パネルによって形成されたバックプレーンの一例を示す図である。

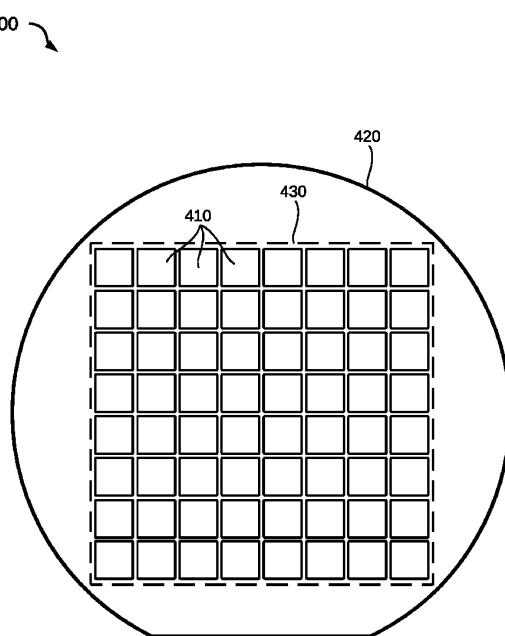

【図4】本開示の態様に従って、タイルがダイシングされた再構築ウエハの一例を示す図である。

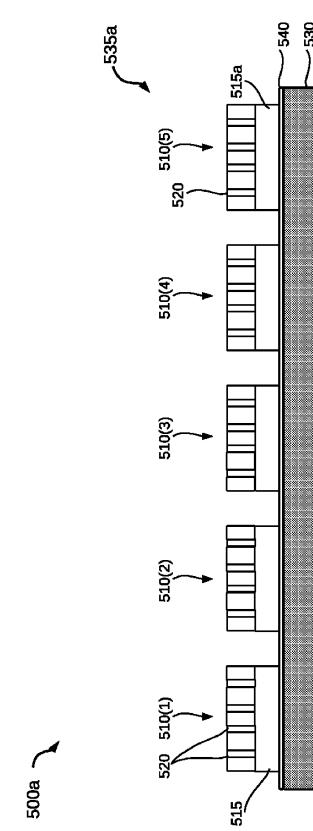

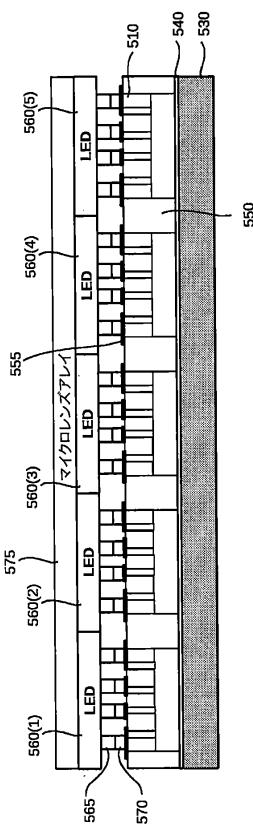

【図5A】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

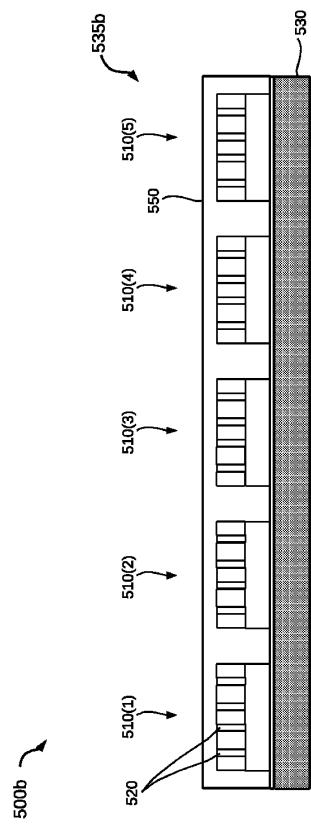

【図5B】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

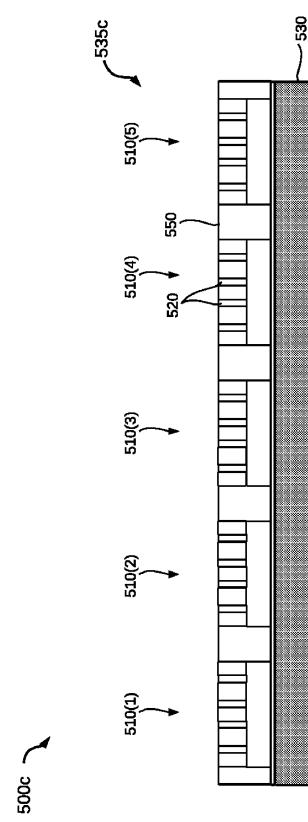

【図5C】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

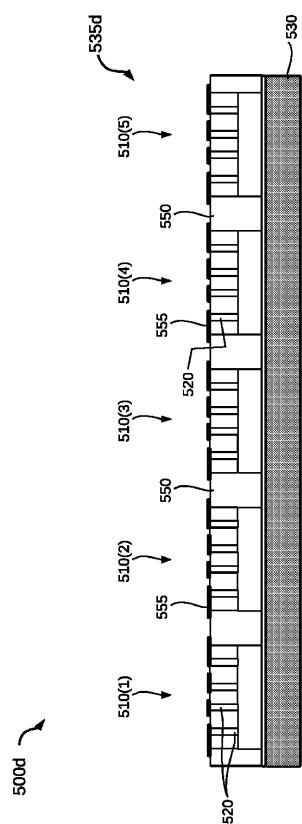

【図5D】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

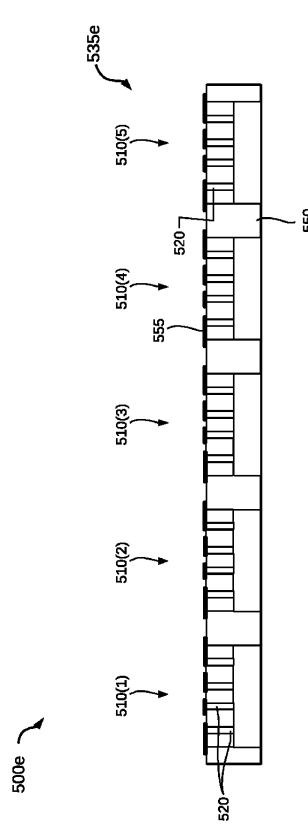

【図5E】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

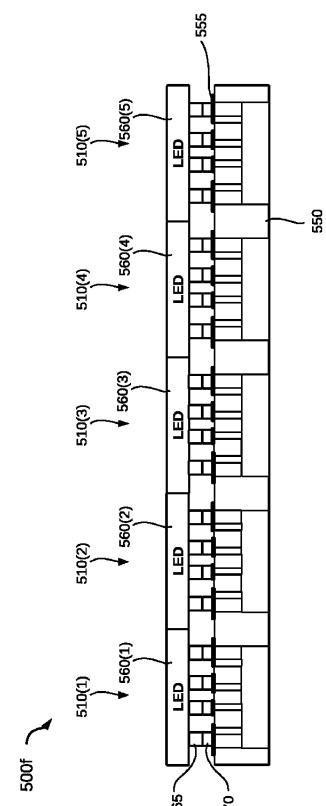

【図5F】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

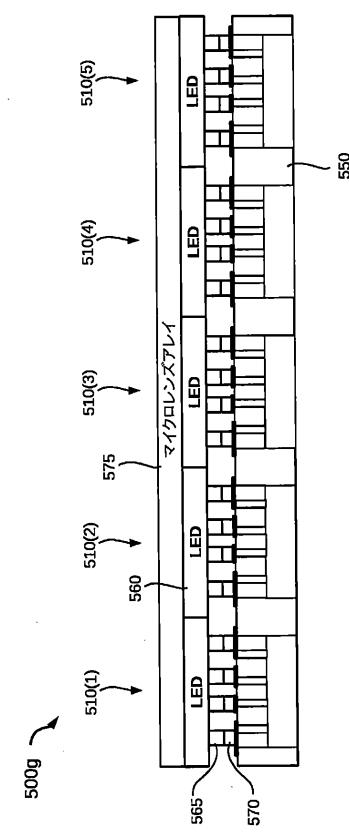

【図5G】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

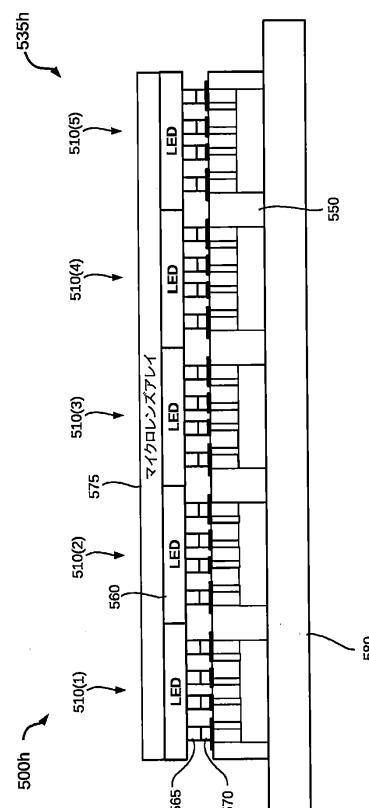

【図5H】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

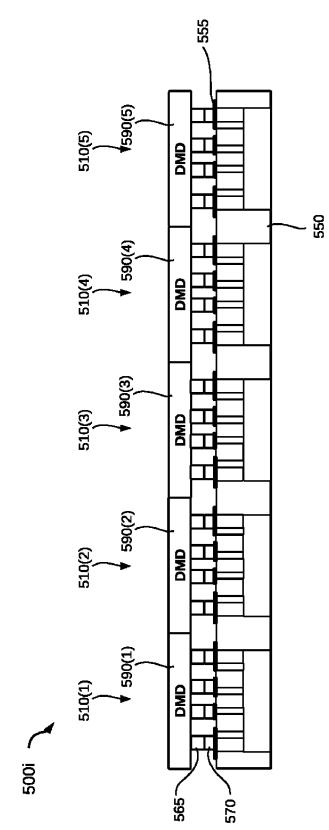

【図5I】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

【図5J】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

【図5K】本開示の態様に従って、ウエハレベルパッケージング（WLP）を用いてバックプレーンおよびディスプレイを形成する例を示す図である。

【図6A】本開示の態様に従って、パネルレベルパッケージング（PLP）を用いてアセンブリを形成する例を示す図である。

【図6B】本開示の態様に従って、パネルレベルパッケージング（PLP）を用いてアセンブリを形成する例を示す図である。

【図7A】本開示の態様に従って、WLPおよびPLP用のCMOSバックプレーンダイ、LEDアレイ、およびマイクロレンズアレイの異なる構成例を示す図である。

【図7B】本開示の態様に従って、WLPおよびPLP用のCMOSバックプレーンダイ、LEDアレイ、およびマイクロレンズアレイの異なる構成例を示す図である。

【図7C】本開示の態様に従って、WLPおよびPLP用のCMOSバックプレーンダイ、LEDアレイ、およびマイクロレンズアレイの異なる構成例を示す図である。

【図7D】本開示の態様に従って、WLPおよびPLP用のCMOSバックプレーンダイ、LEDアレイ、およびマイクロレンズアレイの異なる構成例を示す図である。

【図7E】本開示の態様に従って、WLPおよびPLP用のCMOSバックプレーンダイ、LEDアレイ、およびマイクロレンズアレイの異なる構成例を示す図である。

【図8A】本開示の態様に従って、ディスプレイによって提供される光を制御するためのバックプレーンを製造または製作する異なる方法を示す流れ図である。

【図8B】本開示の態様に従って、ディスプレイによって提供される光を制御するためのバックプレーンを製造または製作する異なる方法を示す流れ図である。

#### 【発明を実施するための形態】

##### 【0011】

###### 詳細な説明

添付の図面に関連して以下で記載される詳細な説明は、様々な構成の説明として意図されており、本明細書に記載されている概念を実施できる唯一の構成を表すように意図され

10

20

30

40

50

ていない。詳細な説明は、様々な概念の完全な理解を与えるための具体的な詳細を含む。しかしながら、これらの具体的な詳細がなくてもこれらの概念を実施できるということは当業者に明らかであろう。場合によっては、これらの概念を曖昧にしないように、プロック図で周知の構成要素を示す。

#### 【 0 0 1 2 】

将来のディスプレイ内の画素の数は、現行のディスプレイ内の画素の数よりも遥かに多く、場合によっては桁違いに多いと予想される。電力消費および全体的帯域幅が非常に高い解像度および非常に大きい画素数を有するディスプレイを実装する能力を制限し得るため、このようなディスプレイは、最終的に使用される種類のバックプレーンアセンブリまたはディスプレイアセンブリにおいて、特に電力消費および全体的帯域幅において、課題を与えるであろう。適切なバックプレーンアセンブリまたはディスプレイアセンブリを決定する際に考慮すべき特徴は、異なる技術オプションおよび異なる集積オプションを含む。「バックプレーン」および「バックプレーンアセンブリ」という用語は、本明細書に使用される場合、同義で使用されてもよい。同様に、「ディスプレイ」および「ディスプレイアセンブリ」という用語は、同義で使用されてもよい。また、いくつかの実装形態において、「ディスプレイ」または「ディスプレイアセンブリ」は、「バックプレーン」または「バックプレーンアセンブリ」を含んでもよい。

10

#### 【 0 0 1 3 】

技術オプションに関して、例えば、アモルファスシリコン ( a - S i ) 、金属酸化物、低温ポリシリコン ( L T P S ) 、および相補型金属酸化膜半導体 ( C M O S ) ウエハを含む、種々の可能な半導体技術が考慮される。これらの半導体技術のうち、L T P S および C M O S ウエハは、バックプレーンの帯域幅および密度要件を達成するためのより柔軟なオプションを提供することができる。例えば、C M O S ウエハは、1 M H z ~ 1 0 0 0 M H z の範囲の帯域幅および 1 μ m ~ 3 0 μ m の範囲のドライバセルピッチをサポートすることができる。一方、L T P S は、1 M H z ~ 1 5 M H z の範囲の帯域幅および 1 0 μ m ~ 1 0 0 0 0 μ m の範囲のドライバセルピッチをサポートすることができる。

20

#### 【 0 0 1 4 】

L T P S バックプレーン設計は、低コストおよび最も少ない接合界面を提供する製造工程を含む。しかしながら、L T P S は、高い精度で広い領域を提供することができるカスタムダイ配置ツールを必要とする。場合によっては、L T P S は、配置面積および精度で充分な性能を提供できないことがある。

30

#### 【 0 0 1 5 】

本開示に記載されたように、パネルレベルパッケージング ( P L P ) 手法を用いて、または代替的にウエハレベルパッケージング ( W L P ) 手法の一部としてウエハタイルを用いて、C M O S バックプレーン設計を実現することができる。P L P 手法は、単一のパネルを用いて、バックプレーン / ディスプレイアセンブリを形成するが、W L P 手法は、ウエハタイルのアレイを用いて、バックプレーン / ディスプレイアセンブリを形成する。これらの 2 つの手法のいくつかの利点または長所は、既知の良好な C M O S ダイのみを使用すること、および高性能バックプレーンを生成することを含む。P L P 手法のいくつかの課題は、パネルレベルパッケージングプロセスが製造に一般的に利用可能ではなく、カスタムまたは非標準プロセスを必要とすることである。カスタムプロセスは、製造コストおよび時間の増加ならびに品質の可能な低下につながる可能性がある。W L P 手法のいくつかの利点または長所は、L E D ボンディングツール、レーザリフトオフツールおよびマイクロレンズ複製ツールを含む良好なツール利用可能性と、既知の良好なタイルに対するより良好な歩留まりとを含む。また、W L P 手法は、P L P 手法に進化する解決策を提供し得る。一方、W L P 手法のいくつかの課題は、タイルを精密にダイシングする必要性、タイルを極めて精密に張る必要性、5 つ以上のウエハタイルをディスプレイに使用する場合（例えば、1 2 インチの正方形ウエハタイルを含む 2 2 インチの対角線ディスプレイの場合）に裏面コンタクトを設ける必要性、および（いくつかの実装形態において、タイルを張るプロセスの完了後にマイクロレンズを適用することによって、マイクロレンズとタイ

40

50

ル間の継ぎ目を低減または排除し得るが)マイクロレンズとタイル間の継ぎ目が見える可能性である。

#### 【0016】

以下で説明される図1～2Cは、バックプレーンまたはディスプレイ(例えば、LEDおよびマイクロレンズを追加したバックプレーン)を作製するためのPLPおよびWLP手法を含む、本開示に記載された様々なバックプレーンおよびディスプレイの態様を適用できる種類のディスプレイの概観を提供する。

#### 【0017】

図1は、ソース120からコンテンツ/データ125(例えば、画像コンテンツ、ビデオコンテンツ、またはその両方)を受信するディスプレイ110の一例を示す図形100を示す。ディスプレイ110は、1つ以上のパネル(図示せず)を含んでもよい。ディスプレイ110内の各パネルは、(例えば、図2Aに示された)発光素子または光反射素子を各々含む発光パネルまたは反射パネルである。また、各パネルは、発光素子または光反射素子を駆動するためのバックプレーンまたはバックプレーンアセンブリを含んでもよい。各パネルは、単一のCMOSパネルから(例えば、CMOSバックプレーンパネルを用いて)作製されてもよく、または複数のCMOSウエハタイルから(例えば、CMOSバックプレーンウエハタイルを用いて)作製されてもよい。発光パネルは、使用された場合、アレイ状に配置された複数の発光素子を含むことができる。これらの発光素子は、本明細書において、「サブラクセル」(sub-raxel)(例えば、図2Aのサ布拉クセルまたは発光素子220aを参照)と呼ばれる。複数のサ布拉クセルをグリッド状またはアレイ状に配列することによって、「ラクセル」(raxel)221(図2Bを参照)を形成することができる。これらの発光素子は、1つ以上の半導体材料から作製される発光ダイオード(LED)であってもよい。これらのLEDは、単一の基板上にモノリシックに集積されてもよい。LEDは、無機LEDであってもよい。LEDは、mLEDまたはμLEDとも呼ばれるマイクロLEDであってもよい。発光素子を作製できる他のディスプレイ技術は、液晶ディスプレイ(LCD)技術または有機LED(OLED)技術を含む。「発光素子」、「発光体」、または単に「エミッタ」という用語は、本開示において同義で使用されてもよい。

#### 【0018】

ディスプレイ110は、超高解像度能力(例えば、8K以上の解像度のサポート)、高ダイナミックレンジ(コントラスト)能力、ライトフィールド能力、またはこれらの能力の組み合わせを有してもよい。ディスプレイ110は、ライトフィールド能力をさらに有してもよく、図2B、2Cに示すようにライトフィールドディスプレイとして動作してもよい。このようなライトフィールド能力を可能にするために、ディスプレイ110は、本明細書では「スーパーラクセル」(super-raxel)とも呼ばれる複数の画像要素を含んでもよい。各スーパーラクセル(例えば、図2Bおよび2Cのスーパーラクセル225)は、複数のグループのサ布拉クセル(例えば、図2Bのラクセル221)を含む。各ラクセル内の複数の発光素子は、同じ半導体基板上にモノリシックに集積されてもよい。スーパーラクセル内の各ラクセルは、光ステアリング光学素子に対して特定の位置(例えば、特定の(x,y)座標位置)から光を放射するように独立して作動されてもよい。図2A～2Cを参照して以下で論議されるように、ライトフィールドディスプレイは、異なる場所から光を選択的に放射または反射することによって、複数のビューをサポートすることができる。

#### 【0019】

図2Aの図形200aは、(画素または表示画素とも呼ばれる)複数の発光素子220aを有するディスプレイ210aを示す。上述したLEDであり得る発光素子220aは、通常、アレイ状に形成され、ディスプレイ210aのより高い画素密度、したがってより高い解像度を提供するように互いに隣接する。ディスプレイ210aは、図1の図形100に示されたディスプレイ110の例であってもよい。

#### 【0020】

10

20

30

40

50

図 2 A に示す例において、発光素子 220a は、ディスプレイ 210a の領域にわたって  $Q \times P$  アレイに編成または配置されてもよい。Q は、アレイ内の画素の行数であり、P は、アレイ内の画素の列数である。このようなアレイの一部の拡大図は、ディスプレイ 210a の右側に示されている。図示されていないが、ディスプレイ 210a は、発光素子 220a のアレイに加えて、1つ以上の発光素子 220a に電力を選択的に提供するように構成された様々な電気トレースおよび接点を含むバックプレーンを含んでもよい。ディスプレイ 210a に結合されたバックプレーンは、本明細書に記載された特徴または構成を有してもよい。

#### 【0021】

図 2 B の図形 200b は、複数の画像要素またはスーパーラクセル 225 を有するライトフィールドディスプレイ 210b を示す。本開示において、「画像要素」という用語および「スーパーラクセル」という用語は、ライトフィールドディスプレイにおける同様の構造ユニットを説明するために同義で使用されてもよい。ライトフィールドディスプレイ 210b は、ライトフィールド能力を有する図形 100 のディスプレイ 110 の例であってもよい。ライトフィールドディスプレイ 210b を異なる種類の用途に使用してもよく、用途に応じてそのサイズを変更してもよい。例示として、ライトフィールドディスプレイ 210b は、腕時計、ニアアイ (near-eye) アプリケーション、電話、タブレット、ラップトップ、モニタ、テレビ、および掲示板のディスプレイとして使用されるときに、異なるサイズを有してもよい。したがって、用途に応じて、ライトフィールドディスプレイ 210b の画像要素 225 は、異なるサイズのアレイ、グリッド、または他の種類の順序付け配列に編成されてもよい。ライトフィールドディスプレイ 210b の画像要素 225 は、1つ以上のディスプレイパネルにわたって分散されてもよい。

10

20

30

#### 【0022】

図 2 B に示す例において、画像要素 225 は、 $N \times M$  アレイに編成または配置され、N はアレイ内の画像要素の行数であり、M は、アレイ内の画像要素の列数である。このようなアレイの一部の拡大図は、ライトフィールドディスプレイ 210b の右側に示されている。画像要素またはスーパーラクセル 225 が、同じ半導体基板上で、赤色 (R) 光、緑色 (G) 光、および青色 (B) 光を生成する異なる LED を発光素子 220b として含む場合、ライトフィールドディスプレイ 210b は、RGB LED スーパーラクセルから作製されると言うことができる。これらの異なる色の LED は、同じ基板上でモノリシックに集積されてもよく、約 1 μm ~ 約 100 μm のサイズ範囲に変動してもよい。

30

#### 【0023】

ライトフィールドディスプレイ 210b の画像要素 225 の各々は、対応する光ステアリング光学素子（例えば、図 2 C の図形 200c に示された一体型イメージングレンズ 215）を含んでもよい。画像要素 225 は、ディスプレイ解像度を定義する最小画像要素サイズを表す。この場合、画像要素 225 のラクセル 221（例えば、発光素子 220b のアレイまたはグリッド）は、その画像要素に対応する光ステアリング光学素子 215 より小さくてもよい。しかしながら、実際には、画像要素 225 のラクセルのサイズは、対応する光ステアリング光学素子 215 のサイズ（例えば、マイクロレンズまたは小型レンズの直径）と同様であってもよく、対応する光ステアリング光学素子 215 のサイズは、画像要素 225 間のピッチ 230b と同様または同じであってもよい。いくつかの実施形態において、スーパーラクセルは、画像要素よりも小さくてもよく、または画像要素とほぼ同じサイズであってもよい。より大きいスーパーラクセル（例えば、画像要素とほぼ同じサイズを有するスーパーラクセル）は、光角度分解能を増加することができる。

40

#### 【0024】

上述したように、発光素子 220b のアレイは、図形 200b の右側に示された画像要素 225 の拡大図に示されている「ラクセル」 221 に配列されてもよい。画像要素 225 は、発光素子 220b の  $X \times Y$  アレイであってもよい。 $X$  は、アレイ内の発光素子 220b の行数であり、 $Y$  は、アレイ内の発光素子 220b の列数である。一例として、画像要素 225 は、81 個の発光素子またはサブラクセル 220b を含む 9 × 9 アレイである。

50

### 【0025】

図2Cの図形200cは、ライトフィールドディスプレイ210cの別の例と、上述しように対応する光ステアリング光学素子215を有する画像要素225のアレイの一部の拡大図とを示す。ピッチ230cは、隣接する画像要素225の中心間の間隔または距離を表し、光ステアリング光学素子215のサイズ（例えば、マイクロレンズまたは小型レンズのサイズ）とほぼ同じであってもよい。これによって、ライトフィールドディスプレイ210cを形成するように光ステアリング光学素子をアレイに配列するときに、光ステアリング光学素子の間に隙間を有しないまたは最小限の隙間しか有しない。図2Cにおいて画像要素225が互いに分離していると示されているが、これは、例示の目的にすぎず、画像要素225の間に隙間を有しないように画像要素225を互いに隣接して作ってもよい。

10

### 【0026】

図3Aは、本開示の態様に従って、複数のタイル310a、310b、310c、310dで形成されたバックプレーン320aの一例を有する図形300aを示す。バックプレーン320aは、図1～2Cに関連して上述したディスプレイのいずれかと共に使用することができる。バックプレーンアセンブリとも呼ばれ得るバックプレーン320aは、アレイを形成するように配置された4つのタイル（例えば、タイル310a、310b、310c、および310d）で作製されてもよい。図3Aの例は、4つのタイルを有するが、バックプレーンは、本開示の範囲から逸脱することなく、より多いまたはより少ないタイルで作製されてもよい。電気コネクタ330を用いて、タイル310a～310dのうちの1つ以上との間で信号を送受信することができる。バックプレーン320a上のタイル310a～310dのうちの1つ以上が発光素子および／または光学素子または要素（例えば、サブラクセル、ラクセル、および／またはスーパーラクセル）を含む場合、バックプレーン320aは、例えば、ディスプレイまたはディスプレイアセンブリと呼ばれてもよい。

20

### 【0027】

図4を参照して以下により詳細に説明するように、タイルまたはウエハタイル310a～310dの各々は、複数のCMOSバックプレーンダイ（各ダイは、良品でかつ作動するダイ）を含む再構築ウエハからダイシングまたは切断されてもよい。すなわち、各タイルは、タイル内に共に保持された複数の別々の電気的に相互接続されたCMOSバックプレーンダイ（図示せず）を含む。図形300aに示すように、バックプレーン320aの外周に位置するタイル310の縁部は、各タイル310a～310d内のCMOSバックプレーンダイとの相互作用および／または通信を可能にする電気コネクタ330を提供する。タイルの縁部の周りに配置された電気コネクタ330の代わりにまたはそれに加えて、シリコン貫通ビア（TSV）電気接続を用いて、バックプレーン320aの基板と1つ以上のタイル310a～310dとの間の電気接続を提供することができる。タイル内の各CMOSバックプレーンダイは、電気的に結合された発光素子または光反射素子の各サブセットを制御するための電気信号を提供するように構成されたCMOS集積回路である。

30

### 【0028】

図3Bは、本開示の態様に従って、単一のパネル340で形成されたバックプレーン320bの一例の図形300bを示す。バックプレーン320bは、図1～2Cに関連して上述したディスプレイのいずれかと共に使用することができる。バックプレーン320bは、バックプレーンアセンブリと呼ばれてもよい。電気コネクタ330を用いて、パネル340との間で信号を送受信することができる。バックプレーン320bを発光素子および／または光学素子もしくは要素に結合する場合、このアセンブリは、ディスプレイまたはディスプレイアセンブリと呼ばれてもよい。電気コネクタ330とディスプレイアセンブリ内の発光素子との間の電気接続の例は、以下で図5A～5Kを参照してさらに詳細に説明される。

40

### 【0029】

以下により詳細に説明されるように、パネル340は、パネル内に共に保持された複数

50

の別々の電気的に相互接続された C M O S バックプレーンダイ（図示せず）を含む。パネル 340 は、再構築ウエハを形成するために使用された方法と同じ方法を用いて、より大きな規模で形成されてもよい。図形 300 b に示すように、パネル 340 の外周に位置する縁部は、パネル内の 1 つ以上の C M O S バックプレーンダイと相互作用または通信するための電気コネクタ 330 を提供する。パネル内の各 C M O S バックプレーンダイは、ディスプレイの 1 つ以上のサブセットの発光素子（例えば、図 2B の 1 つ以上のサブラクセル 220 b）または光反射素子を各自制御するための信号を提供するように構成された C M O S 集積回路である。

### 【 0030 】

図 4 は、本開示の態様に従って、タイル 430 がダイシングまたは切断される再構築ウエハ 420 の一例を示す図形 400 を示す。タイル 430 は、図 3A のタイル 310 を表してもよい。一般的に特定のサイズおよび形状を有するウエハを必要とする従来の半導体製造および処理装置を使用するために、タイルまたはウエハタイル（例えば、図 3A のタイル 310 a ~ 310 d）を形成または製作する 1 つの方法は、ウエハ 420 上に複数の C M O S バックプレーンダイ 410 をアレイに配置し、それから、従来の製造ステップを用いてウエハ 420 を処理した後に、再構築ウエハ 420 から（破線で示す）正方形または長方形のタイル 430 を切断またはダイシングすることによって、標準サイズおよび形状のウエハを再構築する。これによって、標準サイズ / 形状のウエハを処理するように構成された種々の従来の半導体製造工程を通して、再構築ウエハ 420（したがって、タイル 430）を処理することが可能になる。その理由は、ウエハ 420 がなければ、正方形または長方形のタイル 430 は、のサイズおよび形状において非標準的であり、従来の半導体処理ツールおよび機器に適していないからである。

10

### 【 0031 】

図 5A ~ 5I は、本開示の態様に従って、ウエハレベルパッケージング（W L P）手法を用いて、バックプレーンアセンブリ（例えば、図 3A および 3B に示された 1 つ以上のバックプレーン 320 a および 320 b）およびディスプレニアセンブリ（例えば、図 1、2A、2B および 2C に各々示されたディスプレイ 110、210 a、210 b および 210 c）を形成するための例示的なステップを示す図形 500 a ~ 500 i を示す。

20

### 【 0032 】

図 5A の図形 500 a は、再構築ウエハ（例えば、図 4 の再構築ウエハ 420）からダイシングされたタイル 535 a の少なくとも一部の断面図を示す。タイル 535 a は、基板 530 と、接着層 540 とを含み、接着層 540 には、複数の C M O S バックプレーンダイ 510（例えば、図 4 の C M O S バックプレーンダイ 410）が取り付けられている。接着層 540 は、C M O S バックプレーンダイ 510 を基板 530 に永久に結合することができる。このことは、ダイの移動を軽減することができる。この例において、各 C M O S バックプレーンダイ 510 は、ピラー 520（例えば、ダイまたはチップの電気接続）が基板 530 から離れて面するように上向きに配置され、追加のディスプレイ要素（図示せず）と電気的に結合するように構成される。ピラー 520 の下方に位置するダイのベース 515 a（例えば、バックプレーン電子機器および回路を含む C M O S バックプレーンダイ 510 の一部）は、接着層 540 および基板 530 に隣接する。ピラー 520 は、銅（C u）ピラーであってもよい。すなわち、C u を用いて、ダイの電気接続を形成することができる。しかしながら、他の伝導性金属または材料を使用してもよい。C M O S バックプレーンダイ 510 は、例示の目的で離れて示されている（例えば、隣接する C M O S バックプレーンダイの間にギャップを有する）が、密にパッケージすることが意図されている場合、隣接するダイに密に配置されてもよい。一例として、現在では、既存の半導体アセンブリおよびテスト（O S A T）ツールを用いて C M O S バックプレーンダイ 510 間のギャップを 300 μm にすることが可能であるが、100 μm のギャップが望ましい。

30

### 【 0033 】

図 5B の図形 500 b は、タイル 535 b 上の C M O S バックプレーンダイ 510 の上

40

50

方および周囲にオーバーモールド 550（または同様の封止材料）を堆積することによって、CMOS バックプレーンダイ 510 を共に保持することを示す。この例において、オーバーモールド 550 は、CMOS バックプレーンダイ 510 の上部を覆う量（例えば、過剰量）を有する。オーバーモールド 550 は、用途に適したカスタム材料であってもよい。一例は、シリカ充填工ポキシ成形材料（EMC）である。この材料は、硬化時に剛性であるが、ダイの移動を引き起こす可能性がある。別の例は、ポリイミドである。この材料は、柔軟であるが、現在の方法またはプロセスでは供給することができない。場合によっては、インクジェット技術を用いてポリイミドを供給することができる。

#### 【0034】

図 5C の図形 500c は、オーバーモールド 550 の一部を研削、エッチング、または別の方法で除去することによって、CMOS バックプレーンダイ 510 の上部（例えば、ピラー 520 の上部）を露出させる（例えば、過剰量のオーバーモールドを除去する）ことを示すタイル 535c を示す。ポリイミドを用いてオーバーモールド 550 を形成する場合、ポリイミドが常に良好に研削されるとは限らないため、スキージによる堆積または研削を行わない直接パターニングなどの異なる手法を用いて、ポリイミドを供給することが重要である。

#### 【0035】

図 5D の図形 500d は、CMOS バックプレーンダイ 510 間の相互接続を形成するために、（図 5C に示された）CMOS バックプレーンダイ 510 のピラー 520 の露出部分の上面に電気再分配層（RDL）555、例えば銅（Cu）RDL を堆積したタイル 535d を示す。具体的には、RDL 555 は、CMOS バックプレーンダイ 510 を相互接続するために、異なる CMOS バックプレーンダイ 510 のピラー 520 の間に電気接続を提供する。標準的なプロセスを用いて、RDL 555 を堆積することができる。一例として、RDL に必要とされる配線密度が適応リソグラフィ技法にとって困難であり得るが、ダイの移動を考慮するために、適応リソグラフィが用いられ得る。

#### 【0036】

図 5E の図形 500e は、基板 530 および接着層 540 を除去した再構築ウエハからダイシングされたタイル 535e の部分断面図を示す。代替的には、タイル 535e は、基板 530 および / または接着層 540 を使用せずに形成されてもよい。したがって、CMOS バックプレーンダイ 510 は、オーバーモールド 550 によって共に保持される。図形 500e に示すように、RDL 555 は、タイル 535e の上部（すなわち、1 つ以上の CMOS バックプレーンダイ 510 の露出したピラー 520 の上部）および CMOS バックプレーンダイ 510 の底部に配置され、タイル 535e の底部を形成する。

#### 【0037】

追加の構成要素（例えば、LED アレイおよび / またはマイクロレンズアレイ）を有しない、図形 500e に示されたタイル 535e、またはタイル 535e がダイシングされた再構築ウエハは、バックプレーンまたはバックプレーンアセンブリとして見なされてもよい。しかしながら、（以下でより詳細に説明するように）追加の構成要素または素子（例えば、LED アレイおよび / またはマイクロレンズアレイ）を再構築ウエハ上のバックプレーンまたはバックプレーンアセンブリに追加することができる。この構造は、図 4 に関連して上記で説明した方法でダイシングまたは切断され得るディスプレイアセンブリとして見なされてもよい。

#### 【0038】

図 5F の図形 500f は、LED アレイ 560 を CMOS バックプレーンダイ 510 にフリップチップボンディングしたことを示す。LED アレイ 560 の各々は、例えば、図 2A ~ 2C に関連して上述した複数の発光素子を含む別個の半導体チップまたはダイである。LED アレイ 560 は、RDL 555 上に配置された RDL 555 の部分または他の電気接続 570 と電気的に接続する電気接点または接続 565 を含むことができる。図形 500f が LED アレイ 560 と CMOS バックプレーンダイ 510 との間の 1 対 1 の対応を示しているが、これは、単なる例示であり、限定ではない。单一の LED アレイ 56

10

20

30

40

50

0を複数のCMOSバックプレーンダイ510に電気的に結合してもよく、または複数のLEDアレイ560を単一のCMOSバックプレーンダイ510に電気的に結合してもよい。CMOSバックプレーンダイ510の電子装置および回路を選択して、対応するLEDアレイ560のうちの1つ以上の内の1つ以上の発光素子の動作を制御することができる。RDLを用いてディスプレイアセンブリ内のLED、CMOSバックプレーンダイおよび/または他の構成要素を接続するための追加の電気接続スキームは、図5Jおよび5Kを参照して以下で説明される。

#### 【0039】

別の実装形態において、デジタルマイクロミラーデバイス(DMD)反射器などの光反射素子のアレイは、LEDアレイ560と組み合わせて使用されてもよく、またはその代わりに使用されてもよい。この場合、CMOSバックプレーンダイ510の電子装置および回路を選択して、1つ以上の光反射素子の動作を制御することができる。図5Iは、複数のDMD反射器アレイ590を有するディスプレイアセンブリを示している。図5Fに示されたアセンブリと同様に、1つ以上の電気接点または接続565、570は、RDL555をDMDアレイ590に電気的に結合することができる。1つ以上のDMDアレイ590は、CMOSバックプレーンダイ510の各々に電気的に結合されてもよい。代替的に、1つ以上のCMOSバックプレーンダイ510は、DMDアレイ590の各々に電気的に結合されてもよい。

10

#### 【0040】

さらに、図形500fおよび500iに関連して、フリップチップボンディングの精度および再構築ウエハを基板530から除去するためにおよび/またはフリップチップボンディングされるLEDアレイ560もしくはDMDアレイ590を分離するために使用されるレザリフトオフ(LLTO)ツール、例えば、利用可能なウエハスケールLLTOツールに与えるいくつかの考慮事項を説明する。さらなる考慮事項は、LEDアレイ(またはDMD反射アレイ590)とCMOSバックプレーンダイとの間の熱膨張係数(CTE)の不整合を補償するためのアンダーフィルの使用、フリップチップ接続間のギャップが小さいときにアンダーフィルを供給する際の困難度、および事前適用フィルムの代わりにアンダーフィルを使用するか否かを含む。アンダーフィルを使用しない場合、マイクロレンズに関連してボイドが発生し得るか否か、およびこのような発生を回避する方法を考慮すべきである。

20

#### 【0041】

図5Gの図形500gは、CMOSバックプレーンダイ510上面のRDL555の上面にフリップチップ接合されたLEDアレイ560の上面に配置され、LEDアレイ560に取り付けられたマイクロレンズアレイ575を示す。マイクロレンズアレイ575は、様々な光学素子、例えば、図2Cに関連して上述した光ステアリング光学素子(例えば、レンズまたはマイクロレンズ)215を含むことができる。図形500gが単一のマイクロレンズアレイ575を示しているが、これは、単なる例示であり、限定ではない。複数のマイクロレンズアレイ575を使用することも可能である。さらに、以下により詳細に示すように、CMOSバックプレーンダイ510とLEDアレイ560とマイクロレンズアレイ575とは、1対1で対応する必要がない。

30

#### 【0042】

図5Hの図形550hは、図3Aおよび4に関連して上述したタイルのダイシングおよびタイルのボンディングを示す。この例において、図5Gに示された再構築ウエハの少なくとも一部を高精度ダイシングで切断することによって、切断タイル535hを形成する。この例において、切断タイルは、断面図では、CMOSバックプレーンダイ510と、電気接続565、570およびRDL555を通してCMOSバックプレーンダイ510に接続されたフリップチップ接合LEDアレイ560と、LEDアレイ560上面に配置された1つ以上のマイクロレンズアレイ575とを含む。切断タイル535hは、(例えば、接着層(図示せず)を使用する永久結合によって)他のタイル(例えば、図3Aを参照)と共に、剛性基板580に接合されてもよい。タイルのボンディングは、広い領域に

40

50

わたって高度な整列精度を必要とする。図 3 A に関して上記で説明したように、複数のタイルをバックプレーン上で組み立てることによって、ディスプレイアセンブリを形成することができる。

#### 【 0 0 4 3 】

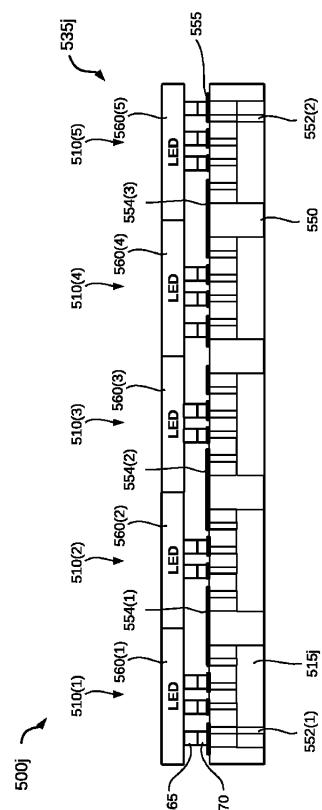

図 5 J および 5 K に各々示された図形 5 0 0 j および 5 0 0 k は、タイル 5 3 5 j、5 3 5 k の部分断面図である。タイル 5 3 5 j、5 3 5 k は、LED アレイ 5 6 0 の間の例示的な電気接続、CMOS バックプレーンダイ 5 1 0、必要に応じて、接着層 5 4 0 および基板 5 3 0 を含む。まず、図 5 J を参照して、タイル 5 3 5 j は、その間に配置された RDL 5 5 5 を用いて、複数の CMOS バックプレーンダイ 5 1 0 に電気的に結合された複数の LED アレイ 5 6 0 を含む。RDL 5 5 5 は、RDL の一部（すなわち、コネクタ 5 5 4）が異なる CMOS バックプレーンダイ間に延在できるようにパターン化される。例えば、RDL 5 5 5 のコネクタ 5 5 4 (1) は、第 1 の CMOS バックプレーンダイ 5 1 0 (1) を第 2 の CMOS バックプレーンダイ 5 1 0 (2) に電気的に結合する。同様に、RDL 5 5 5 のコネクタ 5 5 4 (2) は、第 2 の CMOS バックプレーンダイ 5 1 0 (2) を第 3 の CMOS バックプレーンダイ 5 1 0 (3) に電気的に結合する。同様に、RDL 内の追加のコネクタを用いて、追加の CMOS バックプレーンダイを相互接続することができる。したがって、接続が異なるバックプレーンダイを横断してプリッジするように RDL をパターン化することによって、タイルの中心に位置するバックプレーンダイ 5 1 0 (2)、5 1 0 (3)、5 1 0 (4)、および関連する LED アレイに（例えば、タイルの電気コネクタ 3 3 0 から）電気的にアドレスされ得る。

10

#### 【 0 0 4 4 】

図 5 J および 5 K を共に参照して、CMOS バックプレーンダイ 5 1 0 は、ベース部 5 1 5 j、5 1 5 k を各々有するように示されている。ベース部 5 1 5 j、5 1 5 k は、シリコン材料であってもよい。図形 5 0 0 j、5 0 0 k に示された実施形態において、ベース部 5 1 5 j、5 1 5 k は、CMOS バックプレーンダイ 5 1 0 への電気接続を提供し、および／または特定の実施形態において、ベース部 5 1 5 j、5 1 5 k の底部側から 1 つ以上の導電性ピラー（例えば、図 5 A のピラー 5 2 0）まで延在することができる 1 つ以上のシリコン貫通ビア（TSV）5 5 2 を含むことができる。TSV 5 5 2 は、電気伝導性材料から形成され、（例えば、異なる電気コネクタから、電源から、または制御モジュールから）電流または信号を受信し、電流または信号を、直接にまたは中間コネクタを通して間接的に、1 つ以上の LED アレイ 5 6 0 に送達するように構成されている。

20

#### 【 0 0 4 5 】

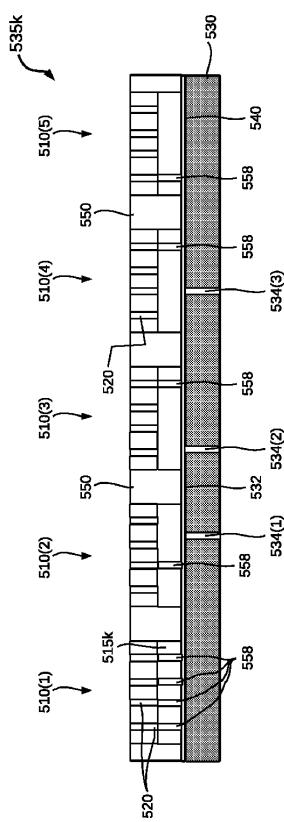

図 5 K の図形 5 0 0 k は、基板 5 3 0（例えば、上面と底面との間）を通って延在する追加の TSV 5 3 4 を示す。タイル 3 5 3 K は、本開示の範囲から逸脱することなく、基板 5 3 0 により多いまたはより少ない TSV 5 3 4 を有してもよい。いくつかの実施形態において、TSV 5 3 4 の底面（すなわち、CMOS バックプレーンダイ 5 1 0 から最も遠い面）は、ディスプレイアセンブリの電源または別の電線導管に電気的に結合されてもよい。TSV 5 3 4 の上面（すなわち、CMOS バックプレーンダイ 5 1 0 に最も近い面）は、CMOS バックプレーンダイ 5 1 0 のベース部 5 1 5 k 内の 1 つ以上の TSV 5 5 8 に直接に結合されてもよい。代替的にまたは追加的に、TSV 5 3 4 の上面は、CMOS バックプレーンダイ 5 1 0 の 1 つ以上の TSV 5 5 8 に電流を送達する前にこの電流を分配するように、RDL または他のプリント回路に結合されてもよい。プリント回路が基板 5 3 0 の上面に配置されている実施形態において、接着層 5 4 0 は、輪郭に沿って形成されまたはプリント回路が接着層によって覆われないように選択的に適用されてもよい。いくつかの実施形態において、プリント回路は、導電性および接着性の両方を有する材料、例えば、電気接続を生成するように選択的に適用される導電性エポキシまたは異方性導電膜（ACF）から形成されてもよい。

30

#### 【 0 0 4 6 】

図 6 A および図 6 B は、本開示の態様に従って、パネルレベルパッケージング（PLP）を用いて、アセンブリを形成する例を示す図形 6 0 0 a および 6 0 0 b を各々示す。再

40

50

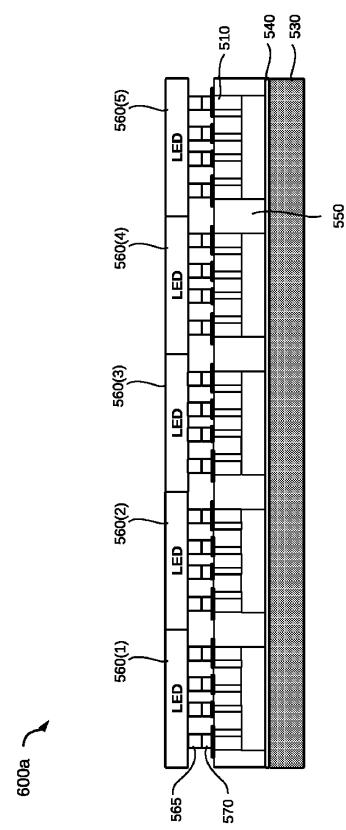

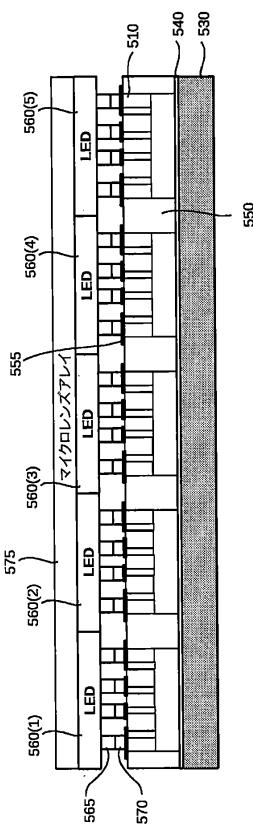

構築ウエハを形成してから、1つ以上のタイルにダイシングまたは切断する図5A～5Kの例とは異なり、図形600aおよび600bは、接着層540を用いてCMOSバックプレーンダイ510を保持し、RDL555を堆積し、電気接点または接続565および570を用いてLEDアレイ560をフリップチップボンディングし、その後1つ以上のマイクロレンズアレイ575を上面に配置する（例えば、図6B）ことによって、（除去されていない）基板530の上面に単一パネルを形成することを示す。PLPを用いて単一パネルを作製するための材料および／またはプロセスは、WLPを用いて（タイルがダイシングされる）再構築ウエハを作製するために使用されるものと同じまたは同様であってもよい。しかしながら、PLPアセンブリは、WLPを用いて形成されたタイルのサイズよりも大きくてよく、正方形または長方形の形状を有してもよい。したがって、PLPを用いて、バックプレーン電子装置だけでなく、光素子および／または光学素子を含む単一パネルバックプレーンアセンブリまたは単一パネルディスプレイアセンブリを作製することができる。PLPを用いて形成されたアセンブリは、アセンブリの周囲の電気コネクタ（図示せず）を含んでもよい。

#### 【0047】

図7A～7Eは、本開示の態様に従って、WLPおよびPLP用のCMOSバックプレーンダイ、LEDアレイ、およびマイクロレンズアレイの異なる構成の例を示す。上述したように、CMOSバックプレーンダイと、LEDアレイと、マイクロレンズアレイとの間に異なる対応関係が存在してもよい。

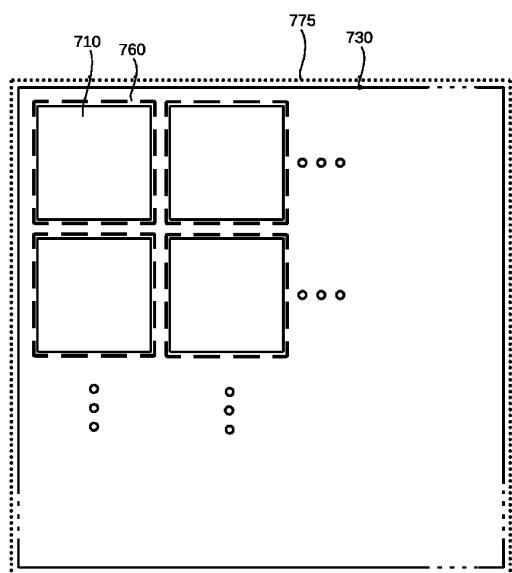

#### 【0048】

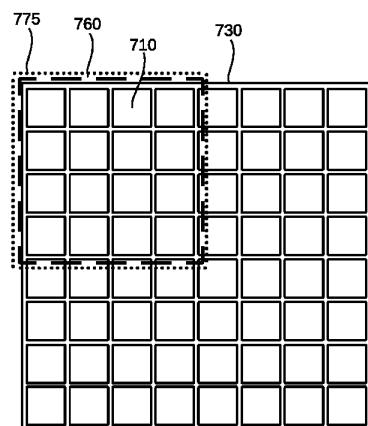

図7Aの図形700aは、アレイに配置された複数のCMOSバックプレーンダイ710を含むタイル（例えば、再構築ウエハからダイシングまたは切断されたタイル）またはパネル730の構成または実装を示す上面図である。各CMOSバックプレーンダイ710は、その上面に配置された対応するLEDアレイ760（破線で示す）を有する。さらに、单一のマイクロレンズアレイ775は、パネル730上のCMOSバックプレーンダイ710およびLEDアレイ760のセット全体を覆う。図3Aに示された2×2アレイのタイルにおいて、各タイルの2つの側面をバックプレーンの縁部に位置する電気コネクタに接続することができるが、アレイの周囲に沿って1つ以上の縁部を有する図7Aのダイ710以外の他のダイをパネル730の縁部に位置する電気コネクタ（図示せず）に直接に接続することができない。したがって、アレイの周囲に沿って縁部を有しない図7Aのダイに電気的にアドレスするために、各CMOSバックプレーンダイ710を隣接するCMOSバックプレーンダイに電気的に接続する。したがって、パネル730の全てのCMOSバックプレーンダイ710は、パネル730の縁部に位置する電気コネクタ（図示せず）から電気的にアドレスされ得る。代替的にまたは追加的に、1つ以上のCMOSバックプレーンダイへの電気接続は、例えば、電気接続を形成するためのビア（図示せず）または他の機構を用いて、パネル730を通して提供されてもよい。電気接続は、ワイヤボンディングなどの従来の方法を用いて提供されてもよい。

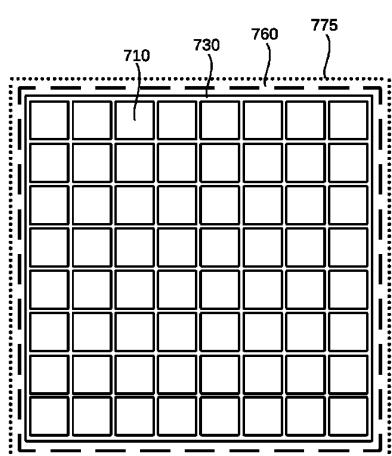

#### 【0049】

図7Bの図形700bは、アレイ（例えば、8×8アレイ）に配置された複数のCMOSバックプレーンダイ710と、CMOSバックプレーンダイ710の上面に配置された单一のLEDアレイ760とを含むタイルまたはパネル730の例示的な構成を示す。また、单一のマイクロレンズアレイ775は、CMOSバックプレーンダイ710およびLEDアレイ760のセット全体を覆う。

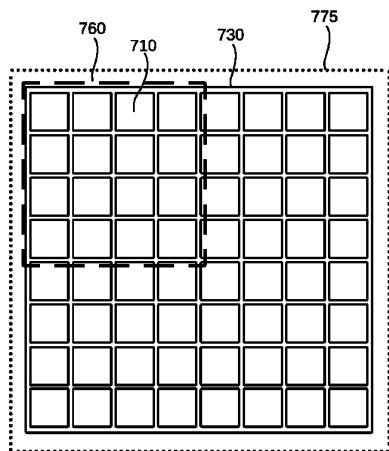

#### 【0050】

図7Cの図形700cは、アレイ（例えば、8×8アレイ）に配列された複数のCMOSバックプレーンダイ710と、CMOSバックプレーンダイ710の上面に設けられ、異なるアレイ（例えば、2×2アレイ）に配列された複数のLEDアレイ760とを含むタイルまたはパネル730の別の例示的構成を示す。この例において、各LEDアレイ760は、CMOSバックプレーンダイ710のサブセット（例えば、CMOSバックプレーンダイ710の4×4アレイ）を覆う。各LEDアレイ760は、同じ数のCMOSバ

10

20

30

40

50

ツクプレーンダイ710を覆ってもよいが、そのような必要がない。また、単一のマイクロレンズアレイ775は、CMOSバックプレーンダイ710およびLEDアレイ760のセット全体を覆う。

#### 【0051】

図7Dの図形700dは、アレイ（例えば、 $8 \times 8$ アレイ）に配置された複数のCMOSバックプレーンダイ710と、異CMOSバックプレーンダイ710の上面に設けられ、異なるアレイ（例えば、 $2 \times 2$ アレイ）に配列された複数のLEDアレイ760とを含むタイルまたはパネル730のさらに別の可能な構成または実装を示す。この例において、各LEDアレイ760は、CMOSバックプレーンダイ710のサブセット（例えば、CMOSバックプレーンダイ710の $4 \times 4$ アレイ）を覆う。各LEDアレイ760は、同じ数のCMOSバックプレーンダイ710を覆ってもよいが、そのような必要がない。また、マイクロレンズアレイ775は、複数であってもよい。この例において、各LEDアレイ760（例えば、マイクロレンズアレイ775の $2 \times 2$ アレイ）に対してマイクロレンズアレイ775が設けられるが、そのような必要がない。

10

#### 【0052】

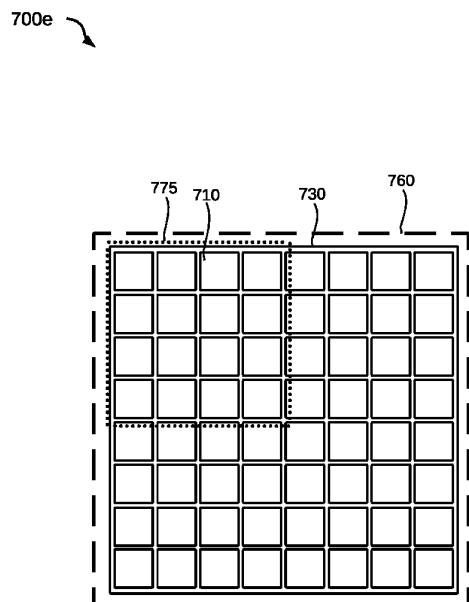

図7Eの図形700eは、アレイ（例えば、 $8 \times 8$ アレイ）に配列された複数のCMOSバックプレーンダイ710と、CMOSバックプレーンダイ710の上面に配置された単一のLEDアレイ760とを含むタイルまたはパネル730の別の構成または実装を示す。また、複数のマイクロレンズアレイ775は、CMOSバックプレーンダイ710およびLEDアレイ760のセット全体を覆う。この例において、マイクロレンズアレイ775は、CMOSバックプレーンダイ710とは異なるアレイ（例えば、 $2 \times 2$ アレイ）に配置され、各マイクロレンズアレイ775は、CMOSバックプレーンダイ710のサブセット（例えば、CMOSバックプレーンダイ710の $4 \times 4$ アレイ）を覆う。

20

#### 【0053】

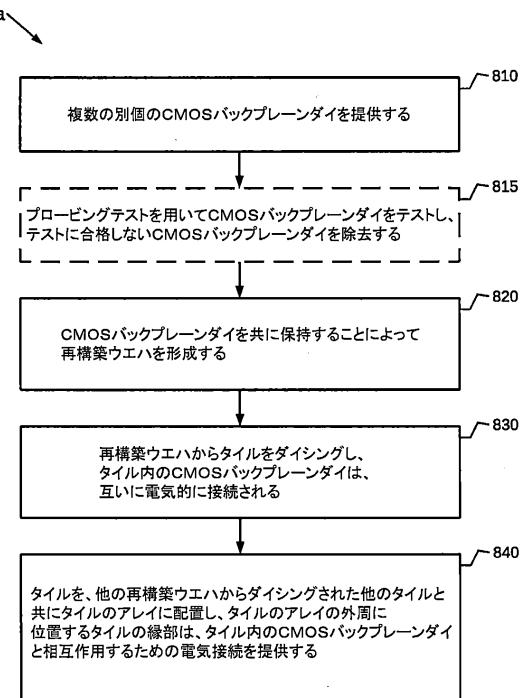

図8Aおよび8Bは、本開示の態様に従って、ディスプレイによって提供された光を制御するためのバックプレーンを製造または製作する異なる方法を示す流れ図である。

#### 【0054】

図8Aの方法800aは、ディスプレイによって提供された光を制御するためのバックプレーンを製造する方法に対応する。

30

#### 【0055】

方法800aは、810において、複数の別個のCMOSバックプレーンダイを提供することを含む。

#### 【0056】

必要に応じて、方法800aは、815において、プローピングテストを用いてCMOSバックプレーンダイをテストし、テストに合格しないCMOSバックプレーンダイを除去することを含む。

#### 【0057】

方法800aは、820において、CMOSバックプレーンダイを共に保持することによって再構築ウエハを形成することを含む。複数のCMOSバックプレーンダイは、剛性基板上に配置された接着層を用いて、互いにに対して固定位置に保持されてもよい。製造コストを低減するために、後続の処理ステップ中に、特製の処理機器ではなく、標準的な処理機器を用いて、CMOSバックプレーンダイおよび基板アセンブリを処理してもよい。さらなる処理ステップは、オーバーモールド層を堆積させることと、オーバーモールド層の一部を除去することによって導電性ピラーを露出させることと、電気再分配層（RDL）を堆積させることと、RDLの上面にLEDまたはDMDパネルを配置することとを含んでもよい。

40

#### 【0058】

方法800aは、830において、ウエハ（本明細書では「再構築ウエハ」とも呼ばれる）からタイルをダイシングすることを含み、タイル内のCMOSバックプレーンダイは、互いに電気的に接続される。

50

**【0059】**

方法 800a は、840において、タイルを、他の再構築ウエハからダイシングされた他のタイルと共にタイルのアレイに配置することを含み、タイルのアレイの外周に位置するタイルの縁部は、タイル内の CMOS バックプレーンダイと相互作用するための電気接続を提供する。

**【0060】**

方法 800a の一態様において、各 CMOS バックプレーンダイは、ディスプレイアセンブリ内の 1 つ以上のサブセットの発光素子または光反射素子を各々制御するための信号を提供するように構成された CMOS 集積回路である。

**【0061】**

方法 800a の一態様において、各 CMOS バックプレーンダイは、各タイルに含まれる前に、ウエハレベルプロービングテストに合格している。

10

**【0062】**

方法 800a の一態様において、再構築ウエハは、基板上に形成され、方法 800a は、再構築ウエハを基板から分離するウエハスケールレーザリフトオフ (LLO) プロセスを実行することによって、再構築ウエハを基板から除去することをさらに含む。

**【0063】**

方法 800a の一態様において、再構築ウエハは、基板を用いて形成され、基板は、タイルを再構築ウエハに固定し、ダイシングを完了した後、再構築ウエハの一部分として残る。

20

**【0064】**

方法 800a の一態様において、再構築ウエハは、基板上に形成され、CMOS バックプレーンダイは、基板に永久に取り付けられることによって、再構築ウエハの適所に保持される。

**【0065】**

方法 800a の一態様において、各タイル内の CMOS バックプレーンダイは、オーバーモールドを用いて共に保持され、CMOS バックプレーンダイは、上向きに配置され、再構築ウエハを形成することは、オーバーモールドの上面の一部を除去して、CMOS バックプレーンダイの電気ピラーを CMOS バックプレーンダイと電気再分配層との間の電気相互接続に露出させることをさらに含む。また、オーバーモールドの上面の一部を除去することは、研削、エッティング、または別の方法でオーバーモールドの上面の一部を除去することを含む。

30

**【0066】**

方法 800a の一態様において、各タイル内の CMOS バックプレーンダイは、オーバーモールドを用いて保持され、方法 800a は、少なくとも CMOS バックプレーンダイの間におよび周囲にオーバーモールドを配置することと、オーバーモールドを硬化させて再構築ウエハの一部を形成することとをさらに含み、オーバーモールドは、シリカ、アルミナ、グラファイト、セラミック、ポリマー、または電子成形材料を含む材料で作製される。ポリマーは、ポリイミドまたはエポキシを含んでもよい。

**【0067】**

方法 800a の一態様において、再構築ウエハからダイシングされるタイルのサイズは、4 インチから 18 インチまでの範囲にある。いくつかの実施形態において、ダイシングされたタイルは、約 11 インチであってもよい。本開示の範囲から逸脱することなく、他のタイルサイズも可能である。

40

**【0068】**

方法 800a の一態様において、再構築ウエハからダイシングされたタイルは、矩形のタイルまたは正方形のタイルである。

**【0069】**

方法 800a の一態様において、再構築ウエハは、ウエハレベル処理のための標準サイズを有し、標準サイズは、150 mm のウエハサイズ、200 mm のウエハサイズ、30

50

0 mmのウエハサイズ、または450 mmのウエハサイズのうち、1つである。

**【0070】**

方法800aの一態様において、タイルのアレイは、剛性基板上に配置される。

方法800aの一態様において、タイルのアレイは、可撓性基板上に配置される。

**【0071】**

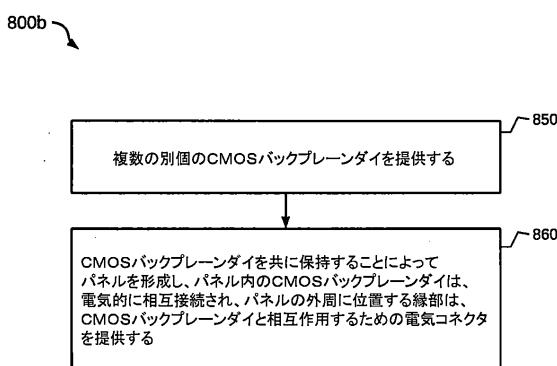

図8Bの方法800bは、ディスプレイによって提供される光を制御するためのバックプレーンを製造する別 の方法に対応する。

**【0072】**

方法800bは、850において、複数の別個のCMOSバックプレーンダイを提供することを含む。

10

**【0073】**

方法800bは、860において、CMOSバックプレーンダイと共に保持することによってパネルを形成することを含み、パネル内のCMOSバックプレーンダイは、電気的に相互接続され、パネルの外周に位置する縁部は、CMOSバックプレーンダイと相互作用するための電気コネクタを提供する。

**【0074】**

方法800bの一態様において、パネルを形成することは、CMOSバックプレーンダイを基板上に接合することによって、CMOSバックプレーンダイと共に保持することを含む。

20

**【0075】**

方法800bの一態様において、パネルを形成することは、オーバーモールドを用いてCMOSバックプレーンダイを保持することを含む。

**【0076】**

方法800bの一態様において、パネルを形成することは、CMOSバックプレーンダイを基板上に取り付けることと、オーバーモールドを用いてCMOSバックプレーンダイを保持することを含む。方法800bは、基板からパネルを分離するレーザリフトオフ( LLO )プロセスを実行することによって、基板からCMOSバックプレーンダイを有するパネルを除去することをさらに含んでもよい。さらに、基板からパネルを除去することは、パネルと基板との間に熱、レーザ、またはUV剥離可能層を使用することを含んでもよい。

30

**【0077】**

方法800bの一態様において、各CMOSバックプレーンダイは、ディスプレイの各サブセットの発光素子または光反射素子を制御するための信号を提供するように構成されたCMOS集積回路である。

**【0078】**

方法800bの一態様において、各CMOSバックプレーンダイは、パネルに含まれる前にウエハレベルプローピングテストに合格している。

**【0079】**

方法800bの一態様において、CMOSバックプレーンダイは、上向きに配置され、パネルを形成することは、オーバーモールドを用いてCMOSバックプレーンダイと共に保持することと、オーバーモールドの上面の一部を除去することによってCMOSバックプレーンダイの電気ピラーを露出させることを含む。また、オーバーモールドの上面の一部を除去することは、オーバーモールドの上面の一部を研削することを含む。さらに、CMOSバックプレーンダイの電気ピラーは、CMOSバックプレーンダイと電気再分配層との間の電気相互接続に露出される。

40

**【0080】**

方法800bの一態様において、パネルを形成することは、オーバーモールドを用いてCMOSバックプレーンダイと共に保持することを含み、方法800bは、少なくともCMOSバックプレーンダイの間におよび周囲にオーバーモールドを配置することと、オーバーモールドを硬化させてパネルを形成することをさらに含み、オーバーモールドは、

50

シリカ、アルミナ、グラファイト、セラミック、ポリマー、または電子成形材料を含む材料で作製される。ポリマーは、ポリイミドまたはエポキシを含んでもよい。

#### 【0081】

本開示は、ライトフィールドディスプレイなどの高解像度ディスプレイと共に使用され得る、バックプレーンおよびディスプレイのためのより大きくより高密度のアセンブリを可能にする種々の技法および装置を説明する。

#### 【0082】

以下の特許請求の範囲は、本明細書に記載される全ての一般的な特徴および具体的な特徴と、言語の問題としてその間にに入ると言われるであろう本方法およびシステムの範囲の全ての記載とを包含するよう意図されている。特に、以下の実施形態およびこれらの実施形態の互いに適合する任意の組み合わせが具体的に考えられる。

10

#### 【0083】

(A) ディスプレイを制御するためのバックプレーンであって、バックプレーンは、アレイに形成された複数のタイルを備え、各タイルは、複数の相補型金属酸化膜半導体(CMOS)バックプレーンダイを含み、アレイの外周を形成するタイルの縁部は、CMOSバックプレーンダイのうちの少なくとも1つに電気信号を導く電気接続を含む。

#### 【0084】

(B) (A)に記載されたバックプレーンにおいて、CMOSバックプレーンダイのうちの少なくとも1つは、ディスプレイの少なくとも1つの発光素子を駆動するための少なくとも1つの電気信号を生成するCMOS集積回路を含む。

20

#### 【0085】

(C) (A)または(B)に記載されたいずれかのバックプレーンにおいて、各CMOSバックプレーンダイは、ディスプレイの少なくとも1つの光反射素子への電気信号を生成するためのCMOS集積回路を含む。

#### 【0086】

(D) (A)～(C)に記載されたいずれかのバックプレーンにおいて、複数のタイルが $2 \times 2$ アレイとして形成されている場合、各タイルは2つの縁部を有し、各縁部はアレイの外周に位置する電気接続を有する。

#### 【0087】

(E) (A)～(D)に記載されたいずれかのバックプレーンにおいて、タイルの縁部に位置する複数のCMOSバックプレーンダイのうちの一部は、タイルの残りのCMOSバックプレーンダイへの外部電気接続を提供する。

30

#### 【0088】

(F) (A)～(E)に記載されたいずれかのバックプレーンにおいて、複数のCMOSバックプレーンダイは、長方形または正方形のアレイに配置され、複数のCMOSバックプレーンダイの各々は、電気再分配層(RDL)を介して、ディスプレイの少なくとも1つのLEDアレイに電気的に接続された複数のピラーを含む。

#### 【0089】

(G) (A)～(F)に記載されたいずれかのバックプレーンにおいて、複数のタイルの各々は、CMOSバックプレーンダイ間のギャップを充填し、かつ、複数のCMOSバックプレーンダイを共に保持するオーバーモールドをさらに含む。

40

#### 【0090】

(H) (A)～(G)に記載されたいずれかのバックプレーンにおいて、オーバーモールドは、シリカ、アルミナ、グラファイト、セラミック、およびポリマーからなる群から選択される材料から形成される。

#### 【0091】

(I) (A)～(H)に記載されたいずれかのバックプレーンにおいて、複数のタイルの各々は、複数のCMOSバックプレーンダイを確実に支持するための基板をさらに含む。

#### 【0092】

(J) (A)～(I)に記載されたいずれかのバックプレーンにおいて、基板は、剛性

50

であり、かつ、複数のCMOSバックプレーンダイのうちの少なくとも1つへの電気接続を提供する複数のシリコン貫通ビア(TSV)を含む。

#### 【0093】

(K) タイルのアレイを含むバックプレーンを備え、各タイルは、電気的に結合された複数のCMOSバックプレーンダイを含み、アレイの外周を形成するタイルの縁部は、複数のCMOSバックプレーンダイのうちの1つ以上に電気信号を導く電気接続を含み、さらに、少なくとも1つのタイルに電気的に結合された少なくとも1つの発光ダイオード(LED)アレイを備える、ディスプレイアセンブリ。

#### 【0094】

(L)(K)に記載されたディスプレイアセンブリにおいて、複数のタイルの各々は、CMOSバックプレーンダイのうちの少なくとも1つのピラーを少なくとも1つのLEDアレイに電気的に接続するために、複数のCMOSバックプレーンダイの各々の少なくとも一部に配置された電気再分配層をさらに含む。

10

#### 【0095】

(M)(K)または(L)に記載されたディスプレイアセンブリは、LEDアレイからの光を屈折させるように構成された少なくとも1つのマイクロレンズアレイをさらに含む。

#### 【0096】

(N)(K)～(M)に記載されたいずれかのディスプレイアセンブリにおいて、少なくとも1つのマイクロレンズアレイは、タイルのアレイを覆う単一のマイクロレンズアレイを含む。

20

#### 【0097】

(O)(K)～(N)に記載されたいずれかのディスプレイアセンブリにおいて、少なくとも1つのマイクロレンズアレイは、複数のマイクロレンズアレイを含み、複数のマイクロレンズアレイの各々は、タイルのアレイの異なるタイルを覆う。

#### 【0098】

(P)(K)～(O)に記載されたいずれかのディスプレイアセンブリにおいて、少なくとも1つのマイクロレンズアレイは、複数のマイクロレンズアレイを含み、複数のマイクロレンズアレイの各々は、単一のCMOSバックプレーンダイを覆う。

#### 【0099】

(Q)(K)～(P)に記載されたいずれかのディスプレイアセンブリにおいて、タイルのアレイの各タイルは、複数のCMOSバックプレーンダイを強固に支持する基板をさらに含む。

30

#### 【0100】

(R)(K)～(M)に記載されたいずれかのディスプレイアセンブリにおいて、基板は、複数のCMOSバックプレーンダイのうちの少なくとも1つへの電気接続を提供する複数のシリコン貫通ビア(TSV)をさらに含む。

#### 【0101】

(S)(K)～(R)に記載されたいずれかのディスプレイアセンブリにおいて、タイルのアレイの各タイルは、CMOSバックプレーンダイ間のギャップを充填し、かつ、CMOSバックプレーンダイを強固に支持するオーバーモールドをさらに含む。

40

#### 【0102】

したがって、図示された実施形態に従って本開示を提供したが、当業者は、これらの実施形態を変更することができ、これらの変更が本開示の範囲内であることを容易に認識するであろう。したがって、当業者は、添付の特許請求の範囲から逸脱することなく、多くの修正を行うことができる。

50

【図面】

【図 1】

【図 2 A】

FIG. 2A

10

【図 2 B】

FIG. 2B

30

【図 2 C】

FIG. 2C

40

50

【図 3 A】

【図 3 B】

10

20

FIG. 3A

FIG. 3B

【図 4】

FIG. 4

【図 5 A】

FIG. 5A

30

40

50

【図 5 B】

【図 5 C】

FIG. 5C

10

20

30

40

【図 5 D】

FIG. 5D

【図 5 E】

FIG. 5E

50

【図 5 F】

FIG. 5F

【図 5 G】

FIG. 5G

【図 5 H】

FIG. 5H

【図 5 I】

FIG. 5I

10

20

30

40

50

【図 5 J】

【図 5 K】

FIG. 5J

10

【図 6 A】

FIG. 6A

20

【図 6 B】

FIG. 6B

30

600b ↗

↗

40

50

【図 7 A】

700a ↗

【図 7 B】

700b ↗

10

20

FIG. 7A

FIG. 7B

【図 7 C】

700c ↗

【図 7 D】

700d ↗

30

40

FIG. 7C

FIG. 7D

50

【図 7 E】

【図 8 A】

FIG. 7E

FIG. 8A

【図 8 B】

FIG. 8B

40

50

---

フロントページの続き

コーポレイテッド内

(72)発明者 ホー , ガン

アメリカ合衆国、9 4 5 3 9 カリフォルニア州、フリーモント、リライアンス・ウェイ、1 2 5

0、ラキシウム・インコーポレイテッド内

審査官 小野 博之

(56)参考文献 米国特許第0 6 0 0 5 6 4 9 ( U S , A )

米国特許出願公開第2 0 1 9 / 0 0 9 6 8 6 4 ( U S , A 1 )

国際公開第2 0 1 9 / 1 2 4 9 5 2 ( WO , A 1 )

国際公開第2 0 1 9 / 1 5 5 2 4 3 ( WO , A 1 )

米国特許出願公開第2 0 0 2 / 0 0 0 1 0 5 1 ( U S , A 1 )

特開2 0 1 8 - 1 8 5 5 1 5 ( J P , A )

特表2 0 2 1 - 5 1 5 2 6 3 ( J P , A )

(58)調査した分野 (Int.Cl. , DB名)

G 0 9 F 9 / 0 0 - 9 / 4 6

H 0 1 L 3 3 / 0 0 - 3 3 / 6 4