(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0114311

(43) 공개일자 2012년10월16일

- (51) 국제특허분류(Int. Cl.)

*H01L 33/44* (2010.01) *H01L 31/0216* (2006.01)

- (21) 출원번호 10-2012-7018892

- (22) 출원일자(국제) 2010년11월30일

심사청구일자 없음

- (85) 번역문제출일자 2012년07월18일

- (86) 국제출원번호 PCT/EP2010/068548

- (87) 국제공개번호 WO 2011/073027

국제공개일자 2011년06월23일

- (30) 우선권주장

10 2009 058 796.9 2009년12월18일 독일(DE)

- (71) 출원인

오스람 옵토 세미컨덕터스 게엠베하

독일 레겐스부르크 라이브니츠슈트라쎄 4 (우:93055)

- (72) 발명자

렐, 알프레드

독일 93142 멕스휘테-하이트호프 비르효브슈트라쎄 19

페러, 미하엘

독일 93077 바트 암바흐 테오도어-헤우스-슈트라쎄 4

(뒷면에 계속)

- (74) 대리인

남상선

전체 청구항 수 : 총 15 항

(54) 발명의 명칭 광전자 소자 그리고 광전자 소자를 제조하기 위한 방법

### (57) 요 약

본 발명은 자동 중에 광을 방출하거나 또는 흡수하기에 적합한 활성 영역(3)을 갖는 적어도 하나의 무기 광전자 활성 반도체 소자(10) 그리고 적어도 하나의 표면 영역(7)에 원자 층 중착에 의해서 제공되고 상기 표면 영역(7)을 밀폐 방식으로(in a hermetically sealing manner) 덮는 밀봉 재료(6)를 구비하는 광전자 소자와 관련이 있다. 본 발명은 또한 광전자 소자를 제조하기 위한 방법과도 관련이 있다.

**대 표 도** - 도1d

(72) 발명자

**슐렝커, 톤만**

독일 93152 니텐도르프 약클베르크 17

**타우츠, 쥐케**

독일 93105 테게른하임 칼-오르프-슈트라쎄 29

**스트라우스, 우베**

독일 93077 바트 압바흐 에리히-캐스트너-슈트라쎄

32

**뮐러, 마르틴**

독일 93170 베른하르트스발트 암 아이헬라케르 20

---

## 특허청구의 범위

### 청구항 1

광전자 소자로서,

작동 중에 광을 방출하거나 또는 흡수하기에 적합한 활성 영역(3)을 갖는 적어도 하나의 무기 광전자 활성 반도체 소자(10)를 포함하며, 그리고

적어도 하나의 표면 영역(7)에, 원자 층 증착에 의해서 제공되고 상기 표면 영역(7)을 밀폐 방식으로(in a hermetically sealing manner) 덮는 밀봉 재료(6)가 제공된,

광전자 소자.

### 청구항 2

제 1 항에 있어서,

상기 반도체 소자(10)가 적어도 하나의 전기 콘택 층(4)을 구비하며, 그리고

상기 밀봉 재료(6)가 상기 콘택 층(4) 또는 상기 콘택 층(4)의 한 부분 영역을 제외한 상기 반도체 소자(10)의 모든 노출 표면을 전체적으로 덮는,

광전자 소자.

### 청구항 3

제 1 항 또는 제 2 항에 있어서,

상기 반도체 소자(10)가 캐리어(11) 상의 조립 면(9)에 제공된,

광전자 소자.

### 청구항 4

제 3 항에 있어서,

상기 밀봉 재료(6)가 상기 반도체 소자(10)의 모든 노출 표면을 덮는,

광전자 소자.

### 청구항 5

제 3 항 또는 제 4 항에 있어서,

상기 반도체 소자(10)가 적어도 하나의 전기 콘택 소자(21)를 통해서 상기 캐리어(11)에 전기적으로 접속되며, 그리고

상기 밀봉 재료(6)가 상기 전기 콘택 소자(21)를 덮는,

광전자 소자.

### 청구항 6

제 3 항 내지 제 5 항 중 어느 한 항에 있어서,

상기 밀봉 재료(6)가 상기 캐리어(11)의 표면(17)의 적어도 한 부분을 덮는,

광전자 소자.

### 청구항 7

제 6 항에 있어서,

상기 밀봉 재료(6)가 상기 캐리어(11)의 전기 접속 영역(22)을 제외한 상기 캐리어(11) 및 반도체 소자(10)의 모든 노출 표면(7, 17)을 전체적으로 덮는,

광전자 소자.

### 청구항 8

제 1 항 내지 제 7 항 중 어느 한 항에 있어서,

상기 반도체 소자(10) 및 밀봉 재료(6)가 하우징 재료(20)에 의해서 적어도 부분적으로 둘러싸인,

광전자 소자.

### 청구항 9

제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

상기 광전자 소자가 다수의 반도체 소자(10)를 구비하며, 그리고

상기 밀봉 재료(6)가 다수의 모든 반도체 소자(10)의 적어도 하나의 표면 영역(7)에 각각 제공된,

광전자 소자.

### 청구항 10

제 1 항 내지 제 9 항 중 어느 한 항에 있어서,

상기 반도체 소자(10)가 상기 적어도 하나의 표면 영역(7)에 적어도 하나의 마이크로 개구(12)를 구비하며, 그리고

상기 밀봉 재료(6)가 상기 마이크로 개구(12)를 밀봉시키는,

광전자 소자.

### 청구항 11

제 10 항에 있어서,

적어도 하나의 마이크로 개구(12)를 갖는 상기 표면 영역(7)이 기판(1) 표면의 부분이고/부분이거나 에피택셜 방식으로 성장된 반도체 층 시퀀스(2)의 층 표면의 부분인,

광전자 소자.

### 청구항 12

제 10 항 또는 제 11 항에 있어서,

상기 반도체 소자(10)가 패시베이션 층(13) 및/또는 성장 보호 층(14)을 구비하며, 그리고

적어도 하나의 마이크로 개구(12)를 갖는 상기 표면 영역(7)이 상기 패시베이션 층(13) 표면의 부분이고/부분이거나 상기 성장 보호 층(14) 표면의 부분인,

광전자 소자.

### 청구항 13

제 1 항 내지 제 12 항 중 어느 한 항에 있어서,

상기 표면 영역(7)이 적어도 부분적으로 차폐된,

광전자 소자.

### 청구항 14

반도체 소자(10)를 구비하는 제 1 항 내지 제 13 항 중 어느 한 항에 따른 광전자 소자를 제조하기 위한 방법으로서,

밀봉 재료(6)를 원자 층 증착에 의해서 반도체 층 결합체(90) 상에 제공하며, 그리고 그 다음에 상기 반도체 층 결합체(90)를 다수의 반도체 소자(10)로 분리시키는, 광전자 소자를 제조하기 위한 방법.

### 청구항 15

반도체 소자(10)를 구비하는 제 1 항 내지 제 13 항 중 어느 한 항에 따른 광전자 소자를 제조하기 위한 방법으로서,

반도체 소자(10)를 캐리어(11) 상에 장착하며, 그리고 그 다음에 밀봉 재료(6)를 원자 층 증착에 의해서 증착하는,

광전자 소자를 제조하기 위한 방법.

## 명세서

### 기술분야

[0001]

본 발명은 광전자 소자 그리고 광전자 소자를 제조하기 위한 방법에 관한 것이다.

### 배경기술

[0002]

발광 다이오드(LED), 단면 방출 레이저(edge emitting laser), 수직 방출 레이저(VCSEL), 레이저-어레이, 포토 다이오드, 태양 전지, 포토 트랜지스터 등과 같은 광전자 반도체 소자들은 조명 기술, 프로젝션, 데이터 저장, 프린팅 기술, 에너지 생성(energy generation) 및 다수의 다른 적용 예에서 키 컴포넌트(key component)로서 사용되는 경우가 점점 증가하고 있다.

[0003]

AlInGaN, InGaAlP 및 AlGaAs와 같은 재료 계를 기본으로 하는 경우에는 방출 또는 겹출 반도체 소자를 위해서 자외선으로부터 적외선까지의 전체 스펙트럼 범위가 커버 될 수 있다. 특히 전술된 반도체 계를 기본으로 하는 광원들은 백열등 또는 할로겐 광원과 같은 경쟁적인 문제 해결 접근 방법들에 대하여 소형화(compactness) 및 긴 수명과 관련하여 여러 가지 장점을 갖는다.

[0004]

예를 들어 LED- 또는 레이저-투영 유닛을 이동 전화기에 또는 투영 스크린의 역광 조명(backlighting) 장치에 접적하는 것과 같은 혁신적인 기술 개발들은 점점 더 작고 특히 더 평평하며 또한 경제적으로 제조될 수 있는 구조적 형상을 요구하고 있다. 이와 같은 요구 사항들과 관련해서 현재의 기술들은 한계에 부닥쳤는데, 그 이유는 시장에서 요구하고 있는 수명이 길고 초소형(ultracompact)인 동시에 경제적으로 제조될 수 있는 반도체 광원들 또는 반도체 수신 장치들은 현재의 통상적인 기술로는 충분히 구현될 수 없기 때문이다.

[0005]

대기 조건 하에서 보호되지 않은 상태로 작동되는 반도체 소자들은 고장률(failure rate)이 상승하는 경향이 있다. 따라서, 산소 및/또는 습기가 반도체 표면에서 상응하는 부품들의 질적 저하(degradation)를 야기한다는 사실이 검사를 통해 입증될 수 있었다.

[0006]

예를 들어 공개문 M. Okayasu 외, "Facet oxidation of InGaAs/GaAs strained quantum-well lasers", J. Appl. Phys., Vol. 69, p. 8346 (1991)에 기재된 바와 같이, 단면 방출 GaAs-레이저에서는 레이저 단면(face t)의 광 유도된 산화가 흡수 손실 그리고 그와 더불어 열적인 가열을 야기하고, 결국에 이와 같은 현상은 레이저 단면의 열적인 파괴("catastrophic optical damage") 그리고 그와 더불어 부품의 고장까지 야기할 수 있다.

[0007]

400 nm 파장 근처에서 방출 범위를 갖는 AlInGaN-레이저에서는, 공개문 V. Kuemmler 외, "Gradual facet degradation of (Al, In)GaN quantum well lasers", Appl. Phys. Lett., Vol. 84(16), p. 2989 (2004) 및 T. Schoedl 외, "Facet degradation of (Al, In)GaN heterostructure laser diodes", Phys. Stat. Sol. (a), Vol. 201(12), p. 2635-2638 (2004)에 기재된 바와 같이, 습기가 있는 상태에서 작동하는 경우에는 부품의 질적 저하가 대폭 증가한다는 사실이 관찰되었다.

[0008]

공개문 T. M. Smeeton 외, "Atomic force microscopy of cleaved facets in III-V-Nitride Laser Diodes grown on free-standing GaN substrates", Appl. Phys. Lett., Vol. 88, 041910 (2006)에 기재된 바와 같이, 원자간 힘 현미경 atomic force microscopy)을 이용한 검사들은 기-III-질화물의 질적으로 저하된 레이저 단면에서 산화물 층이 형성된다는 사실을 검출하였으며, 이때 상기 산화물 층의 두께는 그 아래에 있는 반도체 층의

개별 조성에 의존한다.

[0009] 재료 계 AlGaAs, InGaAlP 및 AlInGaN을 기본으로 하는 LED에서 방해가 되는 외부적인 영향들을 줄이기 위하여, 상기 재료 계들은 일반적으로 전도성 접착제에 의해서 리드 프레임(lead frame) 상에 접착되고 실리콘- 또는 에폭시 수지로 캐스팅 되지만, 이때에는 다양한 문제점들이 고장을 유발할 수 있다. 따라서, 예를 들면 칩- 또는 메사 엣지(mesa edge)에서, 특히 pn-접합부 영역에서 누설 전류 경로가 생성되고, 상기 누설 전류 경로가 정전 방전에 의해서 노화 효과 또는 고장, 더 상세히 말하자면 소위 ESD(ESD: "electrostatic discharge"; 정전 방전)-고장을 야기할 수 있는 위험이 존재한다. 이와 같은 유형의 손상들은 예를 들어 금속 입자들이 전도성 접착제로부터 이동(migration)함으로써 야기될 수 있다.

[0010] 상기와 같은 LED에서의 문제점에 대처하기 위하여, 활성 구역의 임계적인 측면들을 소위 메사 기술로 예치하고 유전체 패시베이션 층을 이용해서 보호하는 경우가 많이 있다. 이 경우에는 중발, 스퍼터링 또는 화학 기상 증착("chemical vapor deposition", CVD)과 같은 코팅 방법들이 사용된다.

[0011] 그러나 통상적으로 사용되는 상기 방법들에 의해서 증착된 층들은 예를 들어 부분적으로 불규칙하게 형성된 급경사의 측면(flank)을 모든 측으로부터 균일하게 변형(reshaping)하는 과정이 상기 방법들에 의해서는 단지 불충분하게만 이루어진다는 단점을 갖는다. 또한, 증착된 층들은 내부에 형성된 잔류 가스, 불순물 또는 내부에 형성된 공백(blank)으로 인해 미세한 공동(cavity)을 갖는 경우가 많다. 이와 같은 패시베이션- 또는 미러 층들의 다공성 구조로 인해 예를 들어 산소 및 습기가 임계적인 반도체 표면에 도달하여 전술된 부품 고장들을 야기할 수 있다.

[0012] 통상적인 재료 계 AlGaAs, InGaAlP 및 AlInGaN을 기본으로 하는 반도체 레이저에서도 일반적으로 비반사 층, 패시베이션 층 또는 유전체 고반사 층들이 민감한 레이저 측면에 제공된다. 일반적으로 이와 같은 코팅은 간행물 T. Mukai 외, "Current status and future prospects of GaN-based LEDs and LDs", Phys. Stat. Sol. (a), Vol. 201(12), p. 2712-2716 (2004) 그리고 S. Ito 외, "AlGaInN violet laser diodes grown on GaN substrates with low aspect ratio", Phys. Stat. Sol. (a), Vol. 200(1), p. 131-134 (2003)에 기재된 바와 같이 코팅 물질의 화학 기상 증착, 중발 또는 스퍼터링에 의해서 이루어진다.

[0013] 레이저 다이오드에서 습기 또는 산소에 의한 고장들을 피하기 위하여, 예를 들어 AlInGaN-레이저 다이오드는 예를 들어 하우징 유형 T038, T056 및 T090과 같은 TO-기반 밀폐형 하우징 안에 보호 가스를 사용하여 패킹(packing) 된다. 이와 같은 방법에서의 단점은 한 편으로는 초과 비용과 연관된 높은 조립 비용이고, 다른 한 편으로는 하우징의 누설 및/또는 하우징 내부의 잔류 습기로 인해 레이저 다이오드의 손상 및 그와 더불어 고장이 방지될 수 없다는 것이다.

[0014] 부품의 안정성을 높이기 위하여 레이저 다이오드를 밀폐 하우징 안에 패킹하는 상기와 같은 비용 집약적이고 대체로 불충분한 조치는, 구조적 형상의 크기와 관련된 제한된 압축성(compactness) 그리고 다른 광학 소자들의 집적화(integration)와 관련된 낮은 유연성(flexibility)이 상기와 같은 조치와 연관되어 있다는 추가의 중대한 단점을 갖는다.

### 발명의 내용

[0015] 본 발명의 특정 실시 예들과 관련된 적어도 한 가지 과제는, 전술된 단점들이 피해질 수 있는 광전자 소자를 제공하는 것이다. 특정 실시 예들과 관련된 한 가지 추가의 과제는 광전자 소자를 제조하기 위한 방법을 제시하는 것이다.

[0016] 상기 과제들은 독립 특허 청구항들의 특징들을 갖는 대상 및 방법에 의해서 해결된다. 상기 대상 및 방법의 바람직한 실시 예들 및 개선 예들은 종속 청구항들에 특징으로 기재되어 있고, 또한 아래의 상세한 설명 및 도면들로부터 드러난다.

[0017] 적어도 한 가지 실시 예에 따라, 광전자 소자는 특히 작동 중에 광을 방출하거나 또는 흡수하기에 적합한 활성 영역을 갖는 적어도 하나의 무기 광전자 활성 반도체 소자를 구비한다. 상기 반도체 소자는 적어도 하나의 표면 영역을 구비하고, 상기 표면 영역에는 원자 층 증착에 의해서 제공되고 상기 표면 영역을 밀폐 방식으로(in a hermetically sealing manner) 덮는 밀봉 재료가 도포 되어 있다.

[0018] 상기 실시 예에서 그리고 이하에서 '광'은 특히 자외선 내지 적외선 스펙트럼 범위의 전자기 방사선, 다시 말해 예를 들어 오로지 가시 스펙트럼 범위에만 해당하지 않는 전자기 방사선을 의미한다.

[0019]

상기 무기 광전자 활성 반도체 소자는 특히 작동 중에 광을 방출할 수 있고, 이 목적을 위해 발광 다이오드(LED), 단면 방출 반도체 레이저, 수직 방출 반도체 레이저(VCSEL), 레이저-어레이 또는 이와 같은 부품들로 이루어진 다수의 소자 또는 이와 같은 부품들의 조합을 구비할 수 있거나 또는 상기 소자들 중에 한 가지 소자일 수 있다. 대안적으로 또는 추가로 상기 무기 광전자 활성 반도체 소자는 작동 중에 광을 흡수할 수 있고, 이 목적을 위해 포토 다이오드, 태양 전지, 태양 전지 패널, 포토 트랜지스터 또는 이와 같은 부품들로 이루어진 다수의 소자 또는 이와 같은 부품들의 조합을 구비할 수 있거나 또는 상기 소자들 중에 한 가지 소자일 수 있다. 이 목적을 위하여 상기 반도체 소자는 재료 그룹 AlGaAs, InGaAlP, AlInGaN 또는 II-VI-화합물 반도체 계 또는 기타의 반도체 재료로부터 선택된 2성분, 3성분 또는 4성분의 III-V-화합물 반도체 계로 이루어진 하나 또는 다수의 작용기성 반도체 층 시퀀스를 구비할 수 있다. 상기 반도체 층 시퀀스는 광을 방출하거나 또는 광을 검출하는, 예컨대 pn-접합부, 이중 헤테로 구조물, 단일-양자 웰 구조물(SQW-구조물) 또는 다중-양자 웰 구조물(MQW-구조물)과 같은 적어도 하나의 활성 영역 그리고 예컨대 금속 층과 같은 전기 콘택 층을 구비할 수 있다. 이와 같은 반도체 층 시퀀스 및 구조물들은 선행 기술에 공지되어 있기 때문에 본 출원서에서는 더 이상 상세하게 기술되지 않는다.

[0020]

밀봉 재료가 도포된 표면 영역은 특히 예를 들어 반도체 레이저로서 구현된 반도체 소자의 경우에는 레이저 단면을 포함할 수 있거나 또는 주변 환경적인 영향 및 기타의 노화 효과에 대하여 특히 민감한 노출된 LED의 pn-접합부, 레이저 다이오드 또는 포토 다이오드도 포함할 수 있다.

[0021]

상기 밀봉 재료에 의해서는 표면 영역이 밀폐 방식으로 덮이고, 그로 인해 밀봉되고 캡슐화된다. 이와 같은 내용은 예를 들어 습기 및/또는 산소가 캡슐화 장치 내부로 침투할 수 없다는 것을 의미할 수 있다. 특히 상기 밀봉 재료는 반도체 소자의 표면 영역 상에서 밀폐형의 밀봉 층을 형성할 수 있으며, 상기 밀봉 층은 습기 및/또는 산소가 주변 대기로부터 표면 영역을 거쳐서 반도체 소자 내부로 침투하지 않도록 그리고 반도체 소자가 자체 능률 및/또는 조성에 있어서 악영향을 받거나 손상되지 않도록 반도체 소자를 습기 및/또는 산소로부터 보호한다. 습기 및/또는 산소에 대하여 보호해주는 역할 이외에 상기 밀봉 재료는 또한 다른 주변 영향들 그리고 특히 추가의 원자 또는 분자 물질들에 대한 효과적인 배리어(barrier)에 의한 보호 작용도 제공해줄 수 있다.

[0022]

또한, 원자 층 증착에 의해서 제공된 밀폐형의 밀봉 재료는 예컨대 CVD, 스퍼터링 또는 진공 증착과 같은 다른 방법들에 의해서 제공된 층들과 비교할 때 두께 및 재료가 대등한 경우에는 상승 된 기계적인 강도를 가질 수 있고, 그와 더불어 예를 들어 스크래치와 같은 기계적인 작용에 대한 보호 효과도 높여줄 수 있다.

[0023]

원자 층 증착("atomic layer deposition", ALD) 방법에서는 가스 형태로 제공된 두 가지 이상의 출발 물질 또는 출발 화합물("전구체(percursor)")의 화학 반응에 의해서 밀봉 재료로부터 반도체 소자의 하나의 표면상에 또는 표면 영역에 층이 형성될 수 있다. 종래의 CVD-방법과 비교할 때 원자 층 증착 방법에서는 출발 화합물들이 주기적으로 차례로 반응 챔버 안으로 유입된다. 이 경우에는 우선 두 개 이상의 가스 형태의 출발 화합물 중에 제 1 화합물이 반응 챔버의 용적에 공급되고, 상기 용적 내에서 반도체 소자가 준비된다. 상기 제 1 출발 화합물은 적어도 하나의 표면 영역에서 흡착될 수 있다. 특히 이 경우에는 상기 제 1 출발 화합물의 문자가 불규칙적으로 그리고 장거리 질서(long range order) 없이 표면 영역 상에서 흡착되어 적어도 부분적으로 비정질의 커버가 형성되는 경우가 바람직할 수 있다. 적어도 하나의 표면 영역이 제 1 출발 화합물로 바람직하게는 완전히 또는 거의 완전히 커버 된 후에는 상기 두 개 이상의 출발 화합물 중에 제 2 출발 화합물이 공급될 수 있다. 상기 제 2 출발 화합물은 표면 영역에서 흡착된 제 1 출발 화합물과 반응할 수 있으며, 이와 같은 반응에 의해서는 상기 밀봉 재료의 아단분자층(submonolayer) 또는 최대 하나의 단분자층이 형성될 수 있다. 그 다음에 제 1 출발 화합물이 재차 공급되는데, 이때 제 1 출발 화합물은 상기 형성된 아단분자층 또는 단분자층 상에서 그리고 경우에 따라서는 여전히 상기 적어도 하나의 표면 영역의 노출된 영역들 상에서 증착될 수 있다. 제 2 출발 화합물을 추가로 공급함으로써 추가의 아단분자층 또는 단분자층이 제조될 수 있다. 상기 출발 화합물들의 가스 유입구들 사이에서 반응 챔버가 세척용 가스, 특히 예컨대 아르곤과 같은 불활성 가스로 세척됨으로써, 결과적으로 출발 화합물이 각각 유입되기 전에는 바람직하게 이전의 출발 화합물이 더 이상 반응 챔버 내부에 존재하지 않게 된다. 이와 같은 방식에 의해서는 부분 반응들이 서로 명확하게 분리되어 적어도 하나의 표면 영역에 한정될 수 있다. 따라서, 원자 층 증착의 한 가지 중요한 특징은 부분 반응이 자동으로 한정된다는 특성인데, 이와 같은 특성이 의미하는 바는 한 가지 부분 반응의 출발 화합물은 자기 자신과는 또는 자기 자신의 배위자(ligand)와는 반응을 하지 않는다는 것이다, 이와 같은 사실은 시간의 길이 및 가스량이 임의적인 경우에도 한 가지 부분 반응의 층 성장을 적어도 하나의 표면 영역에서의 밀봉 재료의 최대 하나의 단분자층에 한정시킨다. 방법 파라미터 및 반응 챔버에 따라서 그리고 밀봉 재료 또는 출발 화합물들의 재료에 따라서 수 밀리 초내지 수 초 사이에서 사이클이 지속 될 수 있으며, 이 경우에는 사이클당 약 0.1 내지 약 3 옹스트롬(angstrom)

두께의 층이 밀봉 재료로부터 발생 될 수 있다.

[0024] 상기 밀봉 재료는 원자 층 중착에 의해서 1 나노미터 이상의 두께로, 바람직하게는 5 나노미터 이상의 두께로 그리고 특히 바람직하게는 10 나노미터 이상의 두께로 그리고 500 nm 이하의 두께로 제공될 수 있다. 특히 상기 밀봉 재료는 200 나노미터 이하의 두께, 바람직하게는 100 나노미터 이하의 두께 그리고 특히 바람직하게는 50 나노미터 이하의 두께를 가질 수 있다. 이와 같은 내용은 상기 밀봉 재료가 1개 이상의 단분자층, 바람직하게는 10개 이상의 단분자층 그리고 5,000개 이하의 단분자층으로 이루어진 하나의 층을 형성한다는 것을 의미할 수 있다. 밀봉 재료를 제공하는 높은 밀도 및 우수한 층 품질에 의해서는, 상기 밀봉 재료 아래에 놓인 반도체 소자의 적어도 하나의 표면 영역을 위해서 습기 및/또는 산소에 대한 효과적인 보호 작용을 보증해줄 수 있을 정도의 두께가 충분할 수 있다. 밀봉 재료의 두께가 얇으면 얇을수록, 밀봉 재료로부터 층을 제조하기 위한 시간 및 재료 비용은 그만큼 더 줄어들게 되며, 그로 인해 높은 경제성이 나타날 수 있게 된다. 밀봉 재료로 이루어진 층이 두꺼우면 두꺼울수록, 밀봉 재료는 예를 들어 기계적인 손상에 대하여 그만큼 더 강하게 저항할 수 있으며, 그리고 상기 밀봉 재료의 밀폐식 캡슐화 특성의 안정성도 그만큼 더 커질 수 있다.

[0025] 전술된 바와 같이 제공된 그리고 적어도 하나의 표면 영역을 덮는 밀봉 재료는 상기와 같은 방식으로 형성된 밀봉 층의 층 두께가 단지 반응 사이클의 개수에만 의존한다는 장점을 가지며, 이와 같은 장점은 층 두께의 정확하고 간단한 제어를 가능하게 한다. 또한, 바람직하게는 출발 화합물들을 반응 챔버에 공급시켜주는 개별 가스 흐름의 균일성에 대한 요구 수준도 단지 낮게만 나타남으로써, 결과적으로 밀봉 재료는 매우 바람직하게 특히 크기가 큰 표면들에도 균질로 그리고 균일하게 제공될 수 있다. 출발 화합물들을 별도로 공급하고 주입(dosing)함으로써 반응들은 기체 상태에서 이미 방해를 받게 되고, 그 결과 예를 들어 진공 중착 또는 CVD와 같은 방법에서 사용될 수 없는 고반응성 출발 화합물들도 사용될 수 있게 된다. 전술된 순서 및 고정된 주입량에 의해서는 각각의 반응 단계마다 충분한 시간이 제공되며, 이와 같은 사실은 바람직하게 프로세스 온도가 상대적으로 낮은 경우에도 밀봉 재료로부터 고순도의 층들을 가능하게 한다. 또한, 제 1 출발 화합물의 흡착 과정 및 후속하는 제 2 출발 화합물과의 화학 반응이 가스에 접근할 수 있는 전체 표면에서 이루어짐으로써, 결과적으로 상기 표면은 실제로 자체의 구조적인 상태 및 상황에 따라 존재하는 입자들, 소위 핀-홀(Pin-Holes)과 같은 개구들 그리고 구멍들과 무관하게 연속하는 반응 사이클에 의해서 점차 변형되어서 밀봉된다.

[0026] 또한, 상기 밀봉 재료는 스퍼터링, 기상 중착 또는 CVD와 같은 다른 방법들에 의해서 제조된 층들과 비교할 때 적어도 하나의 표면 영역에서 결함 없이 제조될 수 있다. 이와 같은 내용이 의미하는 바는, 예를 들어 습기 및/또는 산소 및/또는 다른 원자 혹은 분자 물질들이 밀봉 재료를 거쳐서 적어도 하나의 표면 영역으로 이동할 때에 통과할 수 있는 소위 핀-홀 또는 마이크로 채널(microchannel)이 밀봉 재료 내에 전혀 존재하지 않는다는 것이다.

[0027] 상기 밀봉 재료는 바람직하게 전기 절연성이고, 시각적으로 투명하며, 그리고 예를 들어 알루미늄, 규소, 티타늄, 지르코늄, 탄탈륨 및 하프늄으로부터 선택된 하나 또는 다수의 원소로 구성된 산화물, 질화물 또는 옥시나트라이드를 함유할 수 있다. 특히 밀봉 재료는 다음과 같은 물질들 중에 하나 또는 다수의 물질을 함유할 수 있다: Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, TiO<sub>2</sub>, ZrO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>. 출발 화합물로서는 예를 들어 전술된 물질들의 수소화물 또는 유기 금속 화합물이 적합하며, 그리고 예를 들어 암모니아, 소기(laughing gas) 또는 물은 산소 또는 질소를 위한 출발 화합물로서 적합하다.

[0028] 밀봉 재료에 의해서 반도체 소자의 가급적 효과적인 캡슐화에 도달하기 위해서는, 상기 밀봉 재료를 덮는 적어도 하나의 표면 영역이 상기 반도체 소자의 하나 또는 다수의 상부면, 하부면 및/또는 측면을 둘러싸는 경우가 바람직할 수 있다.

[0029] 또한, 반도체 소자는 이 반도체 소자를 전기적으로 접속하기에 적합한 적어도 하나의 전기 콘택 층을 구비할 수 있다. 상기 전기 콘택 층은 예를 들어 하나 또는 다수의 금속 층을 포함하거나 또는 이와 같은 금속 층 자체일 수 있다. 이때 적어도 하나의 표면 영역은 상기 콘택 층 또는 상기 콘택 층의 한 부분 영역을 제외한 반도체 소자의 모든 노출된 반도체 소자의 표면을 둘러쌀 수 있다. 다른 말로 표현하자면, 이때 밀봉 재료는 상기 콘택 층 또는 상기 콘택 층의 한 부분 영역을 제외한 반도체 소자의 모든 노출된 표면을 전체적으로 덮을 수 있다. 그럼으로써 반도체 소자의 노출된 표면의 밀봉 및 캡슐화가 이루어질 수 있게 되며, 이 경우 상기 전기 콘택 층은 밀봉 재료를 제공한 후에도 계속해서 전기적으로 콘택팅 될 수 있다.

[0030] 본 실시 예에서 그리고 이하에서 노출된 표면으로서는, 광전자 소자가 완성된 후에 예를 들어 주변으로부터 산소 및 습기와 같은 원자 또는 분자 형태의 물질이 표면에 도달할 수 있는 형태로 주변과 콘택 할 수 있는 그러한 표면 및 표면 영역이 언급된다. 그렇기 때문에 본 경우에는 밀폐되지 않은 층, 말하자면 산소- 및/또는 물

을 통과시킬 수 있는 플라스틱 층에 의해서 덮인 표면 또는 표면 영역도 노출이라는 개념에 해당할 수 있다. 특별히 광전자 소자가 캐리어를 구비하고, 표면 또는 표면 영역이 상기 캐리어 상에 반도체 소자를 조립할 목적으로 이용됨으로써 상기 표면 또는 표면 영역이 조립 면으로서 형성된 경우에, 상기 표면 및 표면 영역은 본 경우에 사용된 의미에서의 노출에 해당하지 않는다.

[0031] 특히 조립 면을 갖는 반도체 소자가 캐리어 상에 제공될 수 있다. 상기 캐리어는 예를 들어 히트 싱크(heat sink), 프린트 회로 기판, 리드 프레임, 하우징 몸체 또는 이들로부터 조합된 형태의 부품을 구비하거나 또는 이와 같은 부품일 수 있다. 상기 반도체 소자는 조립 면에 의해서 캐리어 상에 기계적으로, 예를 들면 납땜, 양극 본딩 또는 접착 방법을 이용하여 장착될 수 있다. 추가로 상기 반도체 소자는 조립 면을 통해 캐리어와도 전기적으로 접속될 수 있으며, 이 경우 상기 조립 면은 추후에 추가로 전기 콘택 층으로서 형성될 수도 있다.

[0032] 캐리어 상에 제공된 반도체 소자에서는 밀봉 재료에 의해 밀폐식으로 덮인 적어도 하나의 표면 영역이 반도체 소자의 모든 노출된 표면, 특히 조립 면 외부에 있는 모든 표면을 둘러쌀 수 있음으로써, 상기 밀봉 재료는 반도체 소자의 모든 노출된 표면을 덮게 된다. 본 실시 예에서는 반도체 소자가 조립 면을 제외한 모든 측에서 밀봉 재료에 의해 둘러싸여 있음으로써, 반도체 소자의 효과적인 캡슐화가 가능해진다.

[0033] 또한, 반도체 소자는 추가로 전기 콘택 소자를 통해서도 캐리어에 접속될 수 있다. 이 목적을 위하여 반도체 소자는 조립 면과 상이한 표면에 전기 콘택 층을 구비할 수 있으며, 상기 전기 콘택 층에는 전기 콘택 소자가 접속되어 있다. 상기 전기 콘택 소자는 예를 들어 본딩 와이어 또는 금속 층일 수 있다. 상기 전기 콘택 소자는 또한 특히 바람직하게 반도체 소자의 전기 콘택 층과 함께 밀봉 재료에 의해서 덮일 수 있다.

[0034] 또한, 상기 밀봉 재료는 캐리어 표면의 적어도 한 부분을 덮을 수도 있다. 특히 이 경우에는 밀봉 재료가 캐리어의 표면으로부터 반도체 소자의 적어도 하나의 표면 영역까지 연결된 상태로 연장됨으로써, 결과적으로 상기 밀봉 재료는 반도체 소자와 캐리어 사이에 있는 조립 영역도 덮을 수 있게 된다.

[0035] 또한, 상기 캐리어는 광전자 소자를 예를 들어 제어 회로 또는 전원에 접속시킬 수 있는 전기 접속 영역을 구비할 수도 있다. 이때에는 밀봉 재료가 캐리어의 접속 영역을 제외한 반도체 소자 및 캐리어의 모든 노출된 표면을 덮음으로써, 결과적으로 캐리어는 반도체 소자와 함께 캐리어의 접속 영역을 제외한 모든 표면에서 밀봉 재료에 의해 밀폐식으로 덮이게 된다.

[0036] 또한, 상기 반도체 소자 및 밀봉 재료는 하우징 재료에 의해서 적어도 부분적으로 둘러싸일 수 있다. 상기 하우징 재료는 예를 들어 플라스틱일 수 있고, 특히 투명한 플라스틱일 수 있다. 밀봉 재료가 반도체 소자의 적어도 하나의 표면 영역을 밀폐식으로 덮기 때문에, 바람직하게 하우징 재료 자체는 밀폐형이 아닐 수 있으며, 그리고 오로지 다른 관점들에 따라서만, 말하자면 시각적인 특성들 및/또는 기계적인 특성들에 따라서만 선택될 수 있다. 특히 추가적으로는 캐리어도 하우징 재료에 의해 적어도 부분적으로 변형될 수도 있다.

[0037] 또한, 광전자 소자는 다수의 무기 광전자 활성 반도체 소자 그리고 추가로 또는 대안적으로는 하나 또는 다수의 추가 전자 소자를 구비할 수도 있다. 이때 밀봉 재료는 다수의 반도체 소자 및/또는 전자 소자 중에 각각 하나의 반도체 소자 및/또는 전자 소자의 적어도 하나의 표면 영역에 각각 제공될 수 있으며, 그리고 이때 상기 다수의 반도체 소자 및/또는 전자 소자는 공동으로 캡슐화될 수 있다. 특히 상기 다수의 반도체 소자 및/또는 추가의 전자 소자는 캐리어 상에서 밀봉 재료로 이루어진 상호 연결된 상태의 폐쇄된 층에 의해 덮여서 캡슐화될 수 있다. 그 대안으로서 상기 밀봉 재료로 이루어진 상호 연결된 상태의 층은 밀봉 재료의 제공 후에도 전기적인 콘택팅을 가능하게 하기 위하여 캐리어 상에서 상기 반도체 소자의 전기 콘택 층 또는 전기 접속 영역에 걸쳐 개구들을 가질 수 있다.

[0038] 상기 반도체 소자는 또한 적어도 하나의 표면 영역에 적어도 하나의 마이크로 개구를 가질 수도 있다. 이와 같은 마이크로 개구는 예를 들어 결정 구조 안에 있는 소위 핀-홀, 마이크로 채널, 기공 또는 전위, 말하자면 나사 전위(screw dislocation)에 의해서 표면 영역에 접하도록 형성될 수 있다. 이와 같은 마이크로 개구들 또는 가늘고 긴 홀들은 다양한 이유에서 반도체 소자를 제조할 때에 생성되기 때문에 기술적으로 피할 수 없는 경우가 많은데, 다시 말하자면 에피택셜 방식으로 제공된 층들과 성장 기판 사이에서 나타나는 또는 에피택셜 방식으로 제공된 다양한 층들 사이에서 나타나는 불완전한 격자 매큕 때문에 피할 수 없는 경우가 많다. 기판도 제조와 관련하여 마이크로 개구들을 가질 수 있고, 예를 들어 마이크로 채널들에 의해서 관통될 수 있다. 반도체 소자 내에 있는 이와 같은 마이크로 개구들은 종래의 소자들에서는 고장의 위험을 증가시키는데, 그 이유는 상기 마이크로 채널들을 통해 유해한 가스 또는 도편트 또는 금속까지도 반도체 소자 내부로 또는 상기 반도체 소자 내부에서 예를 들어 활성 영역 내부로 이동하여 차단 전류의 상승 또는 노화에 의한 고장을 야기할 수 있기

때문이다. 마이크로 개구들을 갖는 적어도 하나의 표면 영역에 있는 밀봉 재료는 상기 마이크로 개구들을 밀봉할 수 있고, 그럼으로써 상기 마이크로 개구들 내부에서 원자- 또는 분자 이동을 방지할 수 있다. 이와 같은 상황은 바람직하게 원자 층 증착에 의하여 금경사의 측면들 및 홈들에서도, 그리고 특히 개구 크기 대 깊이의 비율이 1:100까지 이르고 채널 또는 기공의 가장 깊은 점에서도 개구 영역에 있는 표면에서와 대등한 두께로 층이 증착될 수 있는 채널 또는 기공에서도 밀봉 재료의 균질의 증착이 이루어질 수 있음으로써 가능할 수 있다. 특히 전술된 바와 같이, 적어도 하나의 마이크로 개구를 갖는 표면 영역은 기판의 한 표면의 부분이거나 또는 에피택셜 방식으로 성장된 층의 부분일 수 있다.

[0039] 또한, 반도체 층 시퀀스는 패시베이션 층 및/또는 성장 보호층을 구비할 수도 있다. 이때 적어도 하나의 마이크로 개구를 갖는 표면 영역은 밀봉 재료에 의해서 밀폐식으로 밀봉되는 상기 패시베이션 층 및/또는 성장 보호층의 한 표면의 부분일 수 있다.

[0040] 패시베이션 층은 높은 기공도(porosity)를 갖는 경우가 많고, 마이크로 채널을 구비하는 경우도 종종 있는데, 그 원인은 예를 들어 코팅 프로세스에서 코팅될 입자의 노출된 평균적인 광로 길이(optical path length)가 완전한 패킹 밀도(packing density)를 형성하기에는 지나치게 짧은 경우에 패시베이션 층 자체를 제공하기 위해서 사용되는 코팅 방법에 있을 수 있다. 또한, 코팅 캠버 내에 있는 산소와 같은 잔류 가스도 패시베이션 층 내에서 다공성 구조물의 증착을 야기할 수 있다. 패시베이션 층 내에서 반도체 소자의 측면에 그리고/또는 광 결합 해제면에 혹은 레이저 측면에 있는 훌들 또는 마이크로 개구들은 금속의 이동 위험으로 인해 높은 고장 가능성 을 내포하고 있는데, 그 이유는 이와 연관된 필드 상승(field enhancement)이 작동 중에 반도체 소자의 파괴를 야기할 수 있기 때문이다. 또한, 마이크로 개구들에 의해서 형성되는 상기와 같은 공동에 의해서는 습기, 산소 및 다른 유해 가스들이 반도체 소자의 표면에 도달하여 예를 들어 소자 전압의 감소 또는 광학적인 파워의 저하를 야기할 수도 있다. 패시베이션 층 상에 있는 밀봉 재료에 의해서 상기와 같은 위험들이 피해질 수 있다.

[0041] 성장 보호층은 예를 들어 에피택셜 방식의 과도 성장에 의해서 반도체 소자의 반도체 층 시퀀스의 구조화에 적합할 수 있으며, 그로 인해 바람직하게는 자기 정렬 형태의 구조물들이 제조될 수 있게 된다. 따라서, 예를 들어 최적의 깊이를 갖는 가늘고 긴 레이저 브리지는 에피택셜 방식의 성장이 단지 규정된 층까지만 실시됨으로써 그리고 상기 브리지에 적합한 개구를 갖는 구조화된 성장 보호층을 제공한 후에 상기 개구 내부에서 성장이 계속 이루어짐으로써 제조될 수 있다. 상기 성장 보호층이 마이크로 개구를 가지면, 상기 마이크로 개구 내에서는 조절되지 않은 결정 성장이 야기될 수 있으며, 이 경우에 소위 기생 결정들은 바람직하지 않은 변형 가능성, 누설 전류 및 소자의 고장을 결과로 야기할 수 있다. 성장 보호층 상에 있는 밀봉 재료에 의해서 상기와 같은 위험이 피해질 수 있다.

[0042] 표면 영역은 또한 적어도 부분적으로 차폐될 수도 있다. 이와 같은 내용이 의미할 수 있는 사실은, 선행 기술에서 통상적으로 사용되는 지향성 적층 방법, 예컨대 진공 증착 또는 스퍼터링과 같은 방법을 실시하기 위해서 상기 표면 영역에 직접적으로 접근하는 것이 불가능하다는 것이다. 그렇기 때문에 상기와 같은 방법들에서는 구조적으로 차폐된 영역들은 전혀 코팅이 되지 않거나 또는 아주 얇게만 코팅된다. 특히 상기 표면 영역은 예를 들어 표면의 연장 평면을 따라서 돌출부 또는 함몰부, 다시 말하자면 버섯 구조물 또는 피크(peak)에 있는 쇄기 구조물을 갖는, 반도체 소자의 표면에 있는 구조물의 부분일 수 있다. 또한, 차폐된 영역은 공동 또는 갭(gap)에 의해서도 형성될 수 있다. 전술된 원자 층 증착에서의 처리 과정에 의해서는 밀봉 재료가 균질로 그리고 균일한 두께로 상기와 같은 차폐된 표면 영역에 제공될 수 있는데, 그 이유는 상기 방법에 의해서는 코팅될 구조물의 또는 코팅될 반도체 소자의 표면 영역의 구조와 상관없이, 특히 가늘고 긴 형태의 갭 및 공동 내에서도 밀봉 재료의 균일한 제공이 가능하기 때문이다. 이와 같은 장점들은 칩 프로세스에서, 다시 말해 처리가 끝난 반도체 소자의 웨이퍼 결합 과정에서 밀봉 재료를 제공할 때에, 반도체 소자들을 분리할 때에 그리고 반도체 소자들을 장착할 때에 나타날 수 있다.

[0043] 무기 광전자 활성 반도체 소자를 제조하기 위하여 반도체 웨이퍼가 준비될 수 있으며, 상기 반도체 웨이퍼 상에서는 활성 영역을 갖는 반도체 층 시퀀스가 에피택셜 방식으로 증착된다. 상기 반도체 층 시퀀스에는 또한 전기 콘택 층도 제공될 수 있다. 또한, 상기 반도체 층 시퀀스는 예청에 의해서 개별 영역들로 구조화될 수 있으며, 상기 영역들은 개별적으로 분리된 후에 그리고 상기와 같이 형성된 반도체 층 결합체로부터 해체된 후에 반도체 소자를 형성하게 된다. 아직까지 개별적으로 분리되지 않은 반도체 소자의 상기와 같은 형태의 반도체 층 결합체는 웨이퍼 결합체로서도 표기된다.

[0044] 상기 실시 예들에 따른 그리고 하나 또는 다수의 전술된 특징을 갖는 반도체 소자를 구비하는 광전자 소자를 제조하기 위한 한 가지 방법에서, 반도체 층 결합체는 제일 먼저 소수의 반도체 소자로 분리되는데, 상기 소수의

반도체 소자 상에는 추후에 원자 층 증착에 의해서 밀봉 재료가 제공된다.

[0045] 상기 실시 예들에 따른 그리고 하나 또는 다수의 전술된 특징을 갖는 반도체 소자를 구비하는 광전자 소자를 제조하기 위한 추가의 한 가지 방법에서, 밀봉 재료는 원자 층 증착에 의해서 반도체 층 결합체 상에 제공되며, 그 다음에 상기 반도체 층 결합체가 다수의 반도체 소자로 분리된다. 그럼으로써 각각의 반도체 소자는 분리 직후에 이미 표면 영역에 밀봉 재료를 갖게 된다.

[0046] 반도체 층 결합체로서는 예를 들어 전술된 웨이퍼 결합체가 사용될 수 있다. 반도체 층 시퀀스의 성장 후에 그리고/또는 에칭 단계 후에는 웨이퍼 결합체 내에 있는 표면 영역들이 노출될 수 있으며, 상기 표면 영역들은 밀봉 재료의 제공에 의해서 보호되고 밀봉될 수 있다. 웨이퍼 결합체를 분리하기 전에 예를 들어 LED, 레이저 다이오드 또는 포토 다이오드와 같은 광전자 활성 반도체 소자의 민감한 표면들 그리고 표면 영역들이 밀봉 재료의 제공에 의해서 보호될 수 있다. 밀봉 재료를 제공한 후에는 사전에 이미 임계 표면에서 밀봉된 반도체 소자들이 분리 공정에 의해서, 예를 들면 소잉(sawing), 밀링(milling) 또는 에칭에 의해서 얻어질 수 있다.

[0047] 또한, 웨이퍼 결합체는 분리 전에 예를 들어 추후의 반도체 소자를 위한 히트 싱크 또는 전술된 다른 캐리어를 포함하는 캐리어 결합체 상에 제공될 수도 있다. 그 다음에 웨이퍼 결합체 내부에 밀봉 재료가 제공될 수 있고, 추후의 반도체 소자를 형성하는 개별 영역들이 의도한 바대로 측정되고 테스트 될 수 있다. 그 후에 전체 시스템이 개별화될 수 있으며, 이때 상기 개별화 과정에 의해서 이미 캐리어 상에 장착되어 있고 밀봉 재료가 제공된 반도체 소자들이 얻어질 수 있다. 광전자 소자를 제조하기 위한 방법의 범위 안에 있는 상기와 같은 소위 일괄 처리(batch processing; 배치 프로세싱)에 의해서는, 다수의 광전자 소자를 특히 경제적으로 제조할 수 있게 되는데, 그 이유는 개별 반도체 소자들을 처리하는 작업이 최소로 줄어들 수 있기 때문이다.

[0048] 반도체 층 결합체로서는 또한 예를 들어 소위 레이저 다이오드의 바아(bar) 결합체가 사용될 수도 있다. 이때 웨이퍼 결합체 내부에서 제조된 반도체 층 시퀀스는 캡 표면에서 레이저 측면을 형성하기에 적합하도록 복수 개의 바아로 조개진다. 그 다음에 상기 레이저 측면 상에 밀봉 재료가 증착될 수 있다. 웨이퍼 결합체 내에서 레이저 측면들이 이미 전식으로 에칭된 경우에는, 상기 레이저 측면들을 전술된 바와 같이 웨이퍼 결합체 내부에서 사전에 미리 밀봉 재료로 코팅하는 것도 가능할 수 있다.

[0049] 상기 실시 예들에 따른 그리고 하나 또는 다수의 전술된 특징을 갖는 반도체 소자를 구비하는 광전자 소자를 제조하기 위한 추가의 한 가지 방법에서, 반도체 소자는 캐리어 상에 장착된다. 그 다음에 밀봉 재료가 원자 층 증착에 의해서 증착된다. 이때 캐리어는 히트 싱크, 하우징 부품, 리드 프레임 또는 이들 부품들의 조합을 포함하거나 또는 이와 같은 부품들 자체일 수 있다. 반도체 소자가 또한 전기적으로 캐리어 상에 접속되는 경우, 예를 들어 조립 면을 형성하는 전기 콘택 층에 의해서 그리고/또는 전기 콘택 소자에 의해서, 다시 말하자면 전술된 바와 같은 금속 층 또는 본딩 와이어에 의해서 캐리어 상에 접속되는 경우도 특히 바람직할 수 있다. 이 경우에는 바람직하게 효과적인 캡슐화 및 밀봉 결과에 도달하기 위하여 반도체 소자의 모든 노출 표면이 캐리어 표면의 적어도 한 부분과 함께 그리고 경우에 따라서는 전기 콘택 소자와 함께 밀봉 재료로 덮일 수 있는데, 그 이유는 그로 인해 밀봉 단계에서 반도체 소자의 모든 임계적인 경계면 및 표면, 예컨대 측면, 측방 에지 및/또는 노출된 칩 표면이 동시에 보호될 수 있기 때문이다. 이 경우에는 예를 들어 마스킹 기술을 이용한 본딩 또는 납땜에 의해서 반도체 소자를 전기적으로 접속하기 위한 상응하는 윈도우를 제공할 필요가 없으며 그리고/또는 예를 들어 에칭에 의해서 밀봉 재료를 제공한 후에 재차 노출시킬 필요가 없다는 것도 특히 바람직한데, 그 이유는 전기적인 콘택팅이 이미 이루어졌기 때문이다.

[0050] 본 출원서에 기재된 무기 광전자 활성 반도체 소자는 원자 층 증착에 의해 제공된 밀봉 재료에 의하여 주변 영향에 대하여 저항할 수 있게 되고, 따라서 예를 들어 스크래치와 같은 기계적인 부하, 습기 및/또는 산소와 같은 유해 가스에 대해서도 보호될 수 있다. 이와 같은 저항 및 보호 상황은 본 출원서에 기재된 방법에 의해서 바람직하게 경제적으로 실현될 수 있다. 그럼으로써 경제적이고, 혁신적이며, 초소형이고, 노화에 안정적인 광전자 소자가 가능해질 수 있다.

[0051] 특히 광전자 소자 그리고 이와 같은 광전자 소자를 제조하기 위한 방법의 전술된 실시 예들에서는, 원자 층 증착에 의해 제공된 밀봉 재료로 인하여 선행 기술에서 통상적으로 사용되던 보호 가스로 채워진 하우징이 생략될 수 있으며, 그로 인해 한 편으로는 상당한 비용 절감 잠재성에 도달할 수 있게 되고, 다른 한 편으로는 하우징 내부에 남아 있는 잔류 습기 또는 누설과 같은 소자를 파괴하는 여러 원인(source of errors)을 예방할 수 있게 된다. 또한, 보호 가스 밀봉 과정의 생략으로 인해 개별 적용 예와 관련하여 고도의 유연성을 제공해주는 혁신적인 새로운 구조적 형상도 가능해질 수 있다. 특별히 예를 들어 이동 전화기 안에 투영 레이저로서 또는 투영 유닛을 역광 조명할 목적으로 장착되기에 적합할 수 있는 극도로 콤팩트하고 평탄한 구조적 형상을 갖는 광전자

소자가 가능해질 수 있다.

[0052] 추가의 장점들 그리고 바람직한 실시 예들 몇 개선 예들은 아래에서 도 1a 내지 도 6e와 관련하여 기술된 실시 예들로부터 드러난다.

### 도면의 간단한 설명

[0053] 도 1a 내지 도 1d는 한 가지 실시 예에 따른 광전자 소자를 제조하기 위한 방법의 개략도이고,

도 2a 내지 도 3은 추가의 실시 예들에 따른 광전자 소자를 제조하기 위한 방법의 처리 단계들을 도시한 개략도이며,

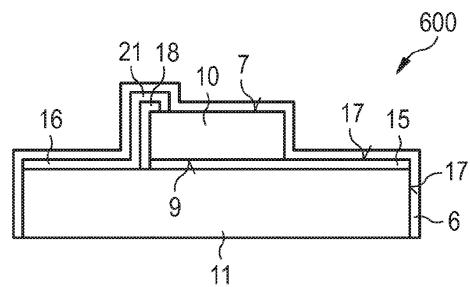

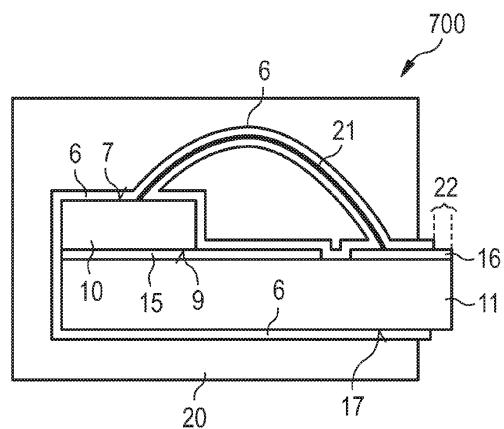

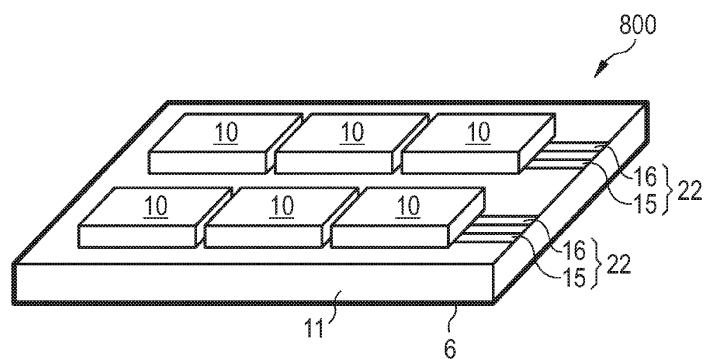

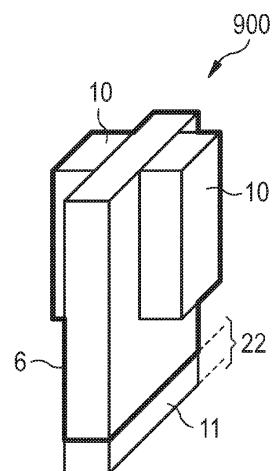

도 4 내지 도 5b는 추가의 실시 예들에 따른 광전자 소자의 개략도이고,

도 6 내지 도 8은 추가의 실시 예들에 따른 광전자 소자를 위한 반도체 소자의 개략도이며, 그리고

도 9 내지 도 13은 추가의 실시 예들에 따른 광전자 소자의 개략도이다.

### 발명을 실시하기 위한 구체적인 내용

[0054] 실시 예들 및 도면들에서 동일한 또는 동일한 작용을 하는 부품들에는 각각 동일한 도면 부호가 제공될 수 있다. 도시된 소자들 그리고 상기 소자들의 상호 크기 비율은 기본적으로 척도에 맞는 것으로 간주 될 수 없으며, 오히려 예컨대 층, 부품, 소자 및 영역과 같은 개별 소자들은 개관을 명확히 할 목적으로 그리고/또는 이해를 도울 목적으로 과도하게 두껍게 또는 크게 치수 설정된 상태로 도시될 수 있다.

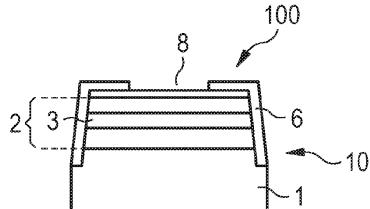

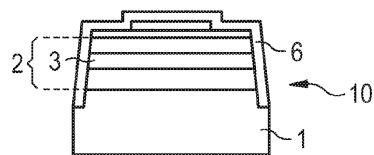

[0055] 도 1a 내지 도 1d에는 한 가지 실시 예에 따라 반도체 소자(10)를 구비한 광전자 소자(100)를 제조하기 위한 방법이 도시되어 있다.

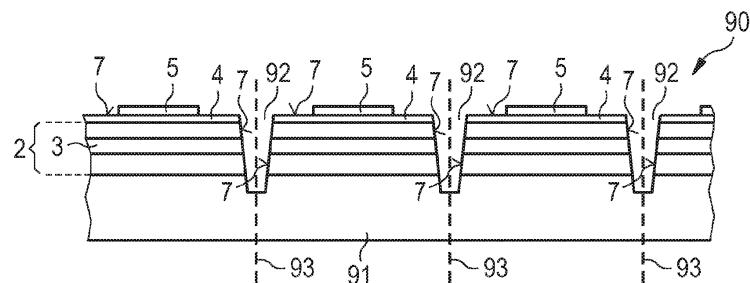

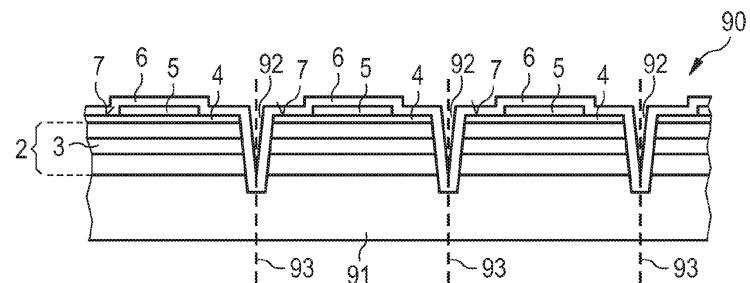

[0056] 도 1a에 따른 제 1 방법 단계에서는 소위 반도체 층 결합체(90)가 소위 웨이퍼 결합체의 형태로 제공된다. 반도체 층 결합체(90)는 반도체 웨이퍼(91)를 구비하며, 상기 반도체 웨이퍼 상에는 활성 영역(3)을 갖는 반도체 층 시퀀스(2)가 증착되어 있다. 반도체 층 시퀀스(2) 상에는 금속, 금속 층 시퀀스 및/또는 금속 합금으로 이루어진 전기 콘택 층(4)이 제공되어 있다. 전기 콘택 층(4)은 도시된 실시 예에서 순전히 예로만 도시되어 있고, 예를 들어 구조화된 상태일 수도 있다. 또한, 하나 또는 다수의 추가 전기 콘택 층이 제공될 수 있음으로써, 결과적으로 반도체 층 시퀀스(2) 및 특히 활성 영역(3)의 양측 콘택팅이 가능해진다. 이와 같은 콘택팅 가능성들은 당업자에게 공지되어 있기 때문에 이곳에서는 더 이상 상세하게 설명되지 않는다.

[0057] 도시된 실시 예에서 반도체 층 결합체(90)는 발광 다이오드(LED)로 구현된 반도체 소자(10)를 제조하기 위한 반도체 층 시퀀스(2)를 순전히 예로서만 포함하기 때문에 작동 중에 광을 방출하기에 적합한 활성 영역(3)을 구비한다. 그 대안으로서 반도체 층 결합체(90)는 예를 들어 단면 방출 레이저 다이오드, 수직 방출 레이저 다이오드(VCSEL), 레이저 다이오드 어레이, 포토 다이오드 또는 태양 전지를 제조하기 위하여 반도체 층 시퀀스(2)도 구비할 수 있다.

[0058] 반도체 층 시퀀스(10)는 도시된 실시 예에서 III-V-화합물 반도체 재료 또는 II-VI-화합물 반도체 재료를 구비한다. III-V-화합물 반도체 재료는 예컨대 B, Al, Ga, In과 같은 제 3 주족으로부터 선택된 적어도 하나의 원소, 그리고 예를 들어 N, P, As와 같은 제 5 주족으로부터 선택된 원소를 포함한다. 특히 상기 'III-V-화합물 반도체 재료'라는 용어는 제 3 주족으로부터 선택된 적어도 하나의 원소 및 제 5 주족으로부터 선택된 적어도 하나의 원소, 예를 들어 질화물- 및 인화물-화합물 반도체를 함유하는 2성분, 3성분 또는 4성분 화합물을 그룹을 포함한다. 이와 같은 2성분, 3성분 또는 4성분 화합물은 또한 예컨대 하나 또는 다수의 도편트 그리고 추가의 성분들을 포함할 수도 있다. 그에 상응하게 II-VI-화합물 반도체 재료는 예컨대 Be, Mg, Ca, Sr과 같은 제 2 주족으로부터 선택된 적어도 하나의 원소, 그리고 예를 들어 O, S, Se와 같은 제 6 주족으로부터 선택된 하나의 원소를 포함한다. 특히 II-VI-화합물 반도체 재료는 제 2 주족으로부터 선택된 적어도 하나의 원소 및 제 6 주족으로부터 선택된 적어도 하나의 원소를 함유하는 2성분, 3성분 또는 4성분 화합물을 포함한다. 이와 같은 2성분, 3성분 또는 4성분 화합물은 또한 예를 들어 하나 또는 다수의 도편트 그리고 추가의 성분들을 포함할 수도 있다. 예를 들어 상기 II-VI-화합물 반도체 재료에는 ZnO, ZnMgO, CdS, ZnCdS, MgBeO가 속한다.

[0059] 반도체 웨이퍼(91)는 예를 들어 전술된 한 가지 화합물 반도체 재료를 함유하는 반도체 재료 또는 사파이어를 포함한다. 특히 이 경우에 반도체 웨이퍼(91)는 GaAs, GaP, GaN 또는 InP를 포함할 수 있거나 또는 이와 같은 물질로 이루어질 수 있거나 또는 대안적으로는 SiC, Si 또는 Ge도 포함할 수 있다.

- [0060] 도시된 실시 예의 대안으로서 반도체 웨이퍼(91)는 반도체 층 시퀀스(2)를 위한 성장 기판을 대신하는 캐리어 기판일 수도 있으며, 상기 캐리어 기판상에는 이전에 제공된 성장 기판상에서 성장된 반도체 층 시퀀스(2)가 이송되었다. 이와 같은 방법 단계들은 예를 들어 소위 박막-반도체 소자를 제조하기 위한 방법의 범위 안에 공지되어 있기 때문에 이곳에서는 더 이상 상세하게 설명되지 않는다.

- [0061] 반도체 층 시퀀스(2)는 활성 영역(3)으로서 예를 들어 종래의 pn-접합부, 이중 혜테로 구조물, 단일-양자 웰 구조물(SQW-구조물) 또는 다중-양자 웰 구조물(MQW-구조물)을 구비할 수 있다. 반도체 층 시퀀스(2)는 활성 영역(3) 외에 추가의 기능적인 층 및 기능적인 영역을 포함할 수 있는데, 예를 들자면 p- 혹은 n-도핑된 전하 캐리어 수송 층, 도핑되지 않은 또는 p- 혹은 n-도핑된 구속-, 클래딩- 또는 도파관 층, 배리어 층, 평탄화 층, 베페 층, 보호층 및/또는 전극 그리고 이들의 조합들을 포함할 수 있다. 활성 영역(3) 또는 추가의 기능적인 층 및 영역과 관련이 있는 상기 구조물들은 특히 구조, 기능 및 구조물과 관련하여 당업자에 공지되어 있기 때문에 이곳에서는 더 이상 상세하게 설명되지 않는다.

- [0062] 또한, 반도체 층 결합체(90)는 반도체 층 시퀀스(2)를 개별 영역으로 세분하는 트렌치(92)를 구비하며, 상기 개별 영역들은 도면에 표시된 분리선을 따라서 분리 후에 반도체 소자(10)를 형성한다.

- [0063] 전기 콘택 층(4) 상에는 구조화된 상태로 구현된 마스크(5)가 제공되어 있으며, 상기 마스크는 그 다음에 제공되는 밀봉 재료(6)의 구조화를 위해서 이용된다. 마스크(5)는 예를 들어 금속, 유전체, 포토 레지스트(photoresist) 또는 이들의 조합물을 구비한다.

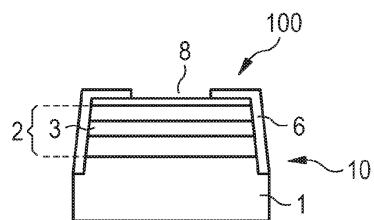

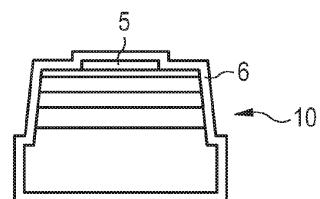

- [0064] 반도체 층 시퀀스(2)는 표면 영역(7)을 구비하며, 상기 표면 영역은 반도체 층 시퀀스(2)의 또는 전기 콘택 층(4)의 상부 면 그리고 특히 트렌치(92)에 의해 노출된 상기 반도체 층 시퀀스(2)의 측면들도 포함한다. 특히 상기 반도체 층 시퀀스의 측면들은 예를 들어 유해 가스와 같은 유해한 영향들로부터 보호되어야만 하는데, 그 이유는 반도체 층 시퀀스(2)의 개별 층들 그리고 특히 활성 영역(3)이 노출되었기 때문이다. 그렇기 때문에 도 1b에 따른 후속하는 한 가지 방법 단계에서는 본 출원서의 일반적인 내용 부분에서 기술된 원자 층 증착에 의해서 표면 영역(7) 상에 밀봉 재료(6)가 제공된다. 상기 밀봉 재료는 도시된 실시 예에서 예컨대 티타늄 산화물, 규소 산화물 또는 규소 질화물과 같은 시각적으로 투명한 전기 절연성 산화물 혹은 질화물 또는 본 출원서의 일반적인 내용 부분에서 언급된 추가의 재료도 포함한다. 밀봉 재료(6)는 500 nm 이하의 두께로 그리고 바람직하게는 10 nm 내지 100 nm의 두께로 제공된다. 원자 층 증착 방법에 의해 제공이 이루어짐으로써 밀봉 재료(6)는 표면 영역(7)을 밀폐식으로 커버하게 되고, 그 결과 특히 트렌치(92)에 의해서 노출된 상기 반도체 층 시퀀스(2)의 측면들은 스크래치에 대하여 강하게 그리고 밀폐식으로 밀봉 및 캡슐화되었다. 또한, 밀봉 재료(6)에 의해서는 추후의 반도체 소자(10) 내부에서 측면 및 칩 에지를 통해서 이루어지는 전류의 누설이 피해질 수 있는데, 그렇지 않으면 상기 누설 전류가 작동을 위한 안정성에 위험 요소가 될 수 있다. 광을 흡수하는 반도체 소자(10)로서 구현된 반도체 소자(10)의 경우에는 누설 전류에 의해 암전류(dark current) 고장이 유발될 수도 있다.

- [0065] 밀봉 재료(6)를 제공한 후에는 반도체 층 결합체(90)가 트렌치(92) 내부에서 소잉, 밀링, 스크래칭 및/또는 에칭 공정에 의해 분리선(93)을 따라서 반도체 소자(10)로 분리되며, 분리된 반도체 소자들 중에 하나의 반도체 소자가 도 1c에 도시되어 있다.

- [0066] 마스크(5)가 박리(lift off) 기술에 의해 반도체 소자(10) 상에서 제거됨으로써(도 1d 참조), 밀봉 재료(6)로 이루어진 층 내부에서는 콘택 개구(8)가 형성되며, 상기 콘택 개구를 통해 전기 콘택 층(4)이 반도체 소자(10)의 전기 단자에 콘택팅될 수 있다. 도시된 실시 예의 대안으로서 마스크(5)는 분리 과정 전에 미리 제거될 수도 있다.

- [0067] 도면에 도시된 방법에 의해서 제조되는 도 1d에 따른 광전자 소자(100)는 작동 중에 광을 방출하기에 적합한 활성 영역(3)을 갖는 반도체 소자(10)를 구비한다. 적어도 하나의 표면 영역(7)에는 상기 표면 영역(7)을 밀폐식으로 덮는 밀봉 재료(6)가 제공되어 있다. 특히 도시된 실시 예에서는 반도체 소자(10)의 측면들이 밀봉 재료(6)에 의해 밀봉됨으로써, 결과적으로는 예를 들어 습기 및/또는 산소와 같은 주변 영향들에 의한 그리고/또는 누설 전류에 의한 활성 영역(3)의 질적 저하 또는 손상이 피해질 수 있게 된다.

- [0068] 도시된 실시 예의 대안으로서 반도체 층 결합체(90)는 웨이퍼 결합체 대신에 레이저 다이오드의 바아 결합체도 형성할 수 있으며, 이와 같은 바아 결합체에서는 예를 들어 캡에 의해 노출된 측면들이 표면 영역(7)을 형성하게 되고, 상기 표면 영역 상에는 밀봉 재료(6)가 제공된다.

- [0069] 추가의 도면들에는 제조 방법의 처리 단계들을 위한 그리고 광전자 소자들을 위한 추가의 실시 예들이 도시되어

있고, 상기 추가의 실시 예들은 이전에 도시된 실시 예의 개선 예들 그리고 변형 예들이며, 달리 기술되지 않는 한, 상기 추가의 실시 예들은 이전에 도시된 실시 예의 특징들을 포함할 수 있다.

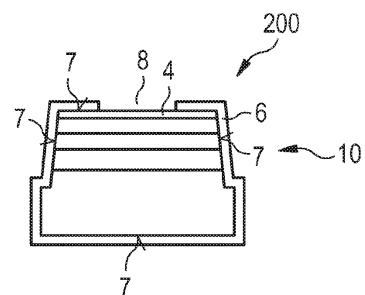

[0070] 도 2a 내지 도 2c에는 광전자 소자(200)를 제조하기 위한 방법의 처리 단계들의 한 가지 실시 예가 도시되어 있으며, 이 경우 도 1a에 도시된 처리 단계에 따라서는 반도체 층 결합체(90)를 반도체 소자(10)로 분리시키는 분리 공정이 실시된다. 도시된 방법의 대안으로서 예를 들어 마스크(5)가 분리된 반도체 소자(10) 상에도 제공될 수 있다.

[0071] 도 2b에 따른 추가의 한 가지 처리 단계에서는 밀봉 재료(6)가 원자 층 중착에 의해 반도체 소자(10)의 모든 표면 영역(7)에서 중착된다. 전술된 박리 기술에 의해서 마스크가 제거되고, 콘택 개구(8) 내부에서 전기 콘택 층이 노출된다(도 2c 참조).

[0072] 상기와 같이 제조된 광전자 소자(200)는 반도체 소자(10)를 구비하고, 상기 반도체 소자에서는 밀봉 재료(6)로 덮인 표면 영역(7)이 전기 콘택 층(4)의 한 부분 영역을 제외한 상기 반도체 소자(10)의 모든 노출된 표면을 둘러싼다. 따라서, 반도체 소자(10)는 모든 측에서 밀폐식으로 덮이고, 스크래치 및 유해한 주변 영향에 대하여 보호되며, 그리고 콘택 개구(8) 내부에서 노출된 전기 콘택 층을 통해 전기적으로 콘택팅 될 수 있다. 이미 앞에서 언급된 바와 같이, 밀봉 재료(6)는 추가의 전기 콘택 층을 노출하기 위하여 추가의 콘택 개구들을 구비하지만, 상기 추가의 콘택 개구들은 도면에 대한 개관을 용이하게 할 목적으로 도면에는 도시되어 있지 않다.

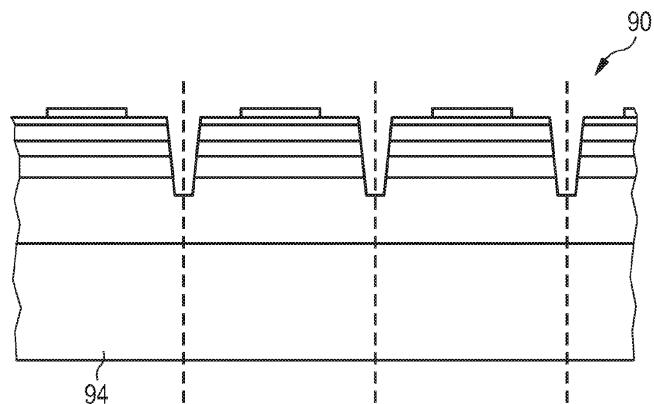

[0073] 도 3에는 한 가지 추가의 실시 예에 따른 광전자 소자를 제조하기 위한 방법에 대한 한 가지 처리 단계가 도시되어 있다. 이 경우 반도체 층 결합체(90)는 캐리어 결합체(94) 상에 제공되며, 상기 캐리어 결합체는 예를 들어 반도체 소자(10)를 위한 히트 싱크를 포함한다. 반도체 층 결합체(90) 및 캐리어 결합체(94)는 예를 들어 납땜, 접착 또는 양극 본딩에 의해서 서로 연결되고, 위?아래로 겹쳐서 장착된다.

[0074] 도시된 실시 예의 대안으로서 사전에 분리된 하나 또는 다수의 반도체 소자(10)가 캐리어 혹은 캐리어 결합체 상에 장착될 수도 있다.

[0075] 그 다음에 캐리어 결합체(94)를 구비하는 반도체 층 결합체(90) 또는 캐리어 혹은 캐리어 결합체 상에 있는 하나 또는 다수의 반도체 소자(10)는 이전의 실시 예들에서와 마찬가지로 계속해서 처리(processing)될 수 있다.

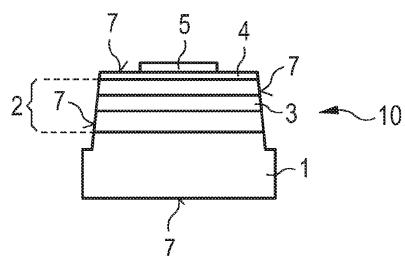

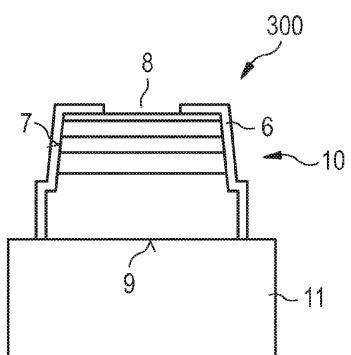

[0076] 도 4에는 광전자 소자(300)를 위한 한 가지 실시 예가 도시되어 있으며, 이 경우 반도체 소자(10)는 조립 면(9)에 의해서 예를 들어 히트 싱크, 리드 프레임 및/또는 프린트 회로 기판과 같은 캐리어(11) 상에 장착되어 있다. 밀봉 재료(6)에 의해서 덮인 표면 영역(7)은 콘택 개구(8)를 제외한 본 명세서의 의미에서의 반도체 소자(10)의 모든 노출된 표면을 둘러싼다. 예를 들어 최적화된 열 방출 및/또는 전기 콘택 층 혹은 본딩 패드에 의한 차폐와 관련하여 광전자 소자에 대하여 요구되는 고유한 조건들에 따라서, 상기와 같은 광전자 소자의 제조는 반도체 소자(10)의 조립과 관련하여 캐리어(11) 상에서 소위 p-사이드-업-조립(p-side-up-Montage) 방식으로 또는 p-사이드-다운-조립(p-side-down-Montage) 방식으로 이루어질 수 있다.

[0077] 도 4에 도시된 실시 예의 대안으로서 밀봉 재료(6)는 또한 전기 콘택 층(4)을 포함하는 모든 노출된 표면 영역(7) 상에도, 다시 말해 조립 면을 제외한 모든 표면에도, 그리고/또는 도 9 내지 도 13과 관련하여 도시된 바와 같이 캐리어(11)의 하나 또는 다수의 표면에 적어도 부분적으로 제공될 수 있다.

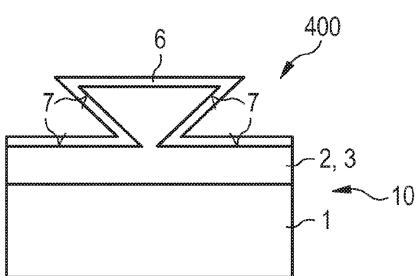

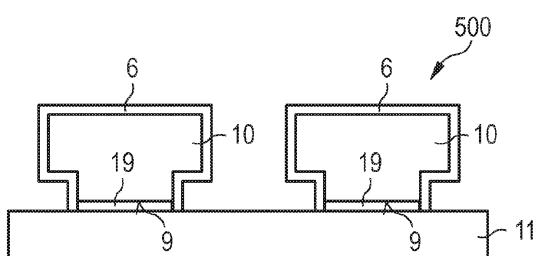

[0078] 도 5a 및 도 5b에는 광전자 소자(400, 500)에 대한 추가의 실시 예들이 도시되어 있으며, 이 경우에는 적어도 하나의 표면 영역(7) 상에 밀봉 재료(6)가 제공되어 있다. 두 가지 실시 예에서 광전자 소자(400, 500)의 반도체 소자(10)는 밀봉 재료(6)로 덮인, 차폐된 표면 영역(7)을 갖는다. 이와 같은 내용이 의미하는 바는, 예컨대 진공 중착 또는 스퍼터링과 같은 지향적인(directed) 중착 방법에 의해서는 표면 영역(7)이 밀봉 재료(6)로 전혀 덮일 수 없거나 또는 적어도 균일하지 않게 덮일 수 있다는 것이다. 도시된 실시 예들에 따르면 상기 표면 영역(7)의 차폐된 영역들은 구조적인 형상에 의해서 반도체 소자(10) 그리고 상기 반도체 소자의 반도체 층 시퀀스(2)가 거꾸로 뒤집힌 뼈기 구조물의 형태로(도 5a 참조) 그리고 벼섯 모양 구조물의 형태로(도 5b 참조) 형성된다. 이때 상기 도시된 구조적인 형상들은 순전히 예에 불과하다. 원자 층 중착에 의해서는 도시된 실시 예들에서 코팅될 표면 영역(7)이 기하학적인 구조와 무관하게 커버 될 수 있는데, 그 이유는 이 방법이 지향적이지 않기 때문이다.

[0079] 그렇기 때문에 본 출원서에 기재된 방법은 특히 바람직하게 캐리어 상에서 서로 나란히 매우 가깝게 배치되어 있는 그리고/또는 예를 들어 가늘고 긴 채널 및/또는 개구 및/또는 조립 면 쪽으로 가면서 점차 좁아지는 구조물을 구비하는 반도체 소자(10)에도 사용될 수 있다.

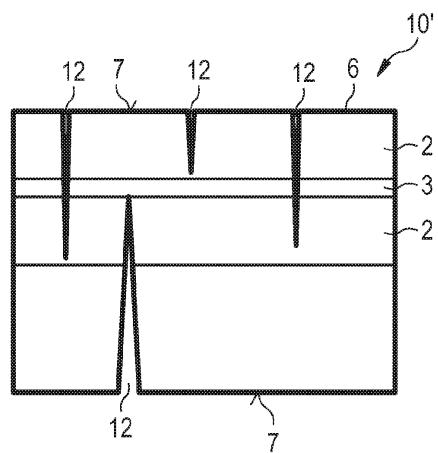

- [0080] 도 6 내지 도 8에는 마이크로 개구(12)를 갖는 반도체 소자( $10'$ ,  $10''$ ,  $10'''$ )에 대한 실시 예들이 도시되어 있다.

- [0081] 도 6에 개략적으로 도시된 바와 같이 반도체 층 시퀀스(2) 및/또는 기판(1) 내부에 있는 마이크로 개구(12)는 대체로 마이크로 채널 및/또는 나사 전위의 형태로 존재할 수 있다. 예를 들어 이와 같은 마이크로 개구(12)는 반도체 층 시퀀스(10)를 제공할 때에 반도체 층 시퀀스(2)와 기판(1) 사이에서 나타나는 그리고/또는 상기 반도체 층 시퀀스(2)의 다양한 층들 사이에서 나타나는 불완전한 격자 매칭 때문에 형성될 수 있다. 기판(1)도 마찬가지로 제조와 관련해서 마이크로 개구(12)를 가질 수 있다. 특히 앞에서 언급된 그리고 이하에서 언급될 실시 예들의 광전자 소자들은 상기와 같은 마이크로 개구를 가질 수 있다.

- [0082] 마이크로 개구(12) 내부에서는 도편트 및/또는 금속 및/또는 습기 및/또는 산소가 예를 들어 활성 영역(3) 안으로 이동하여 차단 전류의 증가 및 노화에 의한 고장을 야기할 수 있다. 마이크로 개구를 포함하는 표면 영역(7)을 도 6에 도시된 바와 같이 밀봉 재료(6)를 이용하여 밀봉함으로써 상기와 같은 위험들이 방지된다.

- [0083] 특히 마이크로 개구(12)의 밀봉은 예를 들어 반도체 층 시퀀스(2)가 에피택셜 방식의 성장 직후에 밀봉 재료(6)에 의해서 밀봉되거나 또는 추후의 한 프로세스 단계에서 전술된 실시 예들에 상응하게 밀봉됨으로써 이루어질 수 있다. 특히 마이크로 개구(12)의 밀봉 과정은 밀봉될 추가의 표면 영역(7), 예를 들어 하나의 반도체 소자(10)의 측면들을 패시베이팅(passivating) 하는 과정과 함께 이루어질 수 있다.

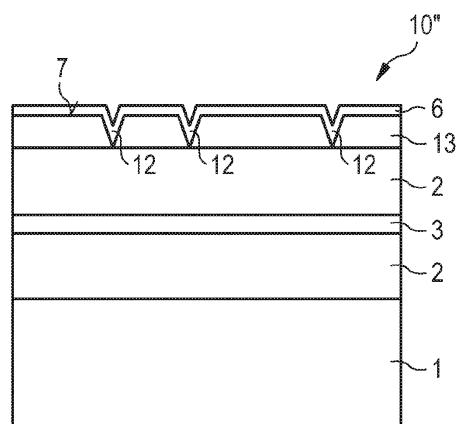

- [0084] 도 7에 도시된 바와 같이 반도체 소자( $10''$ )는 하나의 표면에 패시베이션 층(13)을 구비할 수 있으며, 상기 패시베이션 층은 예를 들어 스퍼터링, 진공 증착 또는 CVD와 같은 종래의 증착 방법에 의해서 증착된다. 본 출원서의 일반적인 내용 부분에 기재된 바와 같이 상기와 같은 패시베이션 층(13)은 예컨대 마이크로 채널과 같은 마이크로 개구(12) 및/또는 상승된 기공도에 의해서 그리고/또는 패시베이션 층(13)의 불완전한 표면 점유에 의해서 야기되는 소위 핀-홀을 구비할 수 있으며, 상기 마이크로 개구 및/또는 핀-홀은 밀봉 재료(6)를 이용한 원자 층 증착에 의해서 밀봉될 수 있다.

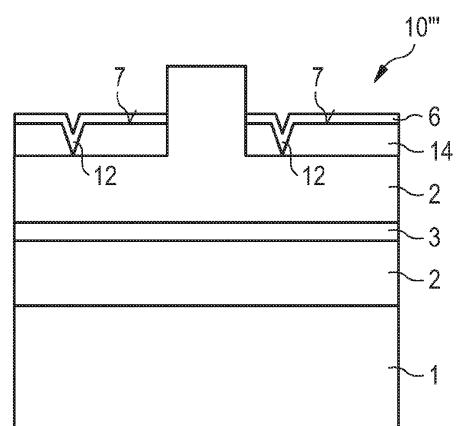

- [0085] 도 8에는 레이저 다이오드로서 형성된 반도체 소자( $10'''$ )가 도시되어 있으며, 상기 반도체 소자는 당업자에게 공지된 브리지 도파관 구조를 갖는다. 상기 브리지 도파관 구조는 이 브리지 도파관 구조가 형성되어야만 하는 영역 안에 하나의 개구를 갖는 성장 보호 층(14)이 반도체 층 시퀀스(2)의 한 부분에 제공됨으로써, 에피택셜 방식의 과도 성장에 의해서 자기 정렬 형태로 제조된다. 상기 성장 보호 층(14)이 표면 영역(7)에 마이크로 개구(12)를 갖는 다공성 성장 보호 층인 경우에는 상기 마이크로 개구(12)의 영역에서 기생 결정들이 성장하게 되며, 이와 같은 기생 결정들은 변형 가능성을 악화시키고, 누설 전류 및/또는 심지어 소자의 고장을 유발할 수도 있다. 원자 층 증착 방법을 이용하여 밀봉 재료(6)를 제공함으로써 표면 영역(7)에 있는 마이크로 개구(12)가 밀봉될 수 있다.

- [0086] 도 9에는 한 가지 추가의 실시 예에 따른 반도체 소자(10)를 구비하는 광전자 소자(600)가 도시되어 있다.

- [0087] 광전자 소자(600)는 캐리어(11)를 구비하며, 상기 캐리어는 그 위에 장착되는 반도체 소자(10)를 위한 히트 싱크로서 형성되었고, 반도체 소자(10)를 전기적으로 콘택팅 하기 위하여 전기 접속 층(15, 16)을 구비한다. 반도체 소자(10)는 상기 전기 접속 층(15) 상에 있는 조립 면(9)에 장착되어 있으며, 이 경우 상기 조립 면(9)은 반도체 소자(10)를 전기 접속하기 위한 전기 콘택 층(도면에 도시되어 있지 않음)으로서도 형성되어 있다. 상기 조립 면에 마주 놓인 측에서 반도체 소자(10)는 도전 층으로 형성된 전기 콘택 소자(21)에 의해서 캐리어의 접속 층(16)에 전기적으로 접속되어 있다. 이 목적을 위하여, 상기 전기 콘택 소자(21)를 예를 들어 반도체 소자(10)의 측면에서 전기 콘택 소자(21)로부터 전기적으로 분리하기 위하여 상기 전기 콘택 소자(21)와 반도체 소자(10) 사이의 영역에는 전기 절연 층(18)이 배치되어 있다.

- [0088] 반도체 소자(10)는 상기 반도체 소자(10)의 모든 노출 표면 및 상기 전기 콘택 소자(21)를 둘러싸는 표면 영역(7)에서 원자 층 증착에 의해 제공되는 밀봉 재료(6)로 덮여 있고, 밀폐식으로 밀봉되어 있다. 또한, 캐리어의 표면(17)도 밀봉 재료(6)로 덮여 있다. 그럼으로써 반도체 소자(10)를 둘러싸는 캡슐화가 성취된다.

- [0089] 선행 기술에 공지된 하우징과 비교할 때 본 발명에 따른 밀봉 재료(6)에 의해서는 캡슐화된 광전자 소자(600)가 매우 콤팩트하게 치수 설정될 수 있다. 이와 같은 상황은 바람직하게 다름 아닌 도면에 도시된 층 모양의 전기 콘택 소자(21)를 이용한 전기 콘택팅과의 조합에 의해서 실현될 수 있는데, 그 이유는 선행 기술에 공지된 하우징이 생략된 경우에는 본딩 와이어의 형태로 형성된 전기 공급부와 반도체 칩 사이에서 통상적으로 사용되는 전기 접속이 전체적인 구조를 높이에 상당한 기여를 할 수 있기 때문이다. 또한, 본딩 와이어로 구현된 전기 콘택 소자(21)와 비교할 때에도 예를 들어 도면에 도시된 하우징이 없는 구조적 형상에서 본딩 와이어를 분리시킴

으로써 광전자 소자(600)의 손상 위험도 줄어든다.

[0090] 도 10에는 한 가지 추가의 실시 예에 따른 반도체 소자(10)를 구비하는 광전자 소자(700)가 도시되어 있으며, 상기 광전자 소자는 이전의 실시 예와 비교할 때 본딩 와이어를 전기 콘택 소자(21)로서 구비한다. 이때 전체 반도체 소자(10)는 노출된 모든 표면 또는 표면 영역(7) 그리고 본딩 와이어(21)에서 밀봉 재료(6)로 덮여 있다. 또한, 전기 접속 층(15, 16)을 구비하는 캐리어도 접속 영역(22)을 제외한 모든 표면(17)에서 밀봉 재료(6)로 덮임으로써, 결과적으로 광전자 소자(700)의 둘러싸는 형태의 밀봉이 성취된다. 콘택팅을 목적으로 전기 접속 층(15, 16)에 접근할 수 있는 전기 접속 영역(22)에 의해서는 외부 전원 및/또는 제어 전자 장치에 대한 광전자 소자(700)의 전기 접속이 이루어진다.

[0091] 또한, 광전자 소자(700)는 투명한 하우징 재료(20)를 구비하며, 상기 하우징 재료는 반도체 소자(10) 및 캐리어(11)의 한 부분을 둘러싸고 있다. 하우징 재료(20)는 비밀폐형의 플라스틱을 구비한다.

[0092] 그와 달리 밀폐형 플라스틱- 또는 금속 하우징 안에 광전자 소자를 캡슐화하는 종래의 방법은 본 발명에 도시된 실시 예와 비교할 때 매우 복잡하고 많은 비용이 소요되는데, 그 이유는 주변에 대한 모든 경계면이 밀봉력과 관련하여 최고의 요구 조건들을 충족시켜야만 하기 때문이다. 이와 같은 상황은 단지 상대적으로 복잡한 방법 그리고 상대적으로 값비싼 재료들에 의해서만 구현될 수 있다. 통상적으로 하우징에 의해서 밀폐식의 캡슐화가 이루어질 필요가 없다면, 특히 예컨대 취급의 용이성, 열 방출 및/또는 시각적인 특성들과 같은 다른 요구 조건들을 충족시키기 위하여 다수의 경우에 하우징 자체는 훨씬 더 단순하게 구현될 수 있다. 밀봉 재료(6)와의 조합에 의해서는 훨씬 더 단순한 하우징이 사용될 수 있으며, 이 경우에는 밀폐식의 밀봉이 보증되면서도 그와 동시에 캡슐화를 위하여 복잡한 공지된 방법 그리고 값비싼 재료들이 피해야 할 수 있다.

[0093] 도 11에는 한 가지 추가의 실시 예에 따른 광전자 소자(800)가 도시되어 있으며, 상기 광전자 소자는 히트 싱크, 리드 프레임, 기판 또는 패널(panel)로서 형성된 캐리어(11) 상에 다수의 반도체 소자(10)를 구비한다. 도시된 실시 예에서는 반도체 소자(10)가 LED로 형성됨으로써, 결과적으로 광전자 소자(800)는 발광 작용을 하는 고출력 모듈이 된다. 반도체 소자(10)는 캐리어(11)와 공동으로 노출된 각각의 표면에서 상호 연결된 상태로 밀봉 재료(6)에 의해 덮여 있으며, 이와 같은 상황은 도 11에 개략적으로 도시되어 있다. 도면에 도시된 영역에서는 단지 전기 접속 트랙(15, 16)만 전기 접속 영역으로 형성되었기 때문에 상기 전기 접속 트랙에는 밀봉 재료(6)가 없다.

[0094] 원자 층 증착에 의해서 제공된 밀봉 재료(6)는 본 실시 예에 도시된 것과 같은 광전자 소자에서는 다른 무엇보다 반도체 소자(10)가 서로 나란히 매우 조밀하게 배치된 경우, 다시 말하자면 어레이-구조적 형상으로 배치된 경우에도 한가지 특별한 장점을 제공해준다. 이때 상기 원자 층 증착 방법은 값이 저렴하고, 표면이 넓으며, 시각적으로 투명한 밀폐식의 압축, 밀봉 또는 반도체 소자(10)들 사이에 존재할 수 있는 가늘고 긴 캡까지도 확실하고 균일하게 밀봉시키는 캡슐화의 제공을 가능하게 해준다. 이때 밀봉 재료(6)는 바람직하게 반도체 소자(10)의 시각적인 기능에 영향을 미치지 않는 시각적으로 투명한 재료를 포함할 수 있다.

[0095] 대안적으로 반도체 소자(10)는 적어도 부분적으로 또는 모두 레이저 다이오드로서 그리고/또는 포토 다이오드로서 형성될 수도 있다. 또한, 반도체 소자(10) 및 상기 반도체 소자의 전기 접속 트랙을 패널 상에 조립하는 범위 안에서 원자 층 증착 방법을 이용하여 밀봉 재료를 제공하는 방식도 실시될 수 있다. 그 다음에 이어서 예컨대 광학 부품들과 같은 캡슐화를 위해서 전혀 필요치 않은 추가의 소자들이 조립될 수 있다.

[0096] 도 12에는 한 가지 추가의 실시 예에 따른 광전자 소자(900)가 도시되어 있고, 상기 광전자 소자는 전기 접속 플레이트 및 그와 동시에 히트 싱크로서 형성된 캐리어(11) 상에 두 개의 반도체 소자(10)를 구비하며, 이때 상기 반도체 소자들은 캐리어(11)의 다양한 표면에 배치되어 있다. 도시된 실시 예에서 반도체 소자(10)는 적색의 레이저 다이오드로서 그리고 녹색의 레이저 다이오드로서 순전히 예로서만 형성되어 있다. 도면에 대한 개관을 명확하게 할 목적으로 전기 콘택 층 및 접속 층은 도시되어 있지 않다. 반도체 소자(10) 및 캐리어(11)는 도 12에 개략적으로 도시되어 있는 바와 같이 전기 접속 영역(22)을 제외한 모든 노출된 표면에서 서로 연결된 상태로 밀봉 재료(6)에 의해 덮여 있다. 그럼으로써, 광전자 소자(900)가 매우 콤팩트한 구조로 형성된 경우에도 다양하게 구현된 반도체 소자(10)들을 공동으로 그리고 동시에 캡슐화하는 것이 가능해지는데, 그 이유는 보호 가스 하우징과 같은 선행 기술에 따른 복잡하고 값비싼 캡슐화 공정이 필요 없기 때문이다. 콤팩트한 구조에 의해서는 반도체 소자(10)가 예를 들어 하나의 공통된 하위 광학 수단을 이용할 수도 있다.

[0097] 앞에서 언급된 송신기-송신기-조합의 형태에 대하여 도시된 실시 예의 대안으로서, 반도체 소자(10)는 또한 예를 들어 LED로서 또는 포토 다이오드 및 광 방출 레이저 다이오드로 구성된 조합으로서 송신기-수신기-조합의

형태로 구현될 수도 있다. 그 대안으로서 반도체 소자(10)는 또한 수신기-수신기-조합의 형태로 두 개의 포토 다이오드로서 구현될 수도 있다. 또한, 도면에 도시된 2개보다 많은 반도체 소자(10) 그리고 추가의 전자 소자들도 캐리어(11) 상에서 한 측에 또는 양측에 배치되어 있고, 밀봉 재료(6)에 의해서 공동으로 캡슐화될 수 있다.

[0098] 도면에 도시된 콤팩트한 구조는 바람직하게 예컨대 프로젝터(projector) 또는 광 배리어(light barrier)와 같은 광전자 부품의 대량 생산에 이용될 수 있는데, 그 이유는 동일하거나 또는 상이한 형태의 반도체 소자(10)들이 구조적으로 밀봉 패킹 되고, 추가의 공간을 필요로 하지 않으면서 공동으로 캡슐화될 수 있기 때문이다.

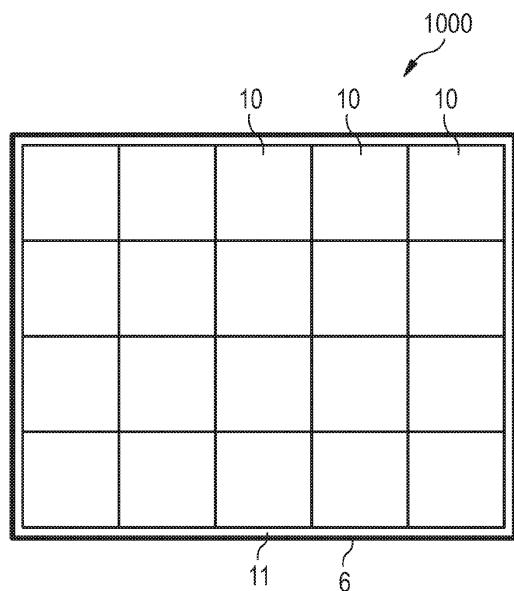

[0099] 도 13에는 한 가지 추가의 실시 예에 따른 광전자 소자(1000)가 도시되어 있으며, 상기 광전자 소자는 태양 전지 패널로서 또는 태양 전지 모듈로서 형성되었다. 광전자 소자(1000)는 다수의 반도체 소자(10)를 구비하며, 상기 반도체 소자들은 태양 전지로서 형성되어 캐리어(11) 상에 공동으로 배치되어 있고, 서로 전기적으로 접속되어 있다. 반도체 소자(10)들은 밀봉 재료(6)에 의해서 공동으로 밀폐식으로 덮여 있기 때문에 우박, 먼지, 습기 및 산소와 같은 주변의 영향 및 스크래치에 대하여 보호된다.

[0100] 태양 전지 및 태양 전지 모듈은 미래의 에너지 공급을 위해서 점점 더 큰 비중을 차지하고 있다. 개별 태양 전지 및 태양 전지 모듈의 고장이 상당한 비용과 결부되어 있기 때문에, 상기와 같은 시스템들은 가급적 효율이 저하되지 않으면서 긴 수명을 가져야만 한다. 태양 전지로서 형성된 반도체 소자(10) 위에 넓은 표면에 걸쳐서 그리고 서로 연결된 상태로 제공된 밀봉 재료(6)에 의해서는, 상기 밀봉 재료가 날씨 보호 방식의 투명한 캡슐의 형태로 형성되어 주변 영향에 대하여 효과적인 보호 효과를 제공해주며, 예를 들어 습기에 의해서 전기 콘택 층 또는 접속 층이 부식될 위험까지도 방지해준다.

[0101] 본 특허 출원서는 독일 특허 출원서 제 10 2009 058 796.9호를 우선권으로 주장하며, 상기 우선권 서류의 공개 내용은 인용의 방식으로 본 출원서에 수용된다.

[0102] 본 발명은 실시 예들을 참조하는 상세한 설명으로 인해 상기 실시 예들에만 한정되지 않는다. 오히려 본 발명은 각각의 새로운 특징 그리고 상기 특징들의 각각의 조합을 포함하며, 상기 특징 또는 특징 조합 자체가 특허 청구범위 또는 실시 예들에 명시적으로 기재되어 있지 않더라도, 특히 상기 각각의 특징 조합은 특허청구범위에 포함된 것으로 간주한다.

## 도면

### 도면 1a

### 도면 1b

도면1c

도면1d

도면2a

도면2b

도면2c

도면3

도면4

도면5a

도면5b

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13