(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-182943

(P2013-182943A)

(43) 公開日 平成25年9月12日(2013.9.12)

(51) Int.Cl.

**H01L 27/146** (2006.01)

**H04N 5/374** (2011.01)

**H01L 21/027** (2006.01)

**G03F 7/20** (2006.01)

F 1

H01L 27/14 A

H04N 5/335 740

H01L 21/30 514A

G03F 7/20 521

テーマコード(参考)

4M118

5C024

5F146

審査請求 未請求 請求項の数 6 O L (全 12 頁)

(21) 出願番号

(22) 出願日

特願2012-44301 (P2012-44301)

平成24年2月29日 (2012.2.29)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】固体撮像装置の製造方法

## (57) 【要約】

【課題】高い解像度および画質を有する大型の固体撮像装置を製造するために有利な技術を提供する。

【解決手段】複数のフォトリソグラフィー工程を経て固体撮像装置を製造する製造方法において、前記複数のフォトリソグラフィー工程は、複数のフォトマスクを使って基板を露光する分割露光工程を含む少なくとも1つの第1リソグラフィー工程と、1つのフォトマスクを使って前記基板を露光する非分割露光工程を含む少なくとも1つの第2リソグラフィー工程とを含み、前記少なくとも1つの第1リソグラフィー工程は、前記基板に活性領域110を定義するためのレジストパターンを形成する工程と、電荷蓄積領域112を定義するためのレジストパターンを形成するリソグラフィー工程とを含む。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

複数のフォトリソグラフィー工程を経て固体撮像装置を製造する製造方法であって、前記複数のフォトリソグラフィー工程は、複数のフォトマスクを使って基板を露光する分割露光工程を含む少なくとも1つの第1リソグラフィー工程と、1つのフォトマスクを使って前記基板を露光する非分割露光工程を含む少なくとも1つの第2リソグラフィー工程とを含み、

前記少なくとも1つの第1リソグラフィー工程は、前記基板に活性領域を定義するためのレジストパターンを形成する工程と、電荷蓄積領域を定義するためのレジストパターンを形成するリソグラフィー工程とを含む、

ことを特徴とする固体撮像装置の製造方法。

10

**【請求項 2】**

前記少なくとも1つの第1リソグラフィー工程は、前記電荷蓄積領域の上に配置された半導体領域を定義するためのレジストパターンを形成するリソグラフィー工程を含み、

前記半導体領域の導電型は、前記電荷蓄積領域の導電型とは異なる、

ことを特徴とする請求項1に記載の固体撮像装置の製造方法。

**【請求項 3】**

前記少なくとも1つの第1リソグラフィー工程は、隣り合う前記電荷蓄積領域の間に配置されたポテンシャルバリア領域を定義するためのレジストパターンを形成するリソグラフィー工程を含み、前記ポテンシャルバリア領域の導電型は、前記電荷蓄積領域の導電型とは異なる、

20

ことを特徴とする請求項1又は2に記載の固体撮像装置の製造方法。

**【請求項 4】**

前記少なくとも1つの第1リソグラフィー工程は、素子分離領域の周囲に配置されるチャネルトップ領域を定義するためのレジストパターンを形成するリソグラフィー工程を含む、

ことを特徴とする請求項1乃至3のいずれか1項に記載の固体撮像装置の製造方法。

30

**【請求項 5】**

前記固体撮像装置は、画素アレイ部および周辺回路部を含み、前記画素アレイ部を構成する素子は、共通のウエル領域の中に形成され、前記周辺回路部は、前記ウエル領域の外側に形成され、

前記少なくとも1つの第2リソグラフィー工程は、前記基板に前記ウエル領域を定義するためのレジストパターンを形成するリソグラフィー工程を含む、

ことを特徴とする請求項1乃至4のいずれか1項に記載の固体撮像装置の製造方法。

**【請求項 6】**

前記少なくとも1つの第2リソグラフィー工程は、遮光パターンを定義するためのレジストパターンを形成するリソグラフィー工程を含む、

ことを特徴とする請求項1乃至5のいずれか1項に記載の固体撮像装置の製造方法。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、固体撮像装置の製造方法に関する。

**【背景技術】****【0002】**

1つの層のパターンを形成するために複数のフォトマスク(レチクル)を使って複数の分割領域を別個に露光する方法がある。このような方法を分割露光と呼ぶことにする。また、1つの層のパターンを形成するために1つのフォトマスクを使って1つの領域を露光する方法がある。このような方法を非分割露光と呼ぶことにする。なお、「層」の概念には、ポリシリコン配線層およびメタル配線層などのように半導体基板の上に配置される配線層のほか、基板に対するイオン注入によって形成されうる不純物領域の二次元的配列で

50

構成されるような半導体基板中の層も含まれるものとする。

【0003】

特許文献1には、ステッパのフィールドサイズ以上の大きさを有する光電変換装置を分割露光によって形成する方法が開示されている。特許文献2には、半導体装置の動作に実質的な影響を与える層およびその下の層に関しては非分割露光を通して形成し、半導体装置の動作に実質的な影響を与える層よりも上の層に関しては分割露光を通して形成することが開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平5-6849号公報

【特許文献2】特開2004-111866号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

一般に、広い領域を露光可能な露光装置は、狭い領域を露光可能な露光装置よりも解像度が低く、アライメント精度も低い。固体撮像装置の撮像領域が大型化した場合に、それを非分割露光によって形成しようとすると、解像度およびアライメント精度が低い露光装置を使用する必要がある。しかしながら、その場合に、その露光装置の解像度によって画素数が制限されたり、画質が制限されたりしうる。そこで、分割露光を適用して固体撮像装置を製造せざるを得なくなるが、あらゆる層を分割露光で形成しようとすると、フォトマスクのコスト、リソグラフィー工程のコスト、露光装置のコストなどが大きくなる。

【0006】

なお、特許文献2に開示された方法は、高い解像度およびアライメント精度が要求される層およびその下の層を非分割露光で形成しようとする思想に基づくものであり、この方法では、高い解像度および画質を有する大型の固体撮像装置を製造することは難しい。

【0007】

本発明は、高い解像度および画質を有する大型の固体撮像装置を製造するために有利な技術を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の1つの側面は、複数のフォトリソグラフィー工程を経て固体撮像装置を製造する製造方法に係り、前記複数のフォトリソグラフィー工程は、複数のフォトマスクを使って基板を露光する分割露光工程を含む少なくとも1つの第1リソグラフィー工程と、1つのフォトマスクを使って前記基板を露光する非分割露光工程を含む少なくとも1つの第2リソグラフィー工程とを含み、前記少なくとも1つの第1リソグラフィー工程は、前記基板に活性領域を定義するためのレジストパターンを形成する工程と、電荷蓄積領域を定義するためのレジストパターンを形成するリソグラフィー工程とを含む。

【発明の効果】

【0009】

本発明によれば、高い解像度および画質を有する大型の固体撮像装置を製造するために有利な技術が提供される。

【図面の簡単な説明】

【0010】

【図1】本発明の製造方法によって製造されうる固体撮像装置を例示する図。

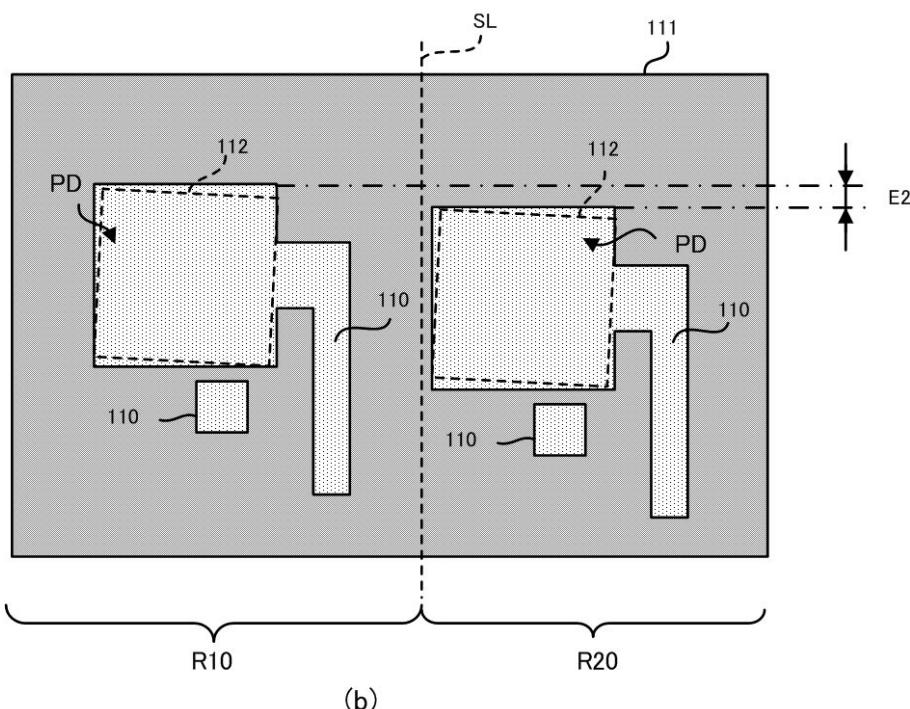

【図2】図1に例示された固体撮像装置の画素アレイ部の部分的な構成を示す図。

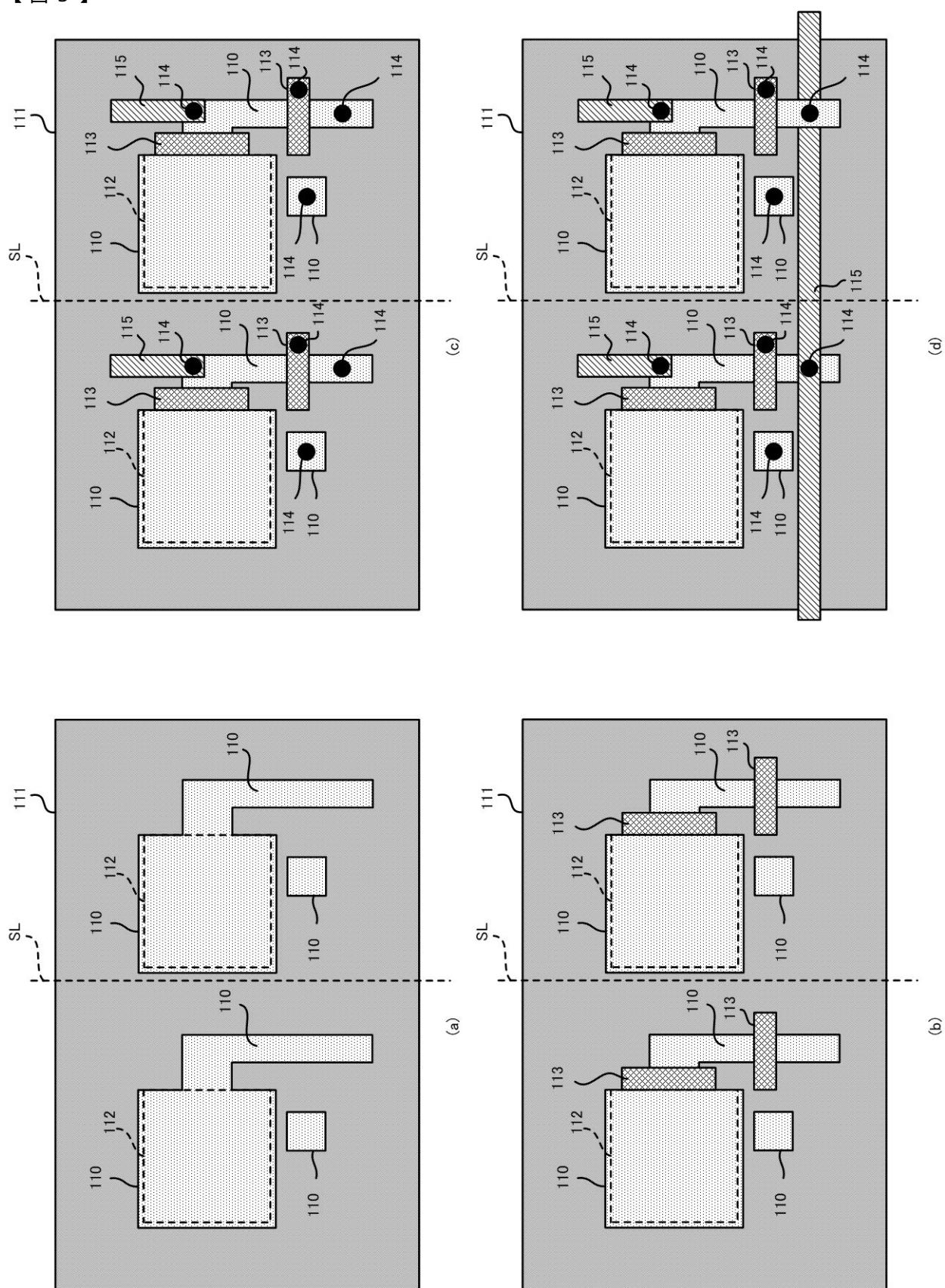

【図3】固体撮像装置の製造方法を例示的に示す図。

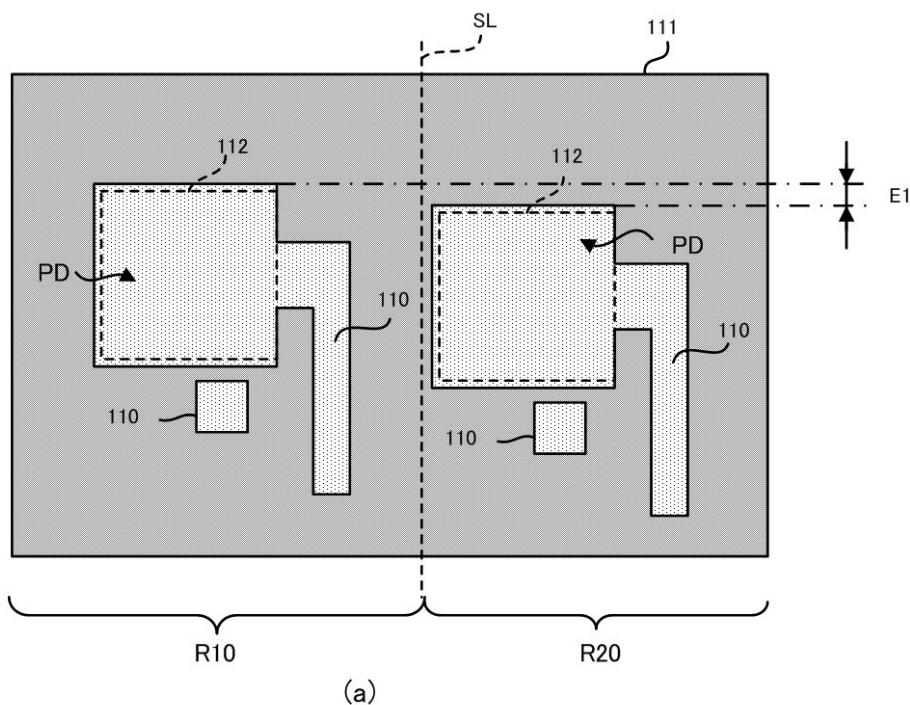

【図4】活性領域と電荷蓄積領域の形成において分割露光工程を含むリソグラフィー工程を適用することの優位性を説明する図。

【発明を実施するための形態】

10

20

30

40

50

## 【0011】

以下、添付図面を参照しながら本発明をその例示的な実施形態を通して説明する。

## 【0012】

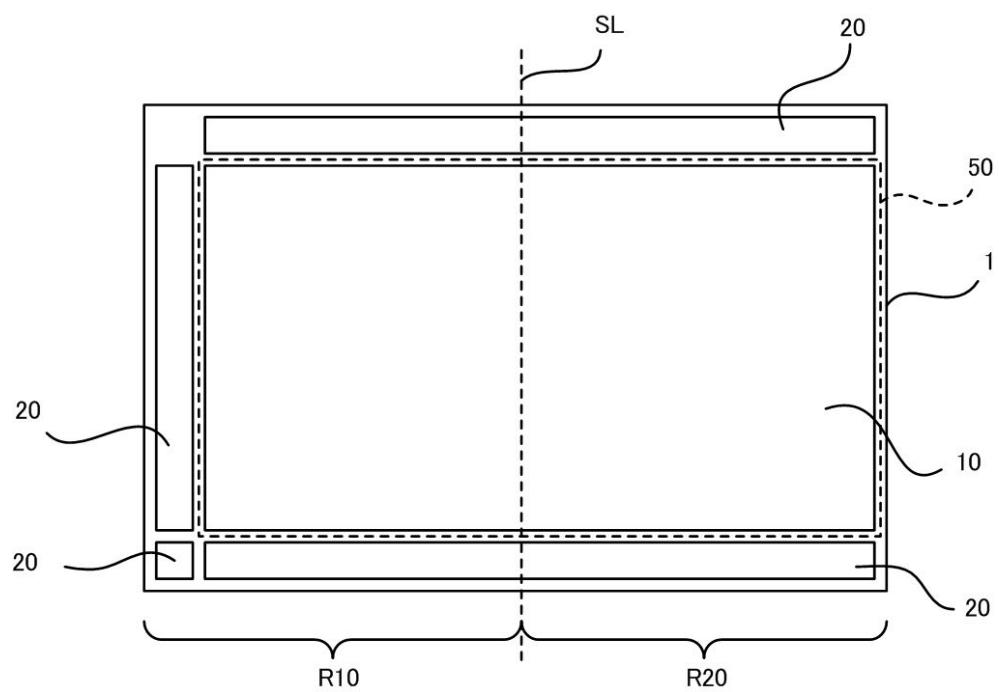

図1には、本発明の製造方法によって製造されうる固体撮像装置1が例示されている。固体撮像装置1は、例えば、MOS型イメージセンサまたはCCDイメージセンサとして構成されうる。固体撮像装置1は、複数行および複数列を構成するように複数の画素が配列された画素アレイ部10と、画素アレイ部10を駆動および/または制御する周辺回路部20とを有する。周辺回路部20は、例えば、行選択回路(例えば行走査回路)、列選択回路(例えば列走査回路)、信号読出回路および制御回路などを含みうる。画素アレイ部10を構成する素子(例えば、光電変換部、トランジスタ)は、共通のウエル領域50に配置され、周辺回路部20を構成する素子(例えば、トランジスタ)は、ウエル領域50の外側に配置されうる。

10

## 【0013】

本発明の実施形態における製造方法は、複数のフォトリソグラフィー工程を経て固体撮像装置1を製造するものである。該複数のフォトリソグラフィー工程は、少なくとも1つの第1リソグラフィー工程と、少なくとも1つの第2リソグラフィー工程とを含む。ここで、各第1リソグラフィー工程は、複数のフォトマスクを使って基板を露光(分割露光)する分割露光工程を含む。各第2リソグラフィー工程は、1つのフォトマスクを使って基板を露光(非分割露光)する非分割露光工程を含む。固体撮像装置1を製造するための基板(例えば半導体基板)は、典型的には複数のチップ領域を含み、各チップ領域に1つの固体撮像装置1が形成され、その後に該基板がダイシングされうる。

20

## 【0014】

分割露光工程では、各チップ領域は、分割線SLで複数の領域、例えば、第1領域R10および第2領域R20に分割して露光される。より具体的には、分割露光工程では、第1領域R10が第1フォトマスクを使用して露光され、第2領域R20が第2フォトマスクを使用して露光される。ここで、第1フォトマスクおよび第2フォトマスクは、互いに異なる部材に形成されてもよいし、1つの部材の互いに異なる領域に形成されてもよい。

20

## 【0015】

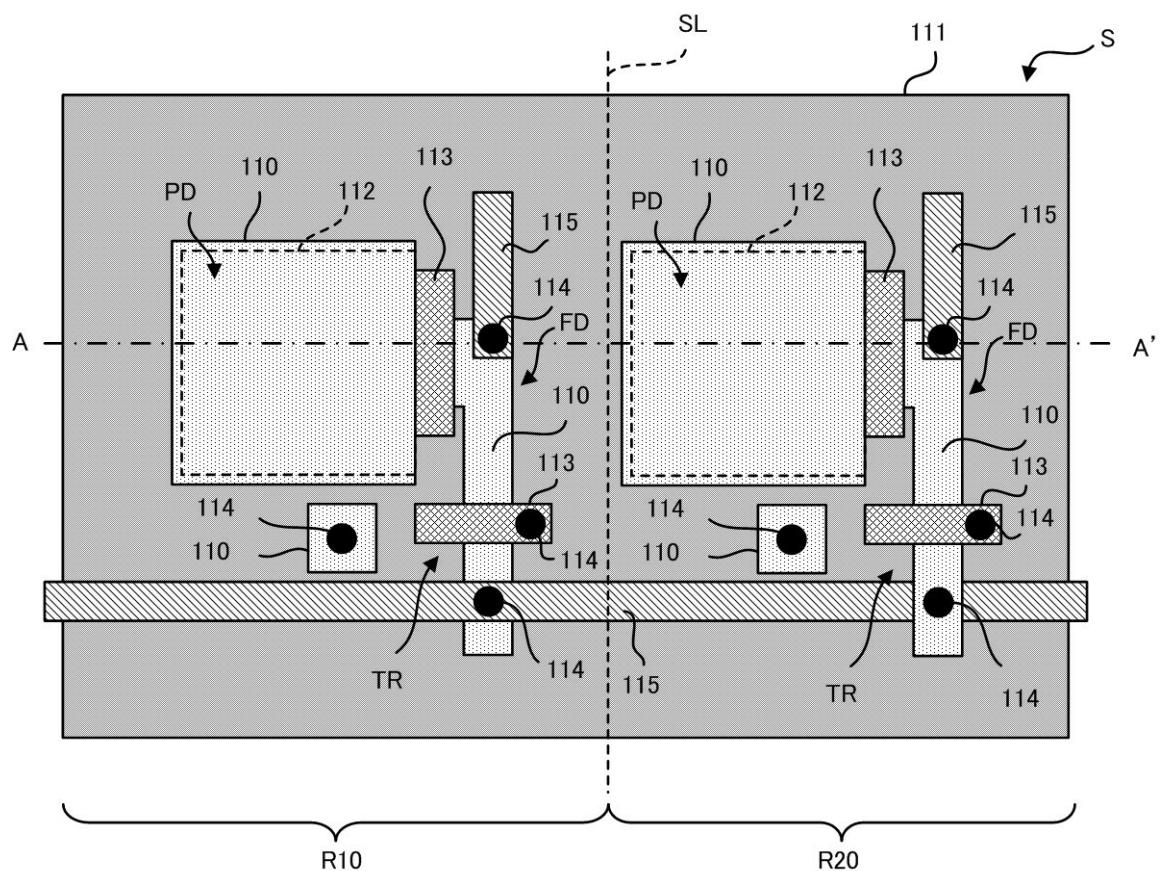

図2(a)は、図1に例示された固体撮像装置1の画素アレイ部10の分割線SL付近における構成を模式的に示す平面図である。図2(b)は、図2(a)のA-A'線にそった断面の構成を模式的に示す断面図である。なお、図2(a)、(b)において、カラーフィルタ、マイクロレンズなどが省略されている。固体撮像装置1の画素アレイ部10は、活性領域110と、素子分離領域111とを含みうる。素子分離領域111は、例えば、STI(Shallow Trench Isolation)またはLOCOS(Local Oxidation of Silicon)でありうる。活性領域110には、光電変換部PDおよび複数のトランジスタTRが配置されている。本実施形態では、素子分離領域111には、STI117が形成されている。

30

## 【0016】

ウエル領域50は、半導体領域60の上に形成されうる。ウエル領域50の導電型(例えばP型)は、例えば、半導体領域60の導電型と同じであり、不純物濃度は半導体領域60の不純物濃度よりも低く設定されうる。光電変換部PDは、ウエル領域50に形成された電荷蓄積領域112を含みうる。電荷蓄積領域112の導電型(例えばN型)は、ウエル領域50の導電型(例えばP型)と異なる。光電変換部PDは、電荷蓄積領域112の上に配置された半導体領域(表面保護領域)116を含みうる。半導体領域116の導電型(例えばP型)は、電荷蓄積領域112の導電型(例えばN型)と異なる。

40

## 【0017】

複数のトランジスタTRの1つは、例えば、光電変換部PDに蓄積された電荷をフローティングディフュージョンFDに転送する転送トランジスタでありうる。ここで、フローティングディフュージョンFDの導電型(例えばN型)は、電荷蓄積領域112の導電型と同じである。複数のトランジスタTRの他の1つは、フローティングディフュージョン

50

F D の電位に応じた信号を垂直信号線（不図示）に出力する増幅トランジスタでありうる。複数のトランジスタ T R の更に他の 1 つは、フローティングディフュージョン F D の電位をリセットするリセットトランジスタでありうる。トランジスタ T R のゲート電極は、例えば、ポリシリコンパターン 1 1 3 で構成されうる。活性領域 1 1 0 およびポリシリコンパターン 1 1 3 には、コンタクトホール 1 1 4 に充填されたプラグが接続されうる。当該プラグには、メタル配線パターン（第 1 配線層パターン）1 1 5 が接続されうる。図 2 ( a )、( b ) では、省略されているが、第 1 配線層パターンとしてのメタル配線パターン 1 1 5 の上には、第 2 配線層パターンが配置されうる。また、第 2 配線層パターンには、第 3 配線層パターンが配置されてもよい。固体撮像装置 1 は、典型的には、遮光パターン 1 2 0 を有しうる。

10

## 【 0 0 1 8 】

分割露光工程を含む少なくとも 1 つの第 1 リソグラフィー工程は、例えば、基板 S に活性領域 1 1 0 を定義するためのレジストパターンを形成するリソグラフィー工程を含みうる。活性領域 1 1 0 は、それを定義するためのレジストパターンの開口部（基板 S の露出部）に素子分離領域 1 1 1 を形成することによって定義されうる。

## 【 0 0 1 9 】

前記少なくとも 1 つの第 1 リソグラフィー工程は、基板 S に電荷蓄積領域 1 1 2 を定義するためのレジストパターンを形成するリソグラフィー工程を含みうる。光電変換部 P D が電荷蓄積領域 1 1 2 および半導体領域 1 1 6 を含む場合、前記少なくとも 1 つの第 1 リソグラフィー工程は、更に、基板 S に半導体領域 1 1 6 を定義するためのレジストパターンを形成するリソグラフィー工程を含みうる。

20

## 【 0 0 2 0 】

前記少なくとも 1 つの第 1 リソグラフィー工程は、更に、隣り合う電荷蓄積領域 1 1 2 の間に配置されたポテンシャルバリア領域 1 1 9 を定義するためのレジストパターンを形成するリソグラフィー工程を含みうる。ここで、ポテンシャルバリア領域 1 1 9 の導電型（例えば P 型）は、電荷蓄積領域 1 1 2 の導電型とは異なる。前記少なくとも 1 つの第 1 リソグラフィー工程は、更に、素子分離領域 1 1 1 の周囲（下面を含む）に配置されるチャネルトップ領域 1 1 8 を定義するためのレジストパターンを形成するリソグラフィー工程を含みうる。ここで、チャネルトップ領域 1 1 8 の導電型は、電荷蓄積領域 1 1 2 の導電型とは異なる。

30

## 【 0 0 2 1 】

非分割露光工程を含む少なくとも 1 つの第 2 リソグラフィー工程は、例えば、基板 S にウエル領域 5 0（図 1 参照）を定義するためのレジストパターンを形成するリソグラフィー工程を含みうる。前記少なくとも 1 つの第 2 リソグラフィー工程は、更に、遮光パターン 1 2 0 を定義するためのレジストパターンを形成するリソグラフィー工程を含みうる。

## 【 0 0 2 2 】

設計および製造の観点で許容される場合、前記少なくとも 1 つの第 2 リソグラフィー工程は、ゲート電極を含むポリシリコンパターン 1 1 3 を定義するためのレジストパターンを形成するリソグラフィー工程を含んでもよい。設計および製造の観点で許容される場合、前記少なくとも 1 つの第 2 リソグラフィー工程は、メタル配線パターン 1 1 5 または他の不図示のメタル配線パターンを形成するリソグラフィー工程を含んでもよい。

40

## 【 0 0 2 3 】

以下、図 1 ~ 図 3 を参照しながら固体撮像装置 1 の製造方法を例示的に説明する。まず、基板 S としてシリコン基板を準備し、非分割露光工程を含む第 2 リソグラフィー工程によって、基板 S の上に、ウエル領域 5 0 を定義する第 1 レジストパターンを形成する。そして、第 1 レジストパターンをイオン注入マスクとして基板 S にイオンを注入することによってウエル領域 5 0 を形成する（図 1、図 2 ( b ) 参照）。ここで、ウエル領域 5 0 の形成後に、ポテンシャルバリア領域 1 1 9 を形成することができる。ポテンシャルバリア領域 1 1 9 を定義するためのレジストパターンは、分割露光工程を含む第 1 リソグラフィー工程によって形成されることが好ましい。

50

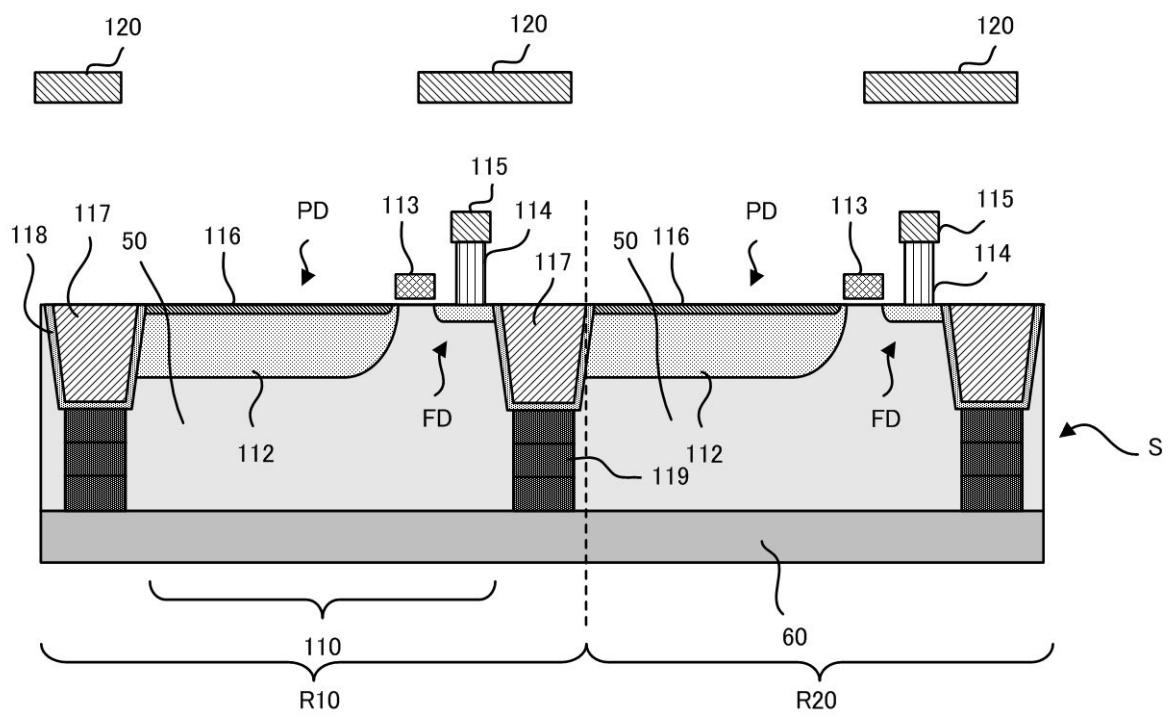

## 【0024】

次いで、分割露光工程を含む第1リソグラフィー工程によって、基板Sの上に、活性領域110を定義するための第2レジストパターンを形成する。第2レジストパターンは、素子分離領域111を形成すべき領域を露出させる開口を有する。第2レジストパターンをエッティングマスクとして基板Sをエッティングしてトレンチを形成する。次いで、該トレンチにイオンを注入することによってチャネルトップ領域118を形成し、その後、該トレンチに絶縁膜を形成することによってSTIで構成された素子分離領域111を形成する(図2(a)、図2(b)、図3(a)参照)。ここで、チャネルトップ領域118を形成するためのマスクとして、第2レジストパターンとは異なるレジストパターンを形成してもよい。この場合、分割露光工程を含む第1リソグラフィー工程によって当該マスクを形成することが好ましい。このような工程に代えて、LOCOS法によって素子分離領域111を形成してもよい。ここで、ポテンシャルバリア領域119を形成してもよい。

10

## 【0025】

次いで、分割露光工程を含む第1リソグラフィー工程によって、基板Sの上に、電荷蓄積領域112を定義するための第3レジストパターンを形成する。そして、第3レジストパターンをマスクとして基板Sにイオンを注入することによって電荷蓄積領域112を形成する(図2(a)、図2(b)、図3(a)参照)。ここで、この実施形態では、活性領域110を定義するための第2レジストパターンおよび電荷蓄積領域112を定義するための第3レジストパターンは、分割露光工程を含む第1リソグラフィー工程で形成される。これにより、活性領域110(または素子分離領域111)と電荷蓄積領域112とを正確に位置合わせすることができ、画素アレイ部10を構成する複数の画素の全体にわたって感度やノイズ(例えば暗電流ノイズ)を均一化することができる。活性領域110(または素子分離領域111)と電荷蓄積領域112とのアライメント誤差が大きくなると、電荷蓄積領域112とそれに接する領域とのPN接合容量が低下し、感度が低下しうる。また、活性領域110(または素子分離領域111)と電荷蓄積領域112とのアライメント誤差が大きくなると、電荷蓄積領域112と素子分離領域111が接触しうる。この場合、暗電流ノイズが増加したり、暗電流ノイズの領域間ばらつきが大きくなったりしうる。

20

## 【0026】

30

次いで、基板Sの上にポリシリコン膜を形成する。そして、分割露光工程を含む第1リソグラフィー工程、又は、非分割露光工程を含む第2リソグラフィー工程によって、ゲート電極を含むポリシリコンパターン113を定義するための第4レジストパターンを形成する。次いで、第4レジストパターンをエッティングマスクとしてポリシリコン膜をエッティングすることによってポリシリコンパターン113を形成する(図2(a)、図2(b)、図3(b)参照)。ここで、半導体領域116を形成する場合には、そのための第5レジストパターンを形成し、第5レジストパターンをイオン注入マスクとして基板Sにイオンを注入することによって半導体領域116を形成することができる。第5レジストパターンは、分割露光工程を含む第1リソグラフィー工程で形成されることが好ましいが、非分割露光工程を含む第2リソグラフィー工程で形成されてもよい。

40

## 【0027】

次いで、ポリシリコンパターン113が形成された基板Sの上に層間絶縁膜(不図示)を形成する。そして、第6レジストパターンを形成し、第6レジストパターンをエッティングマスクとして層間絶縁膜(不図示)をエッティングすることによってコンタクトホール114を形成する(図2(a)、図2(b)、図3(c))。ここで、第6レジストパターンは、分割露光工程を含む第1リソグラフィー工程で形成されることが好ましいが、非分割露光工程を含む第2リソグラフィー工程で形成されてもよい。コンタクトホール114は、導電体(例えば、メタル)によって埋め込まれる。

## 【0028】

次いで、層間絶縁膜(不図示)が形成された基板Sの上にメタル膜(例えばAl-Cu

50

膜)を形成する。そして、第7レジストパターンを形成し、第7レジストパターンをエッチングマスクとしてメタル膜をエッチングすることによってメタル配線パターン115を形成する(図2(a)、図2(b)、図3(d))。ここで、第7レジストパターンは、分割露光工程を含む第1リソグラフィー工程で形成されることが好ましいが、非分割露光工程を含む第2リソグラフィー工程で形成されてもよい。以下、メタル配線パターン115の上の配線構造、遮光パターン120、カラーフィルタおよびマイクロレンズなどが形成されうる。

#### 【0029】

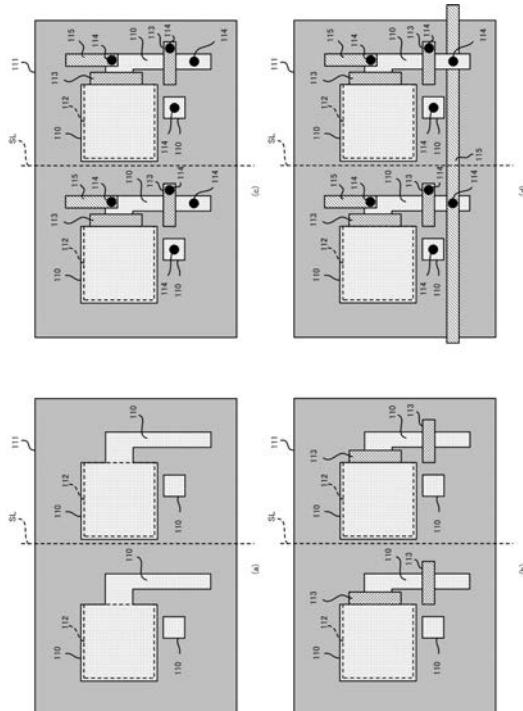

以下、図4を参照しながら、活性領域110と電荷蓄積領域112の形成において分割露光工程を含む第1リソグラフィー工程を適用することの優位性について説明する。図4(a)の例では、活性領域110および電荷蓄積領域112が分割露光工程を含む第1リソグラフィー工程を適用して形成されている。第1領域R10の活性領域110と第2領域R20の活性領域110との間には、アライメント誤差E1があり、図4(a)ではそれが強調して示されている。しかしながら、第1領域R10の電荷蓄積領域112は、第1領域R10の活性領域110に対してアライメントされ、第2領域R20の電荷蓄積領域112は、第2領域R20の活性領域110に対してアライメントされている。よって、第1領域R10においても、第2領域R20においても、活性領域110と電荷蓄積領域112との間のアライメント精度は、分割露光工程を実施する露光装置の精度に依存した高い精度となる。

#### 【0030】

図4(b)には比較例が示されている。図4(b)の比較例では、活性領域110が分割露光工程を含む第1リソグラフィー工程を適用して形成され、電荷蓄積領域112が非分割露光工程を含む第2リソグラフィー工程を適用して形成されている。第1領域R10の活性領域110と第2領域R20の活性領域110との間には、アライメント誤差E2がある。非分割露光工程を含む第2リソグラフィー工程では、第1領域R10に対するアライメントと第2領域R20に対するアライメントとを個別に実施することができない。よって、活性領域110と電荷蓄積領域112の間のアライメント精度が第1領域R10および第2領域R20の双方において低くなりうる。このように、活性領域110、すなわち素子分離領域111と、電荷蓄積領域112との距離が第1領域R10と第2領域R20とで異なると、素子分離領域111の結晶欠陥に起因するノイズが信号に混入する量が異なってしまう。すると、第1領域R10と第2領域R20とで画像に差が生じ、境界に筋が出来てしまう。

#### 【0031】

一方、ウエル領域50は、その境界が画素アレイ部10と周辺回路部20との境界付近に存在するので、アライメント精度に対する要求が低く、非分割露光工程を含む第2リソグラフィー工程を適用することができる。これはコストの低減に寄与する。遮光パターン120についても、アライメント精度に対する要求が低いので、非分割露光工程を含む第2リソグラフィー工程を適用することができ、これはコストの低減に寄与する。

#### 【0032】

更に、電荷蓄積領域112とそれとPN接合を形成する領域とのアライメント誤差が大きくなると、電荷蓄積領域112とそれに接する領域とのPN接合容量が第1領域R10と第2領域R20とで変わってしまい、領域間の画質が変わってしまう。しかし、本実施形態においては、電荷蓄積領域112とそれとPN接合を形成する領域とは、分割露光工程を含む第1リソグラフィー工程で形成される。よって、より高品質の画像を得ることが可能となる。ここで、電荷蓄積領域112とPN接合を形成する領域とは、例えば、半導体領域116、チャネルトップ領域118、ポテンシャルバリア領域119などが挙げられる。

#### 【0033】

本発明のように、活性領域110と電荷蓄積領域112とを第1リソグラフィーにて形成することで、画質を向上することが可能となる。また、電荷蓄積領域112とPN接合

10

20

30

40

50

を形成する領域を第1リソグラフィーにて形成することで、感度あるいはノイズの均一化が可能となり、画質が向上する。

【図1】

【図2】

(a)

(b)

【図3】

【図4】

(a)

(b)

---

フロントページの続き

(72)発明者 熊野 秀臣

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

F ター&ム(参考) 4M118 AB01 BA10 BA14 CA03 CA32 DD04 DD12 EA01 EA14 FA06

FA27 FA28 FA33 GB19

5C024 AX01 CY47 GY31 GZ36

5F146 AA11