(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6494167号

(P6494167)

(45) 発行日 平成31年4月3日(2019.4.3)

(24) 登録日 平成31年3月15日(2019.3.15)

(51) Int.Cl.

H04N 19/86 (2014.01)

F 1

H04N 19/86

請求項の数 4 (全 15 頁)

(21) 出願番号 特願2014-50333 (P2014-50333)

(22) 出願日 平成26年3月13日 (2014. 3. 13)

(65) 公開番号 特開2014-192896 (P2014-192896A)

(43) 公開日 平成26年10月6日 (2014. 10. 6)

審査請求日 平成29年1月31日 (2017. 1. 31)

(31) 優先権主張番号 1146/MUM/2013

(32) 優先日 平成25年3月26日 (2013. 3. 26)

(33) 優先権主張国 インド (IN)

(73) 特許権者 391002340

テクトロニクス・インコーポレイテッド

TEKTRONIX, INC.

アメリカ合衆国 オレゴン州 97077

-0001 ピーバートン サウスウエスト

カール・ブラウン・ドライブ 141

50

(74) 代理人 110001209

特許業務法人山口国際特許事務所

(72) 発明者 ベンカタパリ・アラムセッティ

インド アンドラ プラデシ 52226

7 グントウール・ディスト レパレ・マ

ンダル 8-153/1 ペテル・ポスト

エス/オー・ラマラオ

最終頁に続く

(54) 【発明の名称】 ブロック・アトリビュート決定システム及び方法

## (57) 【特許請求の範囲】

## 【請求項 1】

コンピュータと、

上記コンピュータ内のメモリと、

上記コンピュータの上記メモリに蓄積されたコンテンツと、

少なくとも 1 つの次元において上記コンテンツの複数のエッジ差分を順次計算するエッジ差分計算器と、

複数の上記エッジ差分のローリング標準偏差を計算し、第 1 エッジ差分に対応する第 1 ローリング標準偏差と、上記第 1 エッジ差分の直前に計算された第 2 エッジ差分に対応する第 2 ローリング標準偏差との差が所定しきい値以下の場合に、上記第 1 エッジ差分を濾波することによって、濾波されたエッジ差分を発生するエッジ差分フィルタと、

上記濾波されたエッジ差分からブロック・アトリビュートを決定するブロック・アトリビュート計算器と

を具えるブロック・アトリビュート決定システム。

## 【請求項 2】

上記エッジ差分計算器は、少なくとも 1 次元に直角なコンテンツ内で隣接した複数のピクセルの間の絶対差分を計算し、少なくとも 1 次元に直角で隣接した上記複数のピクセル間の上記絶対差分を加算して和を求め、少なくとも 1 次元内のピクセルの数により上記和をスケーリングして上記エッジ差分を発生するように構成されている請求項 1 のブロック・アトリビュート決定システム。

## 【請求項 3】

少なくとも 1 つの次元でコンテンツの複数のエッジ差分を順次計算する処理と、複数の上記エッジ差分のローリング標準偏差を計算し、第 1 エッジ差分に対応する第 1 ローリング標準偏差と、上記第 1 エッジ差分の直前に計算された第 2 エッジ差分に対応する第 2 ローリング標準偏差との差が所定しきい値以下の場合に、上記第 1 エッジ差分を濾波することによって、濾波されたエッジ差分を発生する処理と、

上記濾波されたエッジ差分から少なくとも 1 つのブロック・アトリビュートを決定する処理と

を具えるブロック・アトリビュート決定方法。

## 【請求項 4】

10

少なくとも 1 つの次元でコンテンツの複数のエッジ差分を順次計算する処理は、上記コンテンツの垂直次元にて垂直エッジ差分と、上記コンテンツの水平次元にて水平エッジ差分とを計算する処理を含み、

上記濾波されたエッジ差分を発生する処理は、上記垂直エッジ差分を濾波して、濾波された垂直エッジ差分を発生する処理と、上記水平エッジ差分を濾波して、濾波された水平エッジ差分を発生する処理とを含み、

上記濾波されたエッジ差分から少なくとも 1 つのブロック・アトリビュートを決定する処理は、上記濾波された垂直エッジ差分から少なくとも第 1 ブロック・アトリビュートを決定する処理と、上記濾波された水平エッジ差分から少なくとも第 2 ブロック・アトリビュートを決定する処理とを含む請求項 3 のブロック・アトリビュート決定方法。

20

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、イメージ及びビデオのコンテンツに関し、特に、イメージ及びビデオのコンテンツにおけるブロッキング・アーティファクトのサイズ及びオフセットであるブロック・アトリビュートを決定するシステム及び方法に関する。

## 【背景技術】

## 【0002】

ブロック・ベースの変換符号化は、イメージ及びビデオの符号化にとって最も普及したアプローチである。JPEG、H.26x 及び MPEG の如きほとんどの現在のイメージ及びビデオの符号化標準は、ブロック・ベースのディスクリート・コサイン変換を用いている。一般に、この変換は、サイズ  $8 \times 8$  のブロックに適用されるし、H.264においては、この変換がサイズ  $4 \times 4$  のブロック（最小サイズ）に適用される。デコーダにおいて、量子化変換係数を逆量子化し、逆変換して、元のイメージを回復させる。よって、低いビット・レートにおいて、サイズ  $8 \times 8$  又は  $4 \times 4$ 、若しくはこれらサイズの整数倍のイメージ及びビデオの符号化ブロッキング・アーティファクト（ブロック・アーティファクト）が予測できる。

30

## 【先行技術文献】

## 【特許文献】

## 【0003】

## 【特許文献 1】特表 2010-532935 号公報

40

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0004】

しかし、実際においては、空間的スケーリング（拡大・縮小）のためにブロッキング・アーティファクトのサイズが変化するかもしだれず、また、ブロッキング・グリッドにおいて偏差が生じるかもしだれない。よって、正確なブロッキング・アーティファクトのサイズ及びグリッド位置を検出しなければ、ブロッキネスの測定基準は、結果的に役に立たない。よって、間違ったピクセル位置で且つ間違ったブロッキング・アーティファクトのサイズで、ブロッキネスを計算することになる。したがって、ブロッキネス・スコアを計算す

50

る前に、適切なブロックネス測定基準にとって、ブロッキング・アーティファクトのサイズ及びオフセットを知る必要がある。

【0005】

従来技術に関連した上述及びその他の問題を解決する必要がある。

【課題を解決するための手段】

【0006】

本発明の概念は、コンピュータ・システムを含んでいる。このコンピュータ・システムには、コンテンツが蓄積される。このコンテンツを分析して、エッジ差分を決定する。これらエッジ差分を濾波して、これらから、ブロックのサイズ及びオフセットの如きブロック・アトリビュートを計算できる。

10

【0007】

本発明の更なる概念は、次の通りである。

(1) コンピュータと；上記コンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1つの次元において上記コンテンツのエッジ差分を計算するエッジ差分計算器と；上記エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・アトリビュートを決定するブロック・アトリビュート計算器とを備えたシステム。

(2) 上記エッジ差分計算器は、少なくとも1次元に直角なコンテンツ内で近傍した複数のピクセルの間の絶対差分を計算し、少なくとも1次元に直角で近接した上記複数のピクセル間の上記絶対差分を加算して和を求め、少なくとも1次元内のピクセルの数により上記和をスケーリングして上記エッジ差分を発生するように構成されている概念1のシステム。

20

(3) 上記エッジ差分フィルタは、上記エッジ差分のローリング標準偏差を計算し、第1エッジ差分の直前の第2エッジ差分に対応する第2ローリング標準偏差よりも大きい所定しきい値未満の第1ローリング標準偏差に対応する上記第1エッジ差分を濾波するように構成された概念1のシステム。

(4) 上記ブロック・アトリビュート計算器は、上記濾波されたエッジ差分からブロック・サイズを決定するブロック・サイズ計算器を含んでいる概念1のシステム。

【0008】

(5) 上記ブロック・サイズ計算器は、隣接し濾波された複数のエッジ差分の間の最も一般的な差分として上記ブロック・サイズを決定するように構成されている概念4のシステム。

30

(6) 上記ブロック・アトリビュート計算器は、上記濾波されたエッジ差分からブロック・オフセットを決定するブロック・オフセット計算器を更に含んでいる概念4のシステム。

(7) 上記ブロック・オフセット計算器は、濾波されたエッジ差分と上記コンテンツのエッジとの間のピクセルの数として上記ブロック・オフセットを決定するように構成されている概念6のシステム。

【0009】

(8) 少なくとも1つの次元でコンテンツのエッジ差分を計算し；上記エッジ差分を濾波して、濾波されたエッジ差分を発生し；上記濾波されたエッジ差分から少なくとも1つのブロック・アトリビュートを決定する方法。

40

(9) 少なくとも1つの次元でコンテンツのエッジ差分を計算することは、上記コンテンツの垂直次元にて垂直エッジ差分と、上記コンテンツの水平次元にて水平エッジ差分とを計算することを含み、；上記エッジ差分を濾波して、濾波されたエッジ差分を発生することは、上記垂直エッジ差分を濾波して、濾波された垂直エッジ差分を発生することと、上記水平エッジ差分を濾波して、濾波された水平エッジ差分を発生することを含み；上記濾波されたエッジ差分から少なくとも1つのブロック・アトリビュートを決定することは、上記濾波された垂直エッジ差分から少なくとも第1ブロック・アトリビュートを決定することと、上記濾波された水平エッジ差分から少なくとも第2ブロック・アトリビュートを

50

決定することを含む概念 8 の方法。

(10) 少なくとも 1 つの次元でコンテンツのエッジ差分を計算することは；上記少なくとも 1 つの次元に直角なコンテンツにて隣接する複数のピクセルの間の絶対差分を計算することと；上記少なくとも 1 つの次元に直角な上記隣接する複数のピクセルの間の上記絶対差分を加算して、和を発生することと；上記少なくとも 1 つの次元にてピクセルの数により上記和をスケーリングして、上記エッジ差分を発生することを含む概念 8 の方法。

【0010】

(11) 上記エッジ差分を濾波して、濾波されたエッジ差分を発生することは；上記エッジ差分のローリング標準偏差を計算することと；第 1 エッジ差分の直前の第 2 エッジ差分に対応する第 2 ローリング標準偏差よりも大きい所定しきい値未満の第 1 ローリング標準偏差に対応する上記第 1 エッジ差分を濾波することを含む概念 8 の方法。 10

(12) 上記濾波されたエッジ差分から少なくとも 1 つのブロック・アトリビュートを決定することは、上記濾波されたエッジ差分からブロック・サイズを決定することを含む概念 8 の方法。

(13) 上記濾波されたエッジ差分からブロック・サイズを決定することは、隣接し濾波された複数のエッジ差分の間の最も一般的な差分として上記ブロック・サイズを決定することを含む概念 12 の方法。

(14) 上記濾波されたエッジ差分から少なくとも 1 つのブロック・アトリビュートを決定することは、上記濾波されたエッジ差分からブロック・オフセットを決定することを更に含む概念 12 の方法。 20

(15) 上記濾波されたエッジ差分からブロック・オフセットを決定することは、濾波されたエッジ差分と上記コンテンツのエッジの間のピクセルの数として上記ブロック・オフセットを決定することを含む概念 14 の方法。

【図面の簡単な説明】

【0011】

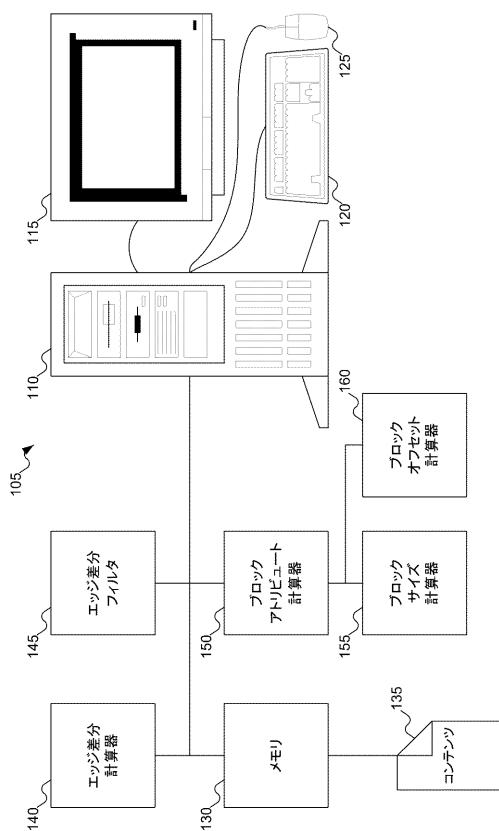

【図 1】本発明の実施例により、コンテンツ内のブロック・アトリビュートを決定するコンピュータ・システムを示す図である。

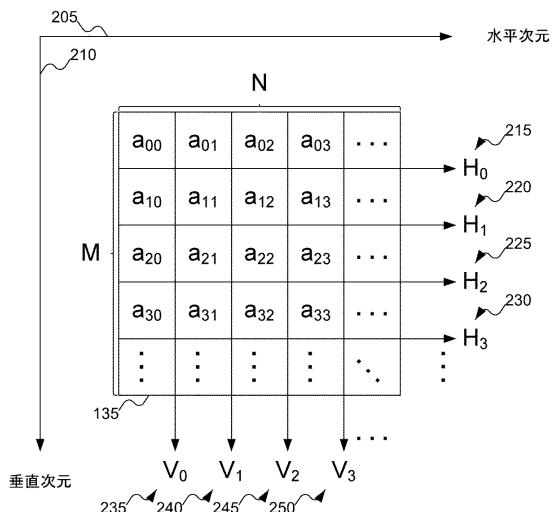

【図 2】図 1 のコンテンツ内で計算したエッジ差分を示す図である。

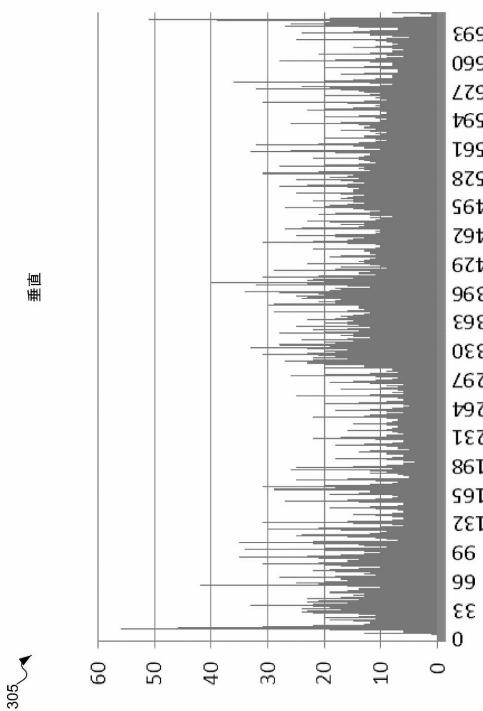

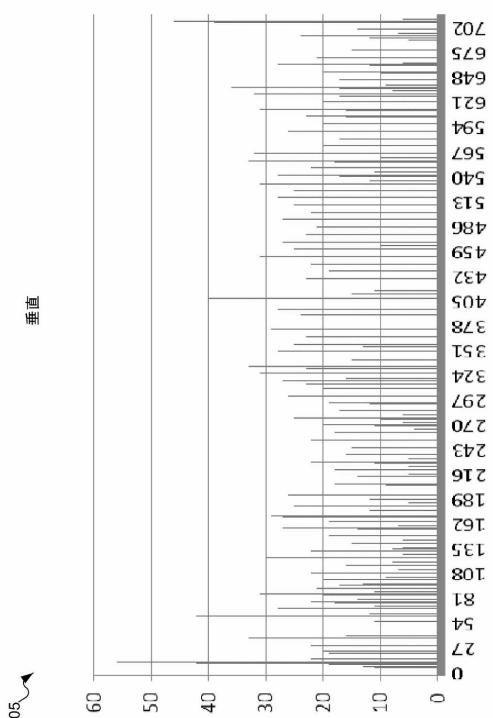

【図 3】グラフにて垂直次元でプロットした図 2 のエッジ差分を示す図である。

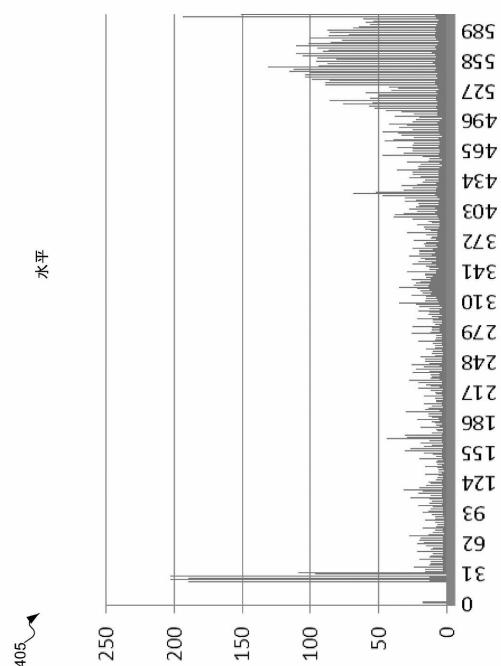

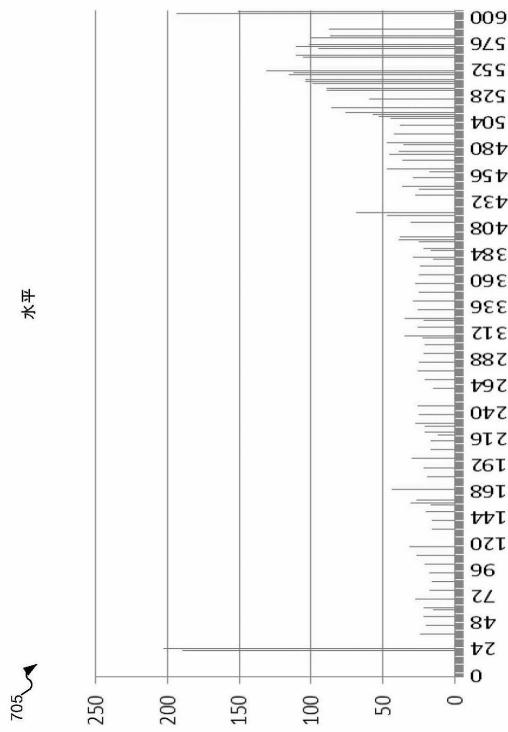

【図 4】グラフにて水平次元でプロットした図 2 のエッジ差分を示す図である。 30

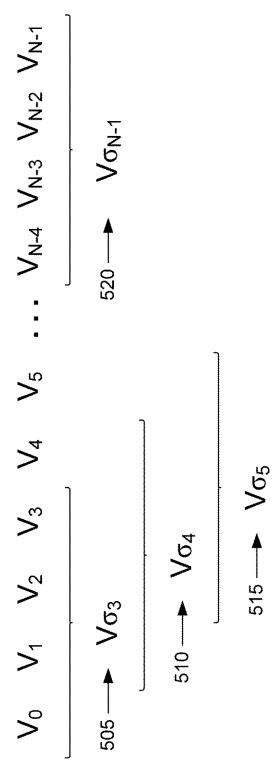

【図 5】図 2 における垂直次元でのエッジ差分のローリング標準偏差を計算する際の説明図である。

【図 6】図 5 に示す如くローリング標準偏差を用いて濾波された図 3 のエッジ差分を示す図である。

【図 7】図 5 に示す如くローリング標準偏差を用いて濾波された図 4 のエッジ差分を示す図である。

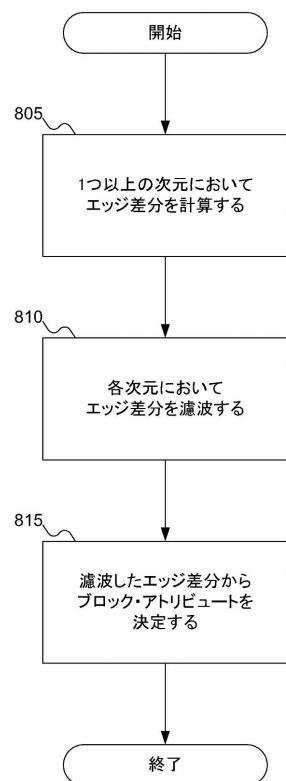

【図 8】本発明の実施例により、図 1 のシステムにおけるコンテンツに対してブロック・アトリビュートを決定する手順を示す流れ図である。

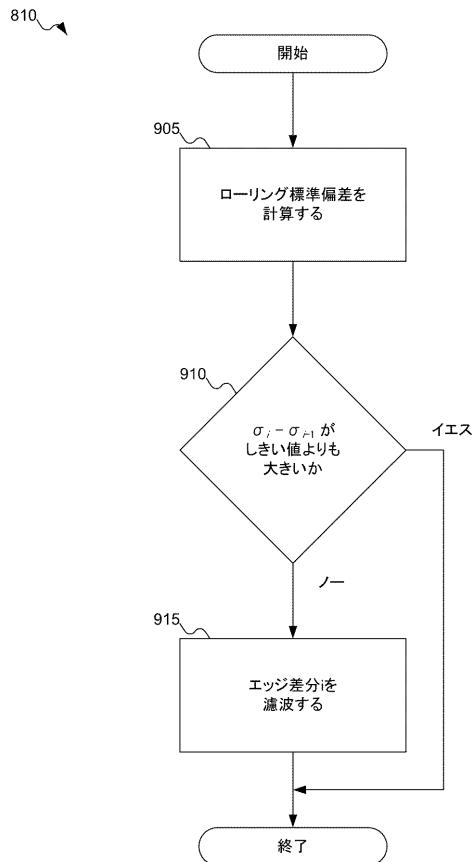

【図 9】図 8 の流れ図において、いかにエッジ差分を濾波するかの詳細を示す流れ図である。 40

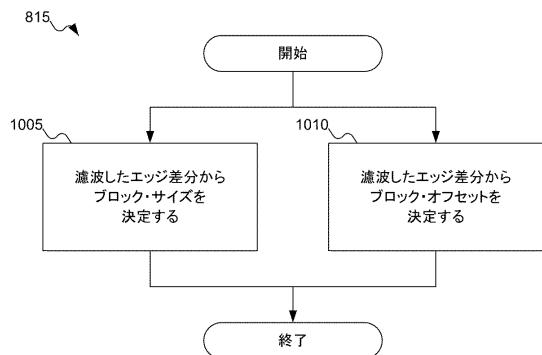

【図 10】図 8 の流れ図において、いかにブロック・アトリビュートを決定するかの詳細を示す流れ図である。

【発明を実施するための形態】

【0012】

図 1 は、本発明の実施例により、コンテンツ内のブロック・アトリビュートを決定する（求める）コンピュータ・システムを示す図である。この図 1 において、コンピュータ・システム 105 は、コンピュータ 110 と、モニタ 115 と、キーボード 120 と、マウス 125 とを含んでいるように図示している。このコンピュータ・システム 105 が他のコンポーネント、例えば、プリンタなどの他の入力／出力装置を含んでもよいことが当業者には理解できよう。更に、図 1 のコンピュータ・システム 105 は、従来の内部コンボ 50

ーネント、例えば、中央処理装置（図示せず）、メモリ130、蓄積装置（図示せず）などを含むこともできる。図1に示さないが、コンピュータ・システム105は、他のコンピュータ・システムと直接的又は間接的に、若しくは任意形式のネットワーク（図示せず）を介して相互作用することができる点が当業者には理解できよう。最後に、図1は、コンピュータ・システム105を従来のディスクトップ・コンピュータとして示しているが、かかるコンピュータ・システム105は、ここでのコンピュータ・システム105に属するサービスを提供できる任意の形式のマシーン又は計算装置、例えば、ラップトップ・コンピュータ、パーソナル・デジタル・アシスタント（PDA）、又は携帯電話などでもよいことが当業者には理解できよう。

## 【0013】

10

コンピュータ110は、メモリ130に蓄積されているコンテンツ135のブロック・アトリビュートを決定するのに用いるコンポーネントを含んでいる。コンピュータ110は、エッジ差分計算器140と、エッジ差分フィルタ145と、ブロック・アトリビュート計算器150を含むことができる。図2～図4を参照して後述するように、エッジ差分計算器140を用いて、エッジ差分を決定することができる。図5～図7を参照して後述するように、エッジ差分フィルタ145を用いて、エッジ差分計算器140が発生したエッジ差分を濾波することができる。最後に、ブロック・アトリビュート計算器150を用いて、濾波されたエッジ差分からコンテンツ用のブロック・アトリビュートを決定することができる。

## 【0014】

20

ブロック・アトリビュートを計算する一部として、ブロック・アトリビュート計算器150は、ブロック・サイズ計算器155とブロック・オフセット計算器160とを含むことができる。ブロック・サイズ計算器155は、ブロッキング・アーティファクトのサイズを決定することができる。ブロック・オフセット計算器160は、ブロッキング・アーティファクトのオフセットを決定することができる。

## 【0015】

コンテンツが2次元（即ち、ビデオ・セグメントからのイメージ又はフレーム）であると仮定すると、ブロック・アトリビュート計算器150（即ち、ブロック・サイズ計算器155及びブロック・オフセット計算器160も含む）は、各次元において別々に動作する。すなわち、他の次元（例えば、水平次元）を参照することなく、1つの次元（例えば、垂直次元）にて、ブロッキング・アーティファクトのサイズとそのオフセットを決定することができる。これは、ブロッキング・アーティファクトが2次元よりも大きい次元で存在した場合、本発明を用いて、他の次元の各次元にてブロッキング・アーティファクトのアトリビュートを独立も決定することができることを意味する。

30

## 【0016】

図1は、メモリ130に蓄積されたコンテンツ135を示すが、コンテンツ135を任意所望の場所に蓄積できることが当業者には理解できよう。例えば、ネットワークされた場所からコンピュータ・システム105がコンテンツ135を引き出すことができる。または、他の可能な手段の中でも、USBキー、コンパクト・ディスク、DVD又はブルーレイ・ディスクの如きポータブル蓄積デバイスからコンテンツ135を読み取ることができる。コンテンツ135用の他の可能な信号源についても当業者には理解できよう。

40

## 【0017】

図2は、図1のコンテンツにて計算されたエッジ差分を示す。図2において、ピクセルのM行N列としてコンテンツ135を示す。上述の如く、コンテンツ135は、イメージでもよく、又は、コンテンツ135は、他の可能なものの中でもビデオ・ファイルからのフレームでもよい。コンテンツ135の行は、水平次元205方向に広がっていると言うことができる、コンテンツ135の列は、垂直次元210方向に広がっていると言うことができる。

## 【0018】

コンテンツ135中のピクセルを考えると、各次元にてエッジ差分を計算できる。よっ

50

て、例えば、水平エッジ差分 215、220、225 及び 230 を水平次元 205 にて示し、垂直エッジ差分 235、240、245 及び 250 を垂直次元 210 にて示す。

【0019】

以下の式を用いてエッジ差分を計算できる。なお、 $V_i$  が垂直エッジ差分で、 $H_i$  が水平エッジ差分で、ABS が絶対値を示し、 $a$  がピクセルを示す。

【0020】

【数1】

$$V_i = \frac{1}{N} \sum_{j=0}^{N-1} ABS(a_{ji} - a_{j(i+1)})$$

10

【0021】

【数2】

$$H_i = \frac{1}{M} \sum_{j=0}^{M-1} ABS(a_{ij} - a_{(i+1)j})$$

10

【0022】

ピクセルの N 列が存在するならば、N - 1 個の垂直エッジ差分が存在する。同様に、ピクセルの M 行が存在するならば、M - 1 個の水平エッジ差分が存在する。これらエッジ差分をグラフとしてプロットすると、図 3 及び図 4 に示すようになる。

【0023】

20

図 3 及び図 4 に示すエッジ差分から直接的にブロック・アトリビュートを計算することが可能であるが、非常に多くの情報を処理しなければならない。ブロック・アトリビュートの計算を簡単にするために、エッジ差分を濾波する。

【0024】

図 5 は、図 2 の垂直次元におけるエッジ差分のローリング標準偏差の計算を示す。図 5 において、4 つのエッジ差分、即ち、所定のエッジ差分とそれに先立つ 3 つのエッジ差分を取る。4 つのエッジ差分の標準偏差を計算でき、その値を  $V_i$  とする。明瞭にするため、垂直エッジ差分を用いて計算した標準偏差を  $V_i$  で表し、水平エッジ差分を  $H_i$  で表す。

【0025】

30

4 つのエッジ差分を用いることには、いくつかの利点がある。なお、これら 4 つのエッジ差分の 3 つは、所定エッジ差分の左側である。4 つのエッジ差分を用いることによる利点は、ブロッキング・アーティファクトのサイズが典型的には 4 の倍数であるという事実である。また、所定エッジ差分の左のエッジ差分を用いることの利点は、全てのエッジ差分がブロッキング・アーティファクトの一部であるときに、標準偏差が、ブロッキング・アーティファクトの一部でないエッジ差分の標準偏差と大きく異なるという事実である。

【0026】

ローリング標準偏差を計算すると、これらをペアで比較できる。 $V_i$  及び  $V_{i-1}$  の間の差分が 1 よりも大きければ、エッジ差分  $V_i$  は、濾波されたエッジ差分に含まれる。そうでなければ、 $V_i$  は、濾波されたエッジ差分から除去される。

40

【0027】

上述の説明において、隣接するローリング標準偏差の間の差分は、1 のしきい値と比較される。しかし、任意のしきい値を用いることができる。しきい値が大きくなれば、濾波されたエッジ差分には少ないエッジ差分が含まれる。これとは逆に、しきい値が小さくなれば、濾波されたエッジ差分には多くのエッジ差分が含まれる。

【0028】

ローリング標準偏差を用いて、エッジ差分を計算して、濾波されたエッジ差分を発生することができる。濾波されたエッジ差分の数は、完全なエッジ差分よりも少ない。図 6 及び図 7 は、図 5 に示す如きローリング標準偏差を用いて濾波された図 3 及び図 4 のエッジ差分を示す。

50

## 【0029】

濾波されたエッジ差分からブロック・アトリビュートを決定することができる。例えば、隣接し濾波されたエッジ差分の間の最も一般的な差分としてブロック・サイズを決定することができ、ブロックのエッジに対応する濾波されたエッジ差分のインデックスをブロック・サイズで割り算した後に、ブロック・オフセットを最も一般的な余りとして決定することができる。

## 【0030】

図8は、本発明の実施例により、図1のシステム内のコンテンツ用のブロック・アトリビュートを決定する過程を示す流れ図である。図8において、ステップ805にて、1つ以上の次元にてエッジ差分を計算する。ステップ810において、各次元において、エッジ差分を濾波する。ステップ815において、濾波されたエッジ差分に基づいて、ブロック・アトリビュートを計算する。

10

## 【0031】

図9は、図8の流れ図において、いかにエッジ差分を濾波するかの詳細を示す流れ図である。図9において、ステップ905にて、ローリング標準偏差を計算する。ステップ910にて、隣接した標準偏差の間の差分を計算して、しきい値と比較する。差分がしきい値よりも小さければ(ノー)、ステップ915にて、対応するエッジ差分を濾波する。そうでなければ(イエス)、対応エッジ差分が、濾波されたエッジ差分に含まれる。

## 【0032】

図10は、図8の流れ図において、いかにブロック・アトリビュートを決定するかの詳細な流れ図を示す。図10において、ステップ1005にて、濾波されたエッジ差分からブロック・サイズを決定する。代わりに、ステップ1010にて、濾波されたエッジ差分からブロック・オフセットを決定する。

20

## 【0033】

以下、本発明の概念を実行する適切なマシーンの簡単で一般的な説明を行う。典型的には、このマシーンは、システム・バスを含んでおり、このシステム・バスは、プロセッサと；例えばランダム・アクセス・メモリ(RAM)、リード・オンリ・メモリ(ROM)又は他の状態保持媒体などのメモリと；蓄積装置と；ビデオ・インターフェースと；入力/出力インターフェース・ポートとに結合する。このマシーンは、キーボード、マウスなどの従来の入力装置からの入力と共に、他のマシーンから受けた指示、仮想現実(VR)環境との相互作用、生物測定(バイオメトリック)フィードバック、又は他の入力信号によって、少なくとも部分的に制御される。ここで用いる用語「マシーン」は、単一のマシーン、又は、協働するマシーン若しくは装置と通信可能に結合されたシステムを広く含むことを意図する。例としてのマシーンは、パーソナル・コンピュータ、ワークステーション、サーバー、ポータブル・コンピュータ、ハンドヘルド装置、電話機、タブレットなどの如き計算装置と共に、例えば自動車、電車、タクシーなどの個人又は公共交通機関の如き交通機関の装置を含んでいる。

30

## 【0034】

マシーンは、プログラマブル又は非プログラマブル・ロジック・デバイス又はアレイ、用途限定集積回路、埋め込みコンピュータ、スマート・カードなどの如き埋め込み制御器を含んでもよい。マシーンは、ネットワーク・インターフェース、モ뎀又は他の通信結合器を介するなどして1つ以上の遠隔マシーンとの1つ以上の接続を使用できる。イントラネット、インターネット、ローカル・エリア・ネットワーク、ワイド・エリア・ネットワークなどの如き物理的及び/又は論理的ネットワークによって、複数のマシーンを相互接続してもよい。ネットワーク通信は、無線周波数(RF)、サテライト、マイクロ波、米国電子技術者協会(IEEE)810.11、ブルーツース、光、赤外線、ケーブル、レーザなど種々の有線及び/又は無線の短距離又は長距離の搬送波及びプロトコルを用いることが当業者には明らかであろう。

40

## 【0035】

本発明は、機能、手順、データ構造、アプリケーション・プログラムなどを含む関連デ

50

ータを参照して又はこれらに関連して説明できる。マシーンがこれらをアクセスすると、タスクを実行するか、又は、理論上のデータ形式若しくは低レベルのハードウェア・コンテキストを定義する。関連データは、例えば、RAM、ROMなどの揮発性及び/又は不揮発性メモリに蓄積できると共に、ハード・ドライブ、フロッピー（登録商標）ディスク、光蓄積装置、テープ、フラッシュ・メモリ、メモリ・スティック、デジタル・ビデオ・ディスク、生物学的（バイオロジカル）蓄積装置などを含む他の蓄積装置及びそれらの関連蓄積媒体にも蓄積できる。関連データは、物理的及び/又は論理的ネットワークを含む通信環境を介して、パケット、直列データ、並列データ、伝搬信号などの形式で伝送できる。また、関連データは、圧縮又は暗号化の形式でも用いることができる。関連データを分散環境で用いることもでき、マシーン・アクセスに対して局部的に及び/又は遠隔的にも蓄積できる。

【0036】

図示した実施例を参照して本発明の原理を説明したが、本発明の要旨を逸脱することなく、これら図示した実施例を配置変更及び細部変更できることが理解できよう。さらに、上述の説明は、特定の実施例についてであるが、他の構成も考慮できる。特に、「一実施例において」などの如き説明をここでは用いたが、これら句は、実施例の可能性を一般的に言及することを意味するものであり、本発明を特定実施例の構成に限定しようとするものではない。ここで用いる如く、これら用語は、他の実施例と組合せ可能な同じ又は異なる実施例も言及できる。

【0037】

本発明の実施例は、限定なく以下の記述にも拡張できる。

【0038】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元において上記コンテンツのエッジ差分を計算するエッジ差分計算器と；上記エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・アトリビュートを決定するブロック・アトリビュート計算器とを備えている。

【0039】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元に直角な上記コンテンツにて隣接する複数のピクセルの間の絶対差分を計算し、上記少なくとも1次元に直角な上記隣接する複数のピクセルの間の絶対差分を加算して、和を発生し、上記少なくとも1次元におけるピクセルの数により上記和をスケーリングして、少なくとも1次元での上記コンテンツのエッジ差分を発生するエッジ差分計算器と；上記エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・アトリビュートを決定するブロック・アトリビュート計算器とを備えている。

【0040】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元にて上記コンテンツの複数のエッジ差分を順次計算するエッジ差分計算器と；複数の上記エッジ差分のローリング標準偏差を計算し、第1エッジ差分に対応する第1ローリング標準偏差と、第1エッジ差分の直前に計算された第2エッジ差分に対応する第2ローリング標準偏差との差が所定しきい値以下の場合に、上記第1エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・アトリビュートを決定するブロック・アトリビュート計算器とを備えている。

【0041】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元にて上記コンテンツの複数のエッジ差分を順次計算するエッジ差分計算器と；各ローリング標準偏差

10

20

30

40

50

を計算するために4つのエッジ差分を用いて上記エッジ差分のローリング標準偏差を計算し、第1エッジ差分に対応する第1ローリング標準偏差と、第1エッジ差分の直前に計算された第2エッジ差分に対応する第2ローリング標準偏差との差が所定しきい値以下の場合に、上記第1エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・アトリビュートを決定するブロック・アトリビュート計算器とを備えている。

【0042】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元にて上記コンテンツの複数のエッジ差分を順次計算するエッジ差分計算器と；第1エッジ差分に対応する第1ローリング標準偏差を計算するために上記第1エッジ差分とこの第1エッジ差分の直前の少なくとも1つのエッジ差分とを用いて第1エッジ差分の第1ローリング標準偏差を計算し、第1エッジ差分の直前に計算された第2エッジ差分に対応する第2ローリング標準偏差を計算し、第1ローリング標準偏差と第2ローリング標準偏差の差が所定しきい値以下の場合に、上記第1エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・アトリビュートを決定するブロック・アトリビュート計算器とを備えている。

【0043】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元にて上記コンテンツのエッジ差分を計算するエッジ差分計算器と；上記エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・サイズを決定するブロック・サイズ計算器を含むブロック・アトリビュート計算器とを備えている。

【0044】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元にて上記コンテンツのエッジ差分を計算するエッジ差分計算器と；上記エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；隣接し濾波されたエッジ差分の間の最も一般的な差分としてブロック・サイズを決定するブロック・サイズ計算器を含むブロック・アトリビュート計算器とを備えている。

【0045】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元にて上記コンテンツのエッジ差分を計算するエッジ差分計算器と；上記エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・サイズを決定するブロック・サイズ計算器と、上記濾波されたエッジ差分からブロック・オフセットを決定するブロック・オフセット計算器とを含むブロック・アトリビュート計算器とを備えている。

【0046】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元にて上記コンテンツのエッジ差分を計算するエッジ差分計算器と；上記エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・サイズを決定するブロック・サイズ計算器と、濾波されたエッジ差分及び上記コンテンツのエッジの間のピクセルの数としてブロック・オフセットを決定するブロック・オフセット計算器とを含むブロック・アトリビュート計算器とを備えている。

【0047】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；上記コンテンツの垂直次元に

10

20

30

40

50

て垂直エッジ差分と上記コンテンツの水平次元にて水平エッジ差分とを計算するエッジ差分計算器と；上記垂直エッジ差分を濾波して、濾波された垂直エッジ差分を発生するとと共に、上記水平エッジ差分を濾波して、濾波された水平エッジ差分を発生するエッジ差分フィルタと；上記濾波された垂直エッジ差分から第1ブロック・アトリビュートを決定するとと共に、上記濾波された水平エッジ差分から第2ブロック・アトリビュートを決定するブロック・オフセット計算器とを含むブロック・アトリビュート計算器とを備えている。

#### 【0048】

本発明の実施例によるシステムは；コンピュータと；このコンピュータ内のメモリと；上記コンピュータの上記メモリに蓄積されたコンテンツと；少なくとも1次元にて上記コンテンツのエッジ差分を計算するエッジ差分計算器と；上記エッジ差分を濾波して、濾波されたエッジ差分を発生するエッジ差分フィルタと；上記濾波されたエッジ差分からブロック・サイズ及びブロック・オフセットを決定するブロック・オフセット計算器とを含むブロック・アトリビュート計算器とを備えている。

#### 【0049】

本発明の実施例による方法は；少なくとも1つの次元でコンテンツのエッジ差分を計算し；上記エッジ差分を濾波して、濾波されたエッジ差分を発生し；上記濾波されたエッジ差分から少なくとも1つのブロック・アトリビュートを決定する。

#### 【0050】

本発明の実施例による方法は；コンテンツの垂直次元で垂直エッジ差分を計算するとと共に、上記コンテンツの水平次元で水平エッジ差分を計算し；上記垂直エッジ差分を濾波して、濾波された垂直エッジ差分を発生し；上記水平エッジ差分を濾波して、濾波された水平エッジ差分を発生し；上記濾波された水平エッジ差分から少なくとも第2ブロック・アトリビュートを決定する。

#### 【0051】

本発明の実施例による方法は；少なくとも1つの次元に直角なコンテンツにて隣接するピクセルの間の絶対差分を計算し；上記少なくとも1つの次元に直角な上記隣接するピクセルの間の上記絶対差分を加算して和を発生し；上記少なくとも1つの次元でのピクセルの数により上記和をスケーリングして、エッジ差分を発生し；上記エッジ差分を濾波して、濾波されたエッジ差分を発生し；上記濾波されたエッジ差分から少なくとも1つのブロック・アトリビュートを決定する。

#### 【0052】

本発明の実施例による方法は；少なくとも1つの次元にてコンテンツの複数のエッジ差分を順次計算し；複数のエッジ差分のローリング標準偏差を計算し；第1エッジ差分に対応する第1ローリング標準偏差と、第1エッジ差分の直前に計算された第2エッジ差分に対応する第2ローリング標準偏差との差が所定しきい値以下の場合に、上記第1エッジ差分を濾波し；上記濾波されたエッジ差分から少なくとも1つのブロック・アトリビュートを決定する。

#### 【0053】

本発明の実施例による方法は；少なくとも1つの次元にてコンテンツの複数のエッジ差分を順次計算し；4つのエッジ差分を用いて、上記エッジ差分のローリング標準偏差を計算し；第1エッジ差分に対応する第1ローリング標準偏差と、第1エッジ差分の直前に計算された第2エッジ差分に対応する第2ローリング標準偏差との差が所定しきい値以下の場合に、上記第1エッジ差分を濾波し；上記濾波されたエッジ差分から少なくとも1つのブロック・アトリビュートを決定する。

#### 【0054】

本発明の実施例による方法は；少なくとも1つの次元にてコンテンツの複数のエッジ差分を順次計算し；対応するエッジ差分及び少なくとも1つの直前のエッジ差分を用いて、複数の上記エッジ差分のローリング標準偏差を計算し；第1エッジ差分に対応する第1ローリング標準偏差と、第1エッジ差分の直前に計算された第2エッジ差分に対応する第2ローリング標準偏差との差が所定しきい値以下の場合に、上記第1エッジ差分を濾波し；

10

20

30

40

50

上記濾波されたエッジ差分から少なくとも1つのブロック・アトリビュートを決定する。

【0055】

本発明の実施例による方法は；少なくとも1つの次元でコンテンツのエッジ差分を計算し；上記エッジ差分を濾波して、濾波されたエッジ差分を発生し；上記濾波されたエッジ差分からブロック・サイズを決定する。

【0056】

本発明の実施例による方法は；少なくとも1つの次元でコンテンツのエッジ差分を計算し；上記エッジ差分を濾波して、濾波されたエッジ差分を発生し；隣接し濾波されたエッジ差分の間の最も一般的な差分としてブロック・サイズを決定する。

【0057】

本発明の実施例による方法は；少なくとも1つの次元でコンテンツのエッジ差分を計算し；上記エッジ差分を濾波して、濾波されたエッジ差分を発生し；上記濾波されたエッジ差分からブロック・サイズ及びブロック・オフセットを決定する。

【0058】

本発明の実施例による方法は；少なくとも1つの次元でコンテンツのエッジ差分を計算し；上記エッジ差分を濾波して、濾波されたエッジ差分を発生し；上記濾波されたエッジ差分から、濾波されたエッジ差分及び上記コンテンツのエッジの間のピクセルの数としてブロック・サイズ及びブロッキング・オフセットを決定する。

【0059】

本発明の実施例による方法は；少なくとも1つの次元でコンテンツのエッジ差分を計算し；上記エッジ差分を濾波して、濾波されたエッジ差分を発生し；上記濾波されたエッジ差分からブロック・サイズを決定し；上記濾波されたエッジ差分からブロック・オフセットを決定する。

【0060】

したがって、上記の実施例での広範囲での変形変更の視点から、上述の詳細説明及び添付図は、単なる説明のためであり、本発明の範囲を限定するものではない。よって、本発明は、特許請求の範囲及びその均等の範囲内となる全ての変形変更を含むものである。

【符号の説明】

【0061】

105 コンピュータ・システム

110 コンピュータ

115 モニタ

120 キーボード

125 マウス

130 メモリ

135 コンテンツ

140 エッジ差分計算器

145 エッジ差分フィルタ

150 ブロック・アトリビュート計算器

155 ブロック・サイズ計算器

160 ブロック・オフセット計算器

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

審査官 岩井 健二

(56)参考文献 特表2012-517774 (JP, A)

特開2002-077629 (JP, A)

特開2001-218233 (JP, A)

米国特許出願公開第2011/0129156 (US, A1)

W.Sabrina Lin et al., Digital Image Source Coder Forensics Via Intrinsic Fingerprints

, IEEE Transactions on Information Forensics and Security, 2009年 9月, Volume 4,

Issue 3, pp.460-475

C.Chen and J.A.Bloom, A Blind Reference-Free Blockiness Measure, PCM 2010, Part I, LNC

S 6297, 2010年, pp.112-123

(58)調査した分野(Int.Cl., DB名)

H04N 19/00 - 19/98