(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4635016号

(P4635016)

(45) 発行日 平成23年2月16日(2011.2.16)

(24) 登録日 平成22年11月26日(2010.11.26)

(51) Int.Cl.

F 1

H04N 7/32 (2006.01)

H04N 7/30 (2006.01)H04N 7/137

H04N 7/133Z

Z

請求項の数 12 (全 11 頁)

(21) 出願番号 特願2007-36846 (P2007-36846)

(22) 出願日 平成19年2月16日 (2007.2.16)

(65) 公開番号 特開2008-205627 (P2008-205627A)

(43) 公開日 平成20年9月4日 (2008.9.4)

審査請求日 平成21年10月20日 (2009.10.20)

(73) 特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100075672

弁理士 峰 隆司

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100084618

弁理士 村松 貞男

最終頁に続く

(54) 【発明の名称】情報処理装置およびインター予測モード判定方法

## (57) 【特許請求の範囲】

## 【請求項 1】

動画像信号を符号化する情報処理装置であって、

符号化対象画面を分割したマクロブロックに対して、互いに異なるブロックサイズを処理単位とする複数種類のインター予測モードの中のいずれかのインター予測モードを用いて予測信号を生成するインター予測手段と、

前記インター予測手段が生成した予測信号と前記マクロブロックの画像信号との間の予測残差信号を、互いに異なるブロックサイズを処理単位とする複数種類のDCT (Discrete Cosine Transform) の中のいずれかのDCTを用いて直交変換する変換手段と、

前記マクロブロック毎に、前記インター予測手段が用いるインター予測モードと前記変換手段が用いるDCTとの組み合わせを、前記複数種類のインター予測モードと前記複数種類のDCTとの中から判定するインター予測モード判定手段と、

を具備し、

前記インター予測モード判定手段は、

前記複数種類のDCTの中の特定種のDCTを対象として、前記複数種類のインター予測モードの中から所定数のインター予測モードを選択する第1の選択手段と、

前記第1の選択手段が選択した前記所定数のインター予測モードと前記複数種類のDCTとの中から1つのインター予測モードおよびDCTの組み合わせを選択する第2の選択手段と、

を有することを特徴とする情報処理装置。

10

20

## 【請求項 2】

前記複数種類の D C T の各ブロックサイズは、第 1 のブロックサイズと、第 1 のブロックサイズよりも大きな第 2 のブロックサイズであり、前記予測モード判定手段の前記第 1 の選択手段は、この第 1 のブロックサイズを処理単位とする D C T および第 2 のブロックサイズを処理単位とする D C T の 2 つの D C T のうち、第 1 のブロックサイズを処理単位とする 1 つの D C T を対象として、前記複数種類のインター予測モードの中から所定数のインター予測モードを選択することを特徴とする請求項 1 記載の情報処理装置。

## 【請求項 3】

前記第 1 のブロックサイズは 4 画素 × 4 画素であり、前記第 2 のブロックサイズは 8 画素 × 8 画素であることを特徴とする請求項 1 記載の情報処理装置。 10

## 【請求項 4】

前記複数種類のインター予測モードの各ブロックサイズは、16 画素 × 16 画素、16 画素 × 8 画素、8 画素 × 16 画素および 8 画素 × 8 画素であることを特徴とする請求項 1 記載の情報処理装置。

## 【請求項 5】

前記インター予測モード判定手段の前記第 1 の選択手段は、符号化対象画面の種類に応じて、前記複数種類のインター予測モードの中から選択するインター予測モードの個数である前記所定数を決定することを特徴とする請求項 1 記載の情報処理装置。

## 【請求項 6】

前記インター予測モード判定手段の前記第 1 の選択手段は、符号化対象画面が B ピクチャの場合の方が、符号化対象画面が P ピクチャの場合よりも少なく前記所定数を決定することを特徴とする請求項 5 記載の情報処理装置。 20

## 【請求項 7】

前記インター予測モード判定手段の前記第 2 の選択手段は、前記第 1 の選択手段が対象とする前記特定の D C T 以外の D C T と前記第 1 の選択手段が選択した前記所定数のインター予測モードとの組み合わせについてのみ評価を行い、前記第 1 の選択手段が対象とする前記特定の D C T と前記第 1 の選択手段が選択した前記所定数のインター予測モードとの組み合わせについては、前記第 1 の選択手段が前記所定数のインター予測モードを選択するために行った評価を援用することを特徴とする請求項 1 記載の情報処理装置。

## 【請求項 8】

符号化対象画面を分割したマクロブロックに対して、互いに異なるブロックサイズを処理単位とする複数種類のインター予測モードの中のいずれかのインター予測モードを用いて予測信号を生成するインター予測手段と、前記インター予測手段が生成した予測信号と前記マクロブロックの画像信号との間の予測残差信号を、互いに異なるブロックサイズを処理単位とする複数種類の D C T (Discrete Cosine Transform) の中のいずれかの D C T を用いて直交変換する変換手段とを具備し、動画像信号を符号化する情報処理装置のインター予測モード判定方法であって、 30

前記マクロブロック毎に、

前記複数種類の D C T の中の特定種の D C T を対象として、前記複数種類のインター予測モードの中から所定数のインター予測モードを選択し、 40

前記選択した前記所定数のインター予測モードと前記複数種類の D C T との中から 1 つのインター予測モードおよび D C T の組み合わせを選択し、この組み合わせを、前記複数種類のインター予測モードと前記複数種類の D C T との中で前記インター予測手段が用いるインター予測モードと前記変換手段が用いる D C T との組み合わせであると判定する、ことを特徴とするインター予測モード判定方法。

## 【請求項 9】

前記複数種類の D C T の各ブロックサイズは、第 1 のブロックサイズと、第 1 のブロックサイズよりも大きな第 2 のブロックサイズであり、この第 1 のブロックサイズを処理単位とする D C T および第 2 のブロックサイズを処理単位とする D C T の 2 つの D C T のうち、第 1 のブロックサイズを処理単位とする 1 つの D C T を対象として、前記複数種類の 50

インター予測モードの中から所定数のインター予測モードを選択することを特徴とする請求項 8 記載のインター予測モード判定方法。

【請求項 10】

前記第 1 のブロックサイズは 4 画素 × 4 画素であり、前記第 2 のブロックサイズは 8 画素 × 8 画素であることを特徴とする請求項 8 記載のインター予測モード判定方法。

【請求項 11】

符号化対象画面の種類に応じて、前記複数種類のインター予測モードの中から選択するインター予測モードの個数である前記所定数を決定することを特徴とする請求項 8 記載のインター予測モード判定方法。

【請求項 12】

符号化対象画面が B ピクチャの場合の方が、符号化対象画面が P ピクチャの場合よりも少なく前記所定数を決定することを特徴とする請求項 11 記載のインター予測モード判定方法。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、例えばパーソナルコンピュータなどの情報処理装置に適用して好適な動画像の符号化技術に関する。

【背景技術】

【0002】

近年、動画像をソフトウェアによって符号化するソフトウェアエンコーダを搭載するパーソナルコンピュータが普及し始めている。また、最近では、次世代の動画像圧縮符号化技術として、H.264 / AVC (Advanced Video Coding) 規格が注目されている。この H.264 / AVC 規格は、MPEG2 や MPEG4 のような従来の圧縮符号化技術よりも高能率の圧縮符号化技術である。このため、H.264 / AVC 規格に対応するエンコード処理においては、MPEG2 や MPEG4 のような従来の圧縮符号化技術よりも多くの処理量が必要とされる。このようなことから、これまでも、動画像のエンコード処理量を低減するための提案等が種々なされている（例えば特許文献 1 等参照）。

【特許文献 1】特開 2006-25077 号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

H.264 / AVC 規格に対応するエンコード処理では、マクロブロック毎の予測モードの判定の処理量が多い。特に、ハイプロファイル (HP:High Profile) では、インター予測において、予測モードのブロックサイズが 8 画素 × 8 画素以上の場合、4 画素 × 4 画素のブロックサイズの DCT (Discrete Cosine Transform)、8 画素 × 8 画素のブロックサイズの DCT のいずれかから最適な方を選択可能となったことで、（実質的に、予測モード数 × 2 の予測モードが存在することになり）当該インター予測の予測モード判定に要する処理量が、予測モード候補数に比例して増大する。このため、例えば画質劣化等を抑止しつつ、この予測モード判定を効率的に行う仕組みが強く望まれる。

【0004】

この発明は、このような事情を考慮してなされたものであり、インター予測の予測モード判定を効率的に行うことを行った情報処理装置およびインター予測モード判定方法を提供することを目的とする。

【課題を解決するための手段】

【0005】

前述した目的を達成するために、この発明の情報処理装置は、動画像信号を符号化する情報処理装置であって、符号化対象画面を分割したマクロブロックに対して、互いに異なるブロックサイズを処理単位とする複数種類のインター予測モードの中のいずれかのインター予測モードを用いて予測信号を生成するインター予測手段と、前記インター予測手段

10

20

30

40

50

が生成した予測信号と前記マクロブロックの画像信号との間の予測残差信号を、互いに異なるブロックサイズを処理単位とする複数種類のDCT (Discrete Cosine Transform) の中のいずれかのDCTを用いて直交変換する変換手段と、前記マクロブロック毎に、前記インター予測手段が用いるインター予測モードと前記変換手段が用いるDCTとの組み合わせを、前記複数種類のインター予測モードと前記複数種類のDCTの中から判定するインター予測モード判定手段と、を具備し、前記インター予測モード判定手段は、前記複数種類のDCTの中の特定種のDCTを対象として、前記複数種類のインター予測モードの中から所定数のインター予測モードを選択する第1の選択手段と、前記第1の選択手段が選択した前記所定数のインター予測モードと前記複数種類のDCTの中から1つのインター予測モードおよびDCTの組み合わせを選択する第2の選択手段と、を有することを特徴とする。

#### 【0006】

また、この発明のインター予測モード判定方法は、符号化対象画面を分割したマクロブロックに対して、互いに異なるブロックサイズを処理単位とする複数種類のインター予測モードの中のいずれかのインター予測モードを用いて予測信号を生成するインター予測手段と、前記インター予測手段が生成した予測信号と前記マクロブロックの画像信号との間の予測残差信号を、互いに異なるブロックサイズを処理単位とする複数種類のDCT (Discrete Cosine Transform) の中のいずれかのDCTを用いて直交変換する変換手段とを具備し、動画像信号を符号化する情報処理装置のインター予測モード判定方法であって、前記マクロブロック毎に、前記複数種類のDCTの中の特定種のDCTを対象として、前記複数種類のインター予測モードの中から所定数のインター予測モードを選択し、前記選択した前記所定数のインター予測モードと前記複数種類のDCTの中から1つのインター予測モードおよびDCTの組み合わせを選択し、この組み合わせを、前記複数種類のインター予測モードと前記複数種類のDCTの中で前記インター予測手段が用いるインター予測モードと前記変換手段が用いるDCTとの組み合わせであると判定する、ことを特徴とする。

#### 【発明の効果】

#### 【0007】

この発明によれば、インター予測の予測モード判定を効率的に行うことの可能とした情報処理装置およびインター予測モード判定方法を提供できる。

#### 【発明を実施するための最良の形態】

#### 【0008】

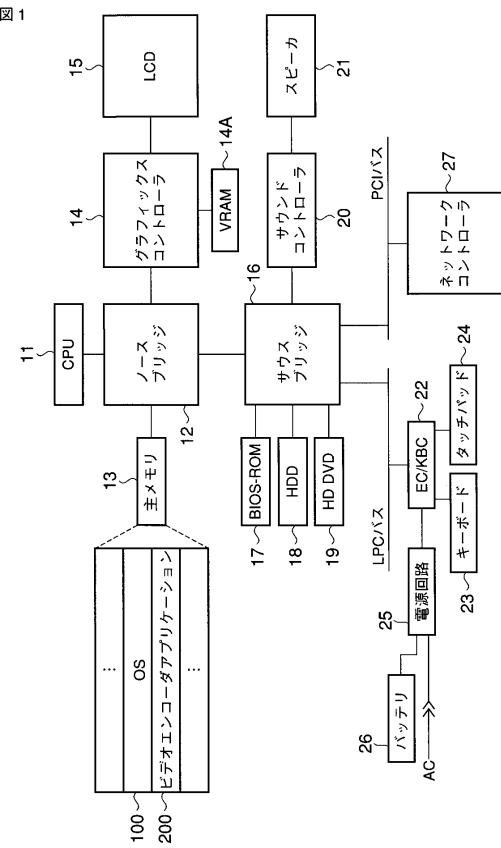

以下、図面を参照して、この発明の一実施形態を説明する。図1には、本実施形態に係る情報処理装置の構成例が示されている。この情報処理装置は、例えばバッテリ駆動可能なノートブック型パーソナルコンピュータ等として実現されている。

#### 【0009】

図1に示すように、このコンピュータは、CPU11、ノースブリッジ12、主メモリ13、グラフィックスコントローラ14、VRAM14A、LCD15、サウスブリッジ16、BIOS-ROM17、HDD18、HDD-DVD19、サウンドコントローラ20、スピーカ21、エンベデッドコントローラ/キーボードコントローラIIC(ECT/KBC)22、キーボード23、タッチパッド24、電源回路25、バッテリ26およびネットワークコントローラ27等を備えている。

#### 【0010】

CPU11は、本コンピュータ内の各部の動作を制御するプロセッサである。CPU11は、HDD18から主メモリ13にロードされるオペレーティングシステム(OS)100や、このOS100の制御下で動作する、ユーティリティを含む各種アプリケーションプログラムを実行する。この各種アプリケーションプログラムの中には、ビデオエンコーダアプリケーション200が含まれている。ビデオエンコーダアプリケーション200は、動画像を符号化するためのソフトウェアであり、H.264/AVC規格に対応するソフトウェアエンコーダとして動作する。また、CPU11は、BIOS-ROM17に

格納された B I O S も実行する。B I O S は、各種ハードウェア制御のためのプログラムである。

【 0 0 1 1 】

ノースブリッジ 1 2 は、C P U 1 1 のローカルバスとサウスブリッジ 1 6 との間を接続するブリッジデバイスである。ノースブリッジ 1 2 は、バスを介してグラフィックスコントローラ 1 4 との通信を実行する機能を有しており、また、主メモリ 1 3 をアクセス制御するメモリコントローラも内蔵されている。グラフィックスコントローラ 1 4 は、本コンピュータのディスプレイモニタとして使用される L C D 1 5 を制御する表示コントローラである。グラフィックスコントローラ 1 4 は、V R A M 1 4 A に書き込まれた画像データから L C D 1 5 に送出すべき表示信号を生成する。

10

【 0 0 1 2 】

サウスブリッジ 1 6 は、P C I バスおよびL P C バス上の各種デバイスを制御するコントローラである。また、このサウスブリッジ 1 6 には、B I O S - R O M 1 7 、H D D 1 8 、H D D V D 1 9 およびサウンドコントローラ 2 0 が直接的に接続され、これらを制御する機能も有している。サウンドコントローラ 2 0 は、スピーカ 2 1 を制御する音源コントローラである。

【 0 0 1 3 】

E C / K B C 2 2 は、電力管理のためのエンベデッドコントローラと、キーボード 2 3 およびタッチパッド 2 4 を制御するためのキーボードコントローラとが集積された 1 チップマイクロコンピュータである。E C / K B C 2 2 は、電源回路 2 5 と協働して、バッテリ 2 6 または外部 A C 電源からの電力を各部に供給制御する。そして、ネットワークコントローラ 2 7 は、例えばインターネットなどの外部ネットワークとの通信を実行する通信装置である。

20

【 0 0 1 4 】

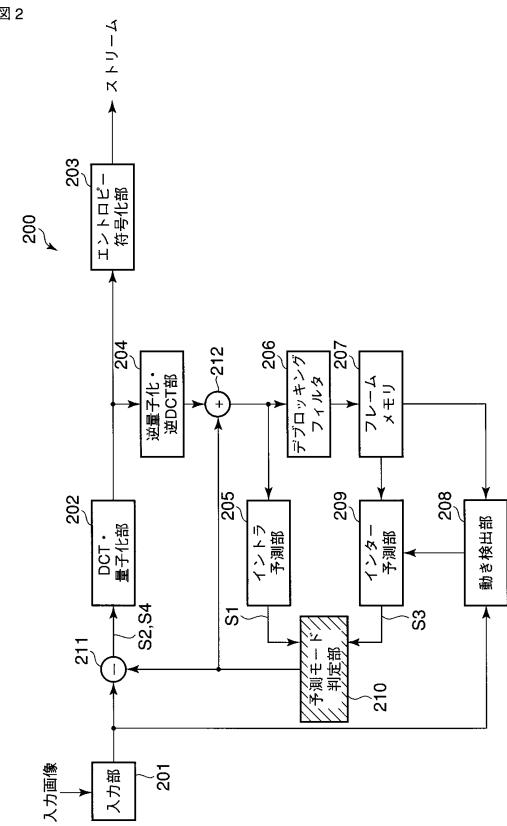

次に、図 2 を参照して、このようなハードウェア構成の本コンピュータ上で動作するビデオエンコーダアプリケーション 2 0 0 によって実現されるソフトウェアエンコーダの機能構成を説明する。

【 0 0 1 5 】

ビデオエンコーダアプリケーション 2 0 0 によるエンコード処理は、H . 2 6 4 / A V C 規格に対応しており、図示のように、ビデオエンコーダアプリケーション 2 0 0 は、入力部 2 0 1 、D C T ・ 量子化部 2 0 2 、エントロピー符号化部 2 0 3 、逆量子化・逆D C T 部 2 0 4 部、イントラ予測部 2 0 5 、デブロッキングフィルタ 2 0 6 、フレームメモリ 2 0 7 、動き検出部 2 0 8 、インター予測部 2 0 9 、予測モード判定部 2 1 0 、可算器 2 1 1 , 2 1 2 等を備えている。

30

【 0 0 1 6 】

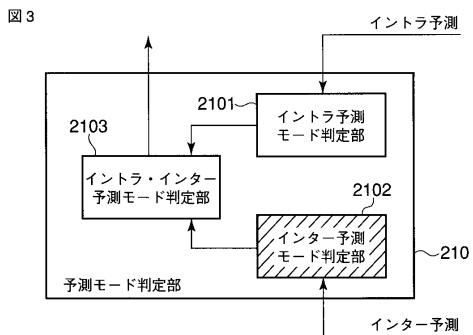

ビデオエンコーダアプリケーション 2 0 0 は、入力部 2 0 1 から入力される各画面（ピクチャ）の符号化を、例えば  $16 \times 16$  画素のマクロブロック単位で実行する。予測モード判定部 2 1 0 は、このマクロブロックごとに、フレーム内予測符号化モード（イントラ予測モード）および動き補償フレーム間予測符号化モード（インター予測モード）のいずれか一方を選択するものである。図 3 は、この予測モード判定部 2 1 0 の機能ブロックを示している。

40

【 0 0 1 7 】

図 3 に示すように、予測モード判定部 2 1 0 は、イントラ予測モード判定部 2 1 0 1 、インター予測モード判定部 2 1 0 2 およびイントラ・インター予測モード判定部 2 1 0 3 を備えている。

【 0 0 1 8 】

イントラ予測モードおよびインター予測モードのいずれにも、各マクロブロック毎に選択し得る複数の予測モード候補が存在しており、第 1 に、イントラ予測モード判定部 2 1 0 1 およびインター予測モード判定部 2 1 0 2 のそれぞれが、この複数の予測モード候補の中から最もコストの優れた（符号量の少ない）予測モード候補を選択する。そして、第

50

2に、イントラ・インター予測モード判定部2103が、イントラ予測モード判定部2101およびインター予測モード判定部2102がそれぞれ選択した2つの予測モード候補を比較して、よりコストの優れた方の予測モード、即ち、イントラ予測モードおよびインター予測モードのいずれか一方を最終的に選択する。

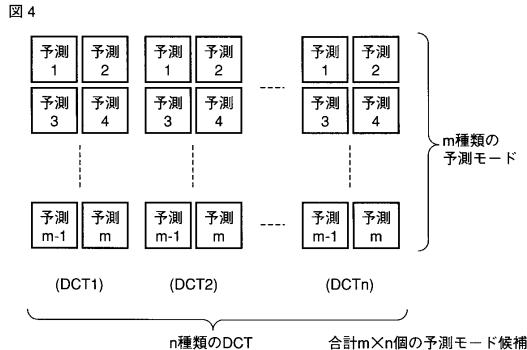

【0019】

ところで、H.264/AVC規格のハイプロファイルでは、インター予測において、予測モードのブロックサイズが8画素×8画素以上の場合、4画素×4画素のブロックサイズのDCT、8画素×8画素のブロックサイズのDCTのいずれかから最適な方を選択可能となっている。従って、仮に、ある規格において、m種類の予測モードが存在し、かつ、n種類のDCTが選択可能である場合、図4に示すように、インター予測だけでm×n個の予測モード候補が実質的に存在することとなる。このような状況において、何らの工夫も凝らさずに、すべての予測モード候補について評価を行い最適な予測モード候補を選択するとしたならば、当該インター予測の予測モード判定に要する処理量が膨大となってしまう。そこで、本コンピュータのインター予測モード判定部2102は、例えば画質劣化等を抑制しつつ、この予測モード判定を効率的に行う仕組みを備えたものであり、以下、この点について詳述する。

【0020】

なお、図2に機能構成が示されるソフトウェアエンコーダは、イントラ予測符号化モード時においては、イントラ予測部205が、符号化対象画面(ピクチャ)から予測信号s1を生成し、符号化対象画面(ピクチャ)からこの予測信号s1を引いた予測誤差信号s2を、DCT・量子化部202が直交変換および量子化し、エントロピー符号化部203が、イントラ予測モード情報、および量子化された直交変換係数に対しエントロピー符号化を行うことによって符号化する。

【0021】

一方、インター予測符号化モード時においては、まず、動き検出部208が、フレームメモリ207に格納された既に符号化された画面(ピクチャ)からの動きを推定し、続いて、インター予測部209が、符号化対象画面に対応する動き補償フレーム間予測信号s3を定められた形状単位で生成する。そして、符号化対象画面(ピクチャ)から動き補償フレーム間予測信号s3を引いた予測誤差信号s4を、DCT・量子化部202が、直交変換および量子化し、エントロピー符号化部203が、インター予測モード情報、および量子化された直交変換係数に対しエントロピー符号化を行うことによって符号化する。

【0022】

また、逆量子化・逆DCT部204は、直交変換および量子化された画像(ピクチャ)の量子化係数を逆量子化および逆直交変換するものであり、デブロッキングフィルタ206は、ブロックノイズを低減するためのデブロッキングフィルタ処理を行うものである。

【0023】

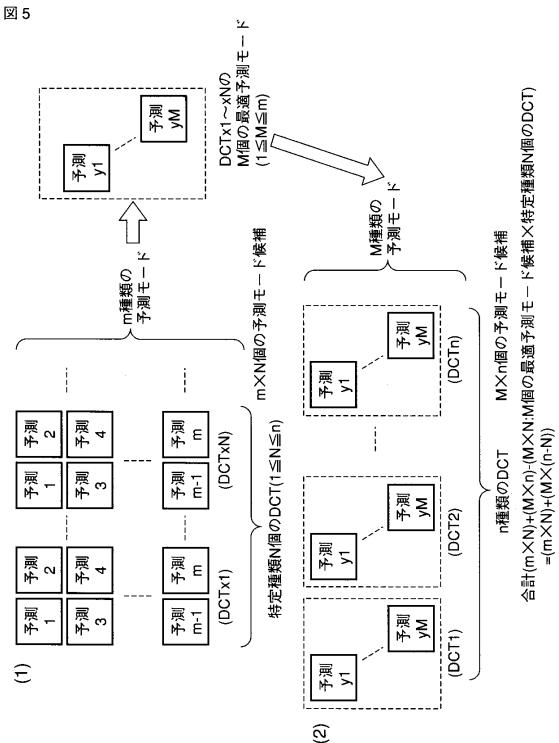

図5は、本コンピュータのインター予測モード判定部2102が実行する予測モード判定の基本原理を説明するための図である。

【0024】

最適な予測モードの候補は、DCTによらずにある程度の割合で同じとなる性質を有している。よって、先に予測モードの選択を行い、最適なDCTの選択判定を行う予測モードを絞り込んだ場合でも、真に最適な予測モードとDCTとの組み合わせを選択できる割合は相当高いといえる。本コンピュータのインター予測モード判定部2102は、この性質に着目し、まず、特定のDCTの条件下で予測モード判定を行い、最適な予測モード候補を選択する(図5(1))。そして、インター予測モード判定部2102は、その最適な予測モード候補のみを対象に、最適なDCTを選択する判定を行い、最終的に予測モードを決定する(図5(2))。なお、この際、特定のDCTについては、最適な予測モード候補の選択時に評価済みであるので、特定のDCT以外のDCTについてのみ評価を行えば良い。

【0025】

10

20

30

40

50

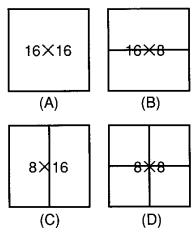

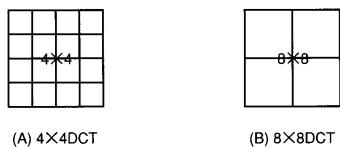

より具体的な例を挙げて説明すると、前述した H.264 / AVC 規格のハイプロファイルでは、図 6 に示すように、16 画素 × 16 画素、16 画素 × 8 画素、8 画素 × 16 画素、8 画素 × 8 画素の互いに異なるブロックサイズを処理単位とする 4 種類の予測モードが存在する。また、この H.264 / AVC 規格のハイプロファイルでは、図 7 に示すように、4 画素 × 4 画素、8 画素 × 8 画素の互いに異なるブロックサイズを処理単位とする 2 種類の DCT が存在する。従って、予測モード候補数は、4 (図 4, 5 の m) × 2 (図 4, 5 の n) = 8 となる。

【0026】

一方、本コンピュータのインター予測モード判定部 2102 は、まず、4 画素 × 4 画素および 8 画素 × 8 画素の 2 種類の DCT のうち、例えば 4 画素 × 4 画素の 1 (図 5 の N) 種類の DCT のみで予測モードの評価を行い (候補数は 4 (m) × 1 (N))、最適な予測モード候補を例えば 1 (図 5 の M) 個選択する。そして、この 4 画素 × 4 画素の DCT で得られた 1 個の最適な予測モード候補のみを対象に、もう一方の 8 画素 × 8 画像の DCT での評価を行い (候補数は 1 (M) × (2 (n) - 1 (N)))、最終的に予測モードを決定する。

【0027】

つまり、この (最適な予測モード候補を 1 つとする) 場合、本コンピュータのインター予測モード判定部 2102 は、 $4 + 1 = 5$  個まで (3 個分) 予測モード候補数を低減することを実現する。4 画素 × 4 画素の DCT、8 画素 × 8 画素の DCT で最適な予測モードが同じとなる確率は高いため、真に最適な組み合わせを選択できる割合は高く、画質劣化はほとんどない。

【0028】

更に、本コンピュータのインター予測モード判定部 2102 は、予測が当たりやすい B ピクチャでは最適な予測モード候補を 1 つとし、P ピクチャでは 2 に増やすといった制御を行っている。即ち、インター予測モード判定部 2102 は、ピクチャの種類に応じて予測モード候補数を決定することで、画質劣化を適応的に抑えながら、予測モード判定に要する処理量を削減することを実現している。

【0029】

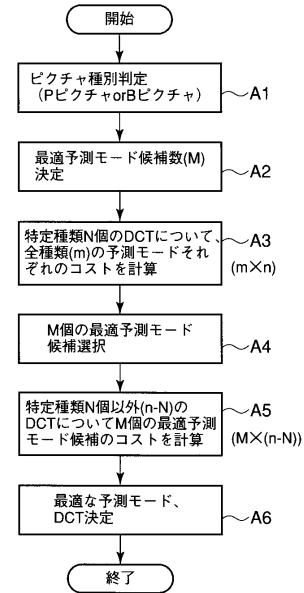

図 8 は、本コンピュータのインター予測モード判定部 2102 が実行する予測モード判定の動作手順を示すフローチャートである。

【0030】

インター予測モード判定部 2102 は、まず、符号化対象画面が P ピクチャまたは B ピクチャのいずれであるのかを判定し (ステップ A1)、P ピクチャであれば 2、B ピクチャであれば 1 のごとく、その判定結果に基づき、最適予測モード候補数を決定する (ステップ A2)。

【0031】

次に、インター予測モード判定部 2102 は、複数種類の DCT の中の特定種類の DCT について、全種類の予測モードそれぞれのコストを計算する (ステップ A3)。このコスト計算の結果に基づき、インター予測モード判定部 2102 は、先に決定した候補数だけ最適予測モード候補を選択する (ステップ A4)。

【0032】

そして、インター予測モード判定部 2102 は、今度は、特定種類の DCT 以外の DCT について、先に決定した候補数だけ選択された最適予測モード候補それぞれのコストを計算し (ステップ A5)、(ステップ A3 にて計算済みの特定種類の DCT に関わるコストを含めた中から) 最適な予測モード、DCT を決定する (ステップ A6)。

【0033】

以上のように、本コンピュータによれば、例えば画質劣化等を招くことなく、インター予測の予測モード判定を効率的に行なうことが可能となる。

【0034】

なお、本発明は上記実施形態そのままで限定されるものではなく、実施段階ではその要

10

20

30

40

50

旨を逸脱しない範囲で構成要素を変形して具体化できる。また、上記実施形態に開示されている複数の構成要素の適宜な組み合わせにより、種々の発明を形成できる。例えば、実施形態に示される全構成要素から幾つかの構成要素を削除してもよい。さらに、異なる実施形態にわたる構成要素を適宜組み合わせてもよい。

【図面の簡単な説明】

【0035】

【図1】この発明の一実施形態に係る情報処理装置（パーソナルコンピュータ）の構成例を示す図

【図2】同実施形態のコンピュータ上で動作するビデオエンコーダアプリケーションによって実現されるソフトウェアエンコーダの機能構成を示す図

10

【図3】同実施形態のコンピュータ上で動作するビデオエンコーダアプリケーションの予測モード判定部の機能ブロックを示す図

【図4】インター予測の予測モード判定の一般的な基本原理を説明するための図

【図5】同実施形態のコンピュータ上で動作するビデオエンコーダアプリケーションのインター予測モード判定部が実行する予測モード判定の基本原理を説明するための図

【図6】同実施形態のコンピュータ上で動作するビデオエンコーダアプリケーションのインター予測モード判定部が実行する予測モード判定の一具体例を説明するための第1の図（予測モードの種類を例示する図）

【図7】同実施形態のコンピュータ上で動作するビデオエンコーダアプリケーションのインター予測モード判定部が実行する予測モード判定の一具体例を説明するための第2の図（DCTの種類を例示する図）

20

【図8】同実施形態のコンピュータ上で動作するビデオエンコーダアプリケーションのインター予測モード判定部が実行する予測モード判定の動作手順を示すフローチャート

【符号の説明】

【0036】

11...CPU、12...ノースブリッジ、13...主メモリ、14...グラフィックスコントローラ、14A...VRAM、15...LCD、16...サウスブリッジ、17...BIOS-ROM、18...HDD、19...HD DVD、20...サウンドコントローラ、21...スピーカ、22...エンベデッドコントローラ/キーボードコントローラIC（EC/KBC）、23...キーボード、24...タッチパッド、25...電源回路、26...バッテリ、27...ネットワークコントローラ、100...オペレーティングシステム（OS）、200...ビデオエンコーダアプリケーション、201...入力部、202...DCT・量子化部、203...エントロピー符号化部、204...逆量子化・逆DCT部、205...イントラ予測部、206...デブロッキングフィルタ、207...フレームメモリ、208...動き検出部、209...インター予測部、210...予測モード判定部、211, 212...可算器、2101...イントラ予測モード判定部、2102...インター予測モード判定部、2103...イントラ・インター予測モード判定部。

30

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【図6】

図6

【図7】

図7

【図8】

図8

---

フロントページの続き

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 藤澤 達朗

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 菊池 義浩

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 川島 裕司

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72)発明者 鈴木 真吾

東京都港区芝浦一丁目1番1号 株式会社東芝内

審査官 畑中 高行

(56)参考文献 特開2004-254327 (JP, A)

特開2006-129153 (JP, A)

特開2003-533141 (JP, A)

特開2005-86249 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N7/24-7/68

H03M7/30-7/50