(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-161237

(P2010-161237A)

(43) 公開日 平成22年7月22日(2010.7.22)

| (51) Int.Cl.            | F 1           | テーマコード (参考) |

|-------------------------|---------------|-------------|

| HO 1 L 21/322 (2006.01) | HO 1 L 21/322 | L           |

| HO 1 L 29/861 (2006.01) | HO 1 L 29/91  | J           |

| HO 1 L 21/329 (2006.01) | HO 1 L 29/91  | A           |

審査請求 未請求 請求項の数 1 O L (全 6 頁)

|           |                          |          |                                          |

|-----------|--------------------------|----------|------------------------------------------|

| (21) 出願番号 | 特願2009-2930 (P2009-2930) | (71) 出願人 | 000003207<br>トヨタ自動車株式会社<br>愛知県豊田市トヨタ町1番地 |

| (22) 出願日  | 平成21年1月8日 (2009.1.8)     | (74) 代理人 | 110000110<br>特許業務法人快友国際特許事務所             |

|           |                          | (72) 発明者 | 岩崎 真也<br>愛知県豊田市トヨタ町1番地 トヨタ自動車株式会社内       |

|           |                          |          |                                          |

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】結晶欠陥の種類や量を制御することで、所望のスイッチング特性が実現可能となる半導体装置を製造する方法を提供する。

【解決手段】本方法は、シリコン領域形成工程 (S 3 0) と、熱処理工程 (S 3 2) と、注入工程 (S 3 6) を備えている。シリコン領域形成工程では、不純物が含有されているシリコン基板と、シリコン基板の表面に堆積されているエピタキシャル層と、からなるシリコン領域を形成する。熱処理工程では、シリコン領域を熱処理する。素子構造形成工程では、熱処理工程後に、シリコン領域内に半導体装置の素子構造を形成する。注入工程では、熱処理工程後に、シリコン領域内に荷電粒子を注入する。熱処理工程では、熱処理条件を制御することによって、シリコン基板からエピタキシャル層に拡散される不純物の濃度や拡散速度を制御することができる。

【選択図】図 2

**【特許請求の範囲】****【請求項 1】**

不純物が含有されているシリコン基板と、そのシリコン基板の表面に堆積されているエピタキシャル層と、からなるシリコン領域を形成するシリコン領域形成工程と、

そのシリコン領域形成工程後に、シリコン領域を熱処理する熱処理工程と、

その熱処理工程後に、シリコン領域内に荷電粒子を注入する注入工程を備えていることを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

10

本発明は、半導体装置の製造方法に関する。

**【背景技術】****【0002】**

シリコン基板内の所定の領域に結晶欠陥を形成することで、シリコン基板内におけるキャリアのライフタイムを制御する技術が知られている。この技術では、シリコン基板内に形成された結晶欠陥が正孔トラップ又は電子トラップとして機能する。正孔トラップ又は電子トラップにキャリアが捕獲されることによって、キャリアの再結合が促進されて半導体装置のスイッチング特性が改善される。

**【0003】**

20

シリコン基板内に結晶欠陥を形成する技術では、一般的に、結晶欠陥を形成する領域（以下、ライフタイム制御領域と称する）に酸素や炭素などの不純物を導入し、その後にライフタイム制御領域に電子線やイオン線などの粒子線を照射する。これによって、シリコン基板内に結晶欠陥が形成され、キャリアのライフタイム制御機能を得ることができる。このような技術の従来例として、例えば特許文献1が挙げられる。

**【先行技術文献】****【特許文献】****【0004】**

30

**【特許文献1】特開2007-266103号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

40

上記した特許文献1の製造方法では、例えばCZ(Czokralski)法又はFZ(Floating Zone)法によって製造されたシリコン基板を利用する。CZ法又はFZ法によって製造されたシリコン基板には、所定の濃度以上の酸素や炭素などの不純物が予め含有されている。このため、CZ法又はFZ法によって製造されたシリコン基板内に結晶欠陥を形成すると、結晶欠陥の種類や量がシリコン基板内に予め含有されている酸素や炭素の濃度によって決定される。CZ法又はFZ法によって製造されたシリコン基板を利用すると、シリコン基板内に形成される結晶欠陥の種類や量を制御することができず、所望のスイッチング特性を得ることができない。

**【0006】**

本発明は上記の課題に鑑みて提案されたものである。本発明は、結晶欠陥の種類や量を制御可能にすることで、所望のスイッチング特性が実現可能となる半導体装置を製造する方法を提供する。

**【課題を解決するための手段】****【0007】**

50

本発明の半導体装置の製造方法は、シリコン領域形成工程と、熱処理工程と、注入工程を備えている。シリコン領域形成工程では、不純物が含有されているシリコン基板と、シリコン基板の表面に堆積されているエピタキシャル層と、からなるシリコン領域を形成する。熱処理工程では、シリコン領域形成工程後に、シリコン領域を熱処理する。注入工程では、熱処理工程後に、シリコン領域内に荷電粒子を注入する。

## 【0008】

本方法では、熱処理工程により、シリコン基板内の不純物がエピタキシャル層に拡散される。このとき、熱処理条件を制御することによって、シリコン基板からエピタキシャル層に拡散される不純物の濃度や拡散速度を制御することができる。注入工程では、シリコン領域のエピタキシャル層内に荷電粒子が注入されて、エピタキシャル層内に結晶欠陥が形成される（ライフタイム制御領域が形成される）。熱処理条件を制御することで、シリコン基板内に予め含有されている不純物の濃度に依存することなく、エピタキシャル層内の不純物濃度が制御でき、エピタキシャル層内の結晶欠陥の種類や量を制御することができる。これによって、所望のキャリアのライフタイム制御機能を得ることができる。

## 【発明の効果】

10

## 【0009】

本発明の方法によると、結晶欠陥の種類や量を制御することができ、所望のスイッチング特性を備えた半導体装置を製造することができる。

## 【図面の簡単な説明】

## 【0010】

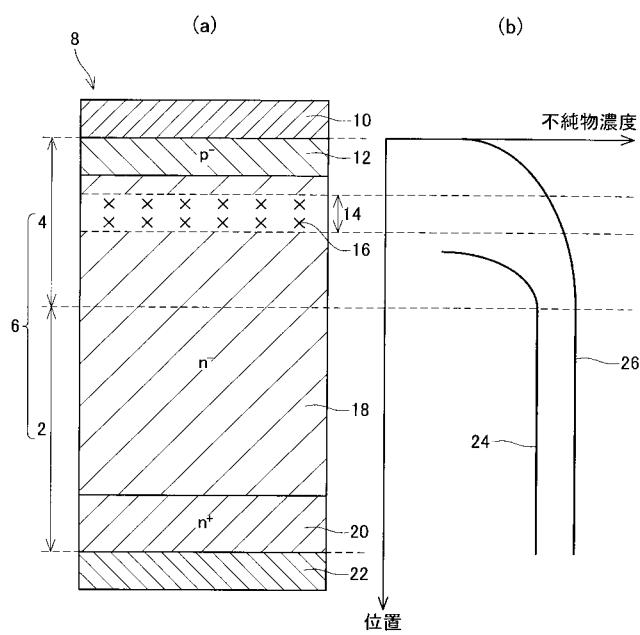

【図1】(a)は、ダイオード8の断面図を示す。(b)は、シリコン領域6内の不純物濃度のプロファイル結果を示す。

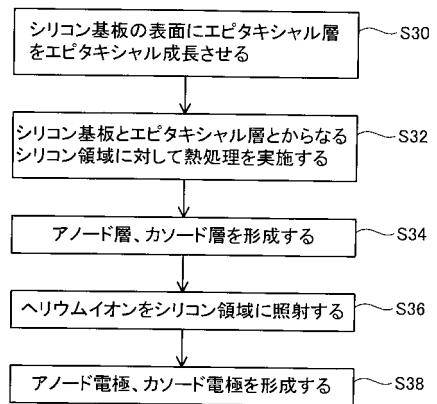

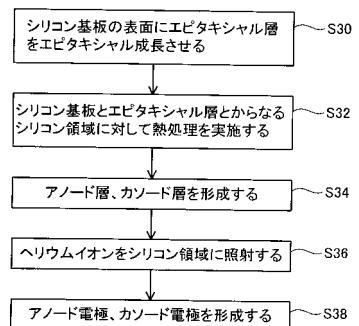

## 【図2】製造方法のフローチャートを示す。

20

## 【発明を実施するための形態】

## 【0011】

以下、本発明の実施の形態について詳細に説明する。

(形態1) 不純物の拡散範囲に応じて、エピタキシャル層の厚みを制御する。

(形態2) 热処理工程とシリコン領域の表面に熱酸化膜を形成する工程を同一の工程で実施する。

(形態3) ライフタイム制御領域を形成する位置および製造後の半導体装置に要求されるデバイス特性に応じて、熱処理工程における熱処理条件を制御する。

(形態4) 素子構造を形成するときに実施する熱処理を考慮して、素子構造形成前の熱処理工程における熱処理条件を決定する。

## 【実施例】

## 【0012】

30

図1(a)に、実施例の製造方法で製造されたダイオード8の断面図を示す。ダイオード8はPINダイオードである。ダイオード8は、シリコン領域6と、アノード電極10と、カソード電極22を備えている。シリコン領域6は、シリコン基板2と、シリコン基板2の表面に堆積されているエピタキシャル層4によって構成されている。シリコン領域6内には、酸素と炭素が含有されている。エピタキシャル層4の表面側には、p<sup>+</sup>型のアノード層12が形成されている。エピタキシャル層4の裏面側とシリコン基板2の表面側には、n<sup>-</sup>型のドリフト層18が形成されている。シリコン基板2の裏面側には、n<sup>+</sup>型のカソード層20が形成されている。エピタキシャル層4内であってアノード層12の下方には、ライフタイム制御領域14が形成されている。ライフタイム制御領域14には、複数の結晶欠陥16が形成されている。アノード電極10は、シリコン領域6の表面に設けられており、アノード層12と接触している。カソード電極22は、シリコン基板6の裏面に設けられており、カソード層20と接触している。ダイオード8では、ライフタイム制御領域14内に形成されている結晶欠陥16が正孔トラップ又は電子トラップとして機能する。正孔トラップ又は電子トラップにキャリアが捕獲されることによって、キャリアの再結合が促進される。

40

## 【0013】

図1(b)に、ダイオード8のシリコン領域6内に含有されている酸素と炭素の濃度をダイオード8の深さ方向にプロファイルした結果を示す。参照符号24は、炭素濃度のプロファイル結果を示している。参照符号26は、酸素濃度のプロファイル結果を示している。図1(b)の横軸は不純物濃度を示しており、図の左側に向かうほど不純物濃度が低

50

い。図1(b)の縦軸はダイオード8の深さ方向における位置を示している。図1(b)に示すように、シリコン基板2内では、酸素濃度と炭素濃度は一定である。エピタキシャル層4内では、酸素濃度と炭素濃度はいずれもシリコン基板2から上方に離れるにつれて低下している。炭素濃度はライフタイム制御領域14の下方のエピタキシャル層4内で検出限界以下となっている。このため、ライフタイム制御領域14内には酸素のみ含有されている。ダイオード8では、酸素を欠陥形成要因とする結晶欠陥16がライフタイム制御領域14内に形成され、スイッチング特性が改善されている。

【0014】

図2に、ダイオード8の製造方法のフローチャートを示す。以下では、ダイオード8を製造する方法を説明する。まず、CZ法又はFZ法によって製造されたシリコン基板2を準備する。シリコン基板2内には、所定の濃度の酸素と炭素が予め含有されている。次に、S30では、準備したシリコン基板2の表面にエピタキシャル層4をエピタキシャル成長させて、シリコン基板2と、シリコン基板2の表面に堆積されているエピタキシャル層4と、からなるシリコン領域6を形成する(シリコン領域形成工程)。シリコン領域形成工程では、エピタキシャル層4をシリコン基板2の表面にエピタキシャル成長させるとときにエピタキシャル層4の厚みを制御することで、後述する熱処理工程で酸素と炭素がエピタキシャル層4まで拡散するときの酸素と炭素の拡散範囲を制御することができる。

10

【0015】

次に、S32では、シリコン領域6を熱処理する(熱処理工程)。熱処理工程は拡散炉内で実施することができる。これによって、シリコン基板2内に含有されている酸素と炭素がエピタキシャル層4まで拡散される。このとき、処理時間、処理温度などの熱処理条件を制御することによって、酸素と炭素がエピタキシャル層4まで拡散するときの拡散範囲、拡散速度、拡散濃度などを制御することができる。このため、ライフタイム制御領域14を形成する深さおよび製造後のダイオード8に要求されるデバイス特性に応じて、熱処理工程における熱処理条件を制御することが好ましい。本実施例の製造方法では、ライフタイム制御領域14を形成する深さに、炭素が殆ど含有されず、かつ、酸素が多く含有されるように熱処理条件を制御する。

20

【0016】

次に、S34では、シリコン領域6の表面にパターニングされた熱酸化膜を形成し、シリコン領域6の表面からボロンなどのp型の不純物を注入して熱処理する。これによって、エピタキシャル層4の表面側にアノード層12を形成する。なお、上述した熱処理工程とシリコン領域6の表面に熱酸化膜を形成する工程を同一の工程で実施してもよい。同一の工程とすることで、製造工程を短縮することができる。次に、シリコン領域6の裏面からリンなどのn型の不純物を注入して熱処理する。これによって、シリコン基板2の裏面側にカソード層18を形成する。なお、アノード層12とカソード層18を形成するときの熱処理においてもシリコン領域6内の酸素と炭素が拡散される。このため、これらの熱処理を考慮して、熱処理工程における熱処理条件を決定することが好ましい。

30

【0017】

次に、S36では、シリコン領域6の表面からアルミホイル膜を介してヘリウムイオン30を照射する(注入工程)。アルミホイル膜をアブソーバとして利用することで、ヘリウムイオン30をシリコン領域6内の所定の深さ(ライフタイム制御領域14を形成する深さ)に注入することができる。これによって、ライフタイム制御領域14を形成する深さに複数の原子空孔が形成される。形成された原子空孔とライフタイム制御領域14に複数の結晶欠陥16が形成される。注入工程では、ヘリウムイオン30の照射条件を制御することによって、ライフタイム制御領域14内に形成される結晶欠陥16の量を制御することができる。なお、注入工程ではシリコン領域6の裏面からヘリウムイオン30を照射してもよい。

40

【0018】

S38では、シリコン領域6の表面にアノード層12と接するアノード電極10を形成

50

する。さらに、シリコン領域 6 の裏面にカソード層 20 と接するカソード電極 22 を形成する。これによって、図 1 ( a ) に示すダイオード 8 が完成する。なお、本実施例では、注入工程の後にアノード電極 10 とカソード電極 22 を形成しているが、アノード電極 10 とカソード電極 22 を形成した後に注入工程を実施してもよい。

#### 【 0 0 1 9 】

本実施例の方法によると、熱処理工程の熱処理条件を制御することで、シリコン基板 2 内に予め含有されている酸素と炭素の濃度に依存することなく、エピタキシャル層 4 内に形成される結晶欠陥 16 の種類や量を制御することができる。CZ 法又は FZ 法によって製造されたシリコン基板 2 を利用してダイオード 8 を製造した場合でも、製造後に良好なキャリアのライフタイム制御機能を得ることができ、所望のスイッチング特性を得ることができる。

また、本実施例の製造方法によると、エピタキシャル層 4 内に形成される結晶欠陥 16 の種類を制御することができるため、リーク電流の増加などデバイス特性を悪化させる結晶欠陥 16 を排除することができる。

さらに、本実施例の製造方法によると、外部からエピタキシャル層 4 内に酸素又は炭素などの不純物を導入しなくても、エピタキシャル層 4 内に不純物を含有させることができる。このため、外部からエピタキシャル層 4 内に不純物を導入するための加速装置などの特別な装置を準備する必要がない。

#### 【 0 0 2 0 】

なお、本実施例の製造方法では、シリコン領域形成工程で、シリコン基板 2 の表面にエピタキシャル層 4 をエピタキシャル成長させてシリコン領域 6 を形成したが、シリコン基板 2 の表面に予めエピタキシャル層 4 が堆積されているシリコン領域 6 を準備してもよい。

#### 【 0 0 2 1 】

以上、本発明の実施例について詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

#### 【 符号の説明 】

#### 【 0 0 2 2 】

2 : シリコン基板

4 : エピタキシャル層

6 : シリコン領域

8 : ダイオード

10 : アノード電極

12 : アノード層

14 : ライフタイム制御領域

16 : 結晶欠陥

18 : ドリフト層

20 : カソード層

22 : カソード電極

S30 ~ S38 : 製造方法

10

20

30

40

【図1】

【図2】