(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4188556号

(P4188556)

(45) 発行日 平成20年11月26日(2008.11.26)

(24) 登録日 平成20年9月19日(2008.9.19)

|                             |                          |

|-----------------------------|--------------------------|

| (51) Int.Cl.                | F 1                      |

| G 0 6 F   1/10   (2006.01)  | G 0 6 F   1/04   3 3 O A |

| H 0 3 D   3/24   (2006.01)  | H 0 3 D   3/24           |

| H 0 3 D   13/00   (2006.01) | H 0 3 D   13/00   A      |

| H 0 3 L   7/00   (2006.01)  | H 0 3 L   7/00   B       |

請求項の数 4 (全 15 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2000-515330 (P2000-515330)  |

| (86) (22) 出願日 | 平成10年8月20日 (1998.8.20)        |

| (65) 公表番号     | 特表2001-519577 (P2001-519577A) |

| (43) 公表日      | 平成13年10月23日 (2001.10.23)      |

| (86) 国際出願番号   | PCT/US1998/017399             |

| (87) 国際公開番号   | W01999/018660                 |

| (87) 国際公開日    | 平成11年4月15日 (1999.4.15)        |

| 審査請求日         | 平成17年8月22日 (2005.8.22)        |

| (31) 優先権主張番号  | 08/946,671                    |

| (32) 優先日      | 平成9年10月7日 (1997.10.7)         |

| (33) 優先権主張国   | 米国 (US)                       |

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 591003943<br>インテル・コーポレーション<br>アメリカ合衆国 95052 カリフォルニア州・サンタクララ・ミッション・カレッジ ブーレバード・2200 |

| (74) 代理人  | 100064621<br>弁理士 山川 政樹                                                             |

| (72) 発明者  | ジャンノパウロス, ジョージ<br>アメリカ合衆国・97229・オレゴン州<br>・ポートランド・ノース ウエスト スプリングフィールド ロード・17130     |

| (72) 発明者  | ウォン, ケン・エル<br>アメリカ合衆国・97229・オレゴン州<br>・ポートランド・ノース ウエスト ベンソン ストリート・9028              |

最終頁に続く

(54) 【発明の名称】クロック信号をデスキーする方法および装置

## (57) 【特許請求の範囲】

## 【請求項 1】

同期デジタル・システムにおいてクロック信号をデスキーする装置であって、複数のクロック信号を受け取り、該クロック信号同士の間の位相関係に基づいて出力を生成するように構成された位相検出回路であって、

第1のクロック信号を所定量だけ遅延させる第1の遅延負荷と、

第2のクロック信号を所定量だけ遅延させる第2の遅延負荷と、

前記遅延されたクロック信号の一方と遅延されないクロック信号の一方とを受け取る

第1の位相検出器と、

前記遅延されたクロック信号の他方と遅延されないクロック信号の他方とを受け取る

第2の位相検出器と、

を備え、該第1、第2の位相検出器が前記遅延されたクロック信号と遅延されていないクロック信号とを比較して前記位相関係を示す出力を生成するよう構成されている位相検出回路と、

複数の遅延回路であって、各遅延回路は複数のクロック信号の対応する一つに結合し、遅延信号に基づいて該複数のクロック信号の1つを調整するためのものである複数の遅延回路と、

前記位相検出回路と前記複数の遅延回路に結合したコントローラとから構成され、前記コントローラは前記位相検出回路からの出力を受けて前記遅延信号を発生し、この遅延信号を前記位相検出回路の出力に基づいて前記複数の遅延回路の1つに送出することを特徴

10

20

とする装置。

【請求項 2】

同期デジタル・システムであって、

周波数を有するシステム・クロックと、

プロセッサとを備え、前記プロセッサは、

前記システム・クロックの周波数を受け取り、一部が該システム・クロックと同期する複数のクロック信号を生成するように構成された生成装置と、

前記複数のクロック信号を受け取り、該クロック信号同士の位相関係に基づいて出力を生成するように構成された位相検出回路であって、

第 1 のクロック信号を所定量だけ遅延させる第 1 の遅延負荷と、 10

第 2 のクロック信号を所定量だけ遅延させる第 2 の遅延負荷と、

前記遅延されたクロック信号の一方と遅延されないクロック信号の一方とを受け取る

第 1 の位相検出器と、

前記遅延されたクロック信号の他方と遅延されないクロック信号の他方とを受け取る

第 2 の位相検出器と、

を備え、該第 1、第 2 の位相検出器が前記遅延されたクロック信号と遅延されていないクロック信号とを比較して前記位相関係を示す出力を生成するよう構成されている位相検出回路と、

複数の遅延回路であって、各遅延回路は複数のクロック信号の対応する一つに結合し、

遅延信号に基づいて該複数のクロック信号の 1 つを調整するためのものである複数の遅延回路と、 20

前記位相検出回路の出力を受信して前記遅延信号を発生し、この遅延信号を前記位相検出回路の出力に基づいて前記複数の遅延回路の 1 つに送出するコントローラとを備えることを特徴とする同期デジタル・システム。

【請求項 3】

複数のクロック信号を受け取り、該クロック信号同士の間の位相関係に基づいて出力データを生成するように構成した位相検出回路であって、

第 1 のクロック信号を所定量だけ遅延させる第 1 の遅延負荷と、

第 2 のクロック信号を所定量だけ遅延させる第 2 の遅延負荷と、

前記遅延されたクロック信号の一方と遅延されないクロック信号の一方とを受け取る

第 1 の位相検出器と、

前記遅延されたクロック信号の他方と遅延されないクロック信号の他方とを受け取る

第 2 の位相検出器と、

を備え、該第 1、第 2 の位相検出器が前記遅延されたクロック信号と遅延されていないクロック信号とを比較して前記位相関係を示す出力を生成するよう構成されている位相検出回路と、

各遅延回路が前記複数のクロック信号の対応する一つに結合している、複数の遅延回路にそれぞれ結合した複数のレジスタと、

前記位相検出回路と前記複数のレジスタとに結合しており、前記位相検出回路からの出力データを読み取って前記複数のクロック信号間の遅延を決定し、かつ前記複数のクロック信号間の遅延を選択的に調整するため該複数のレジスタの 1 つを変更するコントローラとから構成され、

前記遅延回路は前記レジスタに蓄積されている値に基づいて前記複数のクロック信号の 1 つを調整することを特徴とするクロック信号をデスキューする装置。

【請求項 4】

デジタル・システムをデスキューする方法において、この方法は、

遅延回路に接続した複数のクロック信号間の位相関係を決定するステップと、

前記決定された位相関係と前記遅延回路の出力に基づいて、前記複数のクロック信号を同期させるために前記複数のクロック信号の 1 つを調整するステップとを有しており、

さらに、この調整するステップが、 50

前記位相関係をコントローラに供給し、前記位相関係と前記遅延回路の出力に基づいて、前記コントローラが前記複数のクロック信号のどの信号の調整を必要とするかを決定するステップを含んでおり、

前記位相関係を決定するステップが、

第1のクロック信号を第1の位相検出器に供給することと、

第2のクロック信号を所定量だけ遅延させることと、

該遅延された第2のクロック信号を前記第1の位相検出器に供給することと、

遅延されていない前記第2のクロック信号を第2の位相検出器に供給することと、

前記第1のクロック信号を所定量だけ遅延させることと、

前記遅延された第1のクロック信号を前記第2の位相検出器に供給こととを含み、該

第1、第2の位相検出器が、前記第1のクロック信号が第2のクロック信号に先行していること、前記第2のクロック信号が前記第1のクロック信号に先行していること、あるいは前記第1、第2のクロック信号が同期していることのいずれかの位相関係を生成することを含んでおり、さらに、この方法は、

前記調整を必要とすると、前記コントローラによって決定された前記複数のクロック信号の1つに結合している遅延回路にコントローラ信号を送出するステップと、

前記コントローラ信号に基づいて前記複数のクロック信号の1つの信号の遅延を補正するステップとを有していることを特徴としたデジタル・システムをデスキーする方法。

【発明の詳細な説明】

【0001】

(関連出願の相互参照)

本出願は、本出願と同じ日付に出願され、本出願と同じ譲渡人に譲渡された、発明者Xia DaiおよびJohn Thompson Ortonによる「Adaptive Filtering Scheme For Sampling Phase Relations Of Clock Networks」と題する米国特許出願第\_\_\_\_\_号に関する。

【0002】

(発明の分野)

本発明は、クロック分配管理分野に関する。詳細には、本発明は、マイクロプロセッサ内のクロック分配線をデジタル的なデスキー(クロックの立ち上がりのずれを修正する)に関する。

【0003】

(発明の背景)

初期のマイクロプロセッサ設計は、マイクロプロセッサの中央に配置された単一のクロック分配線またはスパインを使用してマイクロプロセッサ全体にわたってクロック信号を送る。マイクロプロセッサ内の格子状の電力分配によって、ダイを横切って非一様な熱勾配および電圧勾配が形成され、送られたクロック信号にスキーが形成される。いくつかのマイクロプロセッサ設計は、ダイの周辺に沿った2本の分配線を使用してこの効果を低減している。しかし、この方法では、依然としてクロック分配線同士の間にスキーが生じる。マイクロプロセッサ設計のクロック周波数が増加するにつれて、クロック分配回路網内のスキー管理はますます重要になっていく。クロック・スキーは、マイクロプロセッサ入出力および内部回路タイミングに影響を与える。最大遅延経路で、クロック・スキーは最大動作周波数を制限する。クロック・スキーは、負荷、回路網分布、およびデバイス不一致と、温度勾配および電圧勾配の関数である。

【0004】

ある従来型のアナログ同期システムでは、中央タップによる一定の遅延が1本の分配線で使用され、それに対して第2の分配線が調整される。このアナログ手法の1つの欠点は、遅延を延長したときにシステムのフィードバック・ループでノイズが生成されることである。

【0005】

10

20

30

40

50

(発明の概要)

マイクロプロセッサ内のクロック分配信号をデジタルにデスキーする装置について説明する。このデジタル・デスキー回路は、クロック分配線内の遅延線と、位相検出回路と、コントローラとで構成される。位相検出回路は、クロック分配線同士の間の位相関係を決定し、同時にノイズを調整し、コントローラ用の出力を生成する。コントローラは、位相検出情報およびあるビットを遅延シフト・レジスタから取り出し、1本の遅延線に離散的な調整を施す。

【0006】

本発明の他の特徴および利点は、添付の図面および以下の詳細な説明から明らかになろう。

10

【0007】

本発明を限定ではなく例として添付の図面に示す。図中、同じ参照番号は同じ要素を示す。

【0008】

(詳細な説明)

プリグローバル・マイクロプロセッサ・クロック分配回路網内の遅延線と、位相検出回路と、制御論理とで構成されたデジタル・デスキー回路について説明する。制御論理は、クロック・スペイン位相関係情報を受け取り、クロック分配回路網内のスキーを補償するように遅延線の遅延を調整する。本発明の実施形態の初期の利点には、実際のクロック回路網構成要素変形形態および相互接続変形形態に基づくスキーの低減が含まれる。1つの所期の利点は、スキーが低減され、同時に、クロック分配回路網のフィードバック・ループが最小限に抑えられることである。

20

【0009】

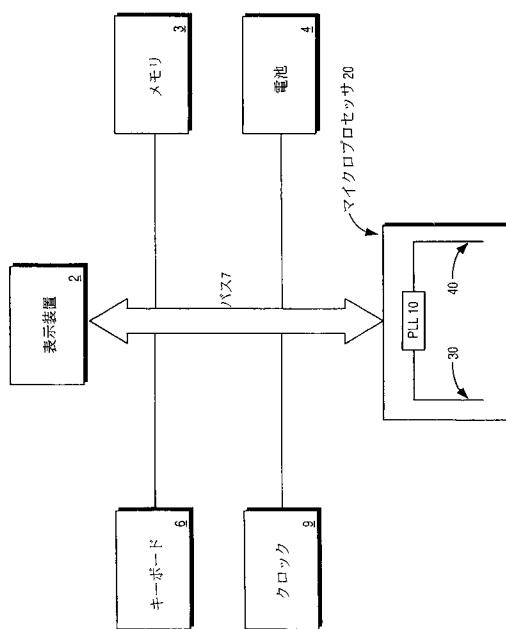

図1は、本発明の実施形態を含むマイクロプロセッサを有するコンピュータ・システムの概略図を示す。コンピュータ・システムは、一実施形態では、電池駆動システムである。他の実施形態では、コンピュータ・システムはAC(「交流」)駆動であってよい。コンピュータ・システムは、ラップトップ・コンピュータ、ノートブック・コンピュータ、デスクトップ・コンピュータ、ワークステーション、メインフレーム、または任意の他の種類のコンピュータでよい。また、コンピュータ・システムは、プリンタ・システムや携帯電話システムなど任意の種類のデータ処理システムまたは信号処理システムでよい。コンピュータ・システムは一般に、表示装置2と、キーボード6と、メモリ3と、電池4と、クロック9と、クロック・スペイン30、40およびフェーズ・ロック・ループ(「PLL」)10を有するマイクロプロセッサ20とを備える。バス7は、様々な構成要素およびサブシステムを互いに結合する。バス7は、信号線、クロック線、および電源線を備える。

30

【0010】

メモリ3は、マイクロプロセッサによって使用される情報を記憶する。メモリ3は、ダイナミック・ランダム・アクセス・メモリ(「DRAM」)、静态的・ランダム・アクセス・メモリ(「SRAM」)、ハード・ディスク・ドライブ、フロッピィ・ディスク、コンパクト・ディスク読み取り専用メモリ装置(「CD-ROM」)、フレッシュ・メモリ、またはその他のメモリ装置を備えることができる。

40

【0011】

電池4は、コンピュータ・システムに電力を供給する。通常、コンピュータ・システムは、AC電力を使用することができるが、電池は、AC電力の使用が不都合であるか、あるいはAC電力が使用不能であるときに使用される。電池4はリチウム電池でも、ニッカド電池でも、ニッケル・メタル・ハライド電池でも、あるいはその他の電池装置でもよい。電池駆動コンピュータ・システムはエネルギーを節約する必要があるので、通常、このようなシステムは、コンピューティング活動が存在しないときに、マイクロプロセッサを含む様々な構成要素またはサブシステムを待機モードまたは低電力モードにする。低電力モードでは、マイクロプロセッサ20の一部またはすべてをオフにすることができ、したが

50

つて、一方または両方のクロック・スペインがオフになる。このような条件の下では、デスキー回路も非活動化する必要がある。システムが通常モードに戻ると、デスキー回路が通常の状態に復元する。本発明の他の実施形態は、システムの電力投入時にクロック分配スペインのデスキーのみを行うように構成することができる。

【0012】

クロック9は、動作を行うタイミング基準を同期されるコンピュータ・システムに与えるために使用される。クロック9は、水晶発振器、タイマ、マルチバイブレータ、またはその他のタイミング装置でよい。クロック9は、マイクロプロセッサなどのコンピュータ・サブシステムにタイミング信号を与え、このようなサブシステムの動作を同期させる。

【0013】

マイクロプロセッサ20は、キーボード6から信号を受け取り、情報を表示装置2に送る。代替実施形態では、マイクロプロセッサ20はコプロセッサでよい。他の実施形態では、マイクロプロセッサ20は、マイクロコントローラなど他の種類のプロセッサでよい。マイクロプロセッサ20は、メモリ3から得た情報を処理し、メモリ3に情報を記憶する。マイクロプロセッサ20は、コンピュータ・プログラムまたはオペレーティング・システムを復号し実行することができる。

10

【0014】

後述の実施形態では、デスキー回路は、マイクロプロセッサ20のPLL10に結合された2つのクロック分配スペイン、すなわち線30および40を備える。ただし、本発明は2つ以上のクロック・スペインまたは単一の分割クロック・スペインを含むことができる。

20

【0015】

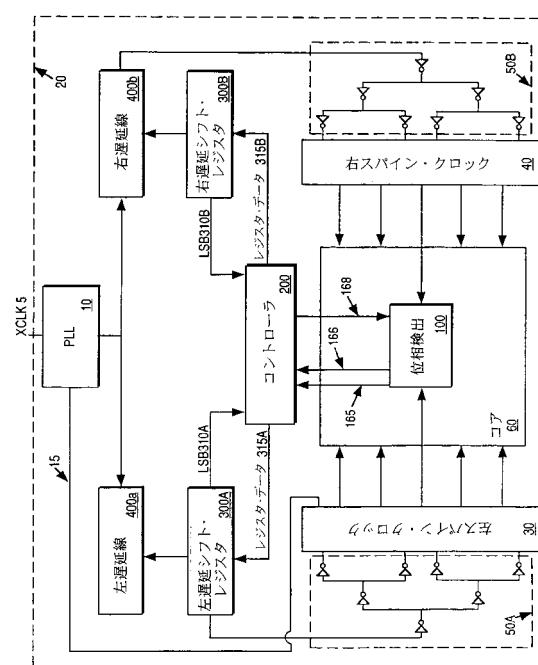

図2は、本発明の一実施形態を実装したマイクロプロセッサ20内のデジタル・デスキー回路のブロック図である。マイクロプロセッサ20内のPLLは、内部クロックを外部クロックに固定するか、あるいは同期させる働きをする。通常、PLLによって生成される内部クロックは、周波数合成と呼ばれる周知の方法によって外部クロックよりも高い周波数で動作する。一実施形態では、PLL10は、入力XCLK5を介してPLLに供給されるクロック9と左クロック・スペイン30を線15を介して同期させる。

【0016】

PLL10は、同期クロック信号を遅延線400aおよび400bを通して出力し、分配部50aおよび50bをバッファする。バッファされた分配部50aおよび50bは、クロック回路網のローディング機能または駆動機能を強化する。クロック・スペイン30および40は、マイクロプロセッサ20のPLL10によって生成される内部クロック・コア60を分配するクロック信号線である。図2の位相検出回路100は、左スペイン・クロック30と右スペイン・クロック40との間の位相関係を判定し、コントローラ200に入力されるバス線165および166のバイナリ出力を生成する。コントローラ200はまた、左遅延シフト・レジスタ300aおよび右遅延シフト・レジスタ300bの最下位ビット(「LSB」)をそれぞれ線LSB310AおよびLSB310Bに沿って受け取る。コントローラ200は、これらの入力を使用して、クロック・スキューを補償するよう遅延線400aおよび400bに沿った容量負荷を調整する。負荷調整は、コントローラ200の出力レジスタ・データ315Aおよび出力レジスタ・データ315Bを介して実行される。レジスタ・データ315Aおよびレジスタ・データ315Bは、左遅延シフト・レジスタ300Aおよび右遅延シフト・レジスタ300Bに記憶されている値を変更する。これらの遅延シフト・レジスタ内の値は、左遅延線400aおよび右遅延線400bに対する容量負荷の除去または付加を介して左スペイン・クロック30および右スペイン・クロック40を変更するために使用される。

30

40

【0017】

一実施形態では、レジスタ・データ315Aは、左遅延レジスタ300AのLSBに値「1」をシフトし、左遅延線400aに容量負荷を付加する。これによって、左クロック・スペイン30上の遅延が延長する。レジスタ・データ315Aは、左遅延レジスタ300

50

A の M S B に値「0」をシフトし、したがって、左遅延線 4 0 0 a に対する容量負荷を低減させる。これによって、左クロック・スパイン 3 0 上の遅延が短縮される。レジスタ・データ 3 1 5 B は、右遅延レジスタ 3 0 0 B に値「1」をシフトし、右遅延線 4 0 0 b に容量負荷を付加し、したがって、右クロック・スパイン 4 0 上の遅延を延長する。レジスタ・データ 3 1 5 B は、右遅延レジスタ 3 0 0 B の M S B に値「0」をシフトし、右遅延線 4 0 0 b に対する容量負荷を低減し、したがって、右クロック・スパイン 4 0 上の遅延を短縮する。

#### 【 0 0 1 8 】

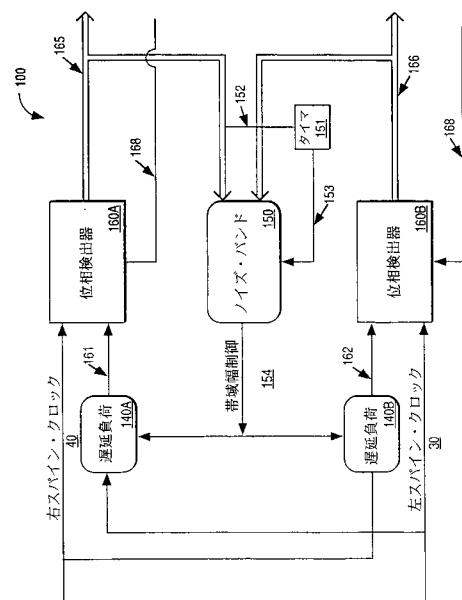

図 3 は位相検出回路 1 0 0 を示す。位相検出回路 1 0 0 は、2 つの対称位相検出器 1 6 0 a および 1 6 0 b と、2 つの遅延負荷 1 4 0 a および 1 4 0 b と、ノイズ・バンド 1 5 0 (以下を参照されたい) とを備えている。図 2 の左スパイン・クロック 3 0 および右スパイン・クロック 4 0 はそれぞれ、位相検出器 1 6 0 a および 1 6 0 b への入力である。位相検出器 1 6 0 a は、線 1 6 1 として示された遅延左スパイン・クロック 3 0 も入力として有する。位相検出器 1 6 0 b は、線 1 6 2 として示された遅延右スパイン・クロック 3 0 も入力として有する。線 1 6 1 および 1 6 2 上の信号は、それぞれ遅延負荷 1 4 0 a および 1 4 0 b によって制御される調整可能な等しい量だけ遅延される。位相検出器 1 6 0 a では、左スパイン・クロック 3 0 からの信号が、一定量だけ遅延され、次いで、右クロック・スパイン 4 0 からの遅延されていない信号と比較される。位相検出器 1 6 0 b では、右スパイン・クロック 4 0 からの信号が、一定量だけ遅延され、次いで、左クロック・スパイン 3 0 からの遅延されていない信号と比較される。各位相検出器は、遅延されたクロック信号が遅延されていないクロック信号に先行しているかどうかを判定する。

#### 【 0 0 1 9 】

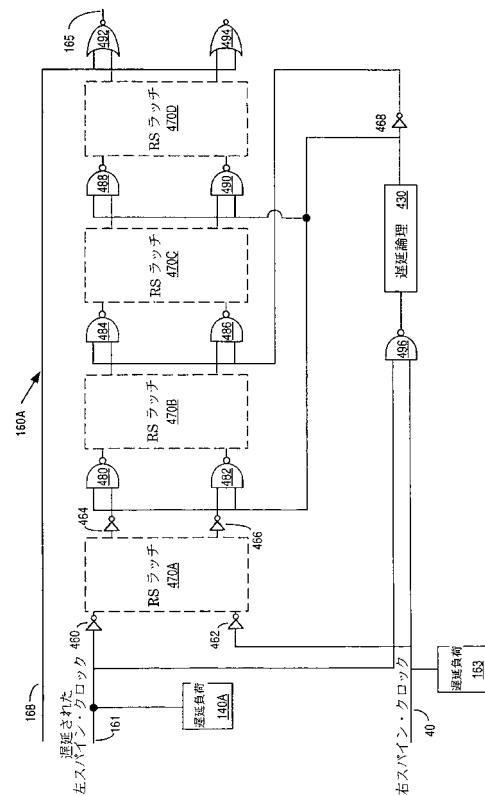

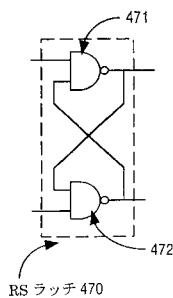

図 4 a は、位相検出回路 1 0 0 の位相検出器 1 6 0 a を示す。位相検出器 1 6 0 a は、4 つの R S ラッチ 4 7 0 を直列結合することによって構成される。入力遅延左スパイン・クロック 1 6 1 は遅延負荷 1 4 0 a 、インバータ 4 6 0 、および N A N D 4 9 6 に結合される。入力右スパイン・クロック 4 0 は遅延負荷 1 6 3 、インバータ 4 6 2 、および N A N D 4 9 6 に結合される。インバータ 4 6 0 および 4 6 2 の出力は第 1 の R S ラッチ 4 7 0 A に出力される。N A N D 4 9 6 の出力は遅延論理 4 3 0 に結合される。

#### 【 0 0 2 0 】

R S ラッチ 4 7 0 A の一方の出力はインバータ 4 6 4 および N A N D 4 8 0 を介して R S ラッチ 4 7 0 B に結合され、それに対して、第 2 の出力はインバータ 4 6 6 および N A N D 4 8 2 を介して R S ラッチ 4 7 0 B に結合される。N A N D ゲート 4 8 0 および 4 8 2 の入力は遅延論理 4 3 0 の出力である。同様な結合によって、R S ラッチ 4 7 0 B が R S ラッチ 4 7 0 C に接続され、R S ラッチ 4 7 0 C が R S ラッチ 4 7 0 D に接続される。しかし、N A N D ゲート 4 8 4 および 4 8 6 の一方の入力はインバータ 4 6 8 の出力に結合され、インバータ 4 6 8 の出力は遅延論理 4 3 0 の出力に結合される。R S ラッチ 4 7 0 D の出力および入力 1 6 8 (以下を参照されたい) は N O R ゲート 4 9 2 に結合される。N O R ゲート 4 9 2 はバイナリ出力 1 6 5 を生成する。

#### 【 0 0 2 1 】

本発明の一実施形態では、7 つの遅延負荷タップと 1 つの固定タップを用いて遅延負荷 1 4 0 a を調整することができる。遅延負荷 1 4 0 a は最初、1 つの固定タップに設定され、遅延負荷 1 6 3 は、整合させるように設定されたタップなしで使用される。タップ当たり遅延は通常、1 5 ピコ秒 (「 p s 」) に設定されるが、設計要件に応じて変更することができる。位相検出器 1 6 0 b は、上記で位相検出器 1 6 0 a に関して説明したのと同様に動作する。

#### 【 0 0 2 2 】

図 4 b は、クロス結合された N A N D ゲート 4 7 1 および 4 7 2 を含む R S ラッチ 4 7 0 を示す。クロス結合された N A N D ゲート 4 7 1 および 4 7 2 は R S (リセット・セット) ラッチとして構成される。ラッチ性能に影響を与える因子は準安定性である。2 つの信号がほぼ同じ時間にラッチされ、完全 V C C レベルまたは完全 V S S (グランド) レベル

10

20

30

40

50

から逸脱した「0」と「1」の間のラッチ出力が得られたときに準安定性が生じる。この条件がラッチ・チェーンに沿って伝搬すると、位相検出器の偽出力状態が得られる。ラッチは、複数のラッチが直列結合されたときに準安定性条件が伝搬する可能性を低減するように設計されパイプライン化される。

#### 【0023】

従来型の位相検出方式は、アナログ電圧を駆動するパルス幅を使用する。位相検出器160aおよび160bは、バス線165および166上でコントローラ200にバイナリ出力を供給する。信号165と信号166の可能な出力組合せは、左スパイン・クロック30と右スパイン・クロック40との間の遅延を反映する。一実施形態では、出力値「10」は、右スパイン・クロック40に先行する左スパイン・クロック30に対応する。出力値「01」は、左スパイン・クロック30に先行する右スパイン・クロック40に対応する。出力値「00」は、ノイズ・バンド・フィルタ150の帯域幅内に残る左スパイン・クロック30と右スパイン・クロック40の両方に対応する。出力「11」は通常、発生しない。位相検出器160aおよび160bへの遅延入力161および162によって、11出力状態が生じることはなくなる（出力11は、各遅延入力が他の入力に先行すること、すなわち、RSラッチ470のクロス結合されたNANDゲートの準安定性のために擬似生成されないかぎり通常は生じない矛盾する条件を意味する。

#### 【0024】

本発明の他の実施形態では、マイクロプロセッサは、すべてのクロック・スパインが使用されるわけではない低電力モードで動作する。このような動作モードでは、デスキューレ路がディスエーブルされ、シフト・レジスタ・ビットが記憶され、位相検出回路100の出力が、コントローラ200によって図2の線168を介して00状態にされる。これは、通常電力モードに戻る際にデスキューレ路をプリシャットダウン状態に再初期設定するために行われる。

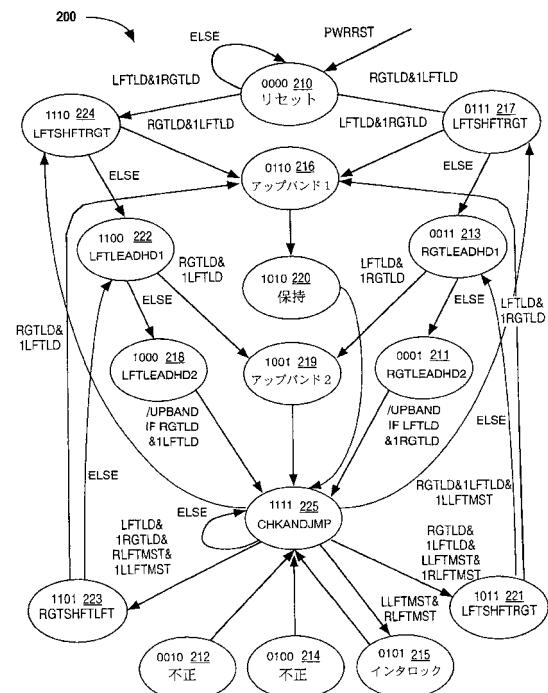

#### 【0025】

図5Aは、コントローラ200の状態図を示す。デスキューレ路の制御は状態マシンによって実行される。この状態マシンは、位相検出回路100出力165および166を遅延シフト・レジスタの最下位ビット（「LSB」）310aおよび310bと共に解釈し、次いで遅延線400aおよび400bを更新する。クロック・スパイン30および40の標本抽出から遅延線400aおよび400bの調整までの呼出し時間は、3クロック・サイクルに過ぎない。新しい標本は第5サイクルで得られる。各4サイクル内に、最大で1回のシフト・イベントしか行われない。

#### 【0026】

更新は、検査ジャンプ（「CHKANDJMP」）状態225で開始する。状態225で、コントローラは左遅延シフト・レジスタ300aまたは右遅延シフト・レジスタ300bをシフト・アップまたはシフト・ダウンする。コントローラは、左クロック・スパイン30と右クロック・スパイン40との間の遅延と、LSB310aおよびLSB310bの値とに基づいてどちらの遅延シフト・レジスタをシフトするかを判定する。前述のように、位相検出出力165および166は、左スパイン・クロック30と右スパイン・クロック40との間の遅延を反映する。たとえば、左クロック・スパイン30が右クロック・スパイン40に先行しており、右遅延シフト・レジスタ300bのLSB310bが「0」である（現在、右遅延線上に負荷がないことを示す）場合、コントローラは状態224に移行し、左遅延シフト・レジスタ300aを1ビットだけシフト・アップする。コントローラ200は、右シフト・レジスタ300b上に遅延が付加されていないことを検出しているので、左クロック・スパイン30に遅延を付加している。次に、コントローラはアップバンド・イベント、すなわち状態216を検出し、状態220を1サイクル保持し、次いでCHKANDJUMP状態225に戻る。アップバンド・イベントが起こるのは、一方の遅延線への修正された遅延が有効になる前にクロック・スパインの位相関係が反転するときである。コントローラは、状態224でアップバンド・イベントを検出しなかつた場合は状態222に進み、状態222でアップバンド・イベントが検出されない場合は

10

20

30

40

50

状態 218 に進む。検出された場合は状態 219 に進む。

【0027】

他の例を挙げると、左クロック・スペイン 30 が右クロック・スペイン 40 に先行しており、右遅延シフト・レジスタ 300b の LSB310b が「1」である（現在、遅延線上に負荷があることを示す）場合、コントローラは状態 223 に移行し、右シフト・レジスタ 300b の MSB に「0」をシフトし、右シフト・レジスタの LSB から「1」をシフトする。前の例と同様に、コントローラは、状態 222 でシフト・レジスタ・ビットを保持し、状態 219 でアップバンド・イベントを監視する。コントローラ状態 221、217、213、および 211 は、右クロック・スペイン 40 が左クロック・スペイン 30 に先行していることをコントローラ 200 が検出したときに、それぞれ状態 223、224、222、および 218 について説明したのと同様に動作する。10

【0028】

不正ブロック 212 および 214 は、正常条件下では存在すべきではない状態であり、このとき、コントローラ 200 が準安定性のために不可能条件を検出し、CHKANDJUMP 状態 225 にループバックする。

【0029】

リセット・ブロック 210 は、コントローラが電力投入または電力リセット（「PWR\_RST」）に入る初期状態である。この初期状態では、シフト・レジスタ 300a にも、あるいはシフト・レジスタ 300b にも遅延は付加されていない。したがって、シフト・レジスタ 300a とシフト・レジスタ 300b は共にすべてのビット位置に「0」を有し、コントローラ 200 はシフト・レジスタ 300a とシフト・レジスタ 300b のいずれかにのみ遅延を付加することができる。このため、この後に続く可能な状態は、それぞれ、左シフト・レジスタ 300a において、「1」が右側の最左ビット 310a にシフトされるか、あるいは右シフト・レジスタ 300b において、「1」が右側の最左ビットにシフトされることに対応する状態 224 または状態 217 の 2 つの状態だけである。コントローラ 200 は次いで、前述のように進行する。20

【0030】

本発明の一実施形態では、コントローラ 200 の状態マシンが、ループ遅延を最小限に抑えるためにインタロックを組み込んでいる。インタロックによって、一方の線への遅延の付加は、他方の線上に遅延が存在するときには妨げられる。調整された遅延線が、前の更新で遅延がなくなるように駆動されており、この遅延をさらに短縮する必要がないことを位相検出回路 100 が示している場合にのみ、コントローラは他の遅延線の遅延の延長を開始する。前の例で例示すると、右遅延シフト・レジスタ 300b の LSB310b が「1」であった場合（現在、遅延線上に負荷が存在する）、右遅延シフト・レジスタ 300b は 1 ビットだけシフト・ダウンされる。したがって、コントローラ 200 は、左クロック・スペイン 30 に遅延を付加する前に、右クロック・スペイン 40 上の遅延を短縮する。遅延シフト・レジスタの両方の LSB に「1」を有するシフト・レジスタ・パターンが検出されると状態 215 に入る。遅延シフト・レジスタの破壊は、準安定イベントによって起こる可能性があり、状態 215 で両方の遅延シフト・レジスタの LSB から 1 をシフト・アウトすることによって正常状態に補正される。電源ノイズによって誘発されるジッタが電源ノイズの量およびクロック・ループ遅延の長さの関数であるので、インタロック機能により、遅延するクロック・スペインは、クロック・ジッタを最小限に抑えるように最小限の遅延に維持される。3040

【0031】

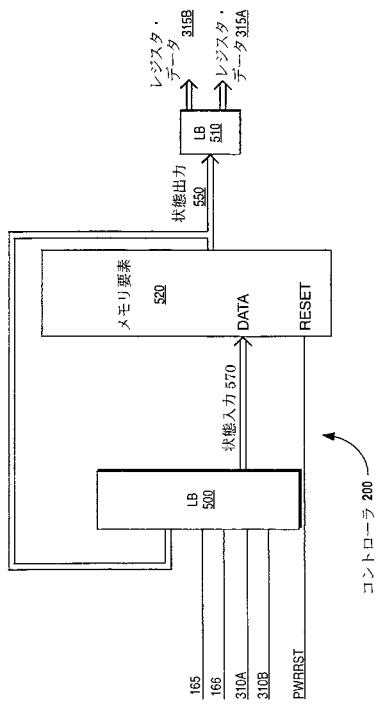

図 5b は、図 5a の状態図の好ましい一実施形態を実現する論理図を示す。図 5a の状態図の様々な変形形態および変形実施が可能である。図 5b は、フィードバック経路でメモリ要素 520 に結合された組合せ論理ブロック（LB）500 および 510 からなる。メモリ要素 520 に記憶されているバイナリ情報は、図 5a に示すコントローラ 200 の状態を定義する。

【0032】

一実施形態では、メモリ要素 520 は、クロス結合されたインバータからなる R S フリップ・フロップを含む。代替実施形態では、メモリ要求はたとえば、ロード可能 / リセット可能なカウンタ、D フリップフロップ、JK フリップフロップ、またはスタティック参照テーブルを含む。

【0033】

コントローラ 200 は入力 165、166、PWR RST、310A および 310B を有する。入力 165 および 166 は図 3 の位相検出回路 100 のバイナリ出力である。入力 165 および 166 は、左スパイン・クロック 30 が先行しているかどうか、右スパイン・クロック 40 が先行しているかどうか、あるいは左スパイン・クロック 30 と右スパイン・クロック 40 が共に図 3 のノイズ・バンド・フィルタ 150 の帯域幅内にあるかどうかをコントローラ 200 に知らせる。入力 PWR RST はコントローラ 200 に電力投入または電力リセットを知らせる。入力 310A および 310B はそれぞれ、左遅延シフト・レジスタ 300a の LSB および右遅延シフト・レジスタ 300b の LSB を表す。これらの入力は、メモリ要素 520 の現在の状態と共に、コントローラ 200 のバイナリ出力を決定する。コントローラ 200 のバイナリ出力はレジスタ・データ 315a およびレジスタ・データ 315b である。出力レジスタ・データ 315a は左遅延シフト・レジスタ 300a 内の値を変更し、それによって、左クロック・スパイン 30 上のクロック遅延が変更される。出力レジスタ・データ 315a は、左遅延シフト・レジスタ 300a の LSB に値「1」をシフトして遅延を延長するか、あるいは左遅延シフト・レジスタ 300a の MSB に値「0」をシフトして遅延を短縮するために使用される。出力レジスタ・データ 315b は右遅延シフト・レジスタ 300b 内の値を変更し、それによって、右クロック・スパイン 40 上のクロック遅延が変更される。出力レジスタ・データ 315b は、右遅延シフト・レジスタ 300b の LSB に値「1」をシフトして遅延を延長するか、あるいは右遅延シフト・レジスタ 300b の MSB に値「0」をシフトして遅延を短縮するために使用される。

【0034】

したがって、コントローラ 200 は、図 5a の状態図に続いて出力レジスタ・データ 315a および出力レジスタ・データ 315b を変更することによって、右クロック・スパイン 40 または左クロック・スパイン 30 に離散的な調整を施すことができる。このクロック調整は、位相検出器回路 100 の出力と、左遅延シフト・レジスタ 300a の LSB および右遅延シフト・レジスタ 300b の LSB に依存する。

【0035】

図 5a の状態入力はメモリ要素 520 に記憶される。メモリ要素 520 は、入力 PWR RST に結合されたリセット入力と、状態入力 570 を介して LB500 に結合された 4 ビット・データ入力と、4 ビット・データ出力、すなわち状態出力 550 とを含む。

【0036】

リセット入力は、アサートされると、状態出力 550 の出力を図 5a の状態 210a に対応する「0000」に変更する。リセット入力は、入力 PWR RST を介してアサートされる。

【0037】

LB500 はメモリ要素 520 の現在の状態を変更する。具体的には、現在の状態を変更する場合、LB は入力状態入力 570 を介してメモリ要素 520 に 4 ビット値をロードする。ローディング値を決定する場合、LB500 は入力 165 および 166、状態出力 550、ならびに入力 LSB310A および LSB310B を標本抽出する。LB500 は、これらの入力に応じて、図 5a の状態図の状態遷移に従う。これらの状態遷移は、アップバンド・イベント、不正状態、インタロック、および正常動作の 4 つの範疇に分類される。

【0038】

アップバンド・イベントは、1 本のクロック線の遅延が生じる前にクロック・スパインの位相関係が逆転するときに起こる。このようなイベント中に、LB500 は、状態出力 5

10

20

30

40

50

50が「0111」または「1110」であるかどうかを判定し、そうである場合、LB500は、1サイクルの間保持されメモリ要素520に値「1111」をロードする。状態出力550が「1100」または「0011」である場合、LB500は遅延なしにメモリ要素520に値「1111」をロードする。この状態シフトは、図5aの状態213、216、217、219、220、222、および224に対応する。

#### 【0039】

不正状態は、準安定性などの異常条件によって起こる。この状態では、状態出力550上で値「0010」および「0100」が生成される。この状態が起こると、LB500はメモリ要素520に値「1111」をロードする。

#### 【0040】

LB500はインタロック、すなわち静的出力「0101」も処理する。インタロックによって、あるクロック線への遅延の付加は、他のクロック線上に遅延が存在するときには妨げられる。特に、コントローラ200は(LB500を介して)、出力信号レジスタ・データ135bおよびレジスタ・データ315aを確実にインタロックに従わせる。したがって、場合によっては、このような出力は、単に所与のクロック線に遅延を付加するのではなく反対側のクロック線からの遅延を短縮することによってクロック・スキューを補償する。この状態シフトは図5aの状態212、214、および215に対応する。

#### 【0041】

正常動作は、前述の遷移を除く、図5aのすべての状態遷移を含む。正常動作中に、LB500は、状態出力550の現在の状態に応じてコントローラ200の次の状態をロードする。LB500は、「1101」、「1110」、「1100」、「1000」、「1011」、「0111」、「0011」、「0001」、および「1111」の各値のうちの1つをメモリ要素520にロードすることができる。この状態シフトは図5aの状態211、213、217、218、221、223、224、または225に対応する。

#### 【0042】

LB510は、入力状態出力550を有し、レジスタ・データ315aおよび315bを出力する。出力レジスタ・データ315aは、コントローラ200が左遅延シフト・レジスタ300aのLSBに値「1」をシフトするか、それとも左遅延シフト・レジスタ300aのMSBに値「0」をシフトするかを決定する。出力レジスタ・データ315bは、コントローラ200が右遅延シフト・レジスタ300bのLSBに値「1」をシフトするか、それとも右遅延シフト・レジスタ300aのMSBに値「0」をシフトするかを決定する。値「1101」、「1000」、「1011」、または「0001」を有する状態出力550は、LB520が信号線レジスタ・データ315aまたは315bを介してレジスタ・シフトをアサートするかどうかを決定する。この状態シフトは図5aの状態211、218、および223に対応する。

#### 【0043】

本発明の他の実施形態では、図3のノイズ・バンド150を使用して高周波数AC電圧ノイズが除去される。これによって、システムが安定化し、クロック・スパン30および40にフェーズ・エラーを付加する可能性がある接続が回避される。ノイズ・バンド150は、帯域幅を制御するようにバス線165および166を介して段階的に調整できる7ビット・シフト・レジスタである。ノイズ・バンド・フィルタ150はまず、最小帯域幅から開始する(すべてのシフト・レジスタ・ビットが「0」)。補正が行われる前に左スパン・クロック30と右スパン・クロック40との間の位相関係が逆転した場合、ノイズ帯域幅は、図6に示すようにレジスタに「1」をシフトすることによって増分され、遅延負荷140aおよび140bからの遅延負荷タップが位相検出器入力161および162に付加される。たとえば、あるサイクル中に左スパン30が右スパン40に先行している場合、クロック回路網にステップ遅延が導入され、左スパン30が遅延される。しかし、遅延が行われる前に、右スパン40が左スパン30に先行していることを位相検出器160aおよび160bが検出した場合、システムが追従できないほど早いノイズ、および現在のノイズ帯域幅よりも大きなノイズがクロック回路網に存在することを

10

20

30

40

50

示すアップバンド・イベントが生じする。このような条件の下では、クロック・スパンの遅延は調整されず、ノイズ・フィルタ150の帯域幅がバス線165および166を介して増大する。このノイズ除去方式は、システムが電圧遷移によるクロック分配回路網のスキー変動のより低速のAC成分を補正できるようにするデジタル信号処理（「DSP」）方式と比べて呼出し時間を短縮する。

#### 【0044】

しかし、ノイズ帯域幅が大きくなればなるほど、スキーも大きくなる。一実施形態では、本発明は図3のアナログ・タイマ151を有し、アナログ・タイマ151は、わずかなノイズ帯域幅を除去するために約10マイクロ秒（「us」）でタイム・アウトする。このタイマがタイム・アウトすると、アップバンド・イベントは起こらず、ノイズ・バンド・シフト・レジスタが線153を介して1だけ減分され、対応するノイズ・バンド遅延140aおよび140bが1遅延タップだけ短縮する。しかし、アップバンド・イベントが起こった場合、コントローラからノイズ・バンドに送られる信号を使用して、タイマが線152を介してリセットされる。

#### 【0045】

図7は、左遅延線400aおよび左シフト・レジスタ300aを示す。本発明の一実施形態では、デジタル遅延線は、直列接続された2つのインバータ401Aおよび402Aを備え、各インバータは、バス・ゲート・スイッチを通してインバータの出力に接続された8つの容量負荷410aおよび420aのバンクを有する。容量負荷の付加または除去は、バス・ゲート・スイッチを開閉する遅延シフト・レジスタ300aによって制御される。2つのインバータを使用することによって、2つのドライバの間で負荷を分割することができ、非反転遅延も形成される。NMOS440負荷とPMOS負荷430は共に、キャパシタンスの電圧感度を低下させ、かつインバータ401aおよび402aの立上がり遅延および立下り遅延を平衡させるために各容量負荷で使用される。

#### 【0046】

遅延シフト・レジスタ300aは、17個の離散的単調遅延ステップ（16個の遅延増分と遅延なし）を可能にする16個のビット（0ないし15）を備える。ステップ当たり遅延は名目上、15psに設定されるが、設計要件に従って増減することができる。16個のビットはそれぞれ、16個の容量負荷のうちの1つに対応する。このように、容量負荷は交互に、2つのインバータ401a、402aの出力に付加されるか、あるいはこれらの出力から除去される。ビット0ないし14は、2ビットごとに（360a）バンク420a内の8つの容量負荷に対応し、ビット1ないし15は、2ビットごとに（350a）バンク410a内の8つの容量負荷に対応する。コントローラ200が遅延の調整を要求するたびに、それぞれ、遅延の延長および遅延の短縮に対応してLSB310aに「1」がシフトされるか、あるいは最上位ビット（「MSB」）320aに「0」がシフトされる。これによって、容量負荷バンク410aおよび420a内の1つの容量負荷がそれぞれ、オンまたはオフに切り替えられる。

#### 【0047】

たとえば、図8Aは、LSB310aから始まる最初の4ビットのそれぞれに「1」で示される4ビット遅延を含むようにプログラムされたシフト・レジスタ300aの現在の状態を示す。右スパン・クロック40が左クロック・スパン30に先行しており、左遅延シフト・レジスタ300aがLSB310aに「1」を含むとコントローラ200が判定した場合、コントローラ200はMSB320aに「0」をシフトし、それによって、図8Bに示すシフト・レジスタ状態が得られる。

#### 【0048】

図2に示す遅延線400bおよび遅延シフト・レジスタ300bは、上記で遅延線400aおよび遅延シフト・レジスタ300aについて説明したのと同様に動作する。

#### 【0049】

上記の明細書では、本発明についてその特定の例示的な実施形態を参照して説明した。しかし、添付の特許請求の範囲の記載された本発明の広い趣旨および範囲から逸脱せずに本

10

20

30

40

50

発明に様々な修正および変更を加えられることが明白であろう。したがって、明細書および図面は、制限的ではなく例示的なものとみなすべきである。

【図面の簡単な説明】

【図 1】 本発明の一実施形態のコンピュータ・システムのブロック図である。

【図 2】 クロックを生成するクロック分配回路網とデジタル・デスキー回路のブロック図である。

【図 3】 位相検出回路を示す図である。

【図 4 A】 位相検出器を示す図である。

【図 4 B】 クロス結合 N A N D ゲートを示す図である。

【図 5 A】 コントローラの状態図である。

【図 5 B】 コントローラの論理ブロック図である。

【図 6】 ノイズ・バンド・シフト・レジスタを示す図である。

【図 7】 遅延線および遅延シフト・レジスタを示す図である。

【図 8 A】 4 ビット遅延を有する遅延シフト・レジスタを示す図である。

【図 8 B】 3 ビット遅延を有する遅延シフト・レジスタを示す図である。

10

【図 1】

【図 2】

【図3】

【図4 A】

【図4 B】

【図5 A】

【図 5 B】

---

フロントページの続き

(72)発明者 テイラー, グレッグ・エフ

アメリカ合衆国・97229・オレゴン州・ポートランド・ノース ウエスト 127ティエイチ

アベニュー・2894

(72)発明者 ダイ, シャ

アメリカ合衆国・95051・カリフォルニア州・サンタ クララ・サンタ クルーズ アベニュー

・2000

審査官 石井 茂和

(56)参考文献 特開平02-255908 (JP, A)

特開平08-054957 (JP, A)

特開平05-066851 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G06F 1/10

H03D 3/24

H03D 13/00

H03L 7/00

WPI(DIALOG)