### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2012-129573 (P2012-129573A)

(43) 公開日 平成24年7月5日(2012.7.5)

(51) Int. Cl.

FL

テーマコード (参考)

HO1L 33/06

(2010, 01)

HO1L 33/00  $1\,1\,2$  5FO41

#### 審査請求 有 請求項の数 9 OL (全 17 頁)

| (21) 出願番号<br>(22) 出願日<br>(62) 分割の表示 | 特願2012-85835 (P2012-85835)<br>平成24年4月4日 (2012.4.4)<br>特願2010-278993 (P2010-278993) | (71) 出願人 | 000003078<br>株式会社東芝<br>東京都港区芝浦一丁目1番1号 |

|-------------------------------------|------------------------------------------------------------------------------------|----------|---------------------------------------|

|                                     | の分割                                                                                | (74)代理人  | 100108062                             |

| 原出願日                                | 平成22年12月15日 (2010.12.15)                                                           |          | 弁理士 日向寺 雅彦                            |

|                                     |                                                                                    | (72) 発明者 | 木村 重哉                                 |

|                                     |                                                                                    |          | 東京都港区芝浦一丁目1番1号 株式会社                   |

|                                     |                                                                                    |          | 東芝内                                   |

|                                     |                                                                                    | (72) 発明者 | 橘浩一                                   |

|                                     |                                                                                    |          | 東京都港区芝浦一丁目1番1号 株式会社                   |

東芝内

(72) 発明者 名古 肇

東京都港区芝浦一丁目1番1号 株式会社

東芝内

最終頁に続く

# (54) 【発明の名称】半導体発光素子の製造方法

# (57)【要約】

【課題】動作電圧を低減した半導体発光素子の製造方法 を提供する。

【解決手段】実施形態に係る半導体発光素子の製造方法 は、n形の第1半導体層と、p形の第2半導体層と、前 記第1半導体層と前記第2半導体層との間に設けられ、 前記第2半導体層から前記第1半導体層に向かう第1方 向に沿って積層され窒化物半導体を含む複数の障壁層と 、前記障壁層どうしの間に設けられInを含む窒化物半 導体を含む井戸層と、を含む発光層と、を備えた半導体 発光素子の製造方法であって、前記障壁層の形成は、反 応炉内を第1温度よりも低い第2温度に設定して第1低 温度形成層を形成する工程と、前記第1低温度形成層を 形成した後、前記反応炉内を前記第1温度に設定して高 温度形成層を形成する工程と、を含む。

## 【選択図】図8

#### 【特許請求の範囲】

### 【請求項1】

n 形の第 1 半導体層と、 p 形の第 2 半導体層と、前記第 1 半導体層と前記第 2 半導体層との間に設けられ、前記第 2 半導体層から前記第 1 半導体層に向かう第 1 方向に沿って積層され窒化物半導体を含む複数の障壁層と、前記障壁層どうしの間に設けられ I n を含む窒化物半導体を含む井戸層と、を含む発光層と、を備えた半導体発光素子の製造方法であって、

前記障壁層の形成は、

反応炉内を第1温度よりも低い第2温度に設定して第1低温度形成層を形成する工程 と、

10

前記第1低温度形成層を形成した後、前記反応炉内を前記第1温度に設定して高温度 形成層を形成する工程と、

を含む半導体発光素子の製造方法。

## 【請求項2】

前記井戸層は、前記井戸層からみて前記第2半導体層の側の前記障壁層との界面を含む p側界面部分と、前記井戸層からみて前記第1半導体層の側の前記障壁層との界面を含む n側界面部分と、を有し、

前記障壁層は、

前記 p 側界面部分における前記第 1 方向に対して垂直な前記面内における等 I n 濃度面の 3 次元凹凸の二乗平均平方根が 0 . 2 5 ナノメートル以下である請求項 1 記載の半導体発光素子の製造方法。

20

## 【請求項3】

前記障壁層の形成は、

前記高温度形成層を形成した後、前記反応炉内を前記第2温度に設定して第2低温度形成層を形成する工程をさらに含む請求項1または2に記載の半導体発光素子の製造方法

## 【請求項4】

前記井戸層の形成は、前記反応炉内を前記第2温度に設定して形成する工程を含み、前記低温度形成層を形成する工程は、前記井戸層を形成した後、前記反応炉内を前記第2温度に維持したまま前記井戸層の上に成膜を行うことを含む請求項1~3のいずれか1つに記載の半導体発光素子の製造方法。

30

# 【請求項5】

前記井戸層を形成する工程は、前記反応炉内にInを含む第1反応ガス及びGaを含む第2反応ガスを導入することを含み、

前記低温度形成層を形成する工程は、前記井戸層を形成する際に前記反応炉内に導入していた前記第1反応ガス及び前記第2反応ガスのうち前記第1反応ガスの導入を停止することを含む請求項4記載の半導体発光素子の製造方法。

### 【請求項6】

前記第2温度は、830 以上である請求項1~5のいずれか1つに記載の半導体発光素子の製造方法。

40

# 【請求項7】

前記第1温度と前記第2温度との差は、40以上100未満である請求項1~6のいずれか1つに記載の半導体発光素子の製造方法。

## 【請求項8】

前記第1温度と前記第2温度との差は、40以上60未満である請求項1~6のいずれか1つに記載の半導体発光素子の製造方法。

#### 【請求項9】

前記障壁層は、

前記p側界面部分の前記第1方向に対して垂直な面内におけるInの濃度のばらつきが、前記n側界面部分の前記第1方向に対して垂直な面内におけるInの濃度のばらつき

以下である請求項1~8のいずれか1つに記載の半導体発光素子の製造方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明の実施形態は、半導体発光素子の製造方法に関する。

【背景技術】

[00002]

窒化物半導体は、紫外、青色、緑色の発光ダイオード(LED:Light Emitting Diode ) や、青紫色、青色のレーザダイオード(LD:Laser Diode)などに応用されている。 このような半導体発光素子において、発光効率や動作電圧などの動作特性の向上がさらに 求められている。

【先行技術文献】

【非特許文献】

[0003]

【非特許文献 1】M.J.Galtrey,R.A.Oliver,M.J.Kappers,C.J.Humphreys,P.H.Clifton , D.Larson, D.W.Saxey, and A.Cerezos, "Three-dimensional atom probe analysis of green- and blue-emitting InxG1-xN/GaN multiple quantum well structure", J. Appl. Phys. 104 (2008) 013524.

【発明の概要】

【発明が解決しようとする課題】

[0004]

本発明の実施形態は、動作電圧を低減した半導体発光素子の製造方法を提供する。

【課題を解決するための手段】

[00005]

実 施 形 態 に 係 る 半 導 体 発 光 素 子 の 製 造 方 法 は 、 n 形 の 第 1 半 導 体 層 と 、 p 形 の 第 2 半 導 体層と、前記第1半導体層と前記第2半導体層との間に設けられ、前記第2半導体層から 前記第1半導体層に向かう第1方向に沿って積層され窒化物半導体を含む複数の障壁層と 、前記障壁層どうしの間に設けられInを含む窒化物半導体を含む井戸層と、を含む発光 層と、を備えた半導体発光素子の製造方法であって、前記障壁層の形成は、反応炉内を第 1温度よりも低い第2温度に設定して第1低温度形成層を形成する工程と、前記第1低温 度形成層を形成した後、前記反応炉内を前記第1温度に設定して高温度形成層を形成する 工程と、を含む。

【図面の簡単な説明】

[0006]

- 【図1】実施形態に係る半導体発光素子を示す模式的断面図である。

- 【図2】実施形態に係る半導体発光素子の一部を示す模式的断面図である。

- 【 図 3 】 実 施 形 態 に 係 る 半 導 体 発 光 素 子 の 一 部 を 拡 大 し た 模 式 的 断 面 図 で あ る 。

- 【図4】図4(a)及び図4(b)は、半導体発光素子の特性を示す模式図である。

- 【図5】図5(a)及び図5(b)は、半導体発光素子の特性を示す模式図である。

- 【図6】半導体発光素子の特性を示すグラフ図である。

【図7】半導体発光素子の特性を示すグラフ図である。

【図8】実施形態に係る半導体発光素子の製造方法を示す模式図である。

【発明を実施するための形態】

[0007]

以下、実施形態を図に基づき説明する。

なお、図面は模式的または概念的なものであり、各部分の厚みと幅との関係、部分間の 大きさの比係数などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す 場合であっても、図面により互いの寸法や比係数が異なって表される場合もある。

また、本願明細書と各図において、既出の図に関して前述したものと同様の要素には同 一の符号を付して詳細な説明は適宜省略する。

10

20

30

40

#### [ 0 0 0 8 ]

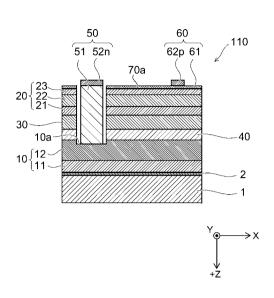

図1は、実施形態に係る半導体発光素子の構成を例示する模式的断面図である。

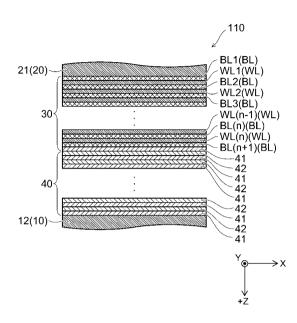

図2は、実施形態に係る半導体発光素子の一部の構成を例示する模式的断面図である。

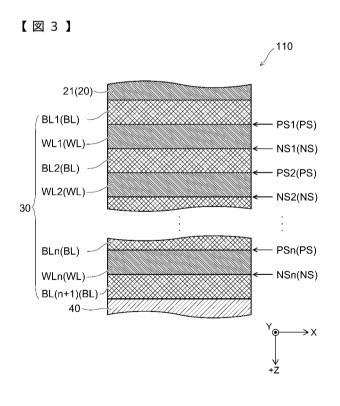

図3は、実施形態に係る半導体発光素子の一部を拡大した模式的断面図である。

### [0009]

図1に表したように、実施形態に係る半導体発光素子110は、n形の第1半導体層10と、p形の第2半導体層20と、第1半導体層10と第2半導体層20との間に設けられた発光層30と、を有する。第1半導体層10及び第2半導体層20は、例えば窒化物半導体を含む。

## [0010]

ここで、第2半導体層20から第1半導体層10に向かう方向を+Z方向(第1方向) とする。+Z方向に対して垂直な1つの方向をX軸方向とする。+Z方向に対して垂直で X軸方向に対して垂直な方向をY軸方向とする。

# [0011]

図2に表したように、発光層30は、+Z方向に沿って積層された複数の障壁層BLと、障壁層BLどうしの間に設けられた井戸層WLと、を含む。井戸層WLは、Inを含む。障壁層BL及び井戸層WLは、窒化物半導体を含む。例えば障壁層BLはGaNを含む。井戸層WLは、InGaNを含む。障壁層BLは、例えば実質的にInを含まない。または、障壁層BLがInを含む場合は、障壁層BLにおけるInの濃度は、井戸層WLにおけるInの濃度よりも低い。

#### [0012]

半導体発光素子110は、例えば窒化物半導体を用いたLEDである。

図1に表したように、例えばc面サファイアの基板1の上に、バッファ層2が設けられる。バッファ層2の上に、例えば下地層11が設けられる。下地層11の上に、n形コンタクト層12には、例えばGaNが用いられる。下地層11には、例えばアンドープのGaNが用いられる。n形コンタクト層12は、第1半導体層10に含まれる。便宜上、下地層11が第1半導体層10に含まれるものと見なしても良い。

## [0013]

本具体例では、n形コンタクト層12の上に、積層体40が設けられている。積層体40においては、例えば、複数の第1層41と、複数の第2層42と、が交互に積層されている。積層体40は、例えば超格子構造を有する。積層体40は必要に応じて設けられ省略しても良い。

## [0014]

積層体 4 0 の上には、発光層 3 0 (活性層)が設けられている。発光層 3 0 は、例えば 多重量子井戸(MQW: Multiple Quantum Well)構造を有する。

図 2 に表したように、発光層 3 0 は、複数の障壁層 B L 及び複数の井戸層 W L が、交互に積層された構造を有することができる。また、発光層 3 0 は、井戸層 W L が 1 つの S Q W (Single Quantum Well)構成を有していてもよい。

### [0015]

図1に表したように、発光層30の上には、第2半導体層20が設けられる。第2半導体層20は、例えば、第1p形層21、第2p形層22及び第3p形層23を含む。第1p形層21は、第3p形層23と発光層30との間に設けられる。第2p形層22は、第1p形層21と第3p形層23との間に設けられる。

#### [0016]

第1 p 形層 2 1 には、例えば p 形 A 1 G a N 層が用いられる。第2 p 形層 2 2 には、例えば、p 形 G a N 層 2 2 が用いられる。第3 p 形層 2 3 には、例えば p 形 G a N 層が用いられる。第3 p 形層 2 3 には、例えば M g ) の濃度は、第2 p 形層 2 2 における p 形 不 純物 濃度よりも高い。第1 p 形層 2 1 は、例えば電子オーバーフロー防止(抑制)層の機能を有する。第3 p 形層 2 3 は、コンタクト層の機能を有する。

10

20

30

40

# [0017]

第3 p 形層 2 3 の上に、第 2 コンタクト電極部 6 1 が設けられている。第 2 コンタクト電極部 6 1 は、例えば、発光層 3 0 から放出される光に対して透光性を有する透明電極である。第 2 コンタクト電極部 6 1 の上の一部には、 p 側パッド電極部 6 2 p が設けられる。 p 側パッド電極部 6 2 p には、例えば N i / A u の積層構造が用いられる。

## [0018]

n 形コンタクト層 1 2 の一部、ならびに、その一部に対応する積層体 4 0 、発光層 3 0 及び第 2 半導体層 2 0 が除去されている。これにより、n 形コンタクト層 1 2 の一部が露出する。第 1 コンタクト電極部 5 1 が、n 形コンタクト層 1 2 が露出した面 1 0 a 上に設けられている。

[0019]

第1コンタクト電極部51は、例えばTi/A1/Ta/Ti/Ptの積層構造を有する。第1コンタクト電極部51の上には、n側パッド電極52nが設けられる。n側パッド電極52nは、例えばNi/Auの積層構造を有する。n側パッド電極52nは、第1コンタクト電極部51上の一部または全面の上に設けられる。

[0020]

なお、第1コンタクト電極部51、n側パッド電極52n、第2コンタクト電極部61 及びp側パッド電極部62pに関する上記の構造及び材料は一例であり、実施形態はこれ に限定されない。

[0021]

積層体 4 0 の第 1 層 4 1 は、例えば I n  $_x$  G a  $_1$   $_x$  N ( 0 x < 1 ) を含む。第 2 層 4 2 は、例えば I I  $_y$  G a  $_1$   $_y$  N ( 0 < y 1 x < y ) を含む。

[0022]

障壁層 B L は、 $In_bGa_{1-b}N(0-b<1)$ を含む。井戸層W L は、 $In_wGa_{1-w}N(0< w<1$ 、b< w)を含む。なお、障壁層 B L 及び井戸層W L は、微量の A 1 等を含んでも良い。

[0023]

障壁層 B L の厚さは、例えば 5 ナノメートル(n m)以上 1 0 n m以下である。また、井戸層 W L の厚さは、例えば 2 n m以上 4 n m以下である。

例えば、発光のピーク波長が 4 5 0 n m である場合は、障壁層 B L には、例えば G a N が用いられ、井戸層 W L には、例えば I n <sub>0 1 5</sub> G a <sub>0 8 5</sub> N が用いられる。

[0024]

図3に表したように、発光層30において、障壁層BL及び井戸層WLが、例えば6~9周期で積層されている。例えば、障壁層BLの数は9であり、井戸層WLの数は8である。実施形態において、井戸層WLの数(及び障壁層BLの数)は、任意である。

[0025]

井戸層WLは、例えば第1井戸層WL1~第n井戸層WLmを含む。ここで、「m」は1以上の整数である。例えば、第(i+1)井戸層WL(i+1)は、第i井戸層WLiと第1半導体層10との間に配置されるものとする。ここで、「i」は1以上の整数である。

[0026]

複数の障壁層 B L は、例えば第1障壁層 B L 1 ~第(m + 1)障壁層 B L (m + 1)を含む。例えば第(i + 1)障壁層 B L (i + 1)は、第i障壁層 B L i と第1半導体層10との間に配置されるものとする。第i 井戸層W L i は、第i 障壁層 B L i と第(i + 1)障壁層 B L (i + 1)との間に配置されるものとする。

[0027]

図3に表したように、井戸層WLは、p側界面部分PSと、n側界面部分NSと、を有する。p側界面部分PSは、井戸層WLからみて第2半導体層20の側の障壁層BLとの界面を含む部分である。n側界面部分NSは、井戸層WLからみて第1半導体層10の側の障壁層BLとの界面を含む部分である。

10

20

30

40

#### [0028]

p側界面部分PSは、第1p側界面部分PS1~第mp側界面部分PSmを含む。第ip側界面部分PSiは、第i井戸層WLiの、第i井戸層WLiと第i障壁層BLiとの界面を含む部分である。

### [0029]

n側界面部分NSは、第1n側界面部分NS1~第mn側界面部分NSmを含む。第in側界面部分NSiは、第i井戸層WLiの、第i井戸層WLiと第(i+1)障壁層BL(i+1)との界面を含む部分である。

### [0030]

本実施形態においては、 p 側界面部分 P S の + Z 方向に対して垂直な面内における I n の濃度のばらつきは、 n 側界面部分 N S の + Z 方向に対して垂直な面内における I n の濃度のばらつき以下である。

#### [0031]

例えば、第ip側界面部分PSiの+ Z 方向に対して垂直な面内におけるInの濃度のばらつきは、第in側界面部分NSiの+ Z 方向に対して垂直な面内におけるInの濃度のばらつき以下である。

これにより、動作電圧が低減する。

## [0032]

例えば、p側界面部分PSの+Z方向に対して垂直な面内におけるInの濃度のばらつきは、p側界面部分PSにおける+Z方向に対して垂直な面内における等In濃度面の3次元凹凸の二乗平均平方根(RMS:Root Mean Saquare)で表される。n側界面部分NSの+Z方向に対して垂直な面内におけるInの濃度のばらつきは、n側界面部分NSにおける+Z方向に対して垂直な面内における等In濃度面の3次元凹凸の二乗平均平方根(RMS)で表される。

### [ 0 0 3 3 ]

すなわち、実施形態においては、例えば、第ip側界面部分PSiの+Z方向に対して垂直な面内における等In濃度面の3次元凹凸のRMSは、第in側界面部分NSiの+Z方向に対して垂直な面内における等In濃度面の3次元凹凸のRMS以下である。

# [0034]

本実施形態に係るこのような構成は、発明者が行った実験により見出された新たな知見に基づいている。以下、この実験について説明する。

# [0035]

c 面サファイヤの基板 1 を M O C V D (Metal Organic Chemical Vapor Deposition) 装置の反応炉に導入する。反応炉のサセプタ上で、基板 1 を 1 1 0 0 に加熱する。これ により、基板 1 の表面の酸化膜を除去した。

# [0036]

基板 1 の上に、厚さ 3 0 n m のバッファ層 2 を形成した。バッファ層 2 の上に、下地層 1 1 として、厚さ 3 マイクロメートル(μm)のアンドープの G a N 層を形成した。さらに、下地層 1 1 の上に、 n 形コンタクト層 1 2 として、厚さ 2 μ m の S i ドープ G a N 層を形成した。

# [0037]

n 形コンタクト層12の上に積層体40を形成した。積層体40の上に、障壁層BLと井戸層WLとを積層したMQW構造の発光層30を形成した。障壁層BLはGaN層である。井戸層WLは、In組成比が15%のIn<sub>0.15</sub>Ga<sub>0.85</sub>N層である。この実験では、障壁層BLと井戸層WLとを交互に8周期積層し、最上の井戸層WL(第1井戸層WL1)の上に最終の障壁層BL(第1障壁層BL1)を形成した。障壁層BLの厚さは5nmである。井戸層WLの厚さは2.5nmである。

#### [0038]

発光層 3 0 の上に、第 1 p 形層 2 1 として、 2 層の A 1 G a N 層を形成した。すなわち、発光層 3 0 の上に、厚さが 5 n m で A 1 組成比が 0 . 3 % の、 1 層目の A 1 G a N 層を

10

20

30

40

10

20

30

40

50

形成した。この上に、厚さが5 n m で A 1 組成比が1 0 % の 2 層目の A 1 G a N 層を形成した。 2 層目の A 1 G a N 層は、5 × 1 0 1 9 / c m 3 で M g を含む。第 1 p 形層 2 1 の上に、第 2 p 形層 2 2 として、厚さが 8 0 n m の p 形 G a N 層を形成した。第 2 p 形層 2 2 における M g の 濃度は 2 × 1 0 1 9 / c m 3 である。第 2 p 形層 2 2 の上に、第 3 p 形層 2 3 として、厚さが 1 0 n m 程度の p 形 G a N 層を形成した。第 3 p 形層 2 3 における M g の 濃度は 1 × 1 0 2 1 / c m 3 である。その後、基板 1 を M O C V D 装置の反応炉から 取り出した。

## [0039]

上記の試料の一部をドライエッチングして、 n 形コンタクト層 1 2 の一部を露出させた。露出した n 形コンタクト層 1 2 の上に、 T i / P t / A u の多層構造の第 1 コンタクト電極部 5 1 を形成した。また、第 2 半導体層 2 0 (第 3 p 形層 2 3)の上に、第 2 コンタクト電極部 6 1 として、透明電極(I T O: Indium Tin Oxide)を形成した。さらに、その一部に、直径 8 0 μ m の N i / A u の積層構造による p 側パッド電極部 6 2 p を形成した。

[0040]

これにより、半導体発光素子が得られる。

実験では、半導体層の形成条件を変えることで、複数の試料(後述する試料S1~S5)を作製した。このようにして得られた試料の発光特性を評価した。その結果、動作電圧が高い試料と低い試料があった。発明者は、このような特性の違いと、半導体発光素子の発光層の状態と、の関係について各種の解析を行った。そして、井戸層WLの面内におけるInの濃度のばらつきの特性が、動作特性に関係していることを見出した。

[0041]

以下では、発光層 3 0 の面内の I n の濃度の変動の評価に関して説明する。発明者は、試料の発光層 3 0 の面内の I n の濃度分布を、 3 次元アトムプローブ(3 D A P ) 法で測定し、 3 次元元素マップを得た。

[0042]

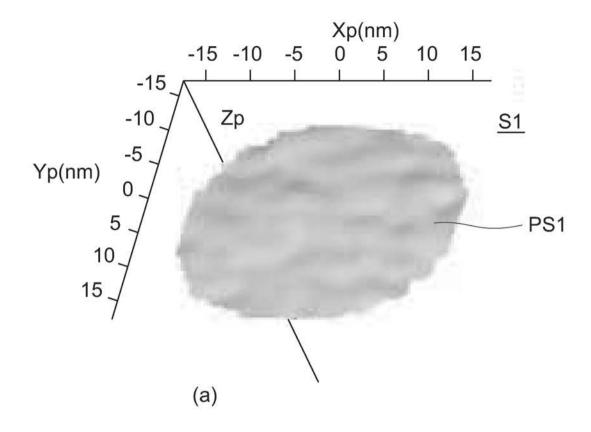

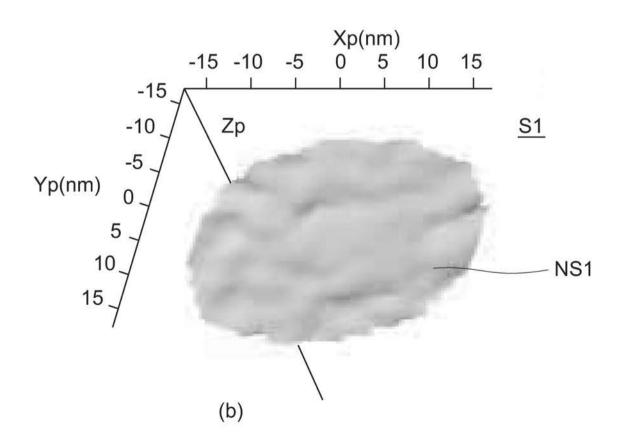

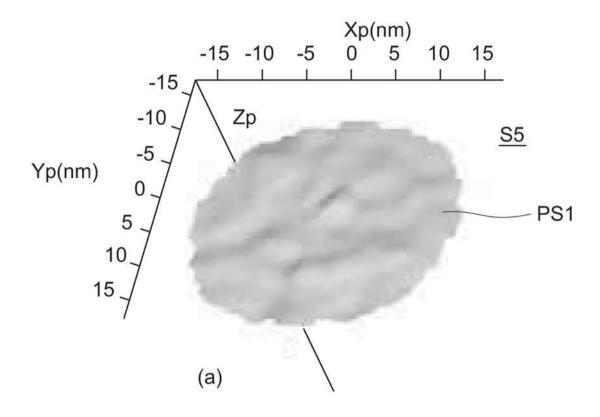

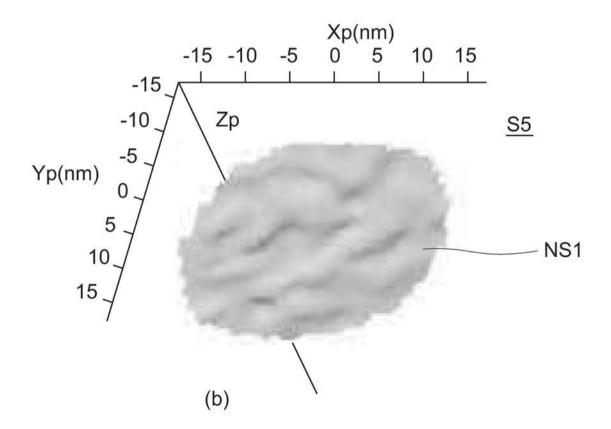

図4(a)、図4(b)、図5(a)及び図5(b)は、半導体発光素子の特性を例示する模式図である。

すなわち、これらの図は、井戸層WLのInの等濃度面の3次元元素マップを例示する図である。

[0043]

この3次元元素マップは、井戸層WLの所定の測定範囲におけるInの濃度の3DAP方による測定値に基づき描かれている。測定範囲は、+Z方向に対して垂直な面(X-Y平面)における直径が30nmの範囲である。この測定範囲におけるInの濃度に基づいて等In濃度面が描かれている。この例では、等In濃度面は、Inの濃度が4.0原子パーセント(atomic%)である面である。

[0044]

図4(a)及び図5(a)は、井戸層WLのp側界面部分PS(この例は第1p側界面部分PS1)におけるInの等濃度面に対応する。図4(b)及び図5(b)は、井戸層WLのn側界面部分NS(この例は第1n側界面部分NS1)におけるInの等濃度面に対応する。

[0045]

これらの図において、XpはX軸方向に沿った位置である。Ypは、Y軸方向に沿った位置である。Zpは、+Z方向に沿った位置である。

[0046]

図4(a)及び図4(b)は、試料S1に関するものである。図5(a)及び図5(b)は、試料S5に関するものである。試料S1と試料S5とでは、半導体層の形成条件が異なっている。試料S1の駆動電圧は、試料S5の駆動電圧よりも低い。

[0047]

図4(a)に表したように、試料S1においては、第1p側界面部分PS1のIn等濃

10

20

30

40

50

度面は、比較的平坦である。図4(b)に表したように、第1n側界面部分NS1におけるInの濃度面には凹凸がある。このように、試料S1においては、第1p側界面部分PS1におけるInの濃度の面内ばらつきは、第1n側界面部分NS1におけるInの濃度の面内ばらつきよりも小さい。第1p側界面部分PS1における等In濃度面のRMSは、0.24nmであった。第1n側界面部分NS1における等In濃度面のRMSは、0.25nmであった。

#### [0048]

図5(b)及び図5(b)に表したように、試料S5においては、第1p側界面部分PS1及び第1n側界面部分NS1のIn等濃度面には、大きな凹凸がある。試料S5においては、第1p側界面部分PS1における等In濃度面のRMSは、0.26nmであった。第1n側界面部分NS1における等In濃度面のRMSは、0.23nmであった。このように、試料S5においては、第1p側界面部分PS1におけるInの濃度の面内ばらつきよりも大きい。

# [0049]

発明者は、このように、動作電圧が低い試料S1と、動作電圧が高い試料S5と、において、井戸層WLのInの濃度の面内ばらつきに差異があることに着目した。そして、p側界面部分PSの面内のInの濃度のばらつきが、n側界面部分NSの面内のInの濃度のばらつき以下のときに、動作電圧が低減できることを見出した。この特性は、発明者が行った独自の実験により初めて見出されたものである。

# [0050]

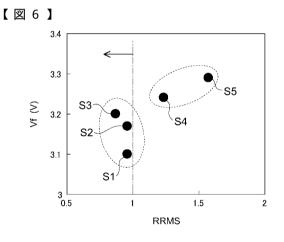

図6は、半導体発光素子の特性を例示するグラフ図である。

同図は、実験で作製した各種の半導体発光素子の試料(試料S1~試料S5)の特性を示している。図6の横軸は、第1井戸層WLの第1p側界面部分PS1における等In濃度面のRMS(RMSP1)と、第1n側界面部分NS1における等In濃度面のRMS(RMSN1)との比RRMSである。RRMSは、RMSP1/RMSN1である。RRMSが1以下であることは、第1p側界面部分PN1のInの濃度のばらつきが第1n側界面部分NS1のInの濃度のばらつき以下であることに対応する。図6の縦軸は、動作電圧Vfである。

## [0051]

図 6 に表したように、RRMSが小さいと、動作電圧Vfが低くなる。特に、RRMSが1以下の場合に動作電圧Vfは小さい。

この特性に基づいて、本実施形態に係る半導体発光素子 1 1 0 では、RRMSが 1 以下に設定される。

# [ 0 0 5 2 ]

このように、本実施形態に係る半導体発光素子110においては、 p 側界面部分 P S における面内の等 I n 濃度面の 3 次元凹凸の R M S が、 n 側界面部分 N S における面内の等 I n 濃度面の 3 次元凹凸の R M S 以下に設定される。これにより、動作電圧 V f が低減できる。

# [0053]

例えば、p側界面部分PSのRMSが、n側界面部分NSのRMS以下であると、第2半導体層20から発光層30に注入されるホールの散乱を抑制することができると考えられる。

## [0054]

ホールは、第2半導体層20から発光層30に注入される。すなわち、p側界面部分PSから井戸層WLにホールが注入される。p側界面部分PSのRMSがn側界面部分NSのRMS以下であると、注入されるホールがp側界面部分PSで散乱しにくくなり、井戸層WLにホールが効率良く注入されると考えられる。

#### [0055]

なお、障壁層 B L 及び井戸層 W L は交互に積層されている。複数の井戸層 W L のうちで発光に寄与する程度が大きいのは、第 2 半導体層 2 0 に最も近い井戸層 W L であると考え

10

20

30

40

50

られる。したがって、最も第2半導体層20に近い井戸層WL(第1井戸層WL1)において、第1p側界面部分PS1のRMSを第1n側界面部分NS1のRMS以下にすることが特に望ましい。これにより、第2半導体層20から発光層30へのホールの注入効率の向上の程度が高まる。これにより、動作電圧Vfの低減の効果がより効果的に発揮される。

# [0056]

本実施形態においては、井戸層WLのp側界面部分PSにおける面内のInの濃度ばらつき(例えば等In濃度面のRMS)をn側界面部分NSにおける面内のInの濃度ばらつき(例えば等In濃度面のRMS)以下にしているが、この構成は、発明者の実験によって初めて見出された構成である。例えば、今までに、井戸層WLのp側界面部分PSの等In濃度面のRMSを測定した例が報告されている。しかし、今までの報告では、p側界面部分PSの等In濃度面のRMSは、n側界面部分NSの等In濃度面のRMSは、n側界面部分NSの等In濃度面のRMSよりも大きい。例えば、p側界面部分PSの等In濃度面のRMSよりも大きい。例えば、p側界面部分PSの等In濃度面のRMSが0.34nmであり、n側界面部分NSの等In濃度面のRMSが0.18nmである。このように、本実施形態は、従来に知られていない特異な構成により、良好な動作特性を得ている。

### [0057]

さらに、半導体発光素子に用いる基板やp側コンタクト層の表面の物理的な構造の凹凸(例えば表面粗さ)に関するRMSを工夫する技術がある。これに対し、本実施形態においては、物理的な構造の凹凸に着目するのではなく、井戸層WLに含まれるInの濃度の面内のばらつきに着目している。そして、井戸層WLにおけるInの濃度の面内のばらつきに関する指標として、例えば等In濃度面のRMSを採用している。これにより、第2半導体層20から発光層30へのホールの注入効率を向上する。

#### [0058]

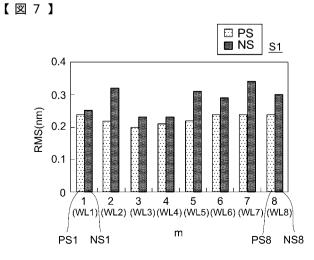

図7は、半導体発光素子の特性を例示するグラフ図である。

同図は、試料S1の特性を示している。横軸は、第2半導体層20の側から数えた井戸層WLの順番の数「m」である。縦軸は、井戸層WLのそれぞれのp側界面部分PSのRMS及びn側界面部分NSのRMSを示す。

# [0059]

図7に表したように、試料S1(すなわち、実施形態に係る半導体発光素子110)においては、複数の井戸層WLのうちで最も第2半導体層20に近い井戸層WL(第1井戸層WL)において、p側界面部分PS(第1p側界面部分PS1)のRMS(+ Z方向に対して垂直な面内におけるInの濃度のばらつき)は、n側界面部分NS(第1n側界面部分NS1)のRMS(+ Z方向に対して垂直な面内におけるInの濃度ばらつき)以下である。具体的には、既に説明したように、第1p側界面部分PS1のRMSは0.24nmであり、第1n側界面部分NS1のRMSは0.25nmである。

# [0060]

さらに、試料S1(半導体発光素子110)においては、第1井戸層WL1~第8井戸層WL8の全ての井戸層WLにおいて、p側界面部分PSのRMSは、n側界面部分NSのRMS以下である。

# [0061]

すなわち、複数の井戸層WLのそれぞれにおいて、 p 側界面部分 P S の R M S ( + Z 方向に対して垂直な面内における I n の濃度のばらつき)は、 n 側界面部分 N S の R M S ( + Z 方向に対して垂直な面内における I n の濃度ばらつき)以下である。すなわち、第 i p 側界面部分 P S i の R M S は、第 i n 側界面部分 N S i の R M S 以下である。本具体例では、第 i p 側界面部分 P S i の R M S は、第 i n 側界面部分 N S i の R M S よりも小さい。

## [0062]

さらに、第 1 p 側界面部分 P S 1 の R M S は、 0 . 2 5 n m である。 このように、複数の井戸層 W L のうちで最も第 2 半導体層 2 0 に近い井戸層 W L (第 1 井戸層WL)において、 p 側界面部分 P S (第 1 p 側界面部分 P S 1 )の R M S ( + Z 方向に対して垂直な面内における I n の濃度のばらつき)は、 0 . 2 5 n m 以下であることが望ましい。

### [0063]

また、複数の井戸層WLのそれぞれにおいて、p側界面部分PSのRMSは、0.25nm以下である。このように、複数の井戸層WLのそれぞれにおいて、p側界面部分PSのRMS(+ Z方向に対して垂直な面内におけるInの濃度のばらつき)は、0.25nm以下であることがさらに望ましい。

# [0064]

これにより、発光層30の内部における量子効率がさらに向上できる。これによりウォールプラグ効率が向上できる。そして動作電圧Vfがより低減できる。

#### [0065]

なお、n側界面部分NSのRMSは、小さいほうが望ましいが、p側界面部分PSのRMSよりも大きいことを許容する。

### [0066]

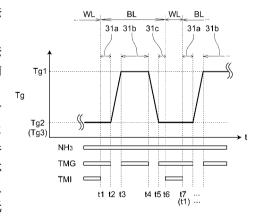

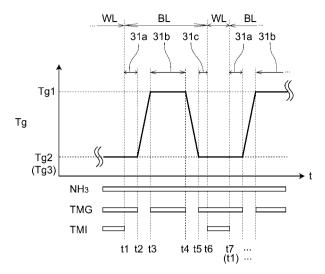

図8は、実施形態に係る半導体発光素子の製造方法を例示する模式図である。

すなわち、図 8 は、M O C V D によって発光層 3 0 を形成する際の温度プロファイル及び反応ガスの導入タイミングを例示している。同図において、横軸は時間 t を示す。縦軸は、温度 T g を示している。また、横軸に合わせて各反応ガスの導入の状態を示している。この例では、反応ガスとして、N H  $_3$ 、 T M G (Trimethylgallium)及び T M I (Trimethylindium)を用いられている。

#### [0067]

図8に表したように、この例では、障壁層BLは、第1温度Tg1で形成される高温形成層31bと、第1温度Tg1よりも低い第2温度Tg2で形成される低温形成層(n側低温形成31a及びp側低温形成層31cの少なくともいずれか)と、を有している。低温形成層は、高温形成層31bと井戸層WLとの間に、設けられる。

#### [0068]

井戸層WLは、第1温度Tg1よりも低い第3温度Tg3で形成される。第3温度Tg3は、第2温度Tg2と同じでも良い。以下では、第3温度Tg3が第2温度Tg2と同じ場合である例について説明する。

### [0069]

温度Tgを第2温度Tg2(この例では第3温度Tg3と同じ)に設定し、NH<sub>3</sub>、TMG及びTMIを反応炉に導入する。これにより、井戸層WLが形成される。所定の厚さで井戸層WLを形成した後、タイミングt1においてTMIの導入を停止する。

# [0070]

タイミング t 1 からタイミング t 2 の間、温度 T g を第 2 温度 T g 2 に維持した状態で、反応炉内に N H 3 及び T M G を導入する。これにより、井戸層 W L の上に、障壁層 B L の一部となる n 側低温形成層 3 1 a が形成される。 n 側低温形成層 3 1 a の厚さは、例えば 1 n m 以上、 2 n m 以下である。 T M G の導入を停止し、 n 側低温形成層 3 1 a の形成を終了する。

# [0071]

タイミング t 2 からタイミング t 3 の間、温度 T g を第 2 温度 T g 2 から第 1 温度 T g 1 へ上昇させる。例えば、 n 側低温形成層 3 1 a により、この昇温過程における井戸層 W L からの I n の消失が抑制される。

#### [0072]

温度Tgが第1温度Tg1に達したタイミングt3においてTMGの導入を再開する。タイミングt3からタイミングt4の間、第1温度Tg1で反応炉内にNH<sub>3</sub>及びTMGを導入する。これにより、障壁層BLの他の一部となる高温形成層31bが形成される。所定の厚さで高温形成層31bを形成した後、タイミングt4においてTMGの導入を停止する。タイミングt4からタイミングt5の間、温度Tgを第1温度Tg1から第2温

10

20

30

40

度Tg2へ下降させる。

### [0073]

温度Tgが第2温度Tg2に下降したタイミングt5において、TMGの導入を再開する。これにより、2つ目の低温形成層であるp側低温形成層31cが形成される。

# [0074]

そして、 p 側低温形成層 3 1 c が所定の厚さになるタイミング t 6 においてTMIの導入を再開する。タイミング t 6 からタイミング t 7 までの間、第 2 温度Tg 2 で、反応炉内にNH<sub>3</sub>、TMG及びTMIを導入する。これにより、井戸層WLが形成される。

### [0075]

タイミングt7以降は、タイミングt1以降の処理を繰り返す。

なお、例えば、p側低温形成層31cは場合によっては省略しても良い。

このような処理を繰り返すことによって、井戸層WL及び障壁層BLが交互に積層される。

# [0076]

ここで、第2温度Tg2は830 以上が好ましい。また、第1温度Tg1と第2温度Tg2との差は、40 以上、100 未満が好ましく、40 以上、60 未満がより好ましい。これにより、p側界面部分PS及びn側界面部分NSにおけるInの濃度の面内ばらつき、すなわち、p側界面部分PS及びn側界面部分NSにおける等In濃度面のRMSを低減し易くできる。

# [0077]

第1温度 T g 1、第2温度 T g 2 及び第2温度 T g 3、並びに、反応ガスの導入タイミングなどの半導体層の形成条件を適正化することで、 p 側界面部分 P S における面内の I n の濃度のばらつきを n 側界面部分 N S における面内の I n の濃度のばらつき以下にできる。

# [0078]

なお、本実施形態においては、超格子構造を有する積層体 4 0 の上にM Q W 構造の発光層 3 0 を形成する場合、積層体 4 0 の成膜条件が適正化される。これにより、井戸層 W L のうちで第 1 半導体層 1 0 に最も近い井戸層 W L における n 側界面部分 N S の I n の濃度の面内ばらつきを抑制している。

# [0079]

例えば、第8n側界面部分NS8のRMSは0.4nm以下にすることが望ましい。また、第1n側界面部分NS1における面内のInの濃度のばらつきを第8n側界面部分NS8における面内のInのばらつきよりも小さくすることが望ましい。

# [ 0 0 8 0 ]

これにより、第1p側界面部分PS1及び第1n側界面部分NS1における面内In濃度のばらつきを抑制しつつ、第1p側界面部分PS1の面内のInの濃度のばらつき以下にできる。

### [0081]

本実施形態において、半導体層の形成には、例えば、有機金属気相(MOCVD)法、分子線エピタキシー(MBE: Molecular Beam Epitaxy)法、ハライド気相成長(HVPE: Hydride vapor phase epitaxy)法などを用いることができる。

#### [0082]

以上説明したように、実施形態に係る半導体発光素子によれば、動作電圧を低減した半導体発光素子が提供できる。

### [0083]

なお、本明細書において「窒化物半導体」とは、 B  $_{\times}$  I n  $_{y}$  A l  $_{z}$  G a  $_{1-x-y-z}$  N ( 0  $_{x}$  1 , 0  $_{y}$  1 , 0  $_{z}$  1 , x + y + z 1 ) なる化学式において組成比 x 、 y 及び z をそれぞれの範囲内で変化させた全ての組成の半導体を含むものとする。またさらに、上記化学式において、 N (窒素)以外の V 族元素もさらに含むもの、 導電型などの各種の物性を制御するために添加される各種の元素をさらに含むもの、 及び、 意図せ

10

20

30

40

ずに含まれる各種の元素をさらに含むものも、「窒化物半導体」に含まれるものとする。 【 0 0 8 4 】

以上、具体例を参照しつつ、本発明の実施の形態について説明した。しかし、本発明の実施形態は、これらの具体例に限定されるものではない。例えば、半導体発光素子に含まれる第1半導体層、第2半導体層、発光層、井戸層、障壁層、高温形成層、低温形成層、積層体及び電極などの各要素の具体的な構成に関しては、当業者が公知の範囲から適宜選択することにより本発明を同様に実施し、同様の効果を得ることができる限り、本発明の範囲に包含される。

[0085]

また、各具体例のいずれか 2 つ以上の要素を技術的に可能な範囲で組み合わせたものも、本発明の要旨を包含する限り本発明の範囲に含まれる。

[0086]

その他、本発明の実施の形態として上述した半導体発光素子を基にして、当業者が適宜 設計変更して実施し得る全ての半導体発光素子も、本発明の要旨を包含する限り、本発明 の範囲に属する。

[0087]

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

[0088]

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる

# 【符号の説明】

[0089]

1 … 基板、 2 … バッファ層、 1 0 … 第 1 半導体層、 1 1 … 下地層、 1 2 … n 形コンタクト層、 2 0 … 第 2 半導体層、 2 1 … 第 1 p 形層、 2 2 … 第 2 p 形層、 2 3 … 第 3 p 形層、 3 0 … 発光層、 3 1 a … n 側低温形成層(低温形成層)、 3 1 b … 高温形成層、 3 1 c … p 側低温形成層(低温形成層)、 3 2 … 井戸層、 4 0 … 積層体、 4 1 … 第 1 層、 4 2 … 第 2 層、 5 1 … 第 1 コンタクト電極部、 5 2 n … n 側パッド電極、 6 1 … 第 2 コンタクト電極部、 6 2 p … p 側パッド電極部、 1 1 0 … 半導体発光素子、 B L … 障壁層、 B L 1 ~ B L i … 第 1 ~ 第 i 障壁層、 N S … n 側界面部分、 N S 1 ~ N S 8 … n 側界面部分、 P o … 光出力、 P S … p 側界面、 P S 1 ~ P S 8 … p 側界面部分、 R R M S … 比、 S 1 ~ S 5 … 試料、 T g 1 ~ T g 3 … 第 1 ~ 第 3 温度、 V f …動作電圧、 W L … 井戸層、 W L 1 ~ W L i … 第 1 ~ 第 i 井戸層、 t 1 ~ t 7 … タイミング

10

30

【図1】 【図2】

# 【図8】

# フロントページの続き

(72)発明者 布上 真也 東京都港区芝浦一丁目 1 番 1 号 株式会社東芝内 F ターム(参考) 5F041 AA21 CA05 CA40 CA46 CA65