# (19) World Intellectual Property Organization

International Bureau

### (43) International Publication Date 3 November 2011 (03.11.2011)

### (10) International Publication Number WO 2011/136837 A1

(51) International Patent Classification: H01L 33/00 (2010.01) H01L 33/50 (2010.01)

(21) International Application Number:

PCT/US2011/000381

(22) International Filing Date:

28 February 2011 (28.02.2011)

(25) Filing Language:

**English**

(26) Publication Language:

English

(30) Priority Data:

12/771,938

30 April 2010 (30.04.2010)

US

- (71) Applicant (for all designated States except US): CREE, INC. [US/US]; 4600 Silcon Drive, Durham, NC 27703 (US).

- (72) Inventors; and

- Inventors/Applicants (for US only): YAO, Zhimin Jamie [US/US]; 98 Manchester Place, Goleta, CA 93117 (US). IBBETSON, James [GB/US]; 910 Randolph Road, Santa Barbara, CA 93111 (US).

- Agents: HEYBL, Jaye, G. et al.; KOPPEL, PATRICK, HEYBL & DAWSON, 2815 Townsgate Road, Suite 215, Westlake Village, CA 91361-5827 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- **Designated States** (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

with international search report (Art. 21(3))

(54) Title: WHITE-EMITTING LED CHIPS AND METHOD FOR MAKING SAME

(57) Abstract: Methods and devices for light emitting diode (LED) chips are provided. In one embodiment of a method, a preformed capping wafer is provided, with the capping wafer comprising a conversion material. A wire-bond free LED wafer is fabricated comprising a plurality of LEDs. The capping wafer is bonded to the LED wafer using an adhesive. The LED chips are later singulated upon completion of all final fabrication steps. The capping wafer provides a robust mechanical support for the LED chips during fabrication, which improves the strength of the chips during fabrication. Additionally, the capping wafer may comprise an integrated conversion material, which simplifies the fabrication process. In one possible embodiment for an LED chip wafer, a submount wafer is provided, along with a plurality of LEDs flip-chip mounted on the submount wafer. Additionally, a capping wafer is bonded to the LEDs using an adhesive, and the capping wafer comprises a conversion material. At least some of the light emitted from the LEDs passes through the capping wafer where at least some of the light is converted by the conversion material.

WO 2011/136837 PCT/US2011/000381

# WHITE-EMITTING LED CHIPS AND METHOD FOR MAKING SAME

[0001] The invention was made with Government support under Contract No. FA8650-05-2-5507. The Government has certain rights in this invention.

### BACKGROUND OF THE INVENTION

# Field of the Invention

[0002] The present invention relates generally to semiconductor devices, and more particularly to wire-bond free, white light emitting devices and methods for fabricating the same.

#### Description of the Related Art

[0003] Light emitting diodes (LED or LEDs) are solid state devices that convert electric energy to light, and generally comprise one or more active layers of semiconductor material sandwiched between oppositely doped layers. When a bias is applied across the doped layers, holes and electrons are injected into the active layer where they recombine to generate light. Light is emitted from the active layer and from all surfaces of the LED.

[0004] Conventional LEDs cannot generate white light from their active layers. Light from a blue emitting LED has been

converted to white light by surrounding the LED with a yellow phosphor, polymer or dye, with a typical phosphor being cerium-doped yttrium aluminum garnet (Ce:YAG). [See Nichia Corp. white LED, Part No. NSPW300BS, NSPW312BS, etc.; See also U.S. Patent No. 5,959,316 to Lowrey, "Multiple Encapsulation of Phosphor-LED Devices"]. The surrounding phosphor material down-converts the wavelength of some of the LED's blue light, changing its color to yellow. Some of the blue light passes through the phosphor without being changed while a substantial portion of the light is down-converted to yellow. The LED emits both blue and yellow light, which combine to provide a white light. In another approach light from a violet or ultraviolet emitting LED has been converted to white light by surrounding the LED with multicolor phosphors or dyes.

[0005] One method used to fabricate efficient semiconductor devices is called flip-chip, or wire-bond free, mounting. Flipchip mounting of LEDs involves mounting the LED onto a submount substrate-side up. Light is then extracted and emitted through the transparent substrate, or the substrate may be removed Flip-chip mounting is an especially desirable altogether. technique for mounting SiC-based LEDs. Since SiC has a higher index of refraction than GaN, light generated in the active region does not internally reflect (i.e. reflect back into the GaN-based layers) at the GaN/SiC interface. Flip-chip mounting extraction offers improved light SiC-based LEDs employing certain chip-shaping techniques known in the art. Flip-chip packaging of SiC LEDs has other benefits as well, such as improved heat extraction/dissipation, which may be desirable depending on the particular application for the chip.

[0006] Various approaches for the fabrication of white-emitting, flip-chip mounted devices have been attempted. For example, Philips Lumileds has developed a thin film flip-chip technology which they combine with their "Lumiramic" phosphor plates to create white-emitting, wire-bond free LEDs. To manufacture these devices, multiple fabrication steps are carried out at the singulated chip level. Base LEDs are individually flip-chip mounted to submount wafers prior to removing the LED substrate. The Lumiramic plates are then bonded to each chip individually.

[0007] As another example, in U.S. Patent Pub. No. 2008/0173884 (assigned to the same assignee as the present invention), the wire-bond free wafer is coated with phosphor-loaded silicone and then cured after it is fabricated. The coated wafers can then be further processed by grinding down the phosphor coating to a uniform thickness. Finally, the wafers are diced, and the singulated chips are placed for die attachment.

[0008] While flip-chip, or wire-bond free, LED chip designs are suitable for a variety of applications, white-emitting flip-chip devices can be difficult to fabricate. To maximize the overall light extraction while limiting the light emission from the sidewalls of the devices, the LED wafer substrate may be thinned or entirely removed. As such, the mechanical support for the remaining material is essentially provided by: the electrodes, and the package or submount the devices are flip-chip mounted onto. This can result in devices that are mechanically delicate and subject to low-yield during fabrication and die handling. Reliability problems after packaging can also be an issue.

[0009] Additionally, the base LED materials (such as SiC, GaN, and various contact metals) may have relatively low coefficients of thermal expansion (CTE), such as in the <20ppm/°C range.

Alternatively, some of the materials provided to make the chips emit white light (such as silicone coating) have high CTE, such as in the >100ppm/°C range. The low CTE and high CTE materials are typically attached to one another to form a completed device, thus creating a CTE mismatch. The CTE mismatch may exacerbate the mechanically delicate nature of the white-emitting, flip-chip devices. This may lead to device failure during temperature cycles.

### SUMMARY OF THE INVENTION

[0010] The present invention provides apparatuses and methods for fabricating semiconductor devices, such as white-emitting, flip-chip lighting devices, that are highly efficient The fabrication of the devices allows for mechanically robust. higher yields and lower costs by performing process steps at the embodiment wafer level rather than the chip level. One according to the present invention comprises a method for fabricating LED chips. The method comprises pre-forming a capping wafer, with the capping wafer comprising a conversion material. A wire-bond free LED wafer comprising a plurality of LEDs is fabricated. The capping wafer is then bonded to the LED wafer using an adhesive. Finally, the LED chips are singulated upon the completion of all final fabrication steps.

[0011] Pursuant to another embodiment according to the present invention, an LED chip wafer is provided comprising a submount wafer and a plurality of LEDs flip-chip mounted on the submount wafer. A capping wafer is also provided, which is bonded to the LEDs using an adhesive. The capping wafer comprises a conversion material. At least some of the light emitted from

the LEDs passes through the capping wafer where at least some of the light is converted by the conversion material.

[0012] In another embodiment according to the present invention, a wire-bond free LED chip is provided. Further, a capping wafer is provided, which is bonded to the LED using an adhesive. The capping wafer serves as a mechanical support for the LED chip. A conversion material is integrated in the capping wafer, with the conversion material converting at least some of the light emitted from said LED.

[0013] These and other further features and advantages of the invention would be apparent to those skilled in the art from the following detailed description, taken together with the accompanying drawings, in which:

#### BRIEF DESCRIPTION OF THE DRAWINGS

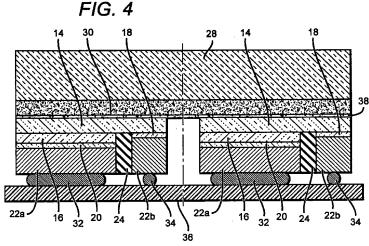

[0001] FIG. 1 is a sectional view of one embodiment of an LED wafer at a fabrication step in one method according to the present invention;

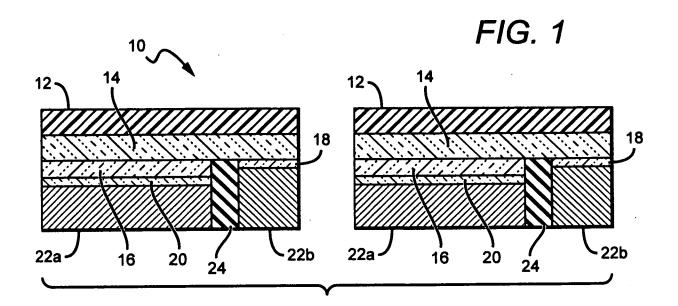

[0002] FIG. 2 is a sectional view of one embodiment of a capping wafer according to the present invention;

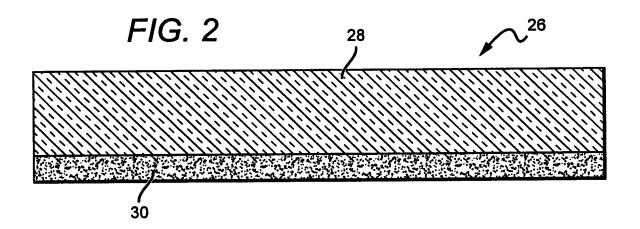

[0003] FIG. 3 is a sectional view of the capping wafer of FIG. 2 bonded to the LED wafer of FIG. 1;

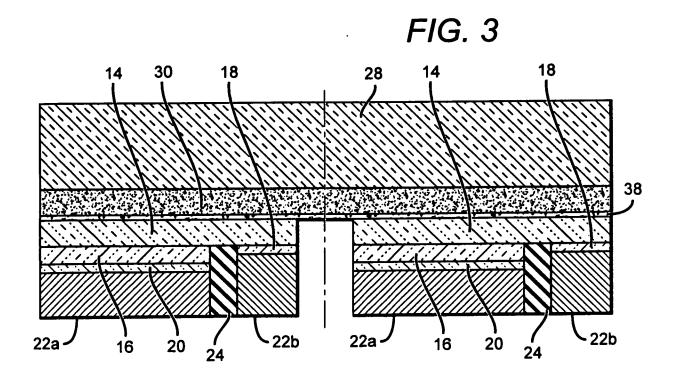

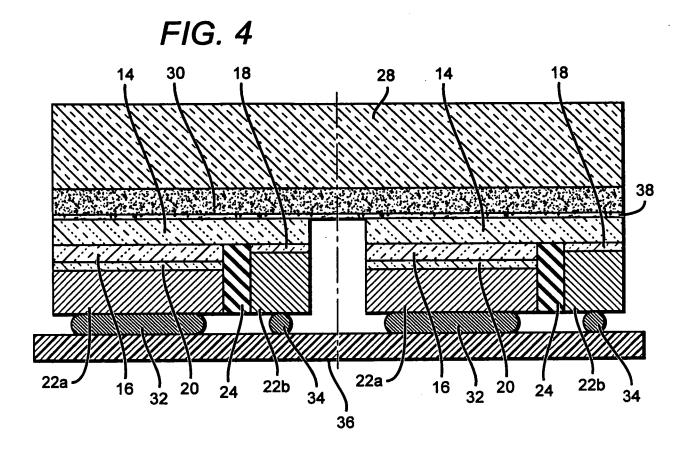

[0004] FIG. 4 is a sectional view of a submount wafer and LED wafer in FIG. 3 following flip-chip mounting;

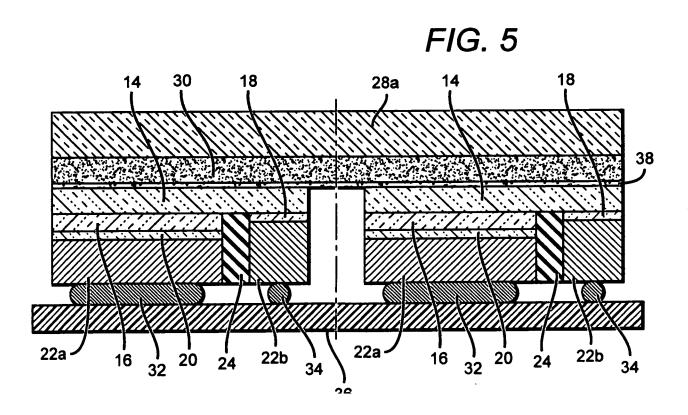

- [0005] FIG. 5 is a sectional view of the capping wafer, submount wafer, and LED wafer in FIG. 4 following grinding/polishing of the capping wafer;

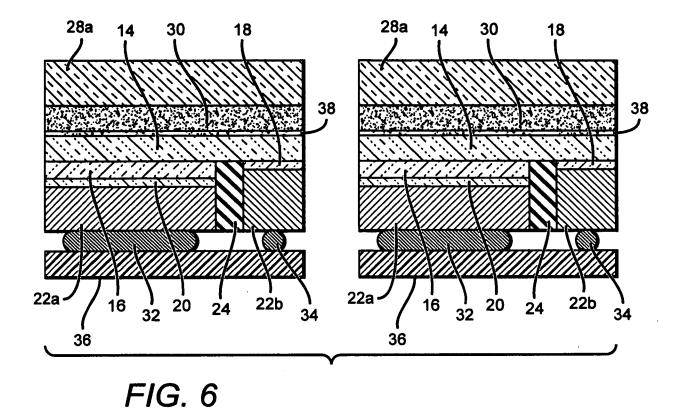

- [0006] FIG. 6 is a sectional view of the capping wafer, submount wafer and LED wafer in FIG. 5 following singulation;

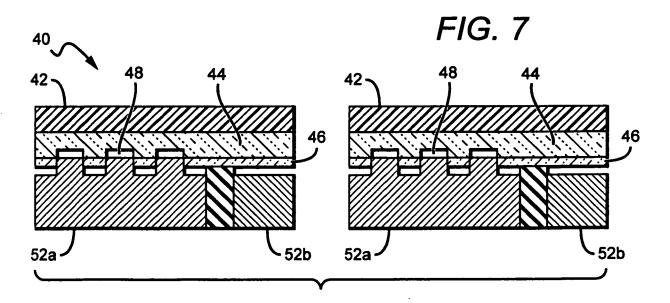

- [0007] FIG. 7 is a sectional view of another embodiment of an LED wafer at a fabrication step in one method according to the present invention;

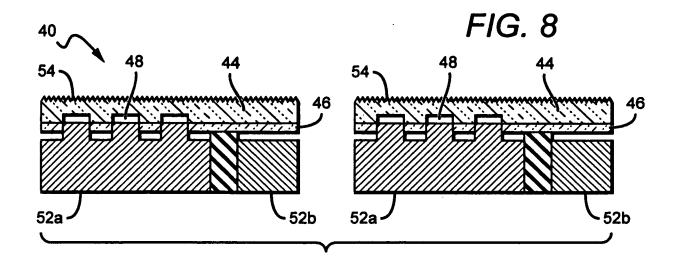

- [0008] FIG. 8 is a sectional view of the LED wafer of FIG. 7 after substrate removal and GaN surface etch;

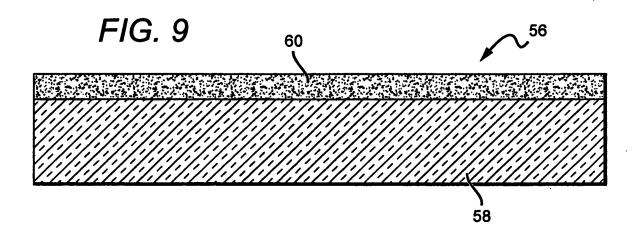

- [0009] FIG. 9 is a sectional view of one embodiment of a capping wafer according to the present invention;

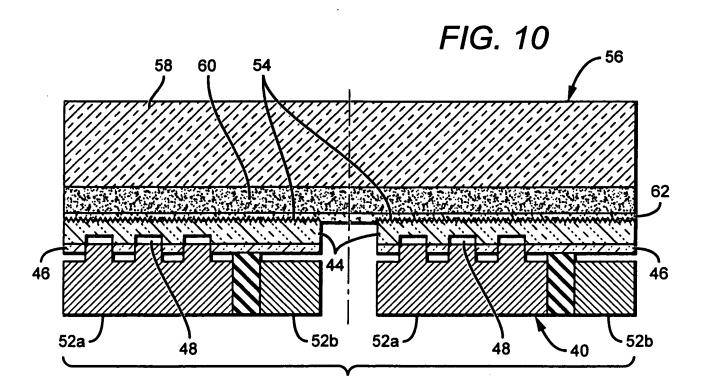

- [0010] FIG. 10 is a sectional view of the capping wafer of FIG. 9 bonded to the LED wafer of FIG. 8;

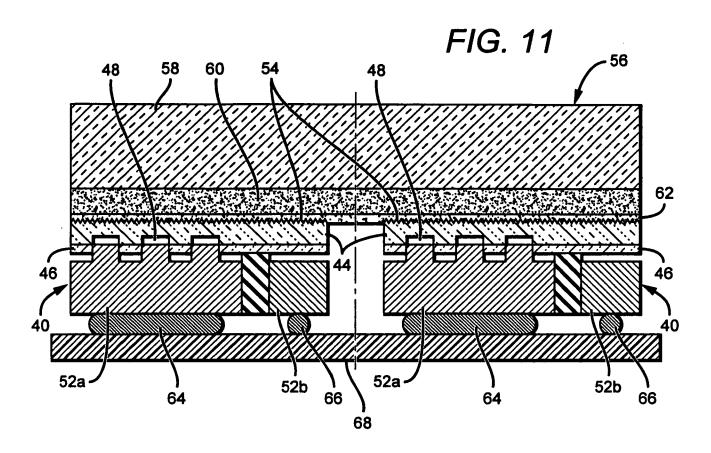

- [0011] FIG. 11 is a sectional view of a submount wafer and LED wafer in FIG. 10 following flip-chip mounting; and

- [0012] FIG. 12 is a sectional view of the capping wafer, submount wafer and LED wafer in FIG. 11 following singulation.

# DETAILED DESCRIPTION OF THE INVENTION

[0014] The present invention provides fabrication methods that are particularly applicable to wafer level capping of semiconductor devices such as LEDs. The present invention also provides semiconductor devices, such as LEDs fabricated using these methods, and related LED packages and LED arrays. The

present invention provides for methods of making devices and devices that can be surface mounted or can otherwise be wirebond free. A capping layer is mounted to the LED wafer and has certain characteristics that can decrease the likelihood that LEDs in the wafer or the other wafer layers of the structure would be damaged during heat cycles. In some embodiments, the capping layer has characteristics that reduce the likelihood that the LEDs or other wafer layers will be damaged during the thermal cycle of the LEDs being mounted to a package or submount. This temperature cycle can heat the LEDs up to approximately 300°C, which has been shown to introduce stresses on layers having differing characteristics.

[0015] In one embodiment, the capping wafer (or layer) is bonded to the LED wafer using an adhesive layer, and embodiments the capping wafer may include a down-converter. In some embodiments, the capping wafer is characterized as having a coefficient of thermal expansion ("CTE") that is close to that of the LED layers in the LED wafer. This allows the capping wafer and LED wafer to expand at similar rates during heat cycles, which reduces the stress between the two. This in turn reduces the damage to the LED wafer that might otherwise be caused by the stresses. In other embodiments, the capping layer can have a CTE that is close to that of the package or submount that the LED is mounted to. This also reduces the stresses experience by the LED during the attachment thermal After the capping wafer is bonded, final fabrication steps may be applied to the unbonded surface of the LED wafer opposite the capping wafer, such that the capping wafer acts as a robust, mechanical support. It is notable that all fabrication steps are completed at the wafer level prior to device singulation.

WO 2011/136837 PCT/US2011/000381

[0016] The present invention is described herein with reference to certain embodiments but it is understood that the invention can be embodied in many different forms and should not be construed as limited to the embodiments set forth herein. particular, the present invention is described below in regards to capping LED wafers with a down-converter capping wafer/layer that typically comprises a phosphor-loaded silicone coating, but it is understood that the capping wafer may be coated with other materials for down-conversion, protection, light extraction or The capping material can also have a conversion scattering. material mixed within it, instead of a conversion material coating. The methods according to the present invention can also be used for capping other semiconductor devices with different Additionally, single or multiple coatings and/or materials. layers can be formed on the capping wafer. A coating can phosphors, one or more phosphors, scattering include no particles and/or other materials. A coating may also comprise a material such as an organic dye that provides down-conversion. With multiple coatings and/or layers, each one can include different phosphors, different scattering particles, different optical properties, such as transparency, index of refraction, and/or different physical properties, as compared to other layers and/or coatings.

[0017] LEDs can have many different semiconductor layers arranged in different ways and can emit many different colors in different embodiments according to the present invention. LED structures, features, and their fabrication and operation are generally known in the art and only briefly discussed herein. The layers of the LEDs can be fabricated using known processes, with a suitable process being fabrication using metal organic chemical vapor deposition (MOCVD). The layers of the LED chips

generally comprise an active layer/region sandwiched between first and second oppositely doped epitaxial layers, all of which are formed successively on a growth substrate. LED chips can be formed on a wafer and then singulated for mounting in a package. It is understood that the growth substrate can remain as part of the final singulated LED or the growth substrate can be fully or partially removed.

[0018] Furthermore, LEDs may have vertical or lateral geometry as is known in the art. Those comprising a vertical geometry may have a first contact on a substrate and a second contact on a p-type layer. An electrical signal applied to the first contact spreads into the n-type layer and a signal applied to the second contact spreads into a p-type layer. In the case of Group-III nitride devices, it is well known that a thin semitransparent current spreading layer typically covers some or all of the p-type layer. It is understood that the second contact can include such a layer, which is typically a metal such as platinum (Pt) or a transparent conductive oxide such as indium tin oxide (ITO).

[0019] LEDs may also comprise a lateral geometry, wherein both contacts are on the top of the LEDs. A portion of the p-type layer and active region is removed, such as by etching, to expose a contact mesa on the n-type layer. A second lateral n-type contact is provided on the mesa of the n-type layer. The contacts can comprise known materials deposited using known deposition techniques.

[0020] It will be understood that when an element is referred to as being "on", "connected to", "coupled to" or "in contact with" another element, it can be directly on, connected or coupled to, or in contact with the other element or intervening elements may

be present. In contrast, when an element is referred to as being "directly on," "directly connected to", "directly coupled to" or "directly in contact with" another element, there are no intervening elements present. Likewise, when a first element is referred to as being "in electrical contact with" or "electrically coupled to" a second element, there is an electrical path that permits current flow between the first element and the second element. The electrical path may include capacitors, coupled inductors, and/or other elements that permit current flow even without direct contact between conductive elements.

[0021] Although the terms first, second, etc. may be used herein to describe various elements, components, regions, and/or sections, these elements, components, regions, and/or sections should not be limited by these terms. These terms are only used to distinguish one element, component, region, or section from another element, component, region, or section. Thus, a first element, component, region, or section discussed below could be termed a second element, component, region, or section without departing from the teachings of the present invention.

[0022] Embodiments of the invention are described herein with reference to cross-sectional view illustrations that are schematic illustrations of embodiments of the invention. As such, the actual thickness of components can be different, and variations from the shapes of the illustrations as a result, for example, of manufacturing techniques and/or tolerances are expected. Embodiments of the invention should not be construed as limited to the particular shapes of the regions illustrated herein but are to include deviations in shapes that result, for example, from manufacturing. A region illustrated or described

as square or rectangular will typically have rounded or curved features due to normal manufacturing tolerances. Thus, the regions illustrated in the figures are schematic in natures and their shapes are not intended to illustrate the precise shape of a region of a device and are not intended to limit the scope of the invention.

[0023] FIGs. 1-6 show one embodiment of wafer level LED chips 10 manufactured using a method according to the present invention with the series of figures showing the LED chips fabrication steps. That is, the LED chips 10 are shown in some figures at a point where all the fabrication steps have not been completed before being separated/singulated into individual LED chips. The LED chips comprise LEDs, and for ease of description and understanding the LEDs are shown as separate devices. It is understood, however, that one or more of the LED layers can be continuous so the LEDs can be provided in wafer form. Vertical phantom lines (as shown in FIGs. 3-5) are included to show separation or the dicing line between the LED chips 10 at a further described below, later fabrication step. As separation or dicing can take place at different points in the fabrication process.

[0024] FIGs. 1-6 also show only two devices at the wafer level, but it is understood that many more LED chips can be formed from a single wafer. For example, when fabricating LED chips having a 1 millimeter (mm) square size, up to 4500 LED chips can be fabricated on a 3 inch wafer.

[0025] Each of the LEDs can have many different semiconductor layers arranged in different ways. The fabrication and operation of LEDs is generally known in the art and only briefly discussed

herein. The layers of the LEDs can be fabricated using known processes with a suitable process being fabrication using metal organic chemical vapor deposition (MOCVD). The layers of the LEDs generally comprise an active layer/region sandwiched between first and second oppositely doped epitaxial layers 14, 16, all of which are formed successively on a substrate 12.

[0026] It is understood that additional layers and elements can also be included in the LEDs, including but not limited to buffer, nucleation, contact and current spreading layers as well as light extraction layers and elements. The active region can comprise single quantum well (SQW), multiple quantum well (MQW), double heterostructure or super lattice structures. In one embodiment, the first epitaxial layer 14 is an n-type doped layer and the second epitaxial layer 16 is a p-type doped layer, although in other embodiments the first layer 14 can be p-type doped and the second layer 16 can be n-type doped. The first and second epitaxial layers 14, 16 are hereinafter referred to as n-type and p-type layers, respectively.

[0027] The active region and layers 14, 16 of the LEDs may be fabricated from different material systems, with preferred material systems being Group-III nitride based material systems. Group-III nitrides refer to those semiconductor compounds formed between nitrogen and the elements in the Group III of the periodic table, usually aluminum (Al), gallium (Ga), and indium (In). The term also refers to ternary and quaternary compounds such as aluminum gallium nitride (AlGaN) and aluminum indium gallium nitride (AlInGaN). In a preferred embodiment, the n- and p-type layers 14, 16 are gallium nitride (GaN) and the active region is InGaN. In alternative embodiments the n- and p-type

layers 14, 16 may be AlGaN, aluminum gallium arsenide (AlGaAs) or aluminum gallium indium arsenide phosphide (AlGaInAsP).

The growth substrate 12 can be made of many materials [0028] such as sapphire, silicon carbide (SiC), aluminum nitride (AlN), GaN, Si, with a suitable substrate being a 4H polytype of silicon carbide, although other silicon carbide polytypes can also be used including 3C, 6H and 15R polytypes. Silicon carbide has certain advantages, such as a closer crystal lattice match to Group III nitrides than sapphire and results in Group III nitride films of higher quality. Silicon carbide also has a very high thermal conductivity so that the total output power of Group-III nitride devices on silicon carbide is not limited by the thermal dissipation of the substrate (as may be the case with some devices formed on sapphire). SiC substrates available from Cree Research, Inc., of Durham, North Carolina and methods for producing them are set forth in the scientific Re. literature as well as in a U.S. Patents, Nos. 5,200,022. In the embodiment 4,946,547; and substrate 12 is at the wafer level, with the plurality of LEDs 10 formed on the wafer substrate 12.

[0029] The substrate 12 can have different thicknesses. In an optional processing step, the substrate 12 can also be thinned or removed using known methods such as mechanical grinding, etching, or laser-ablation to allow for easier and more reliable singulating of the LED chips. This thinning or substrate removal can also result in LED chips having the desired thickness. that the substrate 12 depicted in FIG. 1 is no longer depicted in FIGs. 3-7, as it has been removed according to one possible the substrate is understood that embodiment. Ιt or untouched. In still other alternatively be thinned

embodiments where the substrate 12 is made of a material that is compatible with shaping, such as silicon carbide, the substrate 12 can include different shapes to enhance light extraction.

[0030] The present invention is particularly adapted for use with LEDs arranged so both contacts are accessible from one surface, such as with lateral geometry LEDs as shown. However, it is understood that vertical geometry LEDs may also be used. Lateral geometry devices are usually arranged with a split-level electrode configuration with both electrodes on the top surface of layers on different levels of the device. Thus, the electrodes do not share a common surface but rather a common top-side orientation with respect to the layers on which they are disposed. Charge carriers move laterally through the semiconductor layers for at least a portion of the current path in response to a bias. Several variations of this common geometry are known and used in the art.

[0031] Each of the LEDs can have first and second electrodes or contacts 22a, 22b. In the embodiment shown, the first contact 22a is on the mesa of the p-type layer contact 20 and the second contact 22b is in contact with the n-type layer contact 18. An electrical signal applied to the first contact 22a spreads into the p-type layer 16 and a signal applied to the second contact 22b spreads into the n-type layer 14. The first and second contacts can comprise many different materials such as Au, copper (Cu), nickel (Ni), indium (In), aluminum (Al), silver (Ag), or combinations thereof. In still other embodiments, the comprise conducting oxides and transparent can conducting oxides such as indium tin oxide, nickel oxide, zinc oxide, cadmium tin oxide, titanium tungsten nickel, indium oxide, tin oxide, magnesium oxide, ZnGa<sub>2</sub>O<sub>4</sub>, ZnO<sub>2</sub>/Sb, Ga<sub>2</sub>O<sub>3</sub>/Sn,

$AgInO_2/Sn$ ,  $In_2O_3/Zn$ ,  $CuAlO_2$ , LaCuOS,  $CuGaO_2$  and  $SrCu_2O_2$ . The choice of material used can depend on the location of the contacts as well as the desired electrical characteristics such as transparency, junction resistivity and sheet resistance.

[0032] It is understood that other LED structures and geometries can be provided for use in the present invention with the structures having contacts accessible from one surface. These alternative embodiments can provide this access by utilizing other conductive structures such as conductive vias, traces or other conductive paths.

[0033] In the embodiment shown, the first contact 22a covers substantially the entire p-type layer 16, and the second contact covers a portion of the n-type layer 14. Since light is emitted from the LED primarily through the substrate 12, the first and second contacts 22a, 22b do not interfere with or reduce light emission. In other embodiments, the first and second contacts 22a, 22b can cover less than or more of their respective surfaces and other layers or structures can be included to assist in current spreading across their surfaces. possible embodiment, a thin current spreading layer can cover some or all of the p-type layer 16 and n-type layer 14, which be transparent or semitransparent. Examples materials include platinum (Pt) or a transparent conductive oxide such as indium tin oxide (ITO), although other materials can also be used. The first and second contacts 22a, 22b can have varying thicknesses. In a preferred embodiment, the electrodes/contacts 22a, 22b are substantially thick comprised of metal, and provide the primary mechanical support for the LED chips 10 when/if the substrate 12 is thinned or removed and when/if the GaN surface is further fabricated such as by etching.

[0034] Current spreading structures (not shown) can also be included on the surfaces of the p-type or n-type mesa to improve current spreading and injection from their contacts. The current spreading structures can have many different forms, but preferably comprises fingers of conductive material surface of the LED contacting one of the contacts 22a, 22b. The current spreading structures can be deposited using methods and can comprise the materials described above such as Au, Cu, Ni, In, Al, Ag or combinations thereof and conducting oxides and transparent conducting oxides. According to one other possible embodiment, a filler material 24 may also be provided to electrically isolate first and second contacts 22a, 22b.

[0035] FIG. 2 depicts a capping wafer or layer 26 ("capping wafer") with a desired refractive index, which will be bonded to the LED wafer of LED chips 10. In some embodiments, the capping wafer 26 comprises a transparent and robust layer 28, and a embodiments, phosphor coating or layer 30. In some transparent layer 28 is substantially transparent to the light emitted by the LED chips 10, the light from the phosphor coating 30, or both. It understood, however, that the transparent layer need not be 100% transparent to light from the LED chip 10 and phosphor coating 30. The capping wafer 26 can have a diameter that is substantially similar to or larger than that of the LED wafer, but it is understood that the capping wafer can be smaller than the diameter of the LED wafer and can take many different shapes and sizes. Ideally, the capping wafer 26 is pre-formed, and is bonded to the LED chips 10 at the wafer level

to provide needed mechanical support during the latter stages of device fabrication and when handling the completed devices after they are singulated. As such, the capping wafer 26 can decrease the chances of mechanical damage to the LED chips 10 through fabrication, and increases the potential yield of wire-bond free This can reduce the overall cost of fabricating LED chips. Moreover, the transparent layer 28 can have a CTE that more closely matches the CTE of the LED wafer. The CTE for the transparent layer 28 can fall into many different ranges. For example, in some embodiments the capping wafer 26 may have a CTE in the range of 2-25 ppm/°C, and in another embodiment it can have a CTE in the range of 2-14 ppm/°C. In still embodiments it can have a CTE in the range of 13-20, 5-11, 7-9 or 2-5 ppm/°C, and in some embodiments it can have a CTE of approximately 7.4 ppm/°C.

embodiments, the transparent layer 28 [0036] In some comprise a material with a CTE that matches that of the package (or submount shown for example as element 36 in FIG.4) that the LED is being mounted to. This reduces the stress that is experienced with layers of the LED chip during the the attachment thermal cycle, there reducing the likelihood that the chip will experience damage during this cycle. These transparent layers can have the same ranges of CTE as those described above, including a CTE in the range of 2-14 ppm/°C in one embodiment, and in another embodiment a CTE in the range of 5-11 ppm/°C. In still other embodiments the can have a CTE in the range of 7-9 ppm/°C.

[0037] In some embodiments, the submount can comprise alumina, which has a CTE of approximately 8 ppm/°C, while in other embodiments the submount can comprise aluminum nitride (AlN),

which has a CTE of approximately 5 ppm/°C. Both of these have an acceptable CTE match for certain semiconductor materials, such as GaN which has a CTE in the lateral direction of 5.6 ppm/°C. For each of these submounts a capping wafer should have a transparent layer 28 with a CTE that substantially matches the CTE of the submount. In one embodiment, the CTE difference should be less that 20%, and in other embodiments the CTE difference should be less than 30%. In still other embodiments, the CTE difference should be less than 40%. In one embodiment the capping wafer 26 can comprise a glass transparent layer 28 and a silicone coating 30. Many different types can be used with the transparent laver 28 comprising embodiment of one commercially available glass such as Corning 0211 Borosilicate have a CTE of 7.4 ppm/°C. which can Glass, embodiments, the layer 28 can comprise other materials, such as sapphire, which has a CTE of 7-7.7 ppm/°C depending partially on its crystal orientation. It is understood that many other materials with different CTEs can also be used.

[0038] In other embodiments, the submount can comprise other materials with different CTEs. In some embodiments, the submount can comprise lower CTE materials such as silicon, which has a CTE of approximately 2.5 ppm/°C. In these embodiments the transparent layer 28 capping wafer 26 can have a CTE in the range of 2-14 or 2-5 ppm/°C, while in other embodiments it can have a CTE in the range of 2.5-3.5 ppm/°C. In one embodiment, the transparent layer 28 can comprise low thermal expansion borosilicate glass that can have a CTE of approximately 3.25 ppm/°C, but it is understood that many other materials with different CTEs can also be used.

[0039] In still other embodiments, the submount can comprise a metal, such as Cu, having a higher CTE of 16.4 ppm/°C. In some of these metal embodiments, the capping transparent layer 28 can have a CTE in the range of 10-25 ppm/°C, while in other embodiments the transparent layer can have a CTE in the range of 13-20 ppm/°C. In still other embodiments, the transparent layer can have a CTE in the range of 15-17 ppm/°C. In some embodiments, specialty glasses can be used for the transparent layer 28 having a CTE that is engineered. One such specialty glass includes commercially available Advanced Ceramics Mexim C ACL 2091, which can have an CTE of approximately 16.5 ppm/°C. It is understood that many other materials with different CTEs can also be used.

[0040] In some embodiments, the coating 30 may preferably comprise a phosphor-loaded silicone, with the phosphor acting as a down-converter for white-emitting light sources. It is understood that colors other than white may be desired, or that the LED chip can have its own conversion material to convert light emitted from the LED chip. In these embodiments a down-converter may not be necessary in the capping wafer and the capping wafer acts mainly as a robust mechanical support. However, by incorporating the down-converter as an element of the pre-formed capping wafer 26 for white-emitting light sources, the overall fabrication process can be simplified.

[0041] The silicone in the coating 30 can serve as and adhesive between the capping wafer 26 and the LED chips 10. It is understood however, that other embodiments can be provided without the coating 30. In these embodiments, the transparent layer 28 can be bonded directly to the LED chips 10 using different processes such as heat or pressure to achieve bonding.

WO 2011/136837 PCT/US2011/000381

In these embodiments, the transparent layer can be included with our without a conversion material or phosphor, and in these direct bonded embodiments a conversion material can be included on other surfaces of the transparent layer 28.

embodiment of the capping wafer 26 [0042] While one preferably be formed of glass with a silicone/phosphor coating, it is understood that other materials are suitable according to invention can be used for both. Beyond the the present materials described above, the capping wafer 26 may also comprise a single crystal phosphor sheet, sintered phosphors, or a glass sheet filled with phosphor particles. Moreover, the transparent portion of the capping wafer may alternatively comprise any other suitable materials that can be mechanically robust and capable of withstanding typical die attach processes at high temperatures, with other possible materials including SiC, GaN or ZnO.

[0043] The coating 30 can also comprise many different materials beyond silicone, with the different materials preferably being robust after curing and substantially transparent in the visible wavelength spectrum. Suitable alternative materials silicones, epoxies, spin-on glass, BCB, polymides and polymers, with the being silicone material because of its hiah preferred transparency and reliability in high power LEDs. A suitable is commercially available from Dow® Chemical under number OE6665. In other embodiments, silicone product coating material can be engineered to be index matched with the features such as the chip (semiconductor material) and growth substrate, which can reduce total internal reflection (TIR) and improve light extraction.

ملمار

[0044] Many different phosphors can be used in the coating 30 according to the present invention. In one embodiment according to the present invention LEDs can emit light in the wavelength spectrum and the phosphor absorbs some of the blue light and re-emits yellow. The LED can then emit a white light combination of blue and yellow light. In one embodiment the phosphor comprises commercially available YAG:Ce, although a full range of broad yellow spectral emission is possible using

conversion particles made of phosphors based  $(Gd,Y)_3(Al,Ga)_5O_{12}$ :Ce system. The following lists some additional suitable phosphors used as conversion particles in LED chips, although others can be used. Each exhibits excitation in the blue and/or UV emission spectrum, provides a desirable peak emission, has efficient light conversion, and has acceptable Stokes shift:

### YELLOW/GREEN

$(Sr,Ca,Ba)(Al,Ga)_2S_4:Eu^{2+}$  $Ba_{2}(Mg, Zn) Si_{2}O_{7}: Eu^{2+}$  $Gd_{0.46}Sr_{0.31}Al_{1.23}O_xF_{1.38}:Eu^{2+}_{0.06}$ (Ba<sub>1-x-v</sub>Sr<sub>x</sub>Ca<sub>v</sub>)SiO<sub>4</sub>:Eu Ba<sub>2</sub>SiO<sub>4</sub>:Eu<sup>2+</sup>

#### RED

Lu<sub>2</sub>O<sub>3</sub>: Eu<sup>3+</sup>  $(Sr_{2-x}La_x)(Ce_{1-x}Eu_x)O_4$ Sr<sub>2</sub>Ce<sub>1-x</sub>Eu<sub>x</sub>O<sub>4</sub> Sr<sub>2-x</sub>Eu<sub>x</sub>CeO<sub>4</sub>  $SrTiO_3: Pr^{3+}, Ga^{3+}$ CaAlSiN<sub>3</sub>: Eu<sup>2+</sup> Sr<sub>2</sub>Si<sub>5</sub>N<sub>8</sub>:Eu<sup>2+</sup>

[0045] Different sized phosphor particles can be used including but not limited to nanometer-sized particles to 20-30 micron sized particles, or larger. Smaller particle sizes typically scatter and mix colors better than larger sized particles to provide a more uniform light. Larger particles are typically more efficient at converting light compared to particles, but emit a less uniform light. In one embodiment, the particle sizes are in the range of 2-5 microns. embodiments, the coating 30 can comprise different types of comprise multiple phosphor coatings phosphors or can monochromatic or polychromatic light sources. The coating 30 can also have different concentrations of phosphor materials, with a typical concentration being in range of 30-70% by weight. In one embodiment, the phosphor concentration is approximately 65% by weight, and is preferably uniformly dispersed throughout the binder. Still in other embodiments the coating can comprise different concentrations of types multiple layers of phosphors, or a first coat of clear silicone can be deposited followed by phosphor loaded layers. The coating can also include elements to scatter or mix the light, including but not limited to scattering particles. Furthermore, the surface of the coating 30 and or the transparent layer can be roughened or shaped to enhance light extraction.

[0046] At least one advantage of pre-forming the capping wafer 26 is the ability to prescreen and/or tailor the down-converter to closely match the LED wafer and the desired color point. With regard to the phosphor coating, the coating may be grinded to a desired thickness at the wafer level. Additionally, the thickness of the conversion material can be individually tailored at each LED at the wafer level, which can occur either

before or after the capping wafer and the LED wafer are bonded together. Moreover, the capping wafer is advantageous because it may make any additional packaging unnecessary. As such, a finished die with the capping wafer may serve as a final chip scale package. This can reduce the overall cost and footprint for lighting applications.

[0047] The thickness of the capping wafer 26 can range, for example, from anywhere between 50-5000µm, with a preferred range The capping wafer may initially be substantially of 100-1000µm. thicker prior to bonding it to the LED wafer, and then later be grinded down or polished to a desired final thickness prior to device singulation. For example, the transparent layer 28a of wafer 26 in FIG. 5 is either ground down or polished (as seen in comparison with the wafer of FIG. 4) prior singulation. Thicker wafers may be preferred during fabrication, as they aid in the mechanical robustness of the device and prevent bowing effects during fabrication, which can particularly problematic in larger diameter wafers. Also, light is capable of escaping from the sidewalls of the capping wafer 26, which is advantageous at least in that it allows for thicker This may allow for better efficiency in applications where the wire-bond free chips are not subject to additional packaging.

[0048] FIG. 3 shows capping wafer 26 bonded to LED chips 10 using an adhesive layer 38. Preferably, a thin, transparent adhesive layer 38 with a desired refractive index is used, with one possible suitable material being silicone. However, it is understood that other suitable materials may also be used, with materials preferably being robust after curing and substantially transparent in the visible wavelength spectrum. Suitable

materials include many of those used in the coating 30, including but not limited to silicones, epoxies, glass, inorganic glass, spin-on glass, dielectrics, BCB, polymides, polymers and hybrids thereof, with the preferred material being silicone because of its high transparency and reliability in high power LEDs. Suitable phenyl- and methyl-based silicones are commercially available from Dow® Chemical. In other embodiments, the binder material can be engineered to be index matched with the features such as the chip (semiconductor material) and growth substrate, which can reduce total internal reflection (TIR) and improve light extraction.

[0049] The capping wafer 26 helps to minimize the thermal stress inflicted on the LED wafer while the two wafers are bonded After the capping wafer 26 and LED chips 10 together. final fabrication steps such as mesa and/or metallization applied planarization, can be unbounded surface of the LED chips 10 opposite the capping wafer In this way, the capping wafer 26 may act as a robust 26. mechanical support for the LED chips 10, thus limiting any potential damage to the otherwise delicate chips that may occur during fabrication.

[0050] In some embodiments, the capping wafer 26 and LED chips 10 bonded together as shown in FIG. 3 comprises the completed wafer level processing, with the phantom lines showing the separation or singulation lines between the primary finished product. To make the finished LED chips of FIG. 3 into usable LED components, the LED chips can be flip-chip mounted (i.e. wire bonded) onto conventional packages or submounts (or printed circuit boards). By mounting a capping wafer to the LED chips prior to singlulation, and by choosing a transparent layer

with CTE as described material a above to match the package/submount, the LED chips can be reliably flip-chip mounted with little or no damage to the LED chips. Accordingly, the capping wafer can increase the yield of LED chips that are singulated and flip-chip mounted according to the present invention. In other embodiments, the LED chips wafer can be flip-chip mounted to the package/submount, but this can have result in end devices having a submount that is the same size as the LED and adds an additional attach step.

[0051] When fabrication of the LED chips 10 is complete, each LED chip may comprise portions of submount wafer 36, with the LEDs flip-chip mounted to it. The submount wafer 36 in FIGs. 4-5, like the LEDs above, is shown at a wafer level of the fabrication process. As described above, phantom lines are included to show separation or the dicing line at the submount wafer 36 for the individual LED chips 10. When fabrication is complete and the LED chips 10 are singulated, each of the LED chips will have a portion of the submount wafer 36 as shown in FIG. 6. For example, the submount wafer 36 can be sized for fabricating LED chips having a 1 millimeter (mm) square size, and can provide submount portions for up to 4500 LED chips.

[0052] The submount wafer 36 can be made of many different those described above such and can include materials as conducting or semiconducting materials or insulating materials. suitable materials include ceramics such as oxide, aluminum nitride aluminum or polymide. Ιn embodiments the submount wafer can comprise a printed circuit board (PCB), sapphire or silicon, silicon carbide, or any other suitable material, such as commercially available T-Clad thermal clad insulated substrate material.

[0053] A dielectric layer (not shown) may be included on the surface of the submount wafer 36. The dielectric layer electrically insulates the wafer 36 such that electrical signals on the surfaces of the submount wafer 36 do not spread into the submount wafer 36. This prevents the signals being applied to n-and p-type contacts 22a, 22b from shorting through the submount wafer 36. Different materials can be used for the dielectric layer, with suitable materials being silicon nitride or silicon oxide. For submount wafers made of an insulating material such as ceramic, it may not be necessary to include a dielectric layer for electrical isolation.

[0054] Referring now to FIG. 4, the LEDs in wafer form are flipchip mounted to the submount wafer 36. Flip-chip mounting is generally known in the art and only briefly discussed herein. The LEDs are mounted to the submount wafer 36 by a layer of conductive bond material 32, 34, which is typically one or more bond/metal layers such as solder. The bond material 32, 34 may also be made of a material that reflects light. This reflective property can improve the emission efficiency of an LED chip. In other embodiments, reflectors can be included in many different locations to provide the desired reflective properties. It is understood that the submount wafer 36 can be made of many different materials, such as those described above in the discussion of CTE for desired materials.

[0055] Referring now to FIG. 6, the individual LED chips 10 can be singulated using known methods such as dicing, scribe, breaking, cleaving or etching. This generally comprises cutting through the capping wafer 26 and the submount wafer 36 between LEDs either from the bottom through the submount wafer first or the top through the capping wafer 26 first. The singulating

process separates each of the LED chips 10 with each having substantially the same thickness of capping wafer 26, and as a result, substantially the same amount of mechanical support as well as phosphor and emission characteristics. This allows for reliable and consistent fabrication of LED chips 10 having similar characteristics.

[0056] Following singulating, the LED chips 10 can be mounted in a package, or to a submount or printed circuit board (PCB) without the need for further processing to add phosphor. A conventional encapsulation can then surround the LED chip. In another embodiment, the LED chip can be enclosed by a hermetically sealed cover with an inert atmosphere surrounding the LED chip at or below atmospheric pressure.

[0057] The LED chip 10 can be surface mounted in a package without the use of wire bonds to apply an electrical signal. In particular, there is no wire bond to the top surface of LED chip 10 for applying an electrical signal, which leaves an unobstructed top surface. Accordingly, a package utilizing the LED chip 10 can have secondary optics directly mounted on the top surface without the need for compensating for wire bonds or other structures. This can simplify fabrication of the LED package by not having an intermediate layer between to cover the wire bonds before mounting the secondary optics or by not having other features such as reflective cups that allow for the secondary optics to be mounted above the LED chip with a space for the wire bonds.

[0058] It is understood that in other embodiments, the LED chips' 10 growth substrate can be removed after (or before) flip-chip bonding, with the substrate removed using known grinding and/or etching processes. In other embodiments, the

growth substrate or at least portions thereof remain. The growth substrate or the remaining portions can be shaped or textured to enhance light extraction from the LEDs.

[0059] FIGs. 7-12 show another possible embodiment of wafer level LED chips 40 with the series of figures showing the LED chips 40 at fabrication steps. The LED chips comprise LEDs, and as above, for ease of description and understanding the LEDs are shown as separate devices. Vertical phantom lines (as shown in FIGs. 10-11) are included to show separation or the dicing line between the LED chips 40 at a later fabrication step. Moreover, while FIGs. 7-12 show only two devices at the wafer level, it is understood that many more LED chips can be formed from a single wafer.

[0060] The layers of the LEDs generally comprise an active layer/region sandwiched between first and second oppositely doped epitaxial layers 44, 46, all of which are formed successively on a substrate 42. As described above, it is understood that additional layers and elements can also be included in the LEDs. In one embodiment, the first epitaxial layer 44 is an n-type doped layer and the second epitaxial layer 46 is a p-type doped layer, although in other embodiments the first layer 44 can be p-type doped and the second layer 46 can be n-type doped. The first and second epitaxial layers 44, 46 are hereinafter referred to as n-type and p-type layers, respectively.

[0061] The substrate 42, active region and layers 44, 46 of the LEDs may be fabricated from different material systems as described above. Additionally, as described above with substrate 12, substrate 42 can have different thicknesses. In an optional processing step, the substrate 42 can also be thinned

or removed using known methods such as mechanical grinding, etching, or laser-ablation to allow for easier and more reliable singulating of the LED chips. This thinning or substrate removal can also result in LED chips having the desired thickness. Note that the substrate 42 depicted in FIG. 7 is no longer depicted in FIGs. 8-12, as it has been removed according to one possible embodiment. It is understood that the substrate 42 may alternatively be thinned or untouched. In still other embodiments where the substrate 42 is made of a material that is compatible with shaping, such as sapphire, the substrate 42 can include different shapes to enhance light extraction.

[0062] This particular embodiment is adapted for use with LEDs arranged so both contacts are accessible from one surface, such as with lateral geometry LEDs as shown. However, it is understood that vertical geometry LEDs may also be used. Each of the LEDs can have first and second electrodes or contacts 52a, 52b. In the embodiment shown, the first contact 52a is in contact with the p-type layer 46, and the second contact 52b is in contact with the n-type layer contact 44 by way of vias 48. An electrical signal applied to the first contact 52a spreads into the p-type layer 46 and a signal applied to the second contact 52b spreads into the n-type layer 44.

[0063] It is understood that other LED structures and geometries can be provided for use in the present invention with the structures having contacts accessible from one surface. These alternative embodiments can provide this access by utilizing other conductive structures such as conductive vias, traces or other conductive paths.

[0064] As described above, the first and second contacts 52a, 52b can cover less than or more of their respective surfaces and

other layers or structures can be included to assist in current spreading across their surfaces. Moreover, the first and second contacts 52a, 52b can have varying thicknesses. In a preferred embodiment, the electrodes/contacts 52a, 52b are substantially thick and comprised of metal, and provide the primary mechanical support for the LED chips 40 when/if the substrate 42 is thinned or removed and when/if the GaN surface is further fabricated such as by etching.

[0065] FIG. 9 depicts a capping wafer 56 with a transparent layer 58 and a layer 60 comprising a down-converter, with wafer 56 similar to capping wafer 26 described in detail above. As shown in FIG. 10, the capping wafer 56 is bonded to the LED wafer of LED chips 40 (as shown in FIGs. 7 and 8) using an adhesive 62 similar to adhesive 38 described above. After the capping wafer 56 and LED chips 40 are bonded, final fabrication steps such as mesa etch, planarization, and/or metallization can be applied to the unbounded surface of the LED chips 40 opposite the capping wafer 56.

[0066] When fabrication of the LED chips 40 is complete, each LED chip may comprise portions of submount wafer 68 (similar to wafer 36 above), with the LEDs flip-chip mounted to it. The submount wafer 68 in FIGs. 11-12, like submount wafer 36 shown in FIGs. 4-6 and described above, is shown at a wafer level of the fabrication process. As described above, phantom lines are included to show separation or the dicing line at the submount wafer 68 for the individual LED chips 40. When fabrication is complete and the LED chips 40 are singulated, each of the LED chips will have a portion of the submount wafer 68 as shown in FIG. 12.

[0067] Referring now to FIG. 11, the LEDs in wafer form are flip-chip mounted to the submount wafer 68. The LEDs are mounted to the submount wafer 68 by a layer of conductive bond material 64, 66, which is typically one or more bond/metal layers such as solder.

[0068] Referring now to FIG. 12, the individual LED chips 40 can be singulated using known methods as described above. Following singulating, the LED chips 40 can be mounted in a package, or to a submount or printed circuit board (PCB) without the need for further processing to add phosphor. A conventional encapsulation can then surround the LED chip. The LED chip 40 can be surface mounted in a package without the use of wire bonds to apply an electrical signal.

[0069] Referring now to FIGs. 7-8, the LED chips' 40 growth substrate 42 can be partially or totally removed, with portions of or the entire substrate removed using known grinding and/or etching processes. Additionally, portions of the n-type layer 44 (or various layers according to other contemplated embodiments) can be shaped or textured as shown at top surface 54 to enhance light extraction from the LEDs.

[0070] The LED chips have been described above as being adapted for mounting in packages utilizing a single LED chip. It is understood, however, that the LED chips according to the present invention can be arranged in arrays of LED chips, with the array having LED chips that are structurally the same or similar and emit light at the same or similar wavelengths of light. Alternatively, the LED chips can be structurally different or can emit different wavelengths of light. In some embodiments, the LED chips can be electrically interconnected so that they emit light in response to one electrical signal that is

WO 2011/136837 PCT/US2011/000381

conducted to all the LEDs chips in the array. In other embodiments emission the LEDs chips can be individually controlled by respective signals to control the emission intensity of each of the LED chips. This in turn can control the emission intensity of the LED array, and in arrays having LED chips emitting different colors of light, this can control the intensity and emission color of the overall array.

[0071] While several illustrative embodiments of the invention have been shown and described, numerous variations and alternate embodiments will occur to those skilled in the art. Such variations and alternate embodiments are contemplated, and can be made without departing from the spirit and scope of the invention as defined in the appended claims.

#### WE CLAIM:

1. A method for fabricating light emitting diode (LED) chips, comprising:

pre-forming a capping wafer, said capping wafer comprising

a conversion material;

fabricating a wire-bond free LED wafer comprising a plurality of LEDs;

bonding said capping wafer to said LED wafer using an adhesive; and

singulating said LED chips upon the completion of all final fabrication steps.

- 2. The method of claim 1, further comprising flip-chip mounting said LED wafer on a surface of a submount wafer prior to said singulating.

- 3. The method of claim 1, wherein said capping wafer comprises a transparent layer and a coating comprising said conversion material.

- 4. The method of claim 3, wherein said transparent layer has a coefficient of thermal expansion (CTE) that substantially matches the CTE of said LED wafer.

- 5. The method of claim 3, further comprising mounting said LED chips to a submount, wherein said capping wafer comprises a transparent layer and a coating comprising said conversion material, wherein said transparent layer has a coefficient of thermal expansion (CTE) that substantially matches the CTE of said submount.

- 6. The method of claim 3, wherein said conversion material comprises one or more of a silicone layer with dispersed phosphor particles, a single crystal phosphor sheet, sintered phosphors, or a glass sheet filled with phosphor particles.

- 7. The method of claim 1, wherein said adhesive is substantially transparent and applied in a thin layer.

- 8. The method of claim 7, wherein said adhesive comprises silicone.

- 9. The method of claim 1, wherein said capping wafer keeps said adhesive flat during curing, and further minimizes thermal stress on said LEDs.

- 10. The method of claim 1, wherein said capping wafer acts as a robust mechanical support for said LED chips.

- 11. The method of claim 1, wherein said capping wafer may be grinded down or polished prior to said singulation.

- 12. The method of claim 1, wherein said final fabrication steps comprise one or more of mesa etch, planarization, or metallization.

- 13. The method of claim 2, wherein at least some of said singulated LED chips comprise an LED, a portion of said capping wafer, and a portion of said submount wafer.

- 14. The method of claim 1, wherein said LED chips emit white light.

- 15. The method of claim 1, wherein said LEDs have a lateral geometry and comprise n- and p-type layers, and further comprise first and second contacts on said n- and p-type layers respectively.

- 16. The method of claim 14, wherein one or more of said n- or p-type layers is shaped or textured.

- 17. The method of claim 1, wherein said LEDs are provided on a growth substrate.

- 18. The method of claim 17, further comprising removing at least a portion of said growth substrate prior to bonding said capping wafer.

- 19. The method of claim 17, wherein said substrate is shaped or textured.

- 20. The method of claim 1, wherein said capping wafer comprises multiple layers with different compositions.

- 21. The method of claim 1, further comprising mounting one of said LED chips to a second submount or printed circuit board (PCB).

- 22. A light emitting diode (LED) chip wafer, comprising:

- a submount wafer;

- a plurality of LEDs flip-chip mounted on said submount wafer; and

- a capping wafer bonded to said LED chip wafer using an adhesive, said capping wafer comprising a conversion material,

said capping wafer further a material acting as a robust mechanical support for said LEDs;

wherein at least some of the light emitted from said LEDs passes through said capping wafer where at least some of said light is converted by said conversion material;

wherein said LEDs are capable of being singulated.

- 23. The LED chip wafer of claim 22, wherein the coefficient of thermal expansion for said robust mechanical support material is substantially the same as the CTE for the material comprising the LEDs in said LED chip wafer.

- 24. The LED chip wafer of claim 22, wherein the coefficient of thermal expansion for said robust mechanical support material is substantially the same as the CTE of the material comprising said submount wafer.

- 25. The LED chip wafer of claim 22, wherein there is less than a 40% difference in the coefficient of thermal expansion for said robust mechanical support material compared to the CTE of the material comprising the LEDs in said LED chip wafer.

- 26. The LED chip wafer of claim 22, wherein there is less than a 40% difference in the coefficient of thermal expansion for said robust mechanical support material compared to the CTE of the material comprising the submount wafer.

- 27. The LED chip wafer of claim 22, wherein there is less than a 30% difference in the coefficient of thermal expansion for said robust mechanical support material compared to the CTE of the material comprising the LEDs in said LED chip wafer.

- 28. The LED chip wafer of claim 22, wherein there is less than a 30% difference in the coefficient of thermal expansion for said robust mechanical support material compared to the CTE of the material comprising the submount wafer.

- 29. The LED chip wafer of claim 22, wherein the thickness of the conversion material can be individually tailored at each LED at the wafer level either before or after said capping wafer and said LED wafer are bonded together.

- 30. The LED chip wafer of claim 29, wherein said conversion material comprises phosphor.

- 31. The LED chip wafer of claim 22, wherein at least some of said LEDs have lateral geometry.

- 32. The LED chip wafer of claim 22, wherein said submount wafer is capable of being separated into LED chips.

- 33. The LED chip wafer of claim 22, wherein said capping wafer has a uniform thickness above said LEDs.

- 34. The LED chip wafer of claim 22, wherein said LEDs are made of materials from the Group-III nitride material system.

- 35. The LED chip wafer of claim 22, wherein said LEDs are interconnected in an LED array.

- 36. The LED chip wafer of claim 22, capable of emitting white light from said LEDs and capping wafer.

- 37. The LED chip wafer of claim 22, wherein said wherein said robust support material comprises a transparent material.

- 38. The LED chip wafer of claim 37, wherein said transparent material comprises one or more of glass, SiC, sapphire, GaN, or ZnO, and said conversion material comprises one or more of a silicone layer with dispersed phosphor particles, a single crystal phosphor sheet, sintered phosphors, or a glass sheet filled with phosphor particles.

- 39. The LED chip wafer of claim 22, wherein said adhesive is substantially transparent, applied in a thin layer, and comprises silicone.

- 40. A light emitting diode (LED) chip, comprising:

- a wire-bond free LED;

- a capping wafer bonded to said LED using an adhesive, said capping wafer serving as a mechanical support for said LED chip; and

- a conversion material integrated in said capping wafer, said conversion material converting at least some of the light emitted from said LED.

- 41. The LED chip of claim 40, wherein said capping wafer is continuous over the top surface of said LED and has a substantially uniform thickness.

- 42. The LED chip of claim 40, emitting a white light combination of LED light and light from said conversion material.

- 43. The LED chip of claim 40, further comprising a submount, said LED flip-chip mounted on said submount.

- 44. The LED chip of claim 40, wherein said capping wafer comprises:

- a transparent portion; and

- a layer comprising said conversion material;

wherein said transparent portion comprises one or more of glass, SiC, sapphire, GaN, or ZnO, and said conversion material comprises one or more of a silicone layer with dispersed phosphor particles, a single crystal phosphor sheet, sintered phosphors, or a glass sheet filled with phosphor particles.

45. The LED chip of claim 40, wherein said adhesive comprises silicone.

#### INTERNATIONAL SEARCH REPORT

International application No PCT/US2011/000381

A. CLASSIFICATION OF SUBJECT MATTER INV. H01L33/50 H01L3 H01L33/50 H01L33/00 ADD. According to International Patent Classification (IPC) or to both national classification and IPC **B. FIELDS SEARCHED** Minimum documentation searched (classification system followed by classification symbols) H01L Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched Electronic data base consulted during the international search (name of data base and, where practical, search terms used) EPO-Internal, INSPEC, IBM-TDB, WPI Data C. DOCUMENTS CONSIDERED TO BE RELEVANT Category\* Citation of document, with indication, where appropriate, of the relevant passages Relevant to claim No. Χ WO 2007/063460 A1 (PHILIPS INTELLECTUAL 22-38. PROPERTY [DE]; KONINKL PHILIPS ELECTRONICS 40-44 NV [NL) 7 June 2007 (2007-06-07) page 12, line 16 - page 13, line 8 γ figures 9-11 1-21,45 Α US 2007/215890 A1 (HARBERS GERARD [US] ET 40-45 χ AL) 20 September 2007 (2007-09-20) paragraph [0041] 39 1-38 Α figure 2 US 2008/048200 A1 (MUELLER GERD [US] ET AL MUELLER GERD 0 [US] ET AL) X 40-45 28 February 2008 (2008-02-28) paragraphs [0129], [0135], [0136] Α 1 - 39figures 41A-41E X Further documents are listed in the continuation of Box C. See patent family annex. Special categories of cited documents: "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the "A" document defining the general state of the art which is not considered to be of particular relevance invention "E" earlier document but published on or after the international "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to filing date document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) involve an inventive step when the document is taken alone "Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such docu-"O" document referring to an oral disclosure, use, exhibition or ments, such combination being obvious to a person skilled in the art. other means document published prior to the international filing date but later than the priority date claimed "&" document member of the same patent family Date of the actual completion of the international search Date of mailing of the international search report 27 May 2011 08/06/2011 Name and mailing address of the ISA/ Authorized officer European Patent Office, P.B. 5818 Patentlaan 2 NL - 2280 HV Rijswijk Tel. (+31-70) 340-2040, Fax: (+31-70) 340-3016 Adams, Richard

### **INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2011/000381

| Patent document cited in search report | Publication<br>date | Patent family<br>member(s)                                                                 | Publication<br>date                                                |

|----------------------------------------|---------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| WO 2007063460 A1                       | 07-06-2007          | CN 101366126 A<br>EP 1958269 A1<br>JP 2007150331 A<br>US 2007126017 A1<br>US 2009155943 A1 | 11-02-2009<br>20-08-2008<br>14-06-2007<br>07-06-2007<br>18-06-2009 |

| US 2007215890 A1                       | 20-09-2007          | CN 101405646 A<br>EP 1999510 A1<br>WO 2007107896 A1<br>JP 2007273998 A<br>RU 2008141124 A  | 08-04-2009<br>10-12-2008<br>27-09-2007<br>18-10-2007<br>27-04-2010 |

| US 2008048200 A1                       | 28-02-2008          | US 2011057205 A1                                                                           | 10-03-2011                                                         |