(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4727684号

(P4727684)

(45) 発行日 平成23年7月20日(2011.7.20)

(24) 登録日 平成23年4月22日(2011.4.22)

(51) Int.Cl.

H01L 29/786 (2006.01)

F 1

H01L 29/78 616U

H01L 29/78 616V

H01L 29/78 618B

請求項の数 7 (全 26 頁)

(21) 出願番号 特願2008-76495 (P2008-76495)

(22) 出願日 平成20年3月24日 (2008.3.24)

(65) 公開番号 特開2009-212476 (P2009-212476A)

(43) 公開日 平成21年9月17日 (2009.9.17)

審査請求日 平成20年6月4日 (2008.6.4)

審判番号 不服2008-32688 (P2008-32688/J1)

審判請求日 平成20年12月25日 (2008.12.25)

(31) 優先権主張番号 特願2007-82859 (P2007-82859)

(32) 優先日 平成19年3月27日 (2007.3.27)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2008-25619 (P2008-25619)

(32) 優先日 平成20年2月5日 (2008.2.5)

(33) 優先権主張国 日本国 (JP)

早期審査対象出願

(73) 特許権者 306037311

富士フィルム株式会社

東京都港区西麻布2丁目26番30号

(74) 代理人 100079049

弁理士 中島 淳

(74) 代理人 100084995

弁理士 加藤 和詳

(74) 代理人 100085279

弁理士 西元 勝一

(74) 代理人 100099025

弁理士 福田 浩志

(72) 発明者 中山 昌哉

神奈川県足柄上郡開成町牛島577番地

富士フィルム株式会社内

最終頁に続く

(54) 【発明の名称】薄膜電界効果型トランジスタおよびそれを用いた表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、少なくとも、ゲート電極、ゲート絶縁膜、活性層、ソース電極及びドレイン電極を有する薄膜電界効果型トランジスタであって、

前記活性層が、In、Ga および Zn からなる群より選ばれる少なくとも 1 種若しくはこれらの複合酸化物を含む n 型アモルファス酸化物半導体層であって、

前記活性層と前記ソース電極及び前記ドレイン電極との間に、抵抗層として、In、Ga および Zn からなる群より選ばれる少なくとも 1 種若しくはこれらの複合酸化物を含む n 型アモルファス酸化物半導体層を有し、

前記活性層が前記ゲート絶縁膜と接し、前記抵抗層が前記ソース電極及び前記ドレイン電極と接し、

前記抵抗層の膜厚が 10 nm 以上 100 nm 以下であり、且つ、前記抵抗層の膜厚 / 前記活性層の膜厚比が 1 を越え 10 以下であり、

前記活性層の酸素濃度が前記抵抗層の酸素濃度より低く、

前記活性層の電気伝導度が  $10^{-4} \text{ S cm}^{-1}$  以上  $10^2 \text{ S cm}^{-1}$  未満であり、且つ、前記抵抗層の電気伝導度に対する前記活性層の電気伝導度の比率 (活性層の電気伝導度 / 抵抗層の電気伝導度) が、 $10^1$  以上  $10^{10}$  以下であり、

前記基板上に、前記ゲート電極と、前記ゲート絶縁膜と、前記活性層と、前記抵抗層と、前記ソース電極及び前記ドレイン電極と、をこの順に有する構造であることを特徴とする薄膜電界効果型トランジスタ。

10

20

**【請求項 2】**

前記酸化物半導体が前記InおよびZnを含有し、前記抵抗層のZnとInの組成比( Inに対するZnの比率Zn / Inで表す)が前記活性層の組成比Zn / Inより大きいことを特徴とする請求項1に記載の薄膜電界効果型トランジスタ。

**【請求項 3】**

前記活性層の電気伝導度が $10^{-1} \text{ S cm}^{-1}$ 以上 $10^2 \text{ S cm}^{-1}$ 未満であることを特徴とする請求項1又は請求項2に記載の薄膜電界効果型トランジスタ。

**【請求項 4】**

前記抵抗層の電気伝導度に対する前記活性層の電気伝導度の比率(活性層の電気伝導度 / 抵抗層の電気伝導度)が、 $10^2$ 以上 $10^{10}$ 以下であることを特徴とする請求項1～請求項3のいずれか1項に記載の薄膜電界効果型トランジスタ。10

**【請求項 5】**

前記抵抗層の電気伝導度に対する前記活性層の電気伝導度の比率(活性層の電気伝導度 / 抵抗層の電気伝導度)が、 $10^2$ 以上 $10^8$ 以下であることを特徴とする請求項4に記載の薄膜電界効果型トランジスタ。

**【請求項 6】**

前記基板が可撓性樹脂基板であることを特徴とする請求項1～請求項5のいずれか1項に記載の薄膜電界効果トランジスタ。

**【請求項 7】**

請求項1～請求項6のいずれか1項に記載の薄膜電界効果トランジスタを用いた表示装置。20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、薄膜電界効果型トランジスタおよびそれを用いた表示装置に関する。特に活性層にアモルファス酸化物半導体を用いた薄膜電界効果型トランジスタおよびそれを用いた表示装置に関する。

**【背景技術】****【0002】**

近年、液晶やエレクトロルミネッセンス(ElectroLuminescence: EL)技術等の進歩により、平面薄型画像表示装置(Flat Panel Display: FPD)が実用化されている。特に、電流を通じることによって励起され発光する薄膜材料を用いた有機電界発光素子(以後、「有機EL素子」と記載する場合がある)は、低電圧で高輝度の発光を得るために、携帯電話ディスプレイ、パーソナルデジタルアシスタント(PDA)、コンピュータディスプレイ、自動車の情報ディスプレイ、TVモニター、あるいは一般照明を含む広い分野で、デバイスの薄型化、軽量化、小型化、および省電力の効果などが期待されている。30

これらFPDは、ガラス基板上に設けた非晶質シリコン薄膜や多結晶シリコン薄膜を活性層に用いる電界効果型薄膜トランジスタ(以後の説明で、Thin Film Transistor、もしくはTFTと記載する場合がある)のアクティブマトリクス回路により駆動されている。40

**【0003】**

一方、これらFPDのより一層の薄型化、軽量化、耐破損性の向上を求めて、ガラス基板の替わりに軽量で可撓性のある樹脂基板を用いる試みも行われている。

しかし、上述のシリコン薄膜を用いるトランジスタの製造は、比較的高温の熱工程を要し、一般的に耐熱性の低い樹脂基板上に直接形成することは困難である。

そこで、低温での成膜が可能なアモルファス酸化物、例えば、In-Ga-Zn-O系アモルファス酸化物を半導体薄膜に用いるTFTの開発が活発に行われている(例えば、特許文献1、非特許文献1参照)。

アモルファス酸化物半導体を用いたTFTは、室温成膜が可能であり、フィルム上に作50

製が可能であるので、フィルム（フレキシブル）TFTの活性層の材料として最近注目を浴びている。特に、東工大・細野らにより、a-I<sub>GZO</sub>を用いたTFTは、PEN基板上でも電界効果移動度が約 $10\text{ cm}^2/\text{Vs}$ とガラス上のa-Si系TFTよりも高移動度が報告されて、特にフィルムTFTとして注目されるようになった（例えば、非特許文献2参照）。

#### 【0004】

しかし、このa-I<sub>GZO</sub>を用いたTFTを例えれば表示装置の駆動回路として用いる場合、 $1\text{ cm}^2/\text{Vs} \sim 10\text{ cm}^2/\text{Vs}$ という移動度では、特性は不十分であり、またOFF電流が高く、ON/OFF比が低いという問題がある。特に有機EL素子を用いた表示装置に用いるためには、さらなる移動度の向上、ON/OFF比の向上が要求される。

10

【特許文献1】特開2006-165529号公報

【非特許文献1】IDW/AD'05、845頁-846頁(6 December, 2005)

【非特許文献2】NATURE、Vol. 432(25 November, 2004)

、488頁-492頁

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

本発明の目的は、電界効果移動度が高く、高ON/OFF比を示すアモルファス酸化物半導体を用いた薄膜電界効果型トランジスタを提供することにある。特に、可撓性のある樹脂基板上に作製が可能な高性能の薄膜電界効果型トランジスタを提供することにある。

20

また、その薄膜電界効果型トランジスタを用いた新規な表示装置を提供することにある。

#### 【課題を解決するための手段】

#### 【0006】

本発明の上記課題は下記の手段によって解決された。

<1> 基板上に、少なくとも、ゲート電極、ゲート絶縁膜、活性層、ソース電極及びドレイン電極を有する薄膜電界効果型トランジスタであって、前記活性層が酸化物半導体層であって、前記活性層と前記ソース電極及び前記ドレイン電極の少なくとも一方との間に抵抗層として酸化物半導体層を有し、前記活性層が前記ゲート絶縁膜と接し、前記抵抗層が前記ソース電極及び前記ドレイン電極の少なくとも一方と接し、前記抵抗層の膜厚が前記活性層の膜厚より厚く、前記活性層の電気伝導度が $10^{-4}\text{ S cm}^{-1}$ 以上 $10^2\text{ S cm}^{-1}$ 未満であり、且つ、前記抵抗層の電気伝導度に対する前記活性層の電気伝導度の比率（活性層の電気伝導度 / 抵抗層の電気伝導度）が、 $10^1$ 以上 $10^{10}$ 以下であることを特徴とする薄膜電界効果型トランジスタ。

30

<2> 前記活性層がアモルファス酸化物半導体層であることを特徴とする<1>に記載の薄膜電界効果型トランジスタ。

<3> 前記抵抗層がアモルファス酸化物半導体層であることを特徴とする<1>又は<2>に記載の薄膜電界効果型トランジスタ。

<4> 前記活性層の酸素濃度が前記抵抗層の酸素濃度より低いことを特徴とする<1>～<3>のいずれかに記載の薄膜電界効果型トランジスタ。

40

<5> 前記活性層及び抵抗層の酸化物半導体がIn、GaおよびZnからなる群より選ばれる少なくとも1種若しくはこれらの複合酸化物を含むことを特徴とする<1>～<4>のいずれかに記載の薄膜電界効果型トランジスタ。

<6> 前記酸化物半導体が前記InおよびZnを含有し、前記抵抗層のZnとInの組成比（Inに対するZnの比率Zn/Inで表す）が前記活性層の組成比Zn/Inよりも大きいことを特徴とする<5>に記載の薄膜電界効果型トランジスタ。

<7> 前記活性層の電気伝導度が $10^{-1}\text{ S cm}^{-1}$ 以上 $10^2\text{ S cm}^{-1}$ 未満であることを特徴とする<1>～<6>のいずれかに記載の薄膜電界効果型トランジスタ。

<8> 前記抵抗層の電気伝導度に対する前記活性層の電気伝導度の比率（活性層の電気

50

伝導度 / 抵抗層の電気伝導度 ) が、  $10^2$  以上  $10^{10}$  以下であることを特徴とする < 1 > ~ < 7 > のいずれかに記載の薄膜電界効果型トランジスタ。

< 9 > 前記抵抗層の電気伝導度に対する前記活性層の電気伝導度の比率 ( 活性層の電気伝導度 / 抵抗層の電気伝導度 ) が、  $10^2$  以上  $10^8$  以下であることを特徴とする < 8 > に記載の薄膜電界効果型トランジスタ。

< 10 > 前記基板が可撓性樹脂基板であることを特徴とする < 1 > ~ < 9 > のいずれかに記載の薄膜電界効果トランジスタ。

< 11 > < 1 > ~ < 10 > のいずれかに記載の薄膜電界効果トランジスタを用いた表示装置。

#### 【 0 0 0 7 】

アモルファス酸化物半導体を用いた TFT は、室温成膜が可能であり、可撓性プラスチックフィルムを基板として作製が可能であるので、フィルム (フレキシブル) TFT の活性層の材料として注目された。特に特開 2006 - 165529 号公報で開示されているように、In - Ga - Zn - O 系酸化物を半導体層 (活性層) として用いることにより、電界効果移動度  $10 \text{ cm}^2 / \text{Vs}$  、 ON / OFF 比  $10^3$  超の性能を持つ PET 上に形成された TFT が報告されている。しかしながら、これを例えれば表示装置の駆動回路に用いる場合、移動度、ON / OFF 比の観点から駆動回路を動作するには性能がまだ不十分であった。

それは、従来の技術では、OFF 電流を低減させる為に、活性層の電子キャリア濃度を  $10^{18} / \text{cm}^3$  未満にする必要があった。活性層に用いられるアモルファス酸化物半導体は、電子キャリア濃度が下がると電子移動度が下がる傾向があるので、良好な OFF 特性と、高移動度を両立する TFT を形成することが困難であったからである。

#### 【 0 0 0 8 】

本発明者らは、TFT の電界効果移動度を高め、かつ ON / OFF 比を改良する手段の探索を鋭意進めた。その結果、少なくとも、ゲート電極、ゲート絶縁膜、活性層、ソース電極及びドレイン電極を順次有する薄膜電界効果型トランジスタであって、前記活性層が酸化物半導体層であって、前記活性層と前記ソース電極及び前記ドレイン電極の少なくとも一方との間に抵抗層として酸化物半導体層を有し、前記活性層が前記ゲート絶縁膜と接し、前記抵抗層が前記ソース電極及び前記ドレイン電極の少なくとも一方と接し、前記抵抗層の膜厚が前記活性層の膜厚より厚く、前記活性層の電気伝導度が  $10^{-4} \text{ S cm}^{-1}$  以上  $10^2 \text{ S cm}^{-1}$  未満であり、且つ、前記抵抗層の電気伝導度に対する前記活性層の電気伝導度の比率 (活性層の電気伝導度 / 抵抗層の電気伝導度) が、 $10^1$  以上  $10^{10}$  以下である構成により、課題を解決し得ることを見出し、本発明に到達した。特に、前記基板上に、少なくとも前記抵抗層と前記活性層を層状に有し、前記活性層が前記ゲート絶縁膜と接し、前記抵抗層が前記ソース電極及び前記ドレイン電極の少なくとも一方と接する構成が有効な手段として見出された。

#### 【 発明の効果 】

#### 【 0 0 0 9 】

本発明によると、電界効果移動度が高く、高 ON / OFF 比を示す薄膜電界効果型トランジスタおよびそれを用いた表示装置を提供することができる。特に、可撓性基板を用いたフィルム (フレキシブル) TFT として有用な薄膜電界効果型トランジスタおよびそれを用いた表示装置を提供することができる。

#### 【 発明を実施するための最良の形態 】

#### 【 0 0 1 0 】

##### 1. 薄膜電界効果型トランジスタ

本発明の薄膜電界効果型トランジスタは、少なくとも、ゲート電極、ゲート絶縁膜、活性層、ソース電極及びドレイン電極を順次有し、ゲート電極に電圧を印加して、活性層に流れる電流を制御し、ソース電極とドレイン電極間の電流をスイッチングする機能を有するアクティブ素子である。TFT 構造として、スタガ構造及び逆スタガ構造いずれをも形成することができる。

10

20

30

40

50

## 【0011】

本発明における活性層とソース電極及びドレイン電極の少なくとも一方との間に抵抗層が電気的に接続している。好ましくは、抵抗層の電気伝導度は活性層の電気伝導度より小さい。

好ましくは、前記基板上に少なくとも前記抵抗層と前記活性層を層状に有し、前記活性層の層が前記ゲート絶縁膜と接し、前記抵抗層の層が前記ソース電極及び前記ドレイン電極の少なくとも一方と接する。

好ましくは、前記活性層の電気伝導度が  $10^{-4} \text{ S cm}^{-1}$  以上  $10^2 \text{ S cm}^{-1}$  未満である。より好ましくは  $10^{-1} \text{ S cm}^{-1}$  以上  $10^2 \text{ S cm}^{-1}$  未満である。前記抵抗層の電気伝導度は、好ましくは  $10^{-2} \text{ S cm}^{-1}$  以下、より好ましくは  $10^{-9} \text{ S cm}^{-1}$  以上  $10^{-3} \text{ S cm}^{-1}$  未満であり、前記活性層の電気伝導度より小さい。より好ましくは、抵抗層の電気伝導度に対する活性層の電気伝導度の比率（活性層の電気伝導度 / 抵抗層の電気伝導度）が、 $10^2$  以上  $10^8$  以下である。10

## 【0012】

前記活性層の電気伝導度が  $10^{-4} \text{ S cm}^{-1}$  を下まわると電界効果移動度としては高移動度が得られず、 $10^2 \text{ S cm}^{-1}$  以上では OFF 電流が増加し、良好な ON / OFF 比が得られないで、好ましくない。

また、動作安定性の観点から、抵抗層の膜厚が活性層の膜厚より厚いことが好ましい。

より好ましくは、抵抗層の膜厚 / 活性層の膜厚の比が 1 を超え 100 以下、さらに好ましくは 1 を超え 10 以下である。20

また、別の態様として、抵抗層と活性層の間の電気伝導度が連続的に変化している態様も好ましい。

## 【0013】

活性層及び抵抗層の酸化物半導体は、アモルファス状態であることが好ましい。

好ましくは、活性層の酸化物半導体の酸素濃度が抵抗層の酸化物半導体の酸素濃度より低い。

好ましくは、前記酸化物半導体が In、Ga および Zn からなる群より選ばれる少なくとも 1 種若しくはこれらの複合酸化物を含む。より好ましくは、前記酸化物半導体が前記 In および Zn を含有し、前記抵抗層の Zn と In の組成比（In に対する Zn の比率 Zn / In で表す）が前記活性層の Zn / In 比より大きい。好ましくは、抵抗層の Zn / In 比が活性層の Zn / In 比より 3 % 以上大きく、さらに好ましくは、10 % 以上大きい。30

好ましくは、前記基板が可撓性樹脂基板である。

## 【0014】

## 1) 構造

次に、図面を用いて、詳細に本発明における薄膜電界効果型トランジスタの構造を説明する。

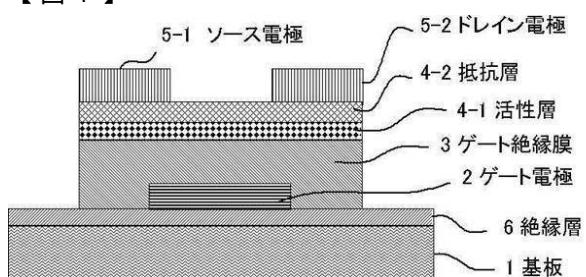

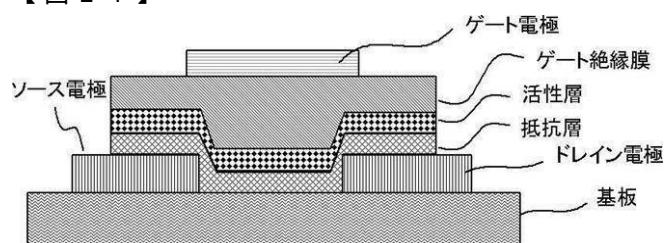

図 1 は、本発明の薄膜電界効果型トランジスタであって、逆スタガ構造の一例を示す模式図である。基板 1 がプラスチックフィルムなどの可撓性基板の場合、基板 1 の一方の面上に絶縁層 6 を配し、その上にゲート電極 2、ゲート絶縁膜 3、活性層 4 - 1、抵抗層 4 - 2 を積層して有し、その表面にソース電極 5 - 1 とドレイン電極 5 - 2 が設置される。活性層 4 - 1 はゲート絶縁膜 3 に接し、抵抗層 4 - 2 はソース電極 5 - 1 およびドレイン電極 5 - 2 に接する。ゲート電極に電圧が印加されていない状態での活性層 4 - 1 の電気伝導度が抵抗層 4 - 2 の電気伝導度より大きくなるように、活性層 4 - 1 および抵抗層 4 - 2 の組成が決定される。ここで、活性層には、特開 2006 - 165529 号公報に開示されている酸化物半導体、例えば In - Ga - Zn - O 系の酸化物半導体を用いる。これらの酸化物半導体は、電子キャリア濃度が高いほど、電子移動度が高くなることが知られている。つまり、電気伝導度が大きいほど、電子移動度が高い。

本発明における構造によれば、薄膜電界効果型トランジスタがゲート電極に電圧が印加された ON の状態では、チャネルとなる活性層が大きい電気伝導度を有しているため、ト50

ランジスタの電界効果移動度は高くなり、高ON電流が得られる。OFFの状態では抵抗層の電気伝導度が小さい為に、抵抗層の抵抗が高いことから、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。

#### 【0015】

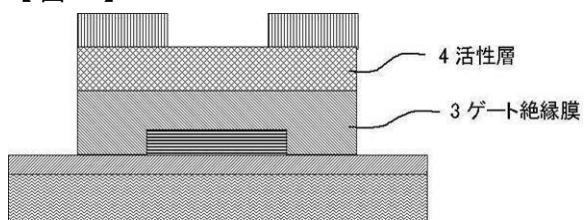

図2は、従来の逆スタガ構造の薄膜電界効果型トランジスタの一例を示す模式図である。

活性層4はその厚み方向に特に電気伝導度の分布を有していない。従来の構成では、OFF電流を低減するために、活性層4の抵抗値を下げる必要がある為に、活性層4のキャリア濃度を下げる必要があった。特開2006-165529号公報によれば、良好なON/OFF比を得るには、活性層4のアモルファス酸化物半導体の伝導度を低減する為に、電子キャリア濃度を $10^{18}/\text{cm}^3$ 未満、より好ましくは $10^{16}/\text{cm}^3$ 未満にすることが開示されている。しかし、特開2006-165529号公報の図2に示されるように、In-Ga-Zn-O系の酸化物半導体では、電子キャリア濃度を下げると膜の電子移動度が減少してしまう。10

その為に、TFTの電界効果移動度で $10\text{ cm}^2/\text{Vs}$ 以上を得ることができず、充分なON電流を得ることができない。そのため、ON/OFF比も充分な特性が得られない。

また、膜の電子移動度を上げるために、活性層4の酸化物半導体の電子キャリア濃度を上げると、活性層4の電気伝導度が増し、OFF電流が増加し、ON/OFF比特性は悪くなる。20

#### 【0016】

図には示してはいないが、本発明の趣旨は、活性層のゲート絶縁膜近傍にある電気伝導度が、活性層のソース電極及びドレイン電極近傍にある電気伝導度より大きくなるように半導体層（本願における半導体層は、活性層及び抵抗層を包含した層を意味する）を設けることにより、その状態が得られる限りその達成手段は図1に示すような複数の半導体層を設けることだけに留まるものではない。連続的に電気伝導度が変化しても良い。

#### 【0017】

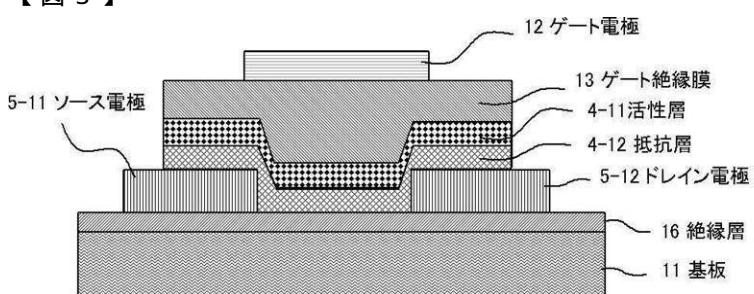

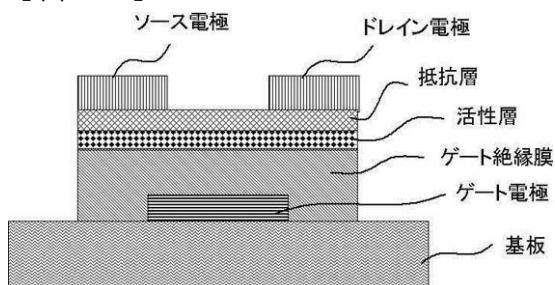

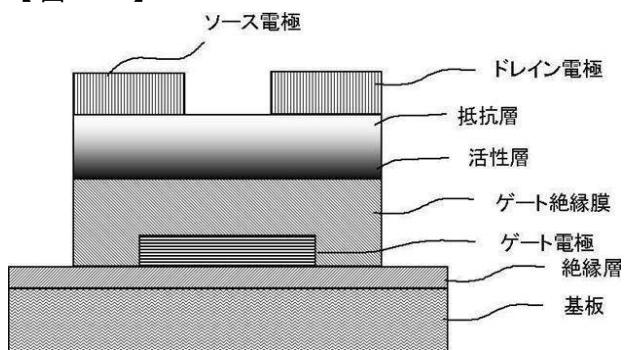

図3は、本発明の薄膜電界効果型トランジスタであって、トップゲート構造の一例を示す模式図である。基板がプラスチックフィルムなどの可撓性基板の場合、基板11の一方の面に絶縁層16を配し、絶縁層上にソース電極5-11とドレイン電極5-12が設置され、抵抗層4-12、活性層4-11を積層した後、ゲート絶縁膜13、ゲート電極12を配する。逆スタガ型構成におけると同様に、活性層4-11（大電気伝導度層）はゲート絶縁膜13に接し、抵抗層4-12（小電気伝導度層）はソース電極5-11およびドレイン電極5-12に接する。ゲート電極に電圧が印加されていない状態での活性層4-11の電気伝導度が抵抗層4-12の電気伝導度より大きくなるように、活性層4-11および抵抗層4-12の組成が決定される。30

#### 【0018】

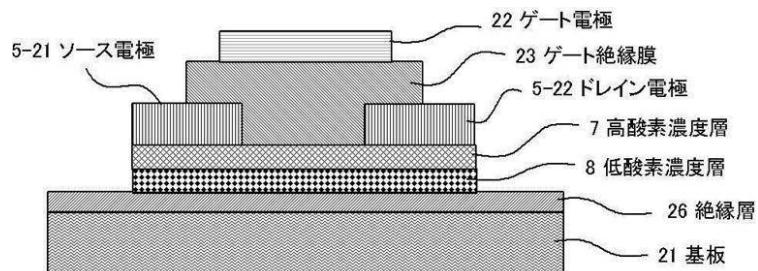

図4は、比較のトップゲート構造薄膜電界効果型トランジスタの一例を示す模式図である。特許文献1として先に提出した特開2006-165529号公報に開示されているように、活性層として高酸素濃度層7と低酸素濃度層8の2層より形成される。高酸素濃度層7は電子キャリア濃度の低い層、つまり電気伝導度の小さい層であり、低酸素濃度層8は電子キャリア濃度の高い層、つまり電気伝導度の大きい層である。従って、この比較の構造では、チャネルとなるゲート絶縁膜23と接した活性層が電子キャリア濃度が低く、電子移動度も低い膜である為、電界効果移動度においても高移動度は達成できない。40

#### 【0019】

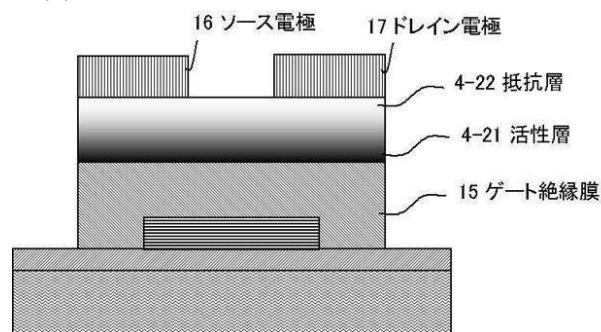

図6は、参考の薄膜電界効果型トランジスタの構成であって、トップゲート構造の一例を示す模式図である。半導体層の電気伝導度が層内で連続的にゲート絶縁膜に接する領域で大きく、ソース・ドレイン電極に接する領域で小さくなるよう変化している構成である。ゲート絶縁膜15に近接した活性層領域4-21の電気伝導度が高く、ソース電極16、ドレイン電極17に近接した領域では電気伝導度が小さく抵抗層4-22を形成する。50

このような構成の半導体層は、半導体層を蒸着する際のターゲット化合物のスパッタリング条件を連続的に変えることによって作製することができる。

#### 【0020】

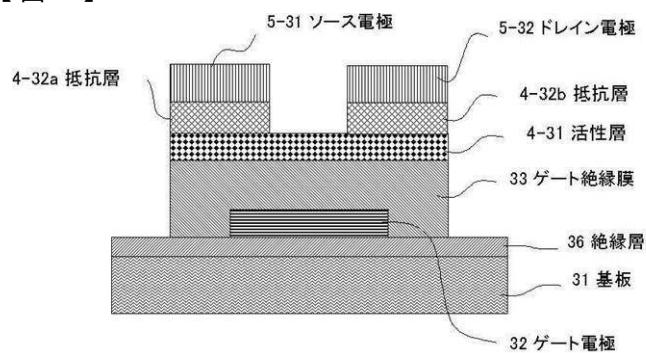

図7は、本発明の薄膜電界効果型トランジスタの別の構成であって、逆スタガ構造の一例を示す模式図である。ゲート絶縁膜33上に、活性層4-31が形成され、抵抗層はパターニングされてソース電極5-31およびドレイン電極5-32が設けられる領域にのみにそれぞれ抵抗層4-32a、4-32bを積層される。ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-31が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、ソース電極5-31およびドレイン電極5-32と活性層4-31との間に電気抵抗の大きな抵抗層4-32aおよび抵抗層4-32bが介在することによって、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。

10

#### 【0021】

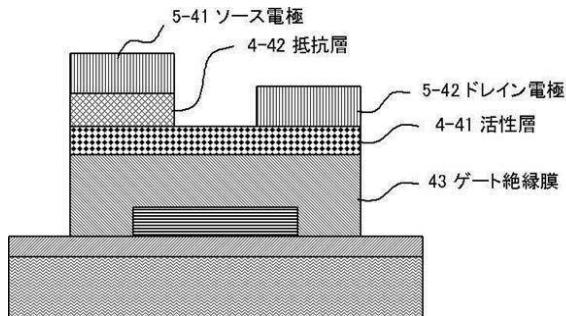

図8は、本発明の薄膜電界効果型トランジスタの別の構成であって、逆スタガ構造の一例を示す模式図である。ゲート絶縁膜43上に、活性層4-41が形成され、抵抗層4-42はパターニングされてソース電極5-41が設けられる領域にのみに積層される。ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-41が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、ソース電極5-41と活性層4-41との間に電気抵抗の大きな抵抗層4-42が介在することによって、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。尚、図8において、ソース電極5-41とドレイン電極5-42とが入れ替わった構成（ドレイン電極5-42と抵抗層4-42とが接続された構成）でももちろん良い。

20

#### 【0022】

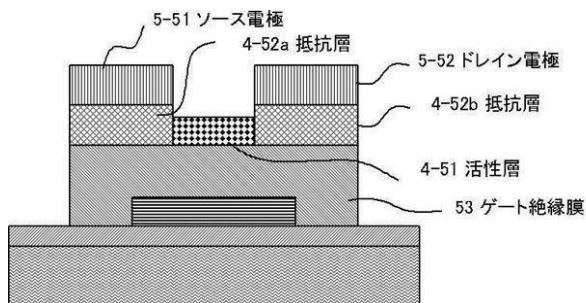

図9は、本発明の薄膜電界効果型トランジスタの別の構成であって、逆スタガ構造の一例を示す模式図である。ゲート絶縁膜53上に、抵抗層4-52a、4-52b、および活性層4-51がパターニングされてソース電極5-51、ドレイン電極5-52が設けられる領域に、抵抗層4-52aおよび4-52bを配置し、抵抗層4-52aと4-52bの間に活性層4-51が配置される。即ち、活性層4-51はソース電極5-51およびドレイン電極5-52と直接電気的に連結することなく、抵抗層4-52aおよび4-52bを介して接続する。

30

ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-51が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、電気抵抗の大きな抵抗層4-52aおよび4-52bによって、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。

40

#### 【0023】

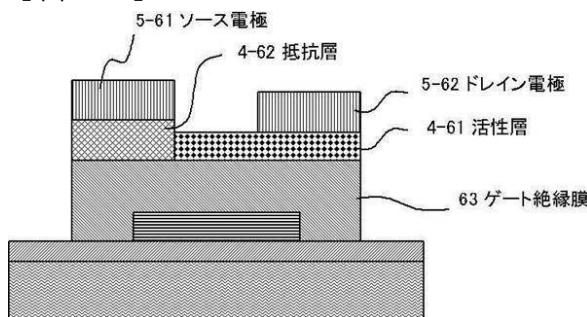

図10は、本発明の薄膜電界効果型トランジスタの別の構成であって、逆スタガ構造の一例を示す模式図である。ゲート絶縁膜63上に、抵抗層4-62、および活性層4-61がパターニングされてソース電極5-61が設けられる領域に、抵抗層4-62を配置し、抵抗層4-62が配置された箇所を除いて活性層4-61が配置される。この構成では、活性層4-61はソース電極5-61と直接電気的に連結することなく、抵抗層4-62を介して接続する。

ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-61が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、電気抵抗の大きな抵抗層4-62によって、OFF

50

電流が低く保たれるために、ON/OFF 比特性が極めて改良される。尚、図10において、ソース電極5-61とドレイン電極5-62とが入れ替わった構成（ドレイン電極5-62と抵抗層4-62とが接続された構成）でももちろん良い。

#### 【0024】

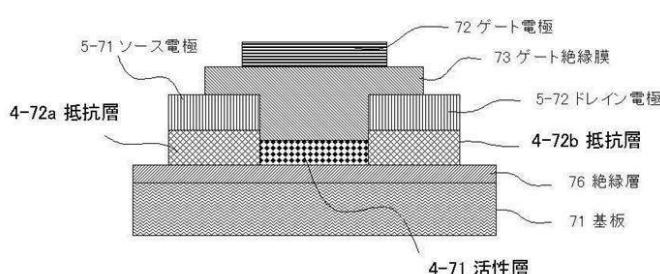

図11は、本発明の薄膜電界効果型トランジスタの別の構成であって、トップゲート構造の一例を示す模式図である。絶縁層76の上に、抵抗層4-72a、4-72b、および活性層4-71がパターニングされてソース電極5-71、ドレイン電極5-72が設けられる領域に、抵抗層4-72aおよび4-72bを配置し、抵抗層4-72aおよび4-72bが配置された箇所を除いて活性層4-71が配置される。この構成では、活性層4-71はソース電極5-71およびドレイン電極5-72と直接電気的に連結することなく、抵抗層4-72aおよび4-72bを介して接続する。

10

ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-71が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、電気抵抗の大きな抵抗層4-72aおよび4-72bによって、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。

。

#### 【0025】

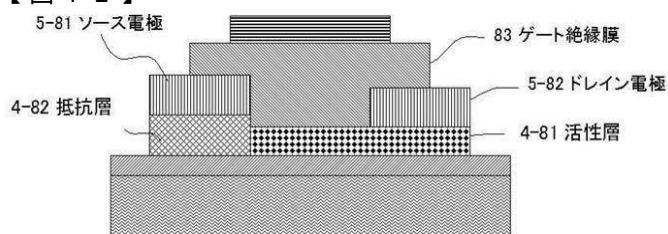

図12は、本発明の薄膜電界効果型トランジスタの別の構成であって、トップゲート構造の一例を示す模式図である。抵抗層4-82および活性層4-81がパターニングされてソース電極5-81が設けられる領域に、抵抗層4-82を配置し、抵抗層4-82が配置された箇所を除いて活性層4-81が配置される。この構成では、活性層4-81はソース電極5-81と直接電気的に連結することなく、抵抗層4-82を介して接続する。

20

ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-81が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、電気抵抗の大きな抵抗層4-82によって、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。尚、図12において、ソース電極5-81とドレイン電極5-82とが入れ替わった構成（ドレイン電極5-82と抵抗層4-82とが接続された構成）でももちろん良い。

30

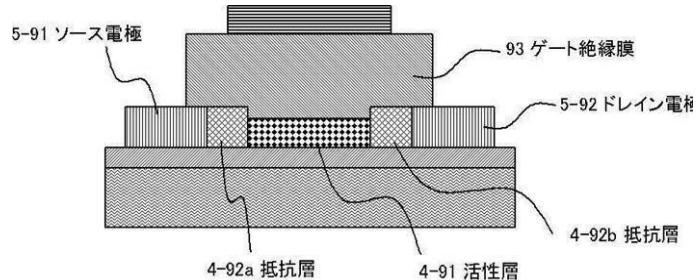

#### 【0026】

図13は、本発明の薄膜電界効果型トランジスタの別の構成であって、トップゲート構造の一例を示す模式図である。絶縁層の上に、抵抗層4-92a、4-92b、および活性層4-91がパターニングされて、配列がソース電極5-91/抵抗層4-92a/活性層4-91/抵抗層4-92b/ドレイン電極5-92となるように配置される。この構成では、活性層4-91はソース電極5-91およびドレイン電極5-92と直接電気的に連結することなく、抵抗層4-92aおよび4-92bを介して接続する。

ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-91が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、電気抵抗の大きな抵抗層4-92aおよび4-92bによって、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。

40

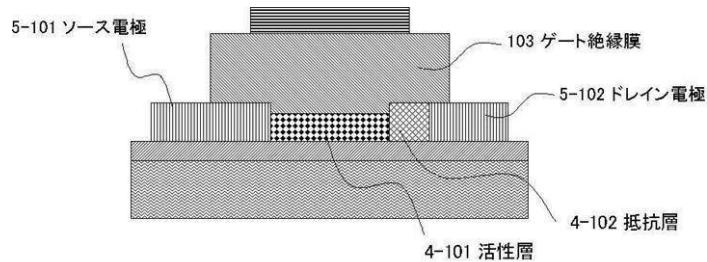

#### 【0027】

図14は、本発明の薄膜電界効果型トランジスタの別の構成であって、トップゲート構造の一例を示す模式図である。絶縁層の上に、抵抗層4-102、および活性層4-101がパターニングされて、配列がソース電極5-101/活性層4-101/抵抗層4-102/ドレイン電極5-102となるように配置される。この構成では、活性層4-101はドレイン電極5-102と直接電気的に連結することなく、抵抗層4-102を介

50

して接続する。

ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-101が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、電気抵抗の大きな抵抗層4-102によって、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。尚、図14において、ソース電極5-101とドレイン電極5-102とが入れ替わった構成（ソース電極5-101と抵抗層4-102とが接続された構成）でももちろん良い。

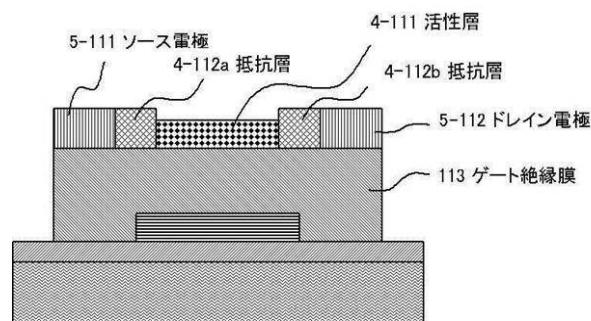

#### 【0028】

図15は、本発明の薄膜電界効果型トランジスタの別の構成であって、逆スタガ構造の一例を示す模式図である。ゲート絶縁膜113の上に、抵抗層4-112a、4-112b、および活性層4-111がパターニングされて、配列がソース電極5-111/抵抗層4-112a/活性層4-111/抵抗層4-112b/ドレイン電極5-112となるように配置される。この構成では、活性層4-111はソース電極5-111およびドレイン電極5-112と直接電気的に連結することなく、抵抗層4-112aおよび4-112bを介して接続する。

ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-111が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、電気抵抗の大きな抵抗層4-112aおよび4-112bによって、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。

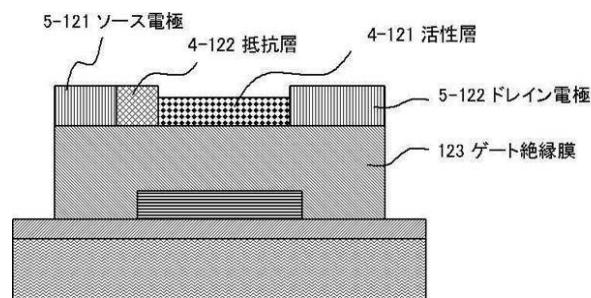

#### 【0029】

図16は、本発明の薄膜電界効果型トランジスタの別の構成であって、逆スタガ構造の一例を示す模式図である。ゲート絶縁膜123の上に、抵抗層4-122、および活性層4-121がパターニングされて、配列がソース電極5-121/抵抗層4-122/活性層4-121/ドレイン電極5-122となるように配置される。この構成では、活性層4-121はソース電極5-121と直接電気的に連結することなく、抵抗層4-122を介して接続する。

ゲート電極に電圧が印可されてチャネルが形成されON状態になった場合、チャネルとなる活性層4-121が大きい電気伝導度を有しているため、トランジスタの電界効果移動度は高くなり、高ON電流が得られる。ゲート電極に電圧が印可されておらず、チャネルが形成されていないOFF状態では、電気抵抗の大きな抵抗層4-122によって、OFF電流が低く保たれるために、ON/OFF比特性が極めて改良される。尚、図16において、ソース電極5-121とドレイン電極5-122とが入れ替わった構成（ドレイン電極5-122と抵抗層4-122とが接続された構成）でももちろん良い。

#### 【0030】

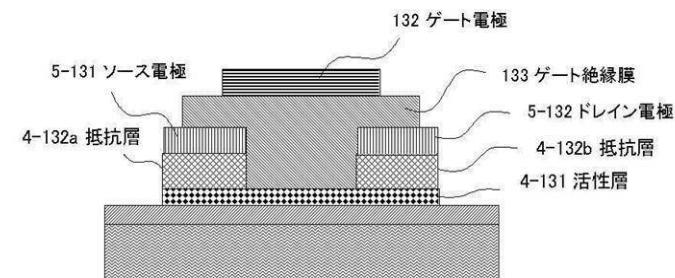

図17は、本発明の薄膜電界効果型トランジスタの別の構成であって、トップゲート構造の一例を示す模式図である。絶縁層の上に、活性層4-131を有し、その上に抵抗層4-132a、4-132bがパターニングされて、ソース電極5-131と活性層4-131の間に抵抗層4-132a、ドレイン電極5-132と活性層4-131の間に抵抗層4-132bが配置される。この構成では、活性層4-131はソース電極5-131およびドレイン電極5-132と直接電気的に連結することなく、抵抗層4-132a、4-132bを介して接続する。従って、同様に上述の本発明の効果が得られる。

#### 【0031】

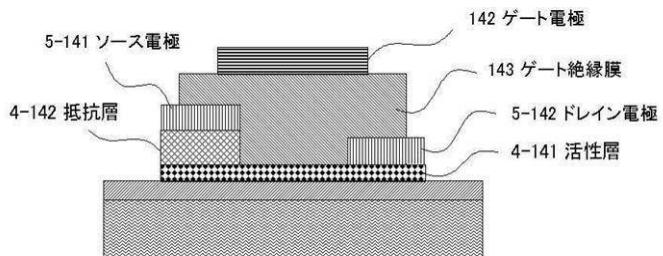

図18は、本発明の薄膜電界効果型トランジスタの別の構成であって、トップゲート構造の一例を示す模式図である。絶縁層の上に、活性層4-141を有し、その上に抵抗層4-142がパターニングされて、ソース電極5-141と活性層4-141の間に配置される。この構成では、活性層4-141はソース電極5-141と直接電気的に連結することなく、抵抗層4-142を介して接続する。従って、同様に上述の本発明の効果が

10

20

30

40

50

得られる。尚、図18において、ソース電極5-141とドレイン電極5-142とが入れ替わった構成（ドレイン電極5-142と抵抗層4-142とが接続された構成）でももちろん良い。

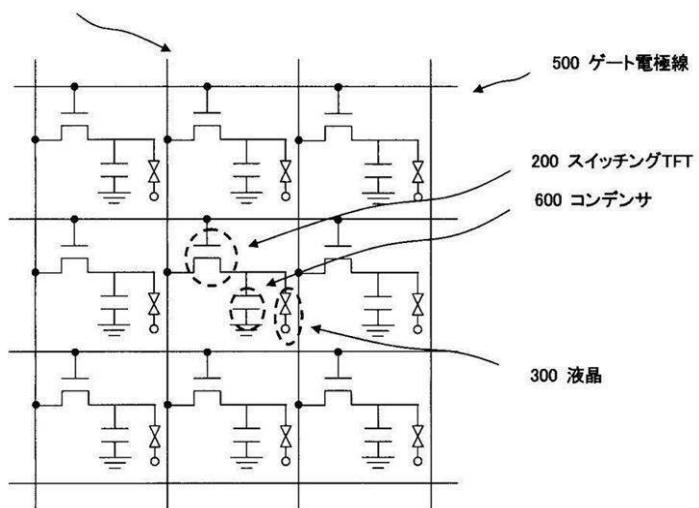

### 【0032】

図19は、本発明のTFT素子を用いたアクティブマトリクス駆動型液晶表示装置の等価回路の模式図である。本発明における表示装置の回路は、特に図19に示すものに限定されるものではなく、従来公知の回路をそのまま応用することができる。

### 【0033】

#### 2) 電気伝導度

本発明における活性層及び抵抗層の電気伝導度について説明する。

10

電気伝導度とは、物質の電気伝導のしやすさを表す物性値であり、物質のキャリア濃度n、電荷素量をe、キャリア移動度μとすると物質の電気伝導度は以下の式で表される。

$$= n e \mu$$

活性層がn型半導体である時は、キャリアは電子であり、キャリア濃度とは電子キャリア濃度を、キャリア移動度とは電子移動度を示す。同様に活性層がp型半導体ではキャリアは正孔であり、キャリア濃度とは、正孔キャリア濃度を、キャリア移動度とは正孔移動度を示す。尚、物質のキャリア濃度とキャリア移動度とは、ホール測定により求めることができる。

### 【0034】

20

#### <電気伝導度の求め方>

厚みが分かっている膜のシート抵抗を測定することにより、膜の電気伝導度を求めることができる。半導体の電気伝導度は温度により変化するが、本文記載の電気伝導度は、室温(20)での電気伝導度を示す。

### 【0035】

#### 3) ゲート絶縁膜

ゲート絶縁膜としては、 $\text{SiO}_2$ 、 $\text{SiN}_x$ 、 $\text{SiON}$ 、 $\text{Al}_2\text{O}_3$ 、 $\text{Y}_2\text{O}_3$ 、 $\text{Ta}_2\text{O}_5$ 、 $\text{HfO}_2$ 等の絶縁体、又はそれらの化合物を少なくとも二つ以上含む混晶化合物が用いられる。また、ポリイミドのような高分子絶縁体もゲート絶縁膜として用いることができる。

30

### 【0036】

ゲート絶縁膜の膜厚としては $10\text{ nm} \sim 10\text{ }\mu\text{m}$ が好ましい。ゲート絶縁膜はリーク電流を減らす、電圧耐性を上げる為に、ある程度膜厚を厚くする必要がある。しかし、ゲート絶縁膜の膜厚を厚くすると、TFTの駆動電圧の上昇を招く結果となる。その為、ゲート絶縁膜の膜厚は無機絶縁体だと $50\text{ nm} \sim 1000\text{ nm}$ 、高分子絶縁体だと $0.5\text{ }\mu\text{m} \sim 5\text{ }\mu\text{m}$ で用いられることが、より好ましい。特に、 $\text{HfO}_2$ のような高誘電率絶縁体をゲート絶縁膜に用いると、膜厚を厚くしても、低電圧でのTFT駆動が可能であるので、特に好ましい。

### 【0037】

#### 4) 活性層、抵抗層

40

本発明に用いられる活性層及び抵抗層には、酸化物半導体が用いられる。特にアモルファス酸化物半導体が好ましい。酸化物半導体、特にアモルファス酸化物半導体は、低温で成膜可能である為に、プラスティックのような可撓性のある樹脂基板に作製が可能である。低温で作製可能な良好なアモルファス酸化物半導体としては、特開2006-165529号公報に開示されているような、Inを含む酸化物、InとZnを含む酸化物、In、Ga及びZnを含有する酸化物であり、組成構造としては、 $\text{InGaO}_3(\text{ZnO})_m$ (mは6未満の自然数)のものが好ましいことが知られている。これらは、キャリアが電子のn型半導体である。

### 【0038】

具体的に本発明に係るアモルファス酸化物半導体は、In-Ga-Zn-Oを含み構成

50

され、結晶状態における組成が  $InGaO_3(ZnO)_m$  ( $m$  は 6 未満の自然数) で表されるアモルファス酸化物半導体が好ましい。特に、 $InGaZnO_4$  がより好ましい。この組成のアモルファス酸化物半導体の特徴としては、電気伝導度が増加するにつれ、電子移動度が増加する傾向を示す。また、電気伝導度を制御するには、成膜中の酸素分圧により制御が可能であることが特開 2006-165529 号公報に開示されている。

もちろん、活性層及び抵抗層には酸化物半導体だけではなく、Si、Geなどの無機半導体、GaAs 等の化合物半導体、ペンタセン、ポリチオフェン等の有機半導体材料、カーボンナノチューブ等にも適応可能である。

#### 【0039】

##### <活性層及び抵抗層の電気伝導度>

本発明における活性層は、ゲート絶縁膜に近接し、ソース電極及びドレイン電極に近接する抵抗層より高い電気伝導度を有することを特徴とする。

抵抗層の電気伝導度に対する活性層の電気伝導度の比率（活性層の電気伝導度 / 抵抗層の電気伝導度）は、 $10^1$  以上  $10^{10}$  以下であり、好ましくは、 $10^2$  以上  $10^{10}$  以下であり、より好ましくは、 $10^2$  以上  $10^8$  以下である。前記活性層の電気伝導度が、 $10^{-4} \text{ S cm}^{-1}$  以上  $10^2 \text{ S cm}^{-1}$  未満である。好ましくは、 $10^{-1} \text{ S cm}^{-1}$  以上  $10^2 \text{ S cm}^{-1}$  未満である。

抵抗層の電気伝導度は、好ましくは  $10^{-2} \text{ S cm}^{-1}$  以下、より好ましくは  $10^{-9} \text{ S cm}^{-1}$  以上  $10^{-3} \text{ S cm}^{-1}$  以下である。

#### 【0040】

##### <活性層と抵抗層の膜厚>

抵抗層の膜厚が活性層の膜厚より厚いことが好ましい。より好ましくは、抵抗層の膜厚 / 活性層の膜厚比が 1 を越え  $100$  以下、さらに好ましくは 1 を越え  $10$  以下である。

活性層の膜厚は、 $1 \text{ nm}$  以上  $100 \text{ nm}$  以下が好ましく、より好ましくは  $2.5 \text{ nm}$  以上  $30 \text{ nm}$  以下である。抵抗層の膜厚は、 $5 \text{ nm}$  以上  $500 \text{ nm}$  以下が好ましく、より好ましくは  $10 \text{ nm}$  以上  $100 \text{ nm}$  以下である。

#### 【0041】

上記の構成の活性層及び抵抗層を用いることにより、移動度が  $10 \text{ cm}^2 / (\text{V} \cdot \text{秒})$  以上の高い移動度の TFT で、オン・オフ比が  $10^6$  以上のトランジスタ特性を実現できる。

#### 【0042】

##### <電気伝導度の調整手段>

電気伝導度の調整手段としては、活性層及び抵抗層が酸化物半導体である場合は下記の手段を挙げることが出来る。

#### 【0043】

##### (1) 酸素欠陥による調整

酸化物半導体において、酸素欠陥ができると、キャリア電子が発生し、電気伝導度が大きくなることが知られている。よって、酸素欠陥量を調整することにより、酸化物半導体の電気伝導度を制御することが可能である。酸素欠陥量を制御する具体的な方法としては、成膜中の酸素分圧、成膜後の後処理時の酸素濃度と処理時間等がある。ここでいう後処理とは、具体的に  $100$  以上の熱処理、酸素プラズマ、UV オゾン処理がある。これらの方法の中でも、生産性の観点から成膜中の酸素分圧を制御する方法が好ましい。成膜中の酸素分圧を調整することにより、酸化物半導体の電気伝導度の制御ができるることは、特開 2006-165529 号公報に開示されており、本手法を利用することができる。

#### 【0044】

##### (2) 組成比による調整

酸化物半導体の金属組成比を変えることにより、電気伝導度が変化することが知られている。例えば、 $InGaZn_{1-x}Mg_xO_4$  において、Mg の比率が増えていくと、電気伝導度が小さくなることが、特開 2006-165529 号公報に開示されている。また、 $(In_2O_3)_{1-x}(ZnO)_x$  の酸化物系において、Zn / In 比が  $10\%$  以上

10

20

30

40

50

では、 $Zn$ 比率が増加するにつれ、電気伝導度が小さくなることが報告されている（「透明導電膜の新展開II」シーエムシー出版 P. 34 - 35）。これら組成比を変える具体的な方法としては、例えば、スパッタによる成膜方法においては、組成比が異なるターゲットを用いる。または、多元のターゲットにより、共スパッタし、そのスパッタレートを個別に調整することにより、膜の組成比を変えることが可能である。

#### 【0045】

##### (3) 不純物による調整

酸化物半導体に、Li, Na, Mn, Ni, Pd, Cu, Cd, C, N, 又はP等の元素を不純物として添加することにより、電子キャリア濃度を減少させること、つまり電気伝導度を小さくすることが可能であることが、特開2006-165529号公報に開示されている。不純物を添加する方法としては、酸化物半導体と不純物元素とを共蒸着により行う、成膜された酸化物半導体膜に不純物元素のイオンをイオンドープ法により行う等がある。

10

#### 【0046】

##### (4) 酸化物半導体材料による調整

上記(1)～(3)においては、同一酸化物半導体系での電気伝導度の調整方法を述べたが、もちろん酸化物半導体材料を変えることにより、電気伝導度を変えることができる。例えば、一般的にSnO<sub>2</sub>系酸化物半導体は、In<sub>2</sub>O<sub>3</sub>系酸化物半導体に比べて電気伝導度が小さいことが知られている。このように酸化物半導体材料を変えることにより、電気伝導度の調整が可能である。特に電気伝導度の小さい酸化物材料としては、Al<sub>2</sub>O<sub>3</sub>、Ga<sub>2</sub>O<sub>3</sub>、ZrO<sub>2</sub>、Y<sub>2</sub>O<sub>3</sub>、Ta<sub>2</sub>O<sub>3</sub>、MgO、又はHfO<sub>2</sub>等の酸化物絶縁体材料が知られており、これらを用いることも可能である。

20

電気伝導度を調整する手段としては、上記(1)～(4)の方法を単独に用いても良いし、組み合わせても良い。

#### 【0047】

##### <活性層及び抵抗層の形成方法>

活性層及び抵抗層の成膜方法は、酸化物半導体の多結晶焼結体をターゲットとして、気相成膜法を用いるのが良い。気相成膜法の中でも、スパッタリング法、パルスレーザー蒸着法(PLD法)が適している。さらに、量産性の観点から、スパッタリング法が好ましい。

30

#### 【0048】

例えば、RFマグネットロンスパッタリング蒸着法により、真空度及び酸素流量を制御して成膜される。酸素流量が多いほど電気伝導度を小さくすることができる。

#### 【0049】

成膜した膜は、周知のX線回折法によりアモルファス膜であることが確認できる。

また、膜厚は触針式表面形状測定により求めることができる。組成比は、RBS(ラザフォード後方散乱)分析法により求めることができる。

#### 【0050】

##### 5) ゲート電極

本発明におけるゲート電極としては、例えば、Al、Mo、Cr、Ta、Ti、Au、またはAg等の金属、Al-Nd、APC等の合金、酸化錫、酸化亜鉛、酸化インジウム、酸化インジウム錫(ITO)、酸化亜鉛インジウムIZO等の金属酸化物導電膜、ポリアニリン、ポリチオフェン、ポリピロ-ルなどの有機導電性化合物、またはこれらの混合物を好適に挙げられる。

40

ゲート電極の厚みは、10nm以上1000nm以下とすることが好ましい。

#### 【0051】

ゲート電極の成膜法は特に限定されることはなく、印刷方式、コ-ティング方式等の湿式方式、真空蒸着法、スパッタリング法、イオンプレ-ティング法等の物理的方式、CVD、プラズマCVD法等の化学的方式、などの中から前記材料との適性を考慮して適宜選択した方法に従って前記基板上に形成することができる。例えば、ITOを選択する場合

50

には、直流あるいは高周波スパッタリング法、真空蒸着法、イオンプレ - ティング法等に従って行うことができる。またゲート電極の材料として有機導電性化合物を選択する場合には湿式製膜法に従って行うことができる。

#### 【0052】

##### 6) ソース電極及びドレイン電極

本発明におけるソース電極及びドレイン電極材料として、例えば、Al、Mo、Cr、Ta、Ti、Au、またはAg等の金属、Al-Nd、APC等の合金、酸化錫、酸化亜鉛、酸化インジウム、酸化インジウム錫(ITO)、酸化亜鉛インジウム(IZO)等の金属酸化物導電膜、ポリアニリン、ポリチオフェン、ポリピロ - ルなどの有機導電性化合物、またはこれらの混合物を好適に挙げられる。

ソース電極及びドレイン電極の厚みは、10nm以上1000nm以下とすることが好みしい。

#### 【0053】

ソース電極及びドレイン電極の製膜法は特に限定されることはなく、印刷方式、コ - ティング方式等の湿式方式、真空蒸着法、スパッタリング法、イオンプレ - ティング法等の物理的方式、CVD、プラズマCVD法等の化学的方式、などの中から前記材料との適性を考慮して適宜選択した方法に従って前記基板上に形成することができる。例えば、ITOを選択する場合には、直流あるいは高周波スパッタリング法、真空蒸着法、イオンプレ - ティング法等に従って行うことができる。またソース電極及びドレイン電極の材料として有機導電性化合物を選択する場合には湿式製膜法に従って行うことができる。

#### 【0054】

##### 7) 基板

本発明に用いられる基板は特に限定されることはなく、例えばYSZ(ジルコニア安定化イットリウム)、ガラス等の無機材料、ポリエチレンテレフタレ - ト、ポリブチレンテレフタレ - ト、ポリエチレンナフタレ - ト等のポリエステル、ポリスチレン、ポリカ - ボネ - ト、ポリエ - テルスルホン、ポリアリレ - ト、アリルジグリコ - ルカ - ボネ - ト、ポリイミド、ポリシクロオレフィン、ノルボルネン樹脂、ポリ(クロロトリフルオロエチレン)等の合成樹脂等の有機材料、などが挙げられる。前記有機材料の場合、耐熱性、寸法安定性、耐溶剤性、電気絶縁性、加工性、低通気性、又は低吸湿性等に優れていることが好みしい。

#### 【0055】

本発明においては特に可撓性基板が好みしく用いられる。可撓性基板に用いる材料としては、透過率の高い有機プラスチックフィルムが好みしく、例えばポリエチレンテレフタレート、ポリブチレンフタレート、ポリエチレンナフタレート等のポリエステル、ポリスチレン、ポリカーボネート、ポリエーテルスルホン、ポリアリレート、ポリイミド、ポリシクロオレフィン、ノルボルネン樹脂、ポリ(クロロトリフルオロエチレン)等のプラスティックフィルムを用いることができる。また、フィルム状プラスティック基板には、絶縁性が不十分の場合は絶縁層、水分や酸素の透過を防止するためのガスバリア層、フィルム状プラスティック基板の平坦性や電極や活性層との密着性を向上するためのアンダーコート層等を備えることも好みしい。

#### 【0056】

ここで、可撓性基板の厚みは、50μm以上500μm以下とすることが好みしい。これは、可撓性基板の厚みを50μm未満とした場合には、基板自体が十分な平坦性を保持することが難しいためである。また、可撓性基板の厚みを500μmよりも厚くした場合には、基板自体を自由に曲げることが困難になる、すなわち基板自体の可撓性が乏しくなるためである。

#### 【0057】

##### 8) 保護絶縁膜

必要によって、TFT上に保護絶縁膜を設けても良い。保護絶縁膜は、活性層または抵抗層の半導体層を大気による劣化から保護する目的や、TFT上に作製される電子デバイ

10

20

30

40

50

スとを絶縁する目的がある。

#### 【0058】

その具体例としては、MgO、SiO、SiO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub>、GeO、NiO、CaO、BaO、Fe<sub>2</sub>O<sub>3</sub>、Y<sub>2</sub>O<sub>3</sub>、又はTiO<sub>2</sub>等の金属酸化物、SiN<sub>x</sub>、SiN<sub>x</sub>O<sub>y</sub>等の金属窒化物、MgF<sub>2</sub>、LiF、AlF<sub>3</sub>、又はCaF<sub>2</sub>等の金属フッ化物、ポリエチレン、ポリプロピレン、ポリメチルメタクリレート、ポリイミド、ポリウレア、ポリテトラフルオロエチレン、ポリクロロトリフルオロエチレン、ポリジクロロジフルオロエチレン、クロロトリフルオロエチレンとジクロロジフルオロエチレンとの共重合体、テトラフルオロエチレンと少なくとも1種のコモノマーとを含むモノマー混合物を共重合させて得られる共重合体、共重合主鎖に環状構造を有する含フッ素共重合体、吸水率1%以上の吸水性物質、吸水率0.1%以下の防湿性物質等が挙げられる。10

#### 【0059】

保護絶縁膜の形成方法については、特に限定はなく、例えば、真空蒸着法、スパッタリング法、反応性スパッタリング法、MBE(分子線エピタキシ)法、クラスターイオンビーム法、イオンプレーティング法、プラズマ重合法(高周波励起イオンプレーティング法)、プラズマCVD法、レーザーCVD法、熱CVD法、ガスソースCVD法、コーティング法、印刷法、又は転写法を適用できる。

#### 【0060】

##### 9) 後処理

必要によって、TFTの後処理として、熱処理を行っても良い。熱処理としては、温度100以上で、大気下または窒素雰囲気下で行う。熱処理を行う工程としては、半導体層を成膜後でも良いし、TFT作製工程の最後に行っても良い。熱処理を行うことにより、TFTの特性の面内バラつきが抑制される、駆動安定性が向上する等の効果がある。20

#### 【0061】

##### 2. 表示装置

本発明の電界効果型薄膜トランジスタは、液晶やEL素子を用いた画像表示装置、特に平面薄型表示装置(Flat Panel Display: FPD)に好ましく用いられる。より好ましくは、基板に有機プラスチックフィルムのような可撓性基板を用いたフレキシブル表示装置に用いられる。特に、本発明の電界効果型薄膜トランジスタは、移動度が高いことから有機EL素子を用いた表示装置、フレキシブル有機EL表示装置に最も好ましく用いられる。30

#### 【0062】

##### (応用)

本発明の電界効果型薄膜トランジスタは、液晶やEL素子を用いた画像表示装置、特にFPDのスイッチング素子、駆動素子として用いることができる。特に、フレキシブルFPD装置のスイッチング素子、駆動素子として用いるのが適している。さらに本発明の電界効果型薄膜トランジスタを用いた表示装置は、携帯電話ディスプレイ、パーソナルデジタルアシスタント(PDA)、コンピュータディスプレイ、自動車の情報ディスプレイ、TVモニター、あるいは一般照明を含む広い分野で幅広い分野で応用される。

また、本発明の電界効果型薄膜トランジスタは、表示装置以外にも、有機プラスチックフィルムのような可撓性基板上に本発明の電界効果型薄膜トランジスタを形成し、I CカードやIDタグなどに幅広く応用が可能である。40

#### 【実施例】

#### 【0063】

以下に、本発明の薄膜電界効果型トランジスタについて、実施例により説明するが、本発明はこれら実施例により何ら限定されるものではない。

#### 【0064】

##### 実施例1

##### 1. 活性層及び抵抗層の作製

<条件1>

50

InGaZnO<sub>4</sub>の組成を有する多結晶焼結体をターゲットとして、RFマグネットロンスパッタ真空蒸着法により、Ar流量1.2 sccm、O<sub>2</sub>流量0.2 sccm、RFパワー200W、圧力0.4 Paの条件で行った。

<条件2>

条件1と同様に、但しO<sub>2</sub>流量を0.6 sccmに変更して行った。

<条件3>

条件1と同様に、但しO<sub>2</sub>流量を1.4 sccmに変更して行った。

<条件4>

条件1と同様に、但しO<sub>2</sub>流量を1.5 sccmに変更して行った。

<条件5>

条件1と同様に、但しO<sub>2</sub>流量を1.8 sccmに変更して行った。

【0065】

上記条件1～5とで同一条件で上記無アルカリガラス基板（コーニング社、品番NO.1737）に直接これらの層を100nm設けた物性測定用サンプルを作製した。これらの物性測定用サンプルを周知のX線回折法により分析した結果、これらの膜はアモルファス膜であることが確認できた。また、これらの物性測定用サンプルの電気伝導度および、ホール測定法によるキャリア濃度、及び組成比を測定した。得られた結果を表1に示す。

【0066】

-電気伝導度の測定方法-

物性測定用サンプルの電気伝導度は、サンプルの測定されたシート抵抗と膜厚から計算し求めた。ここで、シート抵抗を( / )、膜厚をd(cm)とすると、電気伝導度(S cm<sup>-1</sup>)は、=1/( \* d)として算出される。

本実施例において、物性測定用サンプルのシート抵抗10<sup>7</sup>/未満の領域ではロレスター-GP（三菱化学社製）、シート抵抗10<sup>7</sup>/以上の領域ではハイテスター-UP（三菱化学社製）を用いて20の環境下で行った。物性測定用サンプルの膜厚測定には触針式表面形状測定器DekTak-6M（ULVAC社製）を用いた。

【0067】

-ホール効果測定法によるキャリア濃度測定-

物性測定用サンプルのキャリア濃度の測定には、Resist8300型（東陽テクニカ社製）を用いてホール効果測定を行うことにより求めた。ホール効果測定は20の環境下で行った。尚、ホール効果測定を行うことにより、キャリア濃度だけではなく、キャリアのホール移動度も求めることができる。

【0068】

-組成比の測定方法-

物性測定用サンプルの組成比のRBS（ラザフォード後方散乱）分析により、組成比を求めた。

【0069】

【表1】

|     | 酸素流量(sccm) | 電気伝導度(S cm <sup>-1</sup> ) | 電子キャリア濃度(cm <sup>-3</sup> ) | ホール移動度(cm <sup>2</sup> /Vs) | 組成比                        |

|-----|------------|----------------------------|-----------------------------|-----------------------------|----------------------------|

| 条件1 | 0.2        | 4.0 × 10 <sup>1</sup>      | 3 × 10 <sup>19</sup>        | 8.3                         | In:Ga:Zn = 1.0: 0.96: 0.54 |

| 条件2 | 1.2        | 2.6 × 10 <sup>-1</sup>     | 3 × 10 <sup>17</sup>        | 4.9                         |                            |

| 条件3 | 1.4        | 5.7 × 10 <sup>-3</sup>     | 1 × 10 <sup>16</sup>        | 3.0                         |                            |

| 条件4 | 1.5        | 1.0 × 10 <sup>-4</sup>     | 5 × 10 <sup>14</sup>        | 1.3                         | In:Ga:Zn = 1.0: 0.93: 0.57 |

| 条件5 | 1.8        | 1.1 × 10 <sup>-9</sup>     | < 10 <sup>11</sup>          | -                           | In:Ga:Zn = 1.0: 0.95: 0.63 |

【0070】

表1より、酸化物半導体InGaZnO<sub>4</sub>のスパッタ膜において、スパッタ時の酸素流

10

20

30

40

50

量を上げる、つまりスパッタ膜中の酸素濃度を増やすと、電気伝導度が減少し、ホール移動度が減少することが示された。また、組成比において、Zn / In 比が増加すると、電気伝導度が減少し、ホール移動度も減少することが示された。

#### 【0071】

##### 2. TFT 素子の作製

本発明の TFT 素子 1, 2 および比較の TFT 素子 1, 2 を作製した。本発明の TFT 素子 1, 2 および比較の TFT 素子 1, 2 の断面構造を図 20 に示す。

基板としては、無アルカリガラス板（コーニング社、品番 NO. 1737）を用いた。純水 15 分 アセトン 15 分 純水 15 分の順で超音波洗浄を行った前記基板上に、SnO<sub>2</sub> 含有率が 10 質量 % である酸化インジウム錫（ITO）タ - ゲット（インジウム：錫 = 95 : 5（モル比））を用いて、RF マグнетロンスパッタ（条件：成膜温度 43 °C、スパッタガス Ar = 12 sccm、RF パワー 40 W、成膜圧力 0.4 Pa）により、ゲート電極としての ITO 薄膜（厚み 30 nm）を形成した。ゲート電極 ITO のパターニングには、スパッタ時にシャドウマスクを用いることにより行った。

#### 【0072】

次にゲート電極上に、下記のゲート絶縁膜の形成を行った。

ゲート絶縁膜：SiO<sub>2</sub> を RF マグネットロൺスパッタ真空蒸着法（条件：ターゲット SiO<sub>2</sub>、成膜温度 54 °C、スパッタガス Ar / O<sub>2</sub> = 12 / 2 sccm、RF パワー 40 W、成膜圧力 0.4 Pa）にて 200 nm 形成し、ゲート絶縁膜を設けた。ゲート絶縁膜 SiO<sub>2</sub> のパターニングには、スパッタ時にシャドウマスクを用いることにより行った。

#### 【0073】

この上に、InGaZnO<sub>4</sub> からなる活性層及び抵抗層を設けた。本発明の TFT 素子 1, 2 および比較の TFT 素子 1, 2 における活性層及び抵抗層の蒸着条件及び蒸着厚みを表 2 に示した。活性層及び抵抗層の蒸着条件は上記の「1. 活性層及び抵抗層の作製」に示す通りである。尚、活性層及び抵抗層の InGaZnO<sub>4</sub> のパターニングには、上記と同様に、スパッタ時にシャドウマスクを用いることにより行った。

#### 【0074】

次いで、上記活性層又は抵抗層の上にソース電極及びドレイン電極として ITO を 40 nm の厚みに RF マグネットロൺスパッタ（条件：成膜温度 43 °C、スパッタガス Ar = 12 sccm、RF パワー 40 W、成膜圧力 0.4 Pa）にて、蒸着した。尚、ソース電極およびドレイン電極のパターニングには、スパッタ時にシャドウマスクを用いることにより行った。以上により、チャネル長 L = 200 μm、チャネル幅 W = 1000 μm の逆ステータガ構造の本発明の TFT 素子 1, 2 および比較の TFT 素子 1, 2 を作製した。

#### 【0075】

##### 3. 性能評価

得られた各 TFT 素子について、飽和領域ドレイン電圧 Vd = 40 V（ゲート電圧 - 20 V - Vg = 40 V）での TFT 伝達特性の測定を行い、TFT の電界効果移動度および ON / OFF 比を評価した。TFT 伝達特性の測定は、半導体パラメータ・アナライザー 4156 C（アジレントテクノロジー社製）を用いて行った。

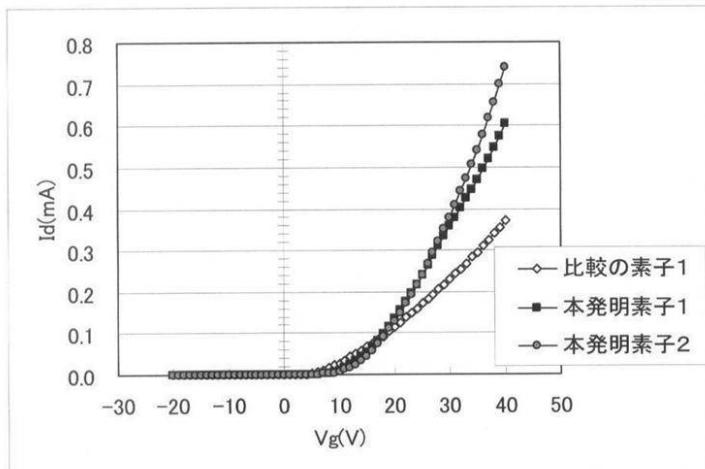

図 5 は、これらの素子の TFT 伝達特性を示す電流 - 電圧特性曲線である。横軸はゲート電圧 Vg、縦軸はドレイン電流 Id である。

#### 【0076】

##### - 電界効果移動度の算出方法 -

飽和領域における電界効果移動度 μ は、TFT 伝達特性から次式で求められる。

$$\mu = (2L / W * C_{ox}) * (I_d^{1/2} / Vg)$$

ここで、L はチャネル長、W はチャネル幅、C<sub>ox</sub> はゲート絶縁膜の静電容量、I<sub>d</sub> はドレイン電流、V<sub>g</sub> はゲート電圧を示す。

#### 【0077】

##### - ON / OFF 比の算出方法 -

10

20

40

50

ON / OFF 比は TFT 伝達特性からドレイン電流  $I_d$  における最大値  $I_{d_{max}}$  と最小値  $I_{d_{min}}$  との比  $I_{d_{max}} / I_{d_{min}}$  から求めた。

#### 【0078】

図 5 の TFT 伝達特性の測定結果から得られた TFT 特性を表 2 に示した。表 2 の結果より、本発明の素子 1, 2 は電界効果移動度が大きくかつ ON / OFF 比が高く優れた性能を示した。一方、中庸の電気伝導度の活性層を 1 層でのみ構成した比較素子 1 は電界効果移動度が小さかった。また、活性層を電気伝導度の小さい抵抗層、抵抗層を電気伝導度の大きい活性層に入れ替えた比較素子 2 は、ON / OFF 比が極めて低下した。

#### 【0079】

以上に明らかなように、本発明による電気伝導度の大きい活性層、及び電気伝導度の小さい抵抗層を有する構成によって、電界効果移動度が大きくかつ ON / OFF 比が高い予想外に優れた性能を示すことが見出された。

#### 【0080】

##### 【表 2】

| 素子 No  | 基板  | ゲート電極/厚み (nm) | 第1活性層 |        | 第2活性層 |        | 素子性能                      |                   |

|--------|-----|---------------|-------|--------|-------|--------|---------------------------|-------------------|

|        |     |               | 蒸着条件  | 厚み(nm) | 蒸着条件  | 厚み(nm) | 移動度 (cm <sup>2</sup> /Vs) | ON/OFF比           |

| 本発明素子1 | ガラス | ITO/30        | 条件2   | 10     | 条件4   | 40     | 15.3                      | $1.4 \times 10^6$ |

| 本発明素子2 | ガラス | ITO/30        | 条件1   | 10     | 条件4   | 40     | 17.2                      | $2.7 \times 10^6$ |

| 比較の素子1 | ガラス | ITO/30        | 条件3   | 50     | -     | -      | 4.3                       | $9.0 \times 10^5$ |

| 比較の素子2 | ガラス | ITO/30        | 条件4   | 10     | 条件1   | 40     | 4.2                       | 1.4               |

| 参考例    | ガラス | Mo/40         | 条件2   | 30     | 条件5   | 20     | 33.2                      | $3.4 \times 10^6$ |

| 本発明素子4 | PEN | Mo/40         | 条件1   | 10     | 条件4   | 40     | 21.1                      | $2.2 \times 10^6$ |

#### 【0081】

##### 実施例 2

###### 1. 本発明の TFT 素子 3 の作製

本発明の TFT 素子 1 の作製において、ゲート電極を ITO 30 nm より Mo 40 nm に変更し、さらに抵抗層を実施例 1 の抵抗層作製条件 5 にて作製し、また活性層と抵抗層の厚みをそれぞれ 30 nm および 20 nm へと変更して、本発明の TFT 素子 3 を作製した。Mo の成膜には、DC マグнетロニンスパッタリング蒸着法（スパッタリング条件：DC パワー 380 W、スパッタガス Ar = 12 sccm、圧力 0.4 Pa）にて行った。

#### 【0082】

###### 2. 性能評価

実施例 1 と同様に、TFT 素子性能を評価した結果を表 2 に示した。

その結果、本発明の TFT 素子 3 は、さらに電界効果移動度が大きくかつ ON / OFF 比が高く、本発明の TFT 素子 1, 2 より優れた性能を示した。しかし、TFT 伝達特性の測定を繰り返し行うと、本発明の TFT 素子 1, 2 の方が、本発明の TFT 素子 3 より ON / OFF 比の劣化が少なく、より耐久性に優れていた。

#### 【0083】

##### 実施例 3

###### 1. 本発明の TFT 素子 4 の作製

本発明の TFT 素子 1 の作製において、基板にはポリエチレンナフタレートフィルムの両面に下記バリア機能を持つ絶縁層を有するバリア付きフィルムを用いた。前記バリアフィルム上に形成するゲート電極を ITO 30 nm より Mo 40 nm に変更し、本発明の TFT 素子 4 を作製した。Mo の成膜は実施例 2 と同様の条件にて行った。

#### 【0084】

上記バリア機能を持つ絶縁層に SiON を用いた。絶縁層 SiON の成膜条件は以下である。

絶縁層：SiON を 500 nm の厚みに蒸着した。SiON の蒸着には RF マグネットロニンスパッタリング蒸着法（スパッタリング条件：ターゲット Si<sub>3</sub>N<sub>4</sub>、RF パワー 40

10

20

30

40

50

0 W、ガス流量 Ar / O<sub>2</sub> = 12 / 3 sccm、成膜圧力 0.45 Pa) を用いた。

### 【0085】

#### 2. 性能評価

実施例 1 と同様に、TFT 素子性能を評価した結果を表 2 に示した。

その結果、本発明の TFT 素子 4 は、ガラス上に作製した本発明の TFT 素子 1 と同等の電界移動度、ON / OFF 比を示した。このことより、本発明の TFT 素子は、有機プラスチックフィルムからなる可撓性基板上においても高移動度、高 ON / OFF 比を示すことがわかった。

### 【0086】

#### 実施例 4

10

##### 1. 本発明の TFT 素子の作製

下記に従って、本発明によるトップゲート型 TFT 素子を作製した。本実施例の TFT 素子の断面構造は図 21 に示す。

実施例 1 と同様に無アルカリガラス板(コーニング社、品番 NO. 1737)を用い、この上にソース電極およびドレイン電極として ITO (厚み 40 nm) を形成した。ITO の成膜方法は実施例 1 と同条件で行った。また、ソース電極およびドレイン電極のパターニングは、実施例 1 と同様のシャドウマスクを用いて行った。

### 【0087】

この上に、抵抗層を条件 4 で 40 nm の厚みに、また活性層を実施例 1 の条件 1 で 10 nm の厚みに設けた。これらの層のパターニングは、実施例 1 と同様のシャドウマスクを用いて行った。

20

### 【0088】

この上に、ゲート絶縁膜として厚み 200 nm の SiO<sub>2</sub> を設けた。SiO<sub>2</sub> の成膜方法は実施例 1 と同条件で行った。また、ゲート絶縁膜のパターニングは、実施例 1 と同様のシャドウマスクを用いて行った。

### 【0089】

次いで、ゲート電極として ITO を 30 nm 設けた。ITO の成膜方法は実施例 1 と同条件で行った。また、ゲート電極のパターニングは、実施例 1 と同様のシャドウマスクを用いて行った。

以上により、チャネル長 L = 200 μm、チャネル幅 W = 1000 μm のトップゲート型 TFT 素子を得た。

30

### 【0090】

#### 2. 性能評価

実施例 1 と同様に、TFT 素子性能を評価した結果、電界効果移動度が 17.7 cm<sup>2</sup> / V s、ON / OFF 比が 3 × 10<sup>6</sup> であった。トップゲート型 TFT でも高移動度、高 ON / OFF 比が得られた。

### 【0091】

#### 実施例 5

実施例 3 における活性層及び抵抗層の調製を下記に変更した以外は実施例 1 と同様にして TFT 素子を作製した。下記条件によれば、ゲート絶縁膜に隣接した活性層の電気伝導性が大きく、ソース電極およびドレイン電極に隣接した抵抗層の電気伝導性が小さく、その間の領域の電気伝導性が連続的に変化した構成が形成される。本実施例の TFT 素子の断面構造は図 22 に示す。

40

### 【0092】

#### < 活性層及び抵抗層の作製条件 >

InGaZnO<sub>4</sub> をターゲットとして用いて、実施例 1 におけると同じスパッタリング装置を用いて、連続した活性層と抵抗層を作製した。スパッタリング条件は、RF パワー 200 W、スパッタガス Ar 流量 12 sccm、圧力 0.4 Pa で、酸素流量を 0.6 sccm から 1.8 sccm まで連続的に変化させながら、膜厚が 50 nm になるまで成膜した。

50

## 【0093】

## &lt;性能評価&gt;

作製したTFT素子を実施例1と同様に評価した所、移動度 $8.9 \text{ cm}^2/\text{Vs}$ 、ON/OFF比 $1.0 \times 10^6$ という良いTFT特性を示した。

## 【図面の簡単な説明】

## 【0094】

【図1】本発明の逆スタガ構造のTFT素子構造を示す模式図である。

【図2】比較の逆スタガ構造のTFT素子構造を示す模式図である。

【図3】本発明のトップゲート構造のTFT素子構造を示す模式図である。

【図4】比較のトップゲート構造のTFT素子構造を示す模式図である。

【図5】逆スタガ構造のTFT素子の電流-電圧特性を示す特性曲線である。横軸は、ゲート電圧(Vg)であり、縦軸はドレイン電流(Id)である。

【図6】本発明の逆スタガ構造のTFT素子構造を示す模式図である。活性層の電気伝導度が層内で連続的にゲート絶縁膜に接する領域で大きく、ソース・ドレイン電極に接する領域の抵抗層で小さくなるよう変化している。

【図7】本発明の別の態様の逆スタガ構造のTFT素子構造を示す模式図である。

【図8】本発明の別の態様の逆スタガ構造のTFT素子構造を示す模式図である。

【図9】本発明の別の態様の逆スタガ構造のTFT素子構造を示す模式図である。

【図10】本発明の別の態様の逆スタガ構造のTFT素子構造の模式図である。

【図11】本発明の別の態様のトップゲート構造のTFT素子構造を示す模式図である。

【図12】本発明の別の態様のトップゲート構造のTFT素子構造を示す模式図である。

【図13】本発明の別の態様のトップゲート構造のTFT素子構造を示す模式図である。

【図14】本発明の別の態様のトップゲート構造のTFT素子構造を示す模式図である。

【図15】本発明の別の態様の逆スタガ構造のTFT素子構造の模式図である。

【図16】本発明の別の態様の逆スタガ構造のTFT素子構造の模式図である。

【図17】本発明の別の態様のトップゲート構造のTFT素子構造の模式図である。

【図18】本発明の別の態様のトップゲート構造のTFT素子構造の模式図である。

【図19】本発明のTFT素子を用いたアクティブマトリクス駆動型液晶表示装置の等価回路の模式図である。

【図20】実施例1～3におけるTFT素子の断面構造の模式図である。

【図21】実施例4におけるTFT素子の断面構造の模式図である。

【図22】実施例5におけるTFT素子の断面構造の模式図である。

## 【符号の説明】

## 【0095】

1, 11, 21, 31, 71, : 基板

2, 12, 22, 32, 72, 132, 142 : ゲート電極

3, 13, 15, 23, 33, 43, 53, 63, 73, 83, 93, 103, 11

3, 123, 133, 143 : ゲート絶縁膜

4, 14 : 活性層

4-1, 4-11, 4-21, 4-31, 4-41, 4-51, 4-61, 4-71

, 4-81, 4-91, 4-101, 4-111, 4-121, 4-131, 4-142

: 活性層

4-2, 4-12, 4-22, 4-32a, 4-32b, 4-42, 4-52a, 4

-52b, 4-62, 4-72a, 4-72b, 4-82, 4-92a, 4-92b, 4

-102, 4-112a, 4-112b, 4-122, 4-132, 4-142 : 抵抗層

5-1, 5-11, 5-21, 16, 5-31, 5-42, 5-51, 5-61, 5

-71, 5-81, 5-91, 5-101, 5-111, 5-121, 5-131, 5-

141 : ソース電極

5-2, 5-12, 5-22, 17, 5-32, 5-42, 5-52, 5-62, 5

-72, 5-82, 5-92, 5-102, 5-112, 5-122, 5-132, 5-

20

30

40

50

1 4 2 : ドレイン電極

6 , 16 , 26 , 36 , 76 , : 絶縁層

7 : 高酸素濃度層 (比較例)

8 . 低酸素濃度層 (比較例)

2 0 0 : スイッチングTFT

3 0 0 : 液晶素子

4 0 0 : 信号電極線

5 0 0 : ゲート電極線

6 0 0 : コンデンサ

【図 1】

【図 2】

【図 3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図 12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

400 信号電極線

【図20】

【図21】

【図 2 2】

---

フロントページの続き

合議体

審判長 相田 義明

審判官 近藤 幸浩

審判官 小川 将之

(56)参考文献 特開2006-165529(JP,A)

特開昭61-5578(JP,A)

特開昭62-42564(JP,A)

特開昭60-160170(JP,A)

特開昭63-258072(JP,A)