(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number

WO 2015/035449 A1

(43) International Publication Date

19 March 2015 (19.03.2015)

WIPO | PCT

(51) International Patent Classification:

H04N 19/00 (2014.01) H04N 19/50 (2014.01)

(21) International Application Number:

PCT/AU2014/000893

(22) International Filing Date:

12 September 2014 (12.09.2014)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

2013228045 13 September 2013 (13.09.2013) AU

(71) Applicant: CANON KABUSHIKI KAISHA [JP/JP]; 30-2, Shimomaruko 3-chome, Ohta-ku, Tokyo, 146-8501 (JP).

(71) Applicant (for AE only): CANON INFORMATION SYSTEMS RESEARCH AUSTRALIA [AU/AU]; PTY LTD, Building A, The Park Estate, 5 Talavera Road, Macquarie Park, NSW 2113 (AU).

(72) Inventor: ROSEWARNE, Christopher James; 5/78 Donnison Street, Gosfrd, NSW 2250 (AU).

(74) Agent: SPRUSON & FERGUSON; GPO BOX 3898, Sydney, New South Wales 2001 (AU).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

Published:

— with international search report (Art. 21(3))

(54) Title: METHOD, APPARATUS AND SYSTEM FOR ENCODING AND DECODING VIDEO DATA

Fig. 18B

(57) Abstract: A method of decoding a coding unit from a video bitstream is disclosed. The coding unit references previously decoded samples. A previous block vector of a previous coding unit to said coding unit to be decoded is determined. The previous coding unit is configured to use intra-block copy. The method decodes, from the video bitstream, a block vector difference for the coding unit to be decoded. The block vector difference indicates a difference between the previous block vector and a block vector of the coding unit to be decoded. The block vector of the coding unit to be decoded is determined using the previous block vector and the block vector difference. The coding unit to be decoded is decoded based on sample values of a reference block selected using the determined block vector.

WO 2015/035449 A1

**METHOD, APPARATUS AND SYSTEM FOR ENCODING AND DECODING

VIDEO DATA**

**TECHNICAL FIELD**

The present invention relates generally to digital video signal processing and, in particular, to a method, apparatus and system for encoding and decoding video data. The present invention also relates to a computer program product including a computer readable medium having recorded thereon a computer program for encoding and decoding video data.

**BACKGROUND**

Many applications for video coding currently exist, including applications for transmission and storage of video data. Many video coding standards have also been developed and others are currently in development. Recent developments in video coding standardisation have led to the formation of a group called the "Joint Collaborative Team on Video Coding" (JCT-VC). The Joint Collaborative Team on Video Coding (JCT-VC) includes members of Study Group 16, Question 6 (SG16/Q6) of the Telecommunication Standardisation Sector (ITU-T) of the International Telecommunication Union (ITU), known as the Video Coding Experts Group (VCEG), and members of the International Organisations for Standardisation / International Electrotechnical Commission Joint Technical Committee 1 / Subcommittee 29 / Working Group 11 (ISO/IEC JTC1/SC29/WG11), also known as the Moving Picture Experts Group (MPEG).

The Joint Collaborative Team on Video Coding (JCT-VC) has produced a new video coding standard that significantly outperforms the "H.264/MPEG-4 AVC" video coding standard. The new video coding standard has been named "high efficiency video coding (HEVC)". Further development of high efficiency video coding (HEVC) is directed towards introducing support of different representations of chroma information present in video data, known as 'chroma formats', and support of higher bit-depths. The high efficiency video coding (HEVC) standard defines two profiles, known as 'Main' and 'Main10', which support a bit-depth of eight (8) bits and ten (10) bits respectively. Further development to increase the bit-depths supported by the high efficiency video coding (HEVC) standard are underway as part of 'Range extensions' activity. Support for bit-depths as high as sixteen (16) bits is under study in the Joint Collaborative Team on Video Coding (JCT-VC).

5        Video data includes one or more colour channels. Typically three colour channels are supported and colour information is represented using a 'colour space'. One example colour space is known as 'YCbCr', although other colour spaces are also possible. The 'YCbCr' colour space enables fixed-precision representation of colour information and thus is well suited to digital implementations. The 'YCbCr' colour space includes a 'luma' channel (Y) and two 'chroma' channels (Cb and Cr). Each colour channel has a particular bit-depth. The bit-depth defines the width of samples in the respective colour channel in bits. Generally, all colour channels have the same bit-depth, although the colour channels may also have different bit-depths.

10       One aspect of the coding efficiency achievable with a particular video coding standard is the characteristics of available prediction methods. For video coding standards intended for compression sequences of two-dimensional video frames, there are three types of prediction: intra-prediction, inter-prediction and intra block copy mode. Frames are divided into one or more blocks, and each block is predicted using one of the types of prediction. Intra-prediction methods allow content of one part of a video frame to be predicted from other parts of the same video frame. Intra-prediction methods typically produce a block having a directional texture, with an intra-prediction mode specifying the direction of the texture and neighbouring samples within a frame used as a basis to produce the texture. Inter-prediction methods allow the content of a block within a video frame to be predicted from blocks in previous video frames. The previous video frames (i.e. in 'decoding order' as opposed to 'display order' which may be different) may be referred to as 'reference frames'. Intra block copy mode creates a reference block from another block located within the current frame. The first video frame within a sequence of video frames typically uses intra-prediction for all blocks within the frame, as no prior frame is available for reference. Subsequent video frames may use one or more previous video frames from which to predict blocks.

30       To achieve the highest coding efficiency, the prediction method that produces a predicted block that is closest to captured frame data is typically used. The remaining difference between the predicted block and the captured frame data is known as the 'residual'. This spatial domain representation of the difference is generally transformed into a frequency domain representation. Generally, the frequency domain representation compactly stores the information present in the spatial domain representation. The frequency domain representation includes a block of 'residual coefficients' that results

from applying a transform, such as an integer discrete cosine transform (DCT). Moreover, the residual coefficients (or ‘scaled transform coefficients’) are quantised, which introduces loss but also further reduces the amount of information required to be encoded in a bitstream. The lossy frequency domain representation of the residual, also known as 5 ‘transform coefficients’, may be stored in the bitstream. The amount of lossiness in the residual recovered in a decoder affects the distortion of video data decoded from the bitstream compared to the captured frame data and the size of the bitstream.

A video bitstream includes a sequence of encoded syntax elements. The syntax elements are ordered according to a hierarchy of ‘syntax structures’. A syntax structure 10 describes a set of syntax elements and the conditions under which each syntax element is coded. A syntax structure may invoke other syntax structures, enabling hierarchy arrangements of syntax elements. A syntax structure may also invoke another instance of the same syntax structure, enabling recursive arrangements of syntax elements. Each syntax element is composed of one or more ‘bins’, which are encoded using a ‘context 15 adaptive binary arithmetic coding’ algorithm. A given bin may be ‘bypass’ coded, in which case there is no ‘context’ associated with the bin. Alternatively, a bin may be ‘context’ coded, in which case there is context associated with the bin. Each context coded bin has one context associated with the bin. The context is selected from one or more possible contexts. The context is retrieved from a memory and each time the context is 20 used, the context is also updated and stored back in the memory. When two or more contexts may be used for a given bin, a rule to determine which context to use is applied at the video encoder and the video decoder. When encoding or decoding the bin, prior information in the bitstream is used to select which context to use. Context information in the decoder necessarily tracks context information in the encoder (otherwise the decoder 25 could not parse a bitstream produced by an encoder). The context includes two parameters: a likely bin value (or ‘valMPS’) and a probability level.

Syntax elements with two distinct values may also be referred to as ‘flags’ and are generally encoded using one context coded bin. A given syntax structure defines the possible syntax elements that can be included in the video bitstream and the circumstances 30 in which each syntax element is included in the video bitstream. Each instance of a syntax element contributes to the size of the video bitstream. An objective of video compression is to enable representation of a given sequence using a video bitstream and having minimal size (e.g. in bytes) for a given quality level (including both lossy and lossless cases). At

the same time, video decoders are invariably required to decode video bitstreams in real time, placing limits on the complexity of the algorithms that can be used. As such, a trade-off between algorithmic complexity and compression performance is made. In particular, modifications that can improve or maintain compression performance while reducing 5 algorithmic complexity are desirable.

## SUMMARY

It is an object of the present invention to substantially overcome, or at least ameliorate, one or more disadvantages of existing arrangements.

According to one aspect of the present disclosure, there is provided a method of 10 decoding a coding unit from a video bitstream, the coding unit referencing previously decoded samples, the method comprising:

determining a previous block vector of a previous coding unit to said coding unit to be decoded, the previous coding unit being configured to use intra-block copy;

15 decoding, from the video bitstream, a block vector difference for said coding unit to be decoded, the block vector difference indicating a difference between the previous block vector and a block vector of said coding unit to be decoded;

determining the block vector of said coding unit to be decoded using the previous block vector and the block vector difference; and

20 decoding said coding unit to be decoded, based on sample values of a reference block selected using the determined block vector.

According to another aspect of the present disclosure, there is provided a system for decoding a coding unit from a video bitstream, the coding unit referencing previously decoded samples, the system comprising:

25 a memory for storing data and a computer program;

a processor coupled to said memory, the computer program comprising instructions for:

determining a previous block vector of a previous coding unit to said coding unit to be decoded, the previous coding unit being configured to use intra-block copy;

30 decoding, from the video bitstream, a block vector difference for said coding unit to be decoded, the block vector difference indicating a difference between the previous block vector and a block vector of said coding unit to be decoded;

determining the block vector of said coding unit to be decoded using the previous block vector and the block vector difference; and

decoding said coding unit to be decoded, based on sample values of a reference block selected using the determined block vector.

5 According to still another aspect of the present disclosure, there is provided an apparatus for decoding a coding unit from a video bitstream, the coding unit referencing previously decoded samples, the apparatus comprising:

means for determining a previous block vector of a previous coding unit to said coding unit to be decoded, the previous coding unit being configured to use intra-block

10 copy;

means for decoding, from the video bitstream, a block vector difference for said coding unit to be decoded, the block vector difference indicating a difference between the previous block vector and a block vector of said coding unit to be decoded;

15 means for determining the block vector of said coding unit to be decoded using the previous block vector and the block vector difference; and

means for decoding said coding unit to be decoded, based on sample values of a reference block selected using the determined block vector.

According to still another aspect of the present disclosure, there is provided a non-transitory computer readable medium having a computer program stored thereon for

20 decoding a coding unit from a video bitstream, the coding unit referencing previously decoded samples, the program comprising:

code for determining a previous block vector of a previous coding unit to said coding unit to be decoded, the previous coding unit being configured to use intra-block copy;

25 code for decoding, from the video bitstream, a block vector difference for said coding unit to be decoded, the block vector difference indicating a difference between the previous block vector and a block vector of said coding unit to be decoded;

code for determining the block vector of said coding unit to be decoded using the previous block vector and the block vector difference; and

30 code for decoding said coding unit to be decoded, based on sample values of a reference block selected using the determined block vector.

According to still another aspect of the present disclosure, there is provided a method of encoding a coding unit into a video bitstream, the method comprising:

determining a previous block vector of a previous coding unit to said coding unit to be encoded, the previous coding unit being configured to use intra-block copy;

determining a block vector difference for said coding unit to be encoded, the block vector difference indicating the difference between the previous block vector and a block vector of said coding unit to be encoded;

5 encoding, into the video bitstream, the block vector difference for said coding unit to be encoded;

encoding said coding unit to be encoded into the video bitstream, using sample values of a reference block selected using the block vector of said coding unit to be 10 encoded.

According to still another aspect of the present disclosure, there is provided a system for encoding a coding unit into a video bitstream, the system comprising:

a memory for storing data and a computer program;

15 a processor coupled to said memory, the computer program comprising instructions for:

determining a previous block vector of a previous coding unit to said coding unit to be encoded, the previous coding unit being configured to use intra-block copy;

determining a block vector difference for said coding unit to be encoded, the block vector difference indicating the difference between the previous block vector and a block vector of said coding unit to be encoded;

encoding, into the video bitstream, the block vector difference for said coding unit to be encoded;

20 encoding said coding unit to be encoded into the video bitstream, using sample values of a reference block selected using the block vector of said coding unit to be encoded.

According to still another aspect of the present disclosure, there is provided an apparatus for encoding a coding unit into a video bitstream, the apparatus comprising:

means for determining a previous block vector of a previous coding unit to said 30 coding unit to be encoded, the previous coding unit being configured to use intra-block copy;

means for determining a block vector difference for said coding unit to be encoded, the block vector difference indicating the difference between the previous block vector and a block vector of said coding unit to be encoded;

5 means for encoding, into the video bitstream, the block vector difference for said coding unit to be encoded;

means for encoding said coding unit to be encoded into the video bitstream, using sample values of a reference block selected using the block vector of said coding unit to be encoded.

According to still another aspect of the present disclosure, there is provided a non-

10 transitory computer readable medium having a computer program stored thereon for encoding a coding unit into a video bitstream, the program comprising:

determining a previous block vector of a previous coding unit to said coding unit to be encoded, the previous coding unit being configured to use intra-block copy;

15 determining a block vector difference for said coding unit to be encoded, the block vector difference indicating the difference between the previous block vector and a block vector of said coding unit to be encoded;

encoding, into the video bitstream, the block vector difference for said coding unit to be encoded;

20 encoding said coding unit to be encoded into the video bitstream, using sample values of a reference block selected using the block vector of said coding unit to be encoded.

According to still another aspect of the present disclosure, there is provided a method of decoding a block from a video bitstream, the block referencing previously decoded samples, the method comprising:

25 determining a prediction mode from the video bitstream;

decoding an intra block copy flag from the video bitstream if the determined prediction mode is intra-prediction, the intra block copy flag indicating that current samples are based on previously decoded samples of a current frame; and

30 decoding the block from the video bitstream, based on the decoded intra block copy flag, by determining sample values for the block from the previously decoded samples.

According to still another aspect of the present disclosure, there is provided a system for decoding a block from a video bitstream, the block referencing previously decoded samples, the system comprising:

a memory for storing data and a computer program;

a processor coupled to the memory, the computer program comprising instructions for:

5                   determining a prediction mode from the video bitstream; decoding an intra block copy flag from the video bitstream if the determined prediction mode is intra-prediction, the intra block copy flag indicating that current samples are based on previously decoded samples of a current frame; and

10                  decoding the block from the video bitstream, based on the decoded intra block copy flag, by determining sample values for the block from the previously decoded samples.

According to still another aspect of the present disclosure, there is provided an apparatus for decoding a block from a video bitstream, the block referencing previously decoded samples, the apparatus comprising:

15                  means for determining a prediction mode from the video bitstream;

means for decoding an intra block copy flag from the video bitstream if the determined prediction mode is intra-prediction, the intra block copy flag indicating that current samples are based on previously decoded samples of a current frame; and

20                  means for decoding the block from the video bitstream, based on the decoded intra block copy flag, by determining sample values for the block from the previously decoded samples.

According to still another aspect of the present disclosure, there is provided a non-transitory computer readable medium having a computer program stored thereon for method of decoding a block from a video bitstream, the block referencing previously decoded samples, the program comprising:

25                  code for determining a prediction mode from the video bitstream;

code for decoding an intra block copy flag from the video bitstream if the determined prediction mode is intra-prediction, the intra block copy flag indicating that current samples are based on previously decoded samples of a current frame; and

30                  code for decoding the block from the video bitstream, based on the decoded intra block copy flag, by determining sample values for the block from the previously decoded samples.

Other aspects are also disclosed.

## BRIEF DESCRIPTION OF THE DRAWINGS

At least one embodiment of the present invention will now be described with reference to the following drawings and and appendices, in which:

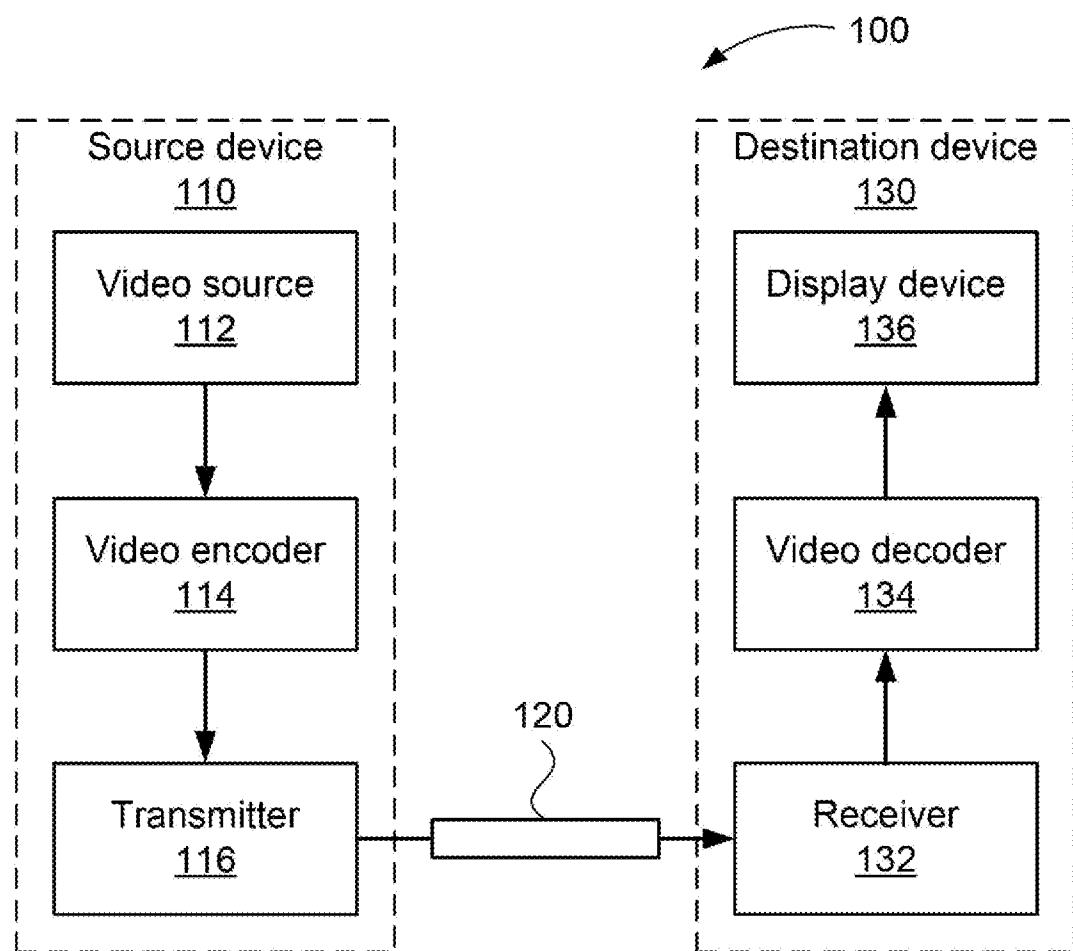

Fig. 1 is a schematic block diagram showing a video encoding and decoding system;

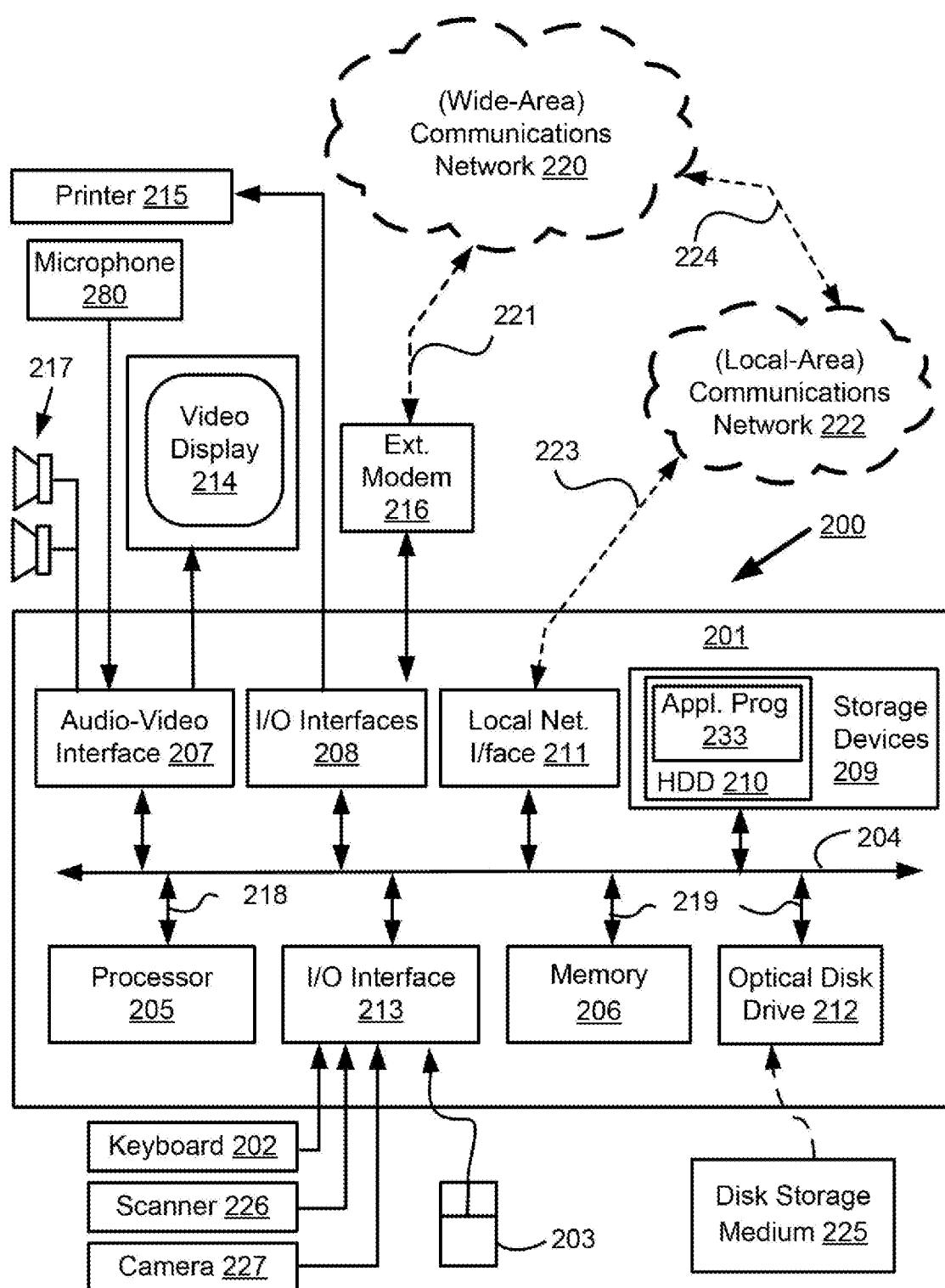

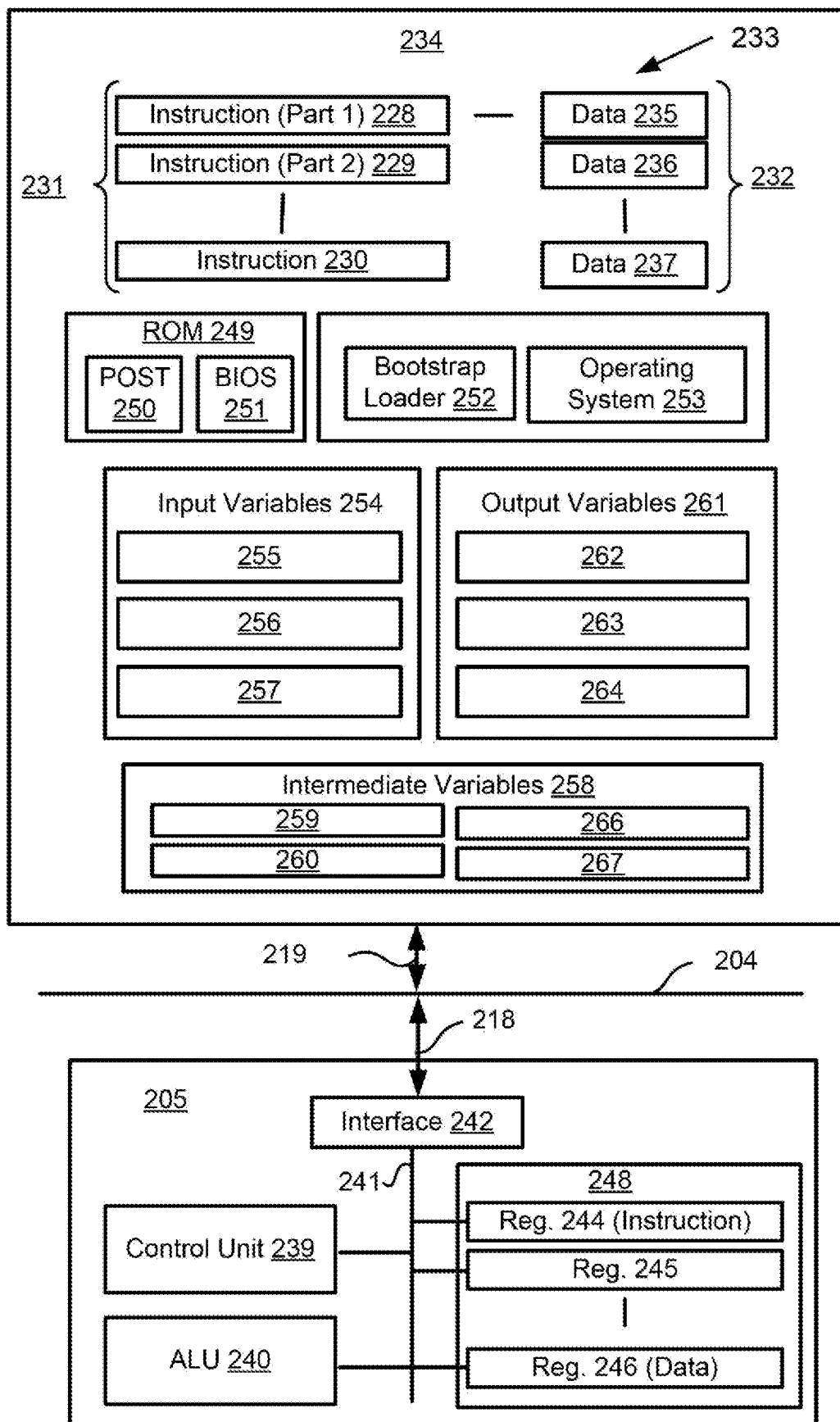

Figs. 2A and 2B form a schematic block diagram of a general purpose computer system upon which one or both of the video encoding and decoding system of Fig. 1 may be practiced;

Fig. 3 is a schematic block diagram showing functional modules of a video encoder;

Fig. 4 is a schematic block diagram showing functional modules of a video decoder;

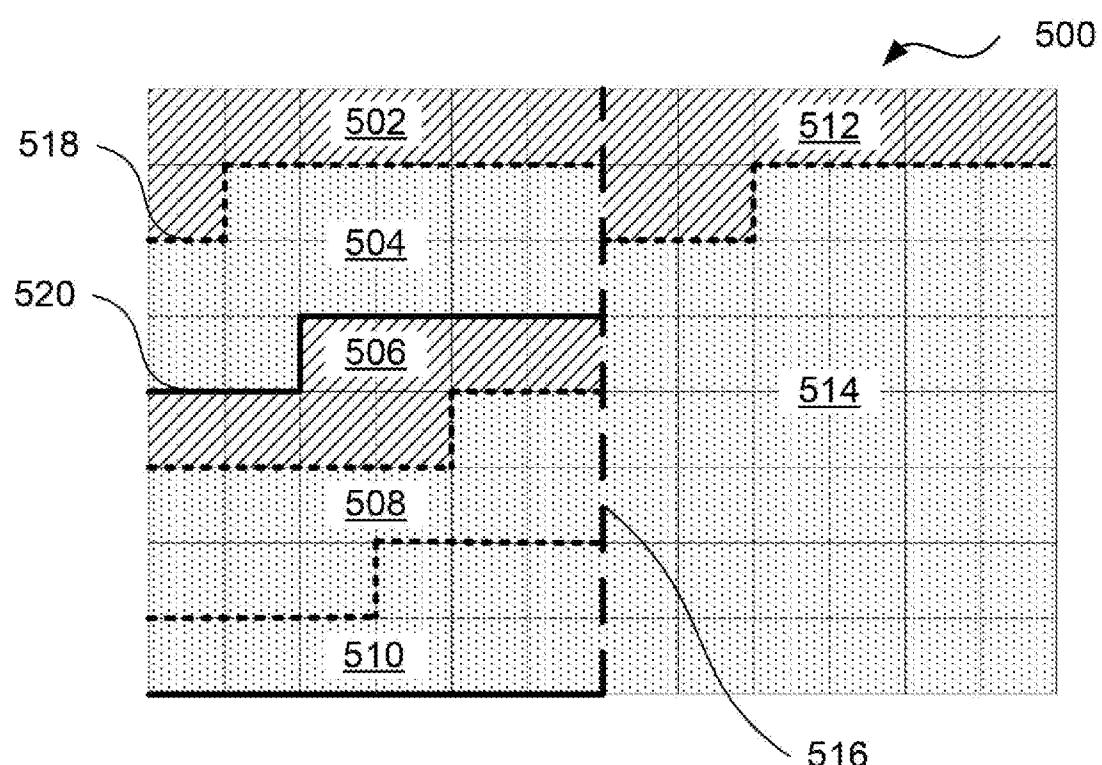

Fig. 5 is a schematic block diagram showing a frame that is divided into two tiles and three slice segments;

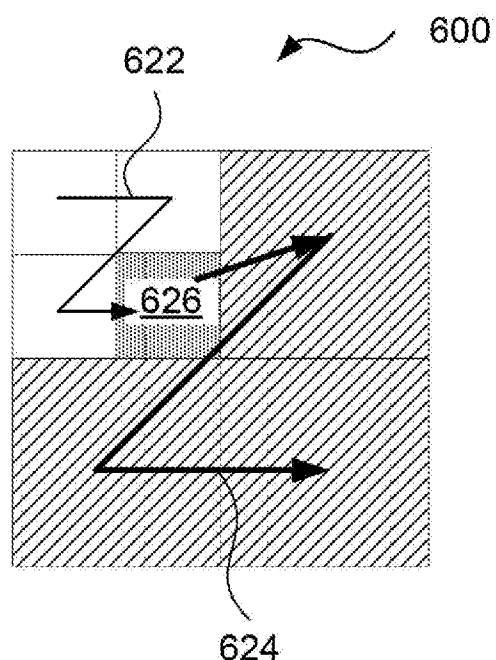

Fig. 6A is a schematic block diagram showing an example 'Z-scan' order of scanning coding units (CUs) within a coding tree block (CTB);

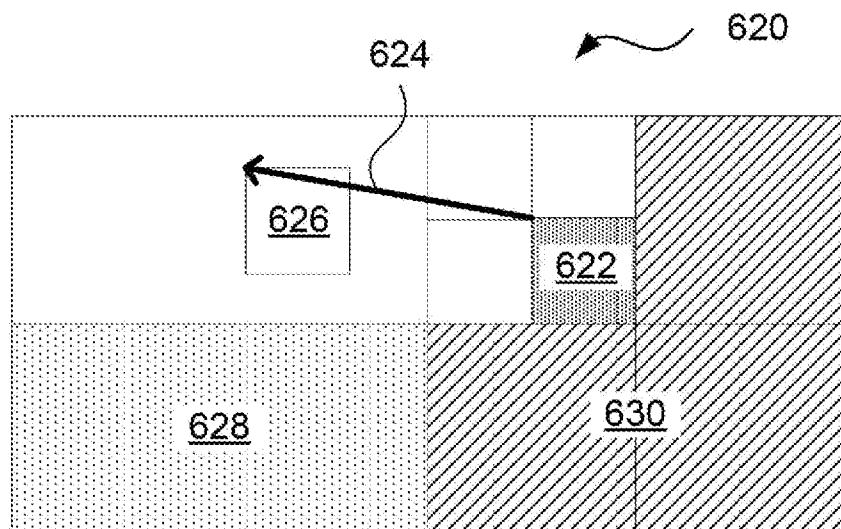

Fig. 6B is a schematic block diagram showing an example block vector referencing a block of samples in a neighbouring coding tree block (CTB) relative to a coding unit (CU) within a current coding tree block (CTB);

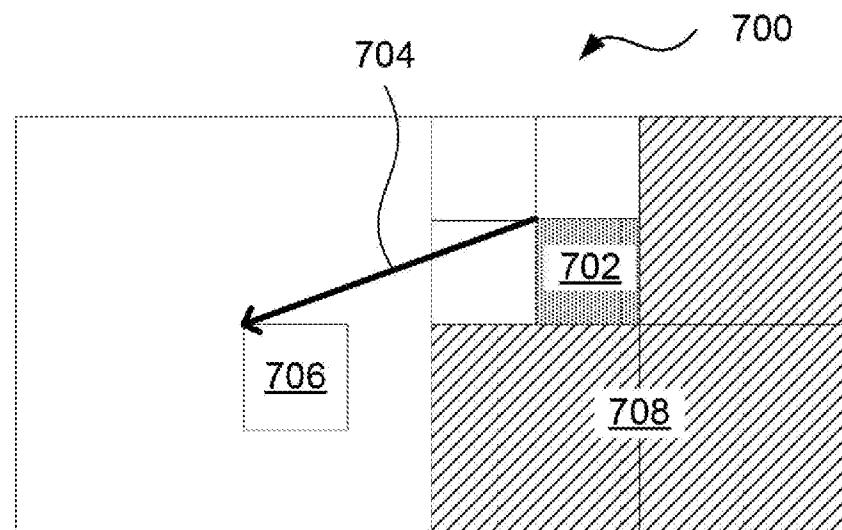

Fig. 7A is a schematic block diagram showing an example block vector referencing a block of samples in a neighbouring coding tree block (CTB) relative to a coding unit (CU) within a current coding tree block (CTB);

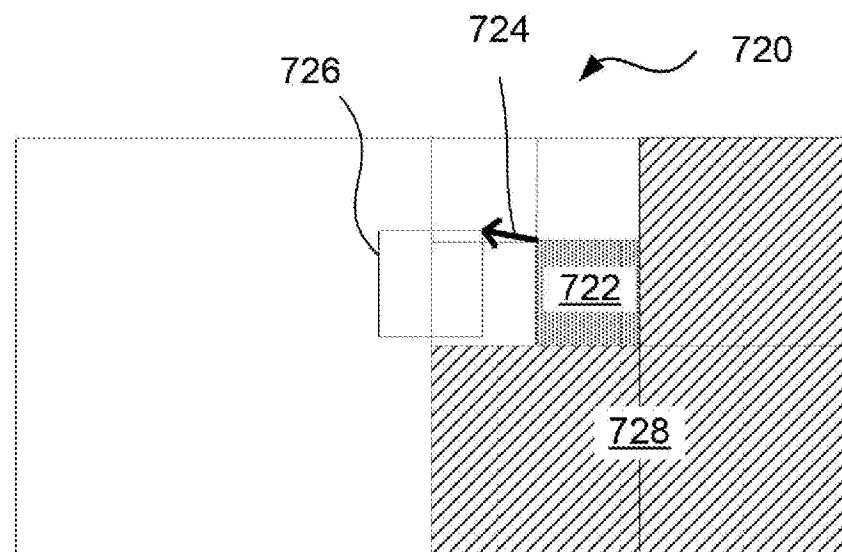

Fig. 7B is a schematic block diagram showing an example block vector referencing a block of samples spanning both a current coding tree block (CTB) and a neighbouring coding tree block (CTB);

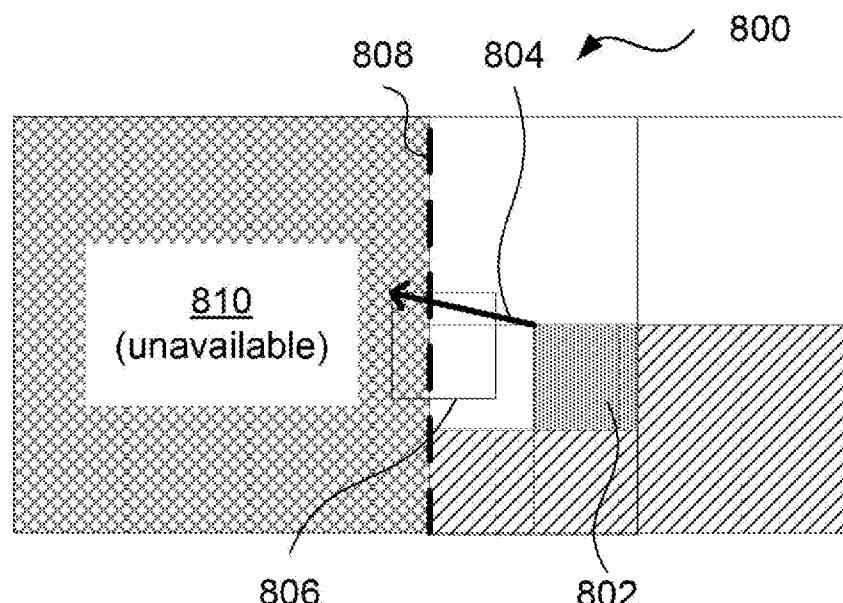

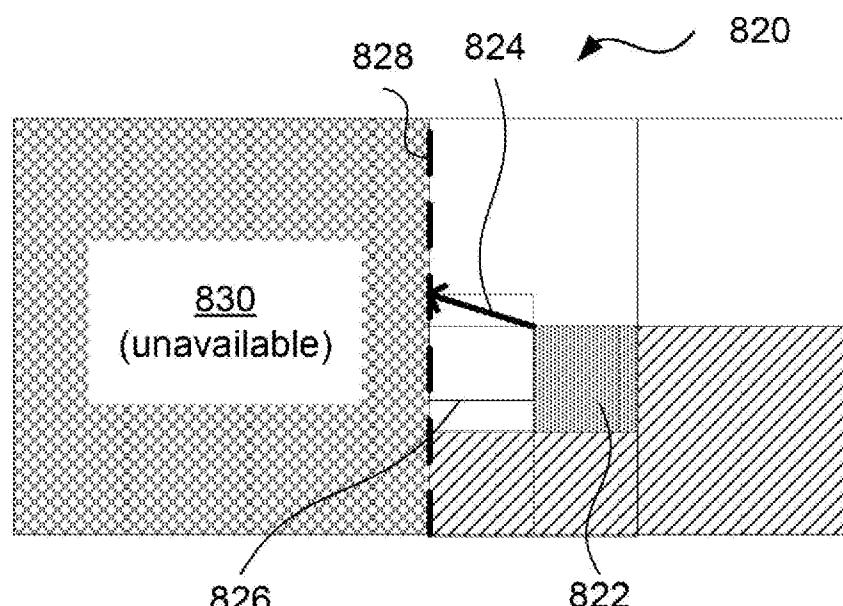

Fig. 8A is a schematic block diagram showing an example block vector referencing a block of samples spanning both a current coding tree block (CTB) and a neighbouring coding tree block (CTB) that is marked as being unavailable;

Fig. 8B is a schematic block diagram showing an example adjusted block vector referencing a block of samples within a current coding tree block (CTB);

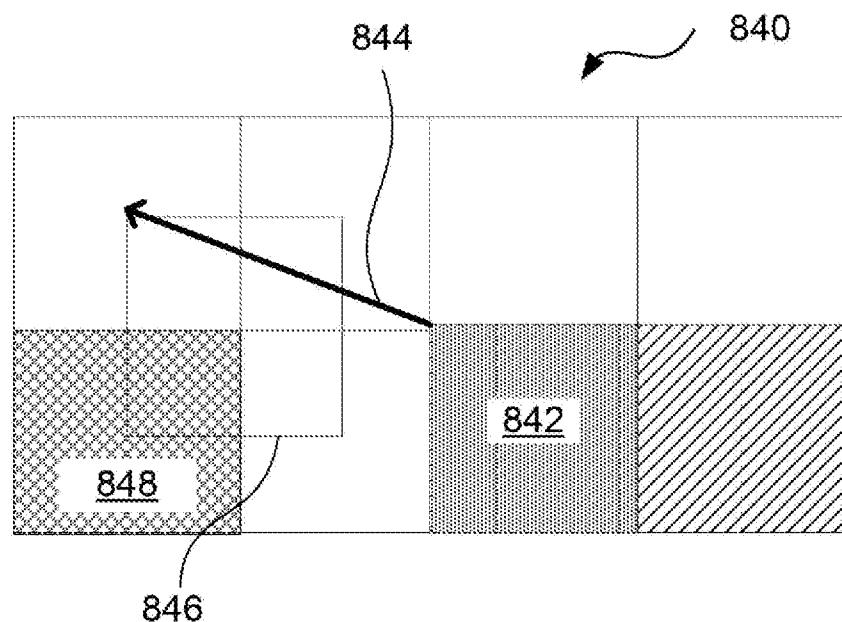

Fig. 8C is a schematic block diagram showing an example block vector referencing a block of samples where some of the referenced samples were decoded using inter-prediction;

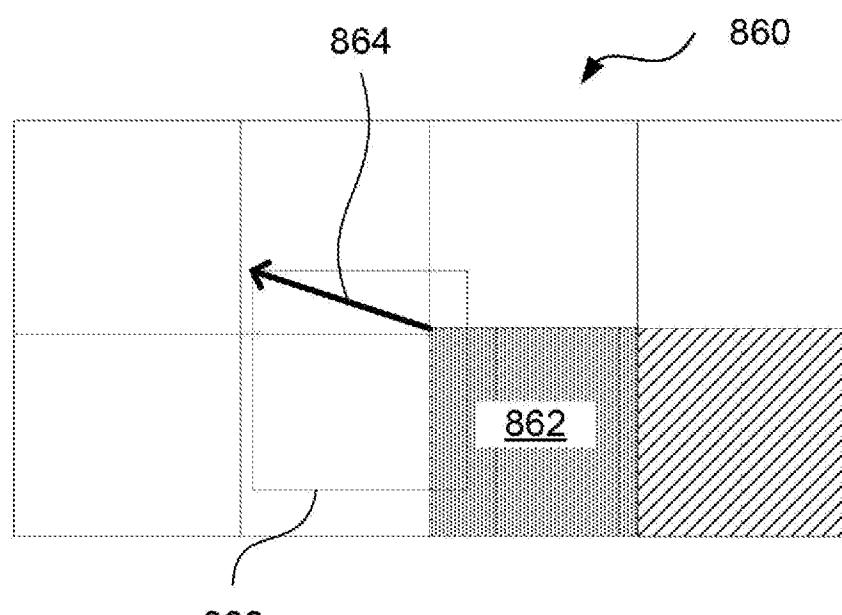

Fig. 8D is a schematic block diagram showing an example block vector referencing a block of samples where a reference block includes samples within a current coding unit (CU);

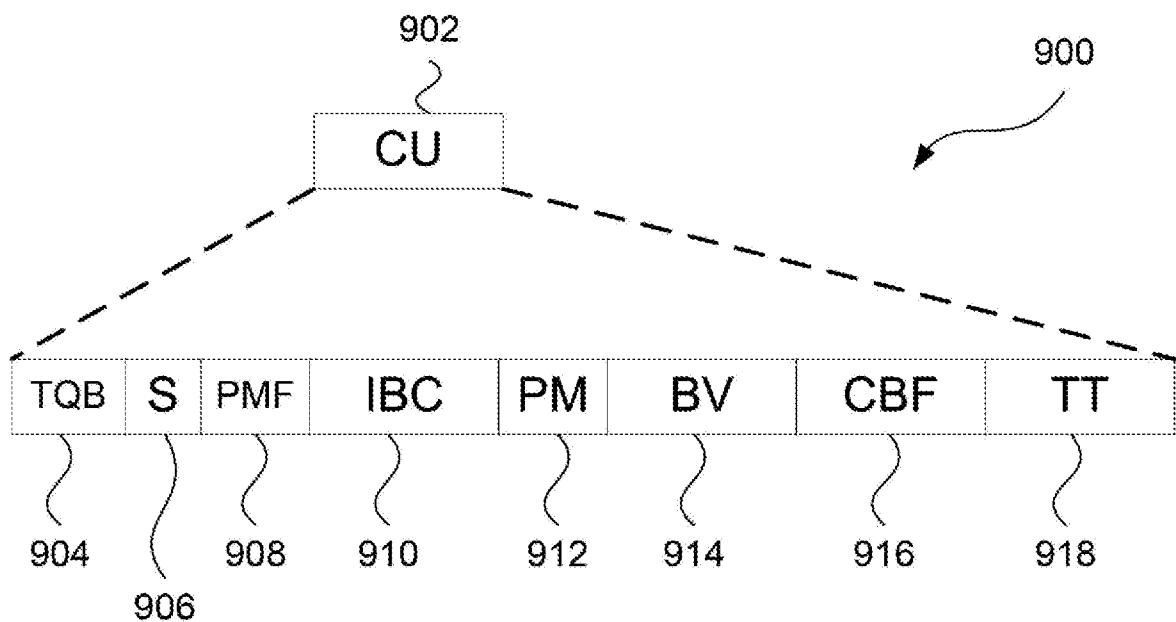

5 Fig. 9 is a schematic block diagram showing a coding unit (CU) syntax structure;

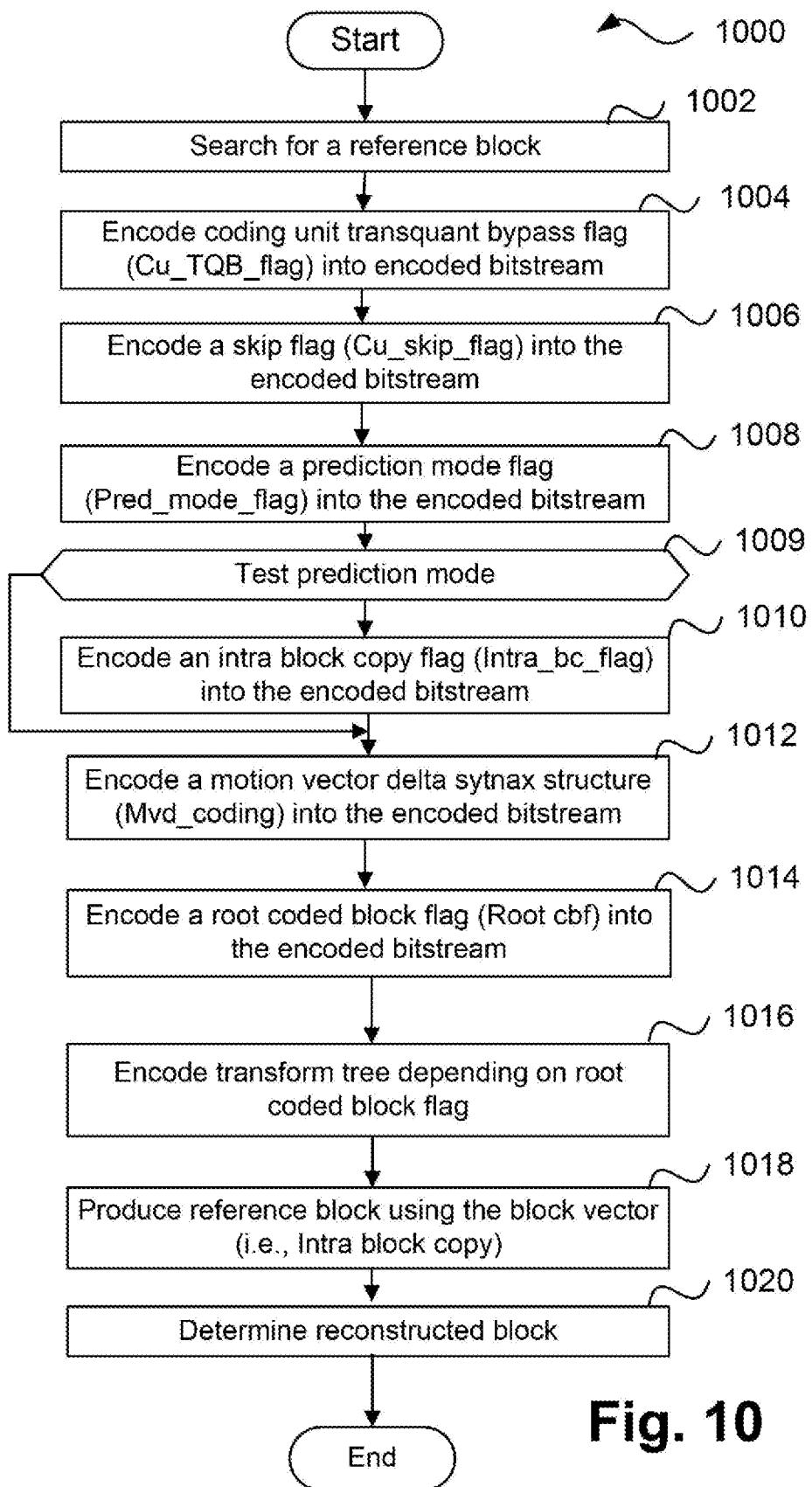

Fig. 10 is a schematic flow diagram showing a method of encoding a coding unit (CU) syntax structure into an encoded bitstream;

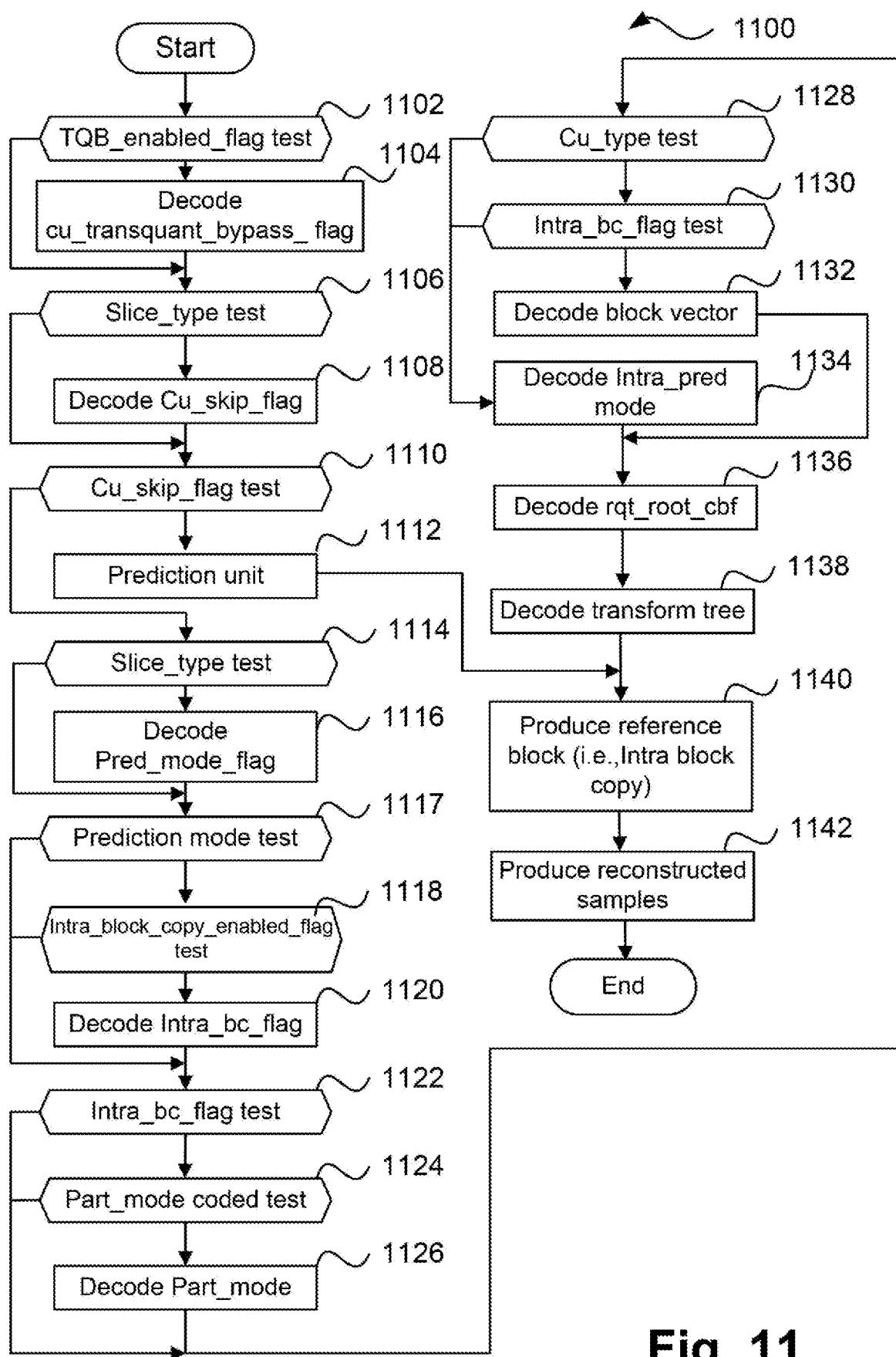

Fig. 11 is a schematic flow diagram showing a method of decoding a coding unit (CU) syntax structure from an encoded bitstream;

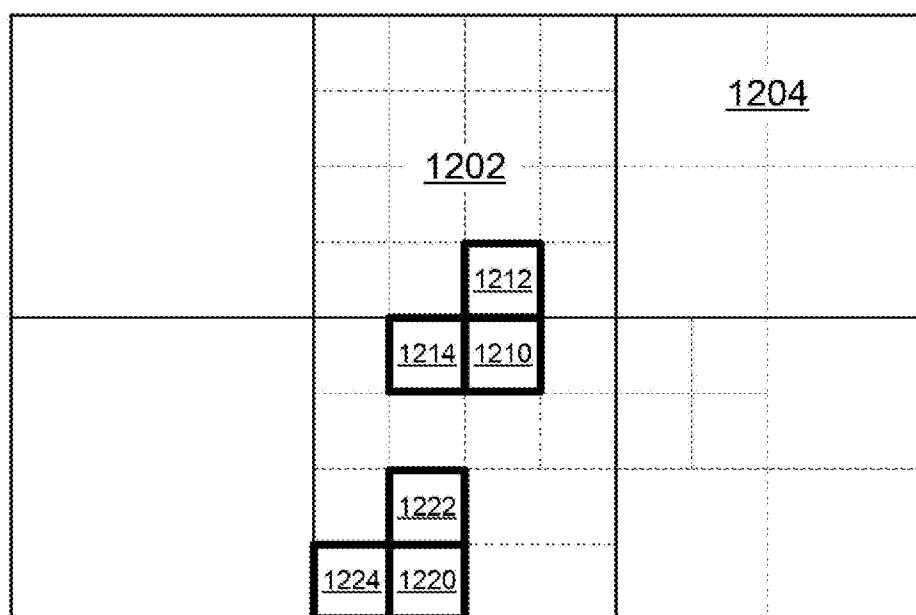

10 Fig. 12A is a schematic block diagram showing context selection for an intra block copy flag for a coding unit (CU);

Fig. 12B is a schematic block diagram showing context selection for an intra block copy flag for a coding unit (CU) aligned to the top of a coding tree block (CTB);

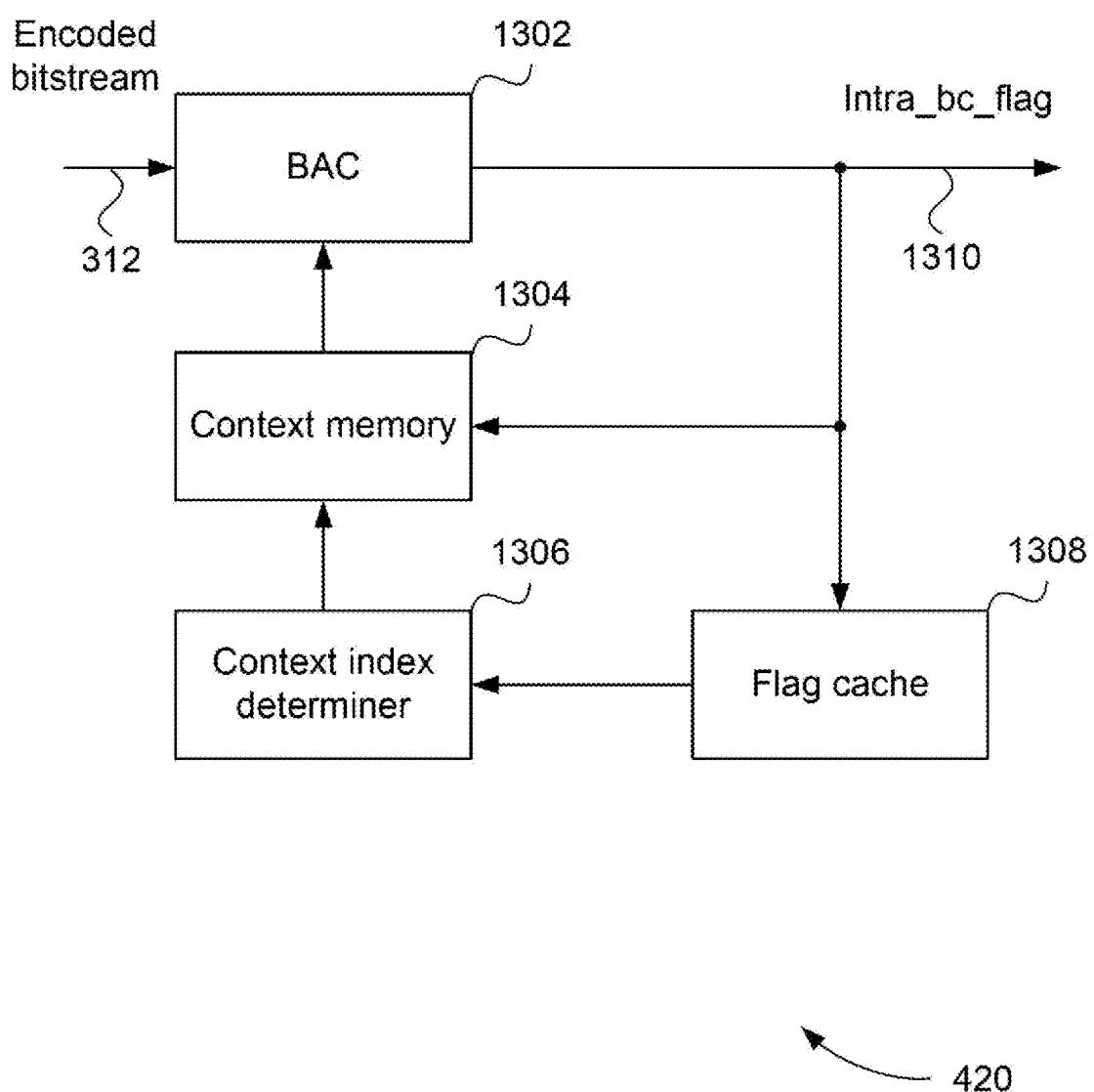

Fig. 13 is a schematic block diagram showing functional modules of the entropy decoder of Fig. 4;

15 Fig. 14 is a schematic flow diagram showing a method of decoding an intra block copy flag for a coding unit (CU);

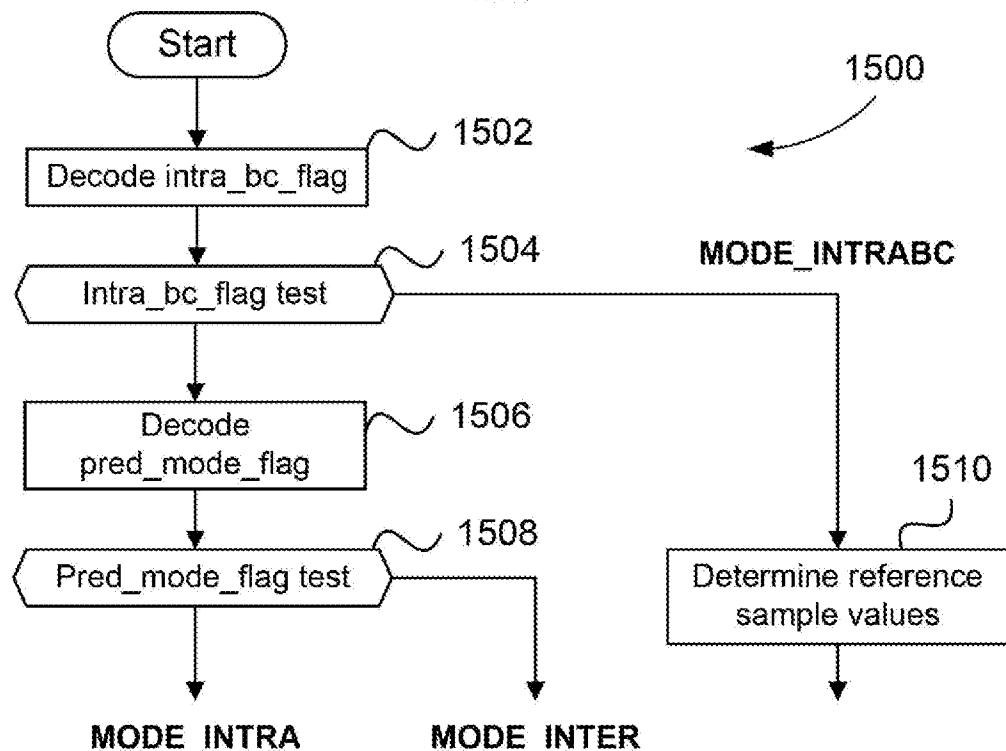

Fig. 15A is a schematic flow diagram showing a method of determining a prediction mode for a coding unit (CU);

20 Fig. 15B is a schematic flow diagram showing a method of determining a prediction mode for a coding unit (CU);

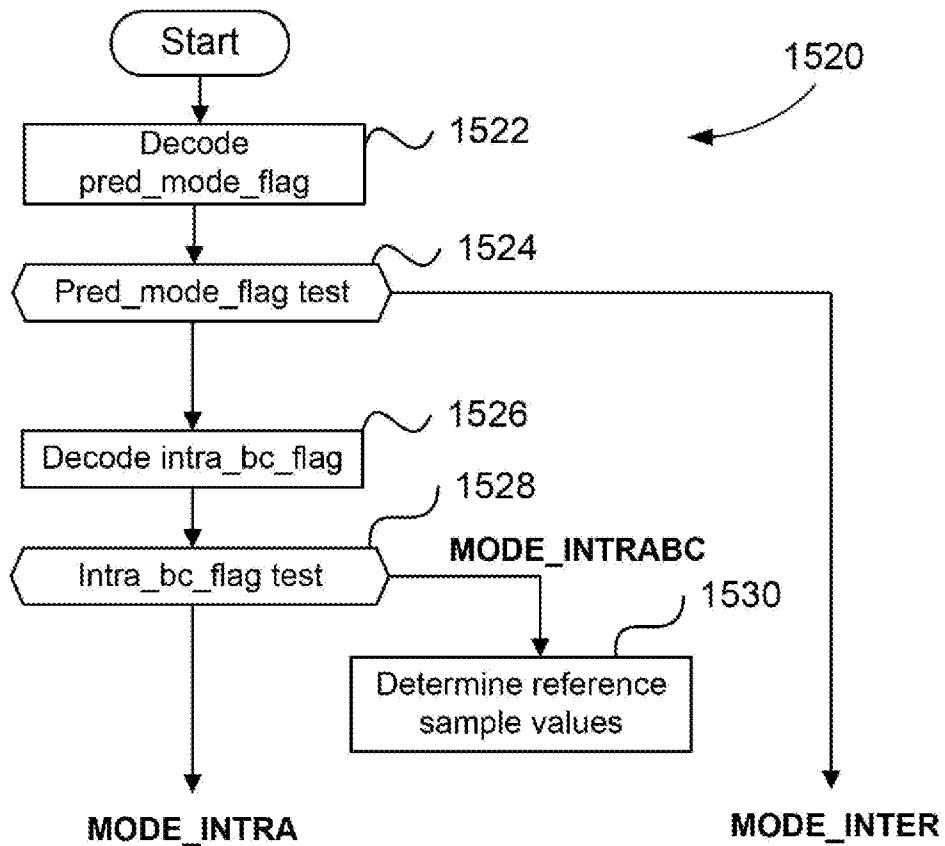

Fig. 16 is a schematic block diagram showing a residual quad-tree (RQT) in a coding unit (CU) within a coding tree block (CTB);

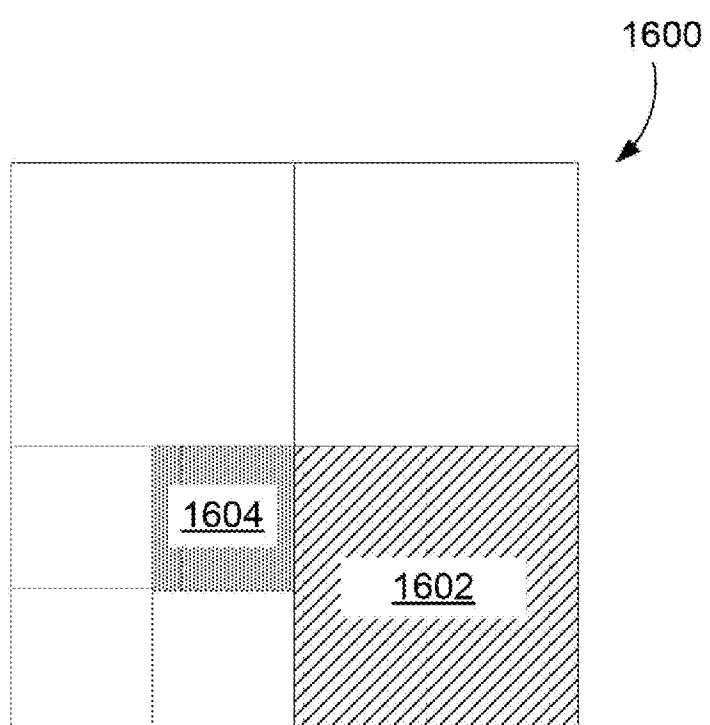

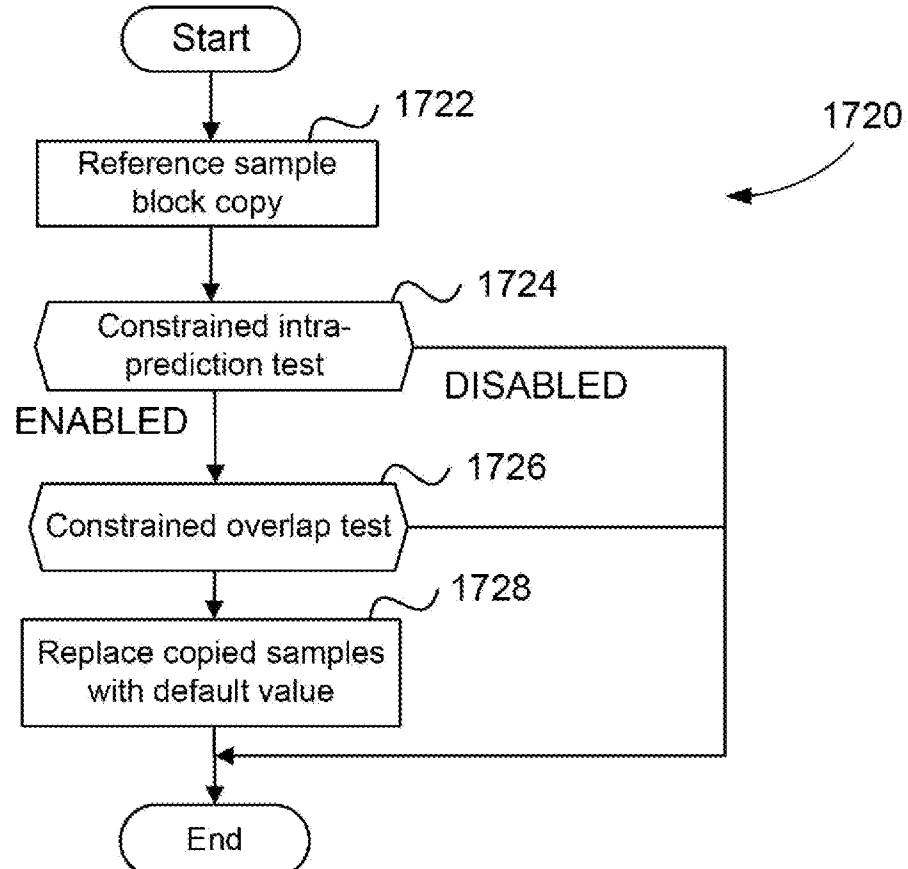

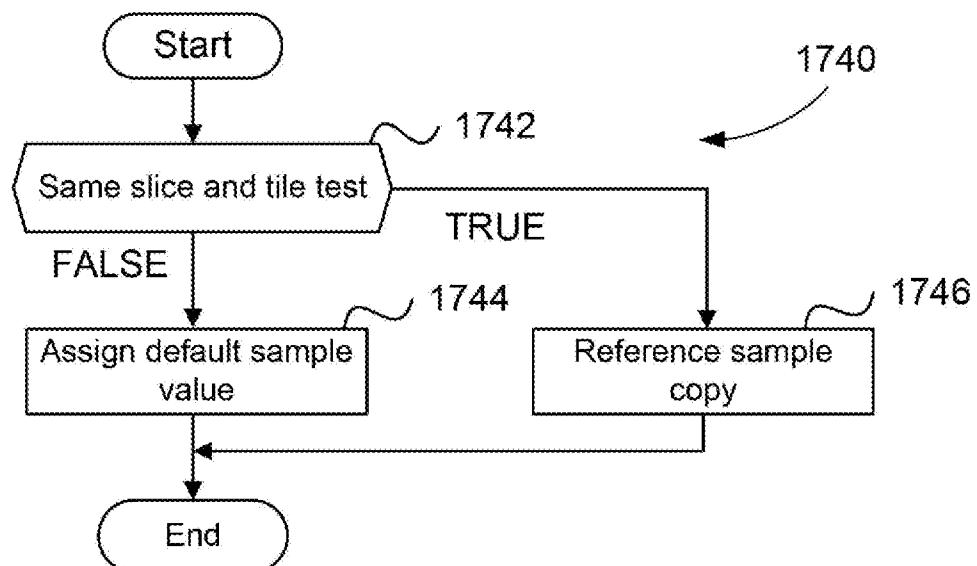

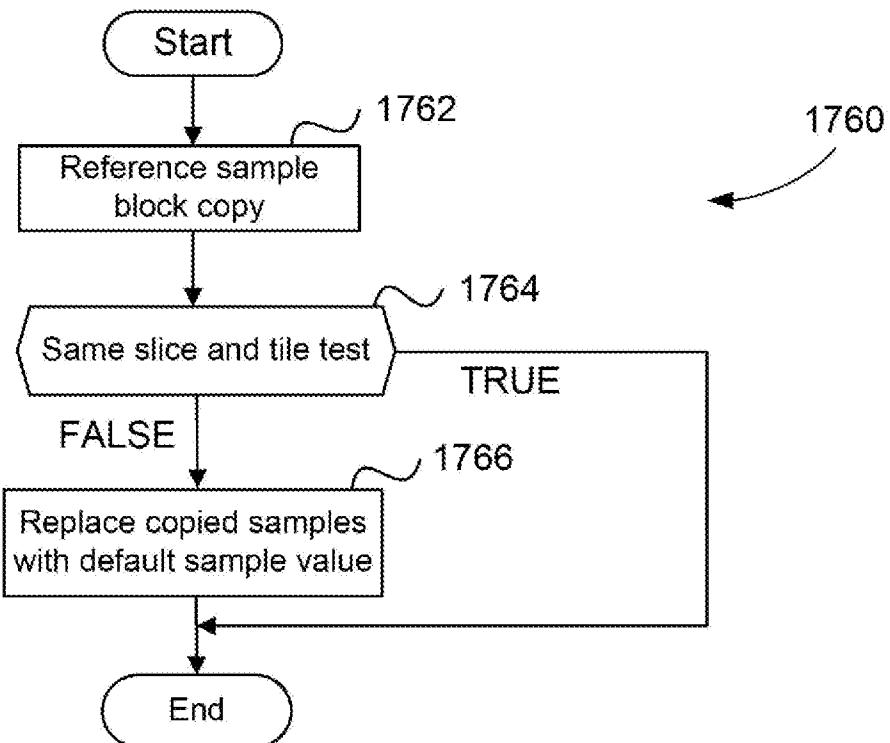

Fig. 17A is a schematic flow diagram showing a method of generating a reference sample block for a coding unit (CU) configured to use the intra block copy mode;

25 Fig. 17B is a schematic flow diagram showing a method of generating a reference sample block for a coding unit (CU) configured to use an intra block copy mode;

Fig. 17C is a schematic flow diagram showing a method of generating a reference sample block for a coding unit (CU) configured to use an intra block copy mode;

30 Fig. 17D is a schematic flow diagram showing a method of generating a reference sample block for a coding unit (CU) configured to use an intra block copy mode;

Fig. 18A is a schematic block diagram showing an example block vector referencing a block of samples where the origin of the block vector is relative to a point other than the current coding unit (CU) location; and

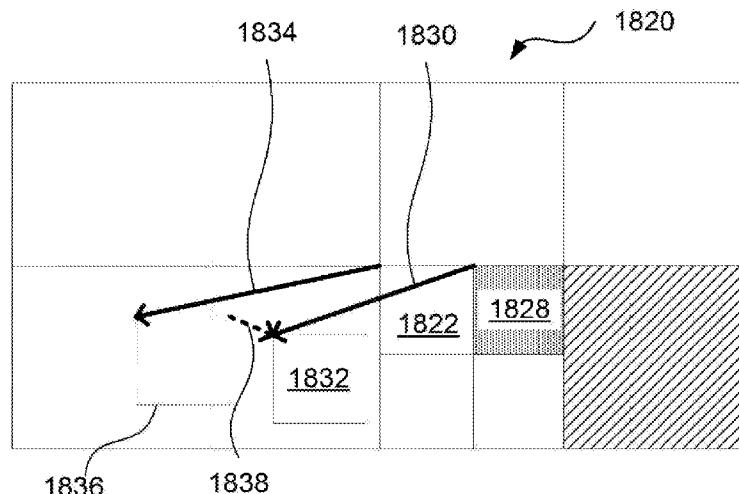

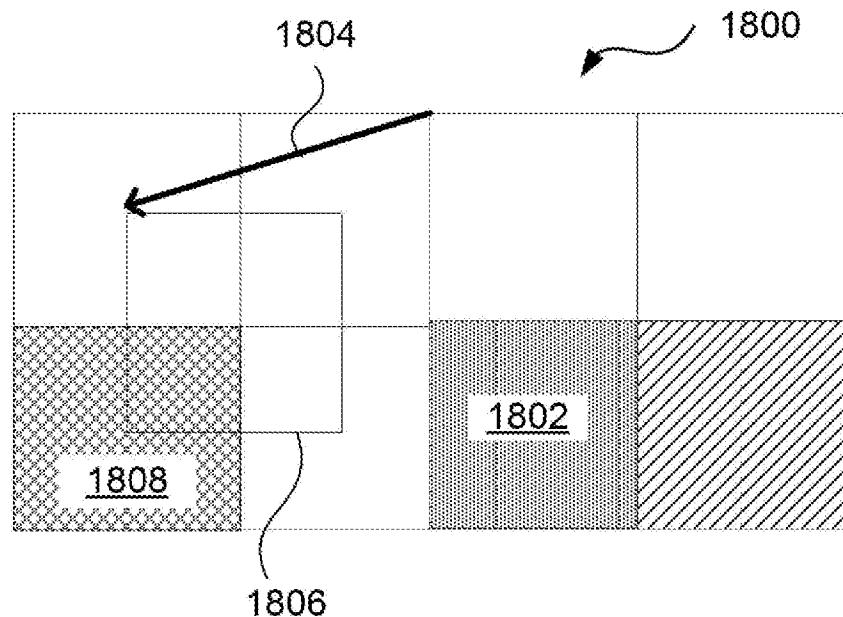

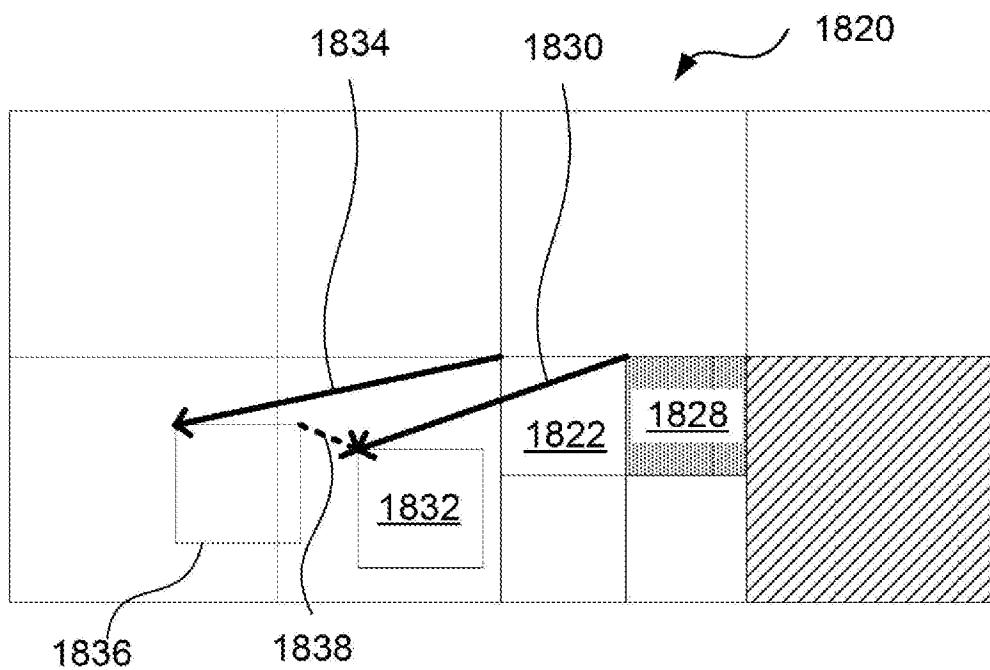

Fig. 18B is a schematic block diagram showing an example block vector representation between successive coding units (CUs) configured to use an intra block copy mode;

5 Appendix A shows a coding unit (CU) syntax structure according to the method of Fig. 11;

Appendix B shows a block vector conformance restriction according to Fig. 8C;

Appendix C shows an intra block copy method according to Fig. 8C;

Appendix D shows a context selection for intra\_bc\_flag according to an arrangement of the method of Fig. 14 with steps 1402-1408 omitted.

## 10 DETAILED DESCRIPTION INCLUDING BEST MODE

Where reference is made in any one or more of the accompanying drawings to steps and/or features, which have the same reference numerals, those steps and/or features have for the purposes of this description the same function(s) or operation(s), unless the contrary intention appears.

15 Fig. 1 is a schematic block diagram showing function modules of a video encoding and decoding system 100. The system 100 may utilise intra block copy techniques to reduce complexity, improve coding efficiency and improve error resilience. Complexity may be reduced by reducing the number of contexts present in the system 100 or by simplifying or removing rules used to select which context to use for a given context coded 20 bin. The system 100 includes a source device 110 and a destination device 130. A communication channel 120 is used to communicate encoded video information from the source device 110 to the destination device 130. In some arrangements, the source device 110 and destination device 130 may comprise respective mobile telephone hand-sets, in which case the communication channel 120 is a wireless channel. In other arrangements, 25 the source device 110 and destination device 130 may comprise video conferencing equipment, in which case the communication channel 120 is typically a wired channel, such as an internet connection. Moreover, the source device 110 and the destination device 130 may comprise any of a wide range of devices, including devices supporting over the air television broadcasts, cable television applications, internet video applications and 30 applications where encoded video data is captured on some storage medium or a file server.

As shown in Fig. 1, the source device 110 includes a video source 112, a video encoder 114 and a transmitter 116. The video source 112 typically comprises a source of

captured video frame data, such as an imaging sensor, a previously captured video sequence stored on a non-transitory recording medium, or a video feed from a remote imaging sensor. Examples of source devices 110 that may include an imaging sensor as the video source 112 include smart-phones, video camcorders and network video cameras.

5 The video encoder 114 converts the captured frame data from the video source 112 into encoded video data and will be described further with reference to Fig. 3. The encoded video data is typically transmitted by the transmitter 116 over the communication channel 120 as encoded video data (or "encoded video information"). It is also possible for the encoded video data to be stored in some storage device, such as a "Flash" memory or a 10 hard disk drive, until later being transmitted over the communication channel 120.

The destination device 130 includes a receiver 132, a video decoder 134 and a display device 136. The receiver 132 receives encoded video data from the communication channel 120 and passes received video data to the video decoder 134. The video decoder 134 then outputs decoded frame data to the display device 136. Examples 15 of the display device 136 include a cathode ray tube, a liquid crystal display, such as in smart-phones, tablet computers, computer monitors or in stand-alone television sets. It is also possible for the functionality of each of the source device 110 and the destination device 130 to be embodied in a single device.

Notwithstanding the example devices mentioned above, each of the source device 20 110 and destination device 130 may be configured within a general purpose computing system, typically through a combination of hardware and software components. Fig. 2A illustrates such a computer system 200, which includes: a computer module 201; input devices such as a keyboard 202, a mouse pointer device 203, a scanner 226, a camera 227, which may be configured as the video source 112, and a microphone 280; and output 25 devices including a printer 215, a display device 214, which may be configured as the display device 136, and loudspeakers 217. An external Modulator-Demodulator (Modem) transceiver device 216 may be used by the computer module 201 for communicating to and from a communications network 220 via a connection 221. The communications network 220, which may represent the communication channel 120, may be a wide-area network 30 (WAN), such as the Internet, a cellular telecommunications network, or a private WAN. Where the connection 221 is a telephone line, the modem 216 may be a traditional "dial-up" modem. Alternatively, where the connection 221 is a high capacity (e.g., cable) connection, the modem 216 may be a broadband modem. A wireless modem may also be

used for wireless connection to the communications network 220. The transceiver device 216 may provide the functionality of the transmitter 116 and the receiver 132 and the communication channel 120 may be embodied in the connection 221.

The computer module 201 typically includes at least one processor unit 205, and a 5 memory unit 206. For example, the memory unit 206 may have semiconductor random access memory (RAM) and semiconductor read only memory (ROM). The computer module 201 also includes an number of input/output (I/O) interfaces including: an audio-video interface 207 that couples to the video display 214, loudspeakers 217 and microphone 280; an I/O interface 213 that couples to the keyboard 202, mouse 203, 10 scanner 226, camera 227 and optionally a joystick or other human interface device (not illustrated); and an interface 208 for the external modem 216 and printer 215. In some implementations, the modem 216 may be incorporated within the computer module 201, for example within the interface 208. The computer module 201 also has a local network 15 interface 211, which permits coupling of the computer system 200 via a connection 223 to a local-area communications network 222, known as a Local Area Network (LAN). As illustrated in Fig. 2A, the local communications network 222 may also couple to the wide network 220 via a connection 224, which would typically include a so-called "firewall" device or device of similar functionality. The local network interface 211 may comprise an Ethernet<sup>TM</sup> circuit card, a Bluetooth<sup>TM</sup> wireless arrangement or an IEEE 802.11 wireless 20 arrangement. However, numerous other types of interfaces may be practiced for the interface 211. The local network interface 211 may also provide the functionality of the transmitter 116 and the receiver 132 and communication channel 120 may also be embodied in the local communications network 222.

The I/O interfaces 208 and 213 may afford either or both of serial and parallel 25 connectivity, the former typically being implemented according to the Universal Serial Bus (USB) standards and having corresponding USB connectors (not illustrated). Storage devices 209 are provided and typically include a hard disk drive (HDD) 210. Other storage devices such as a floppy disk drive and a magnetic tape drive (not illustrated) may also be used. An optical disk drive 212 is typically provided to act as a non-volatile source of 30 data. Portable memory devices, such optical disks (e.g. CD-ROM, DVD, Blu-ray Disc<sup>TM</sup>), USB-RAM, portable, external hard drives, and floppy disks, for example, may be used as appropriate sources of data to the computer system 200. Typically, any of the HDD 210, optical drive 212, networks 220 and 222 may also be configured to operate as the video

source 112, or as a destination for decoded video data to be stored for reproduction via the display 214.

The components 205 to 213 of the computer module 201 typically communicate via an interconnected bus 204 and in a manner that results in a conventional mode of operation 5 of the computer system 200 known to those in the relevant art. For example, the processor 205 is coupled to the system bus 204 using a connection 218. Likewise, the memory 206 and optical disk drive 212 are coupled to the system bus 204 by connections 219. Examples of computers on which the described arrangements can be practised include IBM-PC's and compatibles, Sun SPARCstations, Apple Mac<sup>TM</sup> or alike computer 10 systems.

Where appropriate or desired, the video encoder 114 and the video decoder 134, as well as methods described below, may be implemented using the computer system 200. In particular, the video encoder 114, the video decoder 134 and the methods of Figs. 10, 11, 14, 15A, 15B, 17A, 17B, 17C and 17D to be described, may be implemented as one or 15 more software application programs 233 executable within the computer system 200. The video encoder 114, the video decoder 134 and the steps of the described methods may be effected by instructions 231 (see Fig. 2B) in the software 233 that are carried out within the computer system 200. The software instructions 231 may be formed as one or more code modules, each for performing one or more particular tasks. The software may also be 20 divided into two separate parts, in which a first part and the corresponding code modules performs the described methods and a second part and the corresponding code modules manage a user interface between the first part and the user.

The software may be stored in a computer readable medium, including the storage devices described below, for example. The software is loaded into the computer system 25 200 from the computer readable medium, and then executed by the computer system 200. A computer readable medium having such software or computer program recorded on the computer readable medium is a computer program product. The use of the computer program product in the computer system 200 preferably effects an advantageous apparatus for implementing the video encoder 114, the video decoder 134 and the described methods.

30 The software 233 is typically stored in the HDD 210 or the memory 206. The software is loaded into the computer system 200 from a computer readable medium, and executed by the computer system 200. Thus, for example, the software 233 may be stored

on an optically readable disk storage medium (e.g., CD-ROM) 225 that is read by the optical disk drive 212.

In some instances, the application programs 233 may be supplied to the user encoded on one or more CD-ROMs 225 and read via the corresponding drive 212, or 5 alternatively may be read by the user from the networks 220 or 222. Still further, the software can also be loaded into the computer system 200 from other computer readable media. Computer readable storage media refers to any non-transitory tangible storage medium that provides recorded instructions and/or data to the computer system 200 for execution and/or processing. Examples of such storage media include floppy disks, 10 magnetic tape, CD-ROM, DVD, Blu-ray Disc, a hard disk drive, a ROM or integrated circuit, USB memory, a magneto-optical disk, or a computer readable card such as a PCMCIA card and the like, whether or not such devices are internal or external of the computer module 201. Examples of transitory or non-tangible computer readable transmission media that may also participate in the provision of the software, application 15 programs, instructions and/or video data or encoded video data to the computer module 401 include radio or infra-red transmission channels as well as a network connection to another computer or networked device, and the Internet or Intranets including e-mail transmissions and information recorded on Websites and the like.

The second part of the application programs 233 and the corresponding code 20 modules mentioned above may be executed to implement one or more graphical user interfaces (GUIs) to be rendered or otherwise represented upon the display 214. Through manipulation of typically the keyboard 202 and the mouse 203, a user of the computer system 200 and the application may manipulate the interface in a functionally adaptable manner to provide controlling commands and/or input to the applications associated with 25 the GUI(s). Other forms of functionally adaptable user interfaces may also be implemented, such as an audio interface utilizing speech prompts output via the loudspeakers 217 and user voice commands input via the microphone 280.

Fig. 2B is a detailed schematic block diagram of the processor 205 and a “memory” 234. The memory 234 represents a logical aggregation of all the memory 30 modules (including the HDD 209 and semiconductor memory 206) that can be accessed by the computer module 201 in Fig. 2A.

When the computer module 201 is initially powered up, a power-on self-test (POST) program 250 executes. The POST program 250 is typically stored in a ROM 249

of the semiconductor memory 206 of Fig. 2A. A hardware device such as the ROM 249 storing software is sometimes referred to as firmware. The POST program 250 examines hardware within the computer module 201 to ensure proper functioning and typically checks the processor 205, the memory 234 (209, 206), and a basic input-output systems 5 software (BIOS) module 251, also typically stored in the ROM 249, for correct operation. Once the POST program 250 has run successfully, the BIOS 251 activates the hard disk drive 210 of Fig. 2A. Activation of the hard disk drive 210 causes a bootstrap loader program 252 that is resident on the hard disk drive 210 to execute via the processor 205. This loads an operating system 253 into the RAM memory 206, upon which the operating 10 system 253 commences operation. The operating system 253 is a system level application, executable by the processor 205, to fulfil various high level functions, including processor management, memory management, device management, storage management, software application interface, and generic user interface.

The operating system 253 manages the memory 234 (209, 206) to ensure that each 15 process or application running on the computer module 201 has sufficient memory in which to execute without colliding with memory allocated to another process. Furthermore, the different types of memory available in the computer system 200 of Fig. 2A must be used properly so that each process can run effectively. Accordingly, the aggregated memory 234 is not intended to illustrate how particular segments of memory 20 are allocated (unless otherwise stated), but rather to provide a general view of the memory accessible by the computer system 200 and how such is used.

As shown in Fig. 2B, the processor 205 includes a number of functional modules including a control unit 239, an arithmetic logic unit (ALU) 240, and a local or internal memory 248, sometimes called a cache memory. The cache memory 248 typically 25 includes a number of storage registers 244-246 in a register section. One or more internal busses 241 functionally interconnect these functional modules. The processor 205 typically also has one or more interfaces 242 for communicating with external devices via the system bus 204, using a connection 218. The memory 234 is coupled to the bus 204 using a connection 219.

30 The application program 233 includes a sequence of instructions 231 that may include conditional branch and loop instructions. The program 233 may also include data 232 which is used in execution of the program 233. The instructions 231 and the data 232 are stored in memory locations 228, 229, 230 and 235, 236, 237, respectively.

Depending upon the relative size of the instructions 231 and the memory locations 228-230, a particular instruction may be stored in a single memory location as depicted by the instruction shown in the memory location 230. Alternately, an instruction may be segmented into a number of parts each of which is stored in a separate memory location, as 5 depicted by the instruction segments shown in the memory locations 228 and 229.

In general, the processor 205 is given a set of instructions which are executed therein. The processor 205 waits for a subsequent input, to which the processor 205 reacts to by executing another set of instructions. Each input may be provided from one or more of a number of sources, including data generated by one or more of the input devices 10 + 202, 203, data received from an external source across one of the networks 220, 202, data retrieved from one of the storage devices 206, 209 or data retrieved from a storage medium 225 inserted into the corresponding reader 212, all depicted in Fig. 2A. The execution of a set of the instructions may in some cases result in output of data. Execution may also involve storing data or variables to the memory 234.

15 The video encoder 114, the video decoder 134 and the described methods may use input variables 254, which are stored in the memory 234 in corresponding memory locations 255, 256, 257. The video encoder 114, the video decoder 134 and the described methods produce output variables 261, which are stored in the memory 234 in corresponding memory locations 262, 263, 264. Intermediate variables 258 may be stored 20 in memory locations 259, 260, 266 and 267.

Referring to the processor 205 of Fig. 2B, the registers 244, 245, 246, the arithmetic logic unit (ALU) 240, and the control unit 239 work together to perform sequences of micro-operations needed to perform "fetch, decode, and execute" cycles for every instruction in the instruction set making up the program 233. Each fetch, decode, 25 and execute cycle comprises:

- (a) a fetch operation, which fetches or reads an instruction 231 from a memory location 228, 229, 230;

- (b) a decode operation in which the control unit 239 determines which instruction has been fetched; and

- 30 (c) an execute operation in which the control unit 239 and/or the ALU 240 execute the instruction.

Thereafter, a further fetch, decode, and execute cycle for the next instruction may be executed. Similarly, a store cycle may be performed by which the control unit 239 stores or writes a value to a memory location 232.

Each step or sub-process in the methods Figs. 9 and 10 to be described is associated 5 with one or more segments of the program 233 and is typically performed by the register section 244, 245, 247, the ALU 240, and the control unit 239 in the processor 205 working together to perform the fetch, decode, and execute cycles for every instruction in the instruction set for the noted segments of the program 233.

Fig. 3 is a schematic block diagram showing functional modules of the video 10 encoder 114. Fig. 4 is a schematic block diagram showing functional modules of the video decoder 134. Generally, data is passed between functional modules of the video encoder 114 and the video decoder 134 in blocks or arrays such as, for example, blocks of samples 15 or blocks of transform coefficients. Where a functional module is described with reference to the behaviour of individual array elements (e.g., samples or transform coefficients), the behaviour shall be understood to be applied to all array elements.

The video encoder 114 and video decoder 134 may be implemented using a general-purpose computer system 200, as shown in Figs. 2A and 2B, where the various functional modules may be implemented by dedicated hardware within the computer system 200. Alternatively, the various functional modules of the video encoder 114 and 20 video decoder 134 may be implemented by software executable within the computer system 200, such as one or more software code modules of the software application program 233 resident on the hard disk drive 205 and being controlled in its execution by the processor 205. In another alternative, the various functional modules of the video encoder 114 and video decoder 134 may be implemented by a combination of dedicated 25 hardware and software executable within the computer system 200. The video encoder 114, the video decoder 134 and the described methods may alternatively be implemented in dedicated hardware, such as one or more integrated circuits performing the functions or sub functions of the described methods. Such dedicated hardware may include graphic processors, digital signal processors, application specific integrated circuits (ASICs), field 30 programmable gate arrays (FPGAs) or one or more microprocessors and associated memories. In particular, the video encoder 114 comprises modules 320-350 and the video decoder 134 comprises modules 420-436 which may each be implemented as one or more software code modules of the software application program 233.

Although the video encoder 114 of Fig. 3 is an example of a high efficiency video coding (HEVC) video encoding pipeline, other video codecs may also be used to perform the processing stages described herein. The video encoder 114 receives captured frame data, such as a series of frames, each frame including one or more colour channels.

5 The video encoder 114 divides each frame of the captured frame data, such as frame data 310, into regions generally referred to as 'coding tree blocks' (CTBs). The frame data 310 includes one or more colour planes. Each colour plane includes samples. Each sample occupies a binary word sized according to a bit-depth 390. Thus, the range of possible sample values is defined by the bit-depth 390. For example, if the bit-depth 390 is

10 set to eight (8) bits, sample values may be from zero (0) to two hundred and fifty five (255). Each coding tree block (CTB) includes a hierarchical quad-tree subdivision of a portion of the frame into a collection of 'coding units' (CUs). A coding tree block (CTB) generally occupies an area of 64x64 luma samples, although other sizes are possible, such as 16x16 or 32x32. In some cases even larger sizes for the coding tree block (CTB), such

15 as 128x128 luma samples, may be used. The coding tree block (CTB) may be sub-divided via a split into four equal sized regions to create a new hierarchy level. Splitting may be applied recursively, resulting in a quad-tree hierarchy (or "coding tree"). As the coding tree block (CTB) side dimensions are powers of two and the quad-tree splitting results in a halving of the width and height, the region side dimensions are also powers of two. When

20 no further split of a region is performed, a 'coding unit' (CU) is said to exist within the region. When no split is performed at the top level (or typically the "highest level") of the coding tree block, the region occupying the entire coding tree block contains one coding unit (CU). In such cases, the coding unit (CU) is generally referred to as a 'largest coding unit' (LCU). A minimum size also exists for each coding unit (CU), such as the area

25 occupied by 8x8 luma samples, although other minimum sizes are also possible (e.g. 16x16 luma samples or 32x32 luma samples). Coding units of the minimum size are generally referred to as 'smallest coding units' (SCUs). As a result of the quad-tree hierarchy, the entirety of the coding tree block (CTB) is occupied by one or more coding units (CUs). Each coding unit (CU) is associated with one or more arrays of data samples, generally

30 referred to as 'prediction units' (PUs). Various arrangements of prediction units (PUs) in each coding unit (CU) are possible, with a requirement that the prediction units (PUs) do not overlap and that the entirety of the coding unit (CU) is occupied by the one or more prediction units (PUs). Such a requirement ensures that the prediction units (PUs) cover

the entire frame area. The arrangement of the one or more prediction units (PUs) associated with a coding unit (CU) is referred to as a 'partition mode'.

The video encoder 114 operates by outputting, from a multiplexer module 340, a prediction unit (PU) 382 in accordance with the partition mode of a coding unit (CU). A 5 difference module 344 produces a 'residual sample array' 360. The residual sample array 360 is the difference between the prediction unit (PU) 382 and a corresponding 2D array of data samples from a coding unit (CU) of the coding tree block (CTB) of the frame data 310. The difference is calculated for corresponding samples at each location in the arrays. As differences may be positive or negative, the dynamic range of one difference sample is 10 the bit-depth plus one bit.

The residual sample array 360 may be transformed into the frequency domain in a transform module 320. The residual sample array 360 from the difference module 344 is received by the transform module 320, which converts the residual sample array 360 from a spatial representation to a frequency domain representation by applying a 'forward 15 transform'. The transform module 320 creates transform coefficients, according to a transform having a specific precision. The coding unit (CU) is sub-divided into one or more transform units (TUs). The sub-division of the coding unit (CU) into one or more transform units (TUs) may be referred to as a 'residual quad-tree' or a 'residual quad-tree (RQT)' or a 'transform tree'.

20 The quantiser control module 346 may test the bit-rate required in encoded bitstream 312 for various possible quantisation parameter values according to a 'rate-distortion criterion'. The rate-distortion criterion is a measure of the acceptable trade-off between the bit-rate of the encoded bitstream 312, or a local region thereof, and distortion. Distortion is a measure of the difference between frames present in the frame buffer 332 25 and the captured frame data 310. Methods of measuring distortion include using a peak signal to noise ratio (PSNR) or sum of absolute differences (SAD) metric. In some arrangements of the video encoder 114, the rate-distortion criterion considers only the rate and distortion for the luma colour channel and thus the encoding decision is made based on characteristics of the luma channel. Generally, the residual quad-tree (RQT) is shared 30 between the luma and chroma colour channels, and the amount of chroma information is relatively small compared to luma, so considering luma only in the rate-distortion criterion may be appropriate.

A quantisation parameter 384 is output from the quantiser control module 346. The quantisation parameter may be fixed for a frame of video data, or may vary on a block by block basis as the frame is being encoded. Other methods for controlling the quantisation parameter 384 are also possible. The set of possible transform units (TUs) for a residual quad-tree is dependent on the available transform sizes and coding unit (CU) size. In one arrangement, the residual quad-tree results in a lower bit-rate in the encoded bitstream 312, thus achieving higher coding efficiency. A larger sized transform unit (TU) results in use of larger transforms for both the luma and chroma colour channels. Generally, larger transforms provide a more compact representation of a residual sample array with sample data (or ‘residual energy’) spread across the residual sample array. Smaller transforms generally provide a more compact representation of a residual sample array with residual energy localised to specific regions of the residual sample array compared to larger transforms. Thus, the many possible configurations of a residual quad-tree (RQT) provide a useful means for achieving high coding efficiency of the residual sample array 360 in the high efficiency video coding (HEVC) standard.

A transform control module 348 selects a transform size for use in encoding each leaf node of the residual quad-tree (RQT). For example, a variety of transform sizes (and hence residual quad-tree configurations or transform trees) may be tested and the transform tree resulting in the best trade-off from a rate-distortion criteria may be selected. A transform size 386 represents a size of a selected transform. The transform size 386 is encoded in the encoded bitstream 312 and provided to the transform module 320, the quantiser module 322, the dequantiser module 326 and the inverse transform module 328. The transform size 386 may be represented by the transform dimensions (e.g. 4x4, 8x8, 16x16 or 32x32), the transform size (e.g. 4, 8, 16 or 32), or the log2 of the transform size (e.g. 2, 3, 4 or 5) interchangeably. In circumstances where the numeric value of a particular representation of a transform size is used (e.g. in an equation) conversion from any other representation of the transform size deemed necessary, shall be considered to implicitly occur in the following description.

The video encoder 114 may be configured to perform in a ‘transform quantisation bypass’ mode, where the transform module 320 and the quantisation module 322 are bypassed. In the transform quantisation bypass mode, the video encoder 114 provides a means to losslessly encode the frame data 310 in the encoded bitstream 312. Use of the transform quantisation bypass mode is controlled at the coding unit (CU) level, allowing

portions of the frame data 310 to be losslessly encoded by the video encoder 114. The availability of the transform quantisation bypass mode is controlled via 'high level syntax', enabling signalling overhead of controlling transform quantisation bypass mode to be removed in cases where lossless encoding is not required in any portion of the frame data 5 310. High level syntax refers to syntax structures present in the encoded bitstream 312 that are generally encoded infrequently and are used to describe properties of the bitstream 312. For example, the high level syntax structures of the encoded bitstream 312 may be used to restrict or otherwise configure particular coding tools used in the video encoder 114 and the video decoder 134. Examples of high level syntax structures include 'sequence 10 parameter sets', 'picture parameter sets' and 'slice headers'.

For the high efficiency video coding (HEVC) standard, conversion of the residual sample array 360 to the frequency domain representation is implemented using a transform, such as a modified discrete cosine transform (DCT). In such transforms, the modification permits implementation using shifts and additions instead of multiplications. 15 Such modifications enable reduced implementation complexity compared to a discrete cosine transform (DCT). In addition to the modified discrete cosine transform (DCT), a modified discrete sine transform (DST) may also be used in specific circumstances. Various sizes of the residual sample array 360 and the scaled transform coefficients 362 are possible, in accordance with supported transform sizes. In the high efficiency video 20 coding (HEVC) standard, transforms are performed on 2D arrays of data samples having sizes, such as 32x32, 16x16, 8x8 and 4x4. Thus, a predetermined set of transform sizes are available to the video encoder 114. Moreover, the set of transform sizes may differ between the luma channel and the chroma channels.

Two-dimensional transforms are generally configured to be 'separable', enabling 25 implementation as a first set of 1D transforms operating on the 2D array of data samples in one direction (e.g. on rows). The first set of 1D transforms is followed by a second set of 1D transform operating on the 2D array of data samples output from the first set of 1D transforms in the other direction (e.g. on columns). Transforms having the same width and height are generally referred to as 'square transforms'. Additional transforms, having 30 differing widths and heights may also be used and are generally referred to as 'non-square transforms'. The row and column one-dimensional transforms may be combined into specific hardware or software modules, such as a 4x4 transform module or an 8x8 transform module.

Transforms having larger dimensions require larger amounts of circuitry to implement, even though such larger dimensioned transforms may be infrequently used. Accordingly, the high efficiency video coding (HEVC) standard defines a maximum transform size of 32x32 luma samples. Transforms may be applied to both the luma and 5 chroma channels. Differences between the handling of luma and chroma channels with regard to transform units (TUs) exist. Each residual quad-tree occupies one coding unit (CU) and is defined as a quad-tree decomposition of the coding unit (CU) into a hierarchy including one transform unit (TU) at each leaf node of the residual quad-tree hierarchy. Each transform unit (TU) has dimensions corresponding to one of the supported transform 10 sizes. Similarly to the coding tree block (CTB), it is necessary for the entirety of the coding unit (CU) to be occupied by one or more transform units (TUs). At each level of the residual quad-tree hierarchy a ‘coded block flag value’ signals possible presence of a transform in each colour channel. The signalling may indicate presence of a transform at the current hierarchy level (when no further splits are present), or that lower hierarchy 15 levels may contain at least one transform among the resulting transform units (TUs). When the coded block flag value is zero, all residual coefficients at the present or lower hierarchy levels are known to be zero. In such a case, no transform is required to be performed for the corresponding colour channel of any transform units (TU) at the present hierarchical level or at lower hierarchical levels. When the coded block flag value is one, 20 if the present region is not further sub-divided then the region contains a transform which requires at least one non-zero residual coefficient. If the present region is further sub-divided, a coded block flag value of one indicates that each resulting sub-divided region may include non-zero residual coefficients. In this manner, for each colour channel, zero or more transforms may cover a portion of the area of the coding unit (CU) varying from 25 none up to the entirety of the coding unit (CU). Separate coded block flag values exist for each colour channel. Each coded block flag value is not required to be encoded, as cases exist where there is only one possible coded block flag value.

The scaled transform coefficients 362 are input to the quantiser module 322 where data sample values thereof are scaled and quantised, according to a determined 30 quantisation parameter 384, to produce transform coefficients 364. The transform coefficients 364 are an array of values having the same dimensions as the residual sample array 360. The transform coefficients 364 provide a frequency domain representation of the residual sample array 360 when a transform is applied. When the transform is skipped,

the transform coefficients 364 provide a spatial domain representation of the residual sample array 360 (i.e. quantised by the quantiser module 322 but not transformed by the transform module 320). For the discrete cosine transform (DCT), the upper-left value of the transform coefficients 364 specifies a 'DC' value for the residual sample array 360 and 5 is known as a 'DC coefficient'. The DC coefficient is representative of the 'average' of the values of the residual sample array 360. Other values in the transform coefficients 364 specify 'AC coefficients' for the residual sample array 360. The scale and quantisation results in a loss of precision, dependent on the value of the determined quantisation parameter 384. A higher value of the determined quantisation parameter 384 results in 10 coarser quantisation and hence greater information being lost from the scaled transform coefficients 362. The loss of information increases the compression achieved by the video encoder 114, as there is less information to encode. The increase in compression efficiency occurs at the expense of reducing the visual quality of output from the video decoder 134. For example, a reduction in the peak signal to noise ratio (PSNR) of the 15 decoded frames 412 compared to the frame data 310. The determined quantisation parameter 384 may be adapted during encoding of each frame of the frame data 310. Alternatively, the determined quantisation parameter 384 may be fixed for a portion of the frame data 310. In one arrangement, the determined quantisation parameter 384 may be fixed for an entire frame of frame data 310. Other adaptations of the determined 20 quantisation parameter 384 are also possible, such as quantising each of the scaled transform coefficients 362 with separate values.

The transform coefficients 364 and determined quantisation parameter 384 are taken as input to the dequantiser module 326. The dequantiser module 326 reverses the scaling performed by the quantiser module 322 to produce rescaled transform coefficients 25 366. The rescaled transform coefficients are rescaled versions of the transform coefficients 364. The transform coefficients 364, the determined quantisation parameter 384, the transform size 386 and the bit-depth 390 are also taken as input to an entropy encoder module 324. The entropy encoder module 324 encodes the values of the transform coefficients 364 in an encoded bitstream 312. The encoded bitstream 312 may also be 30 referred to as a 'video bitstream'. Due to a loss of precision (e.g. resulting from the operation of the quantiser module 322), the rescaled transform coefficients 366 are not identical to the original values in the scaled transform coefficients 362. The rescaled

transform coefficients 366 from the dequantiser module 326 are then output to an inverse transform module 328.

The inverse transform module 328 performs an inverse transform from the frequency domain to the spatial domain to produce a spatial-domain representation 368 of 5 the rescaled transform coefficients 366. The spatial-domain representation 368 is substantially identical to a spatial domain representation that is produced at the video decoder 134. The spatial-domain representation 368 is then input to a summation module 342.

A motion estimation module 338 produces motion vectors 374 by comparing the 10 frame data 310 with previous frame data from one or more sets of frames stored in a frame buffer module 332, generally configured within the memory 206. The sets of frames are known as 'reference pictures' and are enumerated in 'reference picture lists'. The motion vectors 374 are then input to a motion compensation module 334 which produces an inter-predicted prediction unit (PU) 376 by filtering data samples stored in the frame buffer 15 module 332, taking into account a spatial offset derived from the motion vectors 374. Not illustrated in Fig. 3, the motion vectors 374 are also passed to the entropy encoder module 324 for encoding in the encoded bitstream 312. The motion vectors may be encoded as 'motion vector differences' (or 'motion vector deltas') representing differences between the motion vector for a current block and a predicted motion vector. The predicted motion 20 vector may be determined from one or more spatially or temporally neighbouring blocks. The predicted motion vector may be used for a current block without encoding a motion vector difference. A coding unit (CU) having no motion vector difference or residual coefficients in the encoded bitstream 312 is referred to as a 'skipped' block.

The intra-frame prediction module 336 produces an intra-predicted prediction unit 25 (PU) 378 using samples 370 obtained from the summation module 342. In particular, the intra-frame prediction module 336 uses samples from neighbouring blocks that have already been decoded to produce intra-predicted samples for the current prediction unit (PU). When a neighbouring block is not available (e.g. at a frame boundary) the neighbouring samples are considered as 'not available' for reference. In such cases, a 30 default value may be used instead of the neighbouring sample values. Typically, the default value (or 'half-tone') is equal to half of the range implied by the bit-depth. For example, when the video encoder 114 is configured for a bit-depth of eight (8), the default value is 128. The summation module 342 sums the prediction unit (PU) 382 from the

multiplexer module 340 and the spatial domain output of the multiplexer 382. The intra-frame prediction module 336 also produces an intra-prediction mode 380 which is sent to the entropy encoder 324 for encoding into the encoded bitstream 312.

An intra block copy module 350 tests various block vectors to produce a reference block for the prediction unit (PU) 382. The reference block includes a block of samples 370 obtained from the current coding tree block (CTB) and/or the previous coding tree block (CTB). The reference block does not include samples from any coding units (CUs) in the current coding tree block (CTB) that have not yet been decoded and hence are not available in the samples 370.

A block vector is a two-dimensional vector referencing a block within the pair of coding tree blocks (CTBs). The intra block copy module 350 may test every valid block vector by conducting a search using a nested loop. However, faster searching methods may be used by the intra block copy module 350 in producing the reference block. For example, the intra block copy module 350 may reduce the search complexity by searching for block vectors aligned horizontally or vertically to the current coding unit (CU). In another example, near-horizontal and near-vertical block vectors may also be searched by the intra block copy module 350 to produce a reference block. In another example, the intra block copy module 350 may test a spatially sparse set of block vectors and then perform a refined search in the neighbourhood of a selected one of the sparse block vectors to produce a final block vector.

Entropy coding a block vector has an associated cost, or rate. One method of entropy coding a block vector is to reuse the motion vector difference (i.e. 'mvd\_coding') syntax structure. The motion vector difference syntax structure permits encoding of a two-dimensional signed vector and is thus suitable for a block vector. The motion vector difference syntax structure encodes smaller magnitude vectors more compactly than larger magnitude vectors. Consequently, in the rate measurement, a bias towards selecting nearby reference blocks may be introduced.

A given block vector results in a particular reference block having a particular distortion. Of the block vectors that are tested by the video encoder 114, the rate-distortion trade-off is applied to determine which block vector to apply for the intra block copy mode. An overall rate distortion trade-off may compare the result for the intra block copy mode with the result for other prediction methods, such as inter-prediction and intra-prediction.

5 Prediction units (PUs) may be generated using either an intra-prediction, an inter-prediction or an intra block copy method. Intra-prediction methods make use of data samples adjacent to the prediction unit (PU) that have previously been decoded (i.e., typically above and to the left of the prediction unit) in order to generate reference data samples within the prediction unit (PU). Various directions of intra-prediction are possible. In one arrangement, thirty three (33) directions of intra-prediction are possible. A 'DC mode' and a 'planar mode' may be supported, for a total of thirty five (35) possible intra-prediction modes.

10 Inter-prediction methods make use of a motion vector to refer to a block from a selected reference frame. With reference to Fig. 3, the motion estimation module 338 and motion compensation module 334 operate on motion vectors 374, having a precision of one eighth (1/8) of a luma sample, enabling precise modelling of motion between frames in the frame data 310. The decision on which of the intra-prediction, the inter-prediction or the intra block copy method to use may be made according to a rate-distortion trade-off.

15 The rate-distortion trade-off is made between the desired bit-rate of the resulting encoded bitstream 312 and the amount of image quality distortion introduced by either the intra-prediction, inter-prediction or the intra block copy method. If intra-prediction is used, one intra-prediction mode is selected from the set of possible intra-prediction modes, also according to a rate-distortion trade-off. The multiplexer module 340 may select the intra-predicted reference samples 378 from the intra-frame prediction module 336, or the inter-predicted prediction unit (PU) 376 from the motion compensation block 334, or the reference block from the intra block copy module 350.

20 The summation module 342 produces a sum 370 that is input to a de-blocking filter module 330. The de-blocking filter module 330 performs filtering along block boundaries, producing de-blocked samples 372 that are written to the frame buffer module 332 configured within the memory 206. The frame buffer module 332 is a buffer with sufficient capacity to hold data from one or more past frames for future reference for inter-predicted prediction units (PUs).

25 For the high efficiency video coding (HEVC) standard, the encoded bitstream 312 produced by the entropy encoder 324 is delineated into network abstraction layer (NAL) units. Frames are encoded using one or more 'slices', with each slice including one or more coding tree blocks (CTBs). Two types of slice are defined, 'independent slice segments' and 'dependent slice segments'. Generally, each slice of a frame is contained in

one NAL unit. The entropy encoder 324 encodes the transform coefficients 364, the intra-prediction mode 380, the motion vectors (or motion vector differences) and other parameters, collectively referred to as ‘syntax elements’, into the encoded bitstream 312 by performing a context adaptive binary arithmetic coding (CABAC) algorithm. Syntax 5 elements are grouped together into ‘syntax structures’. The groupings may contain recursion to describe hierarchical structures. In addition to ordinal values, such as an intra-prediction mode or integer values, such as a motion vector, syntax elements also include flags, such as to indicate a quad-tree split.

The video encoder 114 also divides a frame into one or more ‘tiles’. Each tile is a 10 rectangular set of coding tree blocks (CTBs) that may be encoded and decoded independently, facilitating parallel implementations of the video encoder 114 and the video decoder 134. Within each tile, coding tree blocks (CTBs) are scanned in a raster order and a single core (or thread) implementation of the video encoder 114 or the video decoder 134 scans the tiles in raster scan order. To enable a parallel implementation of the video 15 encoder 114 and the video decoder 134, intra-prediction of blocks along a tile boundary may not use samples from blocks in a neighbouring tile. As such, the neighbouring samples may be marked as not available for intra-prediction even though the sample values do exist.

Although the video decoder 134 of Fig. 4 is described with reference to a high 20 efficiency video coding (HEVC) video decoding pipeline, other video codecs may also employ the processing stages of modules 420-436. The encoded video information may also be read from memory 206, the hard disk drive 210, a CD-ROM, a Blu-ray<sup>TM</sup> disk or other computer readable storage medium. Alternatively the encoded video information may be received from an external source, such as a server connected to the 25 communications network 220 or a radio-frequency receiver.

As seen in Fig. 4, received video data, such as the encoded bitstream 312, is input to the video decoder 134. The encoded bitstream 312 may be read from memory 206, the hard disk drive 210, a CD-ROM, a Blu-ray<sup>TM</sup> disk or other computer readable storage medium. Alternatively the encoded bitstream 312 may be received from an external source 30 such as a server connected to the communications network 220 or a radio-frequency receiver. The encoded bitstream 312 contains encoded syntax elements representing the captured frame data to be decoded.

The encoded bitstream 312 is input to an entropy decoder module 420 which extracts the syntax elements from the encoded bitstream 312 and passes the values of the syntax elements to other blocks in the video decoder 134. The entropy decoder module 420 applies the context adaptive binary arithmetic coding (CABAC) algorithm to decode 5 syntax elements from the encoded bitstream 312. The decoded syntax elements are used to reconstruct parameters within the video decoder 134. Parameters include zero or more residual data array 450 and motion vectors 452. Motion vector differences are decoded from the encoded bitstream 312 and the motion vectors 452 are derived from the decoded motion vector differences.

10 The parameters reconstructed within the video decoder 134 also include a prediction mode 454, a quantisation parameter 468, a transform size 470 and a bit-depth 472. The transform size 470 was encoded in the encoded bitstream 312 by the video encoder 114 according to the transform size 386. The bit-depth 472 was encoded in the encoded bitstream 312 by the video encoder 114 according to the bit-depth 390. The 15 quantisation parameter 468 was encoded in the encoded bitstream 312 by the video encoder 114 according to the quantisation parameter 384. Thus, the transform size 470 is equal to the transform size 386, the bit-depth 472 is equal to the bit-depth 390 and the quantisation parameter 468 is equal to the quantisation parameter 384.

20 The residual data array 450 is passed to a dequantiser module 421, the motion vectors 452 are passed to a motion compensation module 434, and the prediction mode 454 is passed to an intra-frame prediction module 426 and to a multiplexer 428.

With reference to Fig. 4, the dequantiser module 421 performs inverse scaling on 25 the residual data of the residual data array 450 to create reconstructed data 455 in the form of transform coefficients. The dequantiser module 421 outputs the reconstructed data 455 to an inverse transform module 422. The inverse transform module 422 applies an ‘inverse transform’ to convert the reconstructed data 455 (i.e., the transform coefficients) from a frequency domain representation to a spatial domain representation, outputting a residual sample array 456 via a multiplexer module 423. The inverse transform module 422 performs the same operation as the inverse transform module 328. The inverse transform 30 module 422 is configured to perform inverse transforms sized in accordance with the transform size 470 having a bit-depth according to the bit-depth 472. The transforms performed by the inverse transform module 422 are selected from a predetermined set of

transform sizes required to decode an encoded bitstream 312 that is compliant with the high efficiency video coding (HEVC) standard.

5 The motion compensation module 434 uses the motion vectors 452 from the entropy decoder module 420, combined with reference frame data 460 from a frame buffer block 432, configured within the memory 206, to produce an inter-predicted prediction unit (PU) 462 for a prediction unit (PU). The inter-predicted prediction unit (PU) 462 is a prediction of output decoded frame data based upon previously decoded frame data. When the prediction mode 454 indicates that the current prediction unit (PU) was coded using intra-prediction, the intra-frame prediction module 426 produces an intra-predicted 10 prediction unit (PU) 464 for the prediction unit (PU). The intra-predicted prediction unit (PU) 464 is produced using data samples spatially neighbouring the prediction unit (PU) and a prediction direction also supplied by the prediction mode 454. The spatially neighbouring data samples are obtained from a sum 458, output from a summation module 424.