(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5180537号

(P5180537)

(45) 発行日 平成25年4月10日(2013.4.10)

(24) 登録日 平成25年1月18日(2013.1.18)

(51) Int.Cl.

F 1

H01L 27/146 (2006.01)

H01L 31/08 (2006.01)H01L 27/14

H01L 31/08A

R

請求項の数 6 (全 19 頁)

(21) 出願番号 特願2007-218330 (P2007-218330)

(22) 出願日 平成19年8月24日 (2007.8.24)

(65) 公開番号 特開2009-54696 (P2009-54696A)

(43) 公開日 平成21年3月12日 (2009.3.12)

審査請求日 平成22年8月24日 (2010.8.24)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】光電変換装置及びマルチチップイメージセンサ

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換領域を構成するように、第一導電型の第一不純物領域と、信号取り出し領域を構成する第二導電型の第二不純物領域とを含む画素を複数配置してなる光電変換装置において、

前記第一不純物領域は、前記第二不純物領域の側方および下面を取り囲むように配置され、

各画素を分離するために各画素の周囲に当該画素の前記第一不純物領域の側方をその全周にわたって囲むように第一導電型の不純物領域が配置され、前記不純物領域は、前記第一不純物領域の側方をその全周にわたって囲むように一周する経路において、第一導電型の第三不純物領域と、第一導電型の第四不純物領域とを含み、

前記第四不純物領域は隣接する画素の間に配置され、前記第四不純物領域の不純物濃度は前記第三不純物領域の不純物濃度より低いことを特徴とする光電変換装置。

## 【請求項 2】

前記第四不純物領域は互いに隣接する前記第二不純物領域の間に配置された領域を含むことを特徴とする請求項 1 に記載の光電変換装置。

## 【請求項 3】

隣接する画素の前記第二不純物領域の間ににおける前記第四不純物領域の幅は隣接する画素の間ににおける前記第三不純物領域の幅より狭いことを特徴とする請求項 1 又は請求項 2 に記載の光電変換装置。

**【請求項 4】**

前記第四不純物領域の深さは前記第三不純物領域の深さより浅いことを特徴とする請求項1から請求項3のいずれか1項に記載の光電変換装置。

**【請求項 5】**

前記第三不純物領域と前記第四不純物領域で囲われた領域が長方形であり、該長方形の長辺側に第四不純物領域が配置されていることを特徴とする請求項1から4のいずれか1項に記載の光電変換装置。

**【請求項 6】**

請求項1から請求項5のいずれか1項に記載の光電変換装置を複数列状に配置したこと 10 を特徴とするマルチチップイメージセンサ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は光電変換装置及びマルチチップイメージセンサに係わり、特にスキャナ、ビデオカメラ、デジタルスチルカメラ等に用いられる光電変換装置及びマルチチップイメージセンサに関する。

**【背景技術】****【0002】**

画素読み取り用のスキャナ、ファクシミリの読み取りに用いられるリニア型の光電変換装置には、従来、半導体領域を第一導電型の埋め込み領域と第一導電型のバリア領域で分離することで隣接する画素間を分離していた。各画素は、エピタキシャル層からなる第一導電型領域と第一導電型領域内に形成された第二導電型領域のPN接合で作られるフォトダイオードを有している(特許文献1)。

【特許文献1】特開2007-027558号公報

**【発明の開示】****【発明が解決しようとする課題】****【0003】**

しかしながら、特許文献1の構成においては、上記画素分離領域を有する画素の配置ピッチが狭くなっていくと、第一導電型のバリア領域と第二導電型の領域の間隔が狭くなり、フォトダイオードのPN接合容量が増加して感度が低下するという問題があった。

**【0004】**

本発明の目的は、PN接合容量を増やさずに画素間隔を狭めることが可能となる光電変換装置を提供することにある。

**【課題を解決するための手段】****【0005】**

本発明の1つの側面は、光電変換領域を構成するように、第一導電型の第一不純物領域と、信号取り出し領域を構成する第二導電型の第二不純物領域とを含む画素を複数配置してなる光電変換装置において、前記第一不純物領域は、前記第二不純物領域の側方および下面を取り囲むように配置され、各画素を分離するために各画素の周囲に当該画素の前記第一不純物領域の側方をその全周にわたって囲むように第一導電型の不純物領域が配置され、前記不純物領域は、前記第一不純物領域の側方をその全周にわたって囲むように一周する経路において、第一導電型の第三不純物領域と、第一導電型の第四不純物領域とを含み、前記第四不純物領域は隣接する画素の間に配置され、前記第四不純物領域の不純物濃度は前記第三不純物領域の不純物濃度より低いことを特徴とする。

**【発明の効果】****【0008】**

本発明によれば、PN接合容量を増やさずに画素間隔を狭めることが可能となる。

**【発明を実施するための最良の形態】****【0009】**

以下、本発明の実施形態について図面を用いて詳細に説明する。

(第一の実施形態)

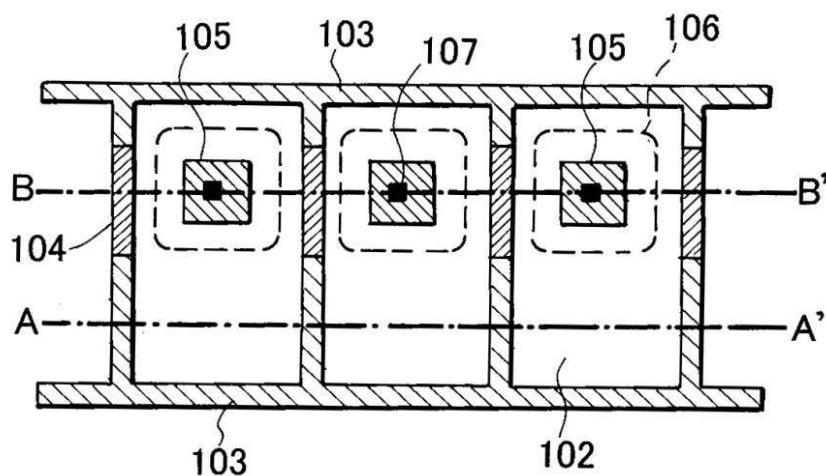

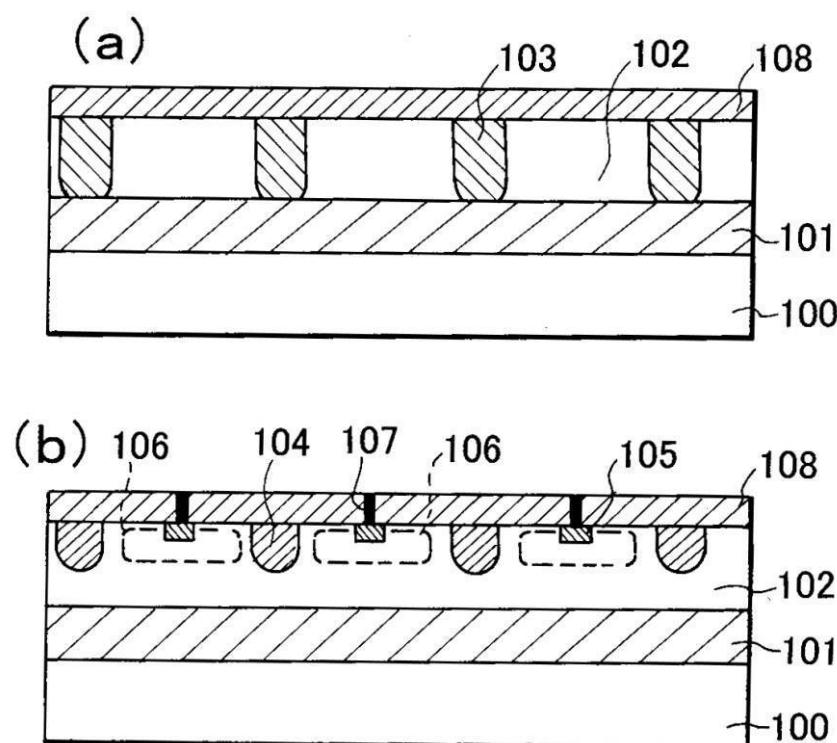

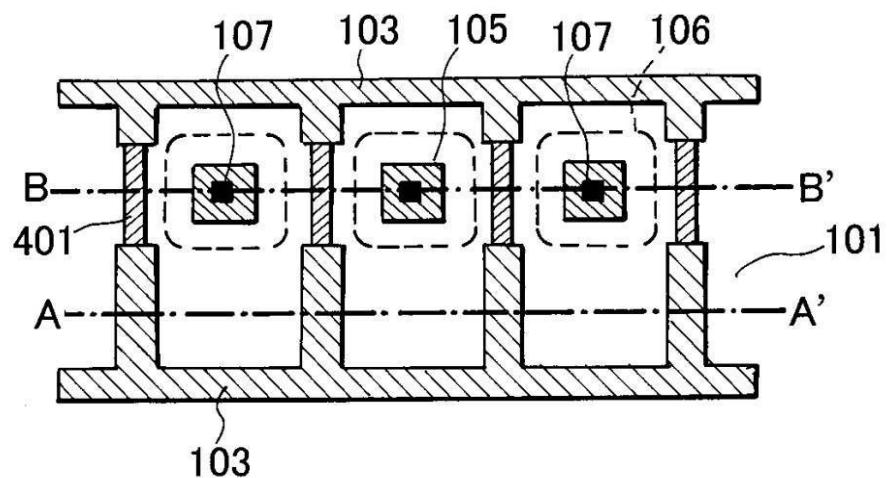

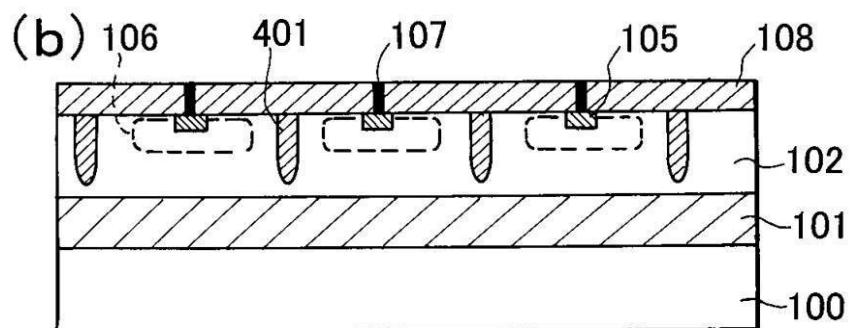

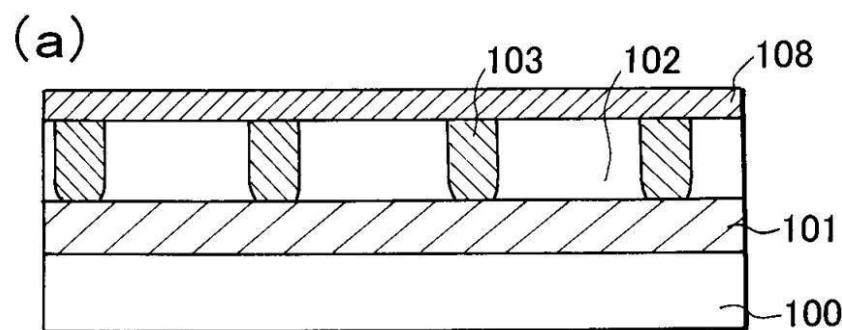

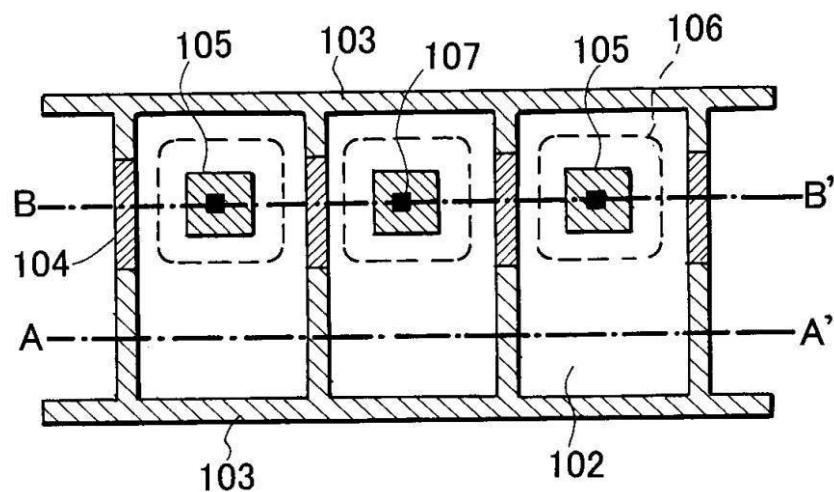

図1は本発明の第一の実施形態における3画素分の平面図である。図2(a)は図1のA-A'断面における断面構造の模式図であり、図2(b)は図1のB-B'断面における断面構造の模式図である。また図1、図2において同一構成部分には同一符号を付している。

【0010】

図1、図2において、100は半導体基板である。本実施形態ではN型の半導体基板の場合を例にして説明する。101はN型の埋め込み拡散領域、102は半導体基板100上に形成されたN型のエピタキシャル領域(光電変換領域を構成する第一不純物領域となる)である。また103は第一のN型画素分離領域(第三不純物領域となる)、104は第二のN型画素分離領域(第四不純物領域となる)、105はP型の電荷取り出し領域(信号取り出し領域を構成する第二不純物領域となる)である。エピタキシャル領域102と電荷取り出し領域105とは画素を構成し、画素は半導体基板に複数個配置される。また、エピタキシャル領域102と電荷取り出し領域105はPN接合を形成し、画素の受光部(光電変換部となる)を構成する。第一のN型画素分離領域103と第二のN型画素分離領域104とは、各画素を分離するため、画素の周囲に設けられる。第二のN型画素分離領域104は隣接する画素間に配される。P型電荷取り出し領域105は金属電極107を介して、ここでは図示していないが読み出し回路へと接続される。また点線で囲われた領域106はPN接合の空乏層領域を示している。

【0011】

断面図の図2(a)及び図2(b)の108はN型エピタキシャル領域102上に形成された層間絶縁膜である。

【0012】

図1に示したように、各画素の受光部は平面的には第一のN型画素分離領域103と第二のN型画素分離領域104に囲まれている。さらに深さ方向は、図2(a)に示したように、N型埋め込み領域101と第一のN型画素分離領域103とで囲まれている。N型エピタキシャル領域102に入射した光に応じて、光電変換により発生した光電荷(ここではホール)はP型電荷取り出し領域105へと集められ、金属電極107を介して読み出し回路へと読み出される。本実施形態において読み出し回路の構成及び動作は省略する。

【0013】

発生した光電荷は空乏層106の外部であれば拡散によってP型電荷取り出し領域105に集められ、空乏層領域106内であればドリフトによってP型電荷取り出し領域105に集められる。

【0014】

N型エピタキシャル領域102は、第一のN型画素分離領域103、第二のN型画素分離領域104、N型埋め込み領域101よりも不純物濃度が低くなるように形成されている。そのためN型エピタキシャル領域102と、第一のN型画素分離領域103、第二のN型画素分離領域104、N型埋め込み領域101との間にはポテンシャル差が生じる。このポテンシャル差は画素間での光電荷の行き来、つまりクロストークを低減するように作用する。また、ポテンシャル差はN型半導体基板100への光電荷の流失を低減して、感度の低下を抑制するように作用する。

【0015】

ここで、課題について説明する。P型電荷取り出し領域105に集められた光電荷は、P型電荷取り出し領域105とN型のエピタキシャル領域102とのPN接合の容量を含む検出容量Cpdによって電荷-電圧変換される。この電荷-電圧変換の式は出力電圧をV、光電荷量をQとすると、出力電圧Vは、

$$V = Q/Cpd$$

であらわされる。

【0016】

したがって集められた光電荷が同じであれば検出容量Cpdが小さいほど出力電圧Vは大きくなり、感度の高い光電変換装置を形成することができる。よって、本構造の画素を用

10

20

30

40

50

いて、感度の高く良好な画像を得ることのできる光電変換装置を実現する為には、この検出容量Cpdを小さくすることが重要である。

【0017】

検出容量の一部を形成する、P型電荷取り出し領域105とN型エピタキシャル領域102間のPN接合の容量Cjは、単位接合面積あたり、

【0018】

【数1】

$$Cj = \frac{\epsilon_s}{W} = \sqrt{\frac{q \epsilon_s N_B}{2(V_{bi} - V)}} \quad \cdots \text{式1}$$

10

【0019】

として求められる。ここで  $\epsilon_s$  はSiの比誘電率でありWは空乏層幅である。

【0020】

また  $V_{bi}$  は内蔵電位、Vは印加電圧、qは電荷素量、 $N_B$  は本例においてはN型エピタキシャル領域102の不純物濃度である。

【0021】

したがってN型エピタキシャル領域102の不純物濃度を低くすることでPN接合の接合容量を小さくすることができる。

20

【0022】

ここで、画素ピッチが狭くなつて行くと、画素分離領域がP型電荷取り出し領域に近接しPN接合に影響を与える、あるいはPN接合を形成する。このような場合において、式1の  $N_B$  はエピタキシャル領域よりも濃度が高い画素分離領域の不純物濃度に置き換わる。従つて、PN接合の容量Cjが大きくなり出力電圧Vが小さくなるため、感度が低下してしまう。そこで、本実施形態では、単に画素分離領域を設けるだけでなく不純物濃度がN型エピタキシャル領域102よりも高く、第一のN型画素分離領域103よりも低い第二のN型画素分離領域104を新たに設けることで光電荷の流出によるクロストークを最小限に抑えつつ、感度を向上させている。

【0023】

30

これは先に述べた、光電荷が空乏層領域106の外部であれば拡散によって、空乏層領域106内であればドリフトによってP型電荷取り出し領域105へと集められる特性を利用している。

【0024】

つまり図1において空乏層領域106内で発生した光電荷は、ドリフトによってP型電荷取り出し領域105へと集められる。このため空乏層領域106を画素境界近傍まで広げれば、高濃度のポテンシャルによって画素間を分離しなくても必要な光電荷をドリフトにより集めることができ、隣接する画素間の光電荷の出入りも低減できる。

【0025】

特に、空乏層領域106近傍には、第一の画素分離領域103より濃度の低い、第二の画素分離領域104を形成することで、PN接合容量へ画素分離領域が与える影響を低減するため検出容量の増加を抑えることができる。

40

【0026】

一方、空乏層領域106の外で発生した光電荷を拡散によって十分に集めるために、空乏層領域106の空乏層への影響の少ない領域はポテンシャル障壁を高くするために、第一の画素分離領域103によって分離している。

【0027】

このように、第一のN型画素分離領域103と、第一のN型画素分離領域103より低濃度の第二の画素分離領域104とを平面的に配置して画素分離を行う。この構成により、高解像度の画素ピッチにおいてもクロストーク増加の防止と感度の低下防止を両立できる

50

画素構造を有した光電変換装置を実現できる。

【0028】

ここでは、第二の画素分離領域104は長方形の画素の長い側に設けられているが、画素が短辺側で隣接する場合には短辺側に設ける。つまり、第二の画素分離領域104は画素間の最も信号読み出し領域に近接した部分に置くことが好ましい。

【0029】

ただし図1のように隣接する二つの画素の電荷取り出し領域105の間に第二の画素分離領域104を配置する構成の場合、狭画素ピッチのセンサ形成する上で特に効果が高い。これは隣接する画素の二つの電荷取り出し領域105の間が画素分離領域と電荷取り出し領域との距離を最も確保しにくいため、空乏層の広がりへの影響が大きい為である。

10

【0030】

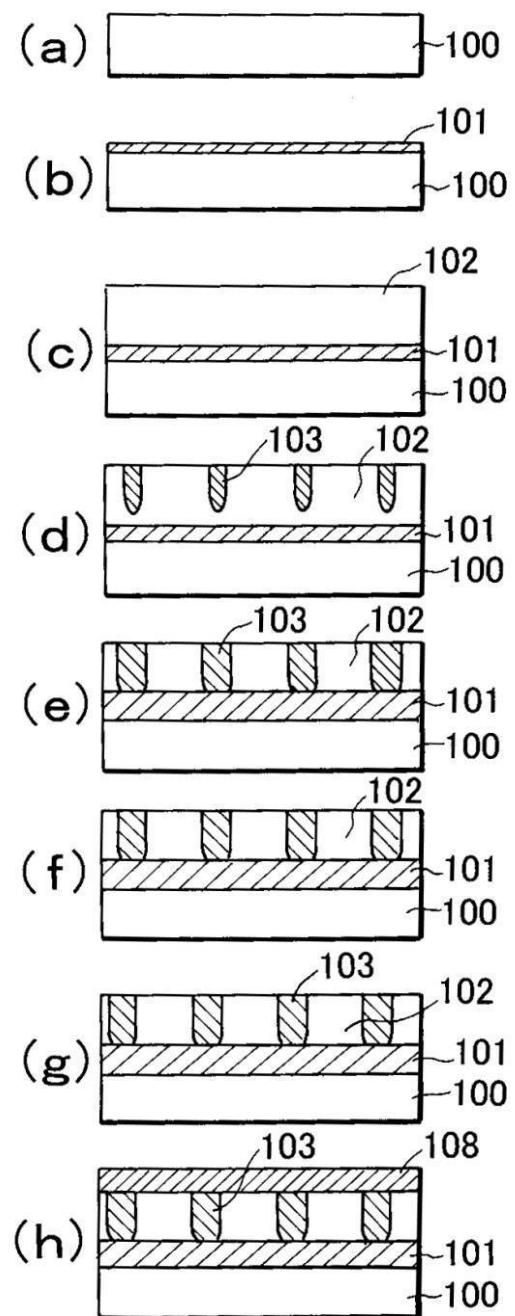

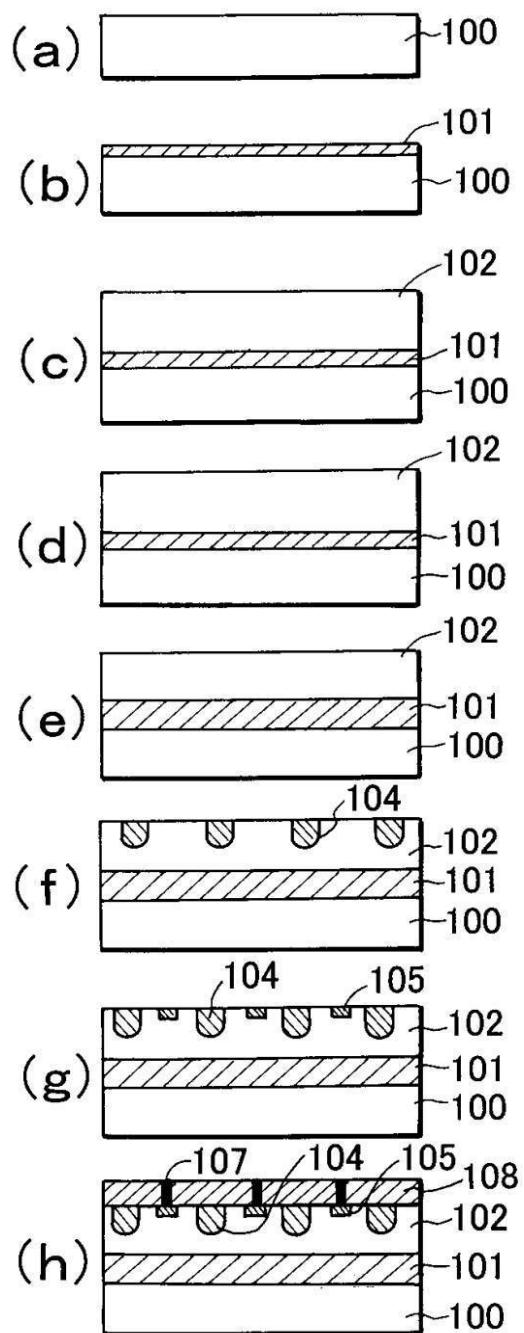

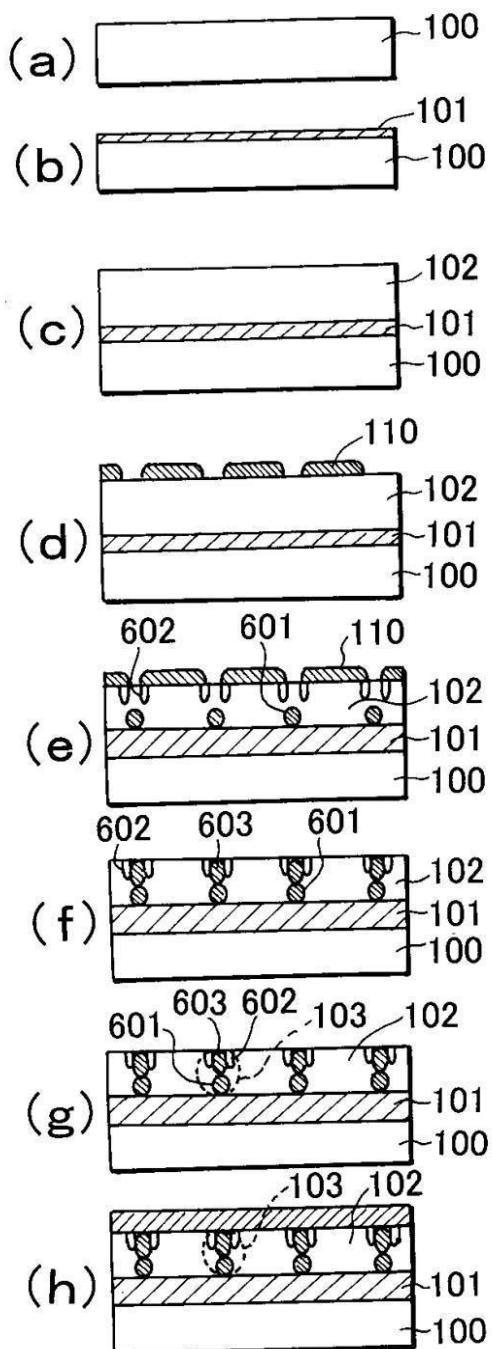

図3(a)～図3(h)及び図4(a)～図4(h)は図1、図2の画素構造の製造工程を説明するための工程図である。図3(a)～図3(h)は図1のA-A'断面に対応し、図4(a)～図4(h)は図1のB-B'断面に対応している。

【0031】

以下、図面を用いて工程ごとに本画素構造の製造工程を説明する。なお製造工程の説明は本画素構造を形成するために必要な拡散領域についてのみとしており、本光電変換装置の読み出し回路を形成するMOSFET等の製造工程の説明は簡略化のため省略している。

【0032】

まず、図3(a)及び図4(a)に示すように、N型半導体基板100を用意する。

20

【0033】

次に、図3(b)及び図4(b)に示すように、N型半導体基板100上にN型埋め込み領域101をイオン注入工程により形成する。

【0034】

次に、図3(c)及び図4(c)に示すように、N型埋め込み層101上にN型エピタキシャル領域102をエピタキシャル成長により形成する。

【0035】

次に、図3(d)及び図4(d)に示すように、N型エピタキシャル領域102中のフォト工程で規定された領域内に、第一のN型画素分離領域103をイオン注入工程により形成する。

30

【0036】

次に、図3(e)及び図4(e)に示すように、N型埋め込み領域101と第一のN型画素分離領域103を熱拡散により拡散する。

【0037】

次に、図3(f)及び図4(f)に示すように、N型エピタキシャル領域102中のフォト工程で規定された領域内に第二のN型画素分離領域104をイオン注入工程により生成する。

【0038】

ここでN型エピタキシャル領域101の不純物濃度は $1e14 \sim 1e15 \text{cm}^3$ 程度であり、またN型埋め込み層102及び第一のN型画素分離領域103の不純物濃度はエピタキシャル領域101よりも高い濃度で、例えば $1e16 \sim 1e18 \text{cm}^3$ を超える濃度である。N型エピタキシャル領域101と第一のN型画素分離領域103とは、画素分離のためのポテンシャルの障壁を形成するため、10～100倍以上の不純物濃度差を有することが望ましい。一方、第二のN型画素分離領域の不純物濃度は $1e15 \sim 1e17 \text{cm}^3$ 程度とし、第一のN型画素分離領域よりも不純物濃度を低く構成する。不純物としては、リンやヒ素が用いられる。

40

【0039】

次に、図3(g)及び図4(g)に示すように、N型エピタキシャル領域102中のフォト工程で規定された領域内に、P型電荷取り出し領域105をイオン注入工程により形成する。

【0040】

50

最後に、図3(h)及び図4(h)に示すように、層間絶縁膜108と金属電極107を形成する。

【0041】

第一のN型画素分離領域103を図3(e)及び図4(e)で述べた熱拡散工程によって形成すると、深さ方向のみならず横方向にも同様に拡散するため、先に述べたように第一のN型画素分離領域103とP型電荷取り出し領域105の距離が近くなりやすく、検出容量の増加による感度の低下が本製造工程においては特に問題となりやすい。

【0042】

例えば第一のN型画素分離領域の不純物濃度が $1e18\text{cm}^3$ ( $1 \times 10^{18}\text{cm}^3$ )であり、エピタキシャル領域の不純物濃度が $1e14\text{cm}^3$ であった場合、N型画素分離領域部付近のエピタキシャル領域はこの中間の不純物濃度を有する。この中間濃度のプロファイルの傾きが仮に $1\mu\text{m}$ あたり濃度が $1/10$ ずつ変化する傾きであるとすると、 $1e18\text{cm}^3$ のN型画素分離領域がエピタキシャル領域の濃度 $1e15\text{cm}^3$ と同じになるには $4\mu\text{m}$ の幅を有する。

【0043】

すなわち、式1に示すPN接合容量に影響する濃度をエピタキシャル領域の不純物濃度 $1e14$ とするためには、第一のN型画素分離領域から空乏層領域端までを最低でも $4\mu\text{m}$ 以上も確保する必要がある。例えば、2400d<sub>p</sub>iの解像度を持つラインセンサの場合、画素ピッチが約 $10.5\mu\text{m}$ となるため、第一のN型画素分離領域から空乏層領域の端まで片側 $4\mu\text{m}$ づつ計 $8\mu\text{m}$ の距離を設けると空乏層領域幅、P型画素分離領域幅を確保することが非常に困難である。そこで、不純物濃度が低い第二のN型画素分離領域は、例えばその不純物濃度を $1e16$ とすると、第二のN型画素分離領域から空乏層領域端までの距離は $2\mu\text{m}$ 以上であればよい。

【0044】

このため、濃度の異なる第一のN型画素分離領域103と第二のN型画素分離領域104とを用いる構造が特に有効に機能する。また本製造工程で示したように第一のN型画素分離領域103の熱拡散の工程後に第二のN型画素分離領域104を形成すれば、第二のN型画素分離領域の横方向の広がりを抑えることができるため、高い効果が得られる。

【0045】

第二のN型画素分離領域の深さ方向の濃度分布は、空乏層領域106が最適に形成されるように選べばよい。

【0046】

また、第二の画素分離領域104を、イオン注入をせず、第一の画素分離領域103からの拡散によって形成することも可能である。このようにして形成された第二の画素分離領域を用いた場合においても本実施形態と同様の効果が得られるものである。

(第二の実施形態)

図5は本発明の第二の実施形態における3画素分の平面図であり、図6(a)は図5のA-A'断面における断面構造の模式図であり、図6(b)は図5のB-B'断面における断面構造の模式図である。また図5、図6において図1、図2と同一の部分には同一符号を付している。図5、図6の構造に関して第一の実施形態と同一の構成部材については説明を省略する。

【0047】

図5及び図6において、第三のN型画素分離領域401は、第一のN型画素分離領域103よりも画素分離領域の幅を狭く形成している。この構造は、例えば先に説明した第一のN型画素分離領域103を形成する工程において、フォト工程で規定するイオン注入領域の形状の幅を制御することで同時に形成できる。本実施形態では第三のN型画素分離領域の不純物濃度は第一のN型画素分離領域と同じとした。

【0048】

P型電荷取り出し領域105とエピタキシャル領域102の間の逆バイアスによって空乏層はエピタキシャル層側に伸びるが、空乏層は第三のN型画素分離領域401に達しないように第三のN型画素領域401の幅を設計した。第一のN型画素分離領域よりも第三のN型が

10

20

30

40

50

素分離領域 401 の不純物濃度が高くてよい。空乏層が第三のN型画素分離領域 401 に達しなければよい。もちろん、第一のN型画素分離領域よりも第三のN型画素分離領域 401 の不純物濃度が低くてもよい。

【0049】

その結果、感度は高く、クロストークの増加を抑えた画素ピッチの小さい光電変換装置を作ることができた。

(第三の実施形態)

図7は第三の実施形態の光電変換装置の平面図である。

【0050】

本実施形態では、第二のN型不純物領域 104 が第一のN型画素分離領域 103 よりも画素分離領域の深さを浅く形成していることが特徴である。例えば、第一のN型画素分離領域 103 が複数層の不純物領域から構成されているのに対し、第二のN型画素分離領域 104 は1層の不純物領域で構成されている。

【0051】

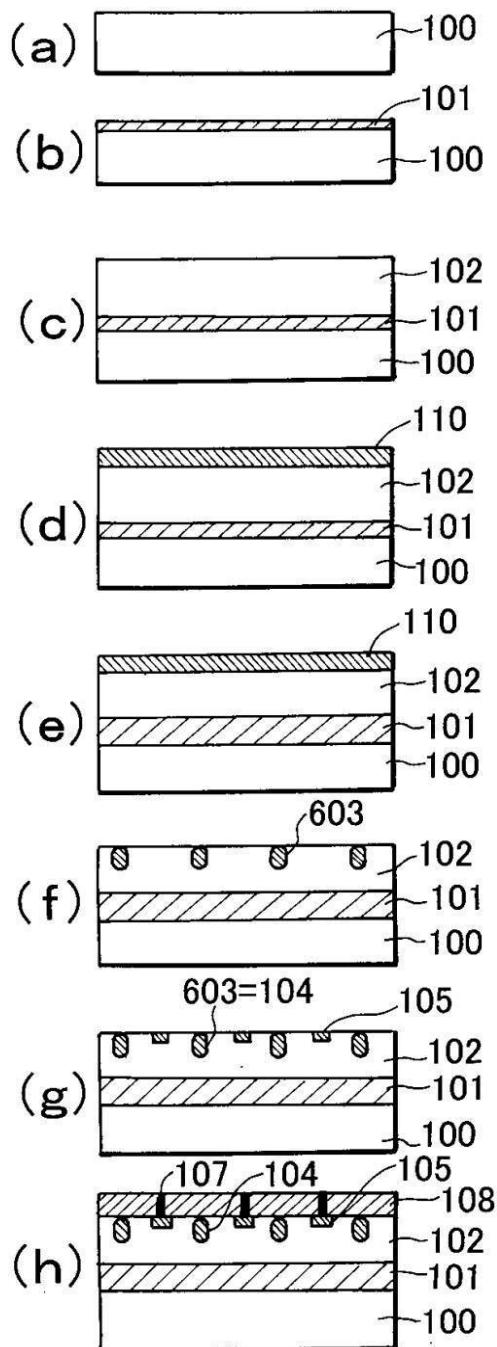

図8(a)～図8(h)及び図9(a)～図9(h)は図7の画素構造の製造工程を説明するための工程図である。図8(a)～図8(h)は図7のA-A'断面に対応し、図9(a)～図9(h)は図7のB-B'断面に対応している。

【0052】

完成した断面図は図8(h)及び図9(h)であり、図8(h)及び図9(h)にいたる工程を示したものが図8(a)～図8(g)及び図9(a)～図9(g)である。

【0053】

なお製造工程の説明は本画素構造を形成するために必要な拡散領域のみについて行い、本光電変換装置の読み出し回路を形成するためのMOSFET等の製造工程は簡略化のため省略している。

【0054】

また図8及び図9において、図3及び図4と同一構成部材には同一符号を付しており説明を省略する。

【0055】

まず、図8(a)及び図9(a)に示すように、N型半導体基板 100 を用意する。

【0056】

次に、図8(b)及び図9(b)に示すように、N型半導体基板 100 上にN型埋め込み領域 101 をイオン注入により形成する。

【0057】

次に、図8(c)及び図9(c)に示すように、N型埋め込み領域 101 上に  $1e14 \sim 1e15 \text{ cm}^3$  程度の不純物濃度を有するN型エピタキシャル領域 102 をエピタキシャル成長により形成する。

【0058】

次に、図8(d)及び図9(d)に示すように、高エネルギーイオン注入用の厚膜フォトレジスト 110 を一部を残してフォト工程でパターニングする。

次に、図8(e)及び図9(e)に示すように、N型エピタキシャル領域 102 中に上記厚膜レジストを介して  $500 \text{ keV} \sim 2.0 \text{ MeV}$  以上の高エネルギーイオン注入工程により、フォト工程で規定された領域内にN型拡散領域 601 が形成される。そして、フォト工程で規定された周辺のレジストの薄い領域に、N型拡散領域 602 が形成される。N型拡散領域 601 の不純物濃度は  $1e16 \text{ cm}^3 (1 \times 10^{16} \text{ cm}^3)$  以上であり、N型拡散領域 602 の不純物濃度は  $1e15 \sim 1e17 \text{ cm}^3$  となる。

【0059】

次に、図8(f)及び図9(f)に示すように、N型エピタキシャル領域 102 中のフォト工程で規定された領域内に  $50 \text{ keV} \sim 200 \text{ keV}$  程度のイオン注入工程によりN型拡散領域 603 を生成する。N型拡散領域 603 の不純物濃度は  $1e17 \text{ cm}^3$  以上となる。なお、A-A'断面のN型拡散領域 601, 602, 603 はN型の拡散領域としてつながり、第

10

20

30

40

50

一の画素分離領域 103 となる。B-B' 断面のN型拡散領域 603 はそのまま第二の画素分離領域 104 と成る。

【0060】

次に、図8(g)及び図9(g)に示すように、N型エピタキシャル領域 102 中のフォト工程で規定された領域内にイオン注入工程によりP型電荷取り出し領域 105 を形成する。

【0061】

最後に、図8(h)及び図9(h)に示すように、層間絶縁膜 108 と金属電極 107 を形成する。

【0062】

B-B' 断面で、深い位置にあるN型不純物層 601 を形成すると、A-A' 断面と同様に、B-B' 断面にもN型不純物層 602 と同じ深さにN型不純物層が形成されてしまうことになる。これは高エネルギーのイオン注入の際に用いる厚いレジスト膜が開口付近で“ダレ”を起こしやすいことにより、シリコン表面から比較的浅い位置にイオンが注入されてしまうことによる。このN型不純物層により、P型信号取り出し領域 107 から広がった空乏層の広がりが抑えられ、光電変換装置の感度低下の原因となる。よって、取り出し電極の近傍には、深い位置に形成されたN型不純物層を作らないことが、高感度を保つつつ、低クロストークを得るのに適した構造である。

【0063】

一方、B-B' 断面のように信号取り出し電極から遠い位置では、N型不純物領域を複数層とすることで、隣接画素への電荷のもれこみを抑えることができる。

【0064】

また本実施形態ではレジスト形状に‘ダレ’が生じることで分離幅が広がることを例としてあげたが、この他にも例えば高エネルギー用の厚膜フォトレジストは通常のレジストよりも、微細なエッチングが行いにくいため、分離幅を広くせざるを得ない。また熱拡散で分離幅を深くまで到達させる場合も、深さの方向のみならず横方向にも拡散するため分離幅が広くなる。

【0065】

このように一般的に深い分離層を形成すると横方向に広い分離幅となりやすく、浅い分離層を形成すると横方向は狭い分離幅で形成することが可能である。

【0066】

したがって本実施形態では第一の画素分離領域 103 を第二の画素分離領域 104 のピーク濃度よりも深い位置に形成することで感度の低下抑制とクロストークの低減を両立できる画素構造を有した光電変換装置を実現できる。

【0067】

上記実施形態ではイオン注入エネルギーを変えた複数回のイオン注入を組み合わせて形成する場合を説明したが、第一の画素分離領域 103 を一度のイオン注入工程で形成してもよい。また第二の画素分離領域 104 を形成するイオン注入工程を第一の画素分離領域 103 を形成するためにも用いたが、別々のイオン注入で形成してもよい。

【0068】

上記第一～第三の実施形態はN型領域中にP型の電荷取り出し領域を設けた場合を例にとつて説明したが、これにかぎるものではなく、逆の導電型の組み合わせにおいても同様の効果が得られるものである。

【0069】

また、第一～第三の実施形態は受光部にエピタキシャル成長により形成した低濃度領域を用いた場合を例にして説明したが、これに限るものではない。例えばシリコン基板に高エネルギーイオン注入で埋め込み領域 101 として、前述した画素分離構造を形成した場合でも本発明は有効である。その時、受光部は、シリコン基板を利用してよいし、適切な不純物濃度になるように、別途イオン注入工程で形成してもよい。

【0070】

10

20

30

40

50

以上説明した第一～第三の実施形態は光電変換装置としてラインセンサの例について説明した。しかしながら、一チップ上に複数行の画素行、例えばR行、G行、B行と画素行が複数配された二次元のセンサにも本発明を適用できる。R行、G行、B行と画素行が複数配された二次元のセンサの場合は真ん中の画素行は、四方の隣接する画素間に第二のN型画素分離領域（第四不純物領域）が配置されることになる。そして、両端の画素行は三方の隣接する画素間に第二のN型画素分離領域（第四不純物領域）が配置されることになる。また、R色、G色、B色の3つの本実施形態のラインセンサを並べて二次元のセンサを構成することができることは勿論である。

## 【0071】

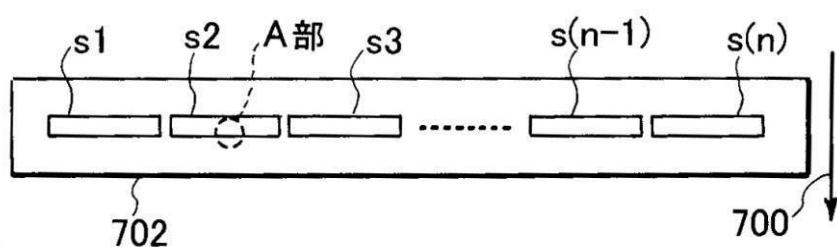

(第四の実施形態)

10

図10は本発明における第四の実施形態におけるマルチチップ方式の半導体イメージセンサの概略図である。S1～S(n)はイメージセンサ実装用基板702に実装された複数の半導体イメージセンサであり、第一～第三の実施形態の光電変換装置を用いることができる。つまり、マルチチップ方式の半導体イメージセンサは第一～第三の実施形態の光電変換装置を複数列状に配置して構成されている。

## 【0072】

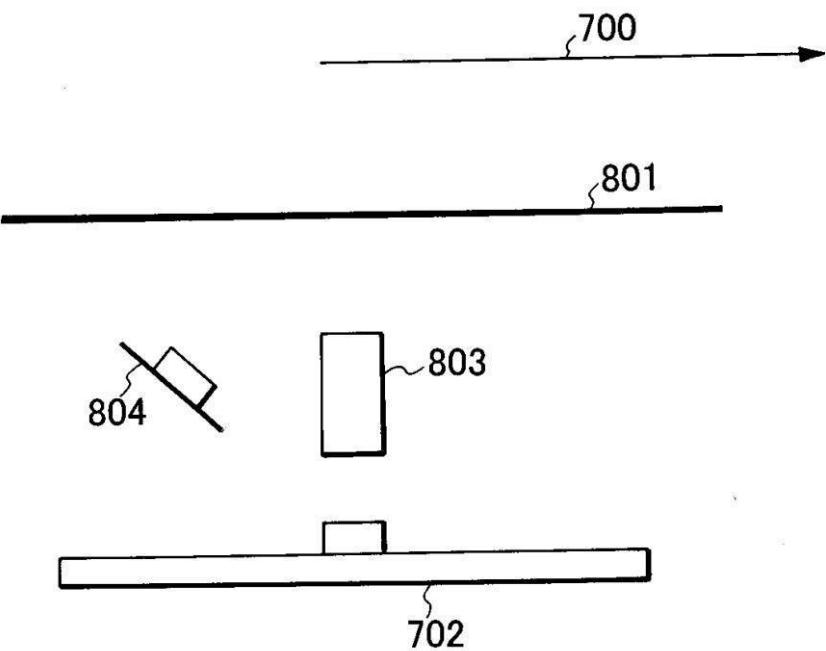

図7は図10のマルチチップ方式の半導体イメージセンサのA部拡大図である。A部拡大図において図1と同一のものには同一符号を付してあるので、説明を省略する。図11は上記マルチチップ方式の半導体イメージセンサを用いた光学系を示す断面構成図である。

## 【0073】

20

図11において、801は原稿、803はセルフォックレンズアレイ（商品名、日本板硝子（株）製）、804は原稿照明用LEDアレイを示している。原稿照明用LEDアレイ804の替わりにLEDと導光体との組み合わせもよく用いられる。

## 【0074】

図10及び図11における矢印700は原稿の副走査方向を示す。この副走査方向の解像度は主にスキャンピッチによって決定される。これに対して主走査方向のピッチはイメージセンサの仕様で決まるので、副走査方向に面積を広げることで感度を向上させている。

## 【0075】

30

ラインセンサにおいて光電変換装置を機械的に動かして画像をスキャンする光電変換装置の場合、主走査方向の解像度よりも副走査方向の解像度が重要と成る場合が多い。このため本実施形態では図7に示すように解像度と感度を両立させるためにアスペクト比が1以上であるように、長方形の画素を形成している。

## 【0076】

単位画素における主走査方向と副走査方向のアスペクト比が1以上の長方形の画素である場合は、本実施形態に示すように長方形の長辺側に対してのみ、第二のN型画素分離領域104を配置させる構成をとることで、クロストークの増加を最小限に抑えつつ、高精細、高感度のマルチチップイメージセンサを実現できた。

## 【産業上の利用可能性】

## 【0077】

40

本発明は、スキャナ、ビデオカメラ、デジタルスチルカメラ等に用いられる光電変換装置に適用される。

## 【図面の簡単な説明】

## 【0078】

【図1】本発明における第一の実施形態の3画素分の構造を示す平面図である。

【図2】(a)は図1におけるA-A'切断面の断面構造の模式図、(b)は図1におけるB-B'切断面の断面構造の模式図である。

【図3】本発明における第一の実施形態の画素構造の半導体プロセスにおける製造工程を説明するための工程図である。

【図4】本発明における第一の実施形態の画素構造の半導体プロセスにおける製造工程を

50

説明するための工程図である。

【図5】本発明における第二の実施形態の3画素分の構造を示す平面図である。

【図6】(a)は図4におけるA-A'切断面の断面構造の模式図、(b)は図4におけるB-B'切断面の断面構造の模式図である。

【図7】本発明の第三の実施形態の光電変換装置の平面図である。

【図8】本発明における第三の実施形態の画素構造の半導体プロセスにおける製造工程を説明するための工程図である。

【図9】本発明における第三の実施形態の画素構造の半導体プロセスにおける製造工程を説明するための工程図である。

【図10】本発明の光電変換装置を用いたマルチチップイメージセンサの構成図である。 10

【図11】本発明の光電変換装置を用いたマルチチップイメージセンサの光学系の図面である。

【符号の説明】

【0079】

|         |                                      |    |

|---------|--------------------------------------|----|

| 100     | N型半導体基板                              | 10 |

| 101     | N型埋め込み拡散領域                           |    |

| 102     | N型エピタキシャル領域                          |    |

| 103     | 第一のN型画素分離領域                          |    |

| 104     | 第二のN型画素分離領域                          |    |

| 105     | P型電荷取り出し領域                           | 20 |

| 106     | 空乏層領域                                |    |

| 107     | 金属電極                                 |    |

| 108     | 層間絶縁膜                                |    |

| 110     | 高エネルギーイオン注入用厚膜フォトレジスト                |    |

| 401     | 第三のN型画素分離領域                          |    |

| 601     | 高エネルギーイオン注入によって形成されたN型拡散領域           |    |

| 602     | 高エネルギーイオン注入によってレジストの薄い部分に形成されたN型拡散領域 |    |

| 603     | イオン注入によって形成されたN型拡散領域                 |    |

| 700     | 原稿スキャン方向矢印                           | 30 |

| 702     | 回路基板                                 |    |

| s1~s(n) | マルチチップ方式の半導体イメージセンサ                  |    |

| 801     | 原稿                                   |    |

| 803     | セルフォックレンズアレイ                         |    |

| 804     | LEDアレイ                               |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 11】

---

フロントページの続き

(72)発明者 山崎 和男

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 光地 哲伸

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 石坂 博明

(56)参考文献 特開平01-303752(JP, A)

特開2003-258229(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/339、27/14、

27/144-27/148、29/762

H01L 31/10、31/107-31/108、31/111