(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4393857号

(P4393857)

(45) 発行日 平成22年1月6日(2010.1.6)

(24) 登録日 平成21年10月23日(2009.10.23)

(51) Int.Cl.

F 1

|                    |                  |              |       |

|--------------------|------------------|--------------|-------|

| <b>G06K 19/07</b>  | <b>(2006.01)</b> | G 06 K 19/00 | J     |

| <b>B42D 15/10</b>  | <b>(2006.01)</b> | B 42 D 15/10 | 501 P |

| <b>G06K 19/077</b> | <b>(2006.01)</b> | B 42 D 15/10 | 521   |

| <b>G06K 19/00</b>  | <b>(2006.01)</b> | G 06 K 19/00 | K     |

|                    |                  | G 06 K 19/00 | Q     |

請求項の数 4 (全 23 頁)

(21) 出願番号 特願2003-424174 (P2003-424174)

(22) 出願日 平成15年12月22日 (2003.12.22)

(65) 公開番号 特開2004-220587 (P2004-220587A)

(43) 公開日 平成16年8月5日 (2004.8.5)

審査請求日 平成18年12月21日 (2006.12.21)

(31) 優先権主張番号 特願2002-378803 (P2002-378803)

(32) 優先日 平成14年12月27日 (2002.12.27)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 高山 徹

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 丸山 純矢

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 後藤 裕吾

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 大野 由美子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】記録媒体の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板及び第2の基板それぞれに金属膜と、金属酸化膜と、絶縁膜と、半導体膜とを順に積層するように形成し、

前記第1の基板及び前記第2の基板それぞれに形成された前記半導体膜を結晶化し、

前記第1の基板及び前記第2の基板それぞれの前記結晶化された半導体膜を用いて、前記第1の基板上に薄膜集積回路及び前記第2の基板上に表示装置を形成し、

前記薄膜集積回路を間に挟んで前記第1の基板と向かい合うように、第1の接着剤を用いて第3の基板を貼り合わせ、かつ前記表示装置を間に挟んで前記第2の基板と向かい合うように、第2の接着剤を用いて第4の基板を貼り合わせ、

前記金属酸化膜を前記金属膜側と前記絶縁膜側とに分離させることで、前記第1の基板及び前記第2の基板を取り除き、

前記薄膜集積回路の前記絶縁膜が形成された側を、第3の接着剤を用いて第5の基板の一方の面に貼り合わせ、

前記表示装置の前記絶縁膜が形成された側を、第4の接着剤を用いて前記第5の基板の他方の面に貼り合わせ、

前記第1の接着剤及び前記第2の接着剤を除去することで、前記第3の基板及び前記第4の基板を取り除き、

前記薄膜集積回路と前記第5の基板の他方の面に設けられた端子とを、前記第5の基板に設けられたコンタクトホールを介して電気的に接続し、

10

20

前記薄膜集積回路と前記表示装置とを、電気的に接続することを特徴とする記録媒体の作製方法。

**【請求項 2】**

第1の基板及び第2の基板それぞれに金属膜と、金属酸化膜と、絶縁膜と、半導体膜とを順に積層するように形成し、

前記第1の基板及び前記第2の基板それぞれに形成された前記半導体膜を結晶化し、

前記第1の基板及び前記第2の基板それぞれの前記結晶化された半導体膜を用いて、前記第1の基板上に薄膜集積回路及び前記第2の基板上に表示装置を形成し、

前記薄膜集積回路を間に挟んで前記第1の基板と向かい合うように、第1の接着剤を用いて第3の基板を貼り合わせ、かつ前記表示装置を間に挟んで前記第2の基板と向かい合うように、第2の接着剤を用いて第4の基板を貼り合わせ、10

前記金属酸化膜を前記金属膜側と前記絶縁膜側とに分離させることで、前記第1の基板及び前記第2の基板を取り除き、

前記薄膜集積回路の前記絶縁膜が形成された側を、第3の接着剤を用いて第5の基板の一方の面に貼り合わせ、

前記表示装置の前記絶縁膜が形成された側を、第4の接着剤を用いて前記第5の基板の他方の面に貼り合わせ、

前記第1の接着剤及び前記第2の接着剤を除去することで、前記第3の基板及び前記第4の基板を取り除き、20

前記薄膜集積回路と前記第5の基板の他方の面に設けられたアンテナとを、前記第5の基板に設けられたコンタクトホールを介して電気的に接続し、

前記薄膜集積回路と前記表示装置とを、電気的に接続することを特徴とする記録媒体の作製方法。20

**【請求項 3】**

請求項1又は請求項2において、

前記第5の基板は、プリント配線基板であることを特徴とする記録媒体の作製方法。

**【請求項 4】**

請求項1乃至請求項3のいずれか一において、

前記表示装置は、液晶表示装置又は発光装置であることを特徴とする記録媒体の作製方法。30

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、メモリやマイクロプロセッサ(CPU)などの集積回路を内蔵したICカードに関し、さらには該ICカードをキャッシュカードとして用いた場合の、取引内容の記帳システムに関する。

**【背景技術】**

**【0002】**

磁気で記録するタイプの磁気カードは記録できるデータがわずか数十バイト程度であるのに対し、半導体のメモリが内蔵されているICカードは、記録できるデータが5KB程度、もしくはそれ以上が一般的であり、格段に大きい容量を確保することができる。その上、磁気カードのようにカード上に砂鉄をかける等の物理的方法によりデータが読み取られる恐れがなく、また記憶されているデータが改ざんされにくいというメリットがある。40

**【0003】**

そして近年、メモリに加えてCPUが搭載されることによって、ICカードはさらに高機能化され、その用途は、キャッシュカード、クレジットカード、プリペイドカード、診察券、学生証や社員証等の身分証明証、定期券、会員証など多岐に渡っている。高機能化の一例として、下記特許文献1には、単純な文字や数字などを表示できる表示装置と、数字を入力するためのキーボードとが搭載されたICカードについて記載されている。

**【0004】**

10

20

30

40

50

【特許文献1】特公平2-7105号公報

【0005】

特許文献1に記載されているように、ICカードに機能を付加することで、新たな利用の仕方が可能になる。現在、ICカードを用いた電子商取引、在宅勤務、遠隔医療、遠隔教育、行政サービスの電子化、高速道路の自動料金収受、映像配信サービス等の実用化が進められており、将来的にはより広範な分野においてICカードが利用されると考えられている。

【発明の開示】

【発明が解決しようとする課題】

【0006】

10

このように利用が広がるにつれ、ICカードの不正使用が無視できない大きな問題となっており、ICカード使用の際の本人認証の確実性を如何に高めるかが、今後の課題である。

【0007】

不正使用の防止策の一つにICカードへの顔写真の掲載がある。顔写真を掲載することで、ATM等の無人の端末装置ではない限り、ICカード使用の際に第三者が目視で本人の認証を行なうことが可能である。そして、至近距離で使用者の顔を撮影できるような防犯用の監視カメラを設置していない場合でも、不正使用の防止を効果的に行なうことができる。

【0008】

20

しかし、一般的に顔写真は印刷法によりICカードに転写されており、偽造によって比較的容易にすり替ることができるという落とし穴がある。

【0009】

またICカードの厚さは一般的に0.7mmと薄い。そのため、集積回路が搭載されるエリアが限られている場合、高機能化を目指そうとすると、回路規模やメモリ容量のより大きい集積回路をその限られた容積の中により多く搭載する必要がある。

【0010】

そこで本発明は、顔写真のすり替などの偽造を防止することでセキュリティを確保することができ、なおかつ顔写真以外の画像の表示できる、より高機能なICカードの提案を課題とする。

30

【課題を解決するための手段】

【0011】

本発明では、ICカード内に收まるような薄さの表示装置を、ICカード内に搭載する。具体的には、以下の手法を用いて集積回路と表示装置を作製する。

【0012】

まず第1の基板上に金属膜を成膜し、該金属膜の表面を酸化することで数nmの極薄い金属酸化膜を成膜する。次に該金属酸化膜上に絶縁膜、半導体膜を順に積層するように成膜する。そして該半導体膜を用いて、集積回路または表示装置に用いられる半導体素子を作製する。なお本明細書では、既存のシリコンウェハを用いて形成された集積回路と区別するために、以下、本発明で用いる上記集積回路を薄膜集積回路と呼ぶ。半導体素子を形成したら、該素子を覆うように第2の基板を貼り合わせ、第1の基板と第2の基板の間に半導体素子が挟まれた状態にする。

40

【0013】

そして第1の基板の半導体素子が形成されている側とは反対の側に、第1の基板の剛性を補強するために第3の基板を貼り合わせる。第2の基板よりも第1の基板の剛性が高いほうが、第1の基板を引き剥がす際に、半導体素子に損傷が与えられにくくスムーズに剥がすことができる。ただし第3の基板は、後に第1の基板を半導体素子から引き剥がす際に、第1の基板の剛性が十分であれば、必ずしも貼り合わせる必要はない。

【0014】

次に、加熱処理等を施すことで金属酸化膜を結晶化し、脆性を高め、基板を半導体素子

50

から剥離しやすくする。そして第1の基板を第3の基板と共に、半導体素子から引き剥がす。なお、金属酸化膜を結晶化するための加熱処理は、第3の基板を貼り合わせる前であってもよいし、第2の基板を貼り合わせる前であってもよい。或いは、半導体素子を形成する工程において行なわれる加熱処理が、この金属酸化膜の結晶化の工程を兼ねていても良い。

#### 【0015】

この引き剥がしによって、金属膜と金属酸化膜の間で分離する部分と、絶縁膜と金属酸化膜の間で分離する部分と、金属酸化膜自体が双方に分離する部分とが生じる。いずれにしろ、半導体素子は第2の基板側に貼り付くように、第1の基板から引き剥がされる。

#### 【0016】

そして第1の基板を剥離した後、半導体素子をプリント配線基板またはインターポーヴにマウントし、第2の基板を剥離する。なお、第2の基板は必ずしも剥離する必要はなく、第2の基板の厚さが問題にならないようであれば、貼り付けたまま完成としても良い。

10

#### 【0017】

なお表示装置の表示素子は、マウントした後に作製する。具体的に液晶表示装置の場合、例えば半導体素子の一つであるTFTに電気的に接続された液晶セルの画素電極や、該画素電極を覆っている配向膜を作製してからマウントし、その後、別途作製しておいた対向基板を貼り合わせて液晶を注入し完成させるようにする。

#### 【0018】

また第1の基板を剥離した後、半導体素子をプリント配線基板またはインターポーヴではなく、表示装置の土台となる別の基板に貼り合わせるようにしても良い。そして表示素子を形成して表示装置が完成した後、表示装置を土台となる基板ごとプリント配線基板またはインターポーヴにマウントするようにしても良い。この場合、第2の基板の剥離は、マウントの前に行なわれることになる。なお、土台となる基板の厚さは、ICカード自体の薄膜化を妨げることのない程度とし、具体的には数百μm以下程度とするのが望ましい。

20

#### 【0019】

また、半導体素子を用いて形成された表示装置または薄膜集積回路と、プリント配線基板またはインターポーヴと、の電気的な接続（ボンディング）は、フリップチップ法、TAB (Tape Automated Bonding) 法を用いても、またワイヤボンディング法を用いても良い。フリップチップ法を用いる場合、ボンディングはマウントと同時に行なわれる。ワイヤボンディング法を用いる場合、ボンディングの工程は、マウントした後、第2の基板が剥離された状態で行なう。

30

#### 【0020】

なお1つの基板上に、複数の薄膜集積回路や表示装置を形成する場合、途中でダイシングを行ない、薄膜集積回路や表示装置を互いに切り離すようにする。ダイシングを行なうタイミングは、薄膜集積回路の場合パッケージングの有無によって異なり、表示装置の場合土台となる基板の有無によって異なるが、いずれの場合においてもプリント配線基板にマウントまたは実装される前に行なう。

#### 【0021】

40

また薄膜集積回路をパッケージングする場合、同一のインターポーヴ上に複数の薄膜集積回路をマウントしてMCPとして用いても良い。この場合も、薄膜集積回路間の電気的なワイヤボンディング法を用いても良いし、フリップチップ法を用いても良い。

#### 【0022】

またインターポーヴは、プリント配線基板との電気的接続をリードフレームで行なうタイプであっても良いし、バンプを用いて行なうタイプであっても良いし、その他公知の形態を有していても良い。

#### 【0023】

本発明では、シリコンウェハで作製された集積回路の膜厚が50μm程度であるのに対し、膜厚500nm以下の薄膜の半導体膜を用いて、トータルの膜厚が1μm以上5μm

50

以下、代表的には 2  $\mu\text{m}$  程度の飛躍的に薄い薄膜集積回路を形成することができる。また表示装置の厚さを 0.5 mm 程度、より望ましくは 0.02 mm 程度とすることができる。よって、表示装置を薄さ 0.05 mm 以上 1 mm 以下の IC カードに搭載することができる。また、回路規模やメモリ容量のより大きい薄膜集積回路を、IC カードの限られた容積の中により多く搭載することができ、小型化、軽量化を妨げずに IC カードの多機能を実現することができる。

#### 【0024】

また本発明は、シリコンウェハに比べて安価で大型のガラス基板を用いることができる 10 ので、より低いコストで、なおかつ高いスループットで薄膜集積回路を大量生産することができ、生産コストを飛躍的に抑えることができる。また、基板を繰り返し使用することも可能なので、コストを削減することができる。

#### 【0025】

また、シリコンウェハで作製された集積回路のように、クラックや研磨痕の原因となるバックグラインド処理を行なう必要がなく、また厚さのバラツキも、薄膜集積回路を構成する各膜の成膜時におけるばらつきに依存することになるので、大きくても数百 nm 程度であり、バックグラインド処理による数～数十  $\mu\text{m}$  のばらつきと比べて飛躍的に小さく抑えられることがある。

#### 【0026】

またプリント配線基板の形状に合わせて薄膜集積回路や表示装置を貼り合わせることが可能なので、IC カードの形状の自由度が高まる。よって例えば、円柱状のピンなどに貼り付けられるような、曲面を有する形状に IC カードを形成することも可能である。 20

#### 【0027】

なお、薄膜集積回路はプリント配線基板上にペアチップとして直接実装する形態に限定されず、インターポーラ上にマウントしてパッケージングしてから実装する形態も取り得る。ペアチップとして実装することで小型化、軽量化を図ることができる。一方、パッケージングしてから実装することで、パッケージングメーカーから供給された薄膜集積回路を電子機器メーカー側で実装する際に、クリーンルームや特殊なボンダ等の設備・技術を必要とせず、実装を容易にできる。そして、薄膜集積回路を外部環境から守り、プリント配線基板のフットプリントを標準化することができ、サブミクロンスケールの薄膜集積回路の配線をプリント配線基板と同程度のミリメートルスケールまで拡大することができる。 30

#### 【0028】

パッケージは、CSP (Chip Size Package)、MCP (Multi Chip Package) のみならず、DIP (Dual In-line Package)、QFP (Quad Flat Package)、SOP (Small Outline Package) などのあらゆる公知の形態が可能である。

#### 【0029】

なお表示装置は、例えば液晶表示装置、有機発光素子に代表される発光素子を各画素に備えた発光装置、DMD (Digital Micromirror Device) 等を用いることができる。また薄膜集積回路にはマイクロプロセッサ (CPU)、メモリ、電源回路、またその他のデジタル回路やアナログ回路を設けることができる。さらに該表示装置の駆動回路や、該駆動回路に供給する信号を生成するコントローラを薄膜集積回路内に設けても良い。 40

#### 【0030】

なお本発明はカードのみに限定されず、上述したような薄膜集積回路及び表示装置を兼ね備え、なおかつホストとのデータの送受が可能な携帯型の記録媒体をその範疇に含む。

#### 【発明の効果】

#### 【0031】

このように本発明では、シリコンウェハに比べて安価で大型のガラス基板を用いることができる。よって、表示装置を薄さ 0.05 mm 以上 1 mm 以下の IC カードに搭載することができ、生産コストを飛躍的に抑えることができる。また、基板を繰り返し使用することも可能なので、コストを削減することができる。 50

**【0032】**

また本発明では飛躍的に薄い薄膜集積回路を形成することができるので、回路規模やメモリ容量のより大きい薄膜集積回路を、ICカードの限られた容積の中により多く搭載することができる。また表示装置を薄さ0.05mm以上1mm以下のICカードに搭載するが可能な程度の厚さで形成することができる。したがって、小型化、軽量化を妨げずにICカードの多機能を実現することができる。

**【0033】**

またプリント配線基板の形状に合わせて薄膜集積回路や表示装置を貼り合わせることが可能なので、ICカードの形状の自由度が高まる。よって例えば、円柱状のピンなどに貼り付けられるような、曲面を有する形状にICカードを形成することも可能である。

10

**【発明を実施するための最良の形態】****【0034】**

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて、本実施の形態の記載内容に限定して解釈されるものではない。

**【0035】**

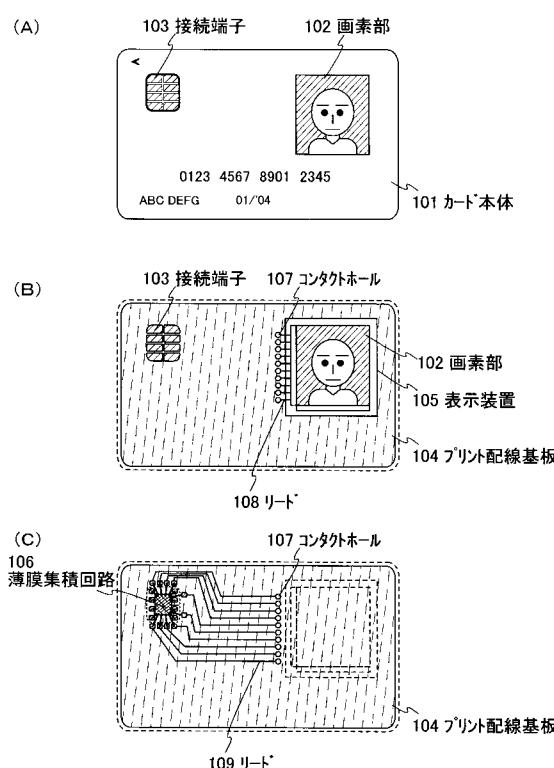

図1(A)に、本発明のICカードの上面図を示す。図1(A)に示すICカードは、ICカードに設けられた接続端子と端末装置のリーダライタとを電気的に接続し、データの送受信を行なう接触型であるが、非接触でデータの送受信を行なう非接触型であってもよい。

20

**【0036】**

101はカード本体であり、102はカード本体101に搭載されている表示装置の画素部、103は同じくカード本体101に搭載されている薄膜集積回路の接続端子に相当する。

**【0037】**

図1(B)に、図1(A)に示したカード本体の内部に封止されているプリント配線基板104の構成を示す。また図1(C)に、図1(B)に示したプリント配線基板104の裏側の構成を示す。プリント配線基板104の一方の面には表示装置105が実装されており、他方の面には薄膜集積回路106が実装されている。

30

**【0038】**

なお図1に示すICカードは、表示装置105と薄膜集積回路106が、プリント配線基板104の異なる面に実装されているが、共に同じ面に実装されていても良い。図1に示すように、表示装置105と薄膜集積回路106が、プリント配線基板104の異なる面に実装されている場合、表示装置105に電気的に接続されているリード(配線)108と、薄膜集積回路106に電気的に接続されているリード(配線)109とを、コンタクトホール107を介して電気的に接続させる。

**【0039】**

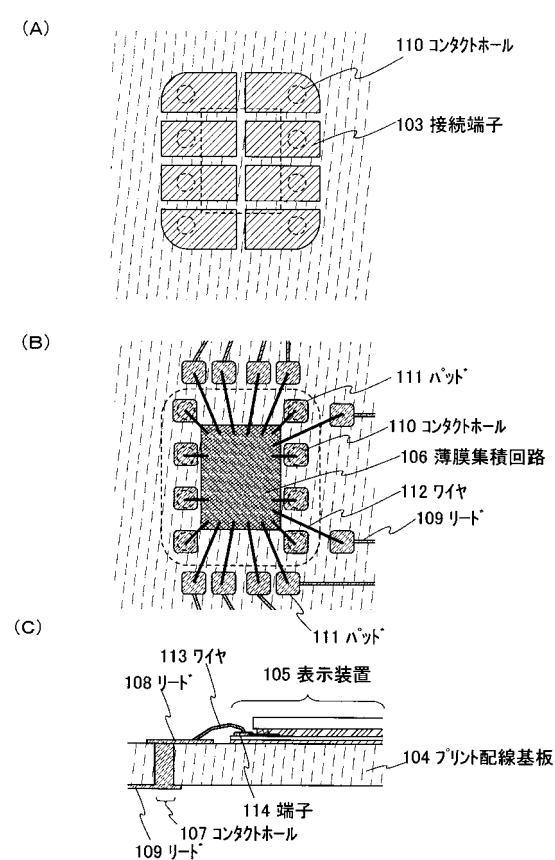

接続端子103は、端末装置に備えられたリーダライタと直接接続し、端末装置とICカードとの間のデータの送受信を行なうための端子である。図2(A)に、図1(B)に示した接続端子103の拡大図を示す。また、図2(B)に、図1(C)に示した薄膜集積回路106の拡大図を示す。

40

**【0040】**

図2(A)では、プリント配線基板104の一方の面に、接続端子103が8つ設けられている例を示しており、無論接続端子の数はこれに限定されない。また図2(B)に示すように、プリント配線基板104の他方の面に、パッド111が複数設けられている。

**【0041】**

パッド111は、ワイヤ112によって薄膜集積回路106と電気的に接続されている。パッド111には、プリント配線基板104に設けられたコンタクトホール110を介して接続端子103と電気的に接続されたものや、リード109に電気的に接続されたも

50

のが存在する。また時には、ワイヤ 112 を設けずに薄膜集積回路 106 と電気的に接続することなく、接続端子 103 やリード 109 と電気的に接続されているパッド 111 を設けても良い。

#### 【0042】

また図 2 (C) に、表示装置 105 とリード 108 の接続部分の断面図を示す。図 2 (C) に示すように、表示装置 105 に設けられた端子 114 とリード 108 とが、ワイヤ 113 によって電気的に接続されており、リード 108 とリード 109 とが、コンタクトホール 107 を介して電気的に接続されている。

#### 【0043】

なお本実施の形態では、パッド 111 と薄膜集積回路 106 との間の電気的な接続を、ワイヤボンディング法を用いて行っているが、本発明はこれに限定されない。ワイヤボンディング法に限らず、ソルダーボールを用いたフリップチップ法で接続しても良いし、その他の方法を用いていても良い。また、表示装置 105 とリード 108 との間の電気的な接続は、ワイヤボンディング法に限定されず、その他の方法を用いていても良い。

#### 【0044】

また接続端子 103 と薄膜集積回路 106 との間の電気的な接続は、本実施の形態に示した形態に限定されない。例えばパッドを設けずに、コンタクトホールを介して直接ワイヤで接続端子と薄膜集積回路とを接続するようにしても良い。

#### 【0045】

次に、薄膜集積回路の作製方法について述べた後、表示装置の作製方法について述べる。なお本実施の形態では、半導体素子として 2 つの TFT を例に挙げて示すが、薄膜集積回路と表示装置に含まれる半導体素子はこれに限定されず、あらゆる回路素子を用いることができる。例えば、TFT の他に、記憶素子、ダイオード、光電変換素子、抵抗素子、コイル、容量素子、インダクタなどが代表的に挙げられる。

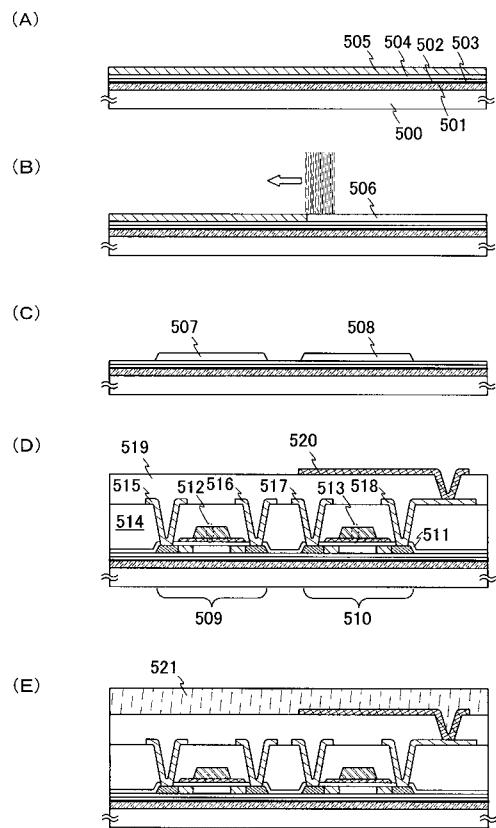

#### 【0046】

まず図 3 (A) に示すように、スパッタ法を用いて第 1 の基板 500 上に金属膜 501 を成膜する。ここでは金属膜 501 にタンゲステンを用い、膜厚を 10 nm ~ 200 nm 、好ましくは 50 nm ~ 75 nm とする。なお本実施の形態では第 1 の基板 500 上に直接金属膜 501 を成膜するが、例えば酸化珪素、窒化珪素、窒化酸化珪素等の絶縁膜で第 1 の基板 500 を覆ってから、金属膜 501 を成膜するようにしても良い。

#### 【0047】

そして金属膜 501 の成膜後、大気に曝すことなく酸化物膜 502 を積層するように成膜する。ここでは酸化物膜 502 として酸化珪素膜を膜厚 150 nm ~ 300 nm となるように成膜する。なお、スパッタ法を用いる場合、第 1 の基板 500 の端面にも成膜が施される。そのため、後の工程における剥離の際に、酸化物膜 502 が第 1 の基板 500 側に残ってしまうのを防ぐために、端面に成膜された金属膜 501 と酸化物膜 502 とを O<sub>2</sub> アッシングなどで選択的に除去することが好ましい。

#### 【0048】

また酸化物膜 502 の成膜の際に、スパッタの前段階としてターゲットと基板との間をシャッターで遮断してプラズマを発生させる、プレスパッタを行なう。プレスパッタは Ar を 10 sccm 、 O<sub>2</sub> をそれぞれ 30 sccm の流量とし、第 1 の基板 500 の温度を 270 °C 、成膜パワーを 3 kW の平衡状態に保って行なう。プレスパッタにより、金属膜 501 と酸化物膜 502 の間に極薄い数 nm ( ここでは 3 nm ) 程度の金属酸化膜 503 が形成される。金属酸化膜 503 は、金属膜 501 の表面が酸化することで形成される。よって本実施の形態では、金属酸化膜 503 は酸化タンゲステンで形成される。

#### 【0049】

なお本実施の形態では、プレスパッタにより金属酸化膜 503 を形成しているが、本発明はこれに限定されない。例えば酸素、または酸素に Ar 等の不活性ガスを添加し、プラズマにより意図的に金属膜 501 の表面を酸化し、金属酸化膜 503 を形成するようにしても良い。

10

20

30

40

50

**【0050】**

次に酸化物膜502を成膜した後、PCVD法を用いて下地膜504を成膜する。ここでは下地膜504として、酸化窒化珪素膜を膜厚100nm程度となるように成膜する。そして下地膜504を成膜した後、大気に曝さずに半導体膜505を形成する。半導体膜505の膜厚は25~100nm(好ましくは30~60nm)とする。なお半導体膜505は、非晶質半導体であっても良いし、多結晶半導体であっても良い。また半導体は珪素だけではなくシリコンゲルマニウムも用いることができる。シリコンゲルマニウムを用いる場合、ゲルマニウムの濃度は0.01~4.5atomic%程度であることが好ましい。

**【0051】**

次に図3(B)に示すように、半導体膜505を公知の技術により結晶化する。公知の結晶化方法としては、電熱炉を使用した熱結晶化方法、レーザ光を用いたレーザ結晶化法、赤外光を用いたランプアニール結晶化法がある。或いは特開平7-130652号公報で開示された技術に従って、触媒元素を用いる結晶化法を用いることもできる。

10

**【0052】**

また、なお予め多結晶半導体膜である半導体膜505を、スパッタ法、プラズマCVD法、熱CVD法などで形成するようにしても良い。

**【0053】**

本実施の形態ではレーザ結晶化により、半導体膜505を結晶化する。連続発振が可能な固体レーザを用い、基本波の第2高調波~第4高調波のレーザ光を照射することで、大粒径の結晶を得ることができる。例えば、代表的には、Nd:YVO<sub>4</sub>レーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いるのが望ましい。具体的には、連続発振のYVO<sub>4</sub>レーザから射出されたレーザ光を非線形光学素子により高調波に変換し、出力10Wのレーザ光を得る。また非線形光学素子を用いて、高調波を射出する方法もある。そして、好ましくは光学系により照射面にて矩形状または橢円形状のレーザ光に成形して、半導体膜505に照射する。このときのエネルギー密度は0.01~100MW/cm<sup>2</sup>程度(好ましくは0.1~10MW/cm<sup>2</sup>)が必要である。そして、走査速度を10~2000cm/s程度とし、矢印の方向に向かってレーザ光を照射する。

20

**【0054】**

なおレーザ結晶化は、連続発振の基本波のレーザ光と連続発振の高調波のレーザ光とを照射するようにしても良いし、連続発振の基本波のレーザ光とパルス発振の高調波のレーザ光とを照射するようにしても良い。

30

**【0055】**

なお、希ガスや窒素などの不活性ガス雰囲気中でレーザ光を照射するようにしても良い。これにより、レーザ光照射による半導体表面の荒れを抑えることができ、界面準位密度のばらつきによって生じる閾値のばらつきを抑えることができる。

**【0056】**

上述した半導体膜505へのレーザ光の照射により、結晶性がより高められた半導体膜506が形成される。次に、図3(C)に示すように半導体膜506をパターニングし、島状の半導体膜507、508が形成され、該島状の半導体膜507、508を用いてTFTに代表される各種の半導体素子が形成される。なお本実施の形態では、下地膜504と島状の半導体膜507、508との間に、電極や絶縁膜等が形成されていても良い。例えば半導体素子の1つであるボトムゲート型のTFTの場合、下地膜504と島状の半導体膜507、508との間に、ゲート電極とゲート絶縁膜が形成される。

40

**【0057】**

本実施の形態では、島状の半導体膜507、508を用いてトップゲート型のTFT509、510を形成する(図3(D))。具体的には、島状の半導体膜507、508を覆うようにゲート絶縁膜511を成膜する。そして、ゲート絶縁膜511上に導電膜を成膜し、パターニングすることで、ゲート電極512、513を形成する。そして、ゲート

50

電極 512、513や、あるいはレジストを成膜しパターニングしたものをマスクとして用い、島状の半導体膜 507、508にn型を付与する不純物を添加し、ソース領域、ドレイン領域、さらにはLDD領域等を形成する。なおここではTFT509、510をn型とするが、p型のTFTの場合は、p型の導電性を付与する不純物を添加する。

#### 【0058】

上記一連の工程によってTFT509、510を形成することができる。なおTFTの作製方法は、上述した工程に限定されない。

#### 【0059】

次にTFT509、510を覆って第1の層間絶縁膜514を成膜する。そして、ゲート絶縁膜511及び第1の層間絶縁膜514にコンタクトホールを形成した後、コンタクトホールを介してTFT509、510と接続する配線515～518を、第1の層間絶縁膜514に接するように形成する。そして配線515～518を覆うように、第1の層間絶縁膜514上に第2の層間絶縁膜519を成膜する。10

#### 【0060】

そして第2の層間絶縁膜519にコンタクトホールを形成し、該コンタクトホールを介して配線518と接続する端子520が、第2の層間絶縁膜519上に形成される。なお本実施の形態では、端子520が配線518を介してTFT510と電気的に接続されているが、半導体素子と端子520との電気的な接続の形態は、これに限定されない。

#### 【0061】

次に、第2の層間絶縁膜519及び端子520上に保護層521を形成する。保護層521は、後に第2の基板を張り合わせたり剥離したりする際に、第2の層間絶縁膜519及び端子520の表面を保護することができ、なおかつ第2の基板の剥離後に除去することが可能な材料を用いる。例えば、水またはアルコール類に可溶なエポキシ系、アクリレート系、シリコーン系の樹脂を全面に塗布し、焼成することで保護層521を形成することができる。20

#### 【0062】

本実施の形態ではスピンドルコートで水溶性樹脂（東亜合成製：VL-WSHL10）を膜厚30μmとなるように塗布し、仮硬化させるために2分間の露光を行ったあと、UV光を裏面から2.5分、表面から10分、合計12.5分の露光を行って本硬化させて、保護層521を形成する（図3（E））。30

#### 【0063】

なお、複数の有機樹脂を積層する場合、有機樹脂同士では使用している溶媒によって塗布または焼成時に一部溶解したり、密着性が高くなりすぎたりする恐れがある。従って、第2の層間絶縁膜519と保護層521と共に同じ溶媒に可溶な有機樹脂を用いる場合、後の工程において保護層521の除去がスムーズに行なわれるよう、第2の層間絶縁膜519を覆うように、なおかつ第2の層間絶縁膜519と端子520との間に挟まれるように、無機絶縁膜（SiNx膜、SiNxOy膜、AlNx膜、またはAlNxOy膜）を形成しておくことがほしい。

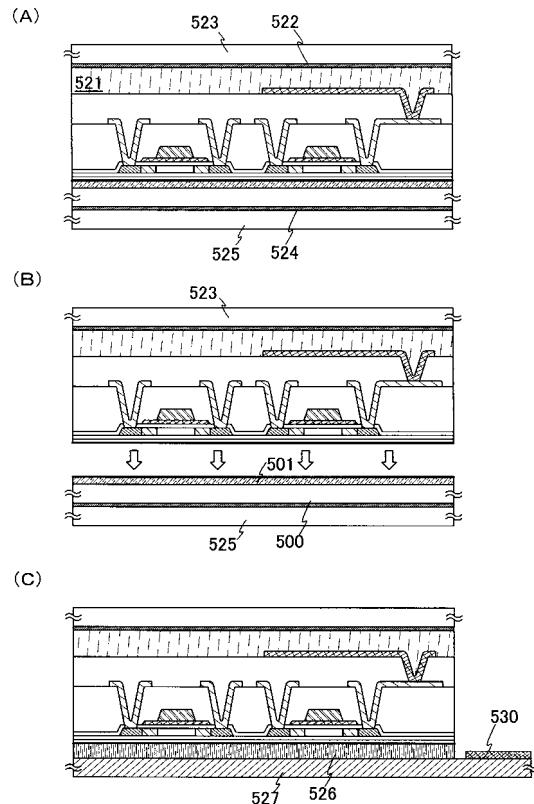

#### 【0064】

次に、後の剥離を行ない易くするために、金属酸化膜503を結晶化させる。結晶化により、金属酸化膜503が粒界において割れやすくなり、脆性を高めることができる。本実施の形態では、420～550、0.5～5時間程度加熱処理を行ない、結晶化を行なった。40

#### 【0065】

次に、金属酸化膜503と酸化物膜502の間の密着性、または金属酸化膜503と金属膜501の間の密着性を部分的に低下させ、剥離開始のきっかけとなる部分を形成する処理を行なう。具体的には、剥離しようとする領域の周縁に沿って外部から局所的に圧力を加えて金属酸化膜503の層内または界面近傍の一部に損傷を与える。本実施の形態では、ダイヤモンドペンなどの硬い針を金属酸化膜503の端部近傍に垂直に押しつけ、そのまま荷重をかけた状態で金属酸化膜503に沿って動かす。好ましくは、スクライバー

装置を用い、押し込み量を0.1mm～2mmとし、圧力をかけて動かせばよい。このように、剥離を行なう前に、剥離が開始されるきっかけとなるような、密着性の低下した部分を形成することで、後の剥離工程における不良を低減させることができ、歩留まり向上につながる。

#### 【0066】

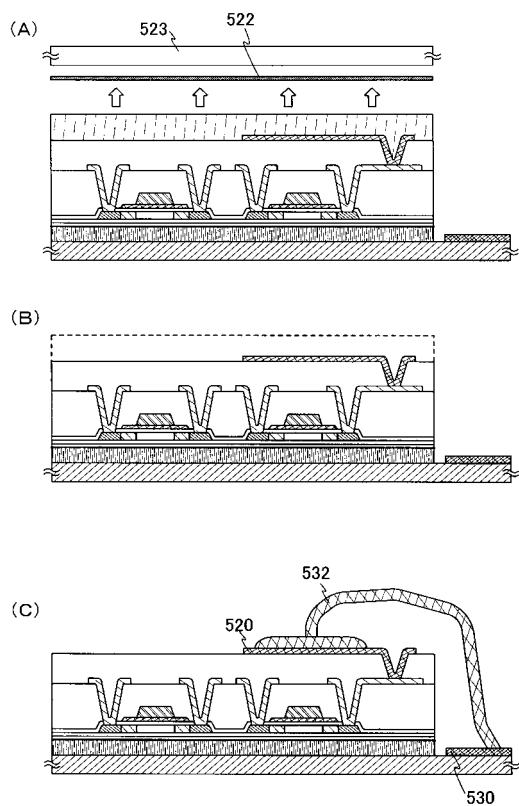

次いで、両面テープ522を用い、保護層521に第2の基板523を貼り付け、さらに両面テープ524を用い、第1の基板500に第3の基板525を貼り付ける（図4（A））。なお両面テープではなく接着剤を用いてもよい。例えば紫外線によって剥離する接着剤を用いることで、第2の基板剥離の際に半導体素子にかかる負担を軽減させることができる。第3の基板525は、後の剥離工程で第1の基板500が破損することを防ぐ。第2の基板523および第3の基板525としては、第1の基板500よりも剛性の高い基板、例えば石英基板、半導体基板を用いることが好ましい。10

#### 【0067】

次いで、金属膜501と酸化物膜502とを物理的に引き剥がす。引き剥がしは、先の工程において、金属酸化膜503の金属膜501または酸化物膜502に対する密着性が部分的に低下した領域から開始する。

#### 【0068】

引き剥がしによって、金属膜501と金属酸化膜503の間で分離する部分と、酸化物膜502と金属酸化膜503の間で分離する部分と、金属酸化膜503自体が双方に分離する部分とが生じる。そして第2の基板523側に半導体素子（ここではTFT509、510）が、第3の基板525側に第1の基板500及び金属膜501が、それぞれ張り付いたまま分離する。引き剥がしは比較的小さな力（例えば、人間の力、ノズルから吹付けられるガスの風圧、超音波等）で行なうことができる。剥離後の状態を図4（B）に示す。20

#### 【0069】

次に、接着剤526でプリント配線基板527と、部分的に金属酸化膜503が付着している酸化物膜502とを接着する（図4（C））。なお本実施の形態では、薄膜集積回路をペアチップとしてプリント配線基板に実装する例について示すが、パッケージングしてから実装する場合は、インターポーラにマウントする。30

#### 【0070】

この接着の際に、両面テープ522による第2の基板523と保護層521との間の密着力よりも、接着剤526による酸化物膜502とプリント配線基板527との間の密着力の方が高くなるように、接着剤526の材料を選択することが重要である。

#### 【0071】

なお、金属酸化膜503が酸化物膜502の表面に残存していると、プリント配線基板527との密着性が悪くなる場合があるので、完全にエッティング等で除去してからプリント配線基板に接着させ、密着性を高めるようにしても良い。

#### 【0072】

プリント配線基板527として、セラミックス基板、ガラスエポキシ基板、ポリイミド基板等の公知の材料を用いることができる。なお薄膜集積回路や表示装置において発生した熱を拡散させるために、2～30W/mK程度の高い熱伝導率を有するのが望ましい。40

#### 【0073】

プリント配線基板527上には、パッド530が設けられている。パッド530は、例えば銅にはんだ、金またはスズをメッキすることで形成されている。

#### 【0074】

接着剤526としては、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤が挙げられる。さらに、銀、ニッケル、アルミニウム、窒化アルミニウムからなる粉末、またはフィラーを含ませて接着剤526も高い熱伝導性を備えていることが好ましい。

#### 【0075】

10

20

30

40

50

次に図5(A)に示すように、保護層521から両面テープ522と第2の基板523を順に、または同時に剥がす。

#### 【0076】

そして図5(B)に示すように保護層521を除去する。ここでは保護層521に水溶性の樹脂が使われているので、水に溶かして除去する。保護層521が残留していると不良の原因となる場合は、除去後の表面に洗浄処理やO<sub>2</sub>プラズマ処理を施し、残留している保護層521を除去することが好ましい。

#### 【0077】

次に、図5(C)に示すようにワイヤボンディング法を用いて、端子520とパッド530をワイヤ532で接続する。マウントと電気的な接続を行なうことで、実装が完了する。

10

#### 【0078】

なお、薄膜集積回路をインターポーラ上にマウントしてパッケージングする場合は、気密封止方式または樹脂封止方式等で封止することができる。気密封止方式を用いる場合、一般的にはセラミック、金属またはガラス等のケースを用いて封止する。また樹脂封止方式を用いる場合、具体的にはモールド樹脂等が用いられる。なお必ずしも薄膜集積回路を封止する必要はないが、パッケージの強度を高めたり、薄膜集積回路において発生した熱を放熱したり、隣接する回路からの電磁ノイズを遮ったりすることができる。

#### 【0079】

なお本実施の形態では、金属膜501としてタンクステンを用いているが、本発明において金属膜はこの材料に限定されない。その表面に金属酸化膜503が形成され、該金属酸化膜503を結晶化することで基板を引き剥がすことができるような金属を含む材料であれば良い。例えば、Wの他にTiN、WN、Mo等を用いることができる。またこれらの合金を金属膜として用いる場合、その組成比によって結晶化の際の加熱処理の最適な温度が異なる。よって組成比を調整することで、半導体素子の作製工程にとって妨げとなるない温度で加熱処理を行なうことができ、半導体素子のプロセスの選択肢が制限されにくく。

20

#### 【0080】

なおレーザ結晶化の際、各薄膜集積回路を、レーザ光のビームスポットの走査方向に対して垂直な方向における幅に収まる領域に形成することで、薄膜集積回路が、ビームスポットの長軸の両端に形成される結晶性の劣った領域(エッジ)を横切るのを防ぎ、少なくとも結晶粒界のほとんど存在しない半導体膜を、薄膜集積回路内の半導体素子に用いることができる。

30

#### 【0081】

上記作製方法によって、トータルの膜厚1μm以上5μm以下、代表的には2μm程度の飛躍的に薄い薄膜集積回路を形成することができる。なお薄膜集積回路の厚さには、半導体素子自体の厚さのみならず、金属酸化膜と半導体素子との間に設けた絶縁膜の厚さと、半導体素子を形成した後に覆う層間絶縁膜の厚さと、端子の厚さとを含める。

#### 【0082】

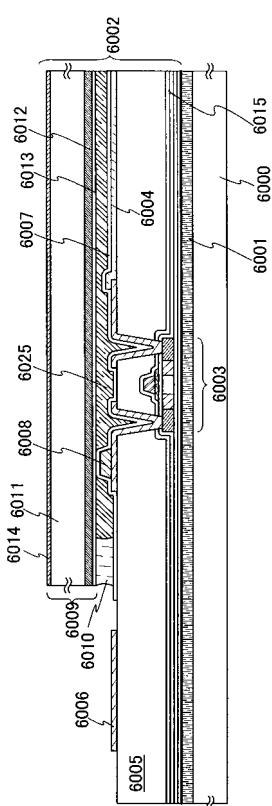

次に、図6を用いて、本発明の表示装置の作製方法について説明する。

40

#### 【0083】

図6は、プリント配線基板6000上に、接着剤6001によってマウントされた表示装置6002の断面図に相当する。図6では、表示装置6002として液晶表示装置を用いた例を示す。

#### 【0084】

図6に示す表示装置6002では、まず図3(A)に示した作製方法に従って、半導体膜まで形成する。そして該半導体膜を用いたTFT6003と、該TFT6003を覆っている無機絶縁膜で形成されたパッシベーション膜6015と、層間絶縁膜6005と、該TFT6003に電気的に接続され、なおかつ層間絶縁膜6005上に形成された画素電極6004と、同じく層間絶縁膜6005上に形成された表示装置6002用の端子6

50

006と、画素電極6004を覆っている配向膜6007とを形成する。そして配向膜6007にはラビング処理を施しておく。また配向膜6007を形成する前に、絶縁膜を用いてスペーサ6008を形成しても良い。なお端子6006は、配向膜6007によって覆われず、露出させるようにする。

#### 【0085】

そして、図3(E)に示した作製方法に従って、配向膜6007上に保護膜を形成し、図4(A)～図5(B)に示した工程に従って、第1の基板を剥離した後、プリント配線基板にマウントし、第2の基板と保護膜を除去する。

#### 【0086】

そして別途形成しておいた対向基板6009を、シール材6010を用いて配向膜6007に貼り合わせる。シール材にはフィラーが混入されていても良い。対向基板6009は、その厚さが数百μm程度の基板6011上に、透明導電膜からなる対向電極6012と、ラビング処理が施された配向膜6013が形成されている。なおこれらに加えて、カラーフィルタや、ディスクリネーションを防ぐための遮蔽膜などが形成されていても良い。また、偏光板6014を、対向基板6009の対向電極6012が形成されている面とは逆の面に、貼り合わせておく。

#### 【0087】

なお基板6011はプラスチック基板を用いることができる。プラスチック基板としては、極性基のついたノルボルネン樹脂からなるARTON:JSR製を用いることができる。また、ポリエチレンテレフタレート(PET)、ポリエーテルスルホン(PES)、ポリエチレンナフタレート(PEN)、ポリカーボネート(PC)、ナイロン、ポリエーテルエーテルケトン(PEEK)、ポリスルホン(PSF)、ポリエーテルイミド(PEI)、ポリアリレート(PAR)、ポリブチレンテレフタレート(PBT)、ポリイミドなどのプラスチック基板を用いることができる。

#### 【0088】

そして液晶6025を注入して封止し、表示装置が完成する。そして表示装置6002用の端子6006と、プリント配線基板6000に設けられたリードとを、ワイヤボンディング法等を用いて、電気的に接続することで、実装が完了する。

#### 【0089】

なお本実施の形態では、表示装置の作製工程において、第1の基板を剥離した後プリント配線基板にマウントしているが、本発明はこれに限定されない。表示装置の土台となる基板を別途用意し、第1の基板を剥離した後、該土台となる基板に貼り合わせるようにしても良い。そして、プリント配線基板に、該土台となる基板ごとマウントするようにしても良い。この場合、表示装置が完成してからプリント配線基板に該表示装置をマウントすることが可能である。つまり、液晶表示装置の場合、液晶を注入して封止することで表示装置を完成させてから、プリント配線基板にマウントすることができる。例えば発光装置では、表示素子である発光素子の作製は、電界発光層の成膜や陰極の成膜などの工程が含まれるので、プリント配線基板上において行なうのが難しい。よって発光装置の場合、土台となる基板を用い、表示装置を完成させてから、プリント配線基板にマウントする方法が有効である。

#### 【0090】

なお、図6に示した液晶表示装置は反射型であるが、バックライトの搭載が可能であれば透過型であってもよい。反射型の液晶表示装置の場合、画像の表示を行なうために消費される電力を透過型よりも抑えることができる。透過型の液晶表示装置の場合、反射型と異なり暗いところでの画像の認識が容易になる。

#### 【0091】

なお本発明で用いる表示装置は、顔写真で人物を識別できる程度の解像度を有していることが必要である。よって、証明写真の代わりに用いるのならば、少なくともQVGA(320×240)程度の解像度が必要であると考えられる。

#### 【0092】

10

20

30

40

50

プリント配線基板への薄膜集積回路、表示装置の実装が完了したら、プリント配線基板を封止材で封止する。カードの封止には一般的に用いられている材料を使用することができ、例えばポリエステル、アクリル酸、ポリ酢酸ビニル、プロピレン、塩化ビニル、アクリロニトリルブタジエンスチレン樹脂、ポリエチレンテレフタレート等の高分子材料を用いることが可能である。なお封止の際、表示装置の画素部が露出するようにし、なおかつ接触型のICカードの場合は、画素部に加えて接続端子も露出するようにする。封止によって、図1(A)に示したような外観を有するICカードを形成することができる。

#### 【0093】

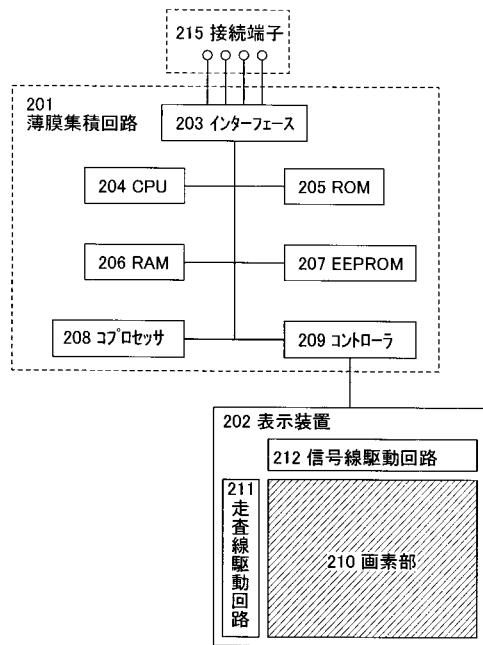

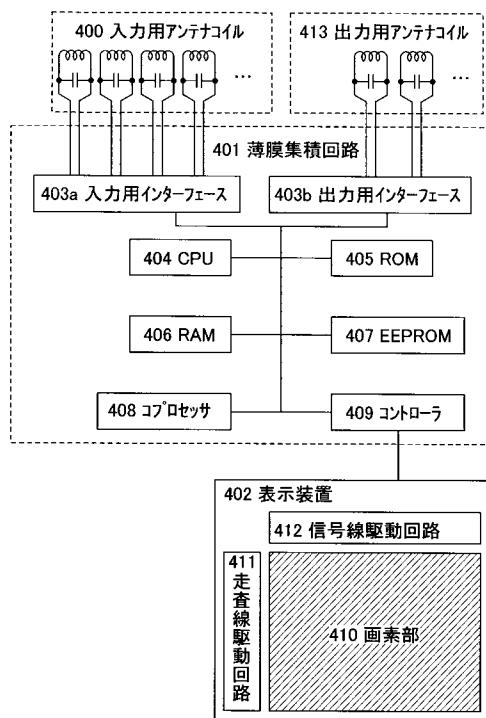

次に、薄膜集積回路と表示装置の構成の一形態について説明する。図7に、本発明のICカードに搭載された薄膜集積回路201と表示装置202のブロック図を示す。

10

#### 【0094】

薄膜集積回路201に設けられたインターフェース203を介して、プリント配線基板に設けられた接続端子215との間で、信号の送受信が行なわれる。またインターフェース203を介して接続端子215からの電源電圧の供給も行なわれる。

#### 【0095】

また図7に示す薄膜集積回路201には、CPU204、ROM205、RAM206、EEPROM207、コプロセッサ208、コントローラ209が設けられている。

20

#### 【0096】

CPU204によって、ICカードの全ての処理が制御されており、ROM205には、CPU204において用いられる各種プログラムが記憶されている。コプロセッサ208は、メインとなるCPU204の働きを助ける副プロセッサであり、RAM206は端末装置との間の通信時のバッファとして機能する他、データ処理時の作業エリアとしても用いられる。そしてEEPROM207は、信号として入力されたデータを定められたアドレスに記憶する。

#### 【0097】

なお、顔写真などの画像データを、書き換え可能な状態で記憶させるならばEEPROM207に記憶し、書き換えが不可能な状態で記憶させるならばROM205に記憶する。また別途画像データの記憶用のメモリを用意しておいても良い。

#### 【0098】

コントローラ209は、画像データを含む信号に表示装置202の仕様に合わせてデータ処理を施し、ビデオ信号として表示装置202に供給する。またコントローラ209は、接続端子215から入力された電源電圧や各種信号をもとに、Hsync信号、Vsync信号、クロック信号CLK、交流電圧(AC Cont)等を生成し、表示装置202に供給する。

30

#### 【0099】

表示装置202には、表示素子が各画素に設けられた画素部210と、前記画素部210に設けられた画素を選択する走査線駆動回路211と、選択された画素にビデオ信号を供給する信号線駆動回路212とが設けられている。

#### 【0100】

なお図7に示した薄膜集積回路201と表示装置202の構成は一例であり、本発明はこの構成に限定されない。表示装置202は画像を表示する機能を有していれば良く、アクティブ型であってもパッシブ型であっても良い。また薄膜集積回路201は表示装置202の駆動を制御する信号を表示装置202に供給することができる機能を有していれば良い。

40

#### 【0101】

このように顔写真のデータを、表示装置において表示させることで、印刷法を用いた場合に比べて顔写真のすり替えを困難にすることができる。さらに顔写真のデータをROM等の書き換えが不可のメモリに記憶することで、偽造されるのを防ぐことができ、ICカードのセキュリティをより確保することができる。また、無理にICカードを分解するとROMが壊れるような構成にしておけば、より確実に偽造を防止することができる。

50

**【0102】**

また表示装置に用いられる半導体膜や絶縁膜等に、シリアルナンバーを刻印しておけば、例えばROMに画像データを記憶させる前のICカードが、盗難等により第三者に不正に渡ったとしても、シリアルナンバーからその流通のルートをある程度割り出すことが可能である。この場合、復元不可能な程度に表示装置を分解しないと消せないような位置に、シリアルナンバーを刻印しておくとより効果的である。

**【0103】**

本発明のICカードは、薄膜集積回路がシリコンウェハで作製したものに比べて飛躍的に薄いので、ICカードの決められた容積の中により多くの薄膜集積回路を積層させて実装することができる。よってプリント配線基板上にレイアウトされる薄膜集積回路の面積を抑えつつ、回路規模やメモリ容量をより大きくすることができ、ICカードをより高機能化することができる。10

**【0104】**

また、半導体素子の作製工程における加熱処理の温度に対し、プラスチック基板は耐性が低く用いることが難しい。しかし本発明では、加熱処理を含む作製工程は温度に対する耐性が比較的高いガラス基板やシリコンウェハ等を用い、該作製工程が終了してから半導体素子をプラスチック基板上に移すことができるので、ガラス基板などに比べて薄いプラスチック基板を用いることができる。そして、ガラス基板の上に形成されている表示装置の厚さが、せいぜい2、3mm程度であるのに対し、本発明ではプラスチック基板を用いることで、表示装置の厚さを0.5mm程度、より望ましくは0.02mm程度と飛躍的に薄くすることができる。よって、ICカードへの搭載も可能となり、よりICカードを高機能化させることができる。20

**【0105】**

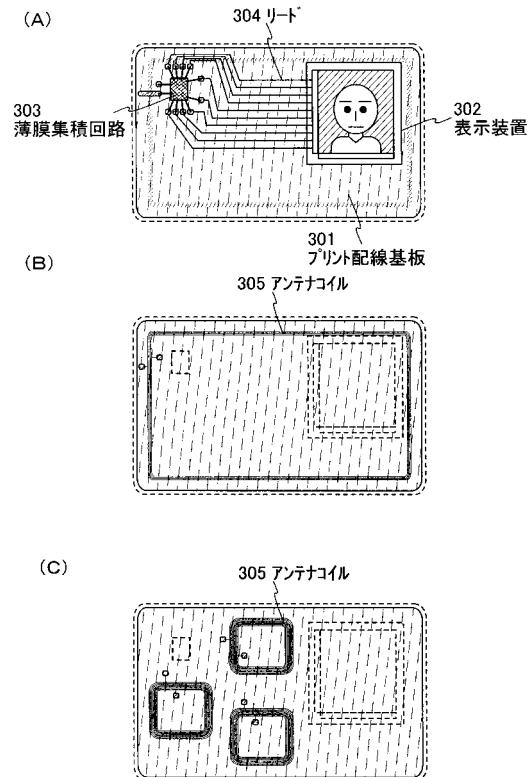

なお、本発明のICカードは接触型に限定されず、非接触型であっても良い。図8を用いて、非接触型の本発明のICカードの構成を示す。

**【0106】**

図8(A)に、非接触型のICカードに封止されているプリント配線基板301の構成を示す。図8(A)に示すように、プリント配線基板301には、表示装置302と薄膜集積回路303が実装されており、表示装置302と薄膜集積回路303はリード304を介して電気的に接続されている。なお、図8(A)では、プリント配線基板301の一方の面に薄膜集積回路303と表示装置302とが共に実装されているが、本発明はこれに限定されない。プリント配線基板301の一方の面に表示装置302が実装され、他方の面に薄膜集積回路303が実装されていても良い。30

**【0107】**

図8(B)に、図8(A)に示したプリント配線基板301の、裏側の構成を示す。図8(B)に示すように、プリント配線基板301にアンテナコイル305が実装されている。アンテナコイル305により、端末装置との間のデータの送受信を、電磁誘導を用いて非接触で行なうことができるので、接触型に比べてICカードが物理的な磨耗や損傷を受けにくい。40

**【0108】**

図8(B)では、アンテナコイル305が作り込まれたプリント配線基板301を用いる例を示しているが、別途作製しておいたアンテナコイルをプリント配線基板301に実装するようにしても良い。例えば銅線などをコイル状に巻き、100μm程度の厚さを有する2枚のプラスチックフィルムの間に該銅線を挟んでプレスしたものを、アンテナコイルとして用いることができる。

**【0109】**

また図8(B)では、1つのICカードにアンテナコイル305が1つだけ用いられているが、図8(C)に示すようにアンテナコイル305が複数用いられていても良い。

**【0110】**

次に、非接触型のICカードにおける、薄膜集積回路と表示装置の構成の一形態につい50

て説明する。図9に、本発明のICカードに搭載された薄膜集積回路401と表示装置402のブロック図を示す。

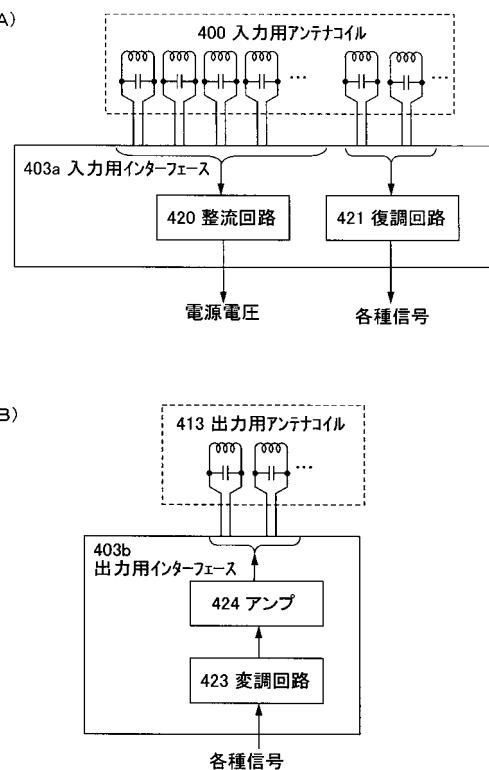

#### 【0111】

400は入力用アンテナコイルであり、413は出力用アンテナコイルである。また403aは入力用インターフェースであり、403bは出力用インターフェースである。なお各種アンテナコイルの数は、図9に示した数に限定されない。

#### 【0112】

図9に示す薄膜集積回路401には、図7の場合と同様に、CPU404、ROM405、RAM406、EEPROM407、コプロセッサ408、コントローラ409が設けられている。また表示装置402には、画素部410と、走査線駆動回路411と、信号線駆動回路412とが設けられている。

10

#### 【0113】

入力用アンテナコイル400によって、端末装置から入力された交流の電源電圧や各種信号は、入力用インターフェース403aにおいて波形整形されたり直流化されたりし、各種回路に供給される。また薄膜集積回路401から出力される出力信号は、出力用インターフェース403bにおいて変調され、出力用アンテナコイル413によって端末装置に送られる。

#### 【0114】

図10(A)に入力用インターフェース403aのより詳しい構成を示す。図10(A)に示す入力用インターフェース403aは、整流回路420と、復調回路421とが設けられている。入力用アンテナコイル400から入力された交流の電源電圧は、整流回路420において整流化され、直流の電源電圧として薄膜集積回路401内の各種回路に供給される。また、入力用アンテナコイル400から入力された交流の各種信号は、復調回路421において復調され、薄膜集積回路401内の各種回路に供給される。

20

#### 【0115】

図10(B)に出力用インターフェース403bのより詳しい構成を示す。図10(B)に示す出力用インターフェース403bは、変調回路423と、アンプ424とが設けられている。薄膜集積回路401内の各種回路から出力用インターフェース403bに入力された各種信号は、変調回路423において変調され、アンプ424において増幅または緩衝増幅された後、出力用アンテナコイル413から端末装置に送られる。

30

#### 【0116】

なお本実施の形態では、非接触型としてコイルアンテナを用いた例を示したが、非接触型のICカードはこれに限定されず、発光素子や光センサ等を用いて光でデータの送受信を行なうようにしても良い。

#### 【0117】

また本実施の形態では、アンテナコイルや接続端子を介してリーダライタから電源電圧が供給されている例について示したが、本発明はこれに限定されない。例えば、リチウム電池等の超薄型の電池を内蔵していても良いし、太陽電池を備えていても良い。

#### 【0118】

このように本発明では、シリコンウェハに比べて安価で大型のガラス基板を用いることができる所以、より低いコストで、なおかつ高いスループットで薄膜集積回路を大量生産することができ、生産コストを飛躍的に抑えることができる。また、基板を繰り返し使用することも可能なので、コストを削減することができる。

40

#### 【0119】

また本発明では飛躍的に薄い薄膜集積回路を形成することができるので、回路規模やメモリ容量のより大きい薄膜集積回路を、ICカードの限られた容積の中により多く搭載することができる。また表示装置を薄さ0.05mm以上1mm以下のICカードに搭載することができる程度の厚さで形成することができる。したがって、小型化、軽量化を妨げずにICカードの多機能を実現することができる。

#### 【0120】

10

20

30

40

50

またプリント配線基板の形状に合わせて薄膜集積回路や表示装置を貼り合わせることが可能なので、ICカードの形状の自由度が高まる。よって例えば、円柱状のピンなどに貼り付けられるような、曲面を有する形状にICカードを形成することも可能である。

#### 【実施例】

##### 【0121】

以下、本発明の実施例について説明する。

##### 【0122】

###### (実施例1)

本実施例では、接触型のICカードに搭載されているインターポーラと薄膜集積回路との電気的な接続の仕方について説明する。

10

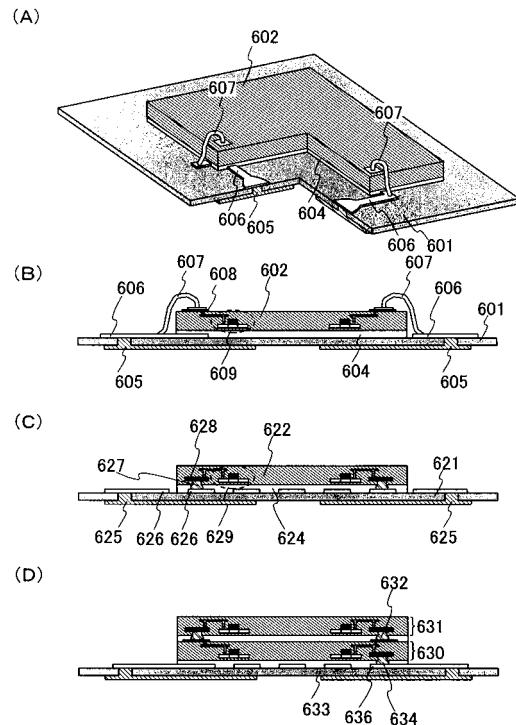

##### 【0123】

図11(A)に、ワイヤボンディング法でインターポーラに接続されている薄膜集積回路の、断面構造を表す斜視図を示す。601はインターポーラ、602は薄膜集積回路に相当する。薄膜集積回路602はインターポーラ601上に、マウント用の接着剤604によりマウントされている。

##### 【0124】

また図11(A)に示すインターポーラ601には、薄膜集積回路602がマウントされている面の裏の面側に、接続端子605が設けられている。そしてインターポーラ601に設けられたパッド606は、インターポーラ601に設けられたコンタクトホールを介して、接続端子605と電気的に接続している。

20

##### 【0125】

なお本実施例では、接続端子605とパッド606とがコンタクトホールを介して直接接続しているが、例えばインターポーラ601の内部において多層化された配線を設け、該配線を介して電気的に接続されるようにしても良い。

##### 【0126】

そして、図11(A)では、薄膜集積回路602とパッド606とが、ワイヤ607によって電気的に接続されている。図11(B)に、図11(A)に示したパッケージの断面図を示す。薄膜集積回路602には半導体素子609が設けられており、また薄膜集積回路602のインターポーラ601が設けられている側とは反対側に、薄膜集積回路用のパッド608が設けられている。パッド608は該半導体素子609と電気的に接続されている。そして薄膜集積回路用のパッド608は、インターポーラ601に設けられたパッド606と、ワイヤ607によって接続されている。

30

##### 【0127】

次に図11(C)に、フリップチップ法を用いてインターポーラに接続されている薄膜集積回路の断面図を示す。図11(C)に示すパッケージは、薄膜集積回路622にソルダーボール627が設けられている。ソルダーボール627は、薄膜集積回路622のインターポーラ621側に設けられており、同じく薄膜集積回路622に設けられたパッド628に接続されている。そして薄膜集積回路622に設けられている半導体素子629が、パッド628と接続されている。パッド628は、半導体素子629としてTFTを用いる場合、該TFTのゲート電極と同じ導電膜から形成されていても良い。

40

##### 【0128】

ソルダーボール627は、インターポーラ621に設けられたパッド626と接続されている。そして図11(C)では、ソルダーボール627間の隙間を埋めるように、アンダーフィル624が設けられている。またインターポーラ621の接続端子625は、インターポーラ621の薄膜集積回路622がマウントされている側とは反対の側に設けられている。そしてインターポーラ621に設けられたパッド626は、インターポーラ625に設けられたコンタクトホールを介して、接続端子625と電気的に接続している。

##### 【0129】

フリップチップ法の場合、接続すべきパッドの数が増加しても、ワイヤボンディング法に比べて、比較的パッド間のピッチを広く確保することができるので、端子数の多い薄膜

50

集積回路の接続に向いている。

【0130】

次に図11(D)に、フリップチップ法を用いて積層されている薄膜集積回路の断面図を示す。図11(D)では、インターポーラ633上に2つの薄膜集積回路630、631が積層されている。そしてインターポーラ633に設けられたパッド636と、薄膜集積回路630との電気的な接続は、ソルダーボール634を用いて行なわれている。また、薄膜集積回路630と薄膜集積回路631との電気的な接続も、ソルダーボール632を用いて行なわれている。

【0131】

なお図11(A)～図11(D)では、薄膜集積回路がペアチップとしてインターポーラにマウントされた例を示したが、本発明では薄膜集積回路がパッケージングされてからマウントされていても良い。この場合も、薄膜集積回路とインターポーラとの電気的な接続は、ソルダーボールを用いたものであっても、ワイヤを用いたものであっても、その組み合わせであっても良い。

10

【0132】

なおソルダーボールとパッドとの接続は、熱圧着や、超音波による振動を加えた熱圧着等様々な方法を用いることができる。なお、アンダーフィルが圧着後のソルダーボール間の隙間を埋めるようにし、接続部分の機械的強度や、パッケージで発生した熱の拡散などの効率を高めるようにしても良い。アンダーフィルは必ずしも用いる必要はないが、インターポーラまたはインターポーラと、薄膜集積回路との熱膨張係数のミスマッチから生ずる応力により、接続不良が起こるのを防ぐことができる。超音波を加えて圧着する場合、単に熱圧着する場合に比べて接続不良を抑えることができる。特に、薄膜集積回路と、インターポーラまたはインターポーラとの間の接続点が100より多い場合に有効である

20

【0133】

(実施例2)

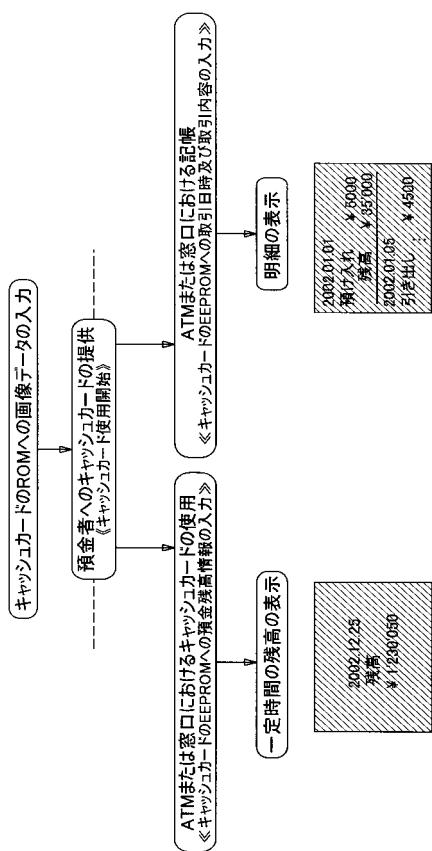

本実施例では、本発明のICカードを銀行のキャッシュカードとして用いる場合の、具体的な利用方法の一例について説明する。

【0134】

図12に示すように、まず銀行などの金融機関において口座を開設する際に、預金者の顔写真の画像データを、キャッシュカードの薄膜集積回路に設けられたROMに記憶する。ROMに顔写真のデータを記憶することで、顔写真のすり替などの偽造を防止することができる。そして該キャッシュカードを預金者に提供することで、キャッシュカードの使用が開始される。

30

【0135】

キャッシュカードはATM(自動現金預入払出機)または窓口における取引に用いられる。そして引き出し、預け入れ、振り込み等の取引が行なわれると、キャッシュカードの薄膜集積回路に設けられているEEPROMに、預金残高や、取引日時などの明細が記憶されるようになる。

【0136】

この取引の後、キャッシュカードの画素部において、預金残高や取引日時などの明細が表示されるようにし、一定時間経過後に該表示が消えるようにプログラムしておいても良い。そして、この取引の際、例えば自動振り込みによる引き落としなどの、キャッシュカードを用いずに行なわれた決済をすべてICカード内に記帳し、画素部においてこれを確認することができるようにしても良い。

40

【0137】

また、デビットカード(R)のように銀行のキャッシュカードを用い、現金のやり取りなしに口座から直接支払いを行なって決済する前に、決済を行なう際に用いる端末装置を介して銀行のホストコンピュータから残高の情報を引き出し、ICカードの画素部にその残高を表示するようにしても良い。端末装置において残高を表示すると使用している際に背後から第三者に盗み見られる怖れがあるが、ICカードの画素部に残高を表示すること

50

で、盗み見られることなく I C カードの使用者が残高を確認することができる。そして、販売店に設置された決済に用いる端末装置を用いて残高の確認をすることができるので、決済の前に残高を確認するためにわざわざ銀行の窓口や A T M などで残高照会や記帳を行なう煩雑さを解消することができる。

#### 【 0 1 3 8 】

なお本発明の I C カードはキャッシュカードに限定されない。本発明の I C カードを定期券やプリペイドカードとして用い、残金が画素部に表示されるようにしても良い。

#### 【 0 1 3 9 】

##### ( 実施例 3 )

本実施例では、1つの基板から複数の液晶表示装置を作製する場合について説明する。

10

#### 【 0 1 4 0 】

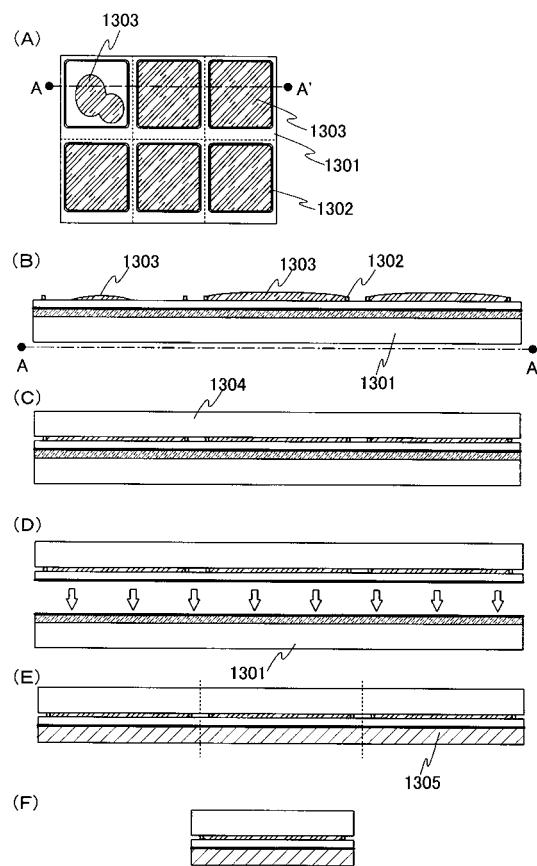

図 13 ( A ) に、第 1 の基板 1301 上に複数の液晶表示装置を同時に作製している場合の、基板の上面図を示す。配向膜が形成された第 1 の基板 1301 には、液晶が封入される領域を囲むようにレイアウトされたシール材 1302 が形成されている。そして、シール材 1302 で囲まれた領域に液晶 1303 が滴下されている。

#### 【 0 1 4 1 】

図 13 ( B ) に、図 13 ( A ) の破線 A - A' における断面図を示す。図 13 ( B ) に示すように、液晶 1303 はシール材 1302 で囲まれた領域に滴下されている。次に図 13 ( C ) に示すように、液晶 1303 をシール材 1302 で囲まれた領域に封入するよう、対向基板 1304 を貼り合わせて圧着する。

20

#### 【 0 1 4 2 】

対向基板の圧着後、図 13 ( D ) に示すように、第 1 の基板 1301 を剥離して除去した後、図 13 ( E ) に示すようにプラスチック基板 1305 を貼り合わせる。そして破線の位置でダイシングを行ない、図 13 ( F ) のように表示装置を互いに切り離す。

#### 【 0 1 4 3 】

なお本実施例では液晶表示装置の場合について述べたが、本発明はこれに限定されず、発光装置やその他の表示装置であっても複数同時に作製することが可能である。

#### 【 0 1 4 4 】

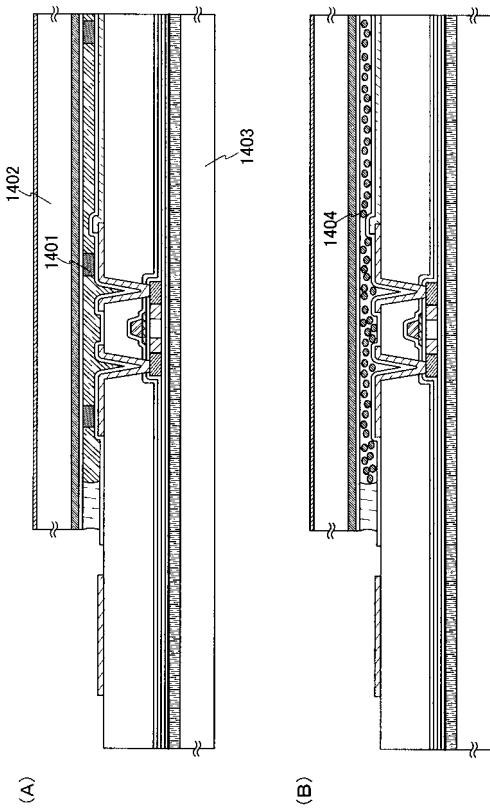

図 14 に、本実施例の液晶表示装置の断面図を示す。図 14 ( A ) に示す液晶表示装置は、画素に柱状のスペーサ 1401 が設けられており、該柱状のスペーサ 1401 によって対向基板 1402 と素子側の基板 1403 との間の密着性を高めている。これにより、第 1 の基板の剥離の際にシール材と重なる領域以外の半導体素子が第 1 の基板側に残留してしまうのを防ぐことができる。

30

#### 【 0 1 4 5 】

また図 14 ( B ) に、ネマチック液晶、スマクチック液晶、強誘電性液晶或いはそれらが高分子樹脂中に含有された P D L C ( ポリマー分散型液晶 ) を用いた液晶表示装置の断面図を示す。P D L C 1404 を用いることで、対向基板 1402 と素子側の基板 1403 との間の密着性が高められ、第 1 の基板の剥離の際にシール材と重なる領域以外の半導体素子が第 1 の基板側に残留してしまうのを防ぐことができる。

#### 【 図面の簡単な説明 】

40

#### 【 0 1 4 6 】

【 図 1 】 本発明の I C カードの外観図と、内部の構造を示す図。

【 図 2 】 接続端子と薄膜集積回路の拡大図と、表示装置とプリント配線基板との接続部分の拡大図。

【 図 3 】 半導体素子の作製方法を示す図。

【 図 4 】 半導体素子の作製方法を示す図。

【 図 5 】 半導体素子の作製方法を示す図。

【 図 6 】 液晶表示装置の断面図。

【 図 7 】 薄膜集積回路と表示装置のブロック図。

【 図 8 】 本発明の I C カードの内部の構造を示す図。

50

【図9】薄膜集積回路と表示装置のブロック図。

【図10】入出力用インターフェースの構造を示すブロック図。

【図11】薄膜集積回路の構造を示す断面図。

【図12】本発明のICカードの利用方法を示す図。

【図13】本発明の表示装置の作製方法を示す図。

【図14】液晶表示装置の断面図。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(72)発明者 秋葉 麻衣

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 村田 充裕

(56)参考文献 特開平11-020360(JP,A)

特開平11-120312(JP,A)

特開平09-311922(JP,A)

特開2000-020665(JP,A)

特開平07-146922(JP,A)

特開2001-100684(JP,A)

特表2000-514937(JP,A)

特開2001-306967(JP,A)

(58)調査した分野(Int.Cl., DB名)

G06K 19/00 - 19/08

B42D 15/10

H01L 27/12