(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6498043号

(P6498043)

(45) 発行日 平成31年4月10日(2019.4.10)

(24) 登録日 平成31年3月22日(2019.3.22)

(51) Int.Cl.

G06F 11/07 (2006.01)

F 1

|      |       |         |

|------|-------|---------|

| G06F | 11/07 | 1 7 2   |

| G06F | 11/07 | 1 5 7   |

| G06F | 11/07 | 1 4 0 J |

| G06F | 11/07 | 1 4 0 P |

請求項の数 12 (全 13 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2015-110801 (P2015-110801)  |

| (22) 出願日  | 平成27年5月29日 (2015.5.29)        |

| (65) 公開番号 | 特開2016-224730 (P2016-224730A) |

| (43) 公開日  | 平成28年12月28日 (2016.12.28)      |

| 審査請求日     | 平成30年5月25日 (2018.5.25)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のコントロールチップが縦列接続された電子機器であって、

第1のコントロールチップの下流側に第2のコントロールチップが配置され、且つ、前記第2のコントロールチップの下流側に第3のコントロールチップが配置され、

前記第2のコントロールチップは、

ウォッチドッグタイマと、

下流側に位置する前記第3のコントロールチップのウォッチドッグタイマが発生する割り込み信号と、自チップが有するウォッチドックタイマが発生する割り込み信号との論理和信号を、前記自チップが有するウォッチドッグタイマから割り込み信号として、上流側に位置する前記第1のコントロールチップに供給するための伝達部と

を有することを特徴とする電子機器。

## 【請求項 2】

前記第2のコントロールチップは、自チップのウォッチドッグタイマが割り込み信号を発生した場合、自チップと下流側に位置する前記第3のコントロールチップをリセットすることを特徴とする請求項1に記載の電子機器。

## 【請求項 3】

前記第2のコントロールチップは、自チップのウォッチドッグタイマが割り込み信号を発生した場合、予め設定された時間が経過してから、自チップをリセットするリセット制御部を有することを特徴とする請求項1又は2に記載の電子機器。

**【請求項 4】**

前記第2のコントロールチップは、下流側の前記第3のコントロールチップから割り込み信号を受信した場合、自チップのCPUに割り込み信号の入力を通知する通知部を有することを特徴とする請求項1乃至3のいずれか1項に記載の電子機器。

**【請求項 5】**

前記第2のコントロールチップは、互いに通信するための通信部を有することを特徴とする請求項1乃至4のいずれか1項に記載の電子機器。

**【請求項 6】**

前記第1のコントロールチップは、外部装置からの印刷データの受信処理を行い、下流に位置する前記第2のコントロールチップと前記第3のコントロールチップの少なくとも1つは、前記通信部を介して受信した印刷データに基づく印刷を行うヘッドの制御を行うことを特徴とする請求項5に記載の電子機器。10

**【請求項 7】**

前記第2のコントロールチップは、用紙の搬送に関する制御を行い、前記第3のコントロールチップは、前記ヘッドを走査するキャリッジの制御を行うことを特徴とする請求項6に記載の電子機器。

**【請求項 8】**

前記第1のコントロールチップは、下流側の前記第2のコントロールチップから割り込み信号を受信した場合、前記ヘッド、モーターの駆動のための電力供給の停止を行うことを特徴とする請求項6または7に記載の電子機器。20

**【請求項 9】**

前記第1のコントロールチップは、前記複数のコントロールチップの最上流に位置することを特徴とする請求項1乃至8のいずれか1項に記載の電子機器。

**【請求項 10】**

前記第1のコントロールチップと前記第3のコントロールチップも、前記ウォッチドッグタイマと前記伝達部とを有することを特徴とする請求項1乃至9のいずれか1項に記載の電子機器。

**【請求項 11】**

前記第1のコントロールチップと前記第2のコントロールチップと前記第3のコントロールチップは、同一の構成であることを特徴とする請求項1乃至10のいずれか1項に記載の電子機器。30

**【請求項 12】**

前記電子機器は、用紙に印刷を行う印刷装置であることを特徴とする請求項1乃至11のいずれか1項に記載の電子機器。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、複数のコントロールチップを縦列接続した電子機器に関するものである。

**【背景技術】****【0002】**

ワードプロセッサ、パーソナルコンピュータ、ファクシミリ等に於ける情報出力装置として、所望される文字や画像等の情報を用紙やフィルム等シート状の記録媒体に記録を行うプリンタが広く使用されている。40

**【0003】**

プリンタの記録方式としては様々な方式が知られている。中でも、用紙等の記録媒体に非接触記録が可能である、カラー化が容易である、静肅性に富む等の理由から、インクジェット方式が近年特に注目されている。また、その構成としては、記録命令に応じてインクを吐出する記録ヘッドを装着し、用紙等の記録媒体の送り方向と交差する方向に往復走査しながら記録を行うシリアル型インクジェット記録方式が、安価で小型化が容易などの点から一般的に広く用いられている。50

**【0004】**

上記のようなインクジェット記録装置では、インク滴を吐出するノズルの集積密度をあげながら、1ドットあたりのインク吐出量を小さくすることで、更なる高解像度画像の記録を実現する。また、より高い画質を得るために、基本となる4色インク（シアン、マゼンタ、イエロー、ブラック）の他に、これらの染料濃度を低くした淡インク、更にはレッド、グリーン、ブルー等の特色インクを同時に記録する等の多彩な技術が展開されている。

**【0005】**

また、この高画質化が進むと記録スピードの低下が懸念される。しかし、係る問題は、記録素子の多数化や駆動周波数の向上、記録ヘッドの往復の走査時に記録を行う両方向記録の様な記録技術の採用、記録用紙の搬送速度の高速化により良好な結果が得られるようになってきている。10

**【0006】**

また、インクジェット記録装置における更なる高速化を目的として、複数のコントローラチップ（以下、単にチップ）を接続してシステムを構成し、さまざまな処理や、端子の機能を分散させるケースが増えてきている。

**【0007】**

複数のチップを接続して構成されたシステムについては、それぞれの機能に特化したチップを用意して構成する方法もあるが、同一チップを用いて前記のシステムを構成できた方が、開発負荷的にも、費用的にも望ましいケースもある。また、システムを複数のチップで構成する場合、それぞれのチップで発生しうるエラー状態をどのように共有し、管理するかが重要となってくる。特にシステムの制御を司るCPUが適切な制御を行えなくなつた場合、記録ヘッドの制御や、モーター制御が正常に行えなくなり、本体の故障につながる可能性がある。こういった状態を回避するために、一般的にはウォッチドックタイマを用いて、CPUを監視し、問題が生じた場合に自動的にリセットをかける監視方法が一般的によく使われている。20

**【0008】**

しかしながら、システムが複数のチップで構成される場合、チップ内のCPUが適切な制御を行えなくなった場合、その状態を、互いのチップでどのように共有して、システム全体をどのように安全に止めるか重要な問題である。こういった状態を想定して、例えば、特許文献1では、一つのウォッチドックを用いて、少なくとも2つのマイクロコントローラを監視する方法が開示されている。ウォッチドックは、第1のマイクロコントローラに割り当てられ、所定期間の時間間隔内での第1のマイクロコントローラのメッセージの通知を監視する。第1のマイクロコントローラによりウォッチドックに通知されたメッセージは、第1のマイクロコントローラと、第1のマイクロコントローラと接続された第2のマイクロコントローラと、の間の通信の結果として形成される寄与を含む。前記寄与に基づいて、ウォッチドックは、第2のマイクロコントローラが正しく動作しているかを検査する手法が開示されている。30

**【先行技術文献】****【特許文献】****【0009】**

【特許文献1】特表2013-541089号公報

**【発明の概要】****【発明が解決しようとする課題】****【0010】**

しかしながら、特許文献1においては、複数のコントローラを一つのウォッチドックタイマにより監視する構成が可能ではあるが、第2のコントローラが正常に動作しているかどうかは、第1のコントローラとの通信によってしか判別できない。このため、仮に第1のコントローラにエラーが発生した場合に、第2のコントローラとの通信が出来なくなる事で、第2のコントローラが制御不能となってしまう可能性がある。50

**【0011】**

何らかのエラーが発生したときにシステム全体で共有することができれば、そのシステムは、エラーに応じた適切な処理を行うことができる。例えば、通信が出来ない理由が、静電気等の影響で通信が一瞬途切れただけの状態であれば、リトライ動作などを行って再度通信の確立を行う様にすれば良い。一方、ウォッチドックタイマが動作しコントローラのリセットが発生した事で通信ができない状態になってしまっているのであれば、大きな電力を消費するモーター、ヘッド等への電力供給を早急に停止させ、システム全体を安全な状態にすることが求められる。

**【0012】**

そのため、複数個のコントローラを用いて構成されたシステムにおいては、特定のコントローラで何らかの原因でエラーが発生し、ウォッチドックタイマが動作した場合、その事をシステム全体で適切に共有するための技術が求められる。10

**【課題を解決するための手段】****【0013】**

この課題を解決するため、例えば本発明の電子機器は以下の構成を備える。すなわち、複数のコントロールチップが縦列接続された電子機器であって、

第1のコントロールチップの下流側に第2のコントロールチップが配置され、且つ、前記第2のコントロールチップの下流側に第3のコントロールチップが配置され、

前記第2のコントロールチップは、

ウォッチドッグタイマと、20

下流側に位置する前記第3のコントロールチップのウォッチドッグタイマが発生する割り込み信号と、自チップが有するウォッチドックタイマが発生する割り込み信号との論理和信号を、前記自チップが有するウォッチドッグタイマから割り込み信号として、上流側に位置する前記第1のコントロールチップに供給するための伝達部とを有する。

**【発明の効果】****【0014】**

本発明によれば、複数のコントローラチップを縦列接続した電子機器において、いずれかのチップで発生したエラー状態となった場合であっても、少なくともそのエラーとなつたチップより上流側のチップ間では、エラーチップの存在を共有する事が可能となる。

**【図面の簡単な説明】****【0015】**

【図1】インクジェット記録装置の主要機構部分を示す図。

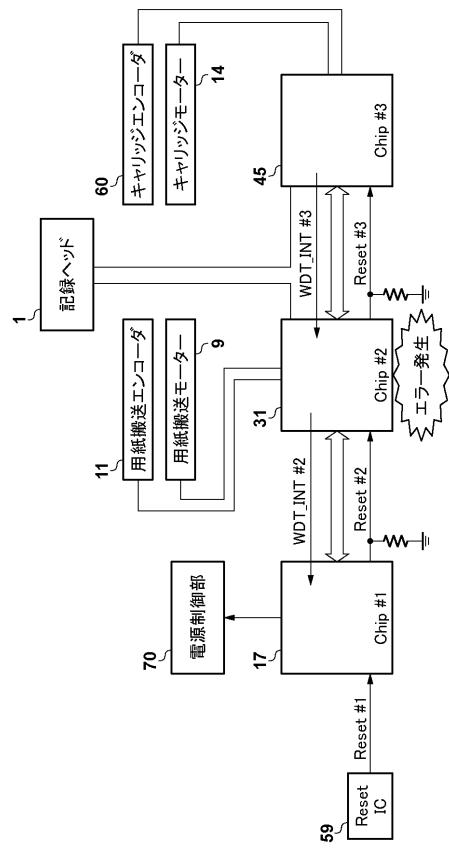

【図2】複数チップ接続構成の関係を示す図。

【図3】コントロールチップのWDT\_INT切り替え部周辺を示す図。

【図4】ウォッチドック割り込み信号とリセット信号との関係を示す図。

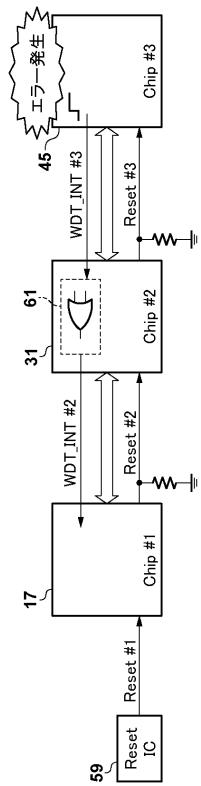

【図5】3つ目のコントロールチップでエラーが発生した場合の信号伝達に係る構成を示す図。

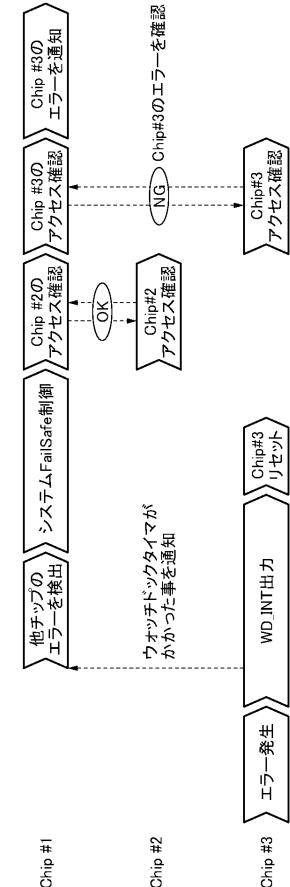

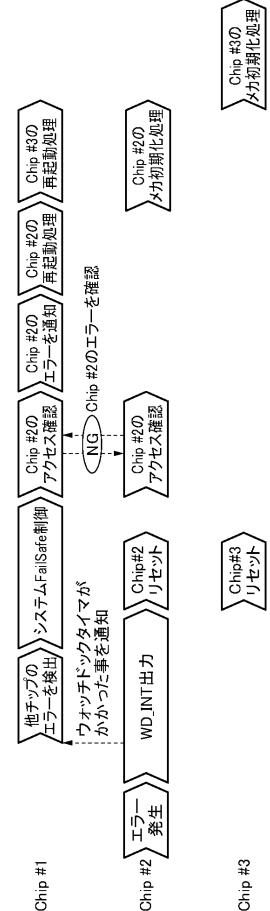

【図6】3つ目のコントロールチップでエラーが発生した場合の処理の流れを示す図。

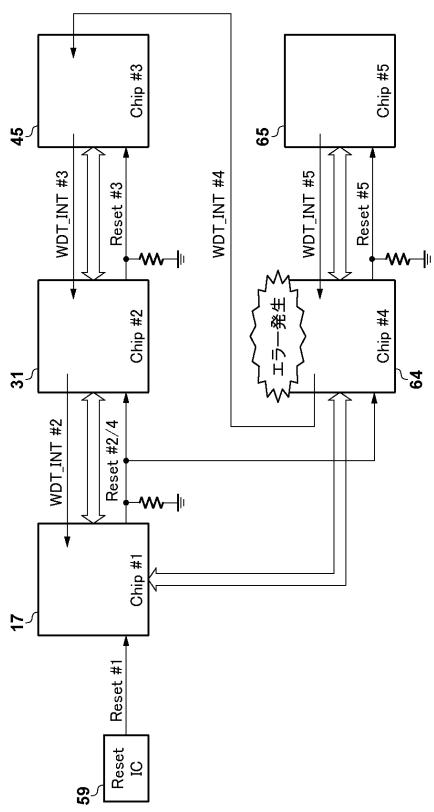

【図7】第2の実施形態におけるシステムの構成を示す図。

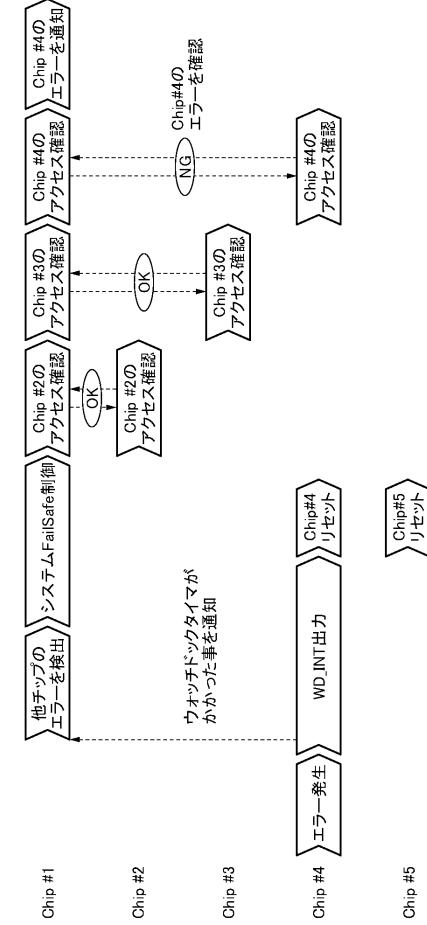

【図8】第2の実施形態におけるエラー発生時の処理の流れを示す図。40

【図9】第3の実施形態におけるシステム構成を示す図。

【図10】第3の実施形態におけるエラー発生時の処理の流れを示す図。

**【発明を実施するための形態】****【0016】**

以下、添付図面に従って本発明に係る実施形態を詳細に説明する。

**【0017】**

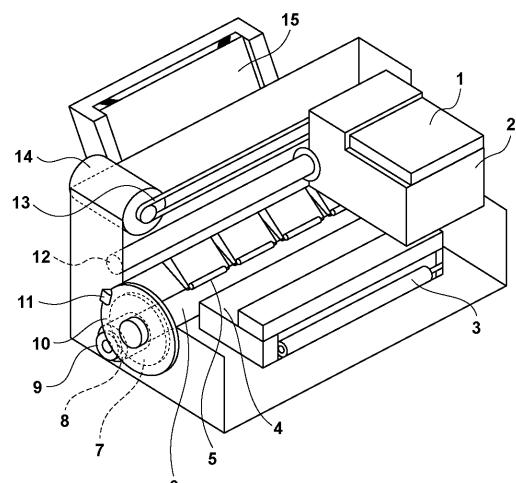

図1は、実施形態が適用する電子機器としての記録装置の主要な構成を示す図である。図1において、符号1は、インクを吐出する複数のノズルからなるノズル列を有する記録ヘッドである。符号2は、記録ヘッド1を搭載し、記録媒体の搬送方向と直交する走査方向に記録ヘッド1を走査するキャリッジである。符号3は記録された記録媒体を記録装置

の外へ搬送する時に用いる排紙ローラ、符号4は記録面の底面に位置するプラテンである。符号5は、記録用紙などの記録媒体15を押さえるために用いられる紙押さえローラである。符号6は記録紙を搬送する用紙搬送ローラである。符号7は用紙搬送ギア、符号8は用紙搬送ギア7と用紙搬送モーターギア9を介して用紙搬送ローラ6を駆動する用紙搬送モーターである。符号10は用紙搬送モーター8に同期して回転するエンコーダフィルムであり、用紙搬送エンコーダ11を用いてエンコーダフィルムに記されたスリットの検知を行い、検知信号を発生する。この信号は、用紙搬送モーターの位置の検出と、記録タイミングの生成に使用される。符号12はキャリッジ2を固定するシャフト、符号13はキャリッジ2をその一部に固定し、案内するためのベルト、符号14はベルト13を回転させるためのモーターである。

10

#### 【0018】

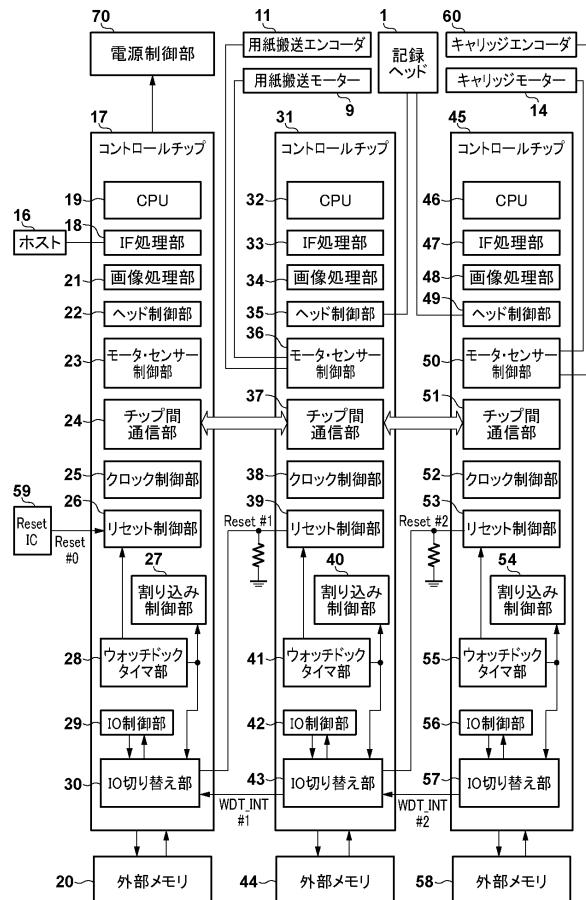

図2は、実施形態における記録装置の基板上に実装させた制御部のブロック構成図である。制御部は、複数個（図示では符号17, 31, 45の3つ）の同一構成のコントロールチップ（以下、単にチップ）を縦列に接続したマルチチップ構成を有する。

#### 【0019】

チップ17は、プログラムに従って処理を実行するCPU19、外部装置との通信を行うためのI/F処理部18、描画処理や2値化処理等を行う画像処理部21、印刷装置の記録ヘッドの駆動を制御するためのヘッド制御部22を有する。また、チップ17は、記録ヘッドや記録媒体を搬送するモーターの制御、並びに、モーターの回転速度や位置を検出するモーター・センサー制御部23、他のチップとの通信を行うためのチップ間通信部24を有する。また、チップ17は、各回路への必要な周波数のクロック信号を発生するクロック制御部25、CPU19へのリセット信号の供給を制御するリセット制御部26、ウォッチドッグタイマ部28、割り込み制御部27を有する。また、チップ17は、IO切り替え部30、及びIO切り替え部30を制御するIO制御部29を有する。

20

#### 【0020】

また、チップ17には、CPU19が実行するプログラムを格納したROM及びワークエリアとして使用するRAMで構成される外部メモリ20が接続されている。また、チップ17には、チップ31やチップ45への電力供給や、記録ヘッド1の駆動や、記録ヘッド1並びに記録媒体15の搬送を行うモーター等の、大きな電力を消費する部分への電力供給を制御するための電源制御部70が接続されている。そして、チップ17には、印刷データの発生源であるPC等のホスト16が接続されている。接続形態は、ネットワークインターフェース、USBインターフェース等があり、その種類は問わない。また、チップ17には、そのチップ17をリセットするためのリセットIC59が接続されている。

30

#### 【0021】

以上がチップ17の構成とそれに接続された構成要素の説明である。チップ31、チップ45は、チップ17と同じである。従って、図示の符号32乃至43、46乃至57は、符号18乃至30と同じであるので説明は省略する。ただし、チップ31、45には図示のごとく、用紙搬送エンコーダ11、用紙搬送モーター9、記録ヘッド1、キャリッジエンコーダ60、キャリッジモーター14が接続されている。また、外部メモリ44, 58を構成するROMには、それぞれのチップに特化したプログラムが格納されることになる。

40

#### 【0022】

ホスト16と接続されるチップ17のリセットは上記のようにリセットIC59からの信号によりリセットされる。そして、チップ17に接続される2番目、3番目のチップ31, 45のチップリセットは、それぞれの前段（上流側）のチップにより制御される。

#### 【0023】

それぞれのチップは、チップ間通信部24、37、51によって接続され各チップ間で制御コマンドのやり取りや、データ転送が行われる。

#### 【0024】

また、このチップ17は、I/F処理部18を介して、ホスト16から送信された制御コ

50

マンドや記録データの受信処理を行う。そして、チップ17のCPU19は、ホスト16から受信された制御コマンドを解析し、この制御コマンドに従って記録装置の制御を行う。尚、外部メモリ20には、上記CPU19が動作するためのプログラムや記録制御回路部23の制御に必要な各種テーブルなどが格納されている。また、チップ31や、チップ45にもCPU32、46が内蔵され、それぞれのチップで必要なプログラムや各種テーブル等が外部メモリ44、58に格納されている。

#### 【0025】

受信された記録データはチップ間通信部24、37、51を通じて、後段（下流側）のチップ31やチップ45に送られ、記録方法に応じた各種の画像処理が施された上で外部メモリ44、58に一旦格納される。外部メモリ44、58には、少なくとも1走査分の記録ヘッド1を駆動するための記録データが格納されている。さらに、マルチバス記録を行うため、又は記録データを2つのノズルに分配して記録するためなどに用いられる画像マスク等も格納されている。10

#### 【0026】

記録ヘッドに接続されているチップ31、46内のCPU32、46は、チップ17からのデータに基づき、印刷処理を実行する。具体的には、CPU32、46は、外部メモリ44、58のRAMに、印刷用の画像データの生成、格納を行う。また、用紙搬送エンコーダ11やキャリッジエンコーダ60からの信号を基にモーター・センサー制御部36、50は記録タイミング信号を生成する。この記録タイミング信号の発生をトリガに、CPU32、46は、外部メモリ44、58に格納された記録データを、ヘッド制御部35、49を介して記録ヘッド1へ送信することで印刷処理を行う。20

#### 【0027】

##### [第1の実施形態]

以下、図2及び図3に従って第1の実施形態の詳細な制御方法について説明する。

#### 【0028】

第1の実施形態では、電子機器として、3チップを縦列接続するシステム（印刷装置）を例として示す。3チップを用いたシステムを構成する事で、メモリ帯域、画像処理機能、端子機能を分散して処理させる事が可能となり、システム全体の処理能力の向上と、使用可能なI/O数を増加させる事が可能となる。

#### 【0029】

ホスト16と接続されている1番目のチップ17は、主にI/F処理や電源制御等のシステム全体を管理するメインチップとしての役割を果たし、そのリセットについては外部ICによるリセット制御が行われる。また、2番目以降のチップ31、及び45については、主にモーター・センサー制御、記録ヘッドの駆動制御等を行うサブチップとしての役割を果たす。また、チップ31、及び45については、自チップの前段に位置するチップの汎用のI/Oを用いてリセット制御信号が行われる。また、リセット制御を行う端子は汎用のI/Oの為、リセット状態では入力状態で、システムが起動後に出力に切り替えて使用される。この為、端子を出力に切り替えて制御できる状態にするまでの論理を固定しておく必要があり、外部抵抗を用意して固定する。また、固定する論理は、チップがリセット状態の時に、リセット信号が接続されている対向チップがリセットされる論理とする。こうする事で、例えば、2番目のチップ31がリセットされた場合、2番目のチップでリセット制御している3番目のチップ45も自動的にリセットされる構成とする事が可能となる。

#### 【0030】

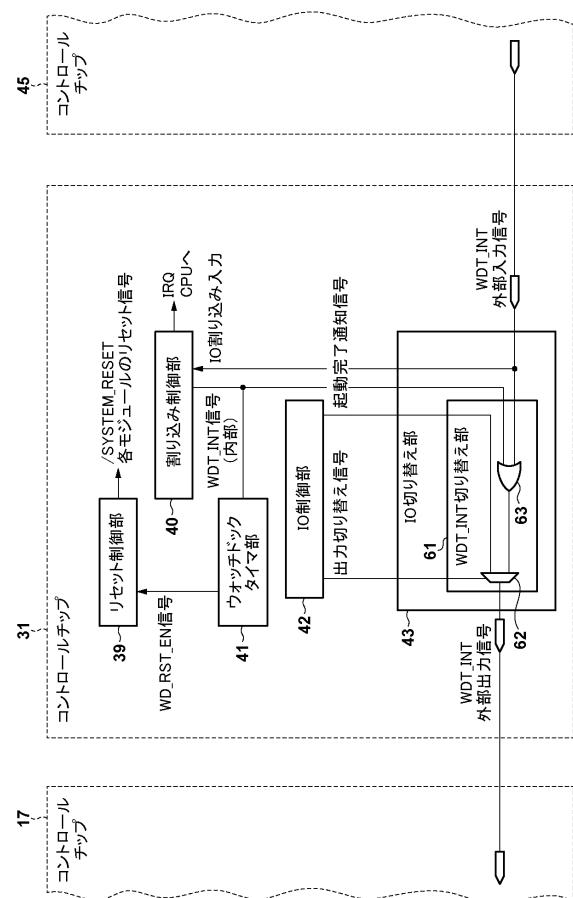

図3に、チップ31のウォッチドックタイマ部41の周囲の構成と、チップ17、45との接続例を示す。ウォッチドックタイマ部41は、ウォッチドックタイマ機能によってエラーを検知した場合、WDT\_INT信号を出力する機能を有する。WDT\_INT切り替え部61は、論理回路63を有する。この論理回路63は、自チップのウォッチドックタイマ部41で生成されるWDT\_INT信号と、後段につながっているチップ45から出力されてコントロールチップ31へ入力されるWDT\_INT外部入力信号とを論理和の演算するORゲートを有

10

20

30

40

50

する。そして、論理回路 6 3 は、その論理和信号を、コントローラチップ 1 7 へ WDT\_INT 外部出力信号として出力する。このように、論理回路 6 3 により、下段に位置するコントローラチップで発生したウォッチドックタイマの割り込み信号 WDT\_INT がファームウェアの介在なく先頭（最上流）のコントローラチップまで供給することが可能になる。つまり、WDT\_INT 切り替え部 6 1 は、自チップと下流側のチップそれぞれのウォッチドックタイマからの割り込み信号を上流側のチップに伝達する伝達部として機能する。また、割り込み制御部 4 0 は、後段のコントローラチップから WDT\_INT 信号を受信した場合、その信号を受信したことを示すことを自チップの CPU に通知する通知部として機能する。具体的には、後段のコントローラチップから WDT\_INT 信号を受信した場合、割り込み制御部 4 0 は割り込み信号を CPU に供給する。

10

#### 【 0 0 3 1 】

また、この対向チップへ出力される WDT\_INT 信号は、I0 制御部 4 2 で生成される起動完了通知信号と WDT\_INT 切り替え部 6 1 のセレクタ 6 2 において、切り替えて I/O を共有する。各コントロールチップの電源が投入され起動が完了した場合は、この信号を CPU から制御する事によって、各コントロールチップの起動状態を示す信号として使用するが、起動完了後にはウォッチドックタイマの割り込み信号を伝達する信号に切り換える。この為、本実施形態における機能を実現する為に、新たに別の信号を用意する事無く、他のコントロールチップのエラー状態を共有する事が可能となる。

#### 【 0 0 3 2 】

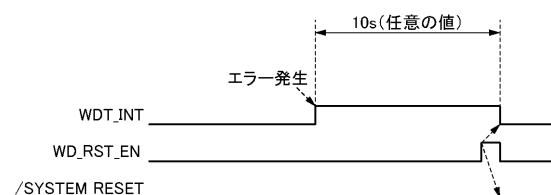

図 4 にウォッチドックタイマの機能によってエラーを検出し、実際にシステムリセットがされるまでのタイミングチャートを示す。実際にエラーを検出すると、ウォッチドックタイマ部 4 1 から出力される WDT\_INT 信号がアサートされる。実施形態では、この段階ですぐにシステムのリセットがかかる訳ではない。つまり、WDT\_INT 信号がアサートされてからリセット制御部 3 9 に対して各モジュールのリセット処理を実行させる為の制御信号 WD\_RST\_EN 信号がアサートされるまで、所定の時間がかかるようにした。この時間は、外部から適宜設定できるようにしても良い。そして、この時間を利用し、エラーが発生したチップよりも前段に位置するチップ間で、エラー発生を共有する。図 4 では一例として、エラーが発生して WDT\_INT 信号がアサート後、10 秒後にリセットされるタイミングチャートを記載している。この時間があれば、外部に出力される WDT\_INT を利用して対向チップとのエラー状態の共有は十分に実施する事ができる。

20

#### 【 0 0 3 3 】

以下、具体的な構成図を示した図 5 と、処理の流れを示した図 6 に従って、3 チップ目のチップ 4 5 においてエラーが発生し、ウォッチドックタイマが動作した場合の例を説明する。3 チップ目のチップ 4 5 でウォッチドックタイマが動作すると、WDT\_INT#3 信号が、2 チップ目のチップ 3 1 の WDT\_INT 切り替え部 6 1 にある論理回路を通過して、1 番目のチップ 1 7 へ到達する。この結果、システム全体を管理している 1 番目のチップ 1 7 は、2 番目以降のチップにエラーが発生していること認識可能となる。また、並行して 3 番目のチップ 4 5 は、適当な時間が経過（実施形態では 10 秒）してから、ウォッチドック機能によってチップ全体がリセットされる。1 番目のチップ 1 7 は、後段チップからのウォッチドックの割り込み信号 WDT\_INT 信号を受信したことに応じて、電源制御部 7 0 を制御し、大きな電力を消費するモーターや、ヘッド等への電力供給を停止させる。この電力供給の制御処理を開始するタイミングは、3 番目のチップ 4 5 がリセットされるタイミングより十分に早い。つまり、3 番目チップ 4 5 がリセットされる以前に、システム全体を安全な状態に移行させることが可能となる。そして、チップ 1 7 は、係る制御を行った後、後段チップへ順次アクセスを試していく事で、どのチップでエラーが発生したかを把握する事ができるようになる。また、全チップが正常になったことを受けて、チップ 1 7 は電源制御部 7 0 を制御し、電力供給を行い、再び印刷可能状態に復帰する。

30

#### 【 0 0 3 4 】

##### [ 第 2 の実施形態 ]

第 2 の実施形態では、最上流のチップに並列に 2 チップが接続され、且つ、それぞれの

40

50

チップに更に縦列にチップが接続されている構成を例として示す。また、第2の実施形態では、4チップ目のチップにおいてエラーが発生し、ウォッチドックタイマが動作した場合を例として示す。記録装置の具体的な構成を図7に示す。以下、処理の流れを示した図8に従って説明する。

#### 【0035】

今、4チップ目のチップ64でウォッチドックタイマによるエラーを検知すると、WDT\_INT#4信号が、チップ45、チップ31のWDT\_INT切り替え部にある論理回路を通過して1番目のチップ17へ到達する。信号が到達後、システム全体を管理している1番目のチップ17は、2番目以降のチップでエラーが発生していること認識する。また、並行してチップ64はウォッチドック機能によってチップ全体がリセットされる。合わせて、チップ64によってリセットの制御を行っているチップ65もリセットされ、チップ64及びチップ65は安全な状態に変化させる事ができる。1番目のチップ17は、第1の実施形態と同様に後段チップからのウォッチドックの割り込み信号WDT\_INT信号を受信したことにより、電源制御部70を制御し、大きな電力を消費するモーターや、ヘッド等への電力供給を停止させる。この結果、システム全体を安全な状態に移行させることができる。この後、チップ17は、後段チップへ順次アクセスを試していく事で、どのチップでエラーが発生したかを把握する事ができる。

#### 【0036】

本第2の実施形態においては、チップ45までのアクセスは確認できるが、チップ64へのアクセスは、チップ64にリセットが入り初期状態となっている為、正しくアクセスする事が出来ず、チップ64でエラーが発生した事を確認する事ができる。

#### 【0037】

##### [第3の実施形態]

第3の実施形態では、3チップが縦列に接続されているシステムにおいて、2チップ目においてウォッチドックタイマが動作した場合を例として示す。具体的な構成図は、図9に示す。本第3の実施形態では、記録動作に必要なモーター・エンコーダ 制御、及びヘッド制御をチップ31、チップ45で分散して処理させる場合を例として示している。こうする事で、システム全体の処理を分散化させる事が可能となり、より高速な記録動作が可能となる。

#### 【0038】

通常、記録動作時は、チップ17に入力されるデータに基づいて、記録装置内のモーター・エンコーダ、ヘッド制御等を動作させ記録用紙へ記録を行う。しかしながら、記録動作の途中で、エラーが発生し、ウォッチドックタイマが動作した場合、用紙を送っている用紙搬送モーター9や、記録ヘッドの動作制御を行っているキャリッジモーター14が止まってしまうことになる。また、それぞれのモーターの位置検出に使用されるエンコーダも止まってしまう。その為、記録途中の用紙も意図しない状態で止まり、次に復帰した時に問題となる場合がある。

#### 【0039】

システム全体をコントロールしているチップ17でウォッチドックタイマが動作した場合は、システム全体に対して再起動をかける事が可能となり、メカの初期化も行われ、記録途中の用紙は正常に処理される。しかしながら、例えば、本第3の実施形態の様に2チップ目のチップ31でエラーが発生し、ウォッチドックタイマが動作した場合は、その後の再起動処理の手順を正しく行う必要がある。具体的には、途中で止まっている記録ヘッドの退避や、記録用紙を強制的に排出する処理が必要となる。

#### 【0040】

以下、処理の流れを示した図10に従って説明する。2チップ目のチップ31でウォッチドックタイマによるエラーを検知すると、WDT\_INT#2信号が、1チップ目17へ出力される。その後、システム全体を管理している1番目のチップ17は、2番目以降のチップでエラーが発生していること認識する。また、並行してチップ31は所定時間経過後にウォッチドック機能によってチップ全体がリセットされる。合わせて、チップ31によって

10

20

30

40

50

リセットの制御を行っているチップ45もリセットされ、チップ31及びチップ45は安全な状態に変化させる事ができる。チップ17は、第1の実施形態と同様である。つまり、チップ17は、後段のチップからのウォッチドッグの割り込み信号WDT\_INT信号を受信後、電源制御部70を制御し、まずは大きな電力を消費するモーターや、ヘッド等への電力供給を一旦停止させ、システム全体を安全な状態に移行させる。そして、チップ17は、後段チップへ順次アクセスを試し2番目のチップ31でエラーが発生している事を把握する。

#### 【0041】

チップ17は、2番目のチップ31でエラーを通知した後、システムとして問題が無いようであれば、チップ31の再起動処理を行う。チップ17は、チップ31との通信が出来るようになった後、続けて3番目のチップ45の再起動処理を行うが、並行して2番目のチップ31のメカの初期化処理を実施する。また、チップ45が通信可能となった後も同様に、チップ45のメカの初期化処理を実施する。この様な構成を有する事で、モーターやセンサー、記録ヘッドを制御しているチップでエラーが発生し、チップの再起動が必要な状況となった場合、少なくともエラーが発生したチップよりも前段のチップ間でエラー状態の共有することができる。故に、エラーが発生した時の記録装置の状態に応じて、記録ヘッドや記録用紙を退避させるなどして、装置の状態をより安全な状態にする事が可能となる。

#### 【0042】

以上述べた様に、本実施形態によれば、複数のチップを接続して構成されたシステムにおいて、いずれかのチップで発生したエラー状態をCPUの介在無しに最上流のチップまで通知する事が可能となり、エラー状態の共有が可能となる。また、エラーが発生したチップを含む下流のチップをリセットする構成を有する事で、どのチップでエラーが発生してもシステム全体を安全に停止、または再起動させる事が可能となる。また、起動完了通知信号と機能を共有する事で、前記機能を実現するために、新たな専用の端子を用意する事なく実現が可能となる。

#### 【符号の説明】

#### 【0043】

17、31、45、64、65...コントロールチップ、16...ホスト、19、32、46...CPU、28、41、55...ウォッチドッグタイマ部、27、40、54...割り込み制御部、30、43、57...I/O切り替え部、27、40、54...割り込み制御部

10

20

30

【図1】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 藤本 和志

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 多賀 実

(56)参考文献 特開平2 - 073451 (JP, A)

特開2014 - 209276 (JP, A)

特開2006 - 157387 (JP, A)

特開平3 - 251932 (JP, A)

特開平2 - 244375 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 11 / 07

G 06 F 11 / 28 - 11 / 36