(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5991739号

(P5991739)

(45) 発行日 平成28年9月14日(2016.9.14)

(24) 登録日 平成28年8月26日(2016.8.26)

|                         |                  |

|-------------------------|------------------|

| (51) Int.Cl.            | F 1              |

| HO 1 L 27/146 (2006.01) | HO 1 L 27/14 A   |

| HO 1 L 27/14 (2006.01)  | HO 1 L 27/14 D   |

| HO 4 N 5/369 (2011.01)  | HO 4 N 5/335 690 |

請求項の数 17 (全 16 頁)

(21) 出願番号 特願2012-136305 (P2012-136305)

(22) 出願日 平成24年6月15日 (2012.6.15)

(65) 公開番号 特開2014-3099 (P2014-3099A)

(43) 公開日 平成26年1月9日 (2014.1.9)

審査請求日 平成27年6月15日 (2015.6.15)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 固体撮像装置およびその製造方法、ならびにカメラ

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換部を有する画素領域と、前記画素領域の少なくとも一部を取り囲むように配置された周辺回路領域と、前記画素領域と前記周辺回路領域との間に配置された中間領域とが半導体基板に配された固体撮像装置の製造方法であって、

前記画素領域の上に第1膜が位置した状態で、前記周辺回路領域の活性領域の上および前記中間領域の上に金属化合物を形成する工程と、

前記金属化合物を形成する工程の後に、前記画素領域、前記周辺回路領域および前記中間領域の上に第2膜を形成する工程と、

前記周辺回路領域および前記中間領域の上に前記第2膜が残るように、前記第2膜のうちの前記画素領域の上に位置する部分を除去する工程と、

前記周辺回路領域および前記中間領域の上に前記第2膜が位置した状態で、前記画素領域、前記周辺回路領域および前記中間領域の上に層間絶縁膜を形成する工程と、

前記画素領域の上において前記層間絶縁膜および前記第1膜に形成された第1コンタクトホールと、前記周辺回路領域の前記金属化合物の上において前記層間絶縁膜および前記第2膜に形成された第2コンタクトホールと、のそれぞれの中にコンタクトプラグを形成する工程と、を有し、

前記第1膜は、前記画素領域の前記光電変換部と前記層間絶縁膜との間に位置する部分を有し、

前記中間領域の上に形成された前記金属化合物は前記周辺回路領域の前記金属化合物か

10

20

ら離れて形成されており、前記コンタクトプラグを形成する工程では、前記中間領域の上に形成された前記金属化合物の上にコンタクトホールを形成しないことを特徴とする固体撮像装置の製造方法。

**【請求項 2】**

前記金属化合物がシリサイドであり、前記第1膜が窒化シリコン膜であり、前記第2膜が窒化シリコン膜であることを特徴とする請求項1に記載の固体撮像装置の製造方法。

**【請求項 3】**

前記画素領域の光電変換部に光を導く導波路を前記層間絶縁膜に形成する工程を更に有し、

前記第2膜のうちの前記画素領域の上に位置する部分を除去する工程は、前記第2膜のうちの前記光電変換部の上に位置する部分が残るように行われ、 10

前記導波路を形成する工程は、前記第2膜の前記光電変換部の上に残った前記部分をエッチングストップ膜として用いて、前記層間絶縁膜に前記導波路が設けられる開口を形成する工程を含む、ことを特徴とする請求項1又は2に記載の固体撮像装置の製造方法。

**【請求項 4】**

前記第1膜をエッチングストップ膜として用いて前記層間絶縁膜および前記第1膜に前記第1コンタクトホールを形成した後に、前記第2膜をエッチングストップ膜として用いて前記層間絶縁膜および前記第2膜に前記第2コンタクトホールを形成することを特徴とする請求項1乃至3のいずれか1項に記載の固体撮像装置の製造方法。

**【請求項 5】**

画素領域と、前記画素領域の少なくとも一部を取り囲むように配置された周辺回路領域と、前記画素領域と前記周辺回路領域との間に配置された中間領域とが半導体基板に配された固体撮像装置の製造方法であって、 20

前記画素領域の活性領域の上に第1膜が位置した状態で、前記周辺回路領域の活性領域および前記中間領域の活性領域に金属化合物を形成する工程と、

前記金属化合物を形成する工程の後に、前記画素領域の前記活性領域、前記周辺回路領域の前記活性領域および前記中間領域の前記活性領域の上に第2膜を形成する工程と、

前記周辺回路領域の前記活性領域および前記中間領域の前記活性領域の上に前記第2膜が残るように、前記第2膜のうちの前記画素領域の前記活性領域の上に位置する部分を除去する工程と、 30

前記周辺回路領域の前記活性領域および前記中間領域の前記活性領域の上に前記第2膜が位置した状態で、前記画素領域、前記周辺回路領域および前記中間領域の上に層間絶縁膜を形成する工程と、

前記第2膜をエッチングストップ膜として用いて前記層間絶縁膜および前記第2膜にコンタクトホールを形成し、前記コンタクトホールの中に、前記周辺回路領域の前記活性領域の前記金属化合物に接触するコンタクトプラグを形成する工程と、を有し、

前記画素領域と前記中間領域との間に、前記画素領域に配されるウエルに基準電圧を供給するためのコンタクト領域が配され、

前記除去する工程では、前記第2膜のうちの前記コンタクト領域の上に位置する部分を除去することを特徴とする固体撮像装置の製造方法。 40

**【請求項 6】**

画素領域と、前記画素領域の周囲に配置された周辺回路領域と、前記画素領域と前記周辺回路領域との間に配置された中間領域とが配された半導体基板、および、前記画素領域と、前記周辺回路領域と、前記中間領域とを覆う層間絶縁膜を有する固体撮像装置であつて、

前記画素領域は光電変換部及び第1半導体領域を有し、前記周辺回路領域は第2半導体領域を有し、前記中間領域は第3半導体領域を有し、

前記光電変換部と前記層間絶縁膜との間および前記第1半導体領域と前記層間絶縁膜との間には、第1膜が配置され、かつ、前記第1半導体領域の上には第1コンタクトプラグが配置され、 50

前記第2半導体領域と前記層間絶縁膜との間には第1金属化合物領域が配置され、

前記第3半導体領域と前記層間絶縁膜との間には前記第1金属化合物領域から離れた第2金属化合物領域が配置され、

前記第1金属化合物領域と前記層間絶縁膜との間には第2膜が配置され、かつ、前記第1金属化合物領域の上には第2コンタクトプラグが配置され、

前記第1膜は、前記第2膜に重なる第1部分と前記第2膜に重ならない第2部分とを有し、前記第1コンタクトプラグは前記層間絶縁膜および前記第1膜の前記第2部分を通して前記第1半導体領域に接続されており、

前記第2膜は、前記第1膜に重なる第3部分と前記第1膜に重ならない第4部分とを有し、前記第2コンタクトプラグは前記層間絶縁膜および前記第2膜の前記第4部分を通して前記第1金属化合物領域に接続されており、

前記層間絶縁膜が前記第2金属化合物領域に接しないように、前記第2金属化合物領域と前記層間絶縁膜との間には前記第2膜が配置され、かつ、前記第2金属化合物領域の上には前記層間絶縁膜を通るコンタクトプラグが配置されていない、

ことを特徴とする固体撮像装置。

#### 【請求項7】

前記第1金属化合物領域および前記第2金属化合物領域がシリサイドを含み、前記第2膜の前記第3部分は、前記第1膜の前記第1部分と前記層間絶縁膜との間に位置することを特徴とする請求項6に記載の固体撮像装置。

#### 【請求項8】

前記第1金属化合物領域はポリシリコンパターンの上に配置されている、

ことを特徴とする請求項6又は7に記載の固体撮像装置。

#### 【請求項9】

前記画素領域と前記中間領域との間に、前記画素領域に設けられた半導体層の電位を固定するための第4半導体領域を有する領域が配置され、

前記第4半導体領域には前記層間絶縁膜および前記第1膜を通して第3コンタクトプラグが接続されている、

ことを特徴とする請求項6乃至8のいずれか1項に記載の固体撮像装置。

#### 【請求項10】

前記第2膜は前記第3コンタクトプラグから離れている、

ことを特徴とする請求項9に記載の固体撮像装置。

#### 【請求項11】

前記画素領域と前記第1膜との間に第3膜が配置されており、

前記第1コンタクトプラグは前記第3膜を通して前記第1半導体領域に接続されており、

前記第3膜は前記第3コンタクトプラグから離れている、

ことを特徴とする請求項9または10に記載の固体撮像装置。

#### 【請求項12】

前記画素領域に配置された光電変換部に光を導く導波路が設けられており、前記第1膜と前記層間絶縁膜との間に配置された膜が、前記導波路に接するように前記第1膜と前記導波路との間に位置している、

ことを特徴とする請求項6乃至11のいずれか1項に記載の固体撮像装置。

#### 【請求項13】

前記第2膜が窒化シリコン膜である、

ことを特徴とする請求項6乃至12のいずれか1項に記載の固体撮像装置。

#### 【請求項14】

前記第1膜が酸化シリコン膜である、

ことを特徴とする請求項6乃至13のいずれか1項に記載の固体撮像装置。

#### 【請求項15】

前記第2半導体領域と前記第2膜との間に酸化シリコンからなる第4膜が配置されてい

10

20

30

40

50

る、

ことを特徴とする請求項 6 乃至 14 のいずれか 1 項に記載の固体撮像装置。

【請求項 16】

前記金属化合物を形成する工程の前に、前記画素領域、前記周辺回路領域および前記中間領域の上に絶縁膜を形成する工程と、

前記絶縁膜をエッチングすることで、前記絶縁膜から、前記第 1 膜と、前記周辺回路領域のポリシリコンパターンの側面にスペーサと、を形成する工程と、を有し、

前記金属化合物を形成する工程では、前記ポリシリコンパターンの上に金属化合物を形成する、

ことを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の固体撮像装置の製造方法。 10

【請求項 17】

請求項 6 乃至 15 のいずれか 1 項に記載の固体撮像装置と、

前記固体撮像装置から出力される信号を処理する処理部と、

を備えることを特徴とするカメラ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、固体撮像装置およびその製造方法、ならびにカメラに関する。

【背景技術】

【0002】 20

特許文献 1 には、周辺回路部のゲート電極、ソース領域およびドレイン領域をシリサイド化する一方で、画素部のゲート電極、ソース領域およびドレイン領域をシリサイド化しない方法が記載されている。特許文献 2 にも同様の方法が記載されている。周辺回路部のゲート電極、ソース領域およびドレイン領域をシリサイド化することにより周辺回路部の MOS トランジスタの動作を高速化することができる。一方、画素部のゲート電極、ソース領域およびドレイン領域をシリサイド化しないことにより、白キズや暗電流の増加を抑えることができる。

【先行技術文献】

【特許文献】

【0003】 30

【特許文献 1】特開 2010 - 56515 号公報

【特許文献 2】特開 2011 - 243474 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献 1、2 には、周辺回路部（周辺回路領域）と画素部（画素領域）との間の境界ないしは中間領域をどのように設計するかに対する考慮がない。

【0005】

本発明者等は、周辺回路部（周辺回路領域）と画素部（画素領域）との間の境界ないしは中間領域において、製造工程中にシリサイドが露出し、このシリサイドが剥離してパーティクルとなる場合があることを見出した。これは歩留まりを低下させる原因となる。 40

【0006】

本発明は、上記の課題認識を契機としてなされたものであり、歩留まりの向上に有利な技術を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明の 1 つの側面は、光電変換部を有する画素領域と、前記画素領域の少なくとも一部を取り囲むように配置された周辺回路領域と、前記画素領域と前記周辺回路領域との間に配置された中間領域とが半導体基板に配された固体撮像装置の製造方法であって、前記画素領域の上に第 1 膜が位置した状態で、前記周辺回路領域の活性領域の上および前記中 50

間領域の上に金属化合物を形成する工程と、前記金属化合物を形成する工程の後に、前記画素領域、前記周辺回路領域および前記中間領域の上に第2膜を形成する工程と、前記周辺回路領域および前記中間領域の上に前記第2膜が残るように、前記第2膜のうちの前記画素領域の上に位置する部分を除去する工程と、前記周辺回路領域および前記中間領域の上に前記第2膜が位置した状態で、前記画素領域、前記周辺回路領域および前記中間領域の上に層間絶縁膜を形成する工程と、前記画素領域の前記半導体領域の上において前記層間絶縁膜および前記第1膜に形成された第1コンタクトホールと、前記周辺回路領域の前記金属化合物の上において前記層間絶縁膜および前記第2膜に形成された第2コンタクトホールと、のそれぞれの中にコンタクトプラグを形成する工程と、を有し、前記第1膜は、前記画素領域の光電変換部と前記層間絶縁膜との間に位置する部分を有し、前記中間領域の上に形成された前記金属化合物は前記周辺回路領域の前記金属化合物から離れて形成されており、前記コンタクトプラグを形成する工程では、前記中間領域の上に形成された前記金属化合物の上にコンタクトホールを形成しないことを特徴とする。

#### 【発明の効果】

#### 【0008】

本発明によれば、歩留まりの向上に有利な技術が提供される。

#### 【図面の簡単な説明】

#### 【0009】

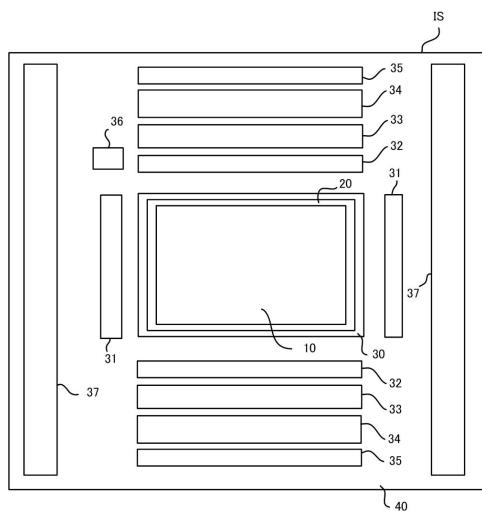

【図1】本発明の1つの実施形態の固体撮像装置の構成を模式的に示す平面図。

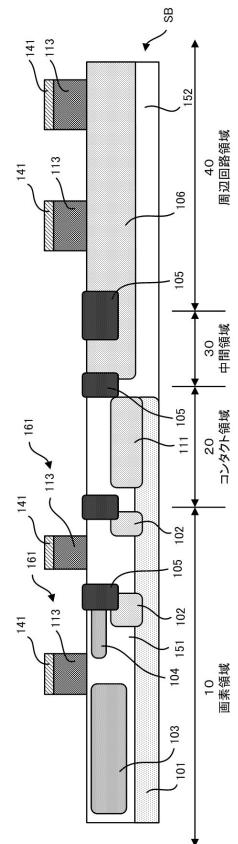

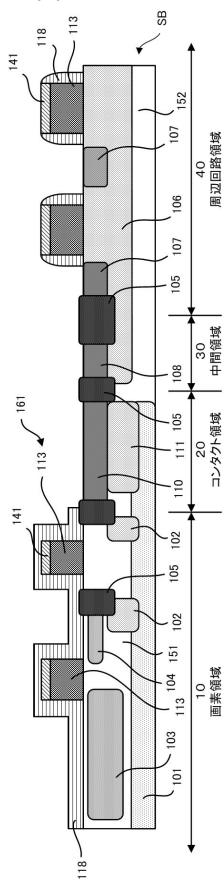

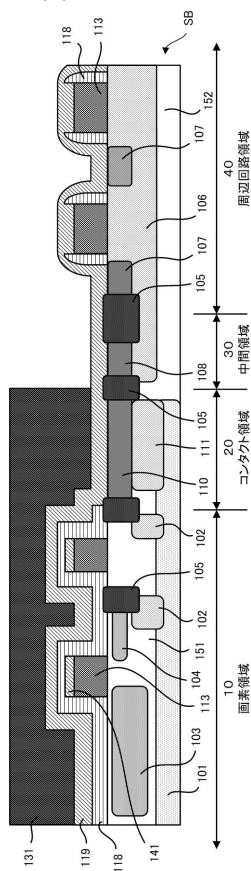

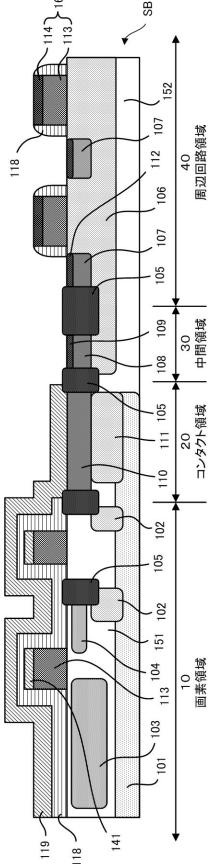

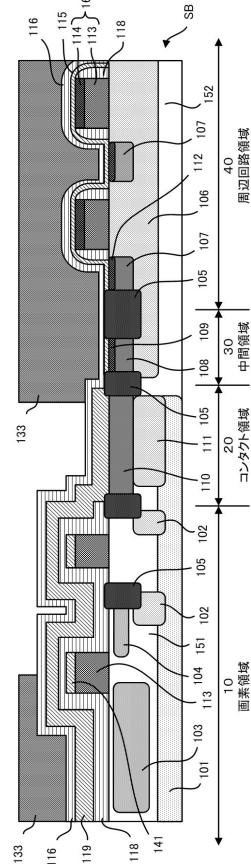

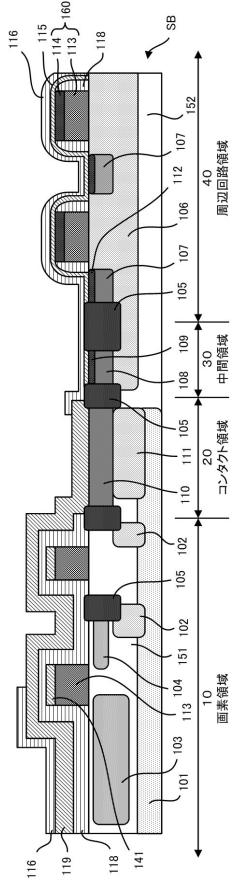

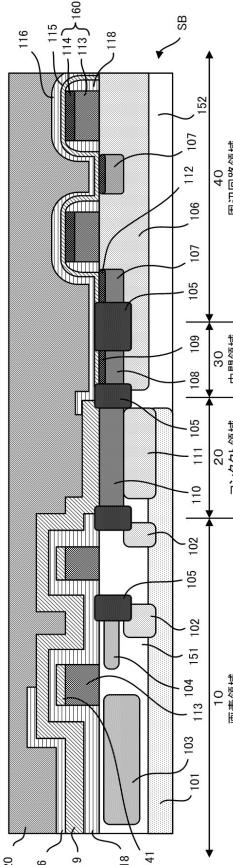

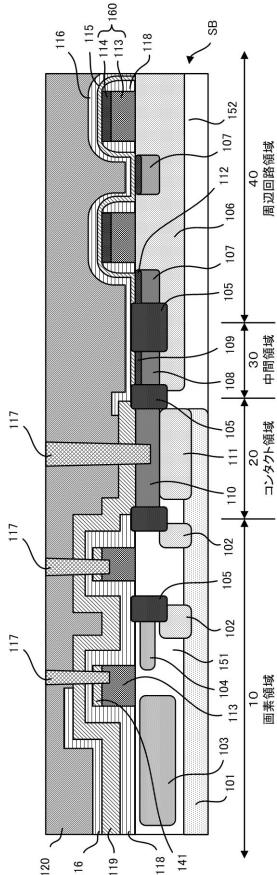

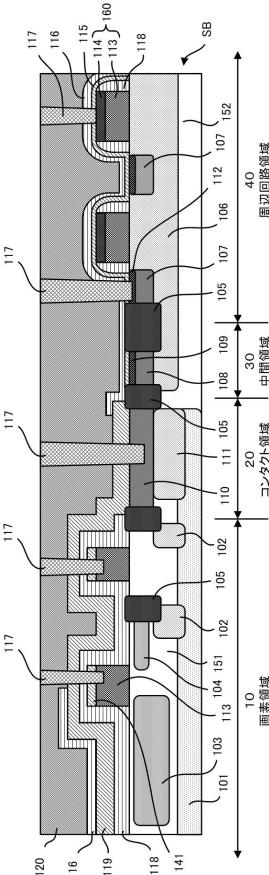

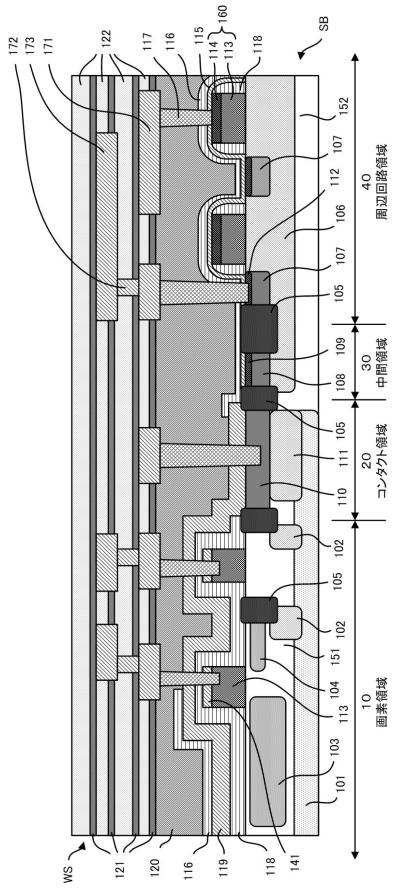

【図2】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

20

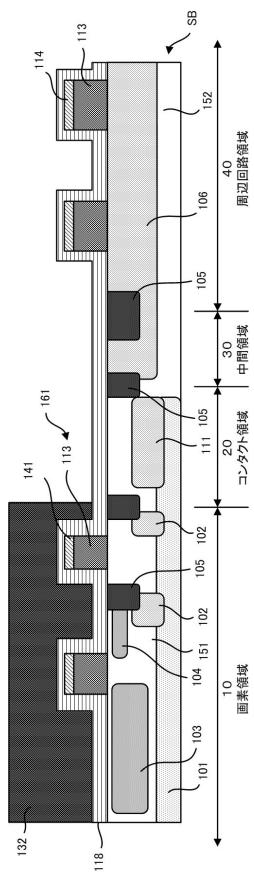

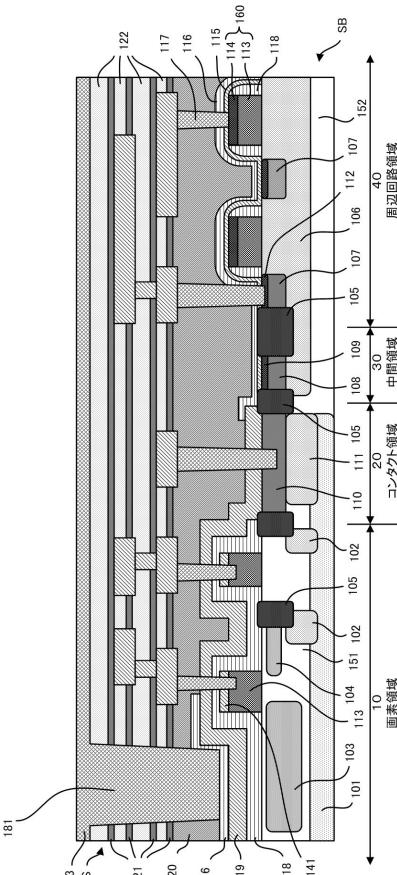

【図3】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

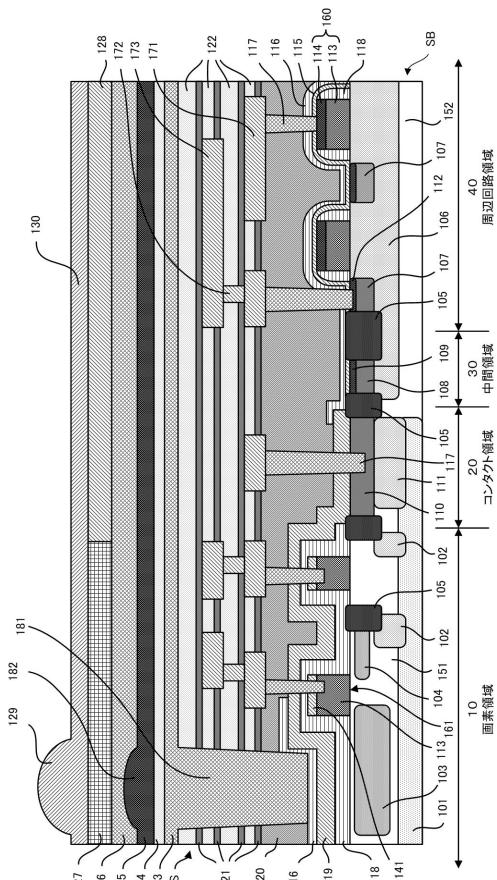

【図4】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

【図5】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

【図6】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

【図7】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

【図8】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

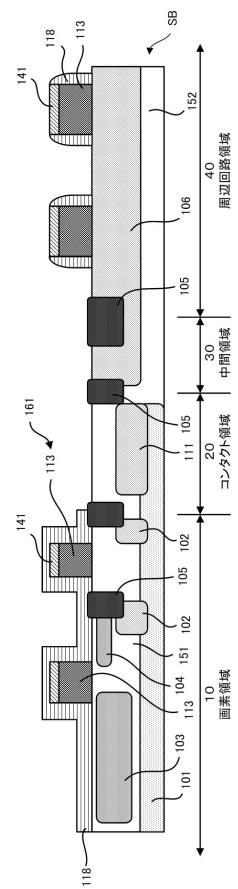

【図9】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

【図10】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

【図11】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

【図12】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

30

【図13】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

【図14】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

【図15】本発明の1つの実施形態の固体撮像装置の製造方法を説明するための断面図。

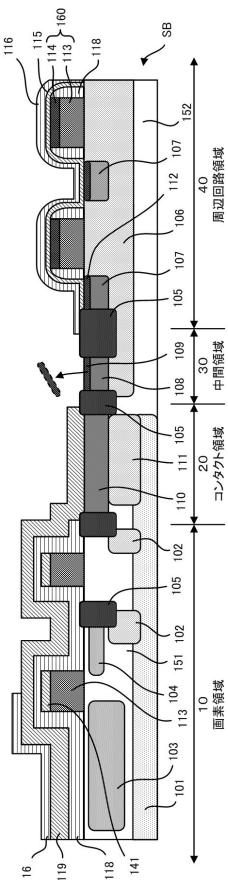

【図16】比較例を示す図。

#### 【発明を実施するための形態】

#### 【0010】

以下、添付図面を参照しながら本発明の実施形態を説明する。以下では、トランジスタの動作を高速にするためにシリサイドを用いる場合を例に説明する。しかしながら、本発明はこれに限定されるものではなく、活性領域を構成する材料と高融点金属との化合物（高融点金属化合物）が形成されていればよい。活性領域を構成する半導体材料の例としては、シリコン、ガリウムヒ素などが考えられ、高融点金属としては、コバルト、タンゲステン、チタンなどがある。また、エッチングストップ膜に関して、エッチングストップ膜でエッチングが停止する場合を例に説明するが、完全に停止しなくとも、被エッチング膜に対してエッティングレートが低い膜を設けてエッティング速度を落とすものであればよい。

#### 【0011】

図1は、本発明の1つの実施形態の固体撮像装置ISの構成を模式的に示す平面図である。固体撮像装置ISは、画素領域10、中間領域30および周辺回路領域40を含み、画素領域10、中間領域30および周辺回路領域40は、半導体基板に配されている。ここで、画素領域10は、複数の画素が複数の行および複数の列を構成するように配列された領域である。各画素は、光電変換部を含む。各画素は、その他、フローティングディフ

40

50

ュージョン、転送ゲート、増幅トランジスタ、リセットトランジスタを含みうる。転送ゲートは、光電変換素部で発生した電荷をフローティングディフュージョンに転送するチャネルを形成する。増幅トランジスタは、フローティングディフュージョンの電位に応じた信号を列信号線に出力する。リセットトランジスタは、フローティングディフュージョンの電位をリセットする。フローティングディフュージョン、増幅トランジスタおよびリセットトランジスタは、複数の画素で共有されてもよい。各画素の選択動作に関しては選択トランジスタを設けてもよいし、リセットトランジスタによりフローティングディフュージョンの電位を切り替えて選択、非選択状態を実現する構成でもよい。

#### 【0012】

周辺回路領域40は、画素領域10の周囲に配置された領域であり、周辺回路領域40には、画素領域10に配置された画素の動作を制御する回路、画素から読み出された信号を処理する回路などが配置されうる。より具体的には、周辺回路領域40には、例えば、垂直走査回路31、水平走査回路32、列アンプ33、列A/D変換器34、メモリ35、タイミング生成回路36、パッド部37が配置されうる。垂直走査回路31は、画素領域10における行を選択する。列アンプ33は、画素領域10の列信号線に出力される信号を増幅する。列A/D変換器34は、列アンプ33から出力されるアナログの画素信号をデジタル信号に変換する。メモリ35は、列A/D変換器34から出力されるデジタルのアナログ信号を保持する。水平走査回路32は、メモリに保持された信号を選択して読み出す。タイミング生成回路36は、垂直走査回路31、水平走査回路32、列アンプ33、列A/D変換器34、メモリ35を制御する信号を生成する。

10

#### 【0013】

中間領域30は、画素領域10と周辺回路領域40との間に配置された領域である。中間領域30には、回路素子が配置されず、したがって、コンタクトプラグも配置されない。画素領域10と中間領域30との間には、画素領域10に配置された半導体層の電位の変動を抑制し、望ましくは電位を固定するためのコンタクトプラグが配置されたコンタクト領域20が配置されうる。より具体的には、該半導体層は、画素のトランジスタのチャネル部を提供するウエルである。コンタクト領域20はウエルに基準電圧を供給することにより、ウエルの電位の変動を抑制している。

#### 【0014】

画素領域10、コンタクト領域20、中間領域30および周辺回路領域40には、活性領域が形成されている。画素領域10の活性領域およびコンタクト領域20の活性領域にはシリサイドが形成されず、周辺回路領域40の活性領域および中間領域30の活性領域にはシリサイドが形成されている。周辺回路領域40の活性領域は、エッチングストップ膜で覆われ、かつ、該エッチングストップ膜に形成された開口を通してコンタクトプラグが接続されている。中間領域30の活性領域は、その全体がエッチングストップ膜で覆われている。

30

#### 【0015】

図15は、固体撮像装置ISの構成を示す模式的な断面図である。固体撮像装置ISは、第1導電型の不純物半導体領域151、152を有する半導体基板SBに形成されている。なお、図15および後に参照する図2～図14では、半導体基板SBの一部分が示されている。

40

#### 【0016】

半導体基板SBには、MOSトランジスタなどの素子を相互に分離するための素子分離105が形成されている。素子分離105は、STI又はLOCOSでありうる。半導体基板SBの表面のうち素子分離105が存在しない領域が活性領域であり、前述のように、画素領域10、コンタクト領域20、中間領域30および周辺回路領域40のそれぞれに活性領域が存在する。

#### 【0017】

画素領域10は、埋め込み半導体層101、光電変換部を構成する半導体領域103、フローティングディフュージョン104および半導体領域102を含みうる。半導体領域

50

103 およびフローティングディフュージョン 104 は、第1導電型の半導体領域で構成されうる。埋め込み半導体層 101 および半導体領域 102 は、第2導電型の半導体領域で構成されうる。ここで、第1導電型および第2導電型は、相互に異なる導電型である。第1導電型が n 型である場合には第2導電型が p 型であり、第1導電型が p 型である場合には第2導電型が n 型である。

#### 【0018】

画素領域 10 には、複数のゲート電極 161 が配置されている。複数のゲート電極 161 は、例えば、転送ゲート電極、増幅トランジスタのゲート電極、リセットトランジスタのゲート電極を含みうる。複数のゲート電極 161 の上には絶縁膜 141 が配置されうる。絶縁膜 141 は、酸化シリコン膜でありうる。ゲート電極 161 は、ポリシリコンパターン 113 で構成されうる。

#### 【0019】

画素領域 10 の活性領域、ゲート電極 161 および素子分離 105 は、絶縁膜 118 で覆われうる。絶縁膜 118 は、絶縁膜 119 で覆われうる。絶縁膜 118 は、窒化シリコン膜でありうる。絶縁膜 119 は、酸化シリコン膜でありうる。半導体領域（光電変換部）103 が配置された領域では、絶縁膜 119 の上にエッティングストップ膜 116 が配置されうる。エッティングストップ膜 116 および絶縁膜 119 は、層間絶縁膜 120 で覆われている。層間絶縁膜 120 の上には、配線構造 WS が配置されている。配線構造 WS は、配線層 171、173、ビア 172 および層間絶縁膜を含む。該層間絶縁膜は、例えば、絶縁膜 121、122 の積層構造を有しうる。絶縁膜 121、122 は、それぞれ、窒化シリコン膜、酸化シリコン膜でありうる。各配線層の配線を構成する材料は、好ましくは銅である。この場合には、ビア 172 についても、配線材料である銅を用いてデュアルダマシン法で構成することもできる。配線層の数に関して、図では画素領域 10、周辺回路領域 40 ともに 2 層の例を示しているが、更に多層の配線層を設けてもよい。更に、画素領域 10 と周辺回路領域 40 とで配線層の数を変えてもよい。好ましくは周辺回路領域 40 の配線層数が画素領域 10 に比べて多くされる。

#### 【0020】

半導体領域（光電変換部）103 の上には、半導体領域 103 に光を導く導波路 181 が配置されうる。導波路 181 は、エッティングストップ膜 116 のうち画素領域 10 に配置されたパターンでエッティングが停止するように配線構造 WS、層間絶縁膜 120 にエッティングによって導波路開口を形成する工程と、該導波路開口に絶縁体を充填する工程とを経て形成されうる。エッティングストップ膜 116 の前記パターンは、その一部の領域が導波路 181 の下面に接し、他の一部の領域が層間絶縁膜 120 に接している。導波路開口に絶縁体を充填する際に、該導波路開口以外の領域にも絶縁膜 123 が形成されうる。導波路 181 および絶縁膜 123 は、例えば、窒化シリコンで構成されうる。

#### 【0021】

コンタクト領域 20 は、第2導電型の半導体領域 110 と、半導体領域 110 と埋め込み半導体層 101 とを電気的に接続する第2導電型の半導体領域 111 とを含みうる。半導体領域 110 にはコンタクトプラグ 117 が電気的に接続されていて、半導体領域 110、111 を介して当該コンタクトプラグ 117 と埋め込み半導体層 101 とが電気的に接続される。これにより、埋め込み半導体層 101 の電位を固定することができる。埋め込み半導体層 101 は、画素領域 10 の全体にわたって広がっている。

#### 【0022】

中間領域 30 は、第1導電型のウエル 106 と、ウエル 106 に形成された第2導電型の半導体領域 108 と、半導体領域 108 の上に配置されたシリサイド 109 とを含みうる。図示されていないが、中間領域 30 は、第2導電型のウエルと、該ウエルに形成された第1導電型の半導体領域と、該半導体領域の上に配置されたシリサイドとを含みうる。

#### 【0023】

中間領域 30 の活性領域、即ちシリサイド 109 が形成された領域は、その全体がエッティングストップ膜 116 で覆われている。ここで、エッティングストップ膜 116 とシリサ

10

20

30

40

50

イド 109との間には、絶縁膜 115が配置されうる。絶縁膜 115は、エッティングストップ膜 116とシリサイド 109との間に生じる応力を緩和するために有用である。エッティングストップ膜 116は、周辺回路領域 40の活性領域、即ちシリサイド 112に接触するコンタクトプラグ 117を形成する際に使用される。

#### 【0024】

周辺回路領域 40は、第1導電型のウエル 106と、ウエル 106に形成された第2導電型の半導体領域 107と、半導体領域 107の上に配置されたシリサイド 112とを含みうる。図示されていないが、周辺回路領域 40は、第2導電型のウエルと、該ウエルに形成された第1導電型の半導体領域と、該半導体領域の上に配置されたシリサイドとを含みうる。半導体領域 107は、MOSトランジスタの拡散領域（ソース領域およびドレン領域）を構成しうる。10

#### 【0025】

周辺回路領域 40の活性領域、即ちシリサイド 112が形成された領域は、エッティングストップ膜 116で覆われ、かつ、エッティングストップ膜 116に形成された開口を通してコンタクトプラグ 117が接続されている。周辺回路領域 40には、ゲート電極 160が配置されている。ゲート電極 160は、半導体領域 107とともに MOSトランジスタを構成しうる。ゲート電極 160は、ポリシリコンパターン 113と、その上に配置されたシリサイド 114とを含む。シリサイド 114は、エッティングストップ膜 116で覆われ、かつ、エッティングストップ膜 116に形成された開口を通してコンタクトプラグ 117が接続されている。エッティングストップ膜 116とシリサイド 112との間、および、エッティングストップ膜 116とシリサイド 114との間には、絶縁膜 115が配置されうる。絶縁膜 115は、エッティングストップ膜 116とシリサイド 112、114との間に生じる応力を緩和するために有用である。20

#### 【0026】

周辺回路領域 40の活性領域に形成されたシリサイド 112に接触するコンタクトプラグ 117を形成する工程は、コンタクトホール形成工程と充填工程とを含みうる。コンタクトホール形成工程では、エッティングストップ膜 116でエッティングが停止するように層間絶縁膜 120にエッティングによって開口を形成した後に該開口を通してエッティングストップ膜 116をエッティングする。これによってコンタクトホールが形成される。充填工程では、該コンタクトホールに導電体を充填する。30

#### 【0027】

中間領域 30および周辺回路領域 40に配置されたエッティングストップ膜 116と、画素領域 10に配置されたエッティングストップ膜 116とは、同一の工程で形成されうる。換言すると、中間領域 30および周辺回路領域 40に配置されたエッティングストップ膜 116と、画素領域 10に配置されたエッティングストップ膜 116とは同一材料で構成され、平坦な部分においては同一の厚さを有しうる。エッティングストップ膜 116は、コンタクト領域 20には配置されていない。

#### 【0028】

導波路 181および絶縁膜 123の上には絶縁膜 124が配置されうる。絶縁膜 124は、例えば、酸化シリコンで構成されうる。絶縁膜 124の上には、絶縁膜 125で構成された層内レンズ 182が配置されうる。絶縁膜 125は、例えば、窒化シリコンで構成されうる。絶縁膜 125の上には、平坦化膜 126が配置されうる。平坦化膜 126の上には、カラーフィルタ 127、128が配置されうる。ここで、画素領域 10に配置されるカラーフィルタ 127は、画素に割り当てられたカラーに応じたカラーフィルタである。一方、コンタクト領域 20、中間領域 30および周辺回路領域 40にもカラーフィルタ 128が配置されることが好ましく、カラーフィルタ 128は、RGBカラーフィルタ構成におけるBカラーフィルタであることが好ましい。カラーフィルタ 127、128が配置された層の上には、マイクロレンズ 129を含むマイクロレンズ層 130が配置されうる。40

#### 【0029】

50

以下、図2～図15を参照しながら固体撮像装置ISの製造方法を例示的に説明する。図2に示す工程では、半導体基板SBに埋め込み半導体層101、半導体領域102、光電変換部103、フローティングディフュージョン104、ウエル106および素子分離105を形成する。不図示であるが、転送ゲート電極となるポリシリコンパターン113の下部に第2導電型の半導体領域を形成し、光電変換部とフローティングディフュージョンの間のパンチスルーや抑制する構成としてもよい。図2に示す工程ではまた、半導体基板SBの上にゲート絶縁膜(不図示)を介してポリシリコンパターン113を形成する。ポリシリコンパターン113は、ゲート絶縁膜の上にポリシリコン層を形成し、その上に絶縁膜141によってハードマスクを形成した後に、絶縁膜141をエッチングマスクとしてポリシリコン層をエッチングすることによって形成されうる。

10

### 【0030】

図3に示す工程では、半導体基板SB、ポリシリコンパターン113および絶縁膜141を覆うように絶縁膜118を形成する。好ましくは、絶縁膜118は、酸化シリコンと窒化シリコンとの積層膜で構成される。図3に示す工程では、更に、画素領域10の絶縁膜118を覆う一方でコンタクト領域20、中間領域30および周辺回路領域40の絶縁膜118が露出するようにレジストパターン132を形成する。

### 【0031】

図4に示す工程では、レジストパターン132をエッチングマスクとして使って、コンタクト領域20、中間領域30および周辺回路領域40の絶縁膜118をエッチングし、その後、レジストパターン132を除去する。これにより、周辺回路領域40のポリシリコンパターン113および絶縁膜141の側面に絶縁膜118からなるサイドスペーサが形成される。

20

### 【0032】

図5に示す工程では、コンタクト領域20の半導体領域111の上の領域、および、中間領域30および周辺回路領域40に配置されているウエル106に不純物イオンを注入し、半導体領域110、108、107を形成する。各半導体領域110、108、107の導電型が異なる場合には、それぞれマスクで異なる導電型の不純物イオンを打ち分けて形成する。

### 【0033】

図6に示す工程では、a)画素領域10の絶縁膜118、b)コンタクト領域20、中間領域30および周辺回路領域40の活性領域、ならびに、c)周辺回路領域40のポリシリコンパターン113を含む構造、を覆うように絶縁膜119を形成する。絶縁膜118は、シリサイド化防止膜として機能する。絶縁膜119は、例えば、酸化シリコン膜でありうる。次いで、画素領域10およびコンタクト領域20における絶縁膜119を覆う一方で中間領域30および周辺回路領域40における絶縁膜119を露出させるレジストパターン131を形成する。

30

### 【0034】

図7に示す工程では、レジストパターン131をエッチングマスクとして使って、中間領域30および周辺回路領域40における絶縁膜119をエッチングし、その後、レジストパターン131を除去する。次いで、露出した半導体領域108、107およびポリシリコンパターン113の表面をシリサイド化してシリサイド109、112、114を形成する。このシリサイド化の具体例を挙げると、次のとおりである。まず、半導体領域108、107およびポリシリコンパターン113を覆うように高融点金属としてのコバルトと該高融点金属の酸化防止膜としての窒化チタンなどで構成される積層膜を形成する。ここで、高融点金属としては、コバルトのほかに、チタン、ニッケル、タンゲステン、モリブデン、タンタル、クロム、パラジウム、プラチナ等を挙げることができる。また、高融点金属の酸化防止膜としては、窒化チタンのほかに、ニッケルやチタン等を挙げができる。次いで、該積層膜を熱処理する。この熱処理により、半導体領域108、107およびポリシリコンパターン113を構成しているシリコンと高融点金属とが反応してシリサイド109、112、114が形成される。次いで、未反応の高融点金属を含む積層

40

50

膜を除去する。

#### 【0035】

図8に示す工程では、画素領域10、コンタクト領域20、中間領域30および周辺回路領域40の構造を覆う絶縁膜115を形成し、その上にエッチングストップ膜116を形成する。好ましくは、絶縁膜115は酸化シリコンであり、エッチングストップ膜116は窒化シリコンである。絶縁膜115は画素領域にも延在して設けられている。画素領域10においては、絶縁膜119と同種の材料である酸化シリコンで形成されているとして、絶縁膜119と一体的に図示している。次いで、レジストパターン133を形成する。レジストパターン133は、画素領域10における半導体領域103が形成された領域、中間領域30及び周辺回路領域40のエッチングストップ膜116を覆う一方で画素領域10のうちMOSトランジスタが形成された領域およびコンタクト領域20を露出させる。

#### 【0036】

図9に示す工程では、レジストパターン133をエッチングマスクとして使って、画素領域10のうちMOSトランジスタが形成された領域とコンタクト領域20とをエッチングし、その後、レジストパターン133を除去する。これにより、画素領域10のうち半導体領域(光電変換部)103が形成された領域、中間領域30および周辺回路領域40にエッチングストップ膜116が残る。また、エッチングストップ膜116の下に配置されている絶縁膜115も残る。つまり、エッチングストップ膜116および絶縁膜115は、中間領域30のシリサイド109および周辺回路領域40のシリサイド112、114を覆うように残される。したがって、コンタクトプラグ117が形成されない中間領域30のシリサイド109がエッチングストップ膜116の除去工程の後に剥離してパーティクルの原因になることが防止される。なお、周辺回路領域40におけるエッチングストップ膜116は、コンタクトホールを形成するためのエッチングにおいて使われる。

#### 【0037】

図16は、比較例を示す図である。図16に示される比較例では、中間領域30のエッチングストップ膜116および絶縁膜115が除去され、シリサイド109が露出した状態が模式的に示されている。このような状態では、シリサイド109が剥離して、これがパーティクルになり易い。よって、図15に例示されるように、中間領域30のシリサイド109をエッチングストップ膜116で覆うことが重要である。

#### 【0038】

図10に示す工程では、画素領域10、コンタクト領域20、中間領域30および周辺回路領域40の構造を覆う層間絶縁膜120を形成する。

#### 【0039】

図11に示す工程では、画素領域10およびコンタクト領域20にコンタクトプラグ117を形成し、図12に示す工程では、周辺回路領域40にコンタクトプラグ117を形成する。ここで、画素領域10、コンタクト領域20および周辺回路領域40に同時にコンタクトプラグ117を形成してもよい。

#### 【0040】

ここで、画素領域10およびコンタクト領域20のコンタクトプラグ117と周辺回路領域40のコンタクトプラグ117とを別個に形成する具体例を説明するが、これは本発明を制限するものではない。図11に示す工程では、絶縁膜118でエッチングが停止するように画素領域10およびコンタクト領域20の層間絶縁膜120および絶縁膜119に開口を形成した後に該開口を通して絶縁膜118および絶縁膜141をエッチングする。これによってコンタクトホールが形成される。このとき、コンタクト領域20にはエッチングストップ膜116がないので、画素領域10よりも深く、半導体基板SBの半導体領域110に届くコンタクトホールが形成される。次いで、該コンタクトホールに導電体を充填することによってコンタクトプラグ117を形成する。

#### 【0041】

図12に示す工程では、エッチングストップ膜116でエッチングが停止するように周

10

20

30

40

50

辺回路領域40の層間絶縁膜120に開口を形成した後に該開口を通してエッティングストップ膜116および絶縁膜115をエッティングする。これによってコンタクトホールが形成される。次いで、該コンタクトホールに導電体を充填することによってコンタクトプラグ117を形成する。

【0042】

図13に示す工程では、配線構造WSを形成する。図14に示す工程では、導波路181を形成する。この工程では、エッティングストップ膜116のうち画素領域10に配置されたパターンが導波路開口を形成するためのエッティングストップ膜として使われる。前述のとおり、エッティングストップ膜116のうち画素領域10に配置されたパターンと周辺回路領域40に配置されたパターンとは同一工程で形成され、平坦部において同一の厚さを有しうる。10

【0043】

具体例を挙げると、図14に示す工程では、エッティングストップ膜116のうち画素領域10に配置されたパターンでエッティングが停止するように配線構造WSおよび層間絶縁膜120をエッティングして導波路開口を形成する。次いで、該導波路開口に絶縁体を充填することによって導波路181が形成される。充填する絶縁体は、層間絶縁膜120よりも屈折率が高い材料で構成されることが好ましい。導波路開口に絶縁体を充填する際に、該導波路開口以外の領域にも絶縁膜123が形成されうる。

【0044】

図15に示す工程では、絶縁膜123、層内レンズ182を有する絶縁膜125、平坦化膜126、カラーフィルタ127、128、および、マイクロレンズ129を有するマイクロレンズ層130を形成する。これによって、固体撮像装置が得られる。20

【0045】

以下、上記の実施形態に係る固体撮像装置の応用例として、該固体撮像装置が組み込まれたカメラについて例示的に説明する。カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置（例えば、パーソナルコンピュータ、携帯端末）も含まれる。カメラは、上記の実施形態として例示された本発明に係る固体撮像装置と、該固体撮像装置から出力される信号を処理する処理部とを含む。該処理部は、例えば、A/D変換器、および、該A/D変換器から出力されるデジタルデータを処理するプロセッサを含みうる。30

【 四 1 】

【 図 2 】

【図3】

【図4】

【図5】

【 図 6 】

【図7】

【 図 8 】

【図9】

【図10】

【図11】

【 図 1 2 】

【図13】

【図14】

【図15】

【 図 1 6 】

---

フロントページの続き

(72)発明者 鈴木 健太郎

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 大貫 裕介

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 西出 隆二

(56)参考文献 特開2011-243747(JP,A)

特開2006-049921(JP,A)

特開2012-074405(JP,A)

特開2006-032672(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H01L 27/14

H04N 5/369