(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-9514

(P2011-9514A)

(43) 公開日 平成23年1月13日(2011.1.13)

(51) Int.Cl.

**HO1L 25/065 (2006.01)**

**HO1L 25/07 (2006.01)**

**HO1L 25/18 (2006.01)**

**HO1L 23/12 (2006.01)**

**HO1L 21/56 (2006.01)**

F 1

HO1L 25/08

HO1L 23/12

HO1L 23/12

HO1L 21/56

Z

501B

N

E

テーマコード(参考)

5 F O 6 1

審査請求 未請求 請求項の数 14 O L (全 29 頁)

(21) 出願番号

特願2009-152259 (P2009-152259)

(22) 出願日

平成21年6月26日 (2009. 6. 26)

(71) 出願人 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部 1753番地

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 杉山 道昭

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 三輪 孝志

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

(72) 発明者 石川 智和

東京都千代田区大手町二丁目6番2号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【要約】

【課題】P O P型の半導体装置において、組み合わせる半導体パッケージの自由度を向上できる技術を提供する。

【解決手段】下段の実装基板である配線基板1Cに金属製の導電性部材3Aを設け、上段の実装基板である配線基板2Cには平面で導電性部材3Aと対応する位置でスルーホール7を設けてそのスルーホール7の側壁に配線を露出させる。それら導電性部材3Aを対応する配線基板2C側のスルーホール7に挿入し、そのスルーホール7を導電性部材3Bで充填することで配線基板1Cと配線基板2Cとを電気的に接続する。配線基板2Cの主面側には、導電性部材3Bと電気的に接続し、上段の半導体部材32が搭載される電極パッド4Bを形成し、電極パッド4Bは平面で下段の半導体チップ22と重なる位置にも配置する。

【選択図】図4 5

## 【特許請求の範囲】

## 【請求項 1】

以下の工程を含むことを特徴とする半導体装置の製造方法：

(a) 第1正面、前記第1正面に形成された第1電極パッド、および前記第1正面とは反対側の第1裏面を有する第1基板を準備する工程；

(b) 第2正面、前記第2正面に形成された第2電極パッド、および前記第2正面とは反対側の第2裏面を有する第2基板を、前記第2基板の前記第2裏面が前記第1基板の前記第1正面と対向するように、前記第1基板上に配置する工程；

ここで、

前記(b)工程では、前記第1基板もしくは前記第2基板の一方に形成され、前記第1基板と前記第2基板との間に配置された半導体チップの厚さよりも大きい高さから成る第1導電性部材を、前記第1基板もしくは前記第2基板の他方に形成されたスルーホール内に配置し、前記第1導電性部材を、前記スルーホール内に形成され、前記第1電極パッドもしくは前記第2電極パッドと電気的に接続されたスルーホール配線と電気的に接続する。

10

## 【請求項 2】

以下の工程を含むことを特徴とする半導体装置の製造方法：

(a) 第1正面、前記第1正面に形成された第1電極パッド、前記第1電極パッドよりも前記第1正面の周縁部側に配置された第2電極パッド、前記第2電極パッド上に形成された第1導電性部材、前記第1正面とは反対側の第1裏面、および前記第1裏面に形成された第3電極パッドを有する第1基板を準備する工程；

20

(b) 表面、前記表面に形成されたボンディングパッド、および前記表面とは反対側の裏面を有する半導体チップを、前記第1基板の前記第1正面に搭載する工程；

(c) 前記半導体チップの前記ボンディングパッドと前記第1基板の前記第1電極パッドとを、第2導電性部材を介して電気的に接続する工程；

(d) 第2正面、前記第2正面に形成された第4電極パッド、前記第2正面とは反対側の第2裏面、前記第2正面から前記第2裏面に向かって形成されたスルーホール、および前記スルーホールの内部に形成されたスルーホール配線を有する第2基板を、前記第1導電性部材が前記スルーホール内に位置し、前記第2基板の前記第2裏面が前記第1基板の前記第1正面と対向するように、前記第1基板上に配置し、前記第1導電性部材と前記スルーホール配線とを電気的に接続させる工程；

30

(e) 前記(d)工程の後、前記第1基板の前記第3電極パッドに外部端子を形成する工程；

ここで、

前記第1導電性部材の高さは、前記半導体チップの厚さよりも大きい。

## 【請求項 3】

請求項2記載の半導体装置の製造方法において、

前記(d)工程後において、前記第1導電性部材は、前記第2基板の前記第2正面から突出していないことを特徴とする半導体装置の製造方法。

40

## 【請求項 4】

請求項3記載の半導体装置の製造方法において、

前記第1導電性部材のうち、前記第1基板の前記第1正面からの一部は絶縁膜によって覆われ、

前記第1導電性部材の前記絶縁膜からの突出量は、前記第2基板の厚さ以下であることを特徴とする半導体装置の製造方法。

## 【請求項 5】

請求項3記載の半導体装置の製造方法において、

前記(d)工程後において、前記第1導電性部材の先端面は、前記第2基板の前記第2正面と前記第2裏面との間に位置することを特徴とする半導体装置の製造方法。

50

## 【請求項 6】

請求項 2 記載の半導体装置の製造方法において、

前記第 1 導電性部材のうち、前記第 1 基板の前記第 1 主面から的一部は絶縁膜によって覆われ、

前記絶縁膜の厚さは、前記第 1 基板の前記第 1 主面に搭載された前記半導体チップの高さより大きいことを特徴とする半導体装置の製造方法。

【請求項 7】

請求項 2 記載の半導体装置の製造方法において、

前記第 1 導電性部材のうち、前記第 1 基板の前記第 1 主面から的一部は絶縁膜によって覆われ、

前記絶縁膜は、平面で前記第 1 基板の前記第 1 主面を囲むように形成され、

10

前記 (d) 工程後において、さらに、

(f) 前記第 1 基板と前記第 2 基板との間に樹脂を供給し、前記第 1 基板と前記第 2 基板との間を前記樹脂で埋め込む工程；

を含むことを特徴とする半導体装置の製造方法。

【請求項 8】

請求項 7 記載の半導体装置の製造方法において、

前記絶縁膜には、前記樹脂を注入するための経路が形成されていることを特徴とする半導体装置の製造方法。

【請求項 9】

請求項 2 記載の半導体装置の製造方法において、

20

さらに、

(f) 前記半導体チップの前記裏面と前記第 2 基板の前記第 2 裏面との間に樹脂を供給し、前記半導体チップの前記裏面と前記第 2 基板の前記第 2 裏面との間を前記樹脂で埋め込む工程；

を含むことを特徴とする半導体装置の製造方法。

【請求項 10】

請求項 2 記載の半導体装置の製造方法において、

前記第 1 導電性部材のうち、前記第 1 基板の前記第 1 主面から的一部は絶縁膜によって覆われ、

前記第 1 導電性部材は、

30

(a1) 前記第 1 基板の前記第 1 主面にマスキング層を形成し、前記マスキング層をパターニングする工程；

(a2) パターニングされた前記マスキング層をマスクとしためっき法にて、前記第 2 電極パッド上に前記第 1 導電性部材を堆積する工程；

(a3) 前記マスキング層を除去し、前記第 1 導電性部材のうち、前記第 1 基板の前記第 1 主面から的一部を前記絶縁膜によって覆う工程；

を含む工程によって形成されていることを特徴とする半導体装置の製造方法。

【請求項 11】

請求項 2 記載の半導体装置の製造方法において、

40

前記第 1 基板中には、前記第 1 電極パッド、前記第 2 電極パッド、前記第 3 電極パッド、および前記第 1 導電性部材と電気的に接続する第 1 配線層が形成され、

前記第 2 基板中には、前記第 2 電極パッドおよび前記スルーホール配線と電気的に接続する第 2 配線層が形成され、

前記第 1 配線層は、前記第 2 配線層より多いことを特徴とする半導体装置の製造方法。

【請求項 12】

請求項 2 記載の半導体装置の製造方法において、

前記第 1 基板の平面外形は、前記第 2 基板の平面外形より大きいことを特徴とする半導体装置の製造方法。

【請求項 13】

50

請求項 2 記載の半導体装置の製造方法において、

前記第 2 基板の前記第 2 主面の前記第 4 電極パッドは、平面で前記第 1 基板に搭載された前記半導体チップと重なる領域に形成されていることを特徴とする半導体装置の製造方法。

【請求項 14】

請求項 2 記載の半導体装置の製造方法において、

(g) 前記第 2 基板の前記第 2 主面には、前記半導体チップと同種または異種の他の半導体チップ、もしくはチップ部品の少なくとも一方を、1 つ以上搭載する工程；

を含むことを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

10

【技術分野】

【0001】

本発明は、半導体装置の製造技術に関し、特に、半導体チップやチップ部品等を複数混載した半導体装置の製造に適用して有効な技術に関するものである。

【背景技術】

【0002】

半導体パッケージやチップ部品（抵抗、コンデンサおよびインダクタ等）等が搭載される実装基板（マザーボード）の小型化や、半導体システムの高速化等を目的として、様々な品種の半導体チップ（マイコンチップおよびメモリチップ等）やチップ部品を1つの半導体装置に混載する MCM (Multi Chip Module) 型の半導体装置が開発されている。

20

【0003】

このような MCM 型の半導体装置の構成としては、たとえば特開 2007-12345

4 号公報（特許文献 1）が示すように、半導体チップあるいはチップ部品を搭載した配線基板を複数準備し、一方の配線基板上に他方の配線基板を積層する、POP (Package On Package) 型の半導体装置などがある。

【0004】

また、他の POP 型の半導体装置の構成としては、たとえば特開 2008-28849

0 号公報（特許文献 2）が図 2 (D) にて示すように、ボール状の電極を介して、下段の配線基板（第 1 の基板 10）と上段の配線基板（第 2 の基板 20）とを電気的に接続し、この上段の配線基板上に別の半導体パッケージを搭載するものがある。

30

【0005】

さらに、他の POP 型の半導体装置の構成としては、たとえば特開 2008-30049

8 号公報（特許文献 3）が図 10 (h) にて示すように、下段の配線基板（第 1 配線層 101）および上段の配線基板（第 2 配線層 104）のそれぞれに電極（バンプ 118）を形成しておき、これらを互いに接合する半導体装置がある。

【先行技術文献】

【特許文献】

【0006】

【特許文献 1】特開 2007-123454 号公報

40

【特許文献 2】特開 2008-288490 号公報

【特許文献 3】特開 2008-300498 号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

POP 型の半導体装置は、予め良品として選別された半導体パッケージを準備し、要求される機能に応じてこれらの半導体パッケージを組合せるため、半導体装置の歩留まりを向上させることができることから、MCM 型の半導体装置の構成の一つとして有効とされている。

【0008】

そこで、本発明者らは、POP 型の半導体装置を製造するに当たり、まず上記特許文献

50

1に開示された構成について検討した。

【0009】

その結果、上記特許文献1に開示された構成の場合、下段側に配置された配線基板上に半導体チップあるいはチップ部品が搭載されているため、上段側に配置される配線基板に形成され、下段の配線基板と電気的に接続するための外部端子の配置箇所に制約が生じることがわかった。

【0010】

そこで、本発明者らは、上記特許文献2に開示された構成について検討した。

【0011】

上記特許文献2に開示された構成の場合、下段の配線基板（第1の基板10）上に別の配線基板（第2の基板20）を積層し、この配線基板（第2の基板20）上に別の半導体パッケージ（電子部品52）を搭載するため、積層する半導体パッケージ（電子部品52）の外部端子の配置箇所を、下段の配線基板（第1の基板10）に形成された電極パッドの位置に合わせなくても良い。すなわち、外部端子の配置箇所に制約が生じない。

10

【0012】

しかしながら、上記特許文献2に開示された構成は、ボール状の電極を介して、下段の配線基板（第1の基板10）と上段の配線基板（第2の基板20）とを電気的に接続するものである。そのため、電極の高さ（大きさ）を、下段の配線基板上に搭載された半導体チップあるいはチップ部品の実装高さよりも高くしなければならない。これにより、隣り合う電極間のピッチも大きくなってしまい、配線基板の外形寸法を小さくすることが困難となる。

20

【0013】

そこで、本発明者らは、上記特許文献3に開示された構成について検討した。

【0014】

上記特許文献3に開示された構成の場合、下段の配線基板（第1配線層101）及び上段の配線基板（第2配線層104）のそれぞれに、Auめっき膜が形成された電極（バンプ118）を設けておき、これらを互いに接合する構成のため、各電極の大きさ（水平方向の幅）を小さくすることができる。

30

【0015】

しかしながら、上記特許文献3に開示された製造方法は、空隙（第2空隙135）が形成された接着層を準備し、電極がこの空隙内に位置するように接着層を下段及び上段の配線基板間に配置し、これらを加熱および加圧することで、それぞれの電極の接合部をこの接着層で覆うものである。

40

【0016】

ところで、近年では、半導体装置の高機能化に伴い、半導体チップと電気的に接続される電極の数も増加する傾向にある。そのため、複数の電極に対応する空隙を接着層に形成する際と、複数の電極を複数の空隙内にそれぞれ配置する際とに、高い位置合わせ精度が要求される。また、上記特許文献3は、各電極に対応する空隙を形成しなくてもよいことも説明しているが、この場合、下段の電極と上段の電極との間に接着層が介在し、下段の半導体パッケージと上段の半導体パッケージとの導通経路に生じる抵抗成分が高くなってしまう。これにより、半導体装置の動作速度の高速化にも対応することが困難となる。

【0017】

本発明の1つの目的は、MCM型の半導体装置において、組み合わせる半導体パッケージの自由度を向上できる技術を提供することにある。

【0018】

本発明の他の1つの目的は、MCM型の半導体装置の小型化を実現できる技術を提供することにある。

【0019】

本発明の他の1つの目的は、MCM型の半導体装置の信頼性を向上できる技術を提供することにある。

50

## 【0020】

本発明の他の1つの目的は、MCM型の半導体装置の動作速度の高速化を実現できる技術を提供することにある。

## 【0021】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

## 【課題を解決するための手段】

## 【0022】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

10

## 【0023】

本発明による半導体装置の製造方法は、以下の工程を含む：

(a) 第1主面、前記第1主面に形成された第1電極パッド、および前記第1主面とは反対側の第1裏面を有する第1基板を準備する工程；

(b) 第2主面、前記第2主面に形成された第2電極パッド、および前記第2主面とは反対側の第2裏面を有する第2基板を、前記第2基板の前記第2裏面が前記第1基板の前記第1主面と対向するように、前記第1基板上に配置する工程；

ここで、

前記(b)工程では、前記第1基板もしくは前記第2基板の一方に形成され、前記第1基板と前記第2基板との間に配置された半導体チップの厚さよりも大きい高さから成る第1導電性部材を、前記第1基板もしくは前記第2基板の他方に形成されたスルーホール内に配置し、前記第1導電性部材を、前記スルーホール内に形成され、前記第1電極パッドもしくは前記第2電極パッドと電気的に接続されたスルーホール配線と電気的に接続する。

20

## 【発明の効果】

## 【0024】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

## 【0025】

(1) MCM型の半導体装置において、組み合わせる半導体パッケージの自由度を向上できる。

30

## 【0026】

(2) MCM型の半導体装置の小型化を実現できる。

## 【0027】

(3) MCM型の半導体装置の信頼性を向上できる。

## 【図面の簡単な説明】

## 【0028】

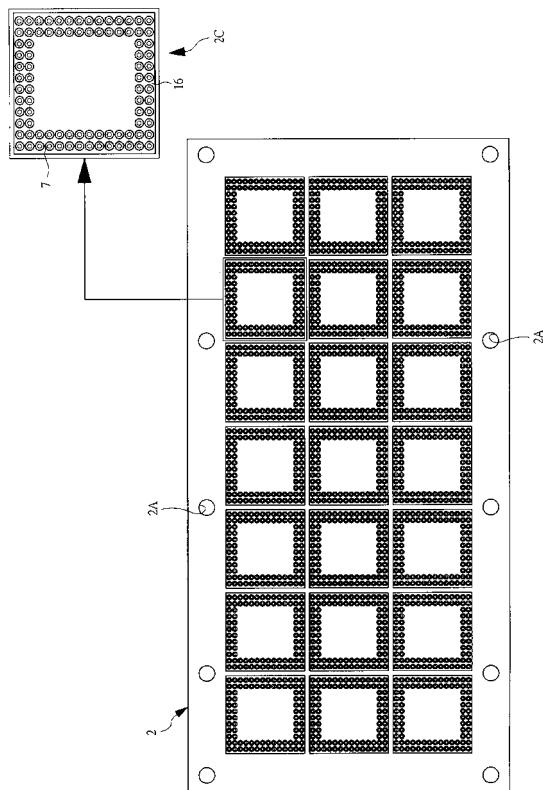

【図1】本発明の一実施の形態である半導体装置を形成するベース基板となる基板母体の主面側を示す平面図である。

【図2】本発明の一実施の形態である半導体装置を形成するベース基板となる基板母体の裏面側を示す平面図である。

40

【図3】本発明の一実施の形態である半導体装置を形成するサブ基板となる基板母体の主面側を示す平面図である。

【図4】本発明の一実施の形態である半導体装置を形成するサブ基板となる基板母体の裏面側を示す平面図である。

【図5】図1および図2に示した基板母体の製造方法を説明する要部断面図である。

【図6】図5に続く基板母体の製造工程中の要部断面図である。

【図7】図6に続く基板母体の製造工程中の要部断面図である。

【図8】図7に続く基板母体の製造工程中の要部断面図である。

【図9】図8に続く基板母体の製造工程中の要部断面図である。

50

【図10】図9に続く基板母体の製造工程中の要部断面図である。

【図11】図10に続く基板母体の製造工程中の要部断面図である。

【図12】図11に続く基板母体の製造工程中の要部断面図である。

【図13】図12に続く基板母体の製造工程中の要部断面図である。

【図14】図13に続く基板母体の製造工程中の要部断面図である。

【図15】図14に続く基板母体の製造工程中の要部断面図である。

【図16】図15に続く基板母体の製造工程中の要部断面図である。

【図17】図16に続く基板母体の製造工程中の要部断面図である。

【図18】図17に続く基板母体の製造工程中の要部断面図である。

【図19】図18に続く基板母体の製造工程中の要部断面図である。

【図20】図19に続く基板母体の製造工程中の要部断面図である。

【図21】図20に続く基板母体の製造工程中の要部断面図である。

【図22】図21に続く基板母体の製造工程中の要部断面図である。

【図23】図22に続く基板母体の製造工程中の要部断面図である。

【図24】図23に続く基板母体の製造工程中の要部断面図である。

【図25】図24に続く基板母体の製造工程中の要部断面図である。

【図26】図25に続く基板母体の製造工程中の要部断面図である。

【図27】図26に続く基板母体の製造工程中の要部断面図である。

【図28】図27に続く基板母体の製造工程中の要部断面図である。

【図29】図28に続く基板母体の製造工程中の要部断面図である。

【図30】図3および図4に示した基板母体の製造方法を説明する要部断面図である。

【図31】図30に続く基板母体の製造工程中の要部断面図である。

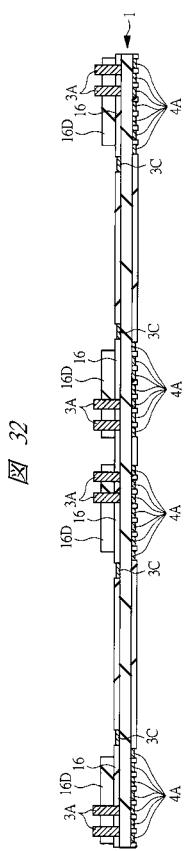

【図32】本発明の一実施の形態である半導体装置の製造方法を説明する要部断面図である。

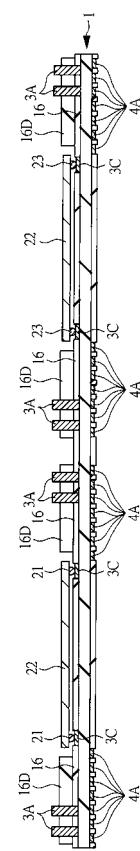

【図33】図32に続く半導体装置の製造工程中の要部断面図である。

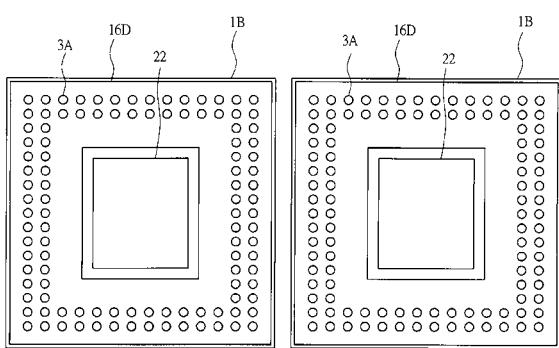

【図34】本発明の一実施の形態である半導体装置の製造工程中の要部平面図である。

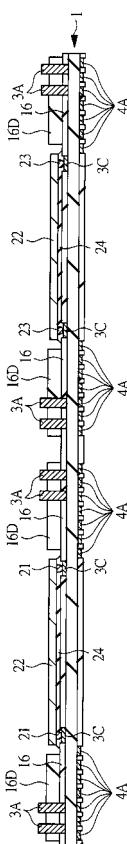

【図35】本発明の一実施の形態である半導体装置の製造工程中の要部断面図である。

【図36】図33に続く半導体装置の製造工程中の要部断面図である。

【図37】本発明の一実施の形態である半導体装置の製造工程中の要部断面図である。

【図38】図37に続く半導体装置の製造工程中の要部断面図である。

【図39】図38に続く半導体装置の製造工程中の要部断面図である。

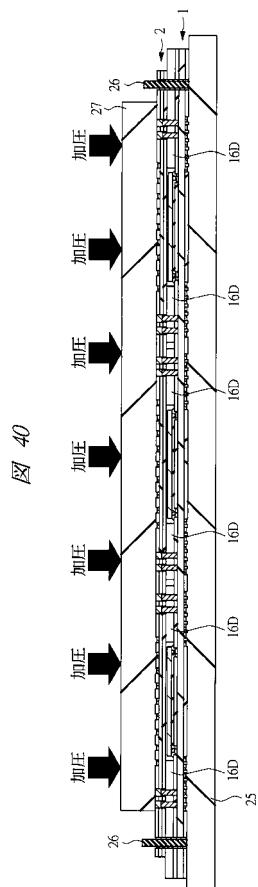

【図40】図39に続く半導体装置の製造工程中の要部断面図である。

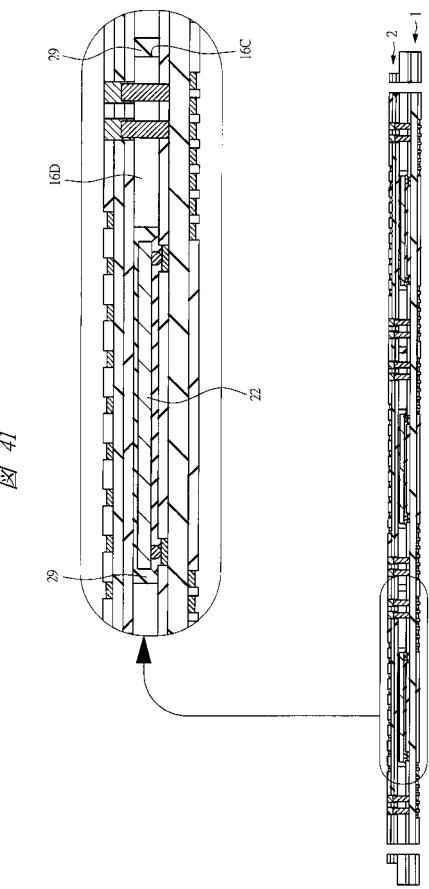

【図41】図40に続く半導体装置の製造工程中の要部断面図である。

【図42】図41に続く半導体装置の製造工程中の要部断面図である。

【図43】本発明の一実施の形態である半導体装置の製造工程中の要部断面図である。

【図44】本発明の一実施の形態である半導体装置の製造工程中の平面図である。

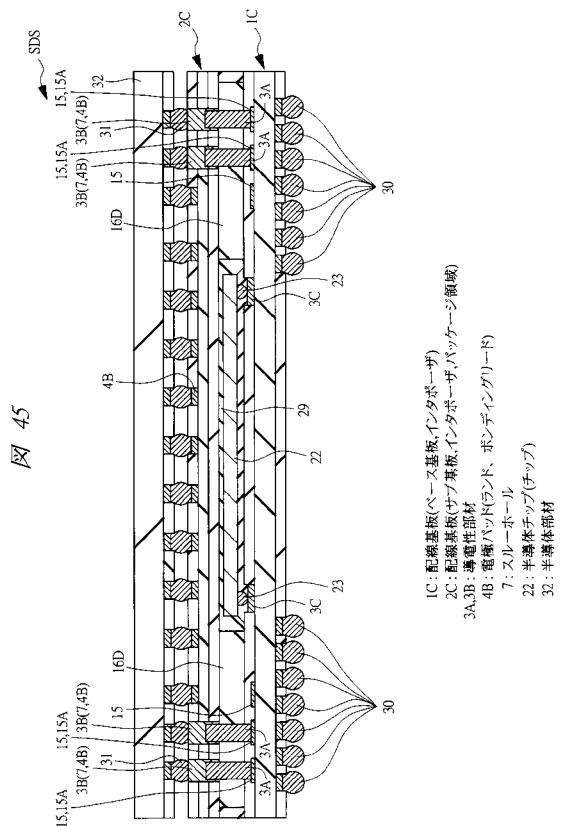

【図45】図43に続く半導体装置の製造工程中の要部断面図である。

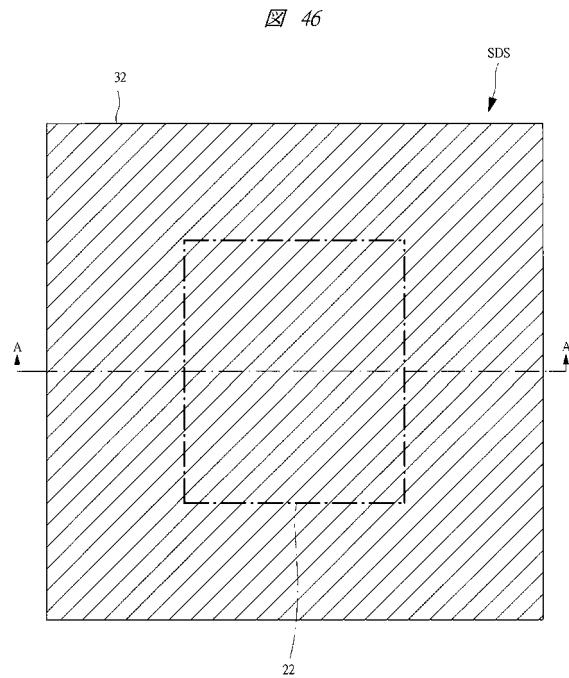

【図46】図44に続く半導体装置の製造工程中の平面図である。

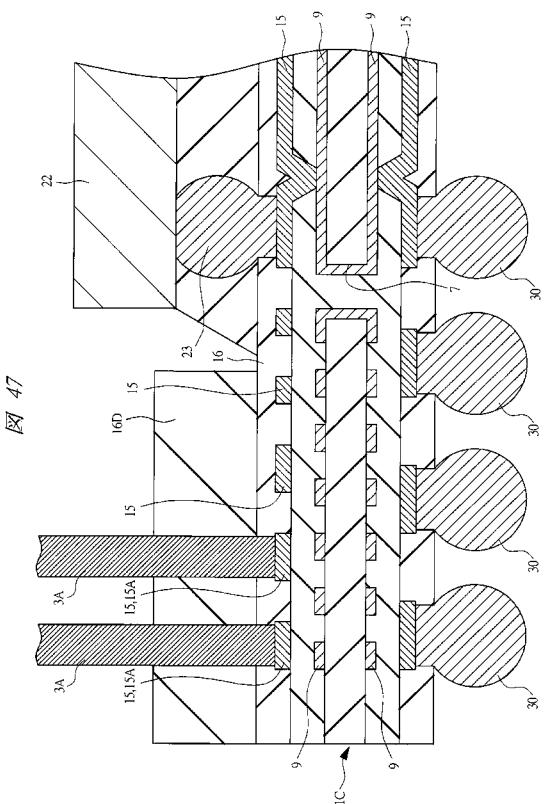

【図47】本発明の一実施の形態である半導体装置の要部断面図である。

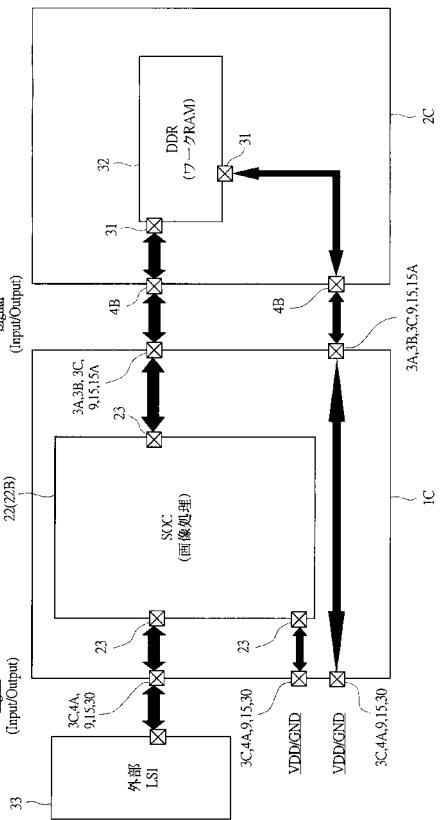

【図48】本発明の一実施の形態である半導体装置を外部実装基板に搭載した際のシステムプロック図である。

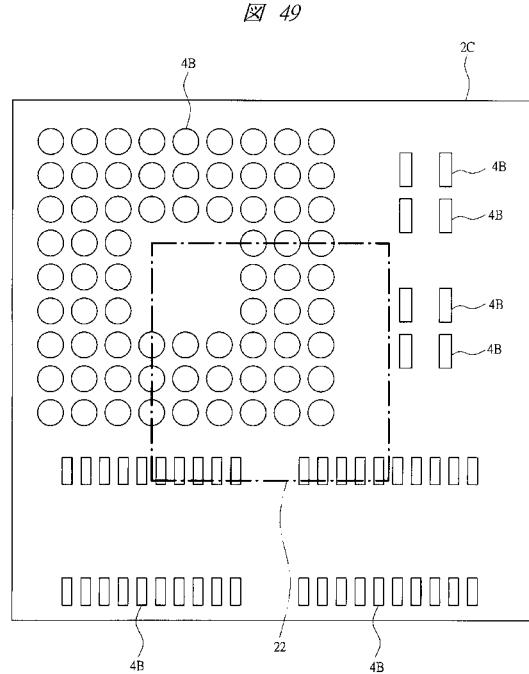

【図49】本発明の一実施の形態である半導体装置の要部平面図である。

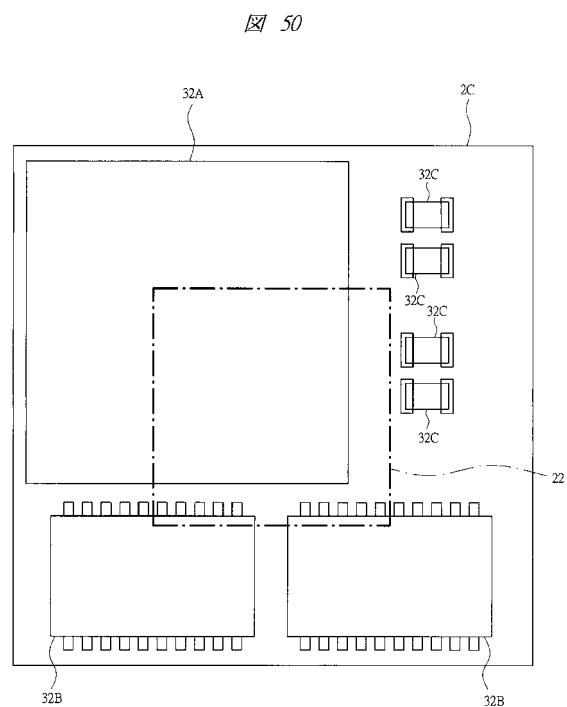

【図50】本発明の一実施の形態である半導体装置の要部平面図である。

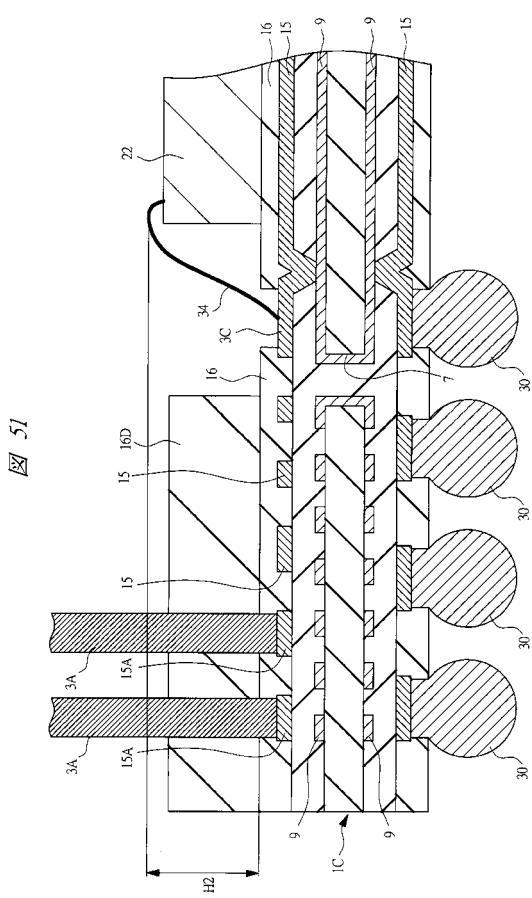

【図51】本発明の一実施の形態である半導体装置の要部断面図である。

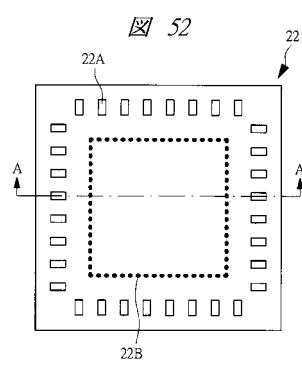

【図52】本発明の一実施の形態である半導体装置に含まれる半導体チップの上面側の平面図である。

【図53】本発明の一実施の形態である半導体装置に含まれる半導体チップの下面側の平面図である。

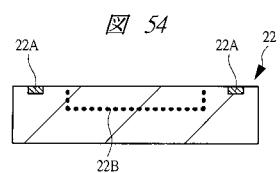

【図54】図52のA-A線における断面図である。

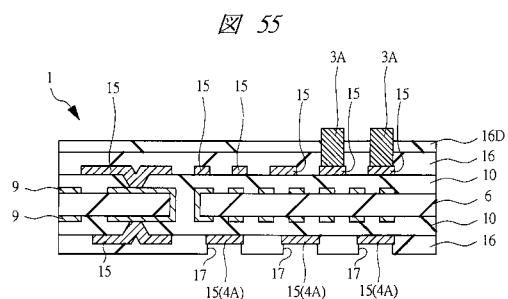

【図55】図26に続く基板母体の製造工程中の要部断面図である。

10

20

30

40

50

## 【発明を実施するための形態】

## 【0029】

[1] <<本願における記載形式、基本的用語および用語の説明>>

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

## 【0030】

また、以下の実施の形態において、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良い。

10

## 【0031】

さらに、以下の実施の形態において、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではないことは言うまでもない。また、実施例等において構成要素等について、「Aからなる」、「Aよりなる」と言うときは、特にその要素のみである旨明示した場合等を除き、それ以外の要素を排除するものでないことは言うまでもない。

## 【0032】

同様に、以下の実施の形態において、構成要素等の形状、位置関係等に言及するときは、特に明示した場合および原理的に明らかにそうでないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、上記数値および範囲についても同様である。

20

## 【0033】

また、材料等について言及するときは、特にそうでない旨明記したとき、または、原理的または状況的にそうでないときを除き、特定した材料は主要な材料であって、副次的要素、添加物、付加要素等を排除するものではない。たとえば、シリコン部材は特に明示した場合等を除き、純粋なシリコンの場合だけでなく、添加不純物、シリコンを主要な要素とする2元、3元等の合金（たとえばS i G e）等を含むものとする。

## 【0034】

また、本実施の形態を説明するための全図において同一機能を有するものは原則として同一の符号を付し、その繰り返しの説明は省略する。

30

## 【0035】

また、本実施の形態で用いる図面においては、平面図であっても図面を見易くするために部分的にハッチングを付す場合がある。

## 【0036】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。

## 【0037】

[2] <<半導体装置の説明>>

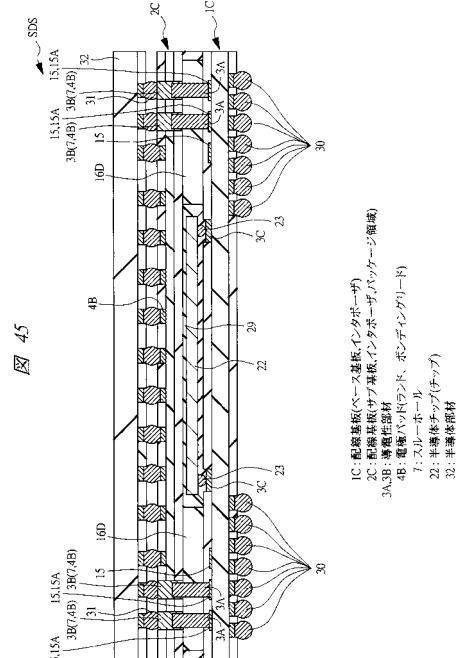

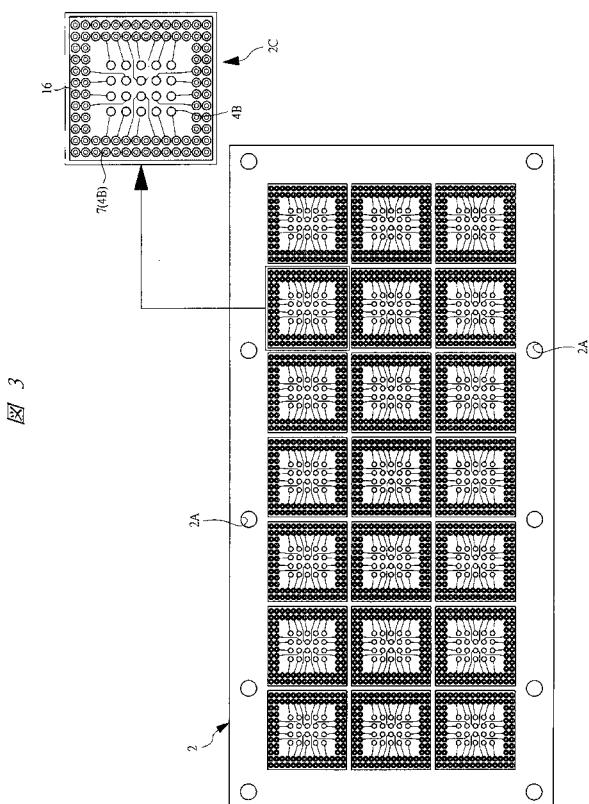

図46は完成した半導体装置（半導体システム）SDSの上面側の平面図、図45は図46のA-A線における断面図である。

## 【0038】

本発明の代表的な実施の形態における半導体装置の構成は、図45に示すように、ベースとなる配線基板（ベース基板、インタポーラ）1C上に半導体チップ（チップ）22が搭載されている。また、この配線基板1C上には、この半導体チップ22を覆うように、付属の配線基板（サブ基板、インタポーラ）2Cが配置されている。また、上段側に位置する配線基板2Cは、配線基板2Cの表裏を貫通するスルーホール内に充填された導電性部材3Bと、配線基板1Cの上面（正面、表面）に形成された導電性部材3Aとを介して、下段側の配線基板1Cと電気的に接続されている。また、下段側の配線基板1Cと上段側の配線基板2Cとの間には、半導体チップ22を封止するように、モールド樹脂（封止体）29が形成されている。また、下段側の配線基板1Cの下面（裏面、実装面）には、外部端子となる複数のバンプ電極30が形成されている。さらに、上段側の配線基板2C

40

50

上には、別に準備しておいた半導体チップ、半導体チップが搭載された半導体パッケージ、あるいはチップ部品などの半導体部材 32 が搭載されている。なお、モールド樹脂（封止体）29 の一部は、半導体チップ 22 と上段側の配線基板 2C との間にも形成される。そのため、たとえ配線基板 2C の厚さを薄くしたとしても、半導体部材 32 を搭載するときの荷重により配線基板 2C が撓む問題を抑制することができる。また、配線基板 2C 上に搭載する半導体部材 32 の種類を変えることにより、様々な半導体システムを構築することが可能である。

【0039】

[3] <<ベース基板の説明>>

次に、本実施の形態における配線基板 1C の詳細について説明する。

10

【0040】

図 1 はベースとなる複数の配線基板（パッケージ領域）1C が形成された多数個取り基板の上面（正面、表面）側の平面図、図 2 は図 1 に示す多数個取り基板の下面（裏面、実装面）側の平面図である。

【0041】

ベースとなる、1つあたりの配線基板 1C の平面形状は、図 1 に示すように、矩形状から成り、本実施の形態では四角形である。また、配線基板 1C の材料は、たとえば、ガラス繊維に樹脂を含浸させた、いわゆる、ガラス・エポキシ樹脂から成る。また、図 1 に示すように、配線基板 1C の上面（表面）における中央部には、後に搭載される半導体チップ 22 と電気的に接続される電極パッド（ボンディングリード）3C が形成されている。この電極パッド 3C は、配線基板 1C の各辺に沿って複数形成されている。また、この複数の電極パッド 3C の周囲、言い換えると、電極パッド 3C よりも配線基板 1C の周縁部側には、図 4 3 に示すように、複数の電極パッド（ランド）15A が形成されている。この電極パッド 15A は、配線基板 1C の各辺に沿って、複数列にわたって形成されており、図 4 8 のシステムブロック図に示すように、複数の電極パッド 3C とそれぞれ電気的に接続されている。また、配線基板 1C の上面には、電極パッド 15A、3C それぞれの一部（表面）を露出するように、ソルダレジスト（絶縁膜、正面用絶縁膜）16（図 2 9 も参照）が形成されている。また、このソルダレジスト 16 から露出する電極パッド 15A の表面には、図 3 2 に示すように、導電性部材 3A が形成されている。なお、本実施の形態では、この導電性部材 3A は、ポスト状（柱状）に形成されており、たとえば銅（Cu）から成る。さらに、このソルダレジスト 16 上には、導電性部材 3A の一部（先端部）を露出し、導電性部材 3A の側面を覆うように、追加でソルダレジスト（絶縁膜、補強用絶縁膜）16D が形成されている。この理由は、電極パッド 15A に形成される導電性部材 3A の高さが、配線基板 1C の上面において、複数の電極パッド 15A の内側に位置するチップ搭載領域に搭載される半導体チップの実装高さよりも大きいからである。しかしながら、導電性部材 3A の直径は、電極パッド 15A において、ソルダレジスト 16 の開口部から露出する面積に相当するため、導電性部材 3A の形状は、細長い円柱形状となる。そこで、本実施の形態では、ソルダレジスト 16D によりこの導電性部材 3A の一部を支持している。これにより、導電性部材 3A を補強することができる。

20

30

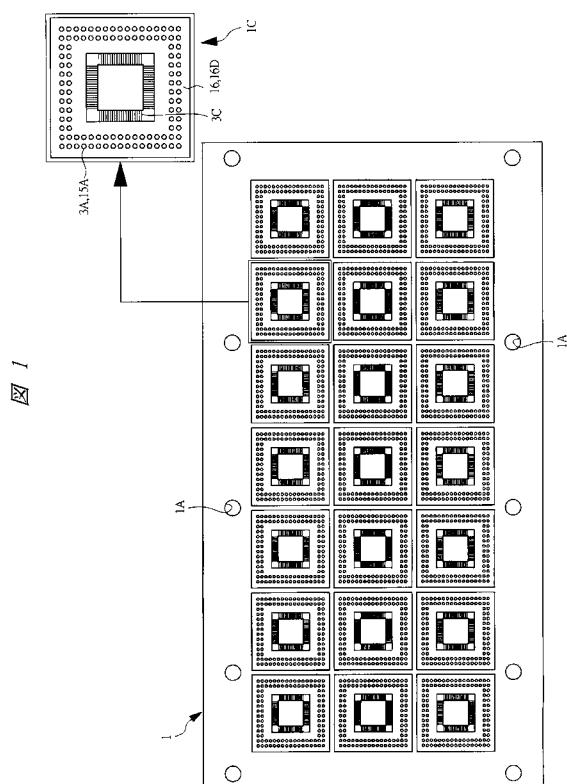

【0042】

一方、配線基板 1C の下面（実装面）には、図 2 に示すように、複数の電極パッド（ランド）4A が形成されている。また、この複数の電極パッド 4A は、配線基板 1C の各辺に沿って、複数列にわたって形成されており、図 4 8 のシステムブロック図に示すように、複数の電極パッド 3C とそれぞれ電気的に接続されている。さらに、配線基板 1C の下面には、電極パッド 4A の一部（表面）を露出するように、ソルダレジスト（絶縁膜、裏面用絶縁膜）16 が形成されている。

40

【0043】

また、配線基板 1C は、図示しないが、複数の配線層を有しており、本実施の形態では 4 層から成る。また、電極パッド（ボンディングリード）3C および電極パッド（ランド）15A のそれぞれは、1 層目（最上層）の配線層に形成された配線（配線パターン）の

50

一部から成り、電極パッド（ランド）4 Aは、4層目（最下層）の配線層に形成された配線（配線パターン）の一部から成る。

【0044】

[4] <<サブ基板の説明>>

次に、本実施の形態における配線基板2 Cの詳細について、説明する。

【0045】

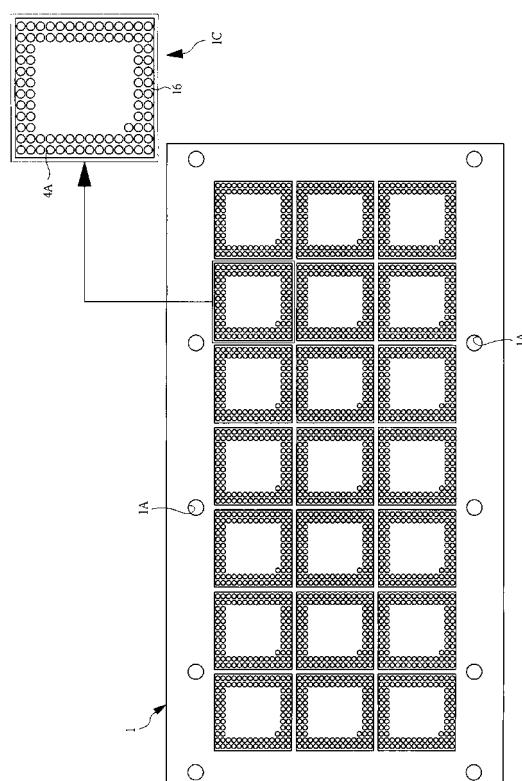

図3はサブとなる複数の配線基板（パッケージ領域）2 Cが形成された多数個取り基板の上面（正面、表面）側の平面図であり、図4は図3に示す多数個取り基板の下面（裏面、実装面）側の平面図である。

【0046】

10

1つ当たりの配線基板2 Cの平面形状は、図3に示すように、矩形状から成り、本実施の形態では四角形である。また、配線基板2 Cの材料は、たとえば、ガラス繊維に樹脂を含浸させた、いわゆるガラス・エポキシ樹脂から成る。また、配線基板2 Cの上面（表面）には、複数の電極パッド（ランド、ボンディングリード）4 Bが形成されている。なお、電極パッド4 Bは、図4 3に示すように、後に下段側の配線基板1 C上に搭載される半導体チップ2 2と平面的に重なる領域にも形成されている。また、配線基板2 Cの上面には、電極パッド4 Bの一部（表面）を露出するように、ソルダレジスト（絶縁膜、正面用絶縁膜）1 6が形成されている。そのため、後の工程において、この付属の配線基板2 Cを、半導体チップ2 2が搭載されたベースとなる配線基板1 C上に配置することで、ベースとなる配線基板1 Cとは外形サイズが異なる半導体部材（半導体チップ、半導体パッケージ、あるいはチップ部品）や、半導体チップ2 2と平面的に重なる領域に形成された外部端子を有する半導体部材を、半導体チップ2 2上に搭載することができるようになる。

20

【0047】

また、配線基板2 Cの下面には、ソルダレジスト（絶縁膜、裏面用絶縁膜）1 6（図2 9参照）が形成されている。

【0048】

30

また、配線基板2 Cは、図示しないが、複数の配線層を有しており、本実施の形態では2層から成る。また、電極パッド（ランド）4 Bは、1層目（最上層）の配線層に形成された配線（配線パターン）の一部から成る。配線基板2 Cには、表裏を貫通するスルーホール7が形成されており、このスルーホール7の側壁に2層目（最下層）の配線層に形成された配線9が露出している（図3 1参照）。詳細は後述するが、前述のベース基板である配線基板1 Cに形成された導電性部材3 Aは、その配線基板2 Cに形成されたスルーホール7内に挿入され、さらにスルーホール7内が導電性部材3 Bで充填されることにより、導電性部材3 Aは、導電性部材3 Bを介して、スルーホール7の側壁に露出した配線9と電気的に接続される。それにより、配線基板1 Cと配線基板2 Cとが電気的に接続される。また、ベース基板である配線基板1 Cに形成された導電性部材3 Aと平面的に重なる位置に形成された電極パッド4 Bは、図3 9および図4 3に示すように、スルーホール7の内部に導電性部材3 Bを充填することで形成される。この時、本実施の形態では、サブ基板である配線基板2 Cの上面と同じ高さ、または上面から突出するように、スルーホール7内に導電性部材3 Bを充填している。これにより、導電性部材3 Aの上部も、電極パッドとして使用することができ、配線基板2 Cに搭載できる半導体部材の汎用性を広げることができる。

40

【0049】

ここで、図4 8のシステムブロック図に示すように、本実施の形態では、配線基板1 C上に搭載される半導体チップ2 2が、外部LSI3 3からの信号に基づいて、配線基板2 C上に搭載される半導体部材3 2を制御する。また、半導体部材3 2を動作させるために必要とする電源電位および基準電位も、配線基板1 Cを介して外部LSI3 3から半導体部材3 2に供給する。そのため、本実施の形態では、配線層の数が配線基板2 Cの配線層の数よりも多い配線基板1 Cを使用している。

【0050】

50

## [ 5 ] &lt;&lt; 半導体チップの説明 &gt;&gt;

次に、配線基板 1 C 上に搭載される半導体チップ 2 2 の詳細について、説明する。

## 【 0 0 5 1 】

図 5 2 は配線基板 1 C 上に搭載される半導体チップ 2 2 の上面（表面、正面）側における平面図、図 5 3 は図 5 2 に示す上面とは反対側の下面（裏面）側の平面図、図 5 4 は図 5 2 の A - A 線における断面図である。

## 【 0 0 5 2 】

半導体チップ 2 2 の平面形状は、図 5 2 に示すように、矩形状から成り、本実施の形態では四角形である。また、半導体チップ 2 2 の材料は、たとえばシリコン（Si）から成る。また、半導体チップ 2 2 の上面（正面）には、半導体チップ 2 2 の各辺に沿って、複数の電極パッド 2 2 A が形成されている。また、半導体チップ 2 2 の中央部には、回路素子（半導体素子）2 2 B が形成されており、図示しないが、この回路素子 2 2 B の周囲に形成された複数の電極パッド 2 2 A は、半導体チップ 2 2 内に形成された配線を介してこの回路素子 2 2 B と電気的に接続されている。また、この回路素子は、図 5 4 に示すように、半導体チップ 2 2 の上面側に形成されている。そして、本実施の形態における半導体チップ 2 2 は、たとえばコントローラ系の半導体チップであり、この回路素子 2 2 B は、図 4 8 に示すように、この回路素子 2 2 B と、完成した半導体装置（半導体システム）SDS の外部に設けられた外部 LSI 3 3 との間で信号の入出力を行うための外部インターフェース、およびこの回路素子 2 2 B と、この半導体装置の内部に設けられる半導体部材 3 2 との間で信号の入出力を行うための内部インターフェースを有している。

10

20

30

40

50

## 【 0 0 5 3 】

一方、半導体チップ 2 2 の上面とは反対側の下面（裏面）の平面形状は、図 5 3 に示すように、矩形状から成り、本実施の形態では、上面側と同様に四角形である。

## 【 0 0 5 4 】

## [ 6 ] &lt;&lt; 半導体装置（半導体システム）SDS の製造方法についての説明 &gt;&gt;

次に、本実施の形態の半導体装置（半導体システム）SDS の製造方法について、以下に説明する。なお、前述のように、本実施の形態の半導体装置は、MCM 型の一種である POP (Package On Package) 型の半導体装置である。また、図 1 ~ 図 4 は、この POP 型の半導体装置の製造に用いられる配線基板の平面図であり、図 1 および図 2 は、それぞれ下段の配線基板 1 C となる基板母体 1 の正面側および裏面側の平面図であり、図 3 および図 4 は、それぞれ配線基板 1 C に積層される上段の配線基板 2 C となる基板母体 2 の正面側および裏面側の平面図である。また、図 1 ~ 図 4 では、1 つの配線基板 1 C もしくは配線基板 2 C となる領域の正面側もしくは裏面側を拡大して示している。

30

## 【 0 0 5 5 】

図 1 ~ 図 4 に示す基板母体 1、2 は、MAP (Mold Array Package) 方式の基板母体となっており、配線基板 1 C もしくは配線基板 2 C となる領域が複数配列され、1 枚の基板母体 1、2 から複数の配線基板 1 C もしくは配線基板 2 C を取得できる構造となっている。基板母体 1、2 には、それぞれガイドホール 1 A およびガイドホール 2 A が複数設けられており、詳細は後述するが、基板母体 1 の正面と基板母体 2 の裏面とを対向させ、対応するガイドホール 1 A とガイドホール 2 A とを貫通するようにガイドを通すことにより、配線基板 1 C となる領域と配線基板 2 C となる領域とが、それぞれ対応するもの同士で対向する状態となる。

## 【 0 0 5 6 】

基板母体 1 (各配線基板 1 C となる領域) の正面側には、金属製の導電性部材 3 A が複数形成されている。対応する配線基板 1 C となる領域と配線基板 2 C となる領域とを平面で重ね合わせた時に、これら導電性部材 3 A は、基板母体 2 (各配線基板 2 C となる領域) を貫通するように形成されたスルーホール 7 (電極パッド 4 B) とそれ 1 対 1 で対応した位置に配置されている。これら導電性部材 3 A とスルーホール 7 (電極パッド 4 B) とを対応するもの同士で電気的に接続することにより、配線基板 1 C と配線基板 2 C とが電気的に接続されることになるが、詳細については、本実施の形態の半導体装置の製造

工程を説明する中で併せて説明する。また、基板母体1の正面側には、半導体チップ搭載用の電極パッド(ポンディンググリード)3Cが形成されている。

【0057】

基板母体1の裏面には、本実施の形態の半導体装置を外部に電気的に接続するための電極パッド4Aが形成され、基板母体2の正面には、半導体チップあるいはチップ部品搭載用の電極パッド4Bが形成されている。また、基板母体1、2中には、配線基板1Cとなる領域毎あるいは配線基板2Cとなる領域毎に配線層が形成されており、この配線層によって、導電性部材3Aと電極パッド4Aとが電気的に接続され、導電性部材3Bと電極パッド4Bとが電気的に接続されている。

【0058】

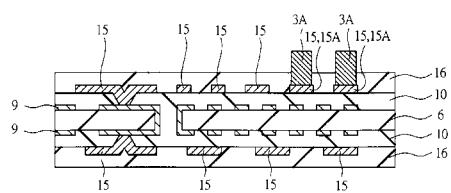

次に、上記基板母体1の製造工程について、図5～図31を用いて説明する。図5～図31では、基板母体1の製造過程における要部断面を示している。

【0059】

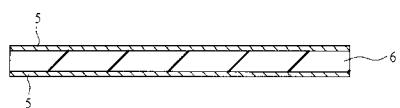

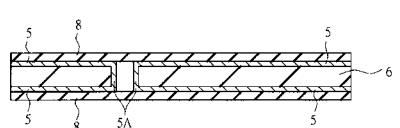

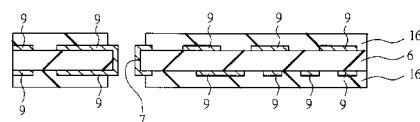

まず、正面および裏面の両面に銅薄膜5が成膜された絶縁性のコア材6を用意する(図5参照)。その材質としては、ガラス・エポキシ樹脂、BTRレジンあるいはアラミド不織布材等を例示することができる。

【0060】

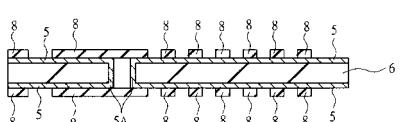

次いで、このコア材6の正面と裏面とを貫通するスルーホール7をドリルまたはレーザー加工により形成する(図6参照)。次いで、めっき法により、スルーホール7の壁面に銅膜5Aを成膜し、正面側の銅薄膜5と裏面側の銅薄膜5とをスルーホール7内の銅膜5Aによって電気的に接続する(図7参照)。次いで、ドライフィルムからなるフォトレジスト膜8をコア材6の正面および裏面の両面に貼付(図8参照)した後に、フォトリソグラフィ技術により、このフォトレジスト膜8をパターニングする(図9参照)。次いで、残ったフォトレジスト膜8をマスクとしてコア材6の両面の銅薄膜5をエッチングすることにより、銅薄膜5をパターニングする。ここまで工程により、コア材6の両面に配線9からなる1層目の配線層を形成することができる(図10参照)。また、コア材6の両面の配線層は、スルーホール7内の銅膜5Aを介して電気的に接続された構造とすることができます。

10

20

【0061】

次に、フォトレジスト膜8を剥離(図11参照)した後、コア材6の両面に絶縁層10を堆積する。また、この絶縁層10により、スルーホール7を埋め込む(図12参照)。絶縁層10の材質としては、コア材6と同様のガラス・エポキシ樹脂、BTRレジンあるいはアラミド不織布材等を例示することができる。

30

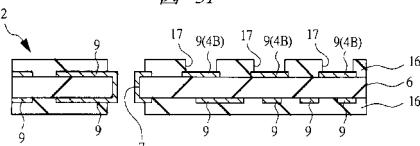

【0062】

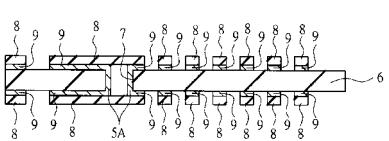

次に、レーザー加工により、コア材6の両面の絶縁層10に一部の配線9に達する開口部11を形成する(図13参照)。次いで、無電解めっき法により、コア材6の両面に銅膜12を成膜する(図14参照)。この時、銅膜12は、開口部11内にも成膜され、開口部11の底部にて銅膜12と配線9とが接続される。次いで、ドライフィルムからなるフォトレジスト膜13をコア材6の正面および裏面の両面に貼付(図15参照)した後に、フォトリソグラフィ技術により、このフォトレジスト膜13をパターニングする(図16参照)。次いで、残ったフォトレジスト膜13をマスクとし、銅膜12をシード層とした電解めっき法により、銅膜12上に選択的に銅膜14を成長させる(図17参照)。次いで、フォトレジスト膜13を剥離(図18参照)した後、ドライフィルムからなるフォトレジスト膜18をコア材6の正面および裏面の両面に貼付する(図19参照)。次いで、フォトリソグラフィ技術により、正面側のフォトレジスト膜18をパターニングし、正面側の銅膜14上のフォトレジスト膜18に選択的に銅膜14に達する開口部19を形成する(図20参照)。次いで、残ったフォトレジスト膜18をマスクとし、開口部19下の銅膜14をシード層としためっき法により、その銅膜14上に選択的に銅膜を成長させることにより、図1を用いて説明した導電性部材3Aを形成する(図21参照)。

40

【0063】

50

次に、フォトレジスト膜18を剥離(図22参照)した後、無電解エッティング法により銅膜12をエッティングし、残った銅膜12および銅膜14から配線15を形成する。なお、配線15の一部は、前述の電極パッド15Aもしくは電極パッド15Bとなる。ここまで工程により、コア材6の両面に配線15からなる2層目の配線層を形成することができる(図23参照)。配線15の一部は、配線9と接続した構造となる。

#### 【0064】

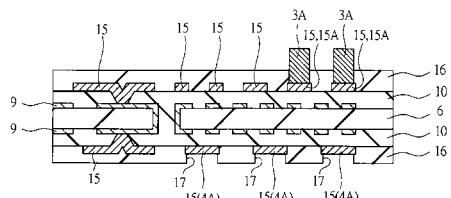

次に、コア材6の両面にソルダレジスト16を印刷する(図24参照)。次いで、そのソルダレジスト16をフォトリソグラフィ技術によりパターニングし、ソルダレジスト16に配線15の一部に達する開口部17を形成する(図25参照)。ここで、コア材6の正面側において、開口部17の底部に露出した配線15の一部は、前述の基板母体1の半導体チップ搭載用の電極パッド3Cとなる(図25での図示は省略)。また、コア材6の裏面側において、開口部17の底部に露出した配線15は、前述の基板母体1の電極パッド4Aとなる。

10

#### 【0065】

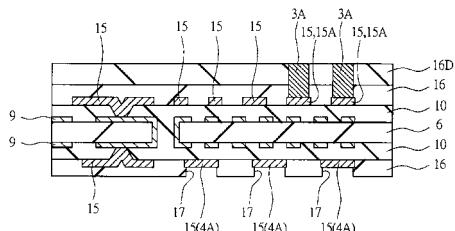

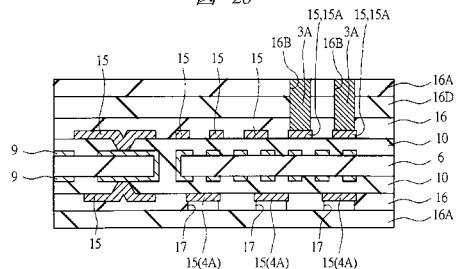

次に、コア材6の正面側にソルダレジスト16Dを印刷する(図26参照)。このソルダレジスト16Dは、表面がポスト状の導電性部材3Aの頂部と揃うような厚さとする。また、ソルダレジスト16Dの膜厚は、後の工程で配線基板1Cに搭載される半導体チップ22よりも厚くなるようにする。

#### 【0066】

次いで、そのソルダレジスト16Dをフォトリソグラフィ技術によりパターニングし、後の工程で半導体チップ22が搭載される領域のソルダレジスト16Dを除去することで、図32に示すような基板母体1を製造する。残ったソルダレジスト16Dは、平面で半導体チップ22が搭載される領域を囲むパターンとなり、さらに、後の工程で半導体チップ22が搭載された領域へモールド樹脂(封止体)29を注入するための注入経路(詳細は図41を用いて後述する)が設けられる。このように、ポスト状の導電性部材3Aは、先端部を除いて周囲がソルダレジスト16ばかりでなく、ソルダレジスト16Dによっても覆われ、封止されている。そのため、導電性部材3Aの高さが高くなても、ソルダレジスト16、16Dが周囲を補強する構造となり、導電性部材3Aを倒れ難くすることができる。

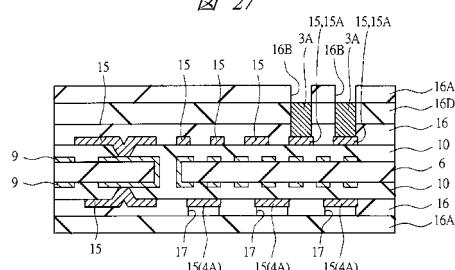

20

#### 【0067】

次に、ドライフィルムからなるフォトレジスト膜16Aをコア材6の正面および裏面の両面に貼付した後に、フォトリソグラフィ技術により、このフォトレジスト膜16Aをパターニングし、導電性部材3A上のフォトレジスト膜16Aに開口部16Bを形成する(図27参照)。次いで、残ったフォトレジスト膜16Aをマスクとし、導電性部材3A(銅膜)をシード層とした電解めっき法により、導電性部材3A上の開口部16B内に選択的に銅膜を成長させ、導電性部材3Aを高くする(図28参照)。次いで、フォトレジスト膜16Aを剥離する。

30

#### 【0068】

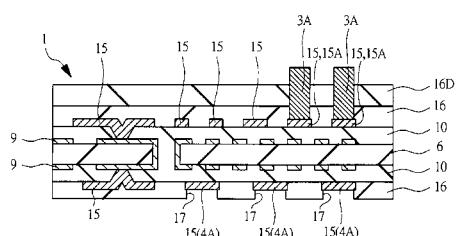

次いで、ドリル加工により、コア材6を貫通する前述のガイドホール1A、2A(図1および図2参照)を形成し、図29に示すような基板母体1を製造する。この時、ソルダレジスト16の表面からの導電性部材3Aの突出高さは、配線基板1Cに搭載される半導体チップ22がバンプ電極を用いて配線基板1Cに接合(フリップチップ接続)される場合には、配線基板1Cに搭載時の半導体チップ22の高さ(ソルダレジスト16の表面から半導体チップ22の裏面までの高さ)より高くなるようにする。また、導電性部材3Aのソルダレジスト16Dからの突出量(突出高さ)は、配線基板2C(後述する基板母体2)の厚さより小さくする。

40

#### 【0069】

上記のような工程で製造される基板母体1であるが、配線基板1Cとなる基板母体1を製造する際に絶縁層10および配線15を形成する工程を繰り返してさらに多層構造を形成したりしてもよい。

50

## 【0070】

また、前述のソルダレジスト16Dを印刷し、そのソルダレジスト16Dをフォトリソグラフィ技術によりパターニングして、後の工程で半導体チップ22が搭載される領域のソルダレジスト16Dを除去した工程(図26参照)の後、プラスト処理によってソルダレジスト16Dを薄くし、ソルダレジスト16Dの表面から導電性部材3Aを突出させてよい(図55参照)。ただし、プラスト処理後のソルダレジスト16Dの厚さが、後の工程で配線基板1Cに搭載される半導体チップ22よりも厚くなるように、予めソルダレジスト16Dは厚く印刷しておく。

## 【0071】

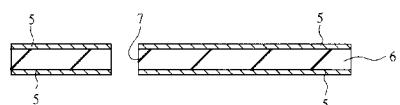

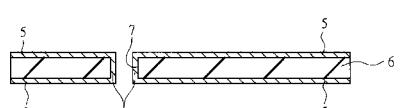

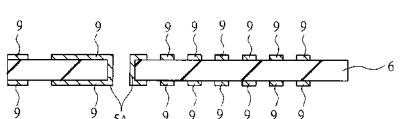

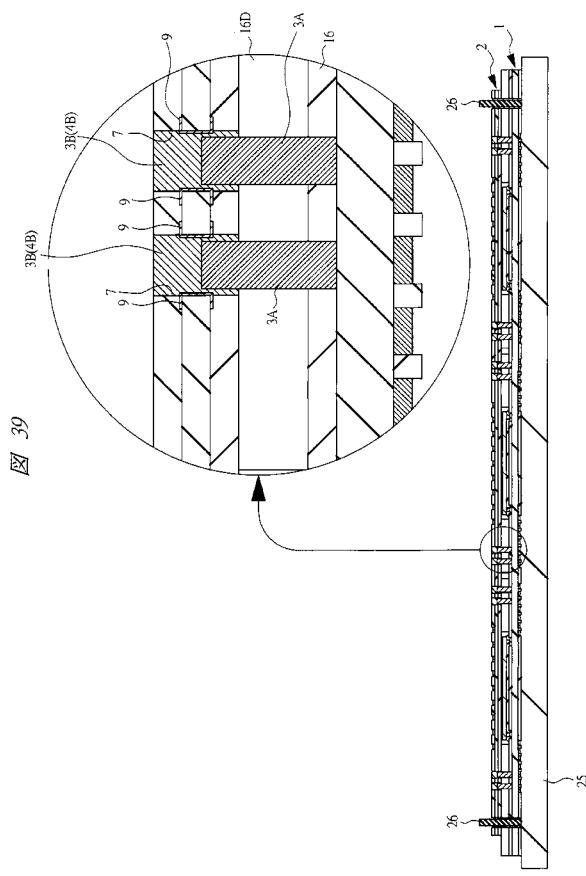

次に、上記基板母体2の製造工程について、図30および図31を用いて説明する。図30および図31では、基板母体2の製造過程における要部断面を示している。

## 【0072】

基板母体2の製造工程は、図5～図10を用いて前述した基板母体1の製造工程における、配線9(1層目の配線層)を形成する工程までは同様である。その後、コア材6の両面にソルダレジスト16を印刷する(図30参照)。この時、スルーホール7上にはソルダレジスト16を印刷しないようにし、スルーホール7の側壁の配線9を露出させる。

## 【0073】

次に、そのソルダレジスト16をフォトリソグラフィ技術によりパターニングし、ソルダレジスト16に配線9の一部に達する開口部17を形成し、基板母体2を製造する(図31参照)。ここで、コア材6の正面側において、開口部17の底部に露出した配線9は、電極パッド(ランド、ボンディングリード)4Bとなる。

## 【0074】

次に、上記のような工程を経て製造された基板母体1、2を用いて、本実施の形態のP0P型の半導体装置を製造する工程について、図32～図46を用いて説明する。

## 【0075】

まず、基板母体1を用意する(図32参照)。次いで、基板母体1の正面における、各配線基板1Cとなる領域に半導体チップ22を搭載する(図33参照)。ここで、図34は、隣接する2つの配線基板1Cとなる領域1Bを拡大して図示した平面図である。図33および図34に示す例では、半導体チップ22は、表面に形成されたボンディングパッド(図示は省略)上にバンプ電極(突起電極)23が形成され、このバンプ電極23が電極パッド3Cと接合されることによって各配線基板1Cとなる領域に搭載される。この時、半導体チップ22は、素子の形成された表面側が基板母体1と対向して搭載されることになる。

## 【0076】

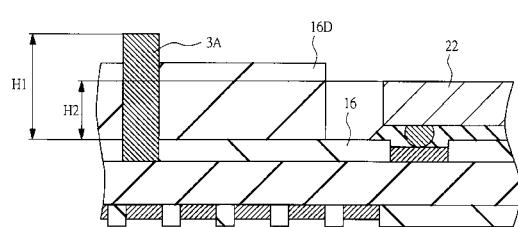

基板母体1、2を製造する工程を説明する中でも述べたが、図35に示すように、ソルダレジスト16Dの表面からの導電性部材3A突出高さH1は、ベース基板となる領域に搭載された半導体チップ22の高さ(半導体チップ22の搭載領域におけるソルダレジスト16の表面から半導体チップ22の裏面までの高さ)H2より高くなっている。

## 【0077】

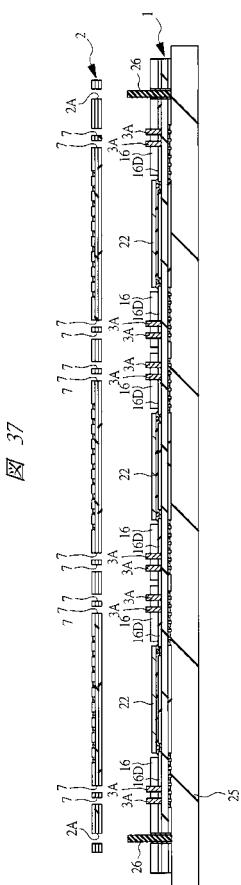

次に、半導体チップ22と基板母体1との間にアンダーフィル樹脂24を塗布(図36参照)した後、加熱圧着用のステージ25に基板母体1を載置する(図37参照)。この時、搭載された基板母体1は、裏面側がステージ25と対向し、ステージ25に備え付けられたガイドピン26を基板母体1のガイドホール1A(図1および図2参照)に通すことで、基板母体1のステージ25上での位置決めをすることができる。次いで、基板母体2を用意する(図37参照)。

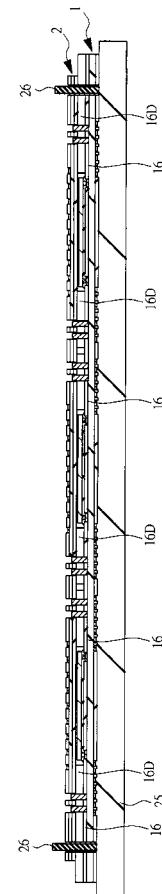

## 【0078】

次に、基板母体2をステージ25に載置する(図38参照)。この時、基板母体2は、導電性部材3Bが形成された裏面側が基板母体1と対向させられ、基板母体2のガイドホール2Aにガイドピン26が通されることで、ステージ25上での位置が決定され、基板母体1におけるソルダレジスト16Dから突出した複数の導電性部材3Aが、各々対応す

る基板母体 2 におけるスルーホール 7 に挿入された状態となる。さらに、前述のように、導電性部材 3 A のソルダレジスト 16 D からの突出量（突出高さ）は、配線基板 2 C（後述する基板母体 2）の厚さより小さくしてあることから、複数の導電性部材 3 A の先端は、基板母体 2 の正面から突出せず、スルーホール 7 内に位置することになる。次の工程でスルーホール 7 内に導電性部材を充填するが、導電性部材 3 A の先端が基板母体 2 の正面から突出していないことから、スルーホール 7 内に充填された導電性部材を半導体チップあるいはチップ部品搭載用の電極パッド（ランド）4 B として用いることが可能となる。それにより、配線基板 2 C の正面において、半導体チップあるいはチップ部品搭載用の領域を広く確保することが可能となる。また、基板母体 1、2 のステージ 25 上での位置が決定されると、基板母体 1 に区画された複数の配線基板 1 C となる領域は、それぞれが対応する基板母体 2 に区画された複数の配線基板 2 C となる領域と 1 対 1 で対向する状態となる。また、基板母体 2 がステージ 25 に載置されると、基板母体 1 におけるポスト状の導電性部材 3 A の周囲を覆うソルダレジスト 16 D の表面が、基板母体 2 の裏面と接する状態となる。

10

#### 【0079】

次に、基板母体 2 のスルーホール 7 に導電性部材 3 B を充填する（図 39 参照）。本実施の形態において、この導電性部材 3 B としては、はんだ（鉛フリーはんだを含む）もしくは銀（Ag）、銅（Cu）、またはこれらの合金（Ag - Cu）などの導電性ペーストを用いることを例示することができる。なお、図 39 では、基板母体 2 のスルーホール 7 付近の拡大断面も併せて示している。前述したように、この導電性部材 3 B をスルーホール 7 に充填することにより、ベース基板である配線基板 1 C に形成された導電性部材 3 A と平面的に重なる位置となる電極パッド 4 B を形成することができる。すなわち、導電性部材 3 A の上部も、電極パッドとして使用することができるようになり、配線基板 2 C に搭載できる半導体部材の汎用性を広げることができる。

20

#### 【0080】

次に、加熱ツール 27 を用い、基板母体 2 を裏面側より加熱および加圧することにより、導電性部材 3 A と導電性部材 3 B とを熱圧着（接合）し、これらを電気的に接続する（図 40 参照）。

20

#### 【0081】

次に、基板母体 1 と基板母体 2 との間にモールド樹脂 29 を注入し、基板母体 1 と基板母体 2 との間を樹脂封止する封止体を形成する（図 41 参照）。なお、図 41 では、1 つの半導体チップ 22 の付近の拡大断面も併せて図示している。モールド樹脂 29 は、前述のソルダレジスト 16 D に設けられ注入経路 16 C を経て半導体チップ 22 が搭載された領域へ注入および充填される。先に説明したように、モールド樹脂 29 の一部は、半導体チップ 22 と基板母体 2（配線基板 2 C）との間に形成されるので、たとえ基板母体 2（配線基板 2 C）の厚さを薄くしたとしても、後の工程で半導体部材 32（詳細は図 45 および図 46 を用いて後述する）を搭載する時の荷重により基板母体 2（配線基板 2 C）が撓む問題を抑制することができる。また、前述のように、導電性部材 3 A の周囲を覆うソルダレジスト 16 D が基板母体 2（配線基板 2 C）の裏面と接しているので、仮に半導体チップ 22 と基板母体 2（配線基板 2 C）との間にモールド樹脂 29 が形成されないなくても、基板母体 2（配線基板 2 C）の裏面と接したモールド樹脂 29 が基板母体 2（配線基板 2 C）を支持する構成となる。この構成によっても、基板母体 2（配線基板 2 C）を撓み難くすることができる。

30

#### 【0082】

次いで、モールド金型から樹脂封止された基板母体 1、2 を取り出し、はみ出したモールド樹脂 29 を除去し成形する。

40

#### 【0083】

次に、基板母体 1 の電極パッド 4 A の各々上にはんだボールを配置し、リフロー処理を施すことによりはんだボールを電極パッド 4 A と接合し、バンプ電極（外部端子）30 を形成する（図 42 参照）。

50

## 【0084】

次に、配線基板1Cとなる領域および配線基板2Cとなる領域の平面外形に沿って、基板母体1、2を切断し、個々の配線基板1Cおよび配線基板2Cの組に個片化する(図43参照)。ここで、図44は、個々の配線基板1Cおよび配線基板2Cの組に個片化後の平面図である。この図44に示すように、本実施の形態では、基板母体1、2は、一括して切断されることから、配線基板1Cおよび配線基板2Cの平面外形寸法は等しくなる。また、本実施の形態では、導電性部材3Bと電気的に接続する電極パッド4Bは、平面で半導体チップ22と重なる位置にも配置されている。すなわち、配線基板2Cにおいては、平面で下段の半導体チップ22と重なる位置でもチップあるいはチップ部品等を搭載することが可能となる。それにより、配線基板1Cおよび配線基板2Cの外形サイズを大型化することなく、配線基板2Cに配置する電極パッド4B(スルーホール7に導電性部材3Bを充填して形成した電極パッド4Bを含む)の数を増やすことが可能となる。また、電極パッド4Bの数が同じであるならば、配線基板1Cおよび配線基板2Cの外形サイズを小型化することができるので、本実施の形態の半導体装置(半導体システム)SDSについても小型化することが可能となる。

10

## 【0085】

次に、外部接続用の電極としてバンプ電極31が形成された半導体部材32を用意する。次いで、そのバンプ電極31を配線基板2Cの電極パッド4Bに接続することで半導体部材32を配線基板2Cに搭載および電気的に接続し、本実施の形態の半導体装置(半導体システム)SDSを製造する。図46は、半導体部材32を配線基板2Cに搭載した時点での平面図である。本実施の形態によれば、平面で下段の半導体チップ22と重なる領域でも、上段の半導体部材32は配置することができる。図46では、半導体部材32の平面外形が配線基板1Cおよび配線基板2Cの平面外形とほぼ同一である場合を図示しているが、半導体部材32の平面外形の方が小さくなっていてもよい。

20

## 【0086】

ここで、図47は、本実施の形態のPOP型の半導体装置の要部断面図であり、図48は、本実施の形態のPOP型の半導体装置をマザーボード等の外部実装基板に搭載した際のシステムブロック図の一例である。

## 【0087】

下層の配線基板1Cに搭載された半導体チップ22は、SOC(System On Chip)型のチップであって画像処理等の論理処理を行い、上層の配線基板2Cに搭載された半導体部材32は、メモリチップであって下段の半導体チップ22が行う論理処理の際にワークRAMとして用いられることを例示できる。半導体チップ22と半導体部材32との間では、バンプ電極23、配線9、15、および導電性部材3A、3Bを介して信号の授受が行われる。半導体チップ22と外部LSI33との間では、バンプ電極23、配線9、15、およびバンプ電極30を介して信号の授受が行われる。半導体チップ22への電源電位(VDD)および基準電位(GND)の供給は、バンプ電極30および配線9、15を介して行われ、半導体部材32への電源電位(VDD)および基準電位(GND)の供給は、バンプ電極30、導電性部材3A、3B、電極パッド4Bおよび配線9、15を介し、半導体チップ22は介さずに行われる。

30

## 【0088】

また、配線基板2Cへは、複数の半導体チップ(マイコンチップおよびメモリチップ等)あるいはチップ部品(抵抗、コンデンサおよびインダクタ等)等を搭載することも可能である。図49は、複数の半導体チップおよびチップ部品を搭載可能とした配線基板2Cの平面図である。配線基板2Cに設けられたパッド電極4Bは、搭載される半導体チップおよびチップ部品に合わせた平面形状で形成されている。このような場合でも、パッド電極4Bは、下段の半導体チップ22と重なる位置に配置することが可能である。なお、配線基板2Cの上面に形成された各パッド電極4Bは、配線基板2Cの上面、下面、または上下面に形成された配線(図示は省略)を介して、配線基板2Cに形成されたスルーホール7内に充填される導電性部材3Bと導通を図っている。また、この配線基板2Cが、た

40

50

とえば3層以上の配線層を有している場合は、さらに内層の配線層に形成された配線を使用することで、複数の半導体部材32との導通を容易に図ることができる。図50は、半導体チップ32A、32Bおよびチップ部品32Cを配線基板2Cに搭載した時点での平面図である。本実施の形態によれば、平面で下段の半導体チップ22と重なる領域でも、上段の半導体チップ32A、32Bおよびチップ部品32Cは配置することができる。すなわち、本実施の形態によれば、上層と下層とで、半導体チップ22、32A、32B、半導体部材32およびチップ部品32Cの組み合わせを大幅に向上することが可能となる。

#### 【0089】

上記の本実施の形態では、配線基板1Cに搭載される半導体チップ22がバンプ電極23を介して実装される場合について説明したが、図51に示すように、ボンディングワイヤ34によって実装される構造であってもよい。この場合、半導体チップ22は、裏面が配線基板1Cの正面と対向するように配線基板1Cに搭載される。上記の実施の形態では、半導体チップ22の電極パッド(図示は省略)上に形成されたバンプ電極23と電気的に接続される配線基板(ベース基板)1Cの電極パッド3Cが、配線基板(ベース基板)1Cの正面において、半導体チップ22と平面的に重なる領域に形成されていたが、図51に示すように、電極パッド3Cは、配線基板(ベース基板)1Cにおいて、半導体チップ22が搭載される領域の周囲に形成される。このようなボンディングワイヤ34を用いる場合には、半導体チップ22上にボンディングワイヤ34のループが形成されることから、ポスト状の導電性部材3Aは、半導体チップ22の厚さ(ソルダレジスト16の表面からボンディングワイヤ34の最高位置までの高さ)H2より高く延在するように形成することが好みしい。

#### 【0090】

上記の本実施の形態によれば、配線基板1Cに搭載された半導体チップ22(バンプ電極23)により実装されている場合には裏面であり、ボンディングワイヤ34により実装されている場合には正面)と配線基板2Cとの間にモールド樹脂29が配置された構造となる(図45参照)。それにより、本実施の形態のPOP型の半導体装置を実装した際に、配線基板2Cが撓んでしまうことを抑制することができる。すなわち、本実施の形態の半導体装置の歩留まりを向上することができ、信頼性を向上することができる。

#### 【0091】

また、上記の本実施の形態によれば、予め基板母体1、2に設けたガイドホール1A、2Aを用いて基板母体1A、2Aの位置を合わせ、基板母体1側に形成された複数の導電性部材3Aを、それぞれ対応する基板母体2側のスルーホール7に挿入する(図38参照)、導電性部材3Aと対応するスルーホール7との位置合わせを容易に行うことができる。また、このように導電性部材3Aと対応するスルーホール7との位置合わせした状況下において、導電性部材3Bをスルーホール7に充填し、熱圧着により導電性部材3Aと導電性部材3Bとを接合するので、配線基板1C(基板母体1)と配線基板2C(基板母体2)との電気的接続(接合)を容易に行うことができる。

#### 【0092】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【0093】

たとえば、前記実施の形態においては、基板母体1の製造工程中にポスト状の導電性部材も形成する場合について説明したが、基板母体1を製造した後に、製造された基板母体1に対してポスト状の導電性部材を形成してもよい。

#### 【0094】

また、前記実施の形態では、下段側に位置し、ベースとなる配線基板1Cにポスト状の導電性部材3Aを形成し、この配線基板1C上に配置される付属の配線基板2Cにスルーホール7を形成することについて説明したが、ベースとなる配線基板1Cにスルーホール

10

20

30

40

50

7を形成し、付属の配線基板2Cにポスト状の導電性部材3Aを形成し、これらを接続する構成としてもよい。しかしながら、上記したように、ベースとなる下段側の配線基板1Cには、外部機器と信号の入出を行なうための外部端子(バンプ電極)30が形成されており、配線基板1Cに形成された配線(図示は省略)を介して、この外部端子と配線基板1Cの上面に形成された電極パッドとを電気的に接続している。そのため、配線レイアウトを考慮した場合、ベースとなる下段側の配線基板1Cにスルーホール7を形成すると、配線レイアウトに制約が生じる、または配線基板の外形サイズを大きくする必要があるため、前記実施の形態のように、サブ基板2Cにスルーホール7を形成しておくことが好ましい。

## 【0095】

10

また、前記実施の形態では、半導体部材32を配線基板(サブ基板)2C上に搭載する工程まで説明し、半導体部材32が搭載された状態を、半導体装置として説明したが、バンプ電極30を配線基板(ベース基板)1Cの下面に形成し、配線基板1C、2Cおよび封止体29を切断することで得られる、図43に示すような構造体を、1つの完成した半導体装置としてもよい。この場合、半導体部材32が搭載されていない状態で、半導体装置は管理または出荷されるため、適用する電子装置の機能に応じて構築される半導体システムを適宜変更できる。

## 【産業上の利用可能性】

## 【0096】

20

本発明の半導体装置の製造方法および半導体装置は、MCM型の半導体装置およびその製造工程に適用することができる。

## 【符号の説明】

## 【0097】

30

- |       |                            |  |

|-------|----------------------------|--|

| 1     | 基板母体                       |  |

| 1 A   | ガイドホール                     |  |

| 1 B   | 領域                         |  |

| 1 C   | 配線基板(ベース基板、インタポーザ)         |  |

| 2     | 基板母体                       |  |

| 2 A   | ガイドホール                     |  |

| 2 C   | 配線基板(サブ基板、インタポーザ、パッケージ領域)  |  |

| 3 A   | 導電性部材                      |  |

| 3 B   | 導電性部材                      |  |

| 3 C   | 電極パッド(ボンディングリード)           |  |

| 4 A   | 電極パッド(ランド)                 |  |

| 4 B   | 電極パッド(ランド、ボンディングリード)       |  |

| 5     | 銅薄膜                        |  |

| 5 A   | 銅膜                         |  |

| 6     | コア材                        |  |

| 7     | スルーホール                     |  |

| 8     | フォトレジスト膜                   |  |

| 9     | 配線                         |  |

| 1 0   | 絶縁層                        |  |

| 1 1   | 開口部                        |  |

| 1 2   | 銅膜                         |  |

| 1 3   | フォトレジスト膜                   |  |

| 1 4   | 銅膜                         |  |

| 1 5   | 配線                         |  |

| 1 5 A | 電極パッド(ランド)                 |  |

| 1 5 B | 電極パッド(ランド)                 |  |

| 1 6   | ソルダレジスト(絶縁膜、正面用絶縁膜、裏面用絶縁膜) |  |

40

50

- 1 6 A フォトレジスト膜

1 6 B 開口部

1 6 C 注入経路

1 6 D ソルダレジスト ( 絶縁膜、補強用絶縁膜 )

1 7 開口部

1 8 フォトレジスト膜

1 9 開口部

2 2 半導体チップ ( チップ )

2 2 A 電極パッド

2 2 B 回路素子 ( 半導体素子 )

2 3 バンプ電極 ( 突起電極 )

2 4 アンダーフィル樹脂

2 5 ステージ

2 6 ガイドピン

2 7 加熱ツール

2 9 モールド樹脂 ( 封止体 )

3 0 バンプ電極

3 1 バンプ電極

3 2 半導体部材

3 2 A 、 3 2 B 半導体チップ

3 2 C チップ部品

3 3 外部 L S I

3 4 ボンディングワイヤ

S D S 半導体装置 ( 半導体システム )

10

20

【図 1】

【図 2】

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図11】

図11

【図24】

図24

【図25】

図25

【図26】

図26

【図27】

図27

【図28】

図28

【図29】

図29

【図30】

図30

【図31】

図31

【図32】

【図33】

【図34】

図34

【図36】

【図35】

図35

【図37】

【 図 3 8 】

【図39】

【 図 4 0 】

【図41】

【 図 4 5 】

【 図 4 6 】

【 図 4 7 】

【 図 4 8 】

【図 49】

【図 50】

【図 51】

【図 52】

【図 53】

【図 5 4】

【図 5 5】

---

フロントページの続き

(72)発明者 平井 達也

東京都千代田区大手町二丁目 6 番 2 号 株式会社ルネサステクノロジ内

F ターム(参考) 5F061 AA01 CA02