(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5688375号

(P5688375)

(45) 発行日 平成27年3月25日(2015.3.25)

(24) 登録日 平成27年1月30日(2015.1.30)

(51) Int.Cl.

F 1

|             |           |      |        |     |

|-------------|-----------|------|--------|-----|

| HO1L 27/10  | (2006.01) | HO1L | 27/10  | 421 |

| HO3K 19/173 | (2006.01) | HO3K | 19/173 | 101 |

| HO3K 19/177 | (2006.01) | HO3K | 19/177 |     |

| HO1L 27/105 | (2006.01) | HO1L | 27/10  | 461 |

| HO1L 45/00  | (2006.01) | HO1L | 27/10  | 448 |

請求項の数 26 (全 21 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2011-546282 (P2011-546282)  |

| (86) (22) 出願日 | 平成22年1月7日(2010.1.7)           |

| (65) 公表番号     | 特表2012-515449 (P2012-515449A) |

| (43) 公表日      | 平成24年7月5日(2012.7.5)           |

| (86) 國際出願番号   | PCT/US2010/020327             |

| (87) 國際公開番号   | W02010/083087                 |

| (87) 國際公開日    | 平成22年7月22日(2010.7.22)         |

| 審査請求日         | 平成24年12月27日(2012.12.27)       |

| (31) 優先権主張番号  | 12/354,121                    |

| (32) 優先日      | 平成21年1月15日(2009.1.15)         |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 597154922<br>アルテラ コーポレイション<br>Altera Corporation<br>アメリカ合衆国 95134 カリフォルニア州 サンホセ イノベーション ドライヴ 101 |

| (74) 代理人  | 100078282<br>弁理士 山本 秀策                                                                           |

| (74) 代理人  | 100062409<br>弁理士 安村 高明                                                                           |

| (74) 代理人  | 100113413<br>弁理士 森下 夏樹                                                                           |

最終頁に続く

(54) 【発明の名称】相変化メモリデバイスを有する分圧器を含む不揮発性メモリ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリ回路であって、該メモリ回路は、分圧器であって、該分圧器は、第一相変化メモリ(PCM)デバイスと、該第一PCMデバイスに結合された第二PCMデバイスとを含む、分圧器と、該分圧器に結合されたハーフラッチと、該ハーフラッチおよび該分圧器に結合されたカスケードトランジスタとを含み、該ハーフラッチは、オーバードライブ電圧端子に結合され、更に、該カスケードトランジスタの第一端子は、該ハーフラッチの出力ノードに結合され、該カスケードトランジスタの第二端子は、該ハーフラッチの入力ノードに結合され、該カスケードトランジスタの第三端子は、該オーバードライブ電圧端子に直接結合され、該第一端子は、該カスケードトランジスタのゲート端子である、メモリ回路。

## 【請求項 2】

請求項1のメモリ回路であって、前記第一PCMデバイスはセット抵抗の状態にあり、前記第二PCMデバイスはリセット抵抗の状態にある、メモリ回路。

## 【請求項 3】

請求項2のメモリ回路であって、

10

20

前記分圧器は、更に、

前記第一P C Mデバイスに結合された第一スイッチと、

該第一スイッチおよび前記第二P C Mデバイスに結合された第二スイッチと

を含む、メモリ回路。

**【請求項4】**

請求項3のメモリ回路であって、

前記ハーフラッチは、pチャンネル金属酸化物半導体(P M O S)トランジスタに直列

で結合されたnチャンネル金属酸化物半導体(N M O S)トランジスタを含む相補型金属

酸化物半導体(C M O S)インバータを含み、該ハーフラッチの前記入力ノードは、該N

M O Sトランジスタのゲートおよび該P M O Sトランジスタのゲートに結合され、

10

前記カスケードトランジスタはP M O Sトランジスタであり、該カスケードトランジ

スタの前記第二端子は、該カスケードトランジスタのドレイン端子であり、該カスケードト

ランジスタの前記第三端子は、該カスケードトランジスタのソース端子であり、

前記第一スイッチはN M O Sトランジスタであり、そして

前記第二スイッチはN M O Sトランジスタである、メモリ回路。

**【請求項5】**

請求項4のメモリ回路であって、更に、

前記分圧器に結合されたアドレスラインスイッチと、

該分圧器と前記ハーフラッチとの間に結合されたリードラインスイッチと

を含む、メモリ回路。

20

**【請求項6】**

請求項5のメモリ回路であって、更に、

前記ハーフラッチの出力ノードに結合されたバスゲートトランジスタ

を含む、メモリ回路。

**【請求項7】**

請求項5のメモリ回路であって、前記アドレスラインスイッチはN M O Sトランジスタで

あり、前記リードラインスイッチはN M O Sトランジスタである、メモリ回路。

**【請求項8】**

請求項1のメモリ回路であって、前記第一P C Mデバイスおよび前記第二P C Mデバイス

は柱状セルメモリデバイスである、メモリ回路。

30

**【請求項9】**

請求項1のメモリ回路を含む分散メモリ。

**【請求項10】**

請求項1のメモリ回路を含むプログラマブルロジックデバイス。

**【請求項11】**

請求項1のメモリ回路を含むプログラマブルロジックデバイスを含むデジタルシステム。

**【請求項12】**

メモリ回路を動作させる方法であって、該方法は、

第一相変化メモリ(P C M)デバイスを第一抵抗状態にセットすることと、

第二P C Mデバイスを第二抵抗状態にセットすることであって、該第一P C Mデバイス

および該第二P C Mデバイスは、分圧器構成において結合されている、ことと、

40

該分圧器に結合されたハーフラッチを用いることと、

該ハーフラッチおよび該分圧器に結合されたカスケードトランジスタを用いることと

を含み、

該ハーフラッチは、オーバードライブ電圧端子に結合され、

更に、該カスケードトランジスタの第一端子は、該ハーフラッチの出力ノードに結合され、

該カスケードトランジスタの第二端子は、該ハーフラッチの入力ノードに結合され、

該カスケードトランジスタの第三端子は、該オーバードライブ電圧端子に直接結合され、

該カスケードトランジスタの第一端子は、該カスケードトランジスタのゲート端子である

、方法。

50

**【請求項 1 3】**

請求項 1 2 の方法であって、前記第一 P C M デバイスをセットすることと、前記第二 P C M デバイスをセットすることとは、前記メモリ回路に結合されたアドレススイッチラインの 1 つのクロックサイクル内で起こる、方法。

**【請求項 1 4】**

請求項 1 2 の方法であって、前記第一抵抗状態はセット抵抗状態であり、前記第二抵抗状態はリセット抵抗状態である、方法。

**【請求項 1 5】**

請求項 1 4 の方法であって、更に、

10

前記第一 P C M デバイスに結合された第一スイッチをオンに切り替えることと、

該第一スイッチおよび前記第二 P C M デバイスに結合された第二スイッチをオンに切り

替えることと

を含み、バスゲートが該第一スイッチを該第二スイッチに結合するノードに結合されて

いる、方法。

**【請求項 1 6】**

請求項 1 5 の方法であって、更に、

前記第一 P C M デバイスおよび前記第二 P C M デバイスをセットすることを可能にする

ためにアドレスラインスイッチをオンに切り替えること

を含む、方法。

**【請求項 1 7】**

請求項 1 6 の方法であって、

前記第一 P C M デバイスをセットすることは、該第一 P C M デバイスに第一パルスを印

加することを含み、

前記第二 P C M デバイスをセットすることは、該第二 P C M デバイスに第二パルスを印

加することを含み、該第一パルスは該第二パルスよりも持続時間が長い、方法。

**【請求項 1 8】**

請求項 1 5 の方法であって、更に、

第一端子で前記ノードに結合され、第二端子で前記バスゲートに結合されたハーフラッ

チに結合されたリードラインスイッチをオンに切り替えることと、

該リードラインスイッチの該第二端子での信号を該ハーフラッチの入力端子に印加する

ことと、

該バスゲートに該ハーフラッチの出力を印加することと

を含む、方法。

**【請求項 1 9】**

請求項 1 8 の方法であって、

前記カスケードトランジスタの第二端子は、前記リードラインスイッチの前記第二端子

に結合されている、方法。

**【請求項 2 0】**

メモリ回路であって、該メモリ回路は、

分圧器であって、該分圧器は、

第一相変化メモリ( P C M ) デバイスであって、該第一 P C M デバイスはセット抵抗

状態にある、第一 P C M デバイスと、

該第一 P C M デバイスに結合された第一スイッチと、

該第一スイッチに結合された第二スイッチと、

該第二スイッチに結合された第二 P C M デバイスであって、該第二 P C M デバイスは

リセット抵抗状態にある、第二 P C M デバイスと

を含む、分圧器と、

該分圧器に結合されたハーフラッチと、

該ハーフラッチおよび該分圧器に結合されたカスケードトランジスタと

を含み、

40

20

30

40

50

該ハーフラッチは、オーバードライブ電圧端子に結合され、更に、該カスケードトランジスタの第一端子は、該ハーフラッチの出力ノードに結合され、該カスケードトランジスタの第二端子は、該ハーフラッチの入力ノードに結合され、該カスケードトランジスタの第三端子は、該オーバードライブ電圧端子に直接結合され、該第一端子は、該カスケードトランジスタのゲート端子である、メモリ回路。

**【請求項 2 1】**

請求項 2 0 のメモリ回路であって、

前記ハーフラッチは、p チャンネル金属酸化物半導体 (PMOS) トランジスタに直列で結合されたn チャンネル金属酸化物半導体 (NMOS) トランジスタを含む相補型金属酸化物半導体 (CMOS) インバータを含み、該ハーフラッチの入力ノードは、該 NMOS トランジスタのゲートおよび該 PMOS トランジスタのゲートに結合され、

前記カスケードトランジスタは、PMOS トランジスタであり、該カスケードトランジスタの前記第二端子は、該カスケードトランジスタのドレイン端子であり、該カスケードトランジスタの前記第三端子は、該カスケードトランジスタのソース端子であり、

前記第一スイッチは、NMOS トランジスタであり、そして

前記第二スイッチは、NMOS トランジスタである、メモリ回路。

**【請求項 2 2】**

請求項 2 1 のメモリ回路であって、更に、

前記分圧器に結合されたアドレスラインスイッチと、

該分圧器と前記ハーフラッチとの間に結合されたリードラインスイッチと

を含み、該アドレスラインスイッチは NMOS トランジスタであり、該リードラインスイッチは NMOS トランジスタである、メモリ回路。

**【請求項 2 3】**

請求項 2 0 のメモリ回路であって、更に、

前記ハーフラッチの出力ノードに結合されたパスゲートトランジスタを含む、メモリ回路。

**【請求項 2 4】**

請求項 2 0 のメモリ回路を含む分散メモリ。

**【請求項 2 5】**

請求項 2 0 のメモリ回路を含むプログラマブルロジックデバイス。

**【請求項 2 6】**

請求項 2 0 のメモリ回路を含むプログラマブルロジックデバイスを含むデジタルシステム

。 【発明の詳細な説明】

【技術分野】

【0001】

(背景)

本発明はメモリ回路に関する。

【背景技術】

【0002】

プログラマブルロジックデバイス (PLD) (また、時々コンプレックス PLD (CPLD)、プログラマブルアレイロジック (PAL)、プログラマブルロジックアレイ (PLA)、フィールド PLA (FPLA)、消去可能 PLD (EPLD)、電気的消去可能 PLD (EEPPLD)、ロジックセルアレイ (LCA)、フィールドプログラマブルゲートアレイ (FPGA)、または他の名称により呼ばれる) は、固定された集積回路 (IC) の利点とカスタム IC の柔軟性を提供する周知の IC である。このようなデバイスは、典型的に、ユーザの特定のニーズに合うようにプログラムできる部分を少なくとも有する “規格品” デバイスを提供する。特定用途向け集積回路 (ASIC) は、従来固定された IC である。しかし、プログラマブルな単数の部分または複数の部分を有する ASIC を提供することは可能である。そのため、IC デバイスが ASIC および PLD 両方の特性

10

20

30

40

50

を有することは可能である。この明細書で使用される P L D という用語は、このようなデバイスを含むために充分広いとみなされる。

#### 【 0 0 0 3 】

P L D は、プログラムまたはリプログラムされ得るコンフィギュレーション要素を有する。コンフィギュレーション要素に新規データを入力することは、P L D のロジック機能および関連するルーティング経路をプログラムまたはリプログラムする。フィールドプログラマブルなコンフィギュレーション要素は、しばしばランダムアクセスメモリ ( R A M ) セルとしてインプリメントされ、P L D の R A M セルは時々“コンフィギュレーション R A M ” ( C R A M ) と呼ばれる。C R A M は、一般的に 6 トランジスタティック R A M ( 6 T - S R A M ) としてインプリメントされる。そのため、C R A M は、一般的に S R A M を指す。このため、C R A M という用語は、この明細書では、S R A M としてインプリメントされるコンフィギュレーションメモリを指すために使用される。10

#### 【 0 0 0 4 】

C R A M は、いくつかの不都合な点を被る。第一に、C R A M は、ソフトエラー（これらは時々“ワンオフエラー”と呼ばれる）に影響を受けやすい。ソフトエラー率 ( S E R ) は、コンポーネントデバイスのサイズが低減されるか、コンポーネントデバイスに印加される電圧（例えば、V c c ）が低減されるにつれ上昇する。この結果、ソフトエラーは、C R A M に使用されるコンポーネントデバイスのサイズ、またはそのコンポーネントデバイスに印加される電圧を減縮することを制限する。それゆえに、より大きいコンポーネントデバイス、およびより高い印加電圧が使用される。更に、時には、デバイスにより多くのキャパシタンスを加えるレイアウトが使用され、このことは C R A M がソフトエラーの影響を受けにくくする。これはレイアウトプロセスを複雑化する。第二に、C R A M は揮発性メモリであるため、P L D の電源がオンにされる度にコンフィギュレーションデータは C R A M にロードされ、保存されなければならない。これは P L D を準備することへ所望されない遅れの原因になる。20

#### 【 0 0 0 5 】

C R A M でのソフトエラーを修正する 1 つのやり方は、コンフィギュレーションデータをリロードすることである。これは、しかし、P L D の動作を中断することを要求する。ソフトエラーを修正する別のテクニックは、複数のリダンダンシー（例えば、3 重リダンダンシー）を使用することである。これは、次には、より大きい C R A M ブロックを使用することを要求する。それに加えて、これらの両方法は、エラー検出方法の使用を要求する。30

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【 0 0 0 6 】

##### （概要）

1 つの側面では、本発明の実施形態は、第一相変化メモリ ( P C M ) デバイスおよび第一 P C M デバイスに結合された第二 P C M デバイスを有する分圧器を含むメモリ回路を提供する。1 つの実施形態では、第一 P C M デバイスはセット抵抗状態にあり、第二 P C M デバイスはリセット抵抗状態にある。また、1 つの実施形態では、分圧器は、更に、第一 P C M デバイスに結合された第一スイッチ、ならびに第一スイッチおよび第二 P C M デバイスに結合された第二スイッチを含む。1 つの実施形態では、メモリ回路は、更に、分圧器に結合されたハーフラッチ、ならびにハーフラッチおよび分圧器に結合されたカスケードトランジスタを含む。40

#### 【 0 0 0 7 】

本発明のメモリ回路の実施形態は、データを保存するために P C M デバイスを使用するため、これは、C R A M よりもソフトエラーの影響を受けにくい。更に、本発明のメモリ回路の実施形態は不揮発性であり、コンフィギュレーション時間を減らす。外部フラッシュメモリおよび内部ブロックメモリの両方は、提案された分散コンフィギュレーション P C M ( C P C M ) メモリセルと比較して遅いコンフィギュレーション時間を持つ。50

本発明は、例えば、以下の項目も提供する。

(項目1)

メモリ回路であって、

第一相変化メモリ(PCM)デバイス、および

該第一PCMデバイスに結合された第二PCMデバイス

を含む分圧器

を含む、メモリ回路。

(項目2)

項目1のメモリ回路であって、上記第一PCMデバイスはセット抵抗の状態にあり、上記第二PCMデバイスはリセット抵抗の状態にある、メモリ回路。

10

(項目3)

項目2のメモリ回路であって、

上記分圧器は、更に、

上記第一PCMデバイスに結合された第一スイッチ、および

該第一スイッチおよび上記第二PCMデバイスに結合された第二スイッチ

を含む、メモリ回路。

(項目4)

項目3のメモリ回路であって、更に、

上記分圧器に結合されたハーフラッチ、および

該ハーフラッチおよび該分圧器に結合されたカスケードトランジスタ

を含む、メモリ回路。

20

(項目5)

項目4のメモリ回路であって、

上記ハーフラッチは、pチャンネル金属酸化物半導体(PMOS)トランジスタに直列で結合されたnチャンネル金属酸化物半導体(NMOS)トランジスタを含む相補型金属酸化物半導体(CMOS)インバータを含み、該ハーフラッチの入力ノードは、該NMOSトランジスタのゲートおよび該PMOSトランジスタのゲートに結合され、

上記カスケードトランジスタはPMOSトランジスタであり、そのトランジスタのゲートは該ハーフラッチの出力ノードに結合され、そのトランジスタのドレインは、該ハーフラッチの該入力ノードに結合され、

30

上記第一スイッチはNMOSトランジスタであり、そして

上記第二スイッチはNMOSトランジスタである、メモリ回路。

(項目6)

項目5のメモリ回路であって、更に、

上記分圧器に結合されたアドレスラインスイッチ、および

該分圧器と上記ハーフラッチの間に結合されたリードラインスイッチ

を含む、メモリ回路。

(項目7)

項目6のメモリ回路であって、更に、

上記ハーフスイッチの出力ノードに結合されたパスゲートトランジスタ

を含む、メモリ回路。

40

(項目8)

項目6のメモリ回路であって、上記アドレスラインスイッチはNMOSトランジスタであり、上記リードラインスイッチはNMOSトランジスタである、メモリ回路。

(項目9)

項目1のメモリ回路であって、上記第一PCMデバイスおよび上記第二PCMデバイスは柱状セルメモリデバイスである、メモリ回路。

(項目10)

項目1のメモリ回路を含む分散メモリ。

(項目11)

50

項目 1 のメモリ回路を含むプログラマブルロジックデバイス。(項目 1 2 )項目 1 のメモリ回路を含むプログラマブルロジックデバイスを含むデジタルシステム。【図面の簡単な説明】【0 0 0 8】

発明の新しい特色は、添付の特許請求範囲に示される。しかし、説明の目的で、発明の特定の実施形態のいくつかの側面は、次の図面への参照により記述される。

【図 1】図 1 は、本発明のメモリ回路の 1 つの実施形態のブロック図である。【図 2】図 2 は、本発明のメモリ回路の別の実施形態の詳細な図である。

【図 3】図 3 A および図 3 B は、図 1 および図 2 のメモリ回路の相変化メモリデバイスをプログラミングするための例示的なタイミング図である。 10

【図 4】図 4 は、例示的な P L D を含む例示的なデータ処理システムを示し、例示的な P L D には、本発明の実施形態に従ったメモリ回路がインプリメントされ得る。

【発明を実施するための形態】【0 0 0 9】

( 詳細説明 )

次の記述は、当業者が発明を作成および使用することを可能にするように示され、特定の用途およびそれらの必須条件の脈絡で提供される。例示的な実施形態への様々な改変は当業者に直ちに明白であり、この明細書で定義される一般的な原理は、他の実施形態および用途に、発明の精神および範囲から離れることなく適用され得る。そのため、本発明は、示された実施形態に制限されるように意図されているのではなく、この明細書に開示される原理および機能と一貫する最も広い範囲を与えるものである。 20

【0 0 1 0】

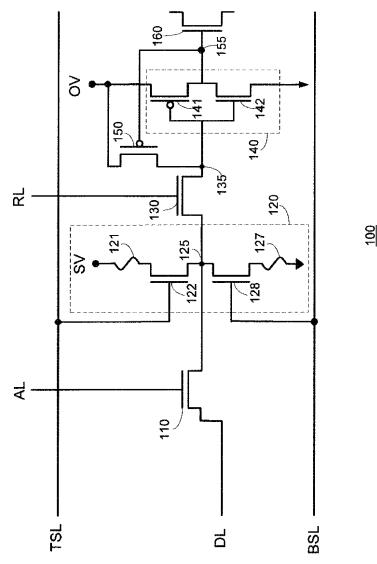

図 1 は、本発明のメモリ回路の 1 つの実施形態のブロック図である。図 1 では、メモリ回路 1 0 0 は、アドレスラインスイッチ 1 1 0 、分圧器 1 2 0 、リードラインスイッチ 1 3 0 、ハーフラッチ 1 4 0 、カスケードトランジスタ 1 5 0 ( ハーフラッチ 1 4 0 とカスケードトランジスタ 1 5 0 の組み合わせは、この明細書ではセンスアンプと呼ばれ得る ) 、およびバスゲート 1 6 0 を含む。バスゲート 1 6 0 は、例えば、ルックアップテーブル ( L U T ) を構成するか、グローバルルーティングに使用するための 2 つの金属相互接続線を接続するために使用され得る。注意すべきは、メモリ回路 1 0 0 はバスゲート 1 6 0 を除くように定義され得ることである。代わりに、メモリ回路 1 0 0 は、アドレスラインスイッチ 1 1 0 およびバスゲート 1 6 0 を除くように定義され得る。メモリ回路 1 0 0 のようなメモリ回路は、時に不揮発性メモリセルと呼ばれることも注意すべきである。 30

【0 0 1 1】

分圧器 1 2 0 は、図 1 に示されるように直列に結合された P C M デバイス 1 2 1 、スイッチ 1 2 2 、スイッチ 1 2 8 、および P C M デバイス 1 2 7 を含む。 P C M デバイス 1 2 1 およびスイッチ 1 2 2 は、この明細書では、上部 P C M デバイス 1 2 1 および上部スイッチ 1 2 2 とそれぞれ呼ばれ得る。同様に、 P C M デバイス 1 2 7 およびスイッチ 1 2 8 は、この明細書では、下部 P C M デバイス 1 2 7 および下部スイッチ 1 2 8 とそれぞれ呼ばれ得る。 40

【0 0 1 2】

1 つの実施形態では、ハーフラッチ 1 4 0 は、相補型金属酸化物半導体 ( C M O S ) インバータであり、これは p チャンネル金属酸化物半導体 ( P M O S ) トランジスタ 1 4 1 および n チャンネル金属酸化物半導体 ( N M O S ) トランジスタ 1 4 2 を含む。

【0 0 1 3】

1 つの実施形態では、アドレスラインスイッチ 1 1 0 、リードラインスイッチ 1 3 0 、スイッチ 1 2 2 およびスイッチ 1 2 8 、ならびにバスゲート 1 6 0 は全て N M O S トランジスタであるのに対し、カスケードトランジスタ 1 5 0 は、 P M O S トランジスタである。1 つの実施形態では、スイッチ 1 2 2 およびスイッチ 1 2 8 は、同じサイズの N M O S トランジスタである。 50

**【0014】**

1つの実施形態では、アドレスライン( A L )信号およびリードライン( R L )信号は、アドレスラインスイッチ110およびリードラインスイッチ130の状態をそれぞれ制御する。データライン( D L )信号は、アドレスラインスイッチ110へ入力される信号である。注意すべきは D L 電圧および D L 電流の両方はアドレスラインスイッチ110に入力されることである。上部セレクトライン( T S L )信号および下部セレクトライン( B S L )信号は、上部スイッチ122および下部スイッチ128の状態をそれぞれ制御する。センス電圧( S V )信号は、図1に示されるように上部PCMデバイス121の1つの端子に印加される。オーバードライブ電圧( O V )信号は、図1に示されるようにハーフラッチ140およびカスケードトランジスタ150に印加される。O V は、所与の技術に対してゲート酸化物の全域に印加される最大の信頼可能な電圧と定義される。O V は、V<sub>c c</sub>とV<sub>o d</sub>の和である。V<sub>o d</sub>は、トランジスタ160の酸化物の厚さに依存し、トランジスタ160がV<sub>t</sub>(V<sub>t</sub>はトランジスタの閾値電圧を表す)の降下なしにドレインからソースまで全電圧信号V<sub>c c</sub>を通すことを可能にするためにV<sub>c c</sub>に加えて必要とされる電圧を表す。言い換えれば、O V = V<sub>c c</sub> + V<sub>o d</sub>である。10

**【0015】**

1つの実施形態では、PCMデバイス121およびPCMデバイス127のそれぞれは、柱状セル構造を有するPCMデバイスである。また、1つの実施形態では、PCMデバイス121およびPCMデバイス127のそれぞれは、第一層、および第一層に接続された第2層を含むPCMデバイスである。1つの実施形態では、第一層は窒化チタン( Ti N )の層を含む。このような第一層は、この明細書ではTi N層と呼ばれ得る。第二層は、ゲルマニウム( Ge )、アンチモン( Sb )、およびテルル( Te )、ならびに窒素( N )のカルコゲナイト合金の層を含み、ゲルマニウム( Ge )、アンチモン( Sb )、およびテルル( Te )は、集合的にGSTと呼ばれる。このような第二層は、この明細書ではGST:N層と呼ばれ得る。1つの実施形態では、PCMデバイス121のTi N層は、S Vと結合された金属コンタクトに結合され、PCMデバイス121のGST:N層は、タングステン( W )から成るコンタクト(この明細書ではWプラグと呼ばれ得る)に結合される。このWプラグは、次には、上部スイッチ122のドレインと結合され得る。また、1つの実施形態では、PCMデバイス127のTi N層はグランドに結合されている金属コンタクトに結合され、PCMデバイス127のGST:N層は、Wプラグに結合される。このWプラグは、次には、下部スイッチ128のドレインに結合される。2030

**【0016】**

注意すべきは、柱状セル構造は、ある他のセル構造よりも少ないエリアを必要とすることである。別の実施形態では、PCMデバイスは水平セル構造を有し得、これは線状セル構造とも呼ばれ得る。

**【0017】**

1つの実施形態では、PCMデバイスは、メモリ回路のCMOSデバイスのためのCMOSプロセスと容易に統合される。

**【0018】**

1つの実施形態では、PCMデバイス121およびPCMデバイス127は、同じ材料で組み立てられ、同じ特徴およびレイアウトを有する。別の実施形態では、PCMデバイス121およびPCMデバイス127は、異なる材料で組み立てられ得、異なる特徴を有し得、異なるレイアウトを有し得る。40

**【0019】**

1つの実施形態では、PCMデバイス121およびPCMデバイス127は、摂氏125度( )の温度で10年のデータリテンションを達成し得る。これは、いくつかのICに要求される85から125の温度での10年のデータリテンションを満たすか上回る。また、1つの実施形態では、PCMデバイス121およびPCMデバイス127は、10<sup>7</sup>サイクルを超えるサイクルの耐久性を達成し得る。これは、いくつかのICに要求される10<sup>2</sup>から10<sup>3</sup>サイクルをはるかに超える。50

## 【0020】

PCMデバイスは、SETの状態（すなわち、低抵抗状態）にあり得るか、RESETの状態（すなわち、高抵抗状態）にあり得る。PCMデバイスの重要なパラメータのいくつかは、保持電圧V<sub>h</sub>、閾値電圧V<sub>th</sub>、SET状態抵抗、およびRESET状態抵抗を含む。1つの実施形態では、PCMデバイスの初期状態または未使用状態は、RESET状態である。これは、PCMデバイス材料の低温堆積を介して達成され得、PLDのようなICを構成するときに大量のクローバ電流を回避することを可能にする。PCMデバイスのV<sub>th</sub>は、数ある中で、PCMデバイスの材料組成、材料の厚さ、およびPCMデバイスのセル構造に依存する。

## 【0021】

1つの実施形態では、SET状態抵抗は、RESET状態抵抗より約3のオーダー低い。別の実施形態では、SET状態抵抗は、RESET状態抵抗より約6のオーダー低い。注意すべきは、本発明の実施形態は、上記の例のSET状態抵抗およびRESET状態抵抗の比率に限られないことである。

## 【0022】

1つの実施形態では、デバイスに印加される電流を約0.2から0.7ミリアンペア(mA)に制限しながらPCMデバイスにそのV<sub>th</sub>を超えるデバイス電圧を印加することは、PCMデバイスをRESET状態からSET状態に遷移させる。また、1つの実施形態では、0.7mAを超える電流を印加しながらPCMデバイスにV<sub>h</sub>より高くV<sub>th</sub>より低いデバイス電圧を印加することは、PCMデバイスをSET状態からRESET状態に遷移させる。注意すべきは、1つの実施形態では、SET状態からRESET状態に遷移するときに、PCMデバイスに印加された電流は早急に遮断されることである。これはPCMデバイス材料をアモルファス状態に保つことを可能にする。電流を早急に遮断することは、PCMデバイス材料のいくらかを結晶化させ得、この結晶化は、PCMデバイスの抵抗を低減する。1つの実施形態では、PCMデバイスをセットまたはリセットするためにPCMデバイスに印加された電流パルスは、10ナノ秒(ns)のオーダーの短パルスである。そのため、1つの実施形態では、PCMデバイスのプログラミングスピードは、10ナノ秒のオーダーである。1つの実施形態では、電流パルス期間は、デバイスをSET状態にするためには約50nsであり、デバイスをRESET状態にするためには約20nsである。また、1つの実施形態では、AL信号の期間は約100nsである。

## 【0023】

メモリ回路100の1つの実施形態では、RESET状態抵抗は、1メガオーム(M)から1ギガオーム(G)の値域にあり、V<sub>th</sub>は、所与の技術ノードに対して、OVをはるかに下回る。1つの実施形態では、V<sub>cc</sub>は約1.2ボルト(V)、OVは約1.55V、V<sub>h</sub>は約0.5V、そしてV<sub>th</sub>は約1.2Vである。上記からもわかるように、1つの実施形態では、V<sub>th</sub>は、V<sub>cc</sub>のオーダーにある。

## 【0024】

1つの実施形態では、リード電流(I<sub>read</sub>)、すなわち、分圧器120を通る電流は、SVおよびPCMデバイス(さらに詳細には、RESET状態のPCMデバイス)により制限される。また、1つの実施形態では、I<sub>read</sub>は、上部スイッチ122および下部スイッチ128に低いゲートバイアスを(V<sub>t</sub>以上で)使用することによって制限され得る。注意すべきは、1つの実施形態では、低いI<sub>read</sub>を有するメモリ回路は、より大きいICとの使用に、より適切であり得ることである。

## 【0025】

V<sub>th</sub>がOVをはるかに下回る1つの実施形態では、I<sub>read</sub>は、約10MのRESET状態抵抗、約0.5VのSV、そして約50マイクロアンペア(μA)のI<sub>ser</sub>に対して、メモリ回路につき約50ナノアンペア(nA)である。I<sub>ser</sub>は、メモリ回路100(より詳細には、メモリ回路100のPCM127およびトランジスタ128)がソフトエラーのイベントを克服できる電流を表す。このような場合、 $1 \times 10^6$ 個のメモリセルの合計スタティックセル電流は約50mA( $50\text{nA} \times 1 \times 10^6$ )である。V

10

20

30

40

50

$t_h$  が OV をはるかに下回る別の実施形態では、約 100M の RESET 状態抵抗、約 0.5V の SV、そして約 5  $\mu$ A の I<sub>ser</sub> に対して、I<sub>read</sub> は、メモリ回路につき約 5 nA である。1つの実施形態では、メモリ回路 100 は、フラッシュメモリに要求されるような速い読みを要求しない。

#### 【0026】

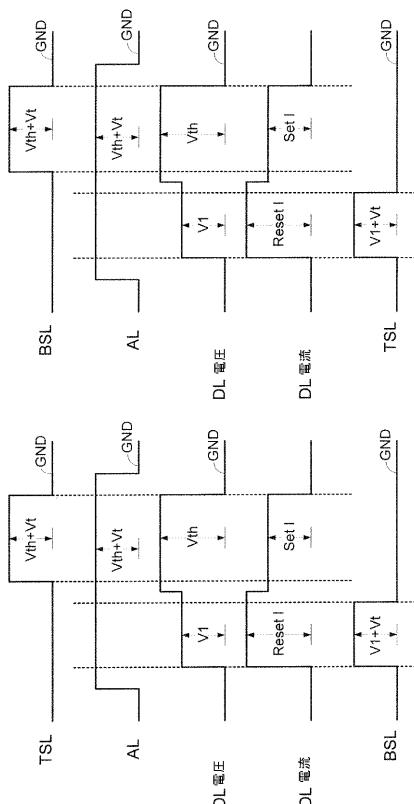

図 3 A および図 3 B は、図 1 および図 2 のメモリ回路の PCM デバイスをプログラミングするための例示的なタイミング図である。図 3 A は、(図 1 および図 2 の) 上部 PCM デバイスを SET 状態に、および(図 1 および図 2 の) 下部 PCM デバイスを RESET 状態にプログラミングするための例示的なタイミング図である。一方、図 3 B は、(図 1 および図 2 の) 上部 PCM デバイスを RESET 状態に、および(図 1 および図 2 の) 下部 PCM デバイスを SET 状態にプログラミングするための例示的なタイミング図である。メモリ回路 100 の動作は、この明細書に、図 3 A および図 3 B ならびに以下の表 1 と共に記述されている。表 1 は、PCM デバイス 121 および PCM デバイス 127 のプログラミングの間、ならびにスリープモード、読みモード、および通常動作モードの間の、図 1 の様々な信号の例示的な値を示す。

#### 【0027】

##### 【表 1 - 1】

|        | DL                                   | AL                  | TSL                 | BSL                 | RL  | SV  | OV  |

|--------|--------------------------------------|---------------------|---------------------|---------------------|-----|-----|-----|

| セット上部  | $\geq V_{th}$<br>I <sub>source</sub> | $\geq V_{th} + V_t$ | $\geq V_{th} + V_t$ | GND                 | GND | GND | GND |

| リセット下部 | V1                                   | $\geq V_1 + V_t$    | GND                 | $\geq V_1 + V_t$    | GND | GND | GND |

| リセット上部 | V1                                   | $\geq V_1 + V_t$    | $\geq V_1 + V_t$    | GND                 | GND | GND | GND |

| セット下部  | $\geq V_{th}$<br>I <sub>source</sub> | $\geq V_{th} + V_t$ | GND                 | $\geq V_{th} + V_t$ | GND | GND | GND |

10

20

30

#### 【0028】

##### 【表 1 - 2】

|      |   |     |     |     |                  |            |                   |

|------|---|-----|-----|-----|------------------|------------|-------------------|

| スリープ | X | GND | Vcc | GND | $< V_{th} + V_t$ | $< V_{th}$ | $< V_{th}$        |

| 読み   | X | GND | Vcc | Vcc | $< V_{th} + V_t$ | $< V_{th}$ | $< V_{th}$        |

| 通常動作 | X | GND | Vcc | Vcc | $< V_{th} + V_t$ | $< V_{th}$ | $V_{cc} + V_{od}$ |

40

表 1

注意すべきは、上記の表 1 では、 $V_{th} < V_1 < V_{th}$  であることである。表 1 では、通常動作モード中、 $OV = V_{cc} + V_{od}$  であることにも注意すべきである。更に、1つの実施形態では、 $V_{th}$  は、DL 電圧の最低必須条件である(すなわち、1つの実施形態では、PCM をセットするためには DL 電圧は  $V_{th}$  より高くなければならない)。それに加えて、GND はグランドを表し、V1 はアドレスラインスイッチ 110 への DL 電圧入力を表し、Vt は MOS デバイス(例えば、アドレスラインスイッチ 110、ならびにスイッチ 122、スイッチ 128、およびスイッチ 130)の閾値電圧を表し、Vcc は MOS デバイスに印加された電源電圧を表し、X はどれでも良い状態を表し、そして I<sub>so</sub>

50

`urce` はアドレスラインスイッチに印加される電流を表す（すなわち、`Isource` は D L 電流を表し、これはプログラミング電流とも呼ばれ得る）。注意すべきは、例えば、表 1 の D L に関して、X は、D L 電圧が G ND から V th であり得ることを示すことである。

#### 【0029】

表 1 では、縦欄 D L、A L、T S L、B S L、R L、S V、および O V は、それぞれ、D L 信号、A L 信号、T S L 信号、B S L 信号、R L 信号、S V 信号、および O V 信号の値を示す。また、表 1 では、横欄 Set Top、Reset Bottom、Reset Top、および Set Bottom は、それぞれ、上部 P CM デバイス 121 をセット、下部 P CM デバイス 127 をリセット、上部 P CM デバイス 121 をリセット、および下部 P CM デバイス 127 をセットするための様々な信号の値を示す。

10 1つの実施形態では、上部 P CM デバイス 121 をセットすること、および下部 P CM デバイス 127 をリセットすることの両方が、A L 信号の 1 つのクロックサイクルで起こる。同様に、1 つの実施形態では、上部 P CM デバイス 121 をリセットすること、および下部 P CM デバイス 127 をセットすることの両方が、A L 信号の 1 つのクロックサイクル内で起こる。別の実施形態では、上部および下部デバイスは、A L 信号の複数クロックサイクル内でプログラムされ得る。更に、表 1 では、横欄 Sleep、Read、および Normal OP は、それぞれ、スリープモード、読みモード、および通常動作モード中の様々な信号の値を示す。

20

#### 【0030】

表 1 からわかるように、上部 P CM デバイス 121 および下部 P CM デバイス 127 のセット中もリセット中も、R L 信号、S V 信号、および O V 信号は全てグランドされる。言い換れば、P CM デバイスのプログラミング中は、R L 信号、S V 信号、および O V 信号は全てグランドされる。P CM デバイスのプログラミング中に R L 信号がグランドされるときに、リードラインスイッチ 130 は開かれる。その結果、1 つの実施形態では、ハーフラッチ 140、カスケードトランジスタ 150、およびバスゲート 160 は、P CM デバイスのプログラミング中には分圧器 120 から電気的にデカップリングされる。同様に、P CM デバイスのプログラミング中に S V 信号がグランドされるときに、S V 信号に結合された P CM デバイス 121 の端子はグランドされる。図 1 からもわかるように、P CM デバイス 127 の 1 つの端子もグランドされる。同様に、P CM デバイスのプログラミング中に O V 信号がグランドされるときに、ハーフラッチ 140 の端子および O V 信号に結合されたカスケードトランジスタ 150 の端子もグランドされる。この状態は、ハーフラッチ 140 およびカスケードトランジスタ 150 を実際上オフの状態にする。

30

#### 【0031】

1 つの実施形態では、P CM デバイス 121 を S E T 状態にプログラミングしている間は、A L 信号は V th + V t 以上であるのに対し、P CM デバイス 127 を R E S E T 状態にプログラミングしている間は、A L 信号は V 1 + V t 以上であり、V 1 は、V h より高く V th より低い。別の実施形態では、P CM デバイス 121 を S E T 状態にプログラミングしている間であり、かつ、P CM デバイス 127 を R E S E T 状態にプログラミングしている間は、A L 信号は V th + V t である。このような実施形態は、図 3 A および図 3 B に示されるように、より簡単な A L 信号を可能にする。また、1 つの実施形態では、P CM デバイス 121 を S E T 状態にプログラミングしている間は、T S L 信号は V t h + V t 以上であり、D L 電圧信号は V th 以上であり、D L 電流信号はセットする電流 (Set I) に制限され、そして B S L 信号はグランドされる。1 つの実施形態では、セットする電流は、電流源 (図示なし) によって制御され、電流源は、D L 電流信号を供給し、P CM デバイス 121 を S E T 状態にするために使用される最大 D L 電流信号を制限する。P CM デバイス 127 を R E S E T 状態にプログラミングしている間は、T S L 信号はグランドされ、D L 電圧信号は V 1 と等しく、D L 電流信号はリセット電流レベル (Reset I) にあり、そして B S L 信号は V 1 + V t 以上である。1 つの実施形態では、リセット電流レベルは、P CM デバイス 127 のトランジスタ 128 上のゲートバ

40

50

イアスで制御される。1つの実施形態では、プログラミング電流 Set\_I および Reset\_I は、約 1 mA より低く、このことはメモリ回路のサイズを小さく保つことを可能にする。別の実施形態では、PCM デバイス 127 を RESET 状態にプログラミングしている間は、BSL 信号は Vth + Vt と等しい。このような場合、TSL 信号および BSL 信号両方の高いバイナリ数値電圧は、Vth + Vt である。

#### 【0032】

1つの実施形態では、PCM デバイス 121 を RESET 状態にプログラミングしている間は、AL 信号は V1 + Vt 以上であるのに対し、PCM デバイス 127 を SET 状態にプログラミングしている間は、AL 信号は Vth + Vt 以上である。別の実施形態では、PCM デバイス 121 を RESET 状態にプログラミングしている間であり、かつ、PCM デバイス 127 を SET 状態にプログラミングしている間は、AL 信号は Vth + Vt である。10 また、1つの実施形態では、PCM デバイス 121 を RESET 状態にプログラミングしている間は、TSL 信号は V1 + Vt 以上であり、DL 電圧信号は V1 と等しく、DL 電流信号はリセット電流レベル (Reset\_I) にあり、そして BSL 信号はグランドされる。1つの実施形態では、リセット電流レベルは、PCM デバイス 121 上のゲートバイアスで制御される。別の実施形態では、PCM デバイス 121 を RESET 状態にプログラミングしている間は、TSL 信号は Vth + Vt と等しい。同様に、1つの実施形態では、PCM デバイス 127 を SET 状態にプログラミングしている間は、TSL 信号はグランドされ、DL 電圧信号は Vth 以上であり、DL 電流信号はセットする電流 (Set\_I) に制限され、そして BSL 信号は Vth + Vt 以上である。1つの実施形態では、セットする電流は、電流源によって制御され、電流源は DL 電流信号を供給し、PCM デバイス 127 を SET 状態にするために使用される最大 DL 電流信号を制限する。20

#### 【0033】

1つの実施形態では、スリープモード中には、DL 信号は X であり、AL 信号はグランドされ、TSL 信号は Vcc と等しく、BSL 信号はグランドされ、RL 信号は Vh + Vt より低く、SV 信号は Vh より低く、そして OV 信号は Vh より低い。注意すべきは、スリープモードは、使用されないビットをオフにすることを可能にすることである。スリープモードは、使用されないロジックエレメント (LE) をオフにするために使用され得、そのため使用されない LE のメモリ回路のメモリリード電流 Iread を避け、全体電流 Icc を低減することも注意すべきである。30 Icc はチップによって消費される合計スタティック電流を表す。1つの実施形態では、スリープモード中には、上部 PCM デバイス 121 は SET 状態にあるのに対し、下部 PCM デバイス 127 は RESET 状態にある。

#### 【0034】

1つの実施形態では、読みモードの間は、DL 信号は X であり、AL 信号はグランドされ、TSL 信号は Vcc と等しく、BSL 信号は Vcc と等しく、RL 信号は Vh + Vt より低く、SV 信号は Vh より低く、そして OV 信号は Vh より低い。1つの実施形態では、読みモードの間は、ハーフラッチ 140 を作動させるには、SV 信号は OV 信号と等しい。注意すべきは、読み動作の間は、OV 信号は SV 信号のレベルまで降下することである。40

#### 【0035】

1つの実施形態では、通常動作モードの間は、DL 信号は X であり、AL 信号はグランドされ、TSL 信号は Vcc と等しく、BSL 信号は Vcc と等しく、RL 信号は Vh + Vt より低く、SV 信号は Vh より低く、そして OV 信号は Vcc + Vod と等しい。通常動作モードでは、PCM デバイスの状態が読まれた後、ハーフラッチ 140 の端子での電圧、および OV 信号に結合されたカスケードトランジスタ 150 の端子での電圧は、読み動作の間に OV 信号が SV 信号のレベルに降下するため、SV から OV に上げられる。通常動作の間は、データはバスゲート 160 を通される。

#### 【0036】

表1からわかるように、スリープモード、読みモード、および通常動作モードの間は、A L信号はグランドされる。その結果、アドレスラインスイッチ110はオフであり、分圧器120はD L電圧信号およびD L電流信号から電気的にデカップリングされる。

#### 【0037】

PCMデバイス121がSET状態にあり、PCMデバイス127がRESET状態にある場合、読み動作の間は、端子125での電圧はSVにほぼ等しい。注意すべきは、SET状態にあるPCMデバイス121は、分圧器120の電圧（すなわち、端子125での電圧）を、約SVに、アクティブに維持することである。端子125での電圧はSVにほぼ等しいため、高いバイナリ数値電圧が、リードラインスイッチ130を介して、ハーフラッチ140に入力される。言い換えれば、高いバイナリ数値電圧は、端子135に印加される。ハーフラッチ140は、端子135での電圧を反転し、端子155で低いバイナリ数値電圧を提供する。端子155は、バスゲート160のゲートに結合されている。上述されたように、1つの実施形態では、バスゲート160はNMOSトランジスタである。それゆえに、端子155での電圧が低いバイナリ数値を有するときには、バスゲート160はオンに切り替えられない。端子155は、カスケードトランジスタ150（1つの実施形態ではPMOSトランジスタ）のゲートにも結合されているため、カスケードトランジスタ150はオンに切り替えられ、そのためOV信号を端子135に結合する。このことは端子135での高いバイナリ数値電圧を補充する。

#### 【0038】

一方、PCMデバイス121がRESET状態にあり、PCMデバイス127がSET状態にある場合、端子125での電圧はグランドにほぼ等しい。注意すべきは、SET状態にあるPCMデバイス127は、分圧器120の電圧（すなわち、端子125での電圧）をアクティブに引き下げる事である。端子125での電圧はグランドにほぼ等しいため、低いバイナリ数値電圧が、リードラインスイッチ130を介して、ハーフラッチ140に入力される。言い換えれば、低いバイナリ数値電圧は、端子135に印加される。ハーフラッチ140は、端子135での電圧を反転し、端子155で高いバイナリ数値電圧を提供する。上述されたように、1つの実施形態では、バスゲート160はNMOSトランジスタである。それゆえに、端子155での電圧が高いバイナリ数値を有するときには、バスゲート160はオンに切り替えられる。端子155は、カスケードトランジスタ150のゲートにも結合されているため、カスケードトランジスタ150はオンに切り替えられず、そのため端子135を電気的にOV信号からデカップリングされたままにする。そのため、このような場合、カスケードトランジスタ150は、端子135での電圧を上昇させない。

#### 【0039】

1つの実施形態では、スリープモード、読みモード、および通常動作モードの間は、最大SV信号はリセット電圧より低く制限され、最低SV信号はセンスアンプのノイズマージンによって制限される。リセット電圧は、PCMデバイスがRESET状態にあるときはVthであり、PCMデバイスがSET状態にあるときはVhである。センスアンプのノイズマージンは、センスアンプがその状態を失わずに耐え得るノイズのレベルである。言い換えれば、センスアンプのノイズマージンは、センスアンプがラッチし得る最低入力電圧である。1つの実施形態では、センスアンプのノイズマージンは、SV信号レベルが、可能な範囲で最小化され得るように評価され、下げされる。SV信号はIreadに影響を及ぼすため、SV信号レベルを下げることは、Ireadを下げる。

#### 【0040】

注意すべきは、メモリ回路100は、ソフトエラーのイベントから回復するため、ソフトエラー抵抗力があることである。ハーフラッチ120でのデータエラーの場合、エラーは、OV信号をSV信号に低減し（これは上述されたように、通常読みプロセスの一部である）、データを分圧器120からハーフラッチ140にリロードすることによって修繕され得る。1つの実施形態では、このような修正は、メモリブロックの縦列またはメモリブロックの横列単位でなされ得る。別の実施形態では、ビット単位でなされ得る。メモリ

10

20

30

40

50

回路 100 は、V<sub>min</sub> (V<sub>min</sub> はデータロスを避けるために RAM に要求される最低供給電圧である) に耐性があることにも注意すべきである。この結果、メモリ回路 100 は、データディスターブに影響を受けない。それに加えて、メモリ回路 100 は、CRA および RAM メモリ回路に存在する読み / 書きマージンの問題を欠点として持たない。

#### 【0041】

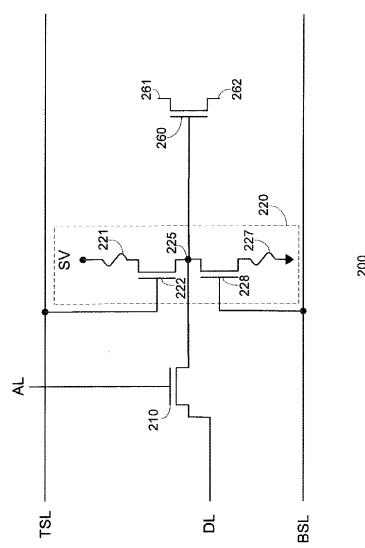

図 2 は、本発明のメモリ回路の別の実施形態の詳細な図である。図 2 では、メモリ回路 200 は、アドレスラインスイッチ 210、分圧器 220、およびバスゲート 260 を含む。注意すべきは、メモリ回路 200 はバスゲート 260 を除くように定義され得ることである。代わりに、メモリ回路 200 は、アドレスラインスイッチ 210 およびバスゲート 260 を除くように定義され得、この場合メモリ回路 200 は分圧器 220 と同じである。メモリ回路 200 のようなメモリ回路は、時にメモリセルと呼ばれることも注意すべきである。

#### 【0042】

分圧器 220 は、図 2 に示されるように直列に結合された PCM デバイス 221、スイッチ 222、スイッチ 228、および PCM デバイス 227 を含む。PCM デバイス 221 およびスイッチ 222 は、この明細書では、上部 PCM デバイス 221 および上部スイッチ 222 とそれぞれ呼ばれ得る。同様に、PCM デバイス 227 およびスイッチ 228 は、この明細書では、下部 PCM デバイス 227 および下部スイッチ 228 とそれぞれ呼ばれ得る。

#### 【0043】

1 つの実施形態では、アドレスラインスイッチ 210、スイッチ 222、スイッチ 228、およびバスゲート 260 は、全て NMOS トランジスタである。

#### 【0044】

メモリ回路 200 では、AL 信号は、アドレスラインスイッチ 210 の状態を制御する。DL 信号はアドレスラインスイッチ 210 へ入力される信号である。注意すべきは、DL 電圧信号および DL 電流信号の両方はアドレスラインスイッチ 210 に入力されることである。TSL 信号および BSL 信号は、上部スイッチ 222 および下部スイッチ 228 の状態をそれぞれ制御する。SV は、上部 PCM デバイス 221 の 1 つの端子に印加される。

#### 【0045】

例外については下述されるが、メモリ回路 200 は、メモリ回路 100 と同様であり、同様な態様で動作する。メモリ回路 100 の相対部と同様な機能を果たすメモリ回路 200 のコンポーネントおよび信号には、それらの相対部の参照番号と 100 異なるものが指定されている。例えば、メモリ回路 200 のアドレスラインスイッチ 210 および分圧器 220 は、それぞれ、メモリ回路 100 のアドレスラインスイッチ 110 および分圧器 120 に対応する。メモリ回路 200 は、メモリ回路 100 と同様であり、同様な形式で動作するため、メモリ回路 100 との相違のいくつかについて述べる以外は、この明細書では更に詳細に記述されない。

#### 【0046】

分圧器 220 の PCM デバイスは、分圧器 120 の PCM デバイスと同様であり、同様な態様でプログラムされる。図 2 からわかるように、メモリ回路 200 は、PCM デバイス 221 および PCM デバイス 227 のプログラミングの間に、分圧器 220 をバスゲート 260 から電気的にデカップリングするリードラインスイッチを含まない。その代わりに、メモリ回路 200 では、PCM デバイス 221 および PCM デバイス 227 のプログラミングの間は、バスゲート 260 の端子 261 および端子 262 (それぞれ、ドレン端子およびソース端子) はグランドされる。その結果、バスゲート 260 は、PCM デバイス 221 および PCM デバイス 227 のプログラミングの間はオンにされない。

#### 【0047】

上述されたように、図 3A および図 3B は、図 1 および図 2 のメモリ回路の PCM デバイスをプログラミングするための例示的なタイミング図である。図 3A は、上部 PCM デ

10

20

30

40

50

バイス 221 を S E T 状態に、および下部 P C M デバイス 227 を R E S E T 状態にプログラミングするための例示的なタイミング図である。一方、図 3B は、上部 P C M デバイス 221 を R E S E T 状態に、および下部 P C M デバイス 227 を S E T 状態にプログラミングするための例示的なタイミング図である。以下の表 2 は、P C M デバイスのプログラミング、スリープモード、および通常動作モードの間の、図 2 の関連する信号の値を示す。

【 0 0 4 8 】

【 表 2 - 1 】

|            | <b>DL</b>                 | <b>AL</b>           | <b>TSL</b>          | <b>BSL</b>          | <b>SV</b> |

|------------|---------------------------|---------------------|---------------------|---------------------|-----------|

| セット<br>上部  | $\geq V_{th}$<br>I source | $\geq V_{th} + V_t$ | $\geq V_{th} + V_t$ | GND                 | GND       |

| リセット<br>下部 | $V_l$                     | $\geq V_l + V_t$    | GND                 | $\geq V_l + V_t$    | GND       |

| リセット<br>上部 | $V_l$                     | $\geq V_l + V_t$    | $\geq V_l + V_t$    | GND                 | GND       |

| セット<br>下部  | $\geq V_{th}$<br>I source | $\geq V_{th} + V_t$ | GND                 | $\geq V_{th} + V_t$ | GND       |

10

20

【 0 0 4 9 】

【 表 2 - 2 】

|          |   |     |     |     |                   |

|----------|---|-----|-----|-----|-------------------|

| スリープ     | X | GND | Vcc | GND | $< V_h$           |

| 通常<br>動作 | X | GND | Vcc | Vcc | $V_{cc} + V_{od}$ |

表 2

表 1 および表 2 からわかるように、これらの表の関連する信号の値は、プログラミングの間は同一である。また、S V 信号の値を例外として、表 1 および表 2 の関連する信号の値は、スリープモードおよび通常動作モードの間は同一である。メモリ回路 200 はリードラインスイッチを含まないため、R L 信号はメモリ回路 200 には該当せず、表 2 には示されない。同様に、メモリ回路 200 は、データを分圧器 220 から読み込むメモリ回路 200 内のハーフラッチまたはラッチがないため、別個のリードモードを含まない。更に、メモリ回路 200 はカスケードトランジスタおよびハーフラッチを含まないため、O V 信号はメモリ回路 200 には該当せず、表 2 には示されない。最後に、スリープモードの間は、S V 信号は、表 1 と表 2 で同じ値を有する。しかし、通常動作モードの間は、表 2 の S V 信号は  $V_{cc} + V_{od}$  であり、これは S V 信号が表 1 で有する値と異なる。注意すべきは、表 2 では、S V 信号は、O V 信号が表 1 で有する値と同じ値を有することである。

30

40

【 0 0 5 0 】

上述されたように、スリープモードの間は、表 2 の関連する信号は、表 1 にある表 2 の相対部と同じ値を有する。これらの値は、表 1 に関して記述されているため、これらの値は、この明細書では表 2 に関して記述されない。通常動作モードの間は、S V 信号を例外として、表 2 の全信号は、表 1 と同じ値を有する。通常動作モードでは、P C M デバイスの状態が読まれた後、これらの値はパスゲート 260 を通される。

【 0 0 5 1 】

上記からわかるように、スリープモードおよび通常動作モードの間は、A L 信号はグランドされる。この結果、アドレスラインスイッチ 210 はオフであり、分圧器 220 は D

50

L 電圧信号およびD L 電流信号から電気的にデカップリングされる。

#### 【0052】

PCMデバイス221がSET状態にあり、PCMデバイス227がRESET状態にある場合、通常動作モードの間は、端子225での電圧はSVにほぼ等しい。端子225は、バスゲート260のゲートに直接結合されているため、高いバイナリ数値電圧がバスゲート260のゲートに印加される。上述されたように、1つの実施形態では、バスゲート260はNMOSトランジスタである。また、通常動作モードの間は、端子261および端子262（それぞれ、バスゲート260のドレイン端子およびソース端子）はグランドされない。それゆえに、端子225での電圧が高いバイナリ数値を有するときには、バスゲート260はオンに切り替えられる。このことは、端子261および端子262を電気的に結合する。10

#### 【0053】

一方、PCMデバイス221がRESET状態にあり、PCMデバイス227がSET状態にある場合、端子225での電圧はグランドにほぼ等しい。この結果、低いバイナリ数値電圧がバスゲート260のゲートに印加される。上述されたように、1つの実施形態では、バスゲート260はNMOSトランジスタである。それゆえに、端子225での電圧が低いバイナリ数値を有するときには、バスゲート260はオンに切り替えられない。この結果、端子261および端子262は電気的に結合されない。

#### 【0054】

メモリ回路200の1つの実施形態では、RESET状態抵抗は、1M から1G の値域にあり、V<sub>th</sub>は、所与の技術ノードに対して、OVより高い。1つの実施形態では、V<sub>cc</sub>は約1.2V、OVは約1.55V、そしてV<sub>th</sub>は約1.7から2Vである。別の実施形態では、V<sub>cc</sub>は約0.9V、OVは約1.2V、そしてV<sub>th</sub>は約1.35から1.7Vである。20

#### 【0055】

プロセスノードのOVと比較して、V<sub>th</sub>は高く、SVは等しい1つの実施形態では、65ナノメートル(nm)プロセスノードにおいて、I<sub>read</sub>は、約1G のRESET状態抵抗、約1.55VのSV、そして約1.5μAのI<sub>ser</sub>に対して、メモリ回路につき約1.5nAである。このような場合、1×10<sup>6</sup>個のメモリセルの合計スタティック電流は約1.5mAである。1つの実施形態では、メモリ回路200は、フラッシュメモリに要求されるような速い読みを要求しない。30

#### 【0056】

SVがOVと等しい1つの実施形態では、より高い電圧のトランジスタが、アドレスラインスイッチ210、上部スイッチ222、および下部スイッチ228に使用される。このようなより高い電圧のトランジスタは、より高い電圧信号を、PCMデバイス221、PCMデバイス227、およびバスゲート260に通すことが可能である。

#### 【0057】

注意すべきは、メモリ回路100およびメモリ回路200は、標準的なDRAMメモリセルよりもエリアが狭いことである。更に注意すべきは、メモリ回路200は、ハーフラッチ回路、リードラインスイッチ、およびカスケードトランジスタを含まないため、メモリ回路200はメモリ回路100より4つ少ないトランジスタを有することである。それに加えて、メモリ回路200は、メモリ回路100に在るRL信号およびOV信号のような信号を含まない。この結果、メモリ回路200は、メモリ回路100よりも信号の複雑さを伴わない。更に、メモリ回路200は、メモリ回路100よりもさらにソフトエラーに影響を受けにくい。実際に、メモリ回路200は、分圧器220がバスゲート260のゲートに結合された端子225での電圧をアクティブに維持するために、ソフトエラーの影響を受けない。40

#### 【0058】

注意すべきは、PCMデバイスはソフトエラーの影響を受けず、不揮発性であることである。同様に、メモリ回路100およびメモリ回路200は不揮発性である。それに加え50

て、メモリ回路 100 およびメモリ回路 200 の分圧器は、漏洩電流を制限する。この結果、より低い待機電力がメモリ回路 100 およびメモリ回路 200 に使用される。更に、メモリ回路 100 およびメモリ回路 200 は、それらがそれぞれソフトエラーに抵抗があり、影響を受けないため、スケーラブルである。このため、メモリ回路 100 およびメモリ回路 200 は、より小さいプロセスノードを使用して作成される、より小さいデバイスに使用され得る。

#### 【 0 0 5 9 】

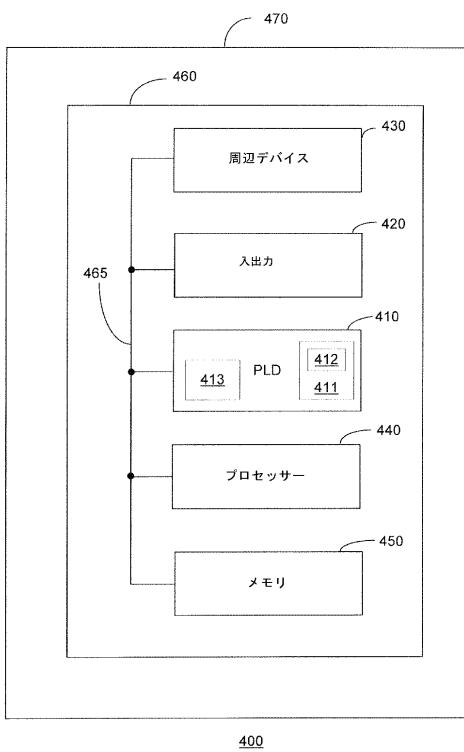

図 4 は、例示的な PLD を含む例示的なデータ処理システムを示し、例示的な PLD には、本発明の実施形態に従ったメモリ回路がインプリメントされ得る。図 4 は、一例として、データ処理システム 400 の PLD 410 を示す。1つの例として、この発明のメモリ回路は、PLD 410 のロジックブロック内の分散メモリにインプリメントされ得る。

このような分散メモリは、LUT を構成するため、ならびにグローバルおよびローカル金属信号線を接続するために使用され得る。1つの実施形態では、この分散インプリメンテーションは従来の CRAM を代替する。1つの実施形態では、PLD 410 は、分散メモリを複数含み得る（しかし、図面を過剰複雑化することを避けるために1つの分散メモリだけが示される）。分散メモリ 411 は、メモリ回路 100 またはメモリ回路 200 のようなメモリ回路を複数含む（しかし、図面を過剰複雑化することを避けるために1つのメモリ回路、メモリ回路 412、だけが示される）。1つの実施形態では、メモリ回路 412 および分散メモリ 411 は、PLD 410 と同じダイ / チップ上にある。1つの実施形態では、PLD 410 のメモリブロック 413 のようなメモリブロックは、PCM ベースのメモリセルを含み得る。1つの実施形態では、PLD 410 は、メモリブロック 413 のようなメモリブロックを複数含み得る（しかし、図面を過剰複雑化することを避けるために1つのこのようなメモリブロックだけが示される）。1つの実施形態では、メモリブロック 413 は、PLD 410 と同じダイ / チップ上にある。1つの実施形態では、メモリブロック 413 は、小型エンベデッドアレイブロック (SEAB) または中型エンベデッドアレイブロック (MEAB) であり得る。別の実施形態では、充分に速いセットおよびリセット時間ががあれば、メモリブロック 413 は、メガ RAM (MRAM) ブロックであり得る。1つの実施形態では、メモリブロック 413 は、不揮発性メモリブロックである。データ処理システム 400 は、1つ以上の次のコンポーネント：プロセッサー 440、メモリ 450、入出力 (I/O) 回路網 420、および周辺デバイス 430 を含み得る。

これらのコンポーネントは、システムバス 465 によって共に結合され、エンドユーザシステム 470 に含まれる回路基板 460 に実装される。システム 400 のようなデータ処理システムは、エンドユーザシステム 470 のような単一のエンドユーザシステムを含み得るか、データ処理システムとして共に機能するシステムを複数含み得る。

10

20

30

40

#### 【 0 0 6 0 】

システム 400 は、コンピューターネットワーキング、データネットワーキング、インストルメンテーション、ビデオ処理、デジタル信号処理（“DSP”）、またはプログラマブルもしくはリプログラマブルロジックを使用することの利点が所望されるいかなる他の用途のような、広く多様な用途に使用され得る。PLD 410 は、多様な異なるロジック機能を実行するために使用され得る。例えば、PLD 410 は、プロセッサー 440（また、代わりの実施形態では、PLD そのものが唯一のシステムプロセッサーとしての役割を果たし得る）と協同で機能するプロセッサーまたはコントローラーとして構成され得る。PLD 410 は、システム 400 の共有リソースへのアクセスをアービトレーションするためのアービタとしても使用され得る。また別の例では、PLD 410 は、プロセッサー 440 と、システム 400 の他のコンポーネントの1つとの間のインターフェイスとして構成され得る。注意すべきは、システム 400 は、単に例示的であることである。

50

#### 【 0 0 6 1 】

1つの実施形態では、システム 400 はデジタルシステムである。この明細書で使用される場合、デジタルシステムは、純然たるデジタルシステムに制限されるように意図されておらず、デジタルおよびアナログのサブシステムの両方を含むハイブリッドシステムを

も含む。

**【 0 0 6 2 】**

図4では、本発明のメモリ回路の実施形態は、P L Dの脈絡で考察される。しかし、注意すべきは、本発明のメモリ回路の実施形態は、P L Dにのみ使用されるように制限されないことである。言い換えれば、本発明のメモリ回路の実施形態は、他のタイプのI Cに使用され得る。

**【 0 0 6 3 】**

本発明は、示された実施形態に関して詳細に記述されているが、様々な変更、改変、および適合は、本開示に基づいてなされ得、本発明の範囲内にあることが意図されることが認識される。発明は、現在最も実用的であり好まれるとみなされる実施形態に関して記述されているが、本発明は、開示された実施形態に制限されるのではなく、これに反して、添付の特許請求の範囲内に含まれる様々な改変および同等な配列を範囲に入れるように意図されることが理解される。

**【 0 0 6 4 】**

(追加的な実施形態)

(実施形態1) メモリ回路を動作させる方法であって、該方法は、

第一相変化メモリ(P C M)デバイスを第一抵抗状態にセットすること、および

第二P C Mデバイスを第二抵抗状態にセットすることであって、該第一P C Mデバイス

および該第二P C Mデバイスは、分圧器のコンフィギュレーションで結合される、こと

を含む、方法。

(実施形態2) 実施形態1の方法であって、前記第一P C Mデバイスをセットすること

および前記第二P C Mデバイスをセットすることは、前記メモリ回路に結合されたアドレ

ススイッチラインの1つのクロックサイクル内で起こる、方法。

(実施形態3) 実施形態1の方法であって、前記第一抵抗状態はセット抵抗状態であり

、前記第二抵抗状態はリセット抵抗状態である、方法。

(実施形態4) 実施形態3の方法であって、更に、

前記第一P C Mデバイスに結合された第一スイッチをオンに切り替えること、および

該第一スイッチおよび前記第二P C Mデバイスに結合された第二スイッチをオンに切り

替えることであって、パスゲートは該第一スイッチを該第二スイッチに結合するノードに

結合されている、こと

を含む、方法。

(実施形態5) 実施形態4の方法であって、更に、

前記第一P C Mデバイスおよび前記第二P C Mデバイスをセットすることを可能にする

ためにアドレスラインスイッチをオンに切り替えること

を含む、方法。

(実施形態6) 実施形態5の方法であって、

前記第一P C Mデバイスをセットすることは、該第一P C Mデバイスに第一パルスを印

加することを含み、

前記第二P C Mデバイスをセットすることは、該第二P C Mデバイスに第二パルスを印

加することを含み、該第一パルスは該第二パルスよりも持続時間が長い、方法。

(実施形態7) 実施形態4の方法であって、更に、

第一端子で前記ノードに結合され、第二端子で前記パスゲートに結合されたハーフラッ

チに結合されたリードラインスイッチをオンに切り替えること、

該第二端子での信号を該ハーフラッチの入力に印加すること、および

該パスゲートに該ハーフラッチの出力を印加すること

を含む、方法。

(実施形態8) 実施形態7の方法であって、更に、

前記パスゲートおよび前記第二端子に結合されたカスケードトランジスタを使用する

こと

を含む、方法。

10

20

30

40

50

(実施形態 9) メモリ回路であって、該メモリ回路は、

(a) 分圧器であって、該分圧器は、

(i) 第一相変化メモリ(PCM)デバイスであって、該第一PCMデバイスはセット抵抗状態にある、第一PCMデバイス、

(ii) 該第一PCMデバイスに結合された第一スイッチ、

(iii) 該第一スイッチに結合された第二スイッチ、および

(iv) 該第二スイッチに結合された第二PCMデバイスであって、該第二PCMデバイスはリセット抵抗状態にある、第二PCMデバイス

を含む、分圧器、

(b) 該分圧器に結合されたハーフラッチ、ならびに

(c) 該ハーフラッチおよび該分圧器に結合されたカスケードトランジスタを含む、メモリ回路。

(実施形態 10) 実施形態 9 のメモリ回路であって、

前記ハーフラッチは、pチャンネル金属酸化物半導体(PMOS)トランジスタに直列で結合されたnチャンネル金属酸化物半導体(NMOS)トランジスタを含む相補型金属酸化物半導体(CMOS)インバータを含み、該ハーフラッチの入力ノードは、該NMOSトランジスタのゲートおよび該PMOSトランジスタのゲートに結合され、

前記カスケードトランジスタは、PMOSトランジスタであり、そのゲートは該ハーフラッチの出力ノードに結合され、そのドレインは該ハーフラッチの入力ノードに結合され、

前記第一スイッチは、NMOSトランジスタであり、そして

前記第二スイッチは、NMOSトランジスタである、メモリ回路。

(実施形態 11) 実施形態 10 のメモリ回路であって、更に、

前記分圧器に結合されたアドレスラインスイッチ、および

該分圧器と前記ハーフラッチとの間に結合されたリードラインスイッチであって、該アドレスラインスイッチはNMOSトランジスタであり、該リードラインスイッチはNMOSトランジスタである、リードラインスイッチ

を含む、メモリ回路。

(実施形態 12) 実施形態 9 のメモリ回路であって、更に、

前記ハーフラッチの出力ノードに結合されたバスゲートトランジスタ

を含む、メモリ回路。

(実施形態 13) 実施形態 9 のメモリ回路を含む分散メモリ。

(実施形態 14) 実施形態 9 のメモリ回路を含むプログラマブルロジックデバイス。

(実施形態 15) 実施形態 9 のメモリ回路を含むプログラマブルロジックデバイスを含むデジタルシステム。

10

20

30

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3A

【図4】

FIG. 4

---

フロントページの続き

|                |              |                  |         |       |       |

|----------------|--------------|------------------|---------|-------|-------|

| (51)Int.Cl.    | F I          |                  |         |       |       |

| <b>G 1 1 C</b> | <b>13/00</b> | <b>(2006.01)</b> | H 0 1 L | 27/10 | 4 8 1 |

|                |              |                  | H 0 1 L | 45/00 | A     |

|                |              |                  | G 1 1 C | 13/00 | 2 1 0 |

|                |              |                  | H 0 1 L | 27/10 | 4 9 1 |

(72)発明者 マックエルヘニー， ピーター ジェイ。

アメリカ合衆国 カリフォルニア 95037， モーガン ヒル， ローン ヒル ドライブ

16705

(72)発明者 スモーレン， リチャード ジー。

アメリカ合衆国 カリフォルニア 94061， レッドウッド シティ， オータム ドライブ

3812

(72)発明者 コステロ， ジョン シー。

アメリカ合衆国 カリフォルニア 94024， ロス アルトス， ハイランズ サークル 8

69

審査官 外山 賀

(56)参考文献 特開2006-108762(JP, A)

特開2004-213860(JP, A)

特開2006-203898(JP, A)

特開平04-223714(JP, A)

(58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| H 0 1 L | 2 7 / 1 0   |

| G 1 1 C | 1 3 / 0 0   |

| H 0 1 L | 2 7 / 1 0 5 |

| H 0 1 L | 4 5 / 0 0   |

| H 0 3 K | 1 9 / 1 7 3 |

| H 0 3 K | 1 9 / 1 7 7 |