#### PCT

# ORGANISATION MONDIALE DE LA PROPRIETE INTELLECTUELLE

# DEMANDE INTERNATIONALE PUBLIEE EN VERTU DU TRAITE DE COOPERATION EN MATIERE DE BREVETS (PCT)

(51) Classification internationale des brevets <sup>6</sup>: H01L 27/12, 21/84, 21/762, 29/786

(11) Numéro de publication internationale:

WO 99/66559

(43) Date de publication internationale: 23 décembre 1999 (23.12.99)

(81) Etats désignés: JP, US, brevet européen (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT,

(21) Numéro de la demande internationale:

PCT/FR99/01403

**A1**

(22) Date de dépôt international:

14 juin 1999 (14.06.99)

(30) Données relatives à la priorité:

98/07495

15 juin 1998 (15.06.98)

Publiée

FR

Avec rapport de recherche internationale.

(71) Déposant (pour tous les Etats désignés sauf US): COMMIS-SARIAT A L'ENERGIE ATOMIQUE [FR/FR]; 31-33, rue de la Fédération, F-75752 Paris 15ème (FR).

(72) Inventeurs; et

(75) Inventeurs/Déposants (US seulement): BELLEVILLE, Marc [FR/FR]; 4bis, rue du Cotaire, F-38120 St. Egrève (FR). BRUEL, Michel [FR/FR]; Presvet n° 9, F-38113 Veurey (FR).

(74) Mandataire: WEBER, Etienne; Brevatome, 25, rue de Ponthieu, F-75008 Paris (FR).

(54) Title: INTEGRATED SILICON-ON-INSULATOR INTEGRATED CIRCUIT WITH DECOUPLING CAPACITY AND METHOD FOR MAKING SUCH A CIRCUIT

(54) Titre: CIRCUIT INTEGRE DE TYPE SOI A CAPACITE DE DECOUPLAGE, ET PROCEDE DE REALISATION D'UN TEL CIRCUIT

#### (57) Abstract

The invention concerns an integrated circuit comprising: at least a first and a second supply terminals (418, 420); at least one active zone (303, 304, 306, 308) formed in a substrate thin layer (206), and electrically connected to at least one of the supply terminals. The invention is characterised in that the circuit further comprises decoupling capacitive means formed by at least one dielectric capacitor (110, 112, 114) connected between said first and second supply terminals and formed in a region of the substrate electrically insulated from the substrate thin layer (206). The invention is useful for producing portable electronic appliances, for example.

#### (57) Abrégé

Circuit intégré comprenant: au moins une première et une deuxième borne d'alimentation (418, 420), au moins une zone active (302, 304, 306, 308) formée dans une couche mince (206) d'un substrat, et reliée électriquement à l'une au moins des bornes d'alimentation. Conformément à l'invention, le circuit comporte en outre des moyens capacitifs de découplage formés par au moins une capacité à diélectrique (110, 112, 114) connectée entre lesdites première et deuxième bornes d'alimentation et formée dans une région du substrat isolée électriquement de la couche mince (206) du substrat. Application à la réalisation d'appareils électroniques portables, par exemple.

#### UNIQUEMENT A TITRE D'INFORMATION

Codes utilisés pour identifier les Etats parties au PCT, sur les pages de couverture des brochures publiant des demandes internationales en vertu du PCT.

| AL            | Albanie                   | ES | Espagne               | LS | Lesotho                  | SI | Slovénie              |

|---------------|---------------------------|----|-----------------------|----|--------------------------|----|-----------------------|

| AM            | Arménie                   | FI | Finlande              | LT | Lituanie                 | SK | Slovaquie             |

| ΑT            | Autriche                  | FR | France                | LU | Luxembourg               | SN | Sénégal               |

| ΑU            | Australie                 | GA | Gabon                 | LV | Lettonie                 | SZ | Swaziland             |

| ΑZ            | Azerbaïdjan               | GB | Royaume-Uni           | MC | Monaco                   | TD | Tchad                 |

| BA            | Bosnie-Herzégovine        | GE | Géorgie               | MD | République de Moldova    | TG | Togo                  |

| BB            | Barbade                   | GH | Ghana                 | MG | Madagascar               | TJ | Tadjikistan           |

| BE            | Belgique                  | GN | Guinée                | MK | Ex-République yougoslave | TM | Turkménistan          |

| BF            | Burkina Faso              | GR | Grèce                 |    | de Macédoine             | TR | Turquie               |

| BG            | Bulgarie                  | HU | Hongrie               | ML | Mali                     | TT | Trinité-et-Tobago     |

| BJ            | Bénin                     | IE | Irlande               | MN | Mongolie                 | UA | Ukraine               |

| BR            | Brésil                    | IL | Israël                | MR | Mauritanie               | UG | Ouganda               |

| BY            | Bélarus                   | IS | Islande               | MW | Malawi                   | US | Etats-Unis d'Amérique |

| CA            | Canada                    | IT | Italie                | MX | Mexique                  | UZ | Ouzbékistan           |

| CF            | République centrafricaine | JP | Japon                 | NE | Niger                    | VN | Viet Nam              |

| $\mathbf{CG}$ | Congo                     | KE | Kenya                 | NL | Pays-Bas                 | YU | Yougoslavie           |

| CH            | Suisse                    | KG | Kirghizistan          | NO | Norvège                  | ZW | Zimbabwe              |

| CI            | Côte d'Ivoire             | KP | République populaire  | NZ | Nouvelle-Zélande         |    |                       |

| CM            | Cameroun                  |    | démocratique de Corée | PL | Pologne                  |    |                       |

| CN            | Chine                     | KR | République de Corée   | PT | Portugal                 |    |                       |

| CU            | Cuba                      | KZ | Kazakstan             | RO | Roumanie                 |    |                       |

| CZ            | République tchèque        | LC | Sainte-Lucie          | RU | Fédération de Russie     |    |                       |

| DE            | Allemagne                 | LI | Liechtenstein         | SD | Soudan                   |    |                       |

| DK            | Danemark                  | LK | Sri Lanka             | SE | Suède                    |    |                       |

| EE            | Estonie                   | LR | Libéria               | SG | Singapour                |    |                       |

|               |                           |    |                       |    | -                        |    |                       |

# CIRCUIT INTEGRE DE TYPE SOI A CAPACITE DE DECOUPLAGE, ET PROCEDE DE REALISATION D'UN TEL CIRCUIT

#### Domaine technique

L'invention concerne une structure de circuit intégré comprenant des moyens capacitifs de découplage des bornes d'alimentation du circuit.

Elle trouve des applications dans les domaines de la micro-électronique pour la réalisation de circuits à composants MOS, MIS ou bipolaires, et permet de réduire le bruit parasite engendré sur les alimentations électriques des circuits, provoqués notamment par des appels de courant transitoires.

De façon plus précise, l'invention peut être mise à profit dans des appareils portables incluant par exemple des microprocesseurs, des circuits de téléphonie sans fil, ou dans toutes applications utilisant les technologies SOI pour leurs caractéristiques en basse consommation.

20

25

15

5

10

#### Etat de la technique antérieure

Dans les circuits intégrés, la distribution des masses et des potentiels d'alimentation vers les dispositifs actifs, c'est-à-dire vers les transistors par exemple, est réalisée par des lignes d'alimentation en un matériau conducteur électrique. Or, lors du fonctionnement des circuits, les lignes d'alimentation doivent fournir des courants transitoires dont l'intensité peut être relativement élevée.

Selon l'intensité de ces courants, mais aussi selon leur localisation, les courants transitoires sont susceptibles de générer un bruit parasite sur les lignes et le système d'alimentation.

2

De façon générale, dans les circuits électroniques, on utilise des condensateurs de filtrage connectés entre les bornes des systèmes d'alimentation pour diminuer le bruit parasite, et placés le plus près possible de la source de courant transitoire.

5

10

30

Dans le domaine de l'électronique intégrée la réalisation des condensateurs de filtrage peut poser problème. Cependant, la structure de certains types de circuits intégrés, tels que les circuits CMOS (Metal-Oxyde-Semiconducteur-Complémentaires) sur substrat massif, permet de découpler naturellement les potentiels d'alimentation et le potentiel de masse.

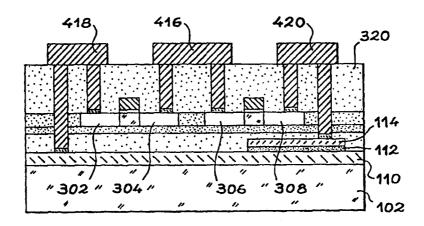

La figure 1 est une coupe schématique d'une portion de circuit intégré de type CMOS usuel.

Sur cette figure, la référence 10 désigne un substrat massif de silicium du type de conductivité P. Dans ce substrat est formé un caisson 12 de type N. Les références 14 et 16 désignent des transistors à effet de champ réalisés respectivement dans le substrat de type P et dans le caisson de type N.

Des zones actives fortement dopées 14a, 14b, 16a, 16b, 18 et 20 forment respectivement les sources et drains des transistors à effet de champ 14, 16, et des prises de contact pour les régions de type P et N.

La zone active 18, de type  $P^+$  est en contact avec le substrat de type P et la zone active 20 de type  $N^+$  est en contact avec le caisson de type N.

Une épaisse couche d'isolant électrique 22 recouvre le substrat et les composants 14, 16 qui y sont réalisés. Cette couche est traversée par des ouvertures 24 emplies d'un matériau conducteur électrique permettant de relier les zones actives à des pistes conductrices 26, 28, 30 formées au-dessus de la

30

couche d'isolant électrique 22. Les ouvertures emplies de matériau conducteur électrique sont encore appelées "vias".

Les vias permettent de relier des zones actives 5 entre elles. Ceci est le cas, par exemple, des vias connectés à la piste conductrice centrale 26 et qui relient électriquement entre elles les zones actives 14b et 16a. Les vias permettent également de relier les zones actives et/ou des régions du substrat à des 10 bornes d'alimentation.

Sur la figure 1, les bornes d'alimentation sont constituées par les pistes conductrices 28, 30 qui sont reliées à une source de tension d'alimentation 31 représenté schématiquement en trait discontinu.

La piste conductrice 28 constitue une borne de masse. Elle est reliée à la zone active 14a du premier transistor 14, et au substrat 10 par l'intermédiaire de la zone active 18. Une deuxième borne d'alimentation, formée par la piste conductrice 30, est reliée notamment au caisson 12 par l'intermédiaire de la zone active 20.

Le caisson 12 forme avec le substrat 10 une jonction semi-conductrice qui présente une certaine capacité de jonction et qui se trouve connectée entre les bornes d'alimentation 28, 30, en parallèle avec les composants.

La capacité de la jonction caisson-substrat permet de filtrer ainsi l'alimentation et de réduire le bruit parasite dû à des appels de courant.

Il existe d'autres types de structures CMOS, à caissons N, à caissons P, ou à double caissons. Des capacités de jonction formées entre les caissons et le substrat permettent généralement d'obtenir un

15

20

25

découplage intrinsèque entre la borne de masse et les autres bornes d'alimentation.

Un certain nombre de circuits intégrés réalisés actuellement ne sont cependant pas formés sur un substrat massif, comme évoqué ci-dessus, mais sont formés dans une couche mince d'un support présentant une structure de type silicium sur isolant. Une telle structure, usuellement désignée par "SOI" (silicon On Insulator), comporte une couche de matériau isolant électrique, par exemple d'oxyde, qui sépare la couche mince de silicium d'une partie massive du support. La réalisation de circuits intégrés sur des substrats de type SOI permet d'augmenter la densité d'intégration, de réduire les capacités parasites et d'améliorer les performances des circuits en termes de fréquence de fonctionnement et de consommation.

Dans le cas des circuits réalisés sur des substrats SOI, l'isolation entre les différents composants ou zones actives est réalisée par des zones d'oxyde.

Ainsi, le découplage entre les masses et les autres bornes d'alimentation, qui se fait par l'intermédiaire du substrat dans les structures sur substrat massif, est beaucoup plus faible dans les circuits réalisés sur des substrats de type SOI.

Un bruit plus important est donc observé dans ces circuits. Ce problème est exposé par exemple dans le document (1) dont la référence est précisée à la fin de la présente description.

30 Une solution possible pour réduire le bruit parasite consiste à ajouter au circuit intégré, formé dans la couche mince de la structure SOI, des capacités de découplage. Ces capacités peuvent être réalisées en

5

utilisant la capacité de grille d'un ou de plusieurs transistors. A titre d'exemple, on peut utiliser un transistor de type NMOS dont la grille est reliée à une borne d'alimentation et dont la source et le drain sont connectés à la masse. Une capacité de meilleure qualité peut être obtenue par une implantation adaptée du canal d'un tel transistor.

Cependant, les transistors ou autres capacités dédiés au découplage des bornes d'alimentation sont placés sur la structure SOI à côté des transistors formant la partie fonctionnelle du circuit intégré. Ils occupent ainsi une place utile, ce qui conduit à une augmentation de la surface totale des puces électroniques.

On peut se référer à ce sujet aux documents (2) et (3) dont les références sont précisées à la fin de la description.

Un arrière-plan technologique de l'invention est aussi illustré par le document (4).

20

25

30

10

#### Exposé de l'invention

La présente invention a pour but de proposer un circuit intégré formé dans une couche mince isolée d'un substrat, tel que par exemple une couche mince d'un substrat SOI, ne présentant pas les limitations mentionnées ci-dessus.

Un but est en particulier de proposer un circuit incluant des moyens pour découpler les bornes d'une ou de plusieurs alimentations, qui permettent de réduire efficacement le bruit parasite des alimentations.

Un but est encore de proposer un tel circuit utilisant une surface de puce réduite.

15

20

25

30

Pour atteindre ces buts, l'invention a plus précisément pour objet un circuit intégré comprenant :

- au moins une première et une deuxième bornes d'alimentation,

- 5 au moins une zone active formée dans une couche mince d'un substrat, et reliée électriquement à l'une au moins des bornes d'alimentation.

Conformément à l'invention, le circuit intégré comporte en outre des moyens capacitifs de découplage formés par au moins une capacité à diélectrique connectée entre lesdites première et deuxième bornes d'alimentation, et formée dans une région du substrat isolée électriquement de la couche mince du substrat.

Au sens de la présente invention, on entend par zone active une zone de la couche mince présentant un type de dopage déterminé. Un circuit électronique peut comporter un très grand nombre de zones actives qui peuvent constituer notamment des parties de transistors telles que les sources ou les drains des transistors.

Par ailleurs, le circuit peut être alimenté en énergie par une ou plusieurs alimentations. On désigne par borne d'alimentation un élément conducteur relié à une alimentation et dont le potentiel est fixé par ladite alimentation. Une borne d'alimentation particulière est la borne de masse.

Grâce à l'invention, comme les moyens capacitifs de découplage ne sont pas réalisés dans la couche mince, ils ne réduisent pas la place disponible pour les composants fonctionnels du circuit intégré, c'est-à-dire pour les zones actives.

Selon un aspect particulier avantageux, la région comportant les moyens capacitifs de découplage

10

15

25

peut s'étendre au moins en partie en-dessous de la zone active ou des zones actives du circuit intégré.

Cette caractéristique permet de contribuer encore davantage à la réduction de la surface totale de la puce comportant le circuit.

Les moyens capacitifs de découplage l'invention peuvent comporter une ou plusieurs capacités à diélectrique. On désigne par capacité à diélectrique une capacité formée de façon comparable à un condensateur, c'est-à-dire avec deux armatures en un matériau conducteur électrique, séparées par un matériau isolant électrique.

Ainsi, la région du substrat isolée de la couche mince peut comporter au moins une première et au moins une deuxième couches de matériau conducteur électrique, électriquement isolées l'une de l'autre, présentant respectivement au moins une face en regard, et reliées respectivement aux première et deuxième bornes d'alimentation.

Les première et deuxième couches de matériau conducteur, par exemple en silicium dopé ou en silicium polycristallin, peuvent être séparées par une couche d'oxyde de silicium.

Selon un perfectionnement de l'invention, les moyens capacitifs de découplage peuvent comporter au moins une couche conductrice électrique formant une armature de condensateur, et connectée à au moins une zone active pour relier ladite zone active à une borne d'alimentation.

L'utilisation des moyens de découplage pour distribuer une alimentation électrique aux zones actives est non seulement très favorable pour diminuer encore davantage les bruits parasites, mais permet

30

aussi de libérer une place importante pour réaliser des pistes d'interconnexion des parties actives et de transport des signaux. Ces pistes sont généralement formées sur un côté de la couche mince opposé à la partie massive du substrat SOI.

L'invention concerne également un procédé de réalisation d'un circuit intégré équipé de moyens capacitifs à diélectrique. Ce procédé comporte les étapes successives suivantes :

- 10 a) formation sur un substrat comprenant une première couche conductrice, dans l'ordre à partir de la surface, une première couche isolante et une deuxième couche conductrice,

- b) mise en forme de la deuxième couche conductrice pour

15 laisser subsister au moins une portion de la deuxième couche conductrice séparée de la première couche conductrice par la première couche isolante,

- c) formation d'une deuxième couche isolante enrobant la portion de la deuxième couche conductrice,

- 20 d) réalisation sur la deuxième couche isolante d'une couche mince de matériau semi-conducteur,

- e) formation dans la couche mince d'au moins un composant comprenant au moins une zone active et oxydation de la couche mince entre les composants,

- 25 f) formation sur la couche mince d'une couche isolante électrique épaisse,

- g) formation d'ouvertures traversant la couche isolante épaisse, la couche mince, et la couche de matériau isolant électrique en dehors des composants pour atteindre les première et deuxième couches conductrices,

- h) mise en place de matériau conducteur dans les ouvertures, et formation des interconnexions

électriques pour relier les première et deuxième couches conductrices respectivement à des première et deuxième bornes d'alimentation électrique.

L'étape g) peut également comporter la formation d'ouvertures traversant la couche isolante épaisse pour atteindre des zones actives de la couche mince, ces ouvertures étant aussi emplies de matériau conducteur électrique pour relier entre elles sélectivement des zones actives ou pour relier des zones actives aux bornes d'alimentation électrique.

D'autres caractéristiques et avantages de la présente invention ressortiront mieux de la description qui va suivre, en référence aux figures des dessins annexés. Cette description est donnée à titre purement illustratif et non limitatif.

#### Brève description des figures

- La figure 1, déjà décrite, est une coupe schématique d'une portion de circuit intégrée CMOS de type connu réalisée sur un substrat de silicium massif.

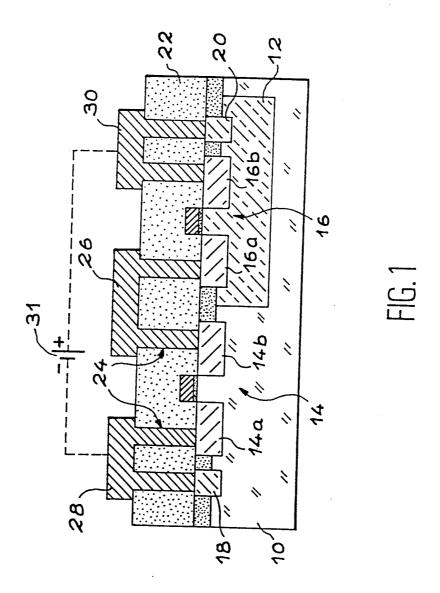

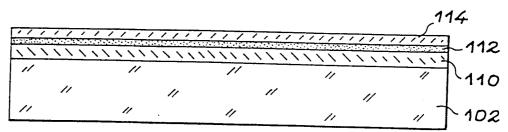

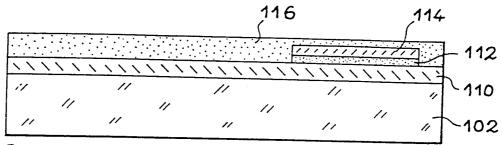

- Les figures 2 à 8 sont des coupes schématiques simplifiées illustrant des étapes successives de fabrication d'un circuit intégré conforme à l'invention.

25

30

5

10

15

20

# Description détaillée de modes de mise en oeuvre de l'invention

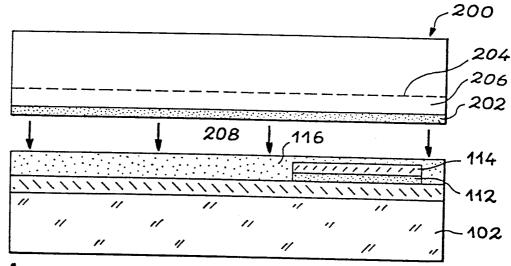

La figure 2 montre un substrat 100 de type N dans lequel on a formé une première couche conductrice 110 fortement dopée N<sup>+</sup>. Cette couche 110 est formée par exemple par implantation d'arsenic avec une dose de 3.10<sup>15</sup>.cm<sup>-2</sup>, suivie d'un recuit à 950°C pendant 1 heure.

Sur la première couche conductrice 110 sont successivement formées une première couche d'oxyde 112 et une deuxième couche conductrice 114. La couche d'oxyde 112 est formée par croissance avec une épaisseur de 15 nm, par exemple.

5

10

15

20

25

La deuxième couche 114, conductrice, est une couche de silicium polycristallin dopé N' et est déposé avec une épaisseur de l'ordre de 600 nm, par exemple. (Sur la figure les épaisseurs des couches ne sont pas proportionnelles, mais représentées en échelle libre).

La première couche d'oxyde 112 et la deuxième couche conductrice 114 sont gravées avec arrêt sur la première couche conductrice 110 en silicium selon un motif permettant de préserver une portion de la deuxième couche conductrice 114 et la couche d'oxyde 112 sous-jacente.

Comme le montre la figure 3, une deuxième couche d'oxyde 116 est déposée sur le substrat de façon à encapsuler la portion de la deuxième couche conductrice 114 préservée lors de la gravure. L'épaisseur de la deuxième couche d'oxyde est par exemple de 1,5 µm.

Cette couche est rendue plane par un polissage mécanochimique lors duquel on préserve de préférence une épaisseur d'oxyde de l'ordre de 0,2 µm au-dessus du silicium polycristallin de la deuxième couche conductrice 114.

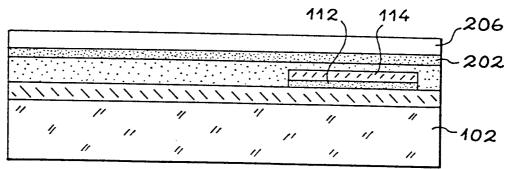

Une étape ultérieure illustrée par les figures 4 et 5 consiste à reporter sur la deuxième couche d'oxyde 116 une structure SOI comprenant une couche d'oxyde 202 et une couche superficielle mince de silicium 206. Ces couches sont reportées à partir d'un deuxième substrat 200.

11

Le deuxième substrat 200 est une plaque de silicium à la surface de laquelle est formée la couche superficielle d'oxyde de silicium 202. Une zone de fragilisation 204, définie par exemple l'implantation d'ions de gaz rare ou d'azote dans le substrat 200, délimite initialement dans celui-ci la couche mince de silicium 206 en contact avec la couche superficielle d'oxyde de silicium. La zone fragilisation 204 s'étend de façon sensiblement parallèle à la surface du deuxième substrat.

5

10

15

Comme l'indiquent des flèches 208 le deuxième substrat 200 est reporté sur le premier substrat 100 en tournant la couche superficielle d'oxyde 202 vers la face du premier substrat de silicium dans laquelle l'implantation a été pratiquée. Cette face est désignée par face supérieure.

La couche d'oxyde 202 est solidarisée de la face supérieure du premier substrat, par exemple, par des forces de liaison atomique.

Puis, un traitement thermique approprié permet de cliver le deuxième substrat 200 selon la zone de fragilisation 204 et de séparer la couche mince 206 du deuxième substrat.

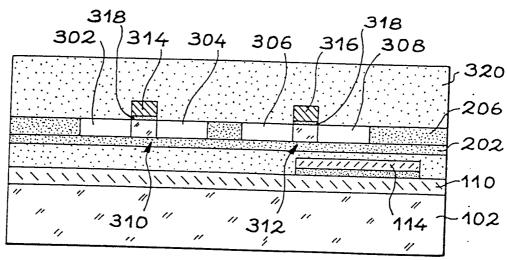

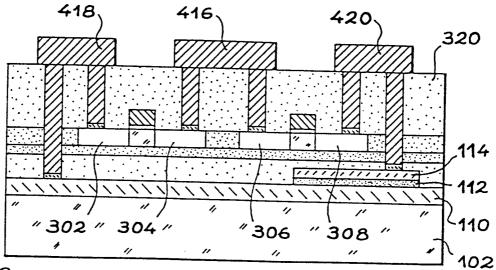

Dans la couche mince 206 sont ensuite formées des zones actives 302, 304, 306, 308 de transistors 310, 312. Les parties restantes de la couche mince sont oxydées et des grilles de transistors 314, 316 sont formées sur la couche mince. Une couche épaisse d'isolant, telle qu'une couche d'oxyde 320 est formée au-dessus de la couche mince de façon à enrober les grilles des transistors. On obtient la structure illustrée par la figure 6.

WO 99/66559 PCT/FR99/01403

Les zones 302, 304 sont dopées N' et forment les source et drain d'un premier transistor NMOS 310. Les zones 306 et 308 sont dopées P' et forment les source et drain d'un deuxième transistor 312 PMOS. Les références 314, 316 désignent respectivement les grilles des transistors 306 et 308, formées sur la couche mince superficielle, par l'intermédiaire d'une couche d'oxyde de grille 318.

5

Les parties de la couche mince superficielle 206, situées entre les transistors 310 et 312 sont oxydées afin d'isoler mutuellement ces composants.

Enfin, comme indiqué ci-dessus, une couche isolante épaisse 320 est formée à la surface du substrat pour recouvrir entièrement les grilles.

- On peut observer que l'agencement mutuel des transistors, c'est-à-dire des zones actives, et les première et deuxième couches conductrices du substrat, est tel que les zones actives chevauchent partiellement les première et deuxième couches conductrices 110, 114.

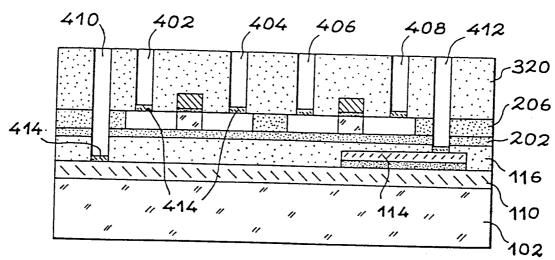

- La figure 7 illustre une étape ultérieure lors de laquelle des ouvertures 402, 404, 406, 408 sont pratiquées dans la couche d'oxyde épaisse pour atteindre les zones actives 302, 304, 306, 308 respectivement.

- Ces ouvertures sont pratiquées par gravure ionique réactive avec arrêt sur le silicium des zones actives. Elles présentent un diamètre de 0,5 μm par exemple.

Des ouvertures 410, 412 sont également 30 pratiquées à travers la couche d'oxyde épaisse, à travers la couche de silicium oxydée en dehors des zones actives, à travers la couche d'oxyde 202 reportée sur le substrat, et à travers la deuxième couche

d'oxyde 116 pour atteindre respectivement les première et deuxième couches conductrices 110, 114. Ces ouvertures peuvent présenter un diamètre plus fort, par exemple de 0,8 µm. Toutes les opérations d'ouverture (de 402 à 412) peuvent éventuellement être simultanées.

5

10

30

Les ouvertures 410, 412 atteignant les couches conductrices ne constituent pas un encombrement trop important à la surface de la puce dans la mesure ou elles sont généralement nettement moins nombreuses que les ouvertures pratiquées à l'aplomb des zones actives.

On observe par ailleurs, que toutes les ouvertures sont pratiquées à travers des matériaux électriquement isolants.

Après un nettoyage chimique du fond des ouvertures et la formation éventuellement d'une couche 414 de barrière de diffusion, par exemple en Ti/TiN, les ouvertures sont emplies d'un matériau conducteur tel que du tungstène déposé par CVD pour former des vias.

Puis, comme le montre la figure 8 des pistes conductrices sont réalisées sur la surface de la couche d'isolant épais 320. Ces pistes conductrices 416, 418, 420 sont en contact avec les vias. Elles sont formées par dépôt puis gravure selon un masque d'une couche de matériau conducteur.

La piste 418, par exemple, est connectée à la source 302 du premier transistor 310 et à la première couche conductrice 110. Elle forme avec la première couche conductrice 110 une borne d'alimentation, en l'occurrence la borne de masse.

La piste 420 qui constitue une deuxième borne d'alimentation et est reliée à la source 308 du

14

deuxième transistor 312 et à la portion restante de la deuxième couche conductrice 114 dans le substrat.

Les première et deuxième couches conductrices 110, 114 séparées par la première couche d'oxyde 112, constituent les armatures d'un condensateur de découplage des bornes de l'alimentation.

5

10

15

20

25

30

De plus, la première couche conductrice 110 du substrat peut être utilisée comme une d'alimentation, par exemple comme ligne de masse commune. Ceci est le cas dans l'exemple de la figure 8 où une zone active 302 est reliée à la première couche conductrice 110 par l'intermédiaire de vias et d'une piste conductrice 418. Une place plus importante peut alors être réservée à la surface de l'oxyde épais 320 pour réaliser des interconnexions entre composants. De manière analogue, la deuxième couche conductrice 114 peut être utilisée comme une ligne d'alimentation.

La description qui précède se réfère à des exemples de circuits réalisés avec un faible nombre de composants et avec seulement deux d'alimentation. L'invention s'applique cependant également à des circuits comprenant un nombre très important de composants et de zones actives, alimentés par une pluralité de sources d'alimentation distinctes. Le nombre de bornes d'alimentation et, éventuellement, le nombre capacités de découplage de est multiplié.

On observe également que comme la réalisation des capacités et des zones actives sont bien distinctes, il est possible d'optimiser séparément les paramètres de fabrication de ces éléments. Ceci constitue un avantage supplémentaire par rapport aux

15

circuits de l'art antérieur réalisé sur un substrat massif.

#### DOCUMENTS CITES

5 *(1)*

Proceedings 1995 IEEE International SOI Conference, Oct. 1995, pages 100-101

"On-chip decoupling capacitor design to reduce switching-noise-induced instability in CMOS/SOI

10 VLSI"

de L.K. Wang and Howard H. chen

(2)

Proceedings 1996 IEEE International SOI Conference, Oct. 1996, pp. 112-113

"Simultaneous Switching noise projection for High-Performance SOI chip design" de L.K. Wang and Howard H. Chen

(3)

1998 IEEE International Solid-State Circuits

Conference, pp. 230-231

de J. Silberman et al.

(4)

US-A-5 378 919

#### REVENDICATIONS

- 1. Circuit intégré comprenant :

- au moins une première et une deuxième bornes d'alimentation (418, 420),

- 5 au moins une zone active (302, 304, 306, 308) formée dans une couche mince (206) d'un substrat, et reliée électriquement à l'une au moins des bornes d'alimentation,

- caractérisé en ce qu'il comporte en outre des moyens capacitifs de découplage formés par au moins une capacité à diélectrique (110, 112, 114) connectée entre lesdites première et deuxième bornes d'alimentation et formée dans une région du substrat isolée électriquement de la couche mince (206) du substrat.

- 2. Circuit intégré selon la revendication 1, dans lequel la région comportant les moyens capacitifs de découplage s'étend au moins en partie sous ladite zone active.

- 3. Circuit selon la revendication 1, lequel la région du substrat isolée de la couche mince 20 (206) comporte au moins une première et au moins une deuxième couches de matériau conducteur électrique 114), électriquement (110,isolées, présentant respectivement au moins une face en regard, et reliées 25 respectivement aux première et deuxième bornes d'alimentation, les première et deuxième couches formant les armatures d'au moins une capacité à diélectrique.

- 4. Circuit selon la revendication 3, dans 30 lequel les première et deuxième couches (110, 114) sont respectivement séparées par une couche d'oxyde de silicium (112).

5. Circuit selon la revendication 1, dans lequel ledit condensateur de découplage comporte au moins une couche conductrice (110) électrique formant une armature, ladite couche étant connectée à au moins une zone active (302) pour relier ladite zone active à une borne d'alimentation.

5

10

- 6. Procédé de réalisation d'un circuit intégré équipé de moyens de découplage capacitif de bornes d'alimentation électrique comprenant les étapes successives suivantes :

- a) formation, sur un substrat (100) comprenant une première couche conductrice (110), dans l'ordre à partir de la surface, une première couche isolante (112) et une deuxième couche conductrice (114),

- b) mise en forme de la deuxième couche conductrice (114) pour laisser subsister au moins une portion de la deuxième couche conductrice séparée de la première couche conductrice par la couche isolante,

- c) formation d'une deuxième couche isolante (116)

20 enrobant la portion de la deuxième couche conductrice,

- d) réalisation sur la deuxième couche isolante (116) d'une couche mince (206) de matériau semiconducteur,

- e) formation dans la couche mince d'au moins un composant comprenant au moins une zone active (302, 304, 306, 308) et oxydation de la couche mince entre les composants,

- f) formation sur la couche mince d'une couche isolante électrique épaisse (320),

- g) formation d'ouvertures traversant la couche isolante épaisse, la couche mince (206), et la couche de matériau isolant électrique (116) en dehors des

20

composants pour atteindre les première et deuxième couches conductrices,

- h) mise en place de matériau conducteur dans les ouvertures et formation d'interconnexions électriques pour relier les première et deuxième couches conductrices respectivement à des première et deuxième bornes d'alimentation électrique.

- 7. Procédé selon la revendication 6, dans lequel l'étape g) comporte en outre la formation d'ouvertures traversant la couche isolante épaisse pour atteindre des zones actives de la couche mince, ces ouvertures étant également emplies lors de l'étape h) de matériau conducteur pour relier des zones actives sélectivement entre elles ou pour relier des zones actives actives aux bornes de l'alimentation électrique.

- 8. Procédé selon la revendication 6, dans lequel l'étape d) comporte le report sur le substrat d'une plaque de silicium (200) présentant une couche superficielle d'oxyde de silicium (202), la couche d'oxyde de silicium étant solidarisée de la deuxième couche isolante et la plaque de silicium étant clivée pour laisser à la surface du substrat la couche mince (206) de matériau semi-conducteur.

- 9. Procédé selon la revendication 6, dans 25 lequel on effectue un polissage de la deuxième couche isolante (116) après l'étape c)

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

### INTERNATIONAL SEARCH REPORT

In national Application No FUT/FR 99/01403

| 0. 400                 |                                                                                                                      |                                                                                       | ,                      |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------|

| IPC 6                  | FICATION OF SUBJECT MATTER H01L27/12 H01L21/84 H01L21/7                                                              | 762 H01L29/786                                                                        |                        |

|                        |                                                                                                                      | •                                                                                     |                        |

| According to           | o International Patent Classification (IPC) or to both national classific                                            | ation and IDO                                                                         |                        |

|                        | SEARCHED                                                                                                             | ation and IPC                                                                         |                        |

| Minimum do             | ocumentation searched (classification system followed by classification                                              | on symbols)                                                                           |                        |

| IPC 6                  | H01L                                                                                                                 |                                                                                       |                        |

|                        |                                                                                                                      |                                                                                       |                        |

| Documenta              | tion searched other than minimum documentation to the extent that s                                                  | uch documents are included in the fields se                                           | earched                |

|                        |                                                                                                                      |                                                                                       |                        |

| Electronic d           | ata base consulted during the international search (name of data ba                                                  | se and, where practical, search terms used                                            | 1)                     |

|                        |                                                                                                                      |                                                                                       | ,                      |

|                        |                                                                                                                      |                                                                                       |                        |

|                        |                                                                                                                      |                                                                                       |                        |

| C DOCUM                | ENTS CONSIDERED TO BE RELEVANT                                                                                       |                                                                                       |                        |

| Category °             | Citation of document, with indication, where appropriate, of the rei                                                 | A                                                                                     |                        |

|                        | oraclion of document, with indication, where appropriate, of the ref                                                 | evant passages                                                                        | Relevant to claim No.  |

| Α                      | US 5 378 919 A (OCHIAI AKIHIKO)                                                                                      |                                                                                       | 1.6.0                  |

|                        | 3 January 1995 (1995-01-03)                                                                                          |                                                                                       | 1-6,9                  |

|                        | cited in the application                                                                                             |                                                                                       |                        |

|                        | column 3, line 35 -column 6, line                                                                                    | 24;                                                                                   |                        |

|                        | figures 1-6                                                                                                          |                                                                                       |                        |

| Α                      | YOSHINO A ET AL: "HIGH-SPEED PEF                                                                                     | RFORMANCE                                                                             | 1,6                    |

|                        | OF 0.35 MUM CMOS GATES FABRICATED                                                                                    | ON LOW-                                                                               |                        |

|                        | DOSE SIMOC SUBSTRATES WITH/WITHOU                                                                                    | JT AN                                                                                 |                        |

|                        | N-WELL UNDERNEATH THE BURIED OXIC<br>IEEE ELECTRON DEVICE LETTERS,                                                   | PE LAYER"                                                                             |                        |

|                        | vol. 17, no. 3, 1 March 1996 (199                                                                                    | 06-03-01),                                                                            |                        |

|                        | pages 106-108, XP000584745                                                                                           | , ,                                                                                   |                        |

|                        | the whole document                                                                                                   |                                                                                       |                        |

|                        | -                                                                                                                    | -/                                                                                    |                        |

|                        |                                                                                                                      |                                                                                       |                        |

|                        |                                                                                                                      |                                                                                       |                        |

|                        |                                                                                                                      |                                                                                       |                        |

|                        |                                                                                                                      |                                                                                       |                        |

| X Furth                | ner documents are listed in the continuation of box C.                                                               | X Patent family members are listed                                                    | in annex.              |

| ° Special ca           | tegories of cited documents :                                                                                        | "T" later document published after the inte                                           | ernational filing date |

| "A" docume             | ent defining the general state of the art which is not<br>ered to be of particular relevance                         | or priority date and not in conflict with<br>cited to understand the principle or the | the application but    |

|                        | ocument but published on or after the international                                                                  | invention "X" document of particular relevance; the c                                 | Naimed invention       |

| "L" docume             | nt which may throw doubts on priority claim(s) or                                                                    | cannot be considered novel or cannot involve an inventive step when the do            | be considered to       |

| citation               | (                                                                                                                    | "Y" document of particular relevance; the considered to involve an in-                | claimed invention      |

| other r                |                                                                                                                      | document is combined with one or mo<br>ments, such combination being obvious          | ore other such docu-   |

| "P" docume<br>later th | ent published prior to the international filing date but<br>nan the priority date claimed                            | in the art. "&" document member of the same patent                                    | ·                      |

|                        | actual completion of the international search                                                                        | Date of mailing of the international sea                                              |                        |

|                        |                                                                                                                      |                                                                                       | F                      |

| 2                      | 1 September 1999                                                                                                     | 29/09/1999                                                                            |                        |

| Name and n             | nailing address of the ISA                                                                                           | Authorized officer                                                                    |                        |

|                        | European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel (-21, 70) 200 200 Tv. 21,551 app. pt. |                                                                                       |                        |

|                        | Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax: (+31-70) 340-3016                                                 | Albrecht, C                                                                           |                        |

# INTERNATIONAL SEARCH REPORT

In national Application No

P∪ Γ/FR 99/01403

|            | ation) DOCUMENTS CONSIDERED TO BE RELEVANT                                                                                                         |                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category ° | Citation of document, with indication, where appropriate, of the relevant passages                                                                 | Relevant to claim No. |

| A          | EP 0 694 977 A (NIPPON ELECTRIC CO)<br>31 January 1996 (1996-01-31)<br>page 10, column 15, line 14 -page 13,<br>column 21, line 33; figures 30-41N | 1,6                   |

| 4          | DE 44 41 724 A (SIEMENS AG) 30 May 1996 (1996-05-30) the whole document                                                                            | 1,6                   |

|            |                                                                                                                                                    |                       |

|            |                                                                                                                                                    |                       |

|            |                                                                                                                                                    |                       |

# INTERNATIONAL SEARCH REPORT

Information on patent family members

In rational Application No PUT/FR 99/01403

| Patent document cited in search report |   | Publication date | Patent family member(s) | Publication date |

|----------------------------------------|---|------------------|-------------------------|------------------|

| US 5378919                             | Α | 03-01-1995       | JP 4237166 A            | 25-08-1992       |

| EP 0694977                             | Α | 31-01-1996       | JP 8032040 A            | 02-02-1996       |

| DE 4441724                             | Α | 30-05-1996       | NONE                    |                  |

Form PCT/ISA/210 (patent family annex) (July 1992)

# RAPPORT DE RECHERCHE INTERNATIONALE

Pu f/FR 99/01403

Pur/FR 99/01403 A. CLASSEMENT DE L'OBJET DE LA DEMANDE CIB 6 H01L27/12 H01L21 H01L21/84 H01L21/762 H01L29/786 Selon la classification internationale des brevets (CIB) ou à la fois selon la classification nationale et la CIB B. DOMAINES SUR LESQUELS LA RECHERCHE A PORTE Documentation minimale consultée (système de classification suivi des symboles de classement) CIB 6 H01L Documentation consultée autre que la documentation minimale dans la mesure où ces documents relèvent des domaines sur lesquels a porté la recherche Base de données électronique consultée au cours de la recherche internationale (nom de la base de données, et si réalisable, termes de recherche utilisés) C. DOCUMENTS CONSIDERES COMME PERTINENTS Catégorie Identification des documents cités, avec, le cas échéant, l'indication des passages pertinents no. des revendications visées Α US 5 378 919 A (OCHIAI AKIHIKO) 1-6,93 janvier 1995 (1995-01-03) cité dans la demande colonne 3, ligne 35 -colonne 6, ligne 24; figures 1-6 Α YOSHINO A ET AL: "HIGH-SPEED PERFORMANCE 1,6 OF 0.35 MUM CMOS GATES FABRICATED ON LOW-DOSE SIMOC SUBSTRATES WITH/WITHOUT AN N-WELL UNDERNEATH THE BURIED OXIDE LAYER" IEEE ELECTRON DEVICE LETTERS vol. 17, no. 3, 1 mars 1996 (1996-03-01), pages 106-108, XP000584745 le document en entier -/--Voir la suite du cadre C pour la fin de la liste des documents X Les documents de familles de brevets sont indiqués en annexe Catégories spéciales de documents cités: document ultérieur publié après la date de dépôt international ou la "A" document définissant l'état général de la technique, non date de priorité et n'appartenenant pas à l'état de la technique pertinent, mais cité pour comprendre le principe considéré comme particulièrement pertinent ou la théorie constituant la base de l'invention "E" document antérieur, mais publié à la date de dépôt international "X" document particulièrement pertinent; l'inven tion revendiquée ne peut ou après cette date "L" document pouvant jeter un doute sur une revendication de priorité ou cité pour déterminer la date de publication d'une autre citation ou pour une raison spéciale (telle qu'indiquée) être considérée comme nouvelle ou comme impliquant une activité inventive par rapport au document considéré isolément "Y" document particulièrement pertinent; l'inven tion revendiquée ne peut être considérée comme impliquant une activité inventive lorsque le document est associé à un ou plusieurs autres "O" document se référant à une divulgation orale, à un usage, à une exposition ou tous autres moyens documents de même nature, cette combinaison étant évidente pour une personne du métier "P" document publié avant la date de dépôt international, mais postérieurement à la date de priorité revendiquée "&" document qui fait partie de la même famille de brevets Date à laquelle la recherche internationale a été effectivement achevée Date d'expédition du présent rapport de recherche internationale 21 septembre 1999 29/09/1999 Nom et adresse postale de l'administration chargée de la recherche internationale Fonctionnaire autorisé Office Européen des Brevets, P.B. 5818 Patentlaan 2. NL – 2280 HV Rijswijk Tel. (+31–70) 340–2040, Tx. 31 651 epo nl, Albrecht, C Fax: (+31-70) 340-3016

1

# RAPPORT DE RECHERCHE INTERNATIONALE

De Inde Internationale No

PUI/FR 99/01403

| C.(suite) DOCUMENTS CONSIDERES COMME PERTINENTS  Catégorie * Identification des documents cités, avec le cas échéant. l'Indicationdes passages pertinents |                                                                                                                                                        |           |                               |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------|--|

| Categorie °                                                                                                                                               | Identification des documents cités, avec,le cas échéant, l'Indicationdes passages p                                                                    | ertinents | no. des revendications visées |  |

| A                                                                                                                                                         | EP 0 694 977 A (NIPPON ELECTRIC CO)<br>31 janvier 1996 (1996-01-31)<br>page 10, colonne 15, ligne 14 -page 13,<br>colonne 21, ligne 33; figures 30-41N |           | 1,6                           |  |

| 4                                                                                                                                                         | DE 44 41 724 A (SIEMENS AG) 30 mai 1996 (1996-05-30) le document en entier                                                                             |           | 1,6                           |  |

|                                                                                                                                                           |                                                                                                                                                        |           |                               |  |

|                                                                                                                                                           |                                                                                                                                                        |           |                               |  |

|                                                                                                                                                           |                                                                                                                                                        |           |                               |  |

|                                                                                                                                                           |                                                                                                                                                        |           |                               |  |

|                                                                                                                                                           |                                                                                                                                                        |           |                               |  |

|                                                                                                                                                           |                                                                                                                                                        |           |                               |  |

|                                                                                                                                                           |                                                                                                                                                        |           |                               |  |

|                                                                                                                                                           |                                                                                                                                                        |           |                               |  |

1

# RAPPORT DE RECHERCHE INTERNATIONALE

Dr. ande Internationale No PUT/FR 99/01403

| Document brevet cité<br>au rapport de recherche |   | Date de publication |       |           | Date de publication |  |

|-------------------------------------------------|---|---------------------|-------|-----------|---------------------|--|

| US 5378919                                      | Α | 03-01-1995          | JP    | 4237166 A | 25-08-1992          |  |

| EP 0694977                                      | Α | 31-01-1996          | JP    | 8032040 A | 02-02-1996          |  |

| DE 4441724 A                                    |   | 30-05-1996          | AUCUN |           |                     |  |

Formulaire PCT/ISA/210 (annexe familles de brevets) (juillet 1992)