(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7552506号**

**(P7552506)**

(45)発行日 令和6年9月18日(2024.9.18)

(24)登録日 令和6年9月9日(2024.9.9)

(51)国際特許分類

|        |                |        |      |   |

|--------|----------------|--------|------|---|

| H 02 M | 1/00 (2007.01) | H 02 M | 1/00 | E |

| H 02 M | 1/08 (2006.01) | H 02 M | 1/08 | A |

F I

請求項の数 4 (全12頁)

|          |                             |

|----------|-----------------------------|

| (21)出願番号 | 特願2021-91317(P2021-91317)   |

| (22)出願日  | 令和3年5月31日(2021.5.31)        |

| (65)公開番号 | 特開2022-183824(P2022-183824) |

|          | A)                          |

| (43)公開日  | 令和4年12月13日(2022.12.13)      |

| 審査請求日    | 令和5年6月16日(2023.6.16)        |

|          |                                          |

|----------|------------------------------------------|

| (73)特許権者 | 000004260<br>株式会社デンソー<br>愛知県刈谷市昭和町1丁目1番地 |

| (74)代理人  | 110000567<br>弁理士法人サトー                    |

| (72)発明者  | 小林 敦<br>愛知県刈谷市昭和町1丁目1番地 株式<br>会社デンソー内    |

| (72)発明者  | 山内 一輝<br>愛知県刈谷市昭和町1丁目1番地 株式<br>会社デンソー内   |

| 審査官      | 今井 貞雄                                    |

最終頁に続く

(54)【発明の名称】 ゲート駆動装置

**(57)【特許請求の範囲】****【請求項1】**

ゲート駆動形の半導体スイッチング素子に対して駆動回路によりゲート駆動信号を与えてオンオフの制御を行うゲート駆動装置であって、

前記半導体スイッチング素子の主端子間の電圧を検出し、オン駆動時に主端子間電圧が上昇に転じたことをもって前記半導体スイッチング素子の短絡状態を判定する判定回路(30、30a、30b、30c)と、

前記判定回路により前記半導体スイッチング素子の短絡状態が判定されたときに前記半導体スイッチング素子を遮断する制御回路(20)と、

を備え、

前記判定回路は、

前記半導体スイッチング素子の主端子間電圧のボトム電圧を保持するボトムホールド回路(40、40a)と、

前記半導体スイッチング素子の前記主端子間電圧が、前記ボトム電圧をヒステリシス電圧分を加算した参照電圧よりも大きくなったときに短絡状態を判定する比較回路(50、50a、50b)と、

を備えるゲート駆動装置。

**【請求項2】**

前記ボトムホールド回路は、前記半導体スイッチング素子がオフすると前記ボトム電圧の保持をリセットするリセットスイッチ(44)を備える請求項1に記載のゲート駆動装

置。

**【請求項 3】**

前記比較回路は、前記ヒステリシス電圧分を調整可能な可変ヒステリシス電源（54）を備える請求項1または2に記載のゲート駆動装置。

**【請求項 4】**

前記半導体スイッチング素子の主端子間の電圧を分圧する分圧回路（2）を備え、

前記判定回路は、前記分圧回路により分圧された前記半導体スイッチング素子の主端子間の電圧を入力して前記半導体スイッチング素子の短絡状態を判定する請求項1から3のいずれかに記載のゲート駆動装置。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

本発明は、ゲート駆動装置に関する。

**【背景技術】**

**【0002】**

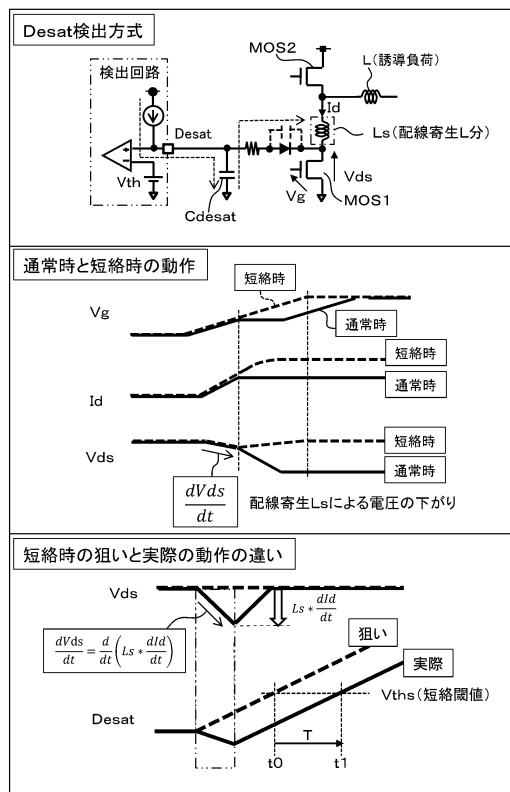

ゲート駆動型の半導体スイッチング素子であるMOSトランジスタなどのパワー素子を駆動制御するゲート駆動装置は、短絡時を検出する機能を備えたものがある。短絡時を検出する方式として、Desat方式がある。これは、オン指令時に短絡している場合にはドレイン・ソース間電圧Vdsが下がらない現象を利用するもので、ドレイン・ソース間電圧Vdsをモニタし、短絡しきい値と比較して短絡時を判定するものである。

20

**【0003】**

Desat方式では、ターンオン指令により、パワー素子のゲート電圧が上昇すると共に、定電流IdesatによりコンデンサCdesatに電荷が充電され、Desat端の電圧すなわちコンデンサCdesatの端子電圧が上昇する。

**【0004】**

この場合、通常時は、パワー素子がオンすると、ドレイン・ソース間電圧Vdsが低下するので、定電流Idesatは、ダイオードを介してパワー素子側に流れ、コンデンサCdesatへの充電が停止るので、Desat端の電圧は短絡しきい値よりも低くなり、通常時と判定することができる。

**【0005】**

30

一方、短絡時は、ドレイン・ソース間電圧Vdsが下がらないので、コンデンサCdesatへの定電流Idesatによる充電は継続することとなり、やがて短絡しきい値を超えて、短絡時を判定することができる。そして、短絡時が判定されると、ゲート駆動装置は、ゲート電圧を下げパワー素子を遮断する。

**【0006】**

しかしながら、このようにパワー素子のドレイン・ソース間電圧Vdsをモニタし、短絡を検出するDesat方式では、パワー素子の電流経路に含まれる配線寄生インダクタンスLsの影響によって短絡判定の遅れを招くことがある。そして、短絡判定の遅れは短絡時にパワー素子に加わる短絡エネルギーを増大させることとなる。また、短絡エネルギーが増大することは、これに耐性を持たせるためには、パワー素子の大型化を招くこととなる。

40

**【先行技術文献】**

**【特許文献】**

**【0007】**

**【文献】特許06525141号公報**

**【文献】特開2017-212870号公報**

**【文献】国際公開番号WO2017/141545A1**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0008】**

50

本発明は、上記事情を考慮してなされたもので、その目的は、ゲート駆動型のスイッチング素子を駆動するときに、短絡時である場合にこれを迅速に判定することができ、スイッチング素子の短絡エネルギーを抑制させることで大型化することを回避できるようにしたゲート駆動装置を提供することにある。

**【課題を解決するための手段】**

**【0009】**

請求項1に記載のゲート駆動装置は、ゲート駆動形の半導体スイッチング素子に対して駆動回路によりゲート駆動信号を与えてオンオフの制御を行うゲート駆動装置であって、前記半導体スイッチング素子の主端子間の電圧を検出し、オン駆動時に主端子間電圧が上昇に転じたことをもって前記半導体スイッチング素子の短絡時を判定する判定回路(30、30a、30b、30c)と、前記判定回路により前記半導体スイッチング素子の短絡状態が判定されたときに前記半導体スイッチング素子を遮断する制御回路(20)とを備えている。前記判定回路は、前記半導体スイッチング素子の主端子間電圧のボトム電圧を保持するボトムホールド回路(40、40a)と、前記半導体スイッチング素子の前記主端子間電圧が、前記ボトム電圧をヒステリシス電圧分を加算した参照電圧よりも大きくなったときに短絡状態を判定する比較回路(50、50a、50b)と、を備えている。

10

**【0010】**

半導体スイッチング素子を上下アームに接続して負荷に給電する構成では、配線寄生インダクタンスがあるため、スイッチング動作の際に短絡があると、半導体スイッチング素子の主端子間電圧が、一度下がってから再び上がってくるという特性がある。このため、一般的に用いられるDesat方式による短絡判定では、主端子間電圧がしきい値レベルまで上昇するのに遅れ時間を伴うため判定遅れが生ずる。

20

**【0011】**

これに対して、本方式では、上記構成を採用することにより、半導体スイッチング素子を駆動したときに、通常時と短絡時とで異なる主端子間電圧の変化を検出することで短絡時を判定することができる。

**【0012】**

すなわち、通常時には半導体スイッチング素子の主端子間電圧はオン状態で最も低い電圧に保持されるが、短絡時には半導体スイッチング素子の主端子間電圧が、一度下がってから再び上がってくる。このような特性の相違を利用して、判定回路では、半導体スイッチング素子の主端子間電圧が上昇することをもって短絡時を判定することができる。

30

**【0013】**

したがって、一定のしきい値まで上昇するのを待って検出する方式と異なり、上昇に転じたことで判定するので、迅速に短絡状態を判定することができ、パワー素子として用いる半導体スイッチング素子の小型化を図ることができる。

**【図面の簡単な説明】**

**【0014】**

**【図1】第1実施形態を示す電気的構成図**

**【図2】第1実施形態を示す作用説明図**

**【図3】第2実施形態を示す電気的構成図**

40

**【図4】第2実施形態を示すタイミングチャート**

**【図5】第3実施形態を示す電気的構成図**

**【図6】第4実施形態を示す電気的構成図**

**【図7】第4実施形態を示す作用説明図**

**【図8】第5実施形態を示す電気的構成図**

**【図9】比較のために示す作用説明図**

**【発明を実施するための形態】**

**【0015】**

(第1実施形態)

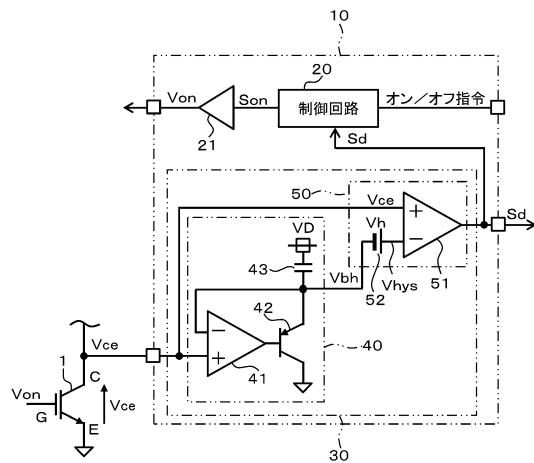

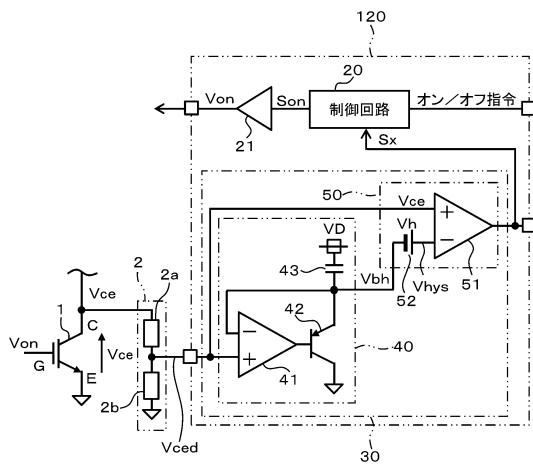

以下、本発明の第1実施形態について、図1、図2および図9を参照して説明する。

50

電気的構成を示す図1において、パワー素子であるゲート駆動形の半導体スイッチング素子としてのIGBT(Insulated Gate Bipolar Transistor)1を上下アームにそれぞれ配置して負荷への通電経路を形成する回路に対して、ゲート駆動装置10は、一方のIGBT1をオン駆動制御する際に、他方のIGBTが短絡状態にあるかどうかを判定することができるようとした機能を備える。

#### 【0016】

ゲート駆動装置10は、制御回路20、判定回路30などを備えている。制御回路20は、外部から与えられるオン／オフ指令のオン指令信号に基づいてゲート駆動信号Sonを生成し、駆動回路21を介してIGBT1のゲートにゲート駆動電圧Vonを与える。制御回路20は、後述するように、IGBT1のオフ駆動機能も備えており、オン駆動中に短絡が検出された場合にはIGBT1を遮断する。

10

#### 【0017】

判定回路30は、ボトムホールド回路40およびヒステリシス付きのコンパレータを有する比較回路50を備えている。判定回路30は、IGBT1のコレクタ・エミッタ間電圧（以下、単に「コレクタ電圧」と称す）Vceを取り込み、この電圧の変化状態から短絡の有無を検出して出力する。

#### 【0018】

ボトムホールド回路40は、オペアンプ41、トランジスタ42およびコンデンサ43を備える。オペアンプ41は、非反転入力端子にコレクタ電圧Vceが入力され、反転入力端子にはコンデンサ43の端子電圧Vbhが入力される。オペアンプ41の出力端子はトランジスタ42のベースに接続される。

20

#### 【0019】

トランジスタ42のエミッタはコンデンサ43を介して直流電源VDに接続され、コレクタはグランドに接続される。コンデンサ43の端子電圧Vphは、トランジスタ42のエミッタとコンデンサ43の共通接続点の電圧である。オペアンプ41は、コレクタ電圧Vceがコンデンサ43の端子電圧であるボトムホールド電圧Vbhよりも小さい期間中はトランジスタ42をオン駆動し、コンデンサ43の充電電荷を放電させる。

#### 【0020】

これにより、コレクタ電圧Vceがボトム電圧VBに達した後に上昇すると、オペアンプ41の出力信号が大きくなり、トランジスタ42がオフしてコンデンサ43への充電が停止する。この結果、コンデンサ43の端子電圧であるボトムホールド電圧Vbhは、コレクタ電圧Vceのボトム電圧VBとなりこの電圧が保持される。

30

#### 【0021】

比較回路50は、コンパレータ51およびヒステリシス電圧Vhを与えるヒステリシス電源52を備える。コンパレータ51は非反転入力端子にコレクタ電圧Vceが入力され、反転入力端子にボトムホールド回路40の出力電圧であるボトムホールド電圧Vbhを、ヒステリシス電源52を通じてヒステリシス電圧Vhだけ上昇させた電圧が参照電圧Vhysとして入力される。

#### 【0022】

コンパレータ51は、コレクタ電圧Vceが参照電圧Vhysよりも大きいときにはハイレベル、小さくなるとローレベルとなる判定信号Sdを出力する。この判定信号Sdは、制御回路20および外部に出力される。

40

#### 【0023】

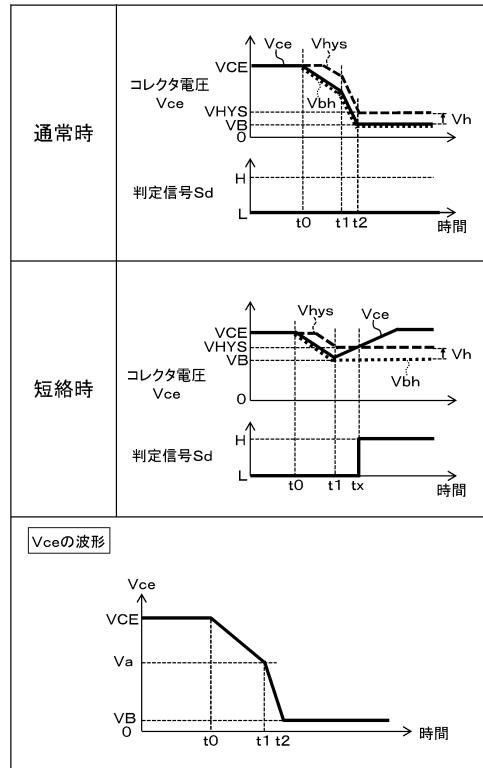

次に、上記構成の作用について、図2および図9も参照して説明する。

まず、Desat方式による課題の原因と、本実施形態の検出方式について、図9を参照してMOSトランジスタを用いた構成で簡単に説明する。上下アームを設けて負荷Lに給電する構成においては、電流経路上に配線寄生インダクタンスLsがDesat方式における検出動作に悪影響を与えることがある。すなわち、MOS1がオン駆動されたときに、ドレイン電圧Vdsが時間と共に変化するときに、寄生インダクタンスLsによってd(Vds)/dtが発生する。このd(Vds)/dtの発生により、検出回路からM

50

O S 1 のドレインに接続されるダイオードの接合容量によりコンデンサ C d e s a t から電荷が引き抜かれる。

#### 【 0 0 2 4 】

コンデンサ C d e s a t から  $d(V_{dS})/dt$  によって引き抜かれる電荷量が、検出回路側から定電流源によって流し込む電流による電荷量を上回り、D e s a t の容量が充電されるよりも放電される量が大となって、図示のように D e s a t 電圧が下がることがある。この結果、 $d(V_{dS})/dt$  によって引き抜かれた電荷を充電した後に再び充電動作によって D e s a t 電圧が上昇し、しきい値電圧に達することで短絡判定がなされるので、配線寄生 L s がなければ狙いの時刻  $t_0$  で短絡判定ができるところ、D e s a t 電圧が低下してから元の電圧に戻るまでの時間 T だけ遅れた時刻  $t_1$  になって短絡判定がなされるので、大幅な検出時間遅れを招くこととなっていた。10

#### 【 0 0 2 5 】

本実施形態においては、配線寄生インダクタンス L s の影響によってコレクタ電圧 V c e の時間変化に起因して電圧低下が発生することを利用している。I G B T 1 のオン駆動時に短絡状態が発生していると、コレクタ電圧 V c e が一度低下した後に再び上昇するという特性を利用してこれを検知するようにしたものである。

#### 【 0 0 2 6 】

図 2 の下段には、短絡が発生していない通常時において I G B T 1 がゲートに駆動電圧が与えられた後にコレクタ電圧 V c e が変化する様子を示している。ゲート電圧がしきい値電圧に達する時刻  $t_0$  で、コレクタ電圧 V c e は V C E から低下し始める。コレクタ電圧 V c e は、ミラー期間に入ると、電圧 V 1 から低下の傾きが急峻になり、電圧 V 2 に達するとオン状態となる。つまり、I G B T 1 のコレクタ電圧 V c e は、ゲート駆動信号が与えられてオン駆動し始めると、電圧 V 1 を経て電圧 V 2 まで低下する。20

#### 【 0 0 2 7 】

図 2 の上段および中段のそれぞれに、通常時および短絡時におけるコレクタ電圧 V c e と判定信号 S d について示している。まず、通常時においては、制御回路 2 0 が外部からオン / オフ指令によってオン駆動するタイミングになると、駆動回路 2 1 にオン駆動信号 S o n を与えて、I G B T 1 のゲートにゲート駆動電圧 V o n を与える。

#### 【 0 0 2 8 】

これにより、時刻  $t_0$  で I G B T 1 のゲート電圧 V g がしきい値電圧に達すると、コレクタ電圧 V c e は、配線寄生インダクタンス L s の影響でコレクタ電流 I c の時間変化で  $L_s \cdot dI_c/dt$  によって電圧 V C E から低下し始める。この後、時刻  $t_1$  でゲート電圧 V g がミラー期間に入つて一定になると、コレクタ電圧 V c e はさらに急峻に低下していく。時刻  $t_2$  になってミラー期間が終了してコレクタ電流 I c が負荷電流に達すると、I G B T 1 はオン状態となり、コレクタ電圧 V c e はほぼ 0 V の低い電圧で一定となる。このときのコレクタ電圧 V c e は、これより低下しないから、ボトム電圧 V B となる。30

#### 【 0 0 2 9 】

これに対して、判定回路 3 0 においては、ボトムホールド回路 4 0 にコレクタ電圧 V c e が取り込まれ、オペアンプ 4 1 に入力されている。ボトムホールド回路 4 0 は、コレクタ電圧 V c e が下降している期間中はトランジスタ 4 2 を駆動させてコンデンサ 4 3 に充電することでボトムホールド電圧 V b h を下げていく。コレクタ電圧 V c e がボトム電圧 V B を経てその電圧に保持されるかあるいは上昇する場合には、トランジスタ 4 2 は駆動されず、ボトムホールド電圧 V b h はボトム電圧 V B に保持される。40

#### 【 0 0 3 0 】

比較回路 5 0 においては、ボトムホールド電圧 V b h がヒステリシス電源 5 2 を介してヒステリシス電圧 V h が加算された参照電圧 V h y s としてコンパレータ 5 1 に入力される。コンパレータ 5 1 は、コレクタ電圧 V c e が参照電圧 V h y s よりも大きくなることはないので、通常時であると判定してローレベルの判定信号 S d を出力する。

#### 【 0 0 3 1 】

次に、短絡時においては、同様に、制御回路 2 0 が外部からオン / オフ指令によってオ50

ン駆動するタイミングになると、駆動回路 21 にオン駆動信号  $S_{on}$  を与えて、IGBT 1 のゲートにゲート駆動電圧  $V_{on}$  を与える。

#### 【0032】

これにより、時刻  $t_0$  で IGBT 1 のゲート電圧  $V_g$  がしきい値電圧に達すると、コレクタ電圧  $V_{ce}$  は、配線寄生インダクタンス  $L_s$  の影響でコレクタ電流  $I_c$  の時間変化で  $L_s \cdot dI_c / dt$  によって電圧  $V_{CE}$  から一旦低下し始め、この後、時刻  $t_1$  以後は再び上昇していく。したがって、コレクタ電圧  $V_{ce}$  のボトム電圧  $V_B$  は、一旦低下した時刻  $t_1$  の時点の電圧となる。

#### 【0033】

これに対して、判定回路 30においては、ボトムホールド回路 40により時刻  $t_1$  のボトム電圧  $V_B$  がボトムホールド電圧  $V_{bh}$  として検出され、このボトム電圧  $V_B$  が保持される。比較回路 50においては、ボトムホールド電圧  $V_{bh}$  にヒステリシス電圧  $V_h$  を加算した参照電圧  $V_{hy}$  がコンパレータ 51に入力される。コンパレータ 51は、コレクタ電圧  $V_{ce}$  がボトム電圧  $V_B$  から上昇する途中の時刻  $t_x$  で参照電圧  $V_{hy}$  よりも大きくなるので、短絡時であると判定してハイレベルの判定信号  $S_d$  を出力する。これにより、制御回路 20は、判定回路 30からハイレベルの判定信号  $S_d$  が入力された時点で IGBT 1をオフさせて遮断するようになる。

10

#### 【0034】

このような本実施形態によれば、判定回路 30としてボトムホールド回路 40および比較回路 50を設け、コレクタ電圧  $V_{ce}$  のボトムホールド電圧から参照電圧  $V_{hy}$  を生成してコレクタ電圧  $V_{ce}$ との比較により短絡状態を判定するようにしたので、従来の Dsat 方式による検出と異なり、短絡を早期に検出することができるようになり、IGBT 1を早期に遮断することで過剰な耐性を持たせたものを使用する必要がなくなり、パワー素子として用いる半導体スイッチング素子の小型化に貢献できる。

20

#### 【0035】

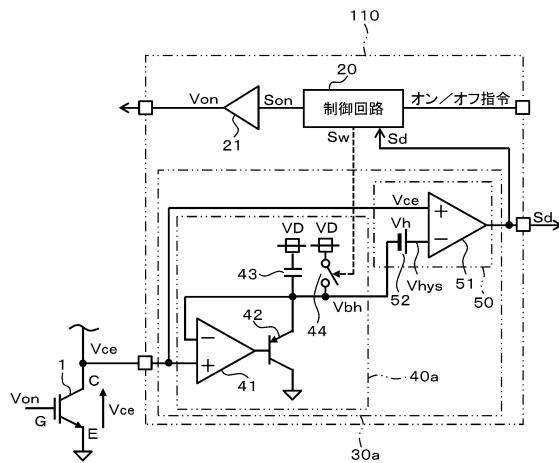

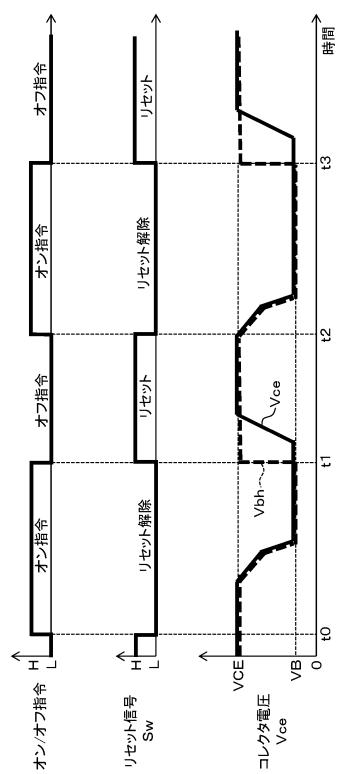

##### (第2実施形態)

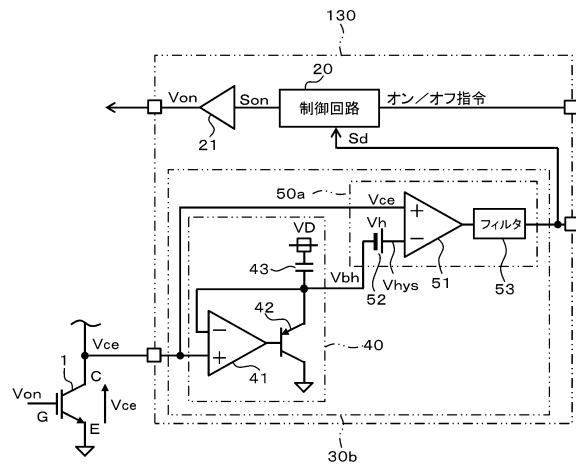

図 3 および図 4 は第2実施形態を示すもので、以下、第1実施形態と異なる部分について説明する。この実施形態では、第1実施形態におけるような判定回路 30のボトムホールド回路 40によりコレクタ電圧  $V_{ce}$  のボトムホールド電圧  $V_{bh}$  を検出する場合に、コレクタ電圧  $V_{ce}$  の波形が異なる場合に対応してボトムホールド電圧  $V_{bh}$  をスイッチング毎にリセットできるようにしたものである。

30

#### 【0036】

図 3において、ゲート駆動装置 110は、判定回路 30に代えて判定回路 30aを備えている。判定回路 30aは、ボトムホールド回路 40に代わるボトムホールド回路 40aを備える。ボトムホールド回路 40aは、リセットスイッチ 44が追加された構成である。リセットスイッチ 44は、コンデンサ 43の両端子間を短絡可能に接続されている。また、リセットスイッチ 44は、制御回路 20からリセット信号  $S_w$  が与えられるとオンしてコンデンサ 43の端子間を短絡状態として電荷の放電を実施する。

#### 【0037】

次に、上記構成の作用について説明する。図 4 は各部の信号の変化状態を示している。この実施形態では、制御回路 20は、オン／オフ指令によりオン指令信号が与えられている期間中は、リセットスイッチ 44をリセット解除すなわちローレベルのリセット信号  $S_w$  を与えてオフ状態に保持し、オフ指令信号が与えられている期間中は、リセットスイッチ 44をリセット状態すなわちハイレベルのリセット信号  $S_w$  を与えてオン状態に保持する。

40

#### 【0038】

これにより、時刻  $t_0$  のタイミングでオン指令が与えられると、リセットスイッチ 44は、リセット信号  $S_w$  がローレベルとなってリセット解除となり、ボトムホールド回路 40aでは、コレクタ電圧  $V_{ce}$  のボトムホールドを行い、コンデンサ 43にボトムホールド電圧  $V_B$  が出力される。これにより、前述した判定処理の動作が行われる。

50

**【 0 0 3 9 】**

この後、時刻  $t_1$  でオン指令からオフ指令に切り替わると、制御回路 20 は、リセットスイッチ 44 にハイレベルのリセット信号  $S_w$  を出力してリセット動作させ、コンデンサ 43 の電荷を放電させ、ボトムホールド電圧  $V_{b\ h}$  を電圧  $V_{C\ E}$  にする。オフ指令が与えられている期間中は、ボトムホールド電圧  $V_{b\ h}$  が電圧  $V_{C\ E}$  に保持される。

**【 0 0 4 0 】**

時刻  $t_2$  で再びオン指令が与えられると、時刻  $t_3$  のオフ指令が与えられるまでの間、制御回路 20 はリセット信号  $S_w$  を解除する。以下、上述と同様にして、制御回路 20 は、スイッチング毎にリセット解除を実施してコレクタ電圧  $V_{c\ e}$  が変動する場合でも、これに対応してその都度ボトムホールド電圧  $V_{b\ h}$  がそのときのボトム電圧  $V_B$  に追随できるように動作させることができる。10

**【 0 0 4 1 】**

このような第 2 実施形態によれば、ボトムホールド回路 40a にリセットスイッチ 44 を設けて、スイッチング毎にボトムホールド電圧  $V_{b\ h}$  をリセットさせるようにしたので、コレクタ電圧  $V_{c\ e}$  がスイッチング毎に変動した場合でも、ボトムホールド電圧  $V_{b\ h}$  を正確に検出できるようになる。

**【 0 0 4 2 】**

なお、リセットはオフ指令が与えられている期間中行う上記実施形態の場合に加えて、ノイズなどによる悪影響が無い場合には、オフ指令が与えられた直後に短時間で実施することもできる。20

**【 0 0 4 3 】****( 第 3 実施形態 )**

図 5 は第 3 実施形態を示すもので、以下、第 1 実施形態と異なる部分について説明する。この実施形態では、ゲート駆動装置 120 は、IGBT 1 のコレクタ電圧  $V_{c\ e}$  を直接取り込むのではなく、分圧回路 2 を介して分圧コレクタ電圧  $V_{c\ e\ d}$  を取り込む構成としている。

**【 0 0 4 4 】**

分圧回路 2 は、分圧抵抗 2a および 2b を直列接続したもので、コレクタ電圧  $V_{c\ e}$  を分圧回路 2 の一端子に入力し、分圧抵抗 2a および 2b の共通接続点から分圧された分圧コレクタ電圧  $V_{c\ e\ d}$  を得る構成である。30

**【 0 0 4 5 】**

IGBT 1 の使用形態によっては、コレクタに高電圧が印加される場合がある。このような場合においては、ゲート駆動装置 120 においては、高電圧のコレクタ電圧  $V_{c\ e}$  を取り込んで判定回路 30 により判定を行う構成においても高電圧を取り扱える構成が必要となるので、全体が大型化したり高価になったりすることがあるが、本実施形態のように分圧コレクタ電圧  $V_{c\ e\ d}$  を取り扱えるようにすることで小型化、低価格化を図ることができる。

なお、分圧回路 2 は、分圧抵抗 2a、2b による構成に限らず、2 個のコンデンサにより分圧する構成とすることもできる。

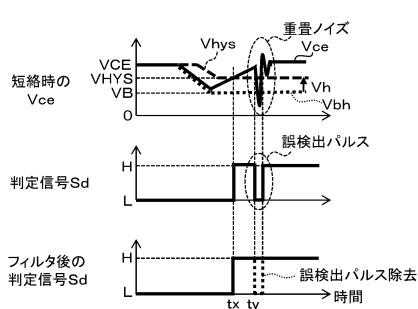

**【 0 0 4 6 】****( 第 4 実施形態 )**

図 6 および図 7 は第 4 実施形態を示すもので、以下第 1 実施形態と異なる部分について説明する。この実施形態では、ゲート駆動装置 130 として、図 6 に示すように、判定回路 30b の比較回路 50a の出力段にフィルタ 53 を設けている。フィルタ 53 は、ノイズを除去するためのローパスフィルタの機能を持つもので、コレクタ電圧  $V_{c\ e}$  などに重畠されるノイズを除去して判定信号  $S_d$  を出力しようとするものである。

**【 0 0 4 7 】**

これにより、例えば図 7 に示すように、判定回路 30b において、入力されるコレクタ電圧  $V_{c\ e}$  が短絡時のものであって、時刻  $t_x$  で短絡状態を判定するハイレベルの判定信号  $S_d$  が出力された後に、時刻  $t_y$  でコレクタ電圧  $V_{c\ e}$  にノイズが重畠した場合には、50

判定信号 S<sub>d</sub> が一時的にローレベルの誤検出パルスを出力してしまう恐れがあった。

#### 【 0 0 4 8 】

これに対して、この実施形態においては、時刻 t<sub>y</sub> でフィルタ前の判定信号 S<sub>d</sub> にノイズに起因したハイレベルの信号が出力されていた場合でも、フィルタ 5<sub>3</sub> を介して出力される判定信号 S<sub>d</sub> ではノイズによるハイレベルの信号部分が除去されるので、誤検出することなく検出動作が行われる。

#### 【 0 0 4 9 】

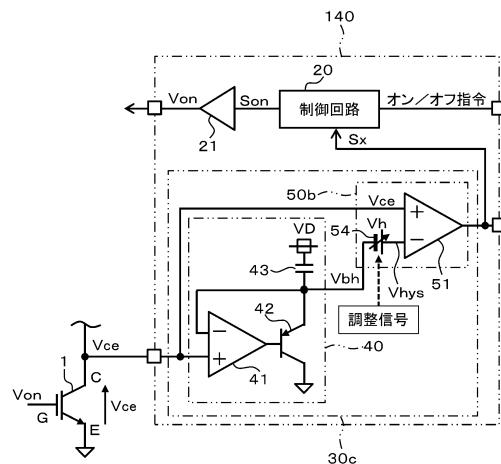

##### ( 第 5 実施形態 )

図 8 は第 5 実施形態を示すもので、以下第 1 実施形態と異なる部分について説明する。

この実施形態では、図 8 に示すように、ゲート駆動装置 1<sub>4</sub>0 は、判定回路 3<sub>0</sub>c において、比較回路 5<sub>0</sub>b として、ヒステリシス電源 5<sub>2</sub> に代えてヒステリシス電圧 V<sub>h</sub> を変更設定することができる可変ヒステリシス電源 5<sub>4</sub> を設ける構成としている。 10

#### 【 0 0 5 0 】

可変ヒステリシス電源 5<sub>4</sub> により、ヒステリシス電圧 V<sub>h</sub> を変更設定することで、システムにおいて発生するノイズで誤動作しないように適切なヒステリシス電圧 V<sub>h</sub> とすることができる。システムにおいてノイズ量は様々であるから、そのノイズ量に応じてヒステリシス電圧 V<sub>h</sub> を調整することで誤動作の発生を抑制することができる。

#### 【 0 0 5 1 】

##### ( 他の実施形態 )

なお、本発明は、上述した実施形態のみに限定されるものではなく、その要旨を逸脱しない範囲で種々の実施形態に適用可能であり、例えば、以下のように変形または拡張することができる。 20

#### 【 0 0 5 2 】

上記各実施形態では、パワー素子として IGBT を用いた場合で説明したが、IGBT 以外に SiCMOS トランジスタなどのパワー系のゲート駆動型の半導体スイッチング素子のいずれにおいても適用することができる。

上記各実施形態は、第 1 実施形態を基本とし、その応用として示しているが、もちろん他の実施形態に複合的に適用することもできる。

#### 【 0 0 5 3 】

本開示は、実施例に準拠して記述されたが、本開示は当該実施例や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。 30

#### 【 符号の説明 】

#### 【 0 0 5 4 】

図面中、1 は IGBT ( ゲート駆動型の半導体スイッチング素子 ) 、2 は分圧回路、1<sub>0</sub>、1<sub>1</sub>0、1<sub>2</sub>0、1<sub>3</sub>0 はゲート駆動装置、2<sub>0</sub> は制御回路、2<sub>1</sub> は駆動回路、3<sub>0</sub>、3<sub>0</sub>a、3<sub>0</sub>b、3<sub>0</sub>c は判定回路、4<sub>0</sub>、4<sub>0</sub>a はボトムホールド回路、4<sub>1</sub> はオペアンプ、4<sub>2</sub> はトランジスタ、4<sub>3</sub> はコンデンサ、4<sub>4</sub> はリセットスイッチ、5<sub>0</sub>、5<sub>0</sub>a、5<sub>0</sub>b は比較回路、5<sub>1</sub> はコンパレータ、5<sub>2</sub> はヒステリシス電源、5<sub>3</sub> はフィルタ、5<sub>4</sub> は可変ヒステリシス電源である。 40

## 【図面】

## 【図 1】

Fig.1

## 【図 2】

Fig.2

## 【図 3】

Fig.3

## 【図 4】

Fig.4

10

20

30

40

50

【図 5】

Fig.5

【図 6】

Fig.6

【図 7】

Fig.7

【図 8】

Fig.8

10

20

30

40

50

【図 9】

Fig.9

10

20

30

40

50

---

フロントページの続き

(56)参考文献 国際公開第2014/115272 (WO, A1)

(58)調査した分野 (Int.Cl., DB名)

H02M 1/00 - 1/44