등록특허 10-2384829

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년04월07일

(11) 등록번호 10-2384829

(24) 등록일자 2022년04월05일

- (51) 국제특허분류(Int. Cl.)

*H05K 7/02* (2006.01) *A61J 1/03* (2006.01)

*B65B 57/02* (2006.01) *B65D 75/32* (2006.01)

- (52) CPC특허분류

*H05K 7/02* (2013.01)

*A61J 1/035* (2013.01)

- (21) 출원번호 10-2018-7013077

- (22) 출원일자(국제) 2016년10월05일

심사청구일자 2021년10월01일

- (85) 번역문제출일자 2018년05월08일

- (65) 공개번호 10-2018-0073594

- (43) 공개일자 2018년07월02일

- (86) 국제출원번호 PCT/US2016/055516

- (87) 국제공개번호 WO 2017/062464

국제공개일자 2017년04월13일

(30) 우선권주장

14/879,874 2015년10월09일 미국(US)

- (56) 선행기술조사문현

WO2010108838 A1

US20100089789 A1

US08960440 B

JP2013031638 A

전체 청구항 수 : 총 13 항

심사관 : 정상민

## (54) 발명의 명칭 접속된 패키징

## (57) 요약

태블릿(112)이 블리스터 팩과 같은 용기로부터 언제 제거되었는지를 결정하기 위한 방법 및 장치가 개시되어 있다. 본 방법은 블리스터 팩(400) 내에 포함된 비폐단화된 덮개 막(104)과 전기적 통신하는 적어도 2개의 단자들(402) 사이에서, 전기적 저항 또는 임피던스와 같은 전기적 특성을 측정하는 것을 포함하고, 여기서, 블리스터 팩(400)으로부터의 태블릿(112)의 제거는 덮개 막(104)에서의 개구부로 귀착됨으로써, 전기적 특성에서의 유한한 변화를 야기시킨다

## 대 표 도

(52) CPC특허분류

*B65B 57/02* (2013.01)

*B65D 75/327* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

하나 이상의 제품 유닛들을 포함하기 위한 장치로서,

제 1 층;

각각의 단자가 상기 제 1 층에서의 개구부의 형성 전 및 후에 상기 제 1 층을 통해 제 1 복수의 단자들의 각각의 다른 단자와 전기적으로 통신하도록 배열되는 상기 제 1 복수의 단자들; 및

상기 복수의 단자들의 각각의 단자와 각각의 다른 단자 사이에서 제 1 전기적 파라미터의 쌍별(pair-wise) 측정들을 행하기 위하여 동작하는 전자 회로부를 포함하고;

상기 제 1 층은 실질적으로 연속적이고, 전기적 전도성이고 비페던화되는 제 1 영역을 포함하고; 그리고

상기 복수의 단자들은 제 1 로케이션에서의 상기 제 1 층에서의 상기 개구부의 형성이 상기 복수의 단자들의 제 1 단자와 제 2 단자 사이에서 측정된 상기 제 1 전기적 파라미터의 크기에서의 제 1 유한한 변화를 야기시키도록 배열되는, 하나 이상의 제품 유닛들을 포함하기 위한 장치.

#### 청구항 2

제 1 항에 있어서,

상기 전자 회로부는 전기적 저항 단층촬영 및 전기적 임피던스 단층촬영으로 구성되는 그룹으로부터 선택된 기법을 통해 상기 제 1 층에서의 적어도 하나의 개구부의 로케이션을 결정하기 위하여 추가로 동작하는, 하나 이상의 제품 유닛들을 포함하기 위한 장치.

#### 청구항 3

제 1 항에 있어서,

상기 전자 회로부는 상기 제 1 전기적 파라미터의 상기 크기에서의 상기 제 1 유한한 변화에 기초하여 제 1 신호를 제공하기 위하여 추가로 동작하는, 하나 이상의 제품 유닛들을 포함하기 위한 장치.

#### 청구항 4

제 1 항에 있어서,

상기 전자 회로부는 상기 복수의 제 1 쌍의 단자들 사이에서 제 1 전기적 자극을 제공하고 제 2 복수의 단자들의 각각의 쌍에서 상기 제 1 전기적 파라미터를 측정함으로써 상기 쌍별 측정들을 행하기 위하여 동작하고, 상기 제 1 복수의 단자들은 제 1 단자, 제 2 단자, 및 상기 제 2 복수의 단자들을 포함하고, 상기 제 2 복수의 단자들은 상기 제 1 단자 및 제 2 단자를 제외하는, 하나 이상의 제품 유닛들을 포함하기 위한 장치.

#### 청구항 5

제 4 항에 있어서,

상기 전자 회로부는 그 상기 제 2 복수의 적어도 하나의 쌍의 단자들 사이에서의 상기 제 1 전기적 파라미터의 상기 크기에서의 제 1 유한한 변화에 기초하여 제 1 신호를 제공하기 위하여 추가로 동작하는, 하나 이상의 제품 유닛들을 포함하기 위한 장치.

#### 청구항 6

제 5 항에 있어서,

상기 전자 회로부는 상기 제 2 복수의 제 3 단자와 제 4 단자 사이에서 제 2 전기적 자극을 제공하고 제 3 복수의 단자들의 각각의 쌍의 단자들 사이에서 상기 제 1 전기적 파라미터를 측정함으로써 상기 쌍별 측정들을 행하

기 위하여 추가로 동작하고, 상기 제 2 복수의 단자들은 상기 제 3 단자, 제 4 단자, 및 상기 제 3 복수의 단자들을 포함하고, 상기 제 3 복수의 단자들은 상기 제 3 단자 및 제 4 단자를 제외하는, 하나 이상의 제품 유닛들을 포함하기 위한 장치.

### 청구항 7

제 4 항에 있어서,

상기 전기적 자극은 전압 및 전류로 구성되는 그룹으로부터 선택되는, 하나 이상의 제품 유닛들을 포함하기 위한 장치.

### 청구항 8

패키지의 상태를 모니터링하기 위한 방법으로서,

상기 패키지가:

제 1 층; 및

하나 이상의 공동들을 포함하는 제 2 층 – 상기 제 1 층 및 제 2 층은 상기 하나 이상의 공동들의 각각 및 상기 제 1 층이 제품 유닛을 유지하기 위하여 동작하는 저장소를 집합적으로 정의하도록 접합됨 – 을 포함하도록 상기 패키지를 제공하는 단계;

각각의 단자가 상기 제 1 층에서의 제 1 개구부의 형성 전 및 후에 상기 제 1 층을 통해 제 1 복수의 단자들의 각각의 다른 단자와 서로 전기적으로 통신하도록 배열되는 제 1 복수의 단자들을 제공하는 단계; 및

상기 제 1 개구부의 형성을 표시하는 제 1 신호를 제공하는 단계를 포함하고;

상기 제 1 층은 실질적으로 연속적이고, 전기적 전도성이고 비페턴화되는 제 1 영역을 포함하도록 제공되고; 그리고

상기 제 1 신호는 상기 제 1 복수의 단자들의 적어도 제 1 쌍의 단자들 사이에서 측정된 제 1 전기적 파라미터의 상기 크기에서의 제 1 유한한 변화에 기초하는 것을 특징으로 하는, 패키지의 상태를 모니터링하기 위한 방법.

### 청구항 9

제 8 항에 있어서,

상기 제 1 유한한 변화가 검출되는 시간에 기초하는 제 2 신호를 제공하는 단계를 더 포함하는, 패키지의 상태를 모니터링하기 위한 방법.

### 청구항 10

제 8 항에 있어서,

그 상기 제 1 복수의 제 2 쌍의 단자들 사이에서 제 1 자극을 제공하는 단계; 및

제 2 복수의 단자들의 각각의 쌍의 단자들 사이에서 상기 제 1 전기적 파라미터를 측정하는 단계 – 상기 제 1 복수의 단자들은 상기 제 2 복수의 단자들을 포함하고, 상기 제 2 복수의 단자들은 상기 제 2 쌍의 단자들을 제외함 – 를 더 포함하고;

상기 제 1 유한한 변화는 상기 제 2 복수의 단자들의 적어도 하나의 쌍 사이에서 측정된 상기 제 1 전기적 파라미터에서 검출되고; 그리고

그 상기 제 2 복수의 각각의 쌍의 단자들에서의 상기 제 1 전기적 파라미터는 상기 제 1 자극에 기초하는, 패키지의 상태를 모니터링하기 위한 방법.

### 청구항 11

제 10 항에 있어서,

그 상기 제 2 복수의 상기 적어도 하나의 쌍의 단자들 사이에서 측정된 상기 전기적 파라미터의 상기 크기에 기

초하여 상기 제 1 개구부의 제 1 로케이션을 추정하는 단계 – 상기 제 1 신호는 상기 제 1 로케이션을 포함하도록 제공됨 – 를 더 포함하는, 패키지의 상태를 모니터링하기 위한 방법.

#### 청구항 12

제 11 항에 있어서,

상기 제 1 개구부의 상기 로케이션 및 상기 제 1 유한한 변화가 검출되는 제 1 시간을 표시하도록, 상기 제 1 신호를 제공하는 단계를 더 포함하는, 패키지의 상태를 모니터링하기 위한 방법.

#### 청구항 13

제 8 항에 있어서,

전기적 저항 단층촬영 및 전기적 임피던스 단층촬영으로 구성되는 그룹으로부터 선택된 기법을 통해 상기 제 1 개구부의 제 1 로케이션을 추정하는 단계를 더 포함하는, 패키지의 상태를 모니터링하기 위한 방법.

#### 청구항 14

삭제

#### 청구항 15

삭제

#### 청구항 16

삭제

#### 청구항 17

삭제

#### 청구항 18

삭제

#### 청구항 19

삭제

#### 청구항 20

삭제

#### 청구항 21

삭제

#### 청구항 22

삭제

#### 청구항 23

삭제

#### 청구항 24

삭제

#### 청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 일반적으로 패키징(packaging)에 관한 것으로, 더 상세하게는, 스마트 패키징에 관한 것이다.

#### 배경 기술

[0002] 용어 "패키징"은 그 생산의 시간으로부터 그 이용까지 제품을 둘러싸는 상이한 부품들의 집합을 지칭한다. 그것은 전형적으로, 출하 및 취급 동안에 물리적 손상으로부터의 보호를 제공하는 것, 절도 저지, 오염을 억제하는 것, 정전기 방전 등으로 인한 전기적 손상으로부터의 보호를 제공하는 것, 탬퍼링(tampering)을 방지하는 것, 제품 열화를 억제하는 것 등과 같은 많은 목적들에 종종 동시에 도움이 된다.

[0003] 최근에는, 블리스터 패키징(blister packaging)이 장난감들, 하드웨어, 전자기기들, 및 약제(medication)들과 같은 많은 제품들을 위한 패키징의 주요 형태가 되고 있다. 블리스터 팩의 주요 부품은 일 유형의 열성형된 플라스틱으로 통상적으로 이루어진 형성가능한 층으로 만들어진 공동이다. 일부 경우들에는, 형성가능한 층은 자신 상으로 다시 절곡됨으로써, 공동을 밀봉하고 "클램쉘(clamshell)" 패키지를 형성한다. 더 전형적으로, 금속 박(metal foil)의 덮개 밀봉부(lidding seal)는 공동들을 밀봉하기 위하여 백킹 층(backing layer)으로서 형성 가능한 층에 접합(join)됨으로써, 하나 이상의 밀폐된 저장소(reservoir)들을 형성한다.

[0004] 블리스터 패키징은 상당히 흔해졌으므로, 지능을 추가함으로써 그 유용성을 개선시키는 것에 있어서 관심이 증가하였다. "스마트", "능동", 또는 "접속된" 패키징으로서 지칭된 바와 같이, 이러한 패키지들은, 제품 상황을 제공하고, 선도를 모니터링하고, 온도 노출을 추적하고, 패키지로 전달된 충격들을 래코딩하고, 하나 이상의 제품 유닛들이 패키지로부터 제거되었을 때에 경보를 전송하는 등을 행하기 위하여 이용될 수 있는 센서들 및 모니터링 회로부를 포함한다. 또한, 복사하기가 매우 어려운 복잡한 제품 코드들을 포함하는 것이 가능함으로써, 위조 시도들을 좌절시킨다. 그 결과, 이러한 추가된 지능은 절도 저지를 증대시킬 수 있고, 제품 위조를 억제 할 수 있고, 제품 엔드-투-엔드(end-to-end)(즉, 생산으로부터 소비자까지)의 추적을 가능하게 하는 등을 행할 수 있다.

[0005] 불운하게도, 지능형 패키징을 제공하기 위한 기존의 접근법들은 전형적으로, 복잡하고, 고가이고, 종종 용이하게 손상된다.

가장 간단한 종래 기술의 접근법은 패키지로부터의 유닛의 제거 동안에 파단되도록 배열되는 전기적 트레이스들에 의존하고, 그 예들은 미국 특허 제8,960,440호, 및 미국 특허 공개 번호 제2010/0089789호에서 개시되어 있다. 멀티-유닛 블리스터 팩들에 대하여, 별도의 트레이스는 각각의 저장소 상에서 정상적으로 배치된다. 전자 회로부는 각각의 트레이스의 저항을 모니터링하고, 트레이스들 중의 하나에 대한 무한 저항이 검출될 때에 신호를 생성한다. 불운하게도, 패턴화된 트레이스들을 블리스터 팩 내로 편입하는 것은 기존의 패키징 접근법들의 상당한 수정을 요구한다. 그 결과, 그것은 상당한 복잡도 및 비용을 추가한다. 또한, 좁은 전도성 트레이스들은 유닛 제거의 잘못된 표시들을 야기시킬 수 있는 부식 및 물리적 손상을 받는다.

또 다른 종래 기술의 스마트-패키징 접근법은 패키지 내에 포함된 제품 유닛들의 광학적 모니터링에 의존한다. 그러나, 능동 광학적 소스들뿐만 아니라, 검출기들을 포함하기 위한 필요성은 패키징 비용들을 상당히 증가시킨

다. 또한, 이러한 디바이스들은 악명 높게도 전력을 많이 소모시키고, 이것은 그것들에 전력을 공급하기 위하여 이용된 배터리의 수명을 단축시킨다.

또 다른 기존의 스마트-패키징 접근법은 패키지 내에 포함된 각각의 유닛과 연관되는 무선-주파수 식별(radio-frequency identification; RFID) 태그들을 채용한다. 이것은 패키징된 제품들의 고도로 신뢰성 있는 추적을 가능하게 하지만, 이 접근법들은 RFID 태그들을 급전시키고 관리할 수 있는 특화된 기지국들을 요구한다. 또한, RFID 태그들이 동작가능한 범위는 상당히 좁다. 또한, 대부분의 RFID-기반 접근법들은 태그와의 RF 통신을 가능하게 하는 필수적인 안테나를 형성하기 위하여 금속-박 덮개-밀봉 층의 패턴화를 요구한다.

[0006] 패키징된 제품의 엔드-투-엔드 추적을 가능하게 하는 간단한 더 저비용의 스마트-패키징 접근법에 대한 필요성은 아직 미충족된 채로 남아 있다.

[0007] 삭제

[0008] 삭제

[0009] 삭제

### 발명의 내용

[0010] 본 발명은 접속된 패키징을 통해 생산으로부터 소비까지, 약들, 약제, 식품들, 소비자 전자 제품들, 배터리들 등과 같은 제품의 추적을 가능하게 한다. 본 발명의 실시형태들은 약제 고수(adherence), 환경적 노출(예컨대, 온도, 충격, 화학적 노출 등), 탬퍼링(tampering), 및 절도를 무선으로 보고하기 위하여 동작한다.

[0011] 본 발명의 예시적인 실시형태는 약학적 제품들을 위한 스마트 패키지이다. 패키지는 전기적으로 전도성이고 비 패턴화되는 제 1 층, 제 1 층을 통해 전기적으로 통신하도록, 제 1 층에 전기적으로 접속되는 제 1 및 제 2 단자들, 복수의 공동들을 가지는 제 2 층, 제 1 및 제 2 단자들 사이의 전기적 저항을 모니터링하고 제 1 층에서의 개구부들의 형성을 표시하는 출력 신호를 제공하기 위한 전자 회로부를 포함한다. 제 1 및 제 2 층들은 제 1 층 및 공동들이 집합적으로 복수의 저장소들을 정의하고 각각의 저장소는 약물 태블릿(medicinal tablet)을 위치시키기 위하여 동작하도록 접합된다. 일부 실시형태들에서, 저장소들은 알약(pill), 캡슐(capsule), 로제지(lozenge) 등과 같은 또 다른 약물 제품 유닛을 유지(hold)하기 위하여 동작한다. 일부 실시형태들에서, 저장소들은 장난감, 식품, 전자 제품 등과 같은 또 다른 생산 유닛을 유지하기 위하여 동작한다.

[0012] 일부 실시형태들에서, 제 1 층은 전기적 비-전도성 막 및 전기적 전도성 막을 포함하고, 여기서, 비-전도성 막은 전도성 막과 복수의 단자들 중의 적어도 하나 사이에 있다. 이러한 실시형태들에서, 단자들은 교류 신호를 이용하여 전도성 막에 용량성으로 결합되고, 그러므로, 제 1 층을 통해 전기적으로 결합된다. 이러한 실시형태들에서, 전자 회로부는 교류 신호를 단자들에 제공하고 그것을 사이의 전기적 임피던스(electrical impedance)를 모니터링하기 위하여 동작한다.

[0013] 일부 실시형태들에서, 복수의 단자들은 제 1 층의 에어리어(area)의 둘레(perimeter) 주위에 배열되고, 전기적 파라미터(예컨대, 전기적 저항 또는 임피던스)가 복수의 단자들 중의 각각의 단자와 각각의 다른 단자 사이에서 측정될 수 있도록, 제 1 층을 통해 전기적으로 결합된다. 일부 실시형태들에서, 각각의 단자와 각각의 다른 단자 사이의 전기적 파라미터는 제 1 층의 에어리어 상에서 전기적 파라미터의 맵을 개발하기 위하여 이용된다. 일부 실시형태들에서, 맵은 전기적 저항 단층촬영 또는 전기적 임피던스 단층촬영 기법들을 이용하여 프로세서에 의해 생성된다. 일부 실시형태들에서, 프로세서는 패키지의 전자 회로부 내에 포함된다. 일부 실시형태들에서, 프로세서는 전자 회로부와 통신하는 외부 프로세서이다.

[0014] 일부 실시형태들에서, 전자 회로부는 패키지로부터 및/또는 패키지로의 무선 통신들을 가능하게 하는 무선 디바이스를 포함한다.

[0015] 본 발명의 실시형태는 하나 이상의 제품 유닛들(112)을 포함하기 위한 장치이고, 장치는: 제 1 영역(406) 전반에 걸쳐 실질적으로 연속적인 제 1 층(104); 각각의 단자가 제 1 층에서의 개구부의 형성 전 및 후에 제 1 층을 통해 제 1 복수의 단자들 중의 각각의 다른 단자와 전기적으로 통신하도록 배열되는 제 1 복수의 단자들(402);

및 (1) 제 1 복수의 단자들 중의 제 1 단자와 제 2 단자 사이에서 전기적 자극을 제공하고 (2) 제 2 복수의 단자들의 각각에서 전기적 파라미터를 측정하기 위하여 동작하는 전자 회로부(404) – 제 1 복수의 단자들은 제 1 단자, 제 2 단자, 및 제 2 복수의 단자들을 포함하고, 제 2 복수의 단자들은 제 1 단자 및 제 2 단자를 제외하고, 전기적 파라미터는 전기적 자극에 기초함 – 를 포함한다.

[0016] 본 발명의 또 다른 실시형태는 하나 이상의 제품 유닛들(112)을 포함하기 위한 장치이고, 장치는: 제 1 영역(406) 전반에 걸쳐 실질적으로 연속적인 제 1 층(104); 각각의 단자가 제 1 층에서의 개구부의 형성 전 및 후에 제 1 층을 통해 제 1 복수의 단자들 중의 각각의 다른 단자와 전기적으로 통신하도록 배열되는 제 1 복수의 단자들(402); 및 (1) 제 1 복수 중의 제 1 단자와 제 2 단자 사이에서 전기적 자극을 제공하고 (2) 제 2 복수의 단자들의 각각에서 전기적 파라미터를 측정하기 위하여 동작하는 전자 회로부(404) – 제 1 복수의 단자들은 제 1 단자, 제 2 단자, 및 제 2 복수의 단자들을 포함하고, 제 2 복수의 단자들은 제 1 단자 및 제 2 단자를 제외하고, 전기적 파라미터는 전기적 자극에 기초함 – 를 포함한다.

[0017] 본 발명의 또 다른 실시형태는 패키지(400)의 상태를 모니터링하기 위한 방법이고, 방법은: 제 1 영역(406)의 전반에 걸쳐 실질적으로 연속적인 제 1 층(104); 및 하나 이상의 공동들(116)을 포함하는 제 2 층(102)을 포함하도록, 패키지를 제공하는 단계 – 제 1 층 및 제 2 층은 하나 이상의 공동들의 각각 및 제 1 층이 제품 유닛(112)을 유지하기 위하여 동작하는 저장소(106)를 집합적으로 정의하도록 접합됨 –; 각각의 단자가 제 1 층에서의 개구부의 형성 전 및 후에 제 1 층을 통해 제 1 복수의 단자들 중의 각각의 다른 단자와 전기적으로 통신하도록 배열되는 제 1 복수의 단자들(402)을 제공하는 단계; 제 1 복수의 단자들 중의 제 1 및 제 2 단자들(402-1 및 402-6) 사이에서 제 1 자극을 제공하는 단계; 및 제 2 복수의 단자들(402-2 내지 402-6, 및 402-7 내지 402-10)의 각각에서 전기적 파라미터를 측정하는 단계 – 제 1 복수의 단자들은 제 2 복수의 단자들을 포함하고, 제 2 복수의 단자들은 제 1 및 제 2 단자들을 제외하고, 또한, 전기적 파라미터는 제 1 자극에 기초함 – 를 포함한다.

### 도면의 간단한 설명

[0018] 도 1a는 본 발명의 예시적인 실시형태에 따라, 블리스터 팩의 분해도의 개략적인 도면을 도시한다. 도 1b는 그 조립 후의 블리스터 팩(100)의 단면도의 개략적인 도면을 도시한다. 도 2는 예시적인 실시형태에 따라, 블리스터 팩의 상태를 모니터링하기 위하여 적당한 방법의 동작들을 도시한다. 도 3은 패키지로부터 태블릿들의 제거 후의 블리스터 팩(100)의 사시도의 개략적인 도면을 도시한다. 도 4는 본 발명의 제 1 대안적인 실시형태에 따라, 블리스터 팩의 평면도의 개략적인 도면을 도시한다. 도 5는 제 1 대안적인 실시형태에 따라, 블리스터 팩의 상태를 모니터링하기 위하여 적당한 예시적인 방법의 동작들을 도시한다. 도 6a 내지 도 6d는 그 둘레 주위에 배열된 4개의 단자들을 가지는 예시적인 덜개 막에서의 알려진 태블릿 로케이션들에서의 개구부들의 상이한 가능한 구성들에 대한 영역(406)의 EIT 모델들을 도시한다. 도 7은 제 1 대안적인 실시형태에 따라, 블리스터 팩에서의 하나 이상의 개구부들의 로케이션을 결정하기 위하여 적당한 서브-방법을 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0019] 본 발명은 소비자 전자기기들, 장난감들, 건강관리 제품들(예컨대, 면도날들 등), 식품들, 토너 카트리지(toner cartridge)들 등을 포함하는 다양한 패키징 응용들에 걸친 이용을 위한 스마트 블리스터 패키징에 관한 것이다. 그러나, 그것은 약학적 패키징에서의 이용을 위하여 특히 양호하게 적합하다는 것이 주목되어야 한다.

[0020] 많은 약물 제품들에 대하여, 블리스터 패키징은 패키징의 지배적인 형태가 되고 있지만; 그러나, 그것은 폭넓은, 망라하는, 다면적인 테스크이다. 그것은 매 유형의 보충제(supplement), 슬포제(poultice), 액체, 고체, 분말, 혼탁액, 또는 적하물(drop)을 전세계의 사람들에게 전달하기 위한 모든 상상가능한 투약량(dosage) 형태로 생명-구조 약들, 의학적 디바이스들, 의학적 치료들, 및 의학적 영양제(nutritional)들(기능식품(nutraceutical)들)과 같은 새로운 제품들을 제공하는 것을 담당한다.

[0021] 약물 제품들의 "탬퍼링"을 좌절시키기 위한 일부 약물 패키징 노력들이 행해졌지만(예컨대, 테이프들, 박 밀봉

들 등과 같은 비-재밀봉가능한 탬퍼 표시기들), 전체적으로, 대부분의 약들 및 약물들은 습도, 산화, 광, 오염 등과 같은 오직 환경적 관심사들을 주로 다루는 방식으로 여전히 패키징된다. 그러나, 본 발명의 양태는 스마트 패키징이 가치를 추가할 수 있고 건강관리 산업을 꾀롭히는 많은 쟁점들에 대한 해결책들을 제공할 수 있고, 특히, 자체-투약 요법(regimen)들과의 환자 준수성(patient compliance)을 개선시킬 수 있다는 것이다. 본 발명에 따른 스마트 패키징은 예를 들어, 투약 이벤트와 같은 어떤 이벤트들이 촉발되고 및/또는 로그되고, 및/또는 관리 제공자와 통신되는 것을 가능하게 한다.

[0022] 환자 준수성은 오늘날에 건강관리 산업과 직면하는 가장 성가신 문제들 중의 하나인 것이 주목되어야 한다. 4명의 미국인들 중에서 거의 3명은 지시된 바와 같이 그 약제들을 취하지 않고, 이것은 특히, 만성적 질병들을 갖는 사람들에 대하여 심각한 건강 결과들로 귀착된다. 선진국들에서는, 일반적인 인구에서의 장기 치료법들에 대한 고수가 평균적으로 약 50%이지만, 개발도상국들에서는 훨씬 더 낮다. 환자들이 처방된 약제 요법들을 고수하는 것의 실패는 열악한 약 효능, 급성 관리에 대한 증가된 필요성으로 인한 더 높은 의학적 관리 비용들, 및 약학적 산업으로의 재정적 손실들에 직접적으로 기여한다. 열악한 환자 준수성의 영향은:

· 단지 미국에서의 년 당 125,000명의 환자 사망들;

· 년 당 2900억 달러의 추가적인 건강관리 비용들; 및

· 2011년의 총 전체적인 약학적 세입에서의 9560억 달러의 59%에 대응하는 년간으로 추정된 5640억 달러의 전체적인 약학적 시장에 대한 손실들에 대해 책임이 있다.

[0026] 게다가, 약들의 절도 및 위조는 전 세계적인 건강 파문들에서의 치명적인 쟁점이 되었다. 위조는 전 세계에서 2%의 범위인 것으로 추정되지만; 그러나, 그것은 개발도상국들에서 집중되고, 여기서, 그것은 일부 영역들에서 60%만큼 높은 것으로 추정된다. 위조 약들의 결과들은 부정적인 부작용들, 열악하거나 비-존재하는 효능, 및 많은 경우들에서의 사망을 포함하여, 심각할 수 있다. 또한, 약제 절도는 부피에 있어서 모든 화물 절도의 오직 5%를 구성하지만, 도난된 약제의 평균 가치는 도난 당 3.78백만 달러이다. 약 생산자들에 대한 직접적인 경제적 영향은 상당할 수 있어서, 최근에는 일부 회사들을 극도로 심하게 타격할 수 있다. 손실된 제품으로 인한 돈의 손실 및 재판 지연들을 심지어 초월하여, 약학적 절도는 또한, 회사의 명성에 대한 손상, 및 시장에 아직 배포되지 않은 제품들을 리콜(recall)하기 위한 필요성과 같은 숨겨진 결과들을 지닌다. 또한, 도난된 약물들은 합법적인 공급 체인에서 종결될 수 있고, 그것을 받는 환자들에게 심각한 위험을 제기할 수 있다.

[0027] 본 발명에 따른 접속된 패키징은 생산으로부터 소비까지의 약의 완전한 수명 사이클에 대한 긍정적인 암시들을 가진다. 본 발명의 실시형태들은:

[0028] i. 개선된 환자 고수/준수성; 또는

[0029] ii. 증가된 효능; 또는

[0030] iii. 처방된 타이밍, 투약량, 재충전들 등에 의해 준수하는 것; 또는

[0031] iv. 다음에 의해 가능하게 된 개선된 결과들을 통한 개선된 치료 성과;

[0032] a. 환자들과의 더 양호한 참여; 또는

[0033] b. 치료법들/효능에 대한 피드백을 측정하고 제공함으로써, 관리제공자들이 치료 성과들을 개선시키고, 약학적 회사들은 세입 제어 및 비용 관리를 개선시키기 위한 기회들을 제공하기 위한 개선된 능력; 또는

[0034] c. 사용자 데이터를 수집하고 분석하기 위한 개선된 능력; 또는

[0035] v. 새로운 분포 모델들(예컨대, 공급자로부터 고객으로의 직접적인 판매들); 또는

[0036] vi. 개선된 약 제어(예컨대, 절도 방지, 위조-방지 등); 또는

[0037] vii. 촉진된 임상적 시험들; 또는

[0038] viii. 새로운 진단 기능들에 대한 기회들;

[0039] ix. i, ii, iii, iv, v, vi, vii, 및 viii의 임의의 조합을 가능하게 한다.

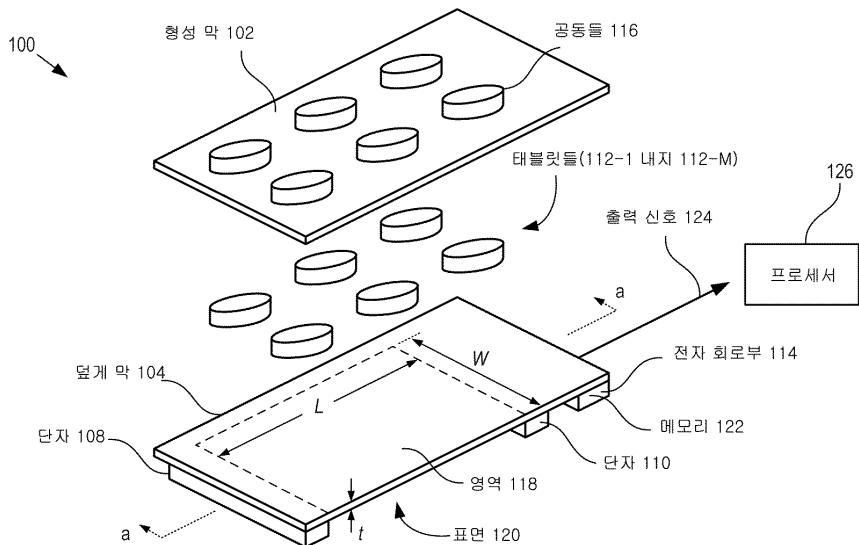

[0040] 도 1a는 본 발명의 예시적인 실시형태에 따라, 블리스터 팩의 분해도의 개략적인 도면을 도시한다.

- [0041] 도 1b는 그 조립 후의 블리스터 팩(100)의 단면도의 개략적인 도면을 도시한다. 도 1b는 도 1a에서 도시된 바와 같이, 라인 a-a를 통해 취해진 블리스터 팩(100)의 단면을 도시한다.

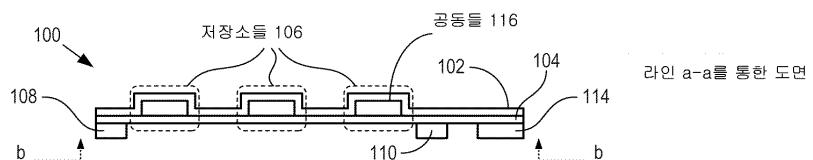

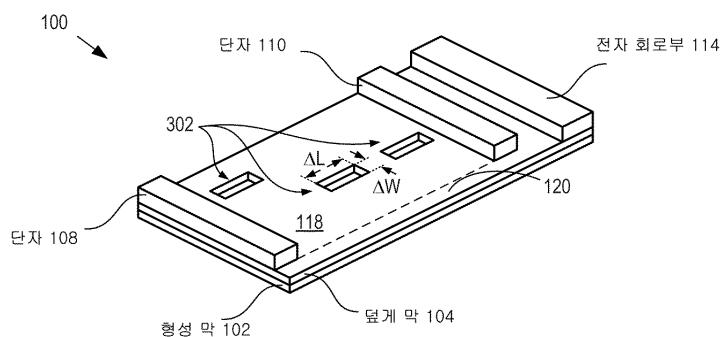

- [0042] 블리스터 팩(100)은 형성 막(102), 덮개 막(104), 저장소들(106), 단자들(108 및 110), 태블릿들(112), 및 전자 회로부(114)를 포함한다. 덮개 막(104)은 각각의 태블릿(112)이 형성 막에서의 반-강성(semi-rigid) 형성된 공동들 중의 임의의 것을 강제로 봉괴시키는 것에 의해 덮개 막을 통해 그것을 푸시(push)함으로써 제거되는 것을 허용하도록 설계되므로, 블리스터 팩(100)은 종종 "푸시-스루(push-through) 팩"으로서 지칭된다. 그러나, 당해 분야의 당업자는 본 발명이 의학적 블리스터 트레이들, 박리-개방(peel-open) 블리스터 팩들 등과 같은 다른 유형들의 패키징과 마찬가지로 이용하기에 적당하다는 것을 인식할 것이다. 또한, 본원에서 설명된 실시형태들은 실질적으로 직사각형 블리스터 팩들이지만, 일부 실시형태들에서, 블리스터 팩(100)은 원형, 타원형, 다각형, 정사각형, 또는 불규칙한 것과 같은, 직사각형 이외의 형상을 가진다. 일부 실시형태들에서, 하나 이상의 단자들은 블리스터 카드(100)의 내부에서 위치된다.

- [0043] 블리스터 팩(100)은 단일의 비절곡된 블리스터 카드이다. 일부 실시형태들에서, 블리스터 팩(100)은 다수의 블리스터 카드들을 포함하고, 그 각각은 하나 이상의 태블릿들을 유지하고, 여기서, 블리스터 카드들은 물리적으로 그리고 전기적으로 접속되지만, 그것들을 용이하게 패키징된 유닛으로 패닝(fanning)하는 것을 용이하게 하는 "절곡 라인들"을 따라 천공된다. 첨부된 청구항들을 포함하는 이 명세서의 목적들을 위하여, 비패턴화되지만, 천공된 절곡 라인들을 포함하는 층의 영역은 실질적으로 연속적인 것으로 고려된다.

- [0044] 당해 분야의 당업자는 많은 유형들의 약제가 알약들, 캡슐들, 로젠파드들 등과 같은, 블리스터 패키지에서의 패키징을 위하여 적당한 형태로 제공된다는 것을 인식할 것이다. 첨부된 청구항들을 포함하는 이 명세서의 목적들을 위하여, 용어 "태블릿"은 모든 이러한 약물 형태들을 망라하는 일반적인 용어로서 이용된다.

- [0045] 형성 막(102)은 공동들(116)(즉, 블리스터들)을 포함하는 열성형된 플라스틱의 층이다. 공동들(116)은 전형적으로, 기존의 열성형 프로세스를 통해 형성되고, 여기서, 형성 막은 가열되고 형성 도구의 특징부들로 가압된다. 당해 분야의 당업자는 본 발명의 범위로부터 이탈하지 않으면서, 형성 막(102)을 제조하기 위한 무수한 적당한 대안적인 방법들이 있다는 것을 인식할 것이다.

- [0046] 공동들(116)의 각각은 태블릿들(112-1 내지 112-M) 중의 하나로 충전되고, 여기서, M은 블리스터 팩(100) 내에 포함된 약물 도우즈(dose)들의 총 수이다(예시적인 실시형태에서, 각각의 도우즈는 단일 태블릿(112)을 포함하고 M=6이다). 태블릿들(112-1 내지 112-M)은 기존의 방식으로 그 개개의 공동들 내로 적재된다. 적재 프로세스/loading process)는 어떤 공동들도 비어 있지 않거나, 다수의 태블릿들을 포함하지 않거나, 손상된 태블릿들을 가지지 않는다는 것을 보장하기 위하여, 자동화된 시각 시스템을 이용하여 정상적으로 모니터링된다. 일부 실시형태들에서, 공동들(116) 중의 적어도 하나는 복수의 태블릿들(112)을 포함한다.

- [0047] 덮개 막(104)은 약학적 응용들을 위하여 적당한, 알루미늄 박과 같은 금속 박의 층이다. 덮개 막(104)은 공동들의 예지들에 대하여 덮개 막을 밀봉하기 위하여, 국소화된 가열 및 가압을 이용하여 기존의 방식으로 형성 막(102)과 접합된다. 일단 형성 막(102) 및 덮개 막(104)이 접합되면, 덮개 막 및 공동들(116)은 저장소들(106)을 접합적으로 정의한다. 저장소들(106)은 태블릿들이 덮개 막을 통해 그것들을 푸시함으로써 조제될 때에 태블릿들(112)의 제거 및 포착을 용이하게 하기 위하여 추가적인 구조가 없는 블리스터 팩의 에어리어인 영역(118) 내에서 위치된다.

- [0048] 일부 실시형태들에서, 덮개 막(104)의 표면(120)은 투약량 스케줄, 긴급 절차들 등과 같은 인쇄된 정보를 포함한다. 일부 실시형태들에서, 덮개 막(104)은 금속 층 및 얇은 전기적 비-전도성 층(예컨대, 정보가 그 상에 인쇄되는 종이 층 등)을 포함하는 다층 막이다. 일부 실시형태들에서, 전도성 층은 블리스터 팩(100)에 대한 제조 프로세스의 일부로서, 비-전도성 덮개 막에 추가된다.

- [0049] 일부 실시형태들에서, 블리스터 팩(100)은 각각이 적어도 하나의 저장소(116)를 포함하는, 개별적인, 용이하게 분리된 블리스터 카드들을 정의하기 위하여 라인들을 따라 천공된다.

- [0050] 단자들(108 및 110)은 영역(118)의 어느 하나의 단부에서의 표면(120) 상에서 배치된 전기적 접촉들이다. 단자들(108 및 110)은 전자 회로부(114)로의 전기적 접속을 가능하게 한다. 단자들(108 및 110)은, 단자들이 덮개 막(104)을 통해 전기적으로 통신하도록, 표면(120) 상에서 배치된다.

- [0051] 일부 실시형태들에서, 단자들(108 및 110)은 전기적 전도성 인쇄 잉크를 이용하여 표면(120) 상에서 직접적으로 형성된다. 이 실시형태들 중의 일부에서, 단자들은 위에서 논의된 바와 같이, 막 상에서의 사용자 정보의 인쇄

동안에 형성된다. 일부 실시형태들에서, 단자들(108 및 110)을 전자 회로부(114)와 상호접속하기 위하여 적당한 전기적 트레이스들은 또한, 전기적 전도성 잉크를 이용하여 블리스터 팩 상에서 형성된다.

[0052] 전자 회로부(114)는 영역(118)의 저항을 모니터링하기 위한 센서 회로부, 날짜 및 시간을 로그(log)하기 위한 메모리 모듈(122), 사용자 및/또는 의학적 서비스 제공자와 통신하기 위한 무선 디바이스, 및 블리스터 팩(100)의 관리의 연속성(chain of custody)을 추적하기 위한 모듈을 포함한다. 전자 회로부(114)는 그것이 단자들(108 및 110)과 전기적으로 결합되도록, 기존의 하이브리드 본딩 기법들을 통해 표면(120) 상에서 장착된다. 일부 실시형태들에서, 전자 회로부(114)는 능동-메트릭스 액정 디바이스들 등의 제조 시에 이용되는 바와 같은, 예를 들어, 박막 트랜지스터 기술을 이용하여 덮개 막(104) 상에서 직접적으로 형성된다. 일부 실시형태들에서, 전자 회로부(114)는 예를 들어, 환경적 인자들(예컨대, 습도, 온도 등), 보관 기간, 광 노출 등을 모니터링하기 위한 추가적인 센서들을 포함한다. 일부 실시형태들에서, 전자 회로부(114)는 투약량 리마인더(dosage reminder)들, 만료 날짜 경고들, 탬퍼 경보들 등과 같은 사용자 정보를 제공하기 위한 시각적 및/또는 청각적 상황 표시기들을 포함한다. 일부 실시형태들에서, 전자 회로부(114)는 정보를 유선 통신들 링크를 통해 블리스터 팩(100)으로 및/또는 블리스터 팩(100)으로부터 통신한다. 일부 실시형태들에서, 전자 회로부(114)는 신호 프로세싱/연산과 같은 추가적인 기능부, 및 전력 모듈(예컨대, 유도성 에너지-결합 시스템, 배터리 팩, 에너지 소기 시스템(energy scavenging system) 등)을 포함한다.

[0053] 바람직하게는, 본 발명의 실시형태들은 기존의 블리스터 패키징 사용자 경험 및 제조와 실질적으로 호환가능하다. 그러므로, 본 발명에 따른 블리스터 팩들은 비테더링(untether)되는 것과, 또한, 약제 조제는 사용자에게 추가된 부담을 지우지 않아야 한다는 것이 바람직하다. 그 결과, 전자 회로부(114)는 전형적으로, 정보가 블리스터 팩(100)으로 및/또는 블리스터 팩(100)으로부터 무선으로 송신되는 것을 가능하게 하는 무선 통신 디바이스를 포함한다. 게다가, 일부 실시형태들에서, 전자 모듈은 블리스터 팩이 "자체-보고"하는 것을 가능하게 한다. 무선 프로토콜의 선택은 일반적으로, 전력 및 비용 요건들에 의해 지배된다. 광대역/셀룰러 통신은 그것이 네트워크에 도달하기 위한 로컬/단거리 게이트웨이를 요구하지 않으므로 가장 바람직하지만; 그러나, 그것은 또한, 전력 및 비용에 있어서 가장 부담스럽다. 매력적인 대안들은 로컬 게이트웨이(예컨대, 사용자의 셀 전화, 커스텀 송신 시스템(custom transmission system), 도킹 스테이션(docking station) 등)와 통신하기 위한 단거리 무선 프로토콜들(예컨대, 블루투스 저전력(Blue Tooth Low Power), 근거리 무선 통신(Near Field Communication), 유도성 결합(Inductive Coupling) 등)을 포함한다. 당해 분야의 당업자는 이러한 접근법들이 데이터가 취출(retrieve)되어야 할 때에(예컨대, 조제 또는 조제 이력의 후속 다운로딩 동안에) 블리스터 팩이 로컬 게이트웨이 근처에 있을 것으로 요구한다는 것을 인식할 것이다.

[0054] 일부 실시형태들에서, 전자 회로부(114)는 적어도 부분적으로, 블리스터 팩(100) 외부의 모듈에서 위치된다. 일부 실시형태들에서, 전자 회로부(114)는 블리스터 팩(100)을 수용하고 위치시키고 단자들(108 및 110)과의 전기적 접속성을 확립하는 도킹 스테이션 내에 적어도 부분적으로 포함된다.

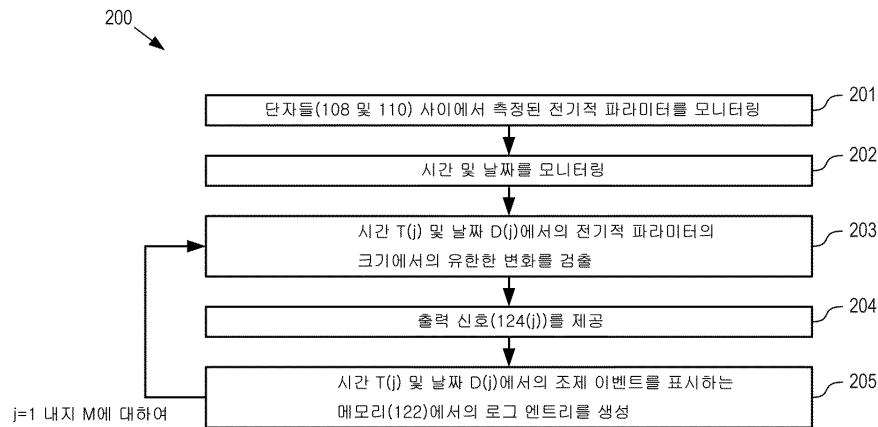

[0055] 도 2는 예시적인 실시형태에 따라, 블리스터 팩의 상태를 모니터링하기 위하여 적당한 방법의 동작들을 도시한다. 방법(200)은 동작(201)과 함께 시작하고, 여기서, 단자들(108 및 110) 사이에서 측정된 전기적 파라미터가 모니터링된다. 예시적인 실시형태에서, (즉, 영역(118)의) 단자들(108 및 110) 사이에서 측정된 전기적 파라미터는 전기적 저항이다.

[0056] 일부 실시형태들에서, 덮개 막(104)은 전기적 비-전도성 막 및 전기적 전도성 막을 포함하고, 여기서, 비-전도성 막은 전기적 전도성 막과 단자들(108 및 110) 사이(또는 전기적 전도성 막과 단자들 중의 적어도 하나 사이)에 있다. 그 결과, 단자들은 제 1 층과 전기적으로 접속되지 않고, 단자들 사이의 전기적 저항은 효과적으로 측정될 수 없다. 그러나, 단자들을 교류(AC) 신호로 구동함으로써, 단자들은 각각의 단자와 전도성 막 사이의 용량성 결합(capacitive coupling)에 의해 제 1 층을 통해 여전히 전기적으로 결합된다. 이러한 실시형태들에서, 전자 회로부(114)는 교류(AC) 신호를 단자들에 제공하고 그것을 사이의 전기적 임피던스(즉, 측정된 전기적 파라미터는 전기적 임피던스임)를 측정하기 위하여 동작한다.

[0057] 일부 실시형태들에서, 덮개 막(104)은 위에서 설명된 바와 같이, 전기적 비-전도성 막 및 전기적 전도성 막을 포함하지만; 그러나, 비-전도성 막은 단자들의 각각이 전도성 막과 직접적인 전기적 접촉을 하는 것을 가능하게 하는 개구부들을 포함한다. 그러므로, 이러한 실시형태들에서, 측정된 전기적 파라미터는 전기적 비저항(resistivity)일 수 있다.

[0058] 영역(118)의 전기적 저항 R의 크기는  $R = \rho \frac{L}{wt}$ 에 의해 주어지고, 여기서,  $\rho$  및 t는 각각, 덮개 막을 구성하는

금속의 비저항 및 두께이고, L은 단자들(108 및 110) 사이의 거리이고, W는 영역(118)의 폭을 정의하는 단자들의 폭이다.

[0059] 동작(202)에서, 전자 회로부(112)는 날짜 및 시간을 모니터링한다.

[0060] 본 발명의 양태는 태블릿이 블리스터 팩(100)으로부터 조제될 때마다, 영역(118)의 전기적 저항의 크기에서의 대응하는 유한한 변화가 발생한다는 것이다.

[0061] 동작(203)에서, 측정된 전기적 파라미터에서의 유한한 변화는 날짜 D(j) 및 시간 T(j)에서 검출되고, 여기서, j는 1 내지 M의 범위 내의 정수이다. 위에서 논의된 바와 같이, M은 블리스터 팩(100) 내에 포함된 도우즈들의 수이다. 첨부된 청구항들을 포함하는 이 명세서의 목적들을 위하여, 전기적 파라미터에서의 "유한한 변화"는 제 1 비-무한 값으로부터 제 2 비-무한 값까지의 변화로서 정의된다. 이 정의는 예를 들어, 그 파단에 이르기 까지의 전도성 트레이스의 저항에서의 변화와 같은, 제 1 비-무한 값으로부터 무한대까지의 변화를 명시적으로 제외한다.

[0062] 도 3은 패키지로부터 태블릿들의 제거 후의 블리스터 팩(100)의 사시도의 개략적인 도면을 도시한다. 도 3에서 도시된 블리스터 팩(100)의 도면은 도 1b에서 도시된 바와 같은 도면 b-b의 것이다. 태블릿은 덮개 막을 통해 그것을 푸시하기 위하여 공동(116)에 대해 가압함으로써 패키지로부터 조제되므로, 태블릿(112)의 제거는 덮개 막(104)에서의 개구부(302)를 야기시킨다. 예시적인 목적들을 위하여, 개구부들(302)은 동일한 직사각형 구멍들로서 도시되어 있다는 것이 주목되어야 한다. 그러나, 실제적으로, 개구부들(302)은 전형적으로 직사각형도 아니고 동일하지도 않다. 또한, 하나 이상의 구멍들은 덮개 막(104)으로부터 완전히 제거되는 것이 아니라, 덮개 막(104)에서 단지 파단되는 금속 박을 포함하는 것이 보편적이다.

[0063] 덮개 막(104)에서의 각각의 개구부는 단자들(108 및 110) 사이의 전기적 경로(즉, 영역(118))로부터 일부 전도성 재료를 제거한다. 이 전도성 재료의 제거는 단자들(108 및 110) 사이에서 측정된 저항의 크기에서의 구별 가능한 유한한 변화를 야기시킨다. 폭  $\Delta W$  및 길이  $\Delta L$ 를 가지는 동일한 직사각형 구멍들(202)이 덮개 막(104)에

서 형성되는 예시적인 예에 대하여, 구멍(202)의 형성으로 인해 발생하는 저항에서의 변화  $\Delta R$ 는 다음에 의해 주어진다:  $\Delta R = R \left( \frac{\Delta L}{L} - \frac{\Delta W}{W} \right)$ . 예시적인 원형 구멍 형상(즉,  $\Delta L = \Delta W$ ) 및 2의 L/W의 비율에 대하여,  $\Delta R$ 는 다음에 의해 주어진다:  $\Delta R = R \left( \frac{\Delta W}{2W} \right)$ .

[0064] 그러므로, 단자들(108 및 110) 사이의 전기적 저항에서의 변화를 모니터링함으로써, 본 발명은 태블릿의 제거, 얼마나 많은 태블릿들이 이벤트 당 조제되는지, 및 조제 이벤트들의 레코드를 검출한다.

[0065] 동작(204)에서, 전자 회로부(114)는 태블릿(112)이 블리스터 팩(100)으로부터 조제되었다는 것뿐만 아니라, 태블릿이 조제되었던 날짜 D(j) 및 시간 T(j)을 표시하는 출력 신호(124(j))를 생성한다. 일부 실시형태들에서, 출력 신호(122)는 얼마나 많은 태블릿들(112)이 조제되었는지 등과 같은 추가적인 정보를 포함한다.

[0066] 동작(205)에서, 전자 회로부(114)는 날짜 D(j) 및 시간 T(j)에서 조제되었던 태블릿들의 수를 포함하는 메모리(122)에서의 로그 엔트리(log entry)를 생성한다.

[0067] 또한, 상기한 접근법을 확장하고 영역(118) 주위에 배열된 추가적인 단자들을 추가함으로써, 각각의 태블릿이 그로부터 조제되는 영역(118) 내의 로케이션을 결정하는 것뿐만 아니라, 조제 이벤트들 및 수들을 결정하는 것의 장인함을 개선시키는 것이 가능하다.

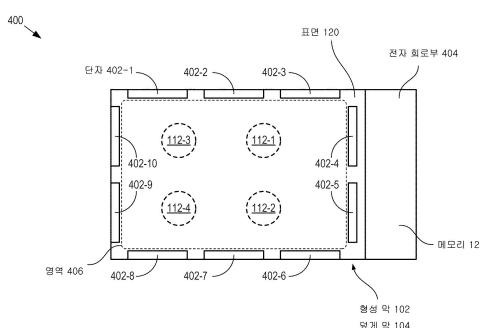

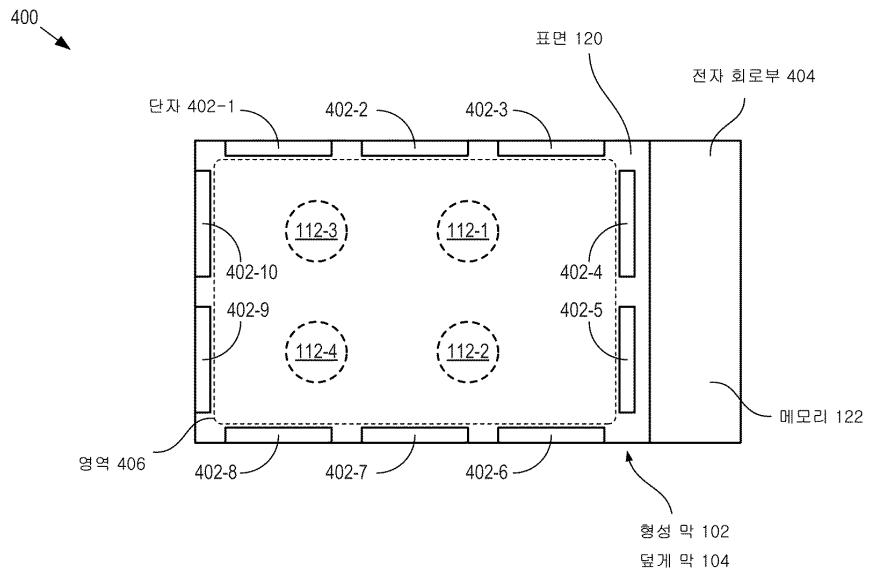

[0068] 도 4는 본 발명의 제 1 대안적인 실시형태에 따라, 블리스터 팩의 평면도의 개략적인 도면을 도시한다. 블리스터 팩(400)은 형성 막(102), 덮개 막(104), 저장소들(106), 단자들(402-1 내지 402-N), 태블릿들(112), 및 전자 회로부(404)를 포함한다. 블리스터 팩(400)은 위에서 그리고 도 1 내지 도 3에 대하여 설명된 블리스터 팩(100)과 유사하지만; 그러나, 블리스터 팩(400)은 영역(118)의 둘레 주위에서 분포되는 더 큰 수의 단자들을 포함한다. 도 4에서 도시된 실시형태는 10개의 단자들(402)(즉, N=10)을 포함하지만, 이 명세서를 관독한 후, 임의의 실제적인 수의 단자들(402)(즉, 여기서, N은 임의의 실제적인 수임)을 포함하는 본 발명의 실시형태들을 어떻게 특정하고, 제조하고, 이용할 것인지는 당해 분야의 당업자에게 명확할 것이 주목되어야 한다.

[0069] 덮개 막(104)의 둘레 주위의 8개의 추가적인 단자들의 추가는 블리스터 팩(100)의 감지 분해능(sensing resolution)을 초월하는 블리스터 팩(400)의 감지 분해능을 개선시켜서, 개별적인 태블릿이 조제되었던 아이덴

티티(identity)가 결정될 수 있다. 단자들(402-1 내지 402-10)(집합적으로, 단자들(402)로서 지칭됨)의 구성은 10개의 단자들 사이의 전기적 저항의 45개의 쌍별(pair-wise) 측정들을 가능하게 한다. 이것은 조제 이벤트 당 그리고 이력적으로의 양자에서, 각각의 조제된 태블릿의 로케이션을 감지하기 위한 충분한 분해능을 가능하게 한다. 당해 분야의 당업자는 달성가능한 감지 분해능이 블리스터 팩 상의 조제된 태블릿들의 수 및 로케이션뿐만 아니라, 블리스터들의 크기 및 밀도, 단자들로부터의 블리스터들의 상대적인 거리, 및 단자들의 크기, 형상, 수, 및 로케이션에 기초한다는 것을 인식할 것이다.

[0070] 전기적 저항 단층촬영(electrical resistance tomography; ERT) 이미징(전기적 저항 이미징(electrical resistance imaging; ERI)으로서 또한 알려짐) 및 전기적 임피던스 단층촬영(electrical impedance tomography; EIT)은 의학적 응용들에서 조직을 이미징하기 위하여 이용된 잘 알려진 기법들이다. 본 발명에 따라 영역(406)에서 형성된 하나 이상의 개구부들의 로케이션을 결정하기 위한 예시적인 방법은, 그 각각이 참조로 본원에 편입되는, 미국 특허 제8,733,432호, 및 Duraiswami 등에 의한, "Efficient 2D and 3D EIT using dual reciprocity boundary element techniques", Engineering Analysis with Boundary Elements, Vol. 22, pp. 13-31(1998)에서 설명된 것들과 같은 유사한 전자기적 및 수학적 모델링 기법들에 기초한다. 이러한 접근법들에서, 시스템의 순방향 모델은 관심 있는 파라미터의 복수의 잠재적인 구성들에 대한 시스템을 모델링함으로써 먼저 개발된다. 그 다음으로, 이 모델링된 구성들은 룩업 테이블(lookup table)에서 저장된다. 그 다음으로, 알려지지 않은 파라미터 구성은 시스템의 측정들을 행함으로써 재구성되고, 그 결과들은 그 다음으로, 저장된 모델들에 의해 예측된 것들과 비교된다. 전형적으로, 반복 알고리즘이 그것을 행함에 있어서 이용되어, 측정된 시스템에서 관심 있는 특징들을 식별한다.

[0071] 당해 분야의 당업자는 단자들(402) 중의 적어도 하나가 덮게 막(104)과 용량성으로 결합되는 실시형태들에서, 영역(406)에서의 전기적 전도성의 맵을 생성하기 위하여 ERI를 이용하는 것은 불가능하지 않지만, 어려울 것이지만; 그러나, EIT는 영역 내의 전기적 임피던스의 맵을 생성하기 위하여 이용될 수 있다는 것을 인식할 것이다.

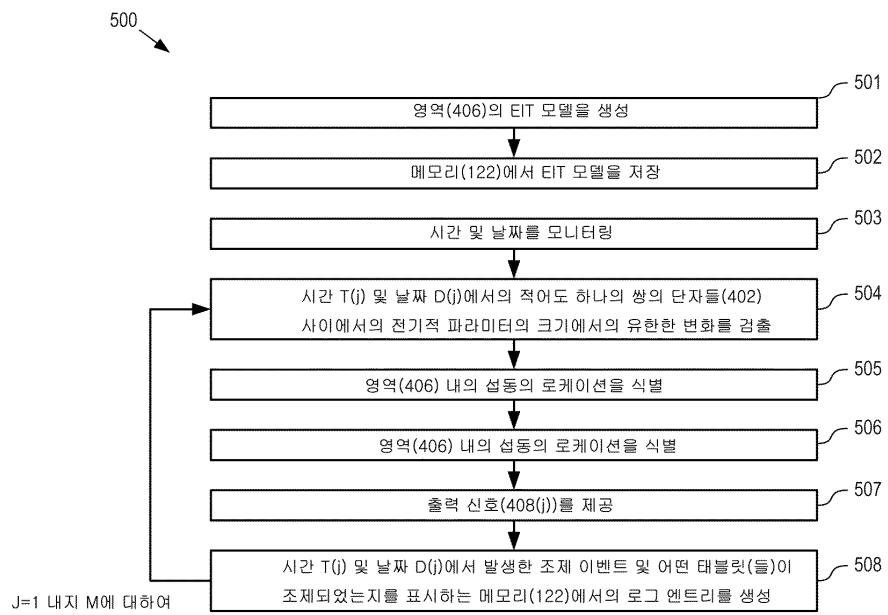

[0072] 도 5는 제 1 대안적인 실시형태에 따라, 블리스터 팩의 상태를 모니터링하기 위하여 적당한 예시적인 방법의 동작들을 도시한다. 방법(500)은 동작(501)과 함께 시작하고, 여기서, 영역(406)의 EIT 모델은 시스템(100)의 외부에 있는 기존의 데이터 프로세싱 시스템인 프로세서(126)에 의해 생성된다. 일부 실시형태들에서, 프로세서(126)는 전자 회로부(114) 내에 포함된다. 일부 실시형태들에서, 프로세서는 이동 디바이스(예컨대, 셀 전화, 태블릿, 랩톱 컴퓨터 등) 또는 기지국과 같은 전자 회로부와 통신하는 외부 프로세서이다. EIT 모델은 가정된 전기적 자극들에 기초한 영역 전반에 걸친 전류 밀도 분포의 복수의 연산된 맵들을 포함한다. 각각의 맵은 덮게 막(104)에서의 개구부들의 상이한 예상된 구성에 기초한다. 이 복수의 연산된 맵들을 생성하는 것은 종종 "순방향 문제를 구하는 것"으로서 지칭된다.

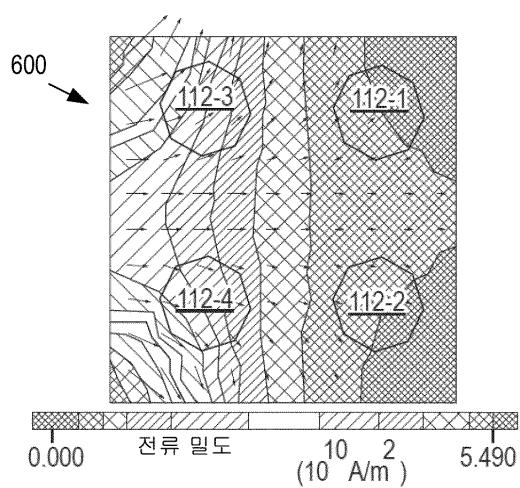

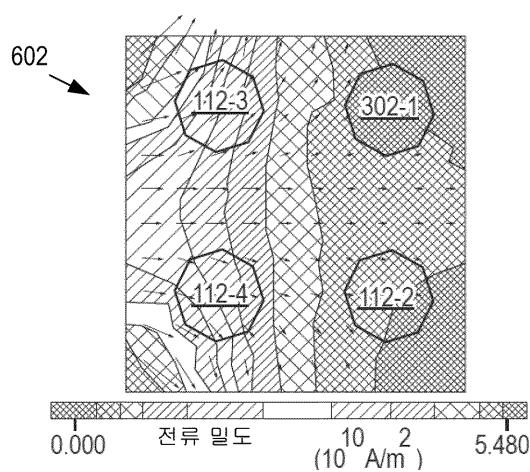

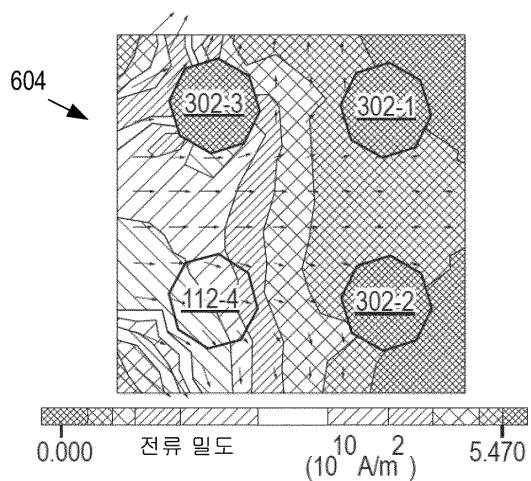

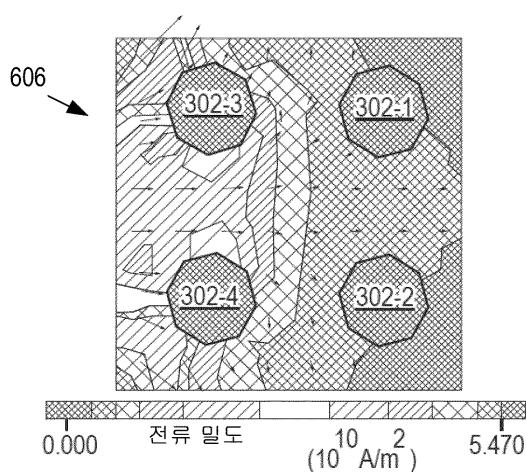

[0073] 도 6a 내지 도 6d는 그 둘레 주위에 배열된 4개의 단자들을 가지는 예시적인 덮게 막에서의 알려진 태블릿 로케이션들에서의 개구부들의 상이한 가능한 구성들에 대한 영역(406)의 EIT 모델들을 도시한다. 도표들(600 내지 606)의 각각은 4-태블릿 블리스터 카드 및 가정된 전기적 자극에 대한 전류 밀도 분포의 유한-요소(finite-element) 2-D 전기적 모델에 기초한다.

[0074] 도표(600)는 그 원래의 상태에 있는 동안(즉, 영역(118) 내에서 임의의 개구부들을 갖지 않는) 덮게 막(104)에서의 전류 밀도 분포를 도시한다.

[0075] 도표(602)는 태블릿(112-1)의 로케이션에서의 개구부(302-1)의 형성 후의 덮게 막(104)에서의 전류 밀도 분포를 도시한다.

[0076] 도표(604)는 태블릿들(112-2 및 112-3)의 로케이션들에서의 개구부들(302-2 및 303-3)의 추가적인 형성 후의 덮게 막(104)에서의 전류 밀도 분포를 도시한다.

[0077] 도표(606)는 태블릿들(112-4)의 로케이션에서의 개구부(302-4)의 추가적인 형성 후의 덮게 막(104)에서의 전류 밀도 분포를 도시한다.

[0078] 각각의 태블릿-에어리어의 전도성이 태블릿(112)이 조제될 때마다 변화한다는 것은 도표들(600 내지 606)로부터 용이하게 알 수 있다. 전도성에서의 이 변화는 영역(406)에서의 전류 밀도 분포 및 단자들(402)에서 측정된 대응하는 출력 전압들에서의 상당한 변화로 귀착된다.

[0079] 동작(502)에서, 영역(406)의 EIT 모델은 메모리(122)에서의 룩업 테이블로서 저장된다.

- [0080] 동작(503)에서, 전자 회로부(404)는 날짜 및 시간을 모니터링한다.

- [0081] 동작(504)에서, 적어도 한 쌍의 단자들(402) 사이에서 측정된 전기적 파라미터에서의 유한한 변화는 날짜 D(j) 및 시간 T(j)에서 검출되고, 여기서, j는 위에서 그리고 블리스터 팩(100)에 대하여 논의된 바와 같이, 1 내지 M의 범위 내의 정수이다. 이 유한한 변화는 영역(406)의 전도성 맵에서의 섭동(perturbation)과 동일시되고, 이것은 태블릿들(112) 중의 하나의 태블릿의 로케이션에서의 태블릿-조제 이벤트가 발생하였다는 것을 표시한다.

- [0082] 동작(505)에서는, 영역(406) 내의 섭동의 로케이션이 식별된다. 일부 실시형태들에서, 섭동의 로케이션은 측정된 EIT 맵을 동작(502)에서 저장된 모델링 결과들과 비교함으로써 식별된다.

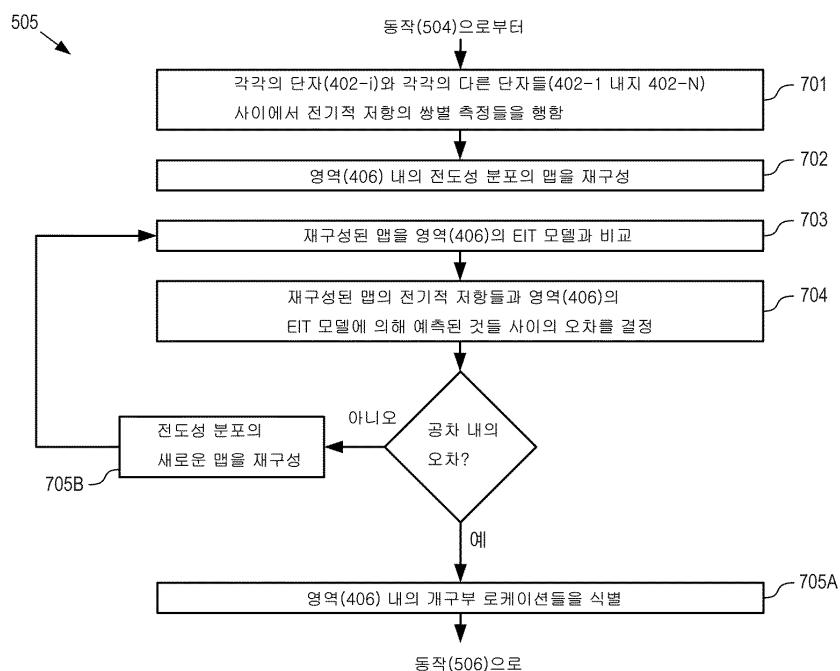

- [0083] 도 7은 제 1 대안적인 실시형태에 따라, 블리스터 팩에서의 하나 이상의 개구부들의 로케이션을 결정하기 위하여 적당한 서브-방법을 도시한다. 동작(505)은 서브-동작(701)과 함께 시작하고, 여기서, 전기적 저항의 쌍별 측정들은 각각의 단자(402-i)와 각각의 다른 단자(402-1 내지 402-(i-1), 및 402-(i+1) 내지 402-N) 사이에서 행해지고, 여기서, i는 1 내지 N의 범위 내의 정수이다. 전형적으로, 전기적 저항은 복수의 전류들을 단자들(402)에 인가하고 동일한 단자들에서 결과적인 전압들을 측정함으로써 결정된다. 일부 실시형태들에서, 동작(501)에서는, 전기적 임피던스의 쌍별 측정들이 각각의 단자(402-i)와 각각의 다른 단자(402-1 내지 402-(i-1), 및 402-(i+1) 내지 402-N) 사이에서 행해지고, 여기서, i는 1 내지 N의 범위 내의 정수이다. 이 쌍별 측정들은 도시된 예에서, 단자(402-1)와 단자들(402-2 내지 402-10)의 각각 사이의 전기적 저항, 단자(402-2)와 단자들(402-3 내지 402-10)의 각각 사이의 전기적 저항, 단자(402-3)와 단자들(402-4 내지 402-10)의 각각 사이의 전기적 저항 등을 포함한다.

- [0084] 서브-동작(702)에서, 영역(406) 내의 전도성 분포의 맵은 측정된 전기적 저항들로부터 재구성된다.

- [0085] 일부 실시형태들에서, 서브-동작(701)에서 행해진 각각의 쌍별 측정은 전류 소스(source) 및 싱크(sink)로서 역할을 하는 제 1 쌍의 단자들 사이의 전류의 생성과, 그 개개의 로케이션들 사이의 전위 차이를 결정하기 위한 제 2 쌍의 단자들 사이의 전위 차이의 측정을 포함한다. 이러한 실시형태들에서, N개의 단자들을 갖는 시스템에 대하여, 대략  $N^4$ 개의 상이한 단자 구성들이 있다. 이러한 쌍별 측정들은 미국 특허 제8,733,432호에서 LaBrecque에 의해 설명된 ERT 방법들 및 Duraiswami 등에 의해, "Efficient 2D and 3D EIT using dual reciprocity boundary element techniques"에서 설명된 EIT 측정들과 유사하다.

- [0086] 예를 들어, LaBrecque는 "...ERT에서, 각각의 측정은 4개의 전극들을 이용하고; 하나의 쌍의 전극들은 전류 소스 및 싱크로서 역할을 하고, 제 2 쌍은 2개의 포인트들 사이의 전위 차이를 측정한다. N개의 전극들을 갖는 시스템에 대하여, 어레이들로서 지정된 대략  $N^4$ 개의 상이한 구성들이 있다."는 것을 개시한다. 유사한 방식으로, Duraiswami는 "전기적 임피던스 단층촬영(EIT)에서, 객체('이미지') 내부의 임피던스들의 분포는 일부 전극들에서 특정된 전류들을 인가함으로써, 그리고 다른 전극들에서 전압의 측정들을 수행함으로써 구해진다. 그 다음으로, 전기장에 대한 수학식들은 매체 내부의 임피던스 분포 및 측정된 전압들 및 인가된 전류들 사이의 관계를 제공한다. 상이한 종류들의 재료들은 상이한 임피던스들을 가지고, 임피던스 맵의 이용가능성은 재료 분포의 이미지를 제공한다."는 것을 개시한다. 당해 분야의 당업자는 LeBrecque 및 Duraiswami에 의해 설명된 것들과 같은 ERT 및 EIT 측정들이 본 발명의 실시형태들에서의 이용을 위하여 적당하다는 것을 인식할 것이다.

- [0087] 서브-동작(703)에서, 재구성된 맵은 메모리(122)에서 저장된 것들과 비교된다.

- [0088] 서브-동작(704)에서, 전기적 저항의 측정된 값들과 단자들 사이의 전기적 저항의 예측된 값들 사이의 오차는 영역(406)의 EIT 모델에 기초한다.

- [0089] 서브-동작(705A)에서, 오차가 특정된 임계치를 충족(즉, 특정된 공차 내에 있음)시킬 경우, 전도성 맵에서의 섭동의 로케이션은 영역(406)의 재구성된 맵에 기초하여 새로운 개구부(302)의 부위로서 식별된다.

- [0090] 서브-동작(705B)에서, 오차가 특정된 임계치를 초과할 경우, 새로운 전도성 분포는 오차 최소화 절차를 이용하여 재구성되고, 서브-동작들(703 및 704)은 오차가 임계치를 충족시킬 때까지 반복된다.

- [0091] 방법(500)으로 지금 돌아가면, 동작(506)에서는, 새로운 개구부(302)의 형성에 의해 조제된 태블릿(112)의 아이덴티티가 결정된다. 전형적으로, 약학적 블리스터 팩은 동일한 약제의 다수의 태블릿들을 포함한다. 그러나 일부 실시형태들에서, 비-약학적 응용들에서의 상이한 유형들의 태블릿들 또는 제품 유닛들은 단일 블리스터 팩

내의 상이한 로케이션들에서 위치된다. 예를 들어, 일부 경우들에서, 블리스트 팩은 함께 취해지도록 의도되는 "약 콕테일(drug cocktail)"의 상이한 부품들을 포함할 수도 있다. 또는, 예시적인 비-약학적 응용에서, 블리스터 팩은 몇몇 상이한 잉크 컬러들의 각각에 대한 프린터 잉크 카트리지를 포함할 수도 있다. 이러한 실시형태들에서, 메모리(122)는 전형적으로, 제품 유형 및 블리스터 팩 내의 로케이션에 대응하는 맵 또는 룩업 테이블을 포함한다.

[0092] 동작(507)에서, 전자 회로부(404)는 출력 신호(408(j))를 생성한다. 출력 신호(408(j))는 위에서 그리고 블리스터 팩(100)에 대하여 설명된 출력 신호(124(j))와 유사하지만; 그러나, 출력 신호(408(j))는 또한, 날짜 D(j) 및 시간 T(j)에서 조제되었던 특정 태블릿(112)에 대한 정보를 포함한다.

[0093] 동작(508)에서, 전자 회로부(404)는, 조제 이벤트가 날짜 D(j) 및 시간 T(j)에서 발생하였다는 것을 표시하고 태블릿(112) 또는 태블릿들이 조제되었던 것에 대한 정보를 또한 포함하는 메모리(122)에서의 로그 엔트리를 생성한다.

[0094] 일부 실시형태들에서, 영역(406)의 둘레 상에서의 단자들(402)의 배치는 증강되거나, 영역의 내부 내에서 배치된 단자들(402)로 대체된다. 일부 실시형태들에서, 단자들은 4개보다 더 많거나 더 적은 변들을 가질 수도 있거나, 비-직사각형 형상들을 포함할 수도 있다.

[0095] 개시물은 예시적인 실시형태의 단지 하나의 예를 교시하고, 발명의 많은 변형들은 이 개시물을 판독한 후에 당해 분야의 당업자들에 의해 용이하게 고안될 수 있고, 본 발명의 범위는 다음의 청구항들에 의해 결정되어야 한다는 것이 이해되어야 한다.

## 도면

### 도면 1a

### 도면 1b

## 도면2

## 도면3

## 도면4

## 도면5

도면6a

도면6b

도면6c

도면6d

도면7