(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 602 25 050 T2 2009.04.02

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 454 482 B1

(21) Deutsches Aktenzeichen: 602 25 050.1

(86) PCT-Aktenzeichen: PCT/US02/39258

(96) Europäisches Aktenzeichen: 02 786 961.9

(87) PCT-Veröffentlichungs-Nr.: WO 2003/055207

(86) PCT-Anmeldetag: 06.12.2002

(87) Veröffentlichungstag

der PCT-Anmeldung: 03.07.2003

(97) Erstveröffentlichung durch das EPA: 08.09.2004

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 13.02.2008

(47) Veröffentlichungstag im Patentblatt: 02.04.2009

(51) Int Cl.<sup>8</sup>: H04N 5/45 (2006.01)

H03M 1/12 (2006.01)

(30) Unionspriorität:

339544 P 11.12.2001 US

(84) Benannte Vertragsstaaten:

DE, FR, GB, IT, TR

(73) Patentinhaber:

Thomson Licensing, Boulogne Billancourt, FR

(72) Erfinder:

RUMREICH, Mark Francis, Indianapolis, IN 46236, US

(74) Vertreter:

Heuer Patentanwälte, 82335 Berg

(54) Bezeichnung: MULTIPLEX-ANALOG/DIGITALUMSETZER

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die vorliegende Erfindung betrifft im Allgemeinen signalverarbeitende Videosysteme und insbesondere ein System und ein Verfahren zum Verarbeiten von analogen Farbdifferenzsignalen, das unter anderem Zeitzuordnung unter Ausgangssignalen eines zeitlich gemeinsam genutzten Analog-/Digitalwandlers (ADC) bereitstellt.

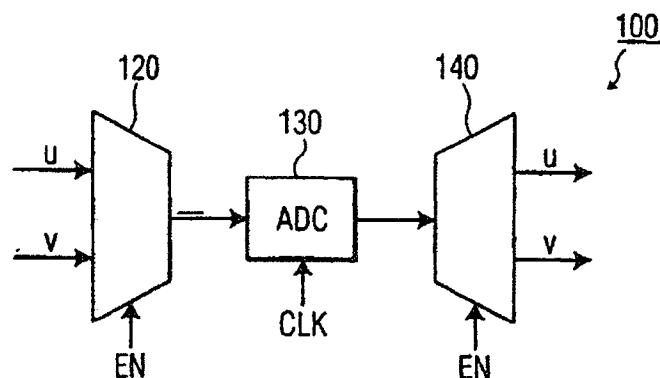

**[0002]** Zeitliche gemeinsame Nutzung eines ADC für mehrere Eingangssignale ist eine hinreichend bekannte Art, um die Anzahl von ADCs in einem Videosystem zu reduzieren. Eine Technik zum gemeinsamen Nutzen eines ADC in solchen Systemen beinhaltet einfaches Multiplexieren. [Fig. 1](#) stellt beispielsweise eine multiplexierte ADC-Anordnung **100** dar, in welcher einfaches Multiplexieren eingesetzt wird. In [Fig. 1](#) empfängt ein Multiplexer **120** gleichzeitig analoge U- und V-Eingangssignale und wird in Abhängigkeit von einem Freigabesignal („EN“) geschaltet, um ausgewählte der empfangenen analogen U- und V-Signale abwechselnd auszugeben. Ein ADC **130** empfängt die analogen U- und V-Ausgangssignale von dem Multiplexer **120** und digitalisiert die empfangenen U- und V-Signale in Abhängigkeit von einem Taktsignal („CLK“), wobei jedes Intervall des CLK-Signals einen einzelnen Taktzyklus oder ein Zeitintervall definiert. In [Fig. 1](#) kann die Frequenz des CLK-Signals beispielsweise die doppelte Frequenz des EN-Signals betragen. Ein Demultiplexer **140** empfängt die von dem ADC **130** ausgegebenen digitalen U- und V-Signale und wird in Abhängigkeit von dem EN-Signal geschaltet, um die digitalen U- und V-Signale auszugeben. Die unten stehende Tabelle 1 stellt eine beispielhafte Arbeitsweise einer multiplexierten ADC-Anordnung **100** dar.

| Taktzyklus         | 1  | 2  | 3  | 4  | 5  |

|--------------------|----|----|----|----|----|

| analoge U          | 45 | 46 | 47 | 48 | 49 |

| analoge V          | 75 | 76 | 77 | 78 | 79 |

| Mux-Position       | U  | V  | U  | V  | U  |

| ADC-Ausgabe        | 45 | 76 | 47 | 78 | 49 |

| demultiplexierte U | 45 | 45 | 47 | 47 | 49 |

| demultiplexierte V | -  | 76 | 76 | 78 | 78 |

Tabelle 1

**[0003]** Wie in Tabelle 1 angegeben, sind die U- und V-Ausgangssignale von dem Demultiplexer **140** (d. h. demultiplexierte U/demultiplexierte V) im Verhältnis zu den entsprechenden Eingangssignalen in den Multiplexer **120** (d. h. analoge U/analoge V) zeitlich nicht zugeordnet, sondern eher zeitlich gestaffelt. Anders ausgedrückt, es gibt keinen Taktzyklus, bei dem die U- und V-Ausgangssignale von dem Demultiplexer **140** im Verhältnis zu den entsprechenden Eingangssignalen in den Multiplexer **120** zeitlich zugeordnet werden. Es ist zu beachten, dass die Tabelle 1 zu Beispiels- und Erläuterungszwecken keine Signalverzögerung durch den ADC **130** und den Demultiplexer **140** veranschaulicht. Es ist bei Tabelle 1 auch zu beachten, dass der Demultiplexer **140** während jedes Taktzyklus sowohl ein U-Ausgangssignal als auch ein V-Ausgangssignal erzeugt. Eines dieser U- und V-Ausgangssignale ist ein Signal, das von dem ADC **130** während des laufenden Taktzyklus bereitgestellt wird, während das andere dieser U- und V-Ausgangssignale von dem ADC **130** während eines vorhergehenden Taktzyklus bereitgestellt wurde.

**[0004]** Für viele Anwendungen bereitet das Fehlen von Zeitzuordnung zwischen Ausgangssignalen, wie in Tabelle 1 wiedergegeben, kein Problem. Bei einigen Systemen ist eine solche Zeitzuordnung allerdings notwendig. Beispielsweise können bestimmte digitale Videosysteme, die eine integrierte Schaltung („IC“) zum Bereitstellen einer Bild-in-Bild-Funktion („PIP“) aufweisen, eine Zeitzuordnung zwischen Ausgangssignalen erfordern.

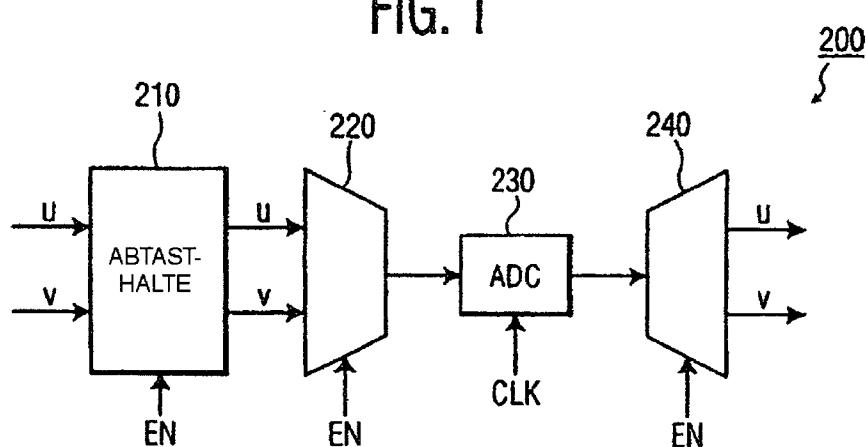

**[0005]** Eine Technik zum Bereitstellen von Zeitzuordnung zwischen Ausgangssignalen beinhaltet das Platzieren einer analogen Abtast-Halte-Schaltung in den Signalweg vor dem Multiplexer, der die Eingaben zu dem ADC bereitstellt. [Fig. 2](#) stellt beispielsweise eine multiplexierte ADC-Anordnung **200** dar, in der eine Abtast-Halte-Schaltung eingesetzt wird. In [Fig. 2](#) empfängt und hält eine Abtast-Halte-Schaltung **210** analoge U- und V-Signale bis zu dem nächsten EN-Signal. Ein Multiplexer **220** empfängt gleichzeitig die gehaltenen analogen U- und V-Signale von der Abtast-Halte-Schaltung **210** und wird in Abhängigkeit von dem EN-Signal geschaltet, um ausgewählte der empfangenen analogen U- und V-Signale abwechselnd auszugeben. Ein ADC **230** empfängt die analogen U- und V-Ausgangssignale von dem Multiplexer **220** und digitalisiert die empfan-

genen U- und V-Signale in Abhängigkeit von dem CLK-Signal, wobei jedes Intervall des CLK-Signals einen einzelnen Taktzyklus oder ein Zeitintervall definiert. In [Fig. 2](#) kann die Frequenz des CLK-Signals beispielsweise die doppelte Frequenz des EN-Signals betragen. Ein Demultiplexer **240** empfängt die von dem ADC **230** ausgegebenen digitalen U- und V-Signale und wird in Abhängigkeit von dem EN-Signal geschaltet, um die digitalen U- und V-Signale auszugeben. Die unten stehende Tabelle 2 stellt eine beispielhafte Arbeitsweise einer multiplexierten ADC-Anordnung **200** dar.

| Taktzyklus         | 1  | 2  | 3  | 4  | 5  |

|--------------------|----|----|----|----|----|

| analoge U          | 45 | 46 | 47 | 48 | 49 |

| analoge V          | 75 | 76 | 77 | 78 | 79 |

| A-H U              | 45 | 45 | 47 | 47 | 49 |

| A-H V              | 75 | 75 | 77 | 77 | 79 |

| Mux-Position       | U  | V  | U  | V  | U  |

| ADC-Ausgabe        | 45 | 75 | 47 | 77 | 49 |

| demultiplexierte U | 45 | 45 | 47 | 47 | 49 |

| demultiplexierte V | -  | 75 | 75 | 77 | 77 |

Tabelle 2

**[0006]** Wie in Tabelle 2 angegeben, werden die Ausgangssignale von dem Demultiplexer **240** (d. h. demultiplexierte U/demultiplexierte V) bei jedem zweiten Taktzyklus zeitlich zugeordnet. In Tabelle 2 werden die Ausgangssignale von dem Demultiplexer **240** beispielsweise während des Taktzyklus 2 und Taktzyklus 4 zeitlich zugeordnet. Es ist zu beachten, dass die Tabelle 2 zu Beispiels- und Erläuterungszwecken keine Signalverzögerung durch den ADC **230** und den Demultiplexer **240** veranschaulicht. Es ist bei Tabelle 2 auch zu beachten, dass der Demultiplexer **240** während jedes Taktzyklus sowohl ein U-Ausgangssignal als auch ein V-Ausgangssignal erzeugt. Eines dieser U- und V-Ausgangssignale ist ein Signal, das von dem ADC **230** während des laufenden Taktzyklus bereitgestellt wird, während das andere dieser U- und V-Ausgangssignale von dem ADC **230** während eines vorhergehenden Taktzyklus bereitgestellt wurde.

**[0007]** Obwohl die multiplexierte ADC-Anordnung **200** von [Fig. 2](#) ein gewisses Maß an Zeitzuordnung bereitstellt, ist sie problematisch, weil die Abtast-Halte-Schaltungen in den meisten standardmäßigen Zellenbibliotheken, die verwendet werden, um schnell eine IC zu entwerfen, nicht verfügbar sind. Daraus folgt, dass die Abtast-Halte-Schaltung als ein „maßgefertigter“ analoger Block betrachtet wird, der für die bestimmte, gerade entwickelte IC entworfen werden muss. Maßgefertigte analoge Blöcke erfordern im Allgemeinen zusätzliche Entwicklungszeit, Kosten und Risiken bei der Entwicklung der IC.

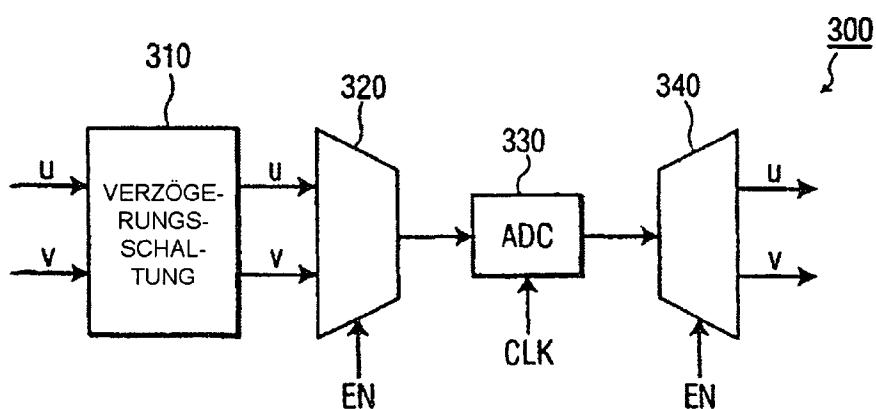

**[0008]** Ein anderer Lösungsansatz zum Bereitstellen von Zeitzuordnung beinhaltet das Platzieren einer analogen Verzögerungsschaltung vor den multiplexierten ADC. [Fig. 3](#) stellt beispielsweise eine multiplexierte ADC-Anordnung **300** dar, in der eine analoge Verzögerungsschaltung eingesetzt wird. In [Fig. 3](#) empfängt eine analoge Verzögerungsschaltung **310** analoge U- und V-Signale und gibt dieselben aus, wobei eines der U- und V-Signale im Verhältnis zu dem anderen Signal differenzial verzögert wird (z. B. um einen Taktzyklus). Ein Multiplexer **320** empfängt die analogen U- und V-Signale von der analogen Verzögerungsschaltung **310** (d. h. eines der U- und V-Signale ist verzögert worden), und wird in Abhängigkeit von dem EN-Signal geschaltet, um ausgewählte der empfangenen analogen U- und V-Signale abwechselnd auszugeben. Ein ADC **330** empfängt die analogen U- und V-Ausgangssignale von dem Multiplexer **320** und digitalisiert die empfangenen U- und V-Signale in Abhängigkeit von dem CLK-Signal, wobei jedes Intervall des CLK-Signals einen einzelnen Taktzyklus oder ein Zeitintervall definiert. In [Fig. 3](#) kann die Frequenz des CLK-Signals beispielsweise die doppelte Frequenz des EN-Signals betragen. Ein Demultiplexer **340** empfängt die von dem ADC **330** ausgegebenen digitalen U- und V-Signale und wird in Abhängigkeit von dem EN-Signal geschaltet, um die digitalen U- und V-Signale auszugeben. Die unten stehende Tabelle 3 stellt die Arbeitsweise der multiplexierten ADC-Anordnung **300** dar.

| Taktzyklus              | 1  | 2  | 3  | 4  | 5  |

|-------------------------|----|----|----|----|----|

| analoge U               | 45 | 46 | 47 | 48 | 49 |

| analoge V               | 75 | 76 | 77 | 78 | 79 |

| Verzögerungsschaltung U | 45 | 46 | 47 | 48 | 49 |

| Verzögerungsschaltung V | -  | 75 | 76 | 77 | 78 |

| Mux-Position            | U  | V  | U  | V  | U  |

| ADC-Ausgabe             | 45 | 75 | 47 | 77 | 49 |

| demultiplexierte U      | 45 | 45 | 47 | 47 | 49 |

| demultiplexierte V      | -  | 75 | 75 | 77 | 77 |

Tabelle 3

[0009] Wie in Tabelle 3 angegeben, sind die Ausgangssignale von dem Demultiplexer **340** (d. h. demultiplexierte U/demultiplexierte V) zu den Ausgangssignalen identisch, die von dem Demultiplexer **240** in [Fig. 2](#) erzeugt wurden.

[0010] Das heißt, dass die Ausgangssignale von dem Demultiplexer **340** bei jedem zweiten Taktzyklus zeitlich zugeordnet werden. In Tabelle 3 werden die Ausgangssignale von dem Demultiplexer **340** beispielsweise während des Taktzyklus 2 und Taktzyklus 4 zeitlich zugeordnet. Es ist zu beachten, dass die Tabelle 3 zu Beispiels- und Erläuterungszwecken keine Signalverzögerung durch den ADC **330** und den Demultiplexer **340** veranschaulicht. Es ist bei Tabelle 3 auch zu beachten, dass der Demultiplexer **340** während jedes Taktzyklus sowohl ein U-Ausgangssignal als auch ein V-Ausgangssignal erzeugt. Eines dieser U- und V-Ausgangssignale ist ein Signal, das von dem ADC **330** während des laufenden Taktzyklus bereitgestellt wird, während das andere dieser U- und V-Ausgangssignale von dem ADC **330** während eines vorhergehenden Taktzyklus bereitgestellt wurde.

[0011] Obwohl die multiplexierte ADC-Anordnung **300** von [Fig. 3](#) auch ein gewisses Maß an Zeitzuordnung bereitstellt, ist sie problematisch, weil der Größenunterschied und die Gruppenverzögerungseigenschaften zwischen den beiden Eingangswegen unerwünschte Reaktionswirkungen der Differenzfrequenz einführen kann. Dieses Problem wird bei Abweichungen aufgrund von Bauteiltoleranzen noch verschlimmert.

[0012] GB-A-1 575 148 offenbart einen elektrischen Energieverbrauchszähler, bei dem ein ADC zwei Serien von digitalen Abtastungen erstellt, indem Strom- und Spannungsabtastungen abwechselnd umgewandelt werden, eine erste von den beiden Serien von Abtastungen interpoliert und einen Betrag elektrischer Energie berechnet, indem Produkte einer interpolierten Abtastung von der ersten Serie und einer entsprechenden Abtastung von der zweiten Serie gebildet und indem die Produkte addiert werden.

[0013] Demzufolge besteht ein Bedarf an einer multiplexierten ADC-Anordnung, welche die vorstehend erwähnten Probleme vermeidet, und zeitlich zugeordnete (d. h. kollokierte) Ausgangssignale bereitstellt. Die vorliegende Erfindung befasst sich mit diesen und anderen Fragestellungen.

[0014] Gemäß der vorliegenden Erfindung schließt ein digitales Videosystem eine multiplexierte ADC-Anordnung ein. Die Anordnung schließt einen ADC zum Umwandeln von jeweils ersten und zweiten analogen Signalen in erste und zweite digitale Signale und zum Ausgeben des ersten digitalen Signals während eines ersten Zeitintervalls und Ausgeben des zweiten digitalen Signals während eines zweiten Zeitintervalls ein. Ein digitales Filter ist zum Filtern der ersten und zweiten analogen Signale, um jeweils erste und zweite gefilterte Signale zu erstellen, und zum Ausgeben der ersten und zweiten gefilterten Signale gleichzeitig während eines dritten Zeitintervalls bereitgestellt.

[0015] Die vorstehend erwähnten und andere Merkmale und Vorteile dieser Erfindung, und die Art und Weise diese zu erhalten, werden deutlicher, und die Erfindung wird besser verstanden, wenn sie unter Bezugnahme auf die nachfolgende Beschreibung von Ausführungsformen der Erfindung im Zusammenhang mit den beigefügten Zeichnungen gesehen wird, wobei:

[0016] [Fig. 1](#) ein Diagramm einer multiplexierten ADC-Anordnung ist, bei der eine einfache Multiplextechnik eingesetzt wird;

[0017] [Fig. 2](#) ein Diagramm einer multiplexierten ADC-Anordnung ist, bei der eine Abtast-Halte-Schaltung eingesetzt wird;

[0018] [Fig. 3](#) ein Diagramm einer multiplexierten ADC-Anordnung ist, bei der ein analoges Verzögerungsfilter eingesetzt wird;

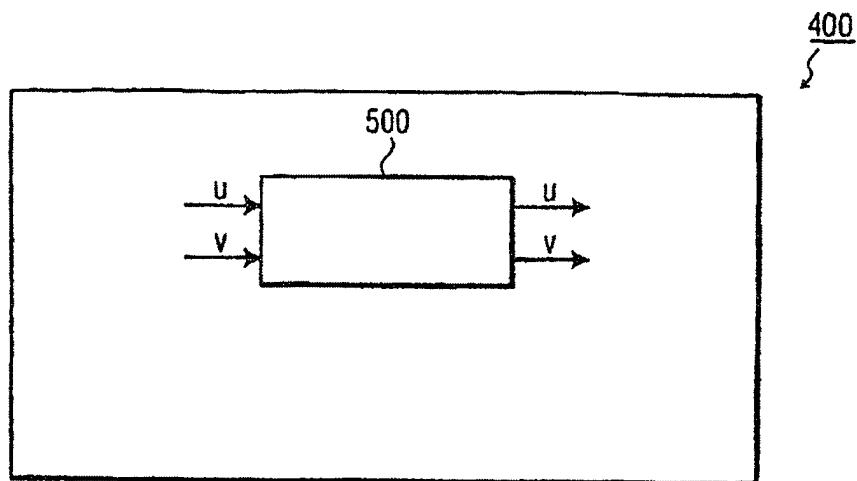

[0019] [Fig. 4](#) ein Diagramm eines beispielhaften Systems ist, das eine multiplexierte ADC-Anordnung gemäß den Prinzipien der vorliegenden Erfindung einschließt;

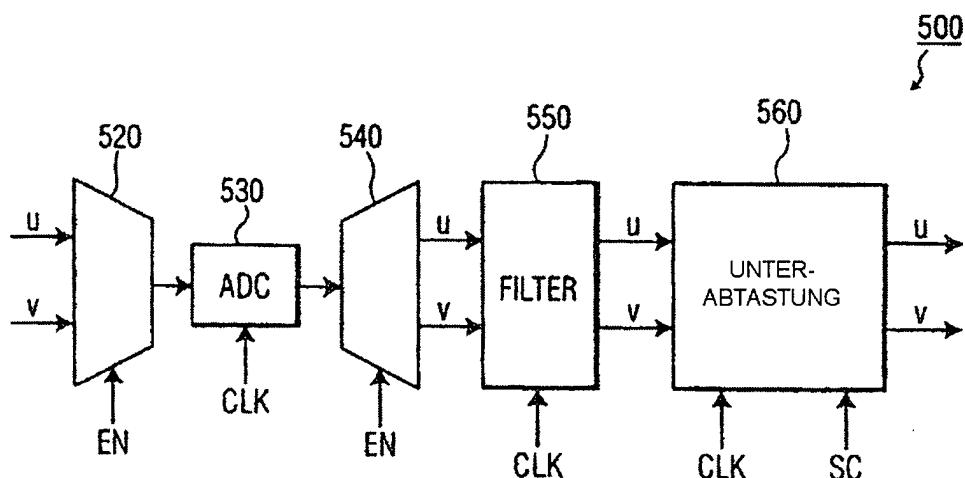

[0020] [Fig. 5](#) ein Diagramm ist, das weitere Einzelheiten der multiplexierten ADC-Anordnung von [Fig. 4](#) bereitstellt; und

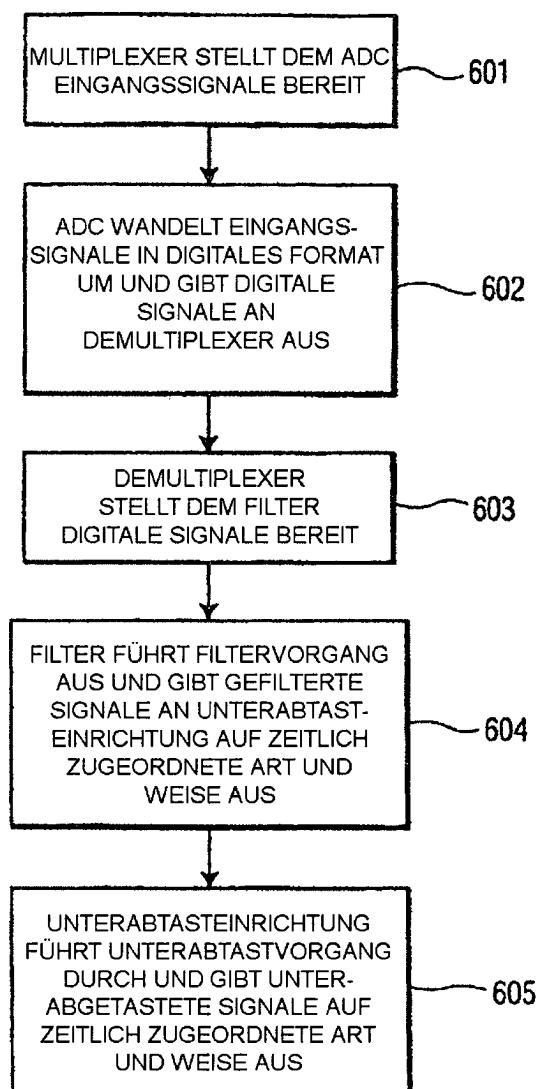

[0021] [Fig. 6](#) ein Ablaufdiagramm ist, das die beispielhaften Schritte zum Ausführen der vorliegenden Erfindung zusammenfasst.

[0022] Die hier ausgeführten Erläuterungen durch Beispiele stellen bevorzugte Ausführungsformen der Erfindung dar und solche Erläuterungen durch Beispiele sind nicht als den Umfang der Erfindung auf irgendeine Art und Weise einschränkend aufzufassen.

[0023] Unter Bezugnahme auf [Fig. 4](#) ist nun ein Diagramm eines beispielhaften Systems **400** gezeigt, das eine multiplexierte ADC-Anordnung **500** gemäß den Prinzipien der vorliegenden Erfindung einschließt. Das System **400** von [Fig. 4](#) kann als ein Audio- und/oder Videosystem, wie beispielsweise ein Fernsehsignalempfänger, ein Zusatzempfangsgerät, ein Videokassettenrekorder („VCR“), ein Abspielgerät für Digitale Versatile Disk („DVD“), eine Videospielkonsole, ein digitaler Videorekorder („PVR“) oder ein anderes Video- und/oder Audiosystem ausgeführt sein.

[0024] In [Fig. 4](#) schließt das System **400** eine multiplexierte ADC-Anordnung **500** ein, welche ihren ADC befähigt (in [Fig. 4](#) nicht ausdrücklich gezeigt), dass er von Eingangssignalen, U und V, zeitlich gemeinsam genutzt wird, und ferner solche Signale befähigt, dass sie zeitlich zugeordnet sind, wenn sie ausgegeben werden. Die U- und V-Eingangssignale können beispielsweise Farbdifferenzsignale in einem digitalen Videosystem, wie beispielsweise einem hochauflösenden Fernsehsystem („HDTV“) oder dergleichen darstellen. Die multiplexierte ADC-Anordnung **500** kann beispielsweise auf einer IC ausgeführt sein. Obwohl nicht ausdrücklich in [Fig. 4](#) gezeigt, kann das System **400** andere Bauteile einschließen, wie beispielsweise andere ICs und andere elektrische oder nicht elektrische Bauteile.

[0025] Unter Bezugnahme auf [Fig. 5](#) ist nun ein Diagramm gezeigt, das weitere Einzelheiten der multiplexierten ADC-Anordnung **500** von [Fig. 4](#) bereitstellt. Wie in [Fig. 5](#) gezeigt, umfasst die multiplexierte ADC-Anordnung **500** einen Multiplexer **520**, einen ADC **530**, einen Demultiplexer **540**, ein Filter **550** und eine Unterabtasteinrichtung **560**. Wie nachstehend erläutert, stellt die multiplexierte ADC-Anordnung **500** zeitlich zugeordnete Ausgangssignale ohne die Verwendung einer analogen Verzögerungseinrichtung vor dem ADC **530** bereit.

[0026] Beim Betrieb empfängt der Multiplexer **520** gleichzeitig analoge U- und V-Eingangssignale und wird in Abhängigkeit von dem EN-Signal geschaltet, um ausgewählte der empfangenen analogen U- und V-Signale abwechselnd auszugeben. Der ADC **530** empfängt die analogen U- und V-Ausgangssignale von dem Multiplexer **520** und digitalisiert die empfangenen U- und V-Signale in Abhängigkeit von dem CLK-Signal, wobei jedes Intervall des CLK-Signals einen einzelnen Taktzyklus oder ein Zeitintervall definiert. Die EN- und CLK-Signale können durch einen Taktgenerator oder eine andere (nicht gezeigte) Einrichtung erstellt werden. Gemäß einem Ausführungsbeispiel beträgt die Frequenz des CLK-Signals in [Fig. 5](#) die doppelte Frequenz des EN-Signals. Beispielsweise kann das CLK-Signal eine Frequenz von 18 MHz aufweisen, während das EN-Signal eine Frequenz von 9 MHz aufweist. Demzufolge empfängt und digitalisiert der ADC **530** nur jedes zweite U- und V-Signal, das in den Multiplexer **520** eingegeben wird. Das heißt, dass der Multiplexer **520** der gestalt geschaltet wird, dass jedes zweite U- und V-Signal, das in den Multiplexer **520** eingegeben wird, verloren geht. Auf diese Art und Weise gibt der ADC **530** ein digitalisiertes U-Signal während eines Taktzyklus aus und gibt ein digitalisiertes V-Signal während des nächsten Taktzyklus aus. Weitere Einzelheiten bezüglich dieser Arbeitsweise werden hier später angegeben.

[0027] Der Demultiplexer **540** empfängt die von dem ADC **530** ausgegebenen digitalen U- und V-Signale und wird in Abhängigkeit von dem EN-Signal geschaltet, um die digitalen U- und V-Signale auszugeben. Wie hier später erläutert, erzeugt der Demultiplexer **540** während jedes Taktzyklus sowohl ein digitales U-Ausgangssignal als auch ein digitales V-Ausgangssignal. Eines dieser digitalen U- und V-Ausgangssignale ist ein Signal,

das von dem ADC **530** während des laufenden Taktzyklus bereitgestellt wird, während das andere dieser digitalen U- und V-Signale von dem ADC **530** während eines vorhergehenden (z. B. eines direkt vorausgehenden) Taktzyklus bereitgestellt wurde. Gemäß einem Ausführungsbeispiel hält der Demultiplexer **540** vorhergehende U- und V-Signalwerte dargestalt, dass er ein laufendes U-Ausgangssignal und ein vorhergehendes V-Ausgangssignal während eines Taktzyklus erzeugt und danach ein vorhergehendes U-Ausgangssignal und ein laufendes V-Ausgangssignal während des nächsten Taktzyklus erzeugt.

**[0028]** Das Filter **550** empfängt die digitalen U- und V-Signale von dem Demultiplexer **540** und führt einen Filtervorgang (z. B. Interpolieren) daran durch, um dadurch zeitlich zugeordnete, gefilterte U- und V-Signale in Abhängigkeit von dem CLK-Signal auszugeben. Insbesondere sind die gefilterten U- und V-Signale, die durch das Filter **550** erzeugt werden, im Verhältnis zu den entsprechenden Eingangssignalen in den Multiplexer **520** zeitlich zugeordnet. In [Fig. 5](#) ist das Filter **550** als eine einzelne Filtereinrichtung zum Arbeiten mit sowohl den U- als auch den V-Signalkanälen gezeigt. Beim Umsetzen der Erfindung in die Praxis kann das Filter **550** allerdings aus mehreren Filtereinrichtungen bestehen, wie beispielsweise einem zweckgebundenen Filter für jeden Signalkanal. Demzufolge umfasst das Filter **550** mindestens eine Filtereinrichtung. Gemäß einem Ausführungsbeispiel führt das Filter **550** die Filtervorgänge dargestalt durch, dass jeder U-Signalwert gleichwertig zu einem halben U-Signalwert eingestellt wird, der von dem Demultiplexer **540** während des laufenden Taktzyklus empfangen wird, plus einem halben U-Signalwert, der von dem Demultiplexer **540** während eines vorhergehenden (z. B. eines direkt vorausgehenden) Taktzyklus empfangen wird. Auf ähnliche Weise wird jeder V-Signalwert gleichwertig zu einem halben V-Signalwert eingestellt, der von dem Demultiplexer **540** während des laufenden Taktzyklus empfangen wird, plus einem halben V-Signalwert, der von dem Demultiplexer **540** während eines vorhergehenden (z. B. eines direkt vorausgehenden) Taktzyklus empfangen wird. Weitere Einzelheiten bezüglich dieses Filtervorgangs werden hier später bereitgestellt.

**[0029]** Eine Unterabtasteinrichtung **560** empfängt die zeitlich zugeordneten, gefilterten U- und V-Signale von dem Filter **550** und führt einen Unterabtastvorgang daran durch, um unterabgetastete U- und V-Signale auf eine zeitlich zugeordnete Art und Weise in Abhängigkeit von dem CLK-Signal und einem Unterabtaststeuerungssignal („SC“) auszugeben. Das SC-Signal steuert die Frequenz, mit welcher die Unterabtasteinrichtung **560** die Unterabtastung durchführt. Beispielsweise kann das SC-Signal die Unterabtasteinrichtung **560** veranlassen, die Unterabtastung an einem Paar von gefilterten U- und V-Signalen bei jedem zweiten Taktzyklus auszuführen. Die zeitlich zugeordneten U- und V-Ausgangssignale von der Unterabtasteinrichtung **560** werden dann zur weiteren Verarbeitung, wie beispielsweise Farbkorrektur, Farbtonkorrektur, Abtastratenumwandlung, und/oder für einen anderen Verarbeitungsvorgang bereitgestellt. So wie das Filter **550** ist die Unterabtasteinrichtung **560** in [Fig. 5](#) als eine einzelne Unterabtasteinrichtung zum Arbeiten mit sowohl den U- als auch den V-Signalkanälen gezeigt. Beim Umsetzen der Erfindung in die Praxis kann die Unterabtasteinrichtung **560** allerdings aus mehreren Unterabtasteinrichtungen bestehen, wie beispielsweise einer zweckgebundenen Unterabtasteinrichtung für jeden Signalkanal. Demzufolge umfasst die Unterabtasteinrichtung **560** mindestens eine Unterabtasteinrichtung.

**[0030]** Unter Bezugnahme auf die unten stehende Tabelle 4 werden nun weitere Einzelheiten bezüglich einer beispielhaften Arbeitsweise der multiplexierten ADC-Anordnung **500** angegeben.

| Taktzyklus         | 1  | 2  | 3  | 4  | 5  |

|--------------------|----|----|----|----|----|

| analoge U          | 45 | 46 | 47 | 48 | 49 |

| analoge V          | 75 | 76 | 77 | 78 | 79 |

| Mux-Position       | U  | V  | U  | V  | U  |

| ADC-Ausgabe        | 45 | 76 | 47 | 78 | 49 |

| demultiplexierte U | 45 | 45 | 47 | 47 | 49 |

| demultiplexierte V | -  | 76 | 76 | 78 | 78 |

| gefilterte U       | -  | 45 | 46 | 47 | 48 |

| gefilterte V       | -  | -  | 76 | 77 | 78 |

Tabelle 4

**[0031]** Wie in Tabelle 4 angezeigt, werden analoge U- und V-Signale (d. h. analoge U und analoge V) gleichzeitig in den Multiplexer **520** während jedes Taktzyklus eingegeben. Die Schaltposition des Multiplexers **520** (d. h. Mux-Position) wechselt abwechselnd von U zu V von einem Taktzyklus zu dem nächsten. In Tabelle 4

wird der Multiplexer **520** beispielsweise geschaltet, um ein analoges U-Signal auszugeben, das einen Wert von 45 während des Taktzyklus 1 aufweist, und wird geschaltet, um ein analoges V-Signal auszugeben, das einen Wert von 76 während des Taktzyklus 2 aufweist. Es ist bei Tabelle 4 auch zu beachten, dass bestimmte U- und V-Eingangssignale in den Multiplexer **520** verloren gehen. Während des Taktzyklus 1 geht beispielsweise das V-Signal mit einem Wert von 75 verloren. Auf ähnliche Weise geht während des Taktzyklus 2 das U-Signal mit einem Wert von 46 verloren. Wie hier später angegeben, werden diese verlorenen Signale durch die Arbeitsweise des Filters **550** ausgeglichen.

**[0032]** Der ADC **530** empfängt die analogen U- und V-Ausgangssignale von dem Multiplexer **520** und digitalisiert die empfangenen U- und V-Signale in Abhängigkeit von dem CLK-Signal. Da der Multiplexer **520** dergestalt geschaltet wird, dass jedes zweite U- und V-Signal, das in den Multiplexer **520** eingegeben wird, verloren geht, empfängt und digitalisiert der ADC **530** nur jedes zweite U- und V-Signal, das in den Multiplexer **520** eingegeben wird. Zu Beispiels- und Erläuterungszwecken stellt Tabelle 4 den ADC **530** so dar, als ob er null Latenzzeit oder Verzögerung zwischen Eingabe und Ausgabe hat. Das heißt, dass Tabelle 4 den ADC **530** veranschaulicht, als ob er ein digitales U- oder V-Ausgangssignal (d. h. ADC-Ausgabe) während desselben Taktzyklus erzeugt, bei dem er ein entsprechendes analoges U- oder V-Eingangssignal von dem Multiplexer **520** empfängt. Beim Umsetzen der Erfindung in die Praxis kann allerdings etwas Verzögerung zwischen der Zeit entstehen, zu welcher der ADC **530** ein analoges U- oder V-Eingangssignal von dem Multiplexer **520** empfängt, und der Zeit, zu welcher der ADC **530** ein entsprechendes digitales U- oder V-Ausgangssignal erzeugt. Beispielsweise kann eine solche Verzögerung einem Taktzyklus oder mehreren Taktzyklen entsprechen.

**[0033]** Der Demultiplexer **540** empfängt die digital umgewandelten U- und V-Signale von dem ADC **530** und wird in Abhängigkeit von dem EN-Signal geschaltet, um die digitalen U- und V-Signale gleichzeitig auszugeben. Wiederum, zu Beispiels- und Erläuterungszwecken, stellt Tabelle 4 den Demultiplexer **540** so dar, als ob er null Verzögerung zwischen Eingabe und Ausgabe hat. Demzufolge veranschaulicht Tabelle 4 den Demultiplexer **540**, als ob er ein laufendes U- oder V-Ausgangssignal (d. h. demultiplexierte U oder demultiplexierte V) während desselben Taktzyklus erzeugt, bei dem er das laufende U- oder V-Signal von dem ADC **530** empfängt. Beim Umsetzen der Erfindung in die Praxis kann allerdings etwas Verzögerung zwischen der Zeit entstehen, zu welcher der Demultiplexer **540** ein U- oder V-Eingangssignal von dem ADC **530** empfängt, und der Zeit, zu welcher der Demultiplexer **540** das U- oder V-Ausgangssignal erzeugt. Beispielsweise kann eine solche Verzögerung einem Taktzyklus oder mehreren Taktzyklen entsprechen.

**[0034]** Wie hier vorstehend angegeben, erzeugt der Demultiplexer **540** während jedes Taktzyklus sowohl ein digitales U-Ausgangssignal als auch ein digitales V-Ausgangssignal. Insbesondere hält der Demultiplexer **540** vorhergehende U- und V-Signalwerte dergestalt, dass er ein laufendes U-Ausgangssignal und ein vorhergehendes V-Ausgangssignal während eines gegebenen Taktzyklus erzeugt und danach ein vorhergehendes U-Ausgangssignal und ein laufendes V-Ausgangssignal während des nächsten Taktzyklus erzeugt. Während des Taktzyklus 3 in Tabelle 4 erzeugt der Demultiplexer **540** beispielsweise das laufende U-Ausgangssignal mit einem Wert von 47 und das V-Ausgangssignal des direkt vorausgehenden Taktzyklus (d. h. Taktzyklus 2) mit einem Wert von 76. Danach, während des Taktzyklus 4, erzeugt der Demultiplexer **540** das laufende V-Ausgangssignal mit einem Wert von 78 und das U-Ausgangssignal des direkt vorausgehenden Taktzyklus (d. h. Taktzyklus 3) mit einem Wert von 47. Auf diese Weise erzeugt der Demultiplexer **540** während jedes Taktzyklus sowohl ein digitales U-Ausgangssignal als auch ein digitales V-Ausgangssignal.

**[0035]** Das Filter **550** empfängt die digitalen U- und V-Signale von dem Demultiplexer **540** und führt einen Filtervorgang daran durch, um dadurch zeitlich zugeordnete, gefilterte U- und V-Signale auszugeben. Wie hier schon vorstehend angegeben, führt das Filter **550** den Filtervorgang gemäß einem Ausführungsbeispiel dergestalt durch, dass jeder U-Signalwert gleichwertig zu einem halben U-Signalwert eingestellt wird, der von dem Demultiplexer **540** während des laufenden Taktzyklus bereitgestellt wird, plus einem halben U-Signalwert, der von dem Demultiplexer **540** während eines vorhergehenden (z. B. eines direkt vorausgehenden) Taktzyklus bereitgestellt wird. Auf ähnliche Weise wird jeder V-Signalwert gleichwertig zu einem halben V-Signalwert eingestellt, der von dem Demultiplexer **540** während des laufenden Taktzyklus bereitgestellt wird, plus einem halben V-Signalwert, der von dem Demultiplexer **540** während eines vorhergehenden (z. B. eines direkt vorausgehenden) Taktzyklus bereitgestellt wird. Während des Taktzyklus 3 in Tabelle 4 gibt das Filter **550** beispielsweise ein gefiltertes U-Signal (d. h. gefiltertes U) mit einem Wert von 46 und ein gefiltertes V-Signal (d. h. gefiltertes V) mit einem Wert von 76 aus. Der Wert 46 für das gefilterte U-Signal wird folgendermaßen abgeleitet:

$$\frac{1}{2}4(47) + \frac{1}{2}4(45) = 46$$

**[0036]** Das heißt für den Taktzyklus 3 in Tabelle 4, dass das gefilterte U-Signal gleichwertig zu einem halben

U-Signalwert (d. h. 47) ist, der von dem Demultiplexer **540** während des laufenden Taktzyklus (d. h. Taktzyklus 3) bereitgestellt wird, plus einem halben U-Signalwert (d. h. 45), der von dem Demultiplexer **540** während des direkt vorausgehenden Taktzyklus (d. h. Taktzyklus 2) bereitgestellt wird. Auf ähnliche Weise wird der Wert 76 für das gefilterte V-Signal folgendermaßen abgeleitet:

$$\frac{1}{2}4(76) + \frac{1}{2}4(76) = 76$$

**[0037]** Das heißt für den Taktzyklus 3 in Tabelle 4, dass das gefilterte V-Signal gleichwertig zu einem halben V-Signalwert (d. h. 76) ist, der von dem Demultiplexer **540** während des laufenden Taktzyklus (d. h. Taktzyklus 3) bereitgestellt wird, plus einem halben V-Signalwert (d. h. 76), der von dem Demultiplexer **540** während des direkt vorausgehenden Taktzyklus (d. h. Taktzyklus 2) bereitgestellt wird. Selbstverständlich kann das Filter **550** andere Arten von Filtervorgängen in Übereinstimmung mit den Prinzipien der vorliegenden Erfindung durchführen. Beispielsweise kann das Filter **550** gefilterte U- und V-Signale erstellen, indem Signalwerte von anderen vorhergehenden Taktzyklen als dem direkt vorausgehenden Taktzyklus verwendet werden.

**[0038]** Die Unterabtasteinrichtung **560** empfängt die zeitlich zugeordneten, gefilterten U- und V-Signale von dem Filter **550** und führt einen Unterabtastvorgang daran durch, um unterabgetastete U- und V-Signale zu erstellen. Obwohl in Tabelle 4 nicht ausdrücklich gezeigt, gibt die Unterabtasteinrichtung **560** die unterabgetasteten U- und V-Signale während eines nachfolgenden Taktzyklus in Abhängigkeit von dem CLK-Signal und dem SC-Signal auf eine zeitlich zugeordnete Art und Weise aus. Wie hier vorstehend schon angegeben, werden die unterabgetasteten U- und V-Signale zur weiteren Verarbeitung, wie beispielsweise Farbkorrektur, Farbtonkorrektur, Abtastratenumwandlung, und/oder für einen anderen Verarbeitungsvorgang bereitgestellt.

**[0039]** Unter Bezugnahme auf [Fig. 6](#) fasst nun ein Ablaufdiagramm **600** die beispielhaften Schritte zum Ausführen der vorliegenden Erfindung zusammen. Zu Beispiels- und Erläuterungszwecken werden die Schritte von [Fig. 6](#) unter Bezugnahme auf die multiplexierte ADC-Anordnung **500** von [Fig. 5](#) beschrieben.

**[0040]** In [Fig. 6](#) beginnt der Verfahrensablauf bei Schritt **601**, wo der Multiplexer **520** dem ADC **530** abwechselnd in Abhängigkeit von dem EN-Signal analoge U- und V-Eingangssignale bereitstellt. Bei Schritt **602** wandelt der ADC **530** die analogen U- und V-Eingangssignale in ein digitales Format um und gibt digitale U- und V-Signale in Abhängigkeit von dem CLK-Signal an den Demultiplexer **540** aus, wobei jedes Intervall des CLK-Signals einen einzelnen Taktzyklus oder ein Zeitintervall definiert. Bei Schritt **603** stellt der Demultiplexer **540** wiederum dem Filter **550** die digitalen U- und V-Signale in Abhängigkeit von dem EN-Signal bereit. Bei Schritt **604** führt das Filter **550** einen Filtervorgang (z. B. Interpolieren) an den digitalen U- und V-Signalen durch, die von dem Demultiplexer **540** bereitgestellt werden, und gibt gefilterte U- und V-Signale an die Unterabtasteinrichtung **560** auf eine zeitlich zugeordnete Art und Weise in Abhängigkeit von dem CLK-Signal aus. Danach, bei Schritt **605**, führt die Unterabtasteinrichtung **560** einen Unterabtastvorgang an den gefilterten U- und V-Signalen durch, die von dem Filter **550** bereitgestellt werden, und gibt unterabgetastete U- und V-Signale auf eine zeitlich zugeordnete Art und Weise aus. Die zeitlich zugeordneten U- und V-Ausgangssignale von der Unterabtasteinrichtung **560** werden danach zur weiteren Verarbeitung, wie beispielsweise Farbkorrektur, Farbtonkorrektur, Abtastratenumwandlung, und/oder für einen anderen Verarbeitungsvorgang bereitgestellt.

**[0041]** Wie hier beschrieben macht die vorliegende Erfindung vorteilhafterweise analoge Verzögerungsmittel in einem multiplexierten ADC-System überflüssig, das zeitlich zugeordnete Ausgabeabtastungen bereitstellt. Obwohl die bevorzugten Ausführungsformen hier unter Bezugnahme auf nur zwei Eingangssignale (d. h. U und V) beschrieben werden, ist es für die Fachleute unmittelbar erkennlich, dass die Prinzipien der vorliegenden Erfindung auf Systeme angewendet werden können, die mehr als zwei Eingangssignale haben. Demzufolge können die Prinzipien der vorliegenden Erfindung angewendet werden, um jede Anzahl von Signalkanälen mit zeitlich zugeordneten Ausgangssignalen bereitzustellen.

**[0042]** Die hier beschriebene vorliegende Erfindung ist insbesondere auf unterschiedliche Videosysteme anwendbar, entweder mit oder ohne Anzeigeeinrichtungen. Demzufolge ist vorgesehen, dass der Ausdruck „Videosystem“ oder ähnliche Ausdrücke, wie hier verwendet, unterschiedliche Arten von Systemen oder Geräten umfasst, einschließlich, aber nicht beschränkt auf Fernsehgeräte und Bildschirme, die eine Anzeigeeinrichtung einschließen, und Systeme oder Geräte, wie ein Zusatzempfangsgerät, VCR, DVD-Abspielgerät, eine Videospielkonsole, ein PVR oder ein anderes Videosystem, das vielleicht keine Anzeigeeinrichtung einschließt. Darüber hinaus kann die vorliegende Erfindung auch auf andere Systeme anwendbar sein, wie beispielsweise Audiosysteme, die einen Videoausgang aufweisen.

### Patentansprüche

1. Digitales Videosystem (**500**), umfassend:

Mittel (**520**, **530**, **540**), aufweisend einen Analog-/Digitalwandler (**530**) zum Umwandeln von gleichzeitigen ersten und zweiten analogen Farbdifferenzsignalen in jeweils erste und zweite digitale Signale und zum Ausgeben des ersten digitalen Signals während eines ersten Zeitintervalls und zum Ausgeben des zweiten digitalen Signals während eines zweiten Zeitintervalls, das sich von dem genannten ersten Zeitintervall unterscheidet; und ein digitales Filter (**550**) zum Filtern der ersten und zweiten digitalen Signale, um jeweils erste und zweite gefilterte Signale zu erstellen, wobei die genannten ersten und zweiten gefilterten Signale Werte haben, welche jeweils gleichzeitigen Werten der genannten ersten und zweiten analogen Farbdifferenzsignale entsprechen, und

Mittel (**560**) zum gleichzeitigen Ausgeben der genannten Werte der ersten und zweiten gefilterten Signale, welche jeweils gleichzeitigen Werten der genannten ersten und zweiten analogen Farbdifferenzsignale entsprechen, während eines dritten Zeitintervalls.

2. System (**400**) nach Anspruch 1, ferner einen Multiplexer (**520**) zum Bereitstellen der ersten und zweiten analogen Farbdifferenzsignale zu dem Analog-/Digitalwandler (**530**) umfassend.

3. System (**400**) nach Anspruch 1, ferner einen Demultiplexer (**540**) zum Empfangen der ersten und zweiten digitalen Signale von dem Analog-/Digitalwandler (**520**) und zum Bereitstellen der ersten und zweiten digitalen Signale zu dem digitalen Filter (**550**) umfassend.

4. System (**400**) nach Anspruch 1, ferner mindestens eine Unterabtasteinrichtung (**560**) zum Durchführen eines Unterabtastvorgangs an den ersten und zweiten gefilterten Signalen umfassend, um jeweils erste und zweite unterabgetastete Signale zu erstellen, und zum Ausgeben der ersten und zweiten unterabgetasteten Signale auf eine zeitlich zugeordnete Art und Weise während eines vierten Zeitintervalls.

5. System (**400**) nach Anspruch 4, wobei das erste, zweite, dritte und vierte Zeitintervall jeweils einem einzelnen Taktzyklus entspricht.

6. Verfahren zum Verarbeiten von analogen Farbdifferenzsignalen in einem digitalen Videosystem (**500**), die folgenden Schritte umfassend:

Umwandeln von gleichzeitigen ersten und zweiten analogen Farbdifferenzsignalen in jeweils erste und zweite digitale Signale;

Ausgeben des ersten digitalen Signals während eines ersten Zeitintervalls;

Ausgeben des zweiten digitalen Signals während eines zweiten Zeitintervalls, das sich von dem genannten ersten Zeitintervall unterscheidet;

Filtern der ersten und zweiten digitalen Signale, um jeweils erste und zweite gefilterte Signale zu erstellen, wobei die genannten ersten und zweiten gefilterten Signale Werte haben, die jeweils gleichzeitigen Werten der genannten ersten und zweiten analogen Farbdifferenzsignale entsprechen; und gleichzeitiges Ausgeben der genannten Werte der ersten und zweiten gefilterten Signale, welche jeweils gleichzeitigen Werten der genannten ersten und zweiten analogen Farbdifferenzsignale entsprechen, während eines dritten Zeitintervalls.

7. Verfahren nach Anspruch 6, ferner einen Schritt des Multiplexierens der ersten und zweiten analogen Farbdifferenzsignale vor dem Umwandlungsschritt umfassend.

8. Verfahren nach Anspruch 6, ferner einen Schritt des Demultiplexierens der ersten und zweiten digitalen Signale vor dem Filterschritt umfassend.

9. Verfahren nach Anspruch 6, ferner folgende Schritte umfassend:

Durchführen eines Unterabtastvorgangs an den ersten und zweiten gefilterten Signalen, um jeweils erste und zweite unterabgetastete Signale zu erstellen; und

Ausgeben der ersten und zweiten unterabgetasteten Signale auf eine zeitlich zugeordnete Art und Weise während eines vierten Zeitintervalls.

10. Verfahren nach Anspruch 9, wobei das erste, zweite, dritte und vierte Zeitintervall jeweils einem einzelnen Taktzyklus entspricht.

Es folgen 3 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

600

S

FIG. 6