(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6463169号

(P6463169)

(45) 発行日 平成31年1月30日(2019.1.30)

(24) 登録日 平成31年1月11日(2019.1.11)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| HO4L 25/02 (2006.01) | HO4L 25/02 J |

| HO4N 5/378 (2011.01) | HO4N 5/378   |

| HO4L 25/40 (2006.01) | HO4L 25/40 Z |

| HO3K 23/00 (2006.01) | HO3K 23/00 E |

| HO3K 21/12 (2006.01) | HO3K 21/12   |

請求項の数 15 (全 16 頁)

(21) 出願番号 特願2015-39318 (P2015-39318)

(22) 出願日 平成27年2月27日 (2015.2.27)

(65) 公開番号 特開2016-163156 (P2016-163156A)

(43) 公開日 平成28年9月5日 (2016.9.5)

審査請求日 平成30年2月27日 (2018.2.27)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】電子回路およびカメラ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1信号を出力する第1出力端子および前記第1信号より周期が小さい第2信号を出力する第2出力端子を有する生成回路と、

第1入力端子および第3出力端子を有する第1デコーダと、

第2入力端子、第3入力端子および第4出力端子を有する第2デコーダと、

前記生成回路の前記第1出力端子に電気的に接続された第1伝送線および前記生成回路の前記第2出力端子に電気的に接続された第2伝送線を含む伝送路と、を備え、

前記第1信号は、基準クロックの立ち上がりエッジおよび立ち下がりエッジの一方である第1エッジに同期し、前記第2信号は、前記基準クロックの立ち上がりエッジおよび立ち下がりエッジの他方である第2エッジに同期し、

前記第1デコーダの前記第1入力端子は、前記第1伝送線に電気的に接続され、

前記第1デコーダの前記第3出力端子は、前記第2デコーダの前記第2入力端子への信号の入力を制御し、

前記第2デコーダの前記第3入力端子は、前記第2伝送線に電気的に接続され、

前記第2デコーダは、前記第2入力端子および前記第3入力端子に入力される信号に従つて、デコードされた信号を第4出力端子から出力する、

ことを特徴とする電子回路。

## 【請求項 2】

前記生成回路は、前記第1信号を含む第1信号群および前記第2信号を含む第2信号群

10

20

を生成し、

前記第1信号群は、前記第1エッジに同期し、前記第2信号群は、前記第2エッジに同期し、

前記伝送路は、前記第1伝送線を含む複数の第1信号線および前記第2伝送線を含む複数の第2信号線を含み、

前記複数の第1信号線は、前記第1信号群のうち対応する第1信号を伝送し、前記複数の第2信号線は、前記第2信号群のうち対応する第2信号を伝送し、

前記複数の第1伝送線と前記複数の第2伝送線とは交互に配置されている、

ことを特徴とする請求項1に記載の電子回路。

**【請求項3】**

10

前記伝送路を介して送られてくる前記第1信号群および前記第2信号群を前記第1エッジおよび前記第2エッジの一方にのみ同期するように同期化する同期化回路を更に備える、

ことを特徴とする請求項2に記載の電子回路。

**【請求項4】**

前記生成回路は、前記基準クロックに従って動作して複数ビットの信号を生成する論理回路と、前記論理回路から出力される前記複数ビットの信号に従って前記第1信号群および前記第2信号群を生成するタイミング調整回路とを含む、

ことを特徴とする請求項2又は3に記載の電子回路。

**【請求項5】**

20

前記タイミング調整回路は、前記第1エッジに従って同期化を行うことによって前記第1信号群を生成する複数の第1フリップフロップと、前記第2エッジに従って同期化を行うことによって前記第2信号群を生成する複数の第2フリップフロップとを含み、

前記複数の第1フリップフロップに前記第1エッジを提供する信号線と、前記複数の第2フリップフロップに前記第2エッジを提供する信号線とが互いに交差していない、

ことを特徴とする請求項4に記載の電子回路。

**【請求項6】**

前記論理回路は、前記基準クロックに従ってカウント動作を行うカウンタを含む、

ことを特徴とする請求項4又は5に記載の電子回路。

**【請求項7】**

30

前記カウンタは、バイナリカウンタである、

ことを特徴とする請求項6に記載の電子回路。

**【請求項8】**

前記カウンタは、グレイコードカウンタである、

ことを特徴とする請求項6に記載の電子回路。

**【請求項9】**

前記カウンタは、カウント値をリセットする機能およびカウント値をセットする機能の少なくとも一方を有することを特徴とする請求項8に記載の電子回路。

**【請求項10】**

複数の画素を有する画素アレイと、

40

前記画素アレイからの信号をA/D変換するA/D変換器と、を更に備え、

前記カウンタによるカウント値が前記A/D変換器に供給される、

ことを特徴とする請求項6乃至9のいずれか1項に記載の電子回路。

**【請求項11】**

複数の画素を有する画素アレイと、

前記画素アレイにおける画素を選択するための選択回路を更に備え、

前記第1信号群および前記第2信号群は、前記伝送路を介して前記選択回路に供給される、

ことを特徴とする請求項6乃至9のいずれか1項に記載の電子回路。

**【請求項12】**

50

前記第1デコーダの前記第3出力端子は、同期回路を介して前記第2デコーダの前記第2入力端子に接続されている、

ことを特徴とする請求項1乃至11のいずれか1項に記載の電子回路。

**【請求項13】**

前記同期回路は、前記第1デコーダの前記第3出力端子から出力される信号を前記基準クロックに同期させた信号を前記第2デコーダの前記第2入力端子に出力する、

ことを特徴とする請求項12に記載の電子回路。

**【請求項14】**

前記同期回路は、前記第1デコーダの前記第3出力端子から出力される信号を前記基準クロックの前記第2エッジに同期させた信号を前記第2デコーダの前記第2入力端子に出力する、

ことを特徴とする請求項13に記載の電子回路。

**【請求項15】**

請求項10又は11に記載の電子回路を固体撮像装置として備えることを特徴とするカメラ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、電子回路およびカメラに関する。

**【背景技術】**

**【0002】**

信号線間の距離が小さくなると、信号線間の寄生容量が問題となってくる。特に、隣接する2本の信号線に互いに逆相の信号が出力される場合に、該2本の信号線の間の寄生容量によって信号の遷移が遅延する。特許文献1には、隣接する2本の信号線に互いに逆相の信号が伝達される場合の問題を解決することを目的とする発明が記載されている。具体的には、特許文献1には、互いに同相の信号を伝達する複数の信号配線からなる第1の信号配線群および第1の信号配線群とは逆相の信号を伝達する複数の信号配線からなる第2の信号配線群を有する半導体記憶装置が記載されている。この半導体装置では、第1の信号配線群と第2の信号配線群との距離が同一信号配線群内の信号配線間距離より大きい。

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【特許文献1】特開平2-28449号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

特許文献1に記載されたように信号線間の距離を大きくすることによって寄生容量に起因する信号の遷移の遅延を低減する方法では、信号線群が占める領域が大きくなり、これが回路面積の増大をもたらしうる。

**【0005】**

本発明は、回路面積の増大を抑制しつつ信号の伝達を高速化するための有利な技術を提供することを目的とする。

**【課題を解決するための手段】**

**【0006】**

本発明の1つの側面は、電子回路に係り、前記電子回路は、第1信号を出力する第1出力端子および前記第1信号より周期が小さい第2信号を出力する第2出力端子を有する生成回路と、第1入力端子および第3出力端子を有する第1デコーダと、第2入力端子、第3入力端子および第4出力端子を有する第2デコーダと、前記生成回路の前記第1出力端子に電気的に接続された第1伝送線および前記生成回路の前記第2出力端子に電気的に接続された第2伝送線を含む伝送路と、を備え、前記第1信号は、基準クロックの立ち上

10

20

30

40

50

がりエッジおよび立ち下がりエッジの一方である第1エッジに同期し、前記第2信号は、前記基準クロックの立ち上がりエッジおよび立ち下がりエッジの他方である第2エッジに同期し、前記第1デコーダの前記第1入力端子は、前記第1伝送線に電気的に接続され、前記第1デコーダの前記第3出力端子は、前記第2デコーダの前記第2入力端子への信号の入力を制御し、前記第2デコーダの前記第3入力端子は、前記第2伝送線に電気的に接続され、前記第2デコーダは、前記第2入力端子および前記第3入力端子に入力される信号に従って、デコードされた信号を第4出力端子から出力する。

【発明の効果】

【0007】

本発明によれば、回路面積の増大を抑制しつつ信号の伝達を高速化するための有利な技術が提供される。 10

【図面の簡単な説明】

【0008】

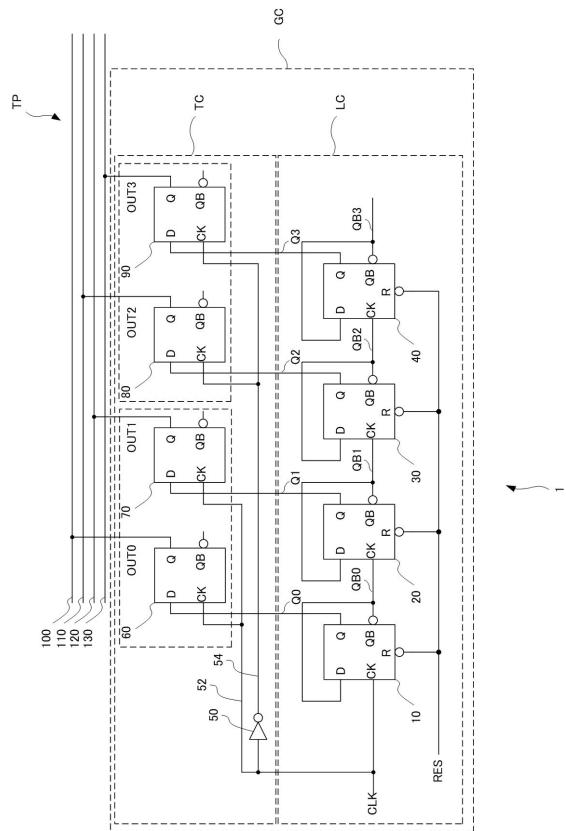

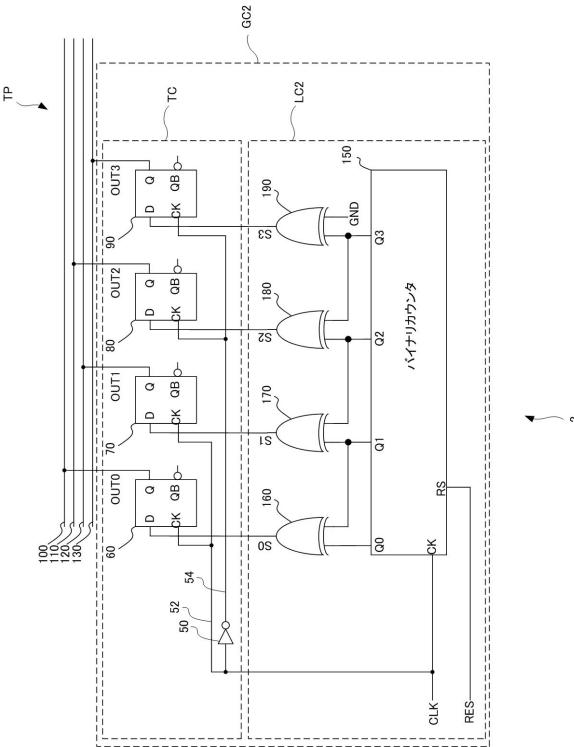

【図1】第1実施形態の電子回路またはカウンタの構成を示す図。

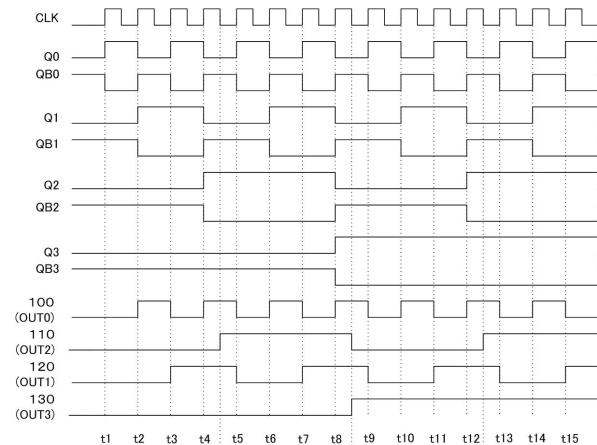

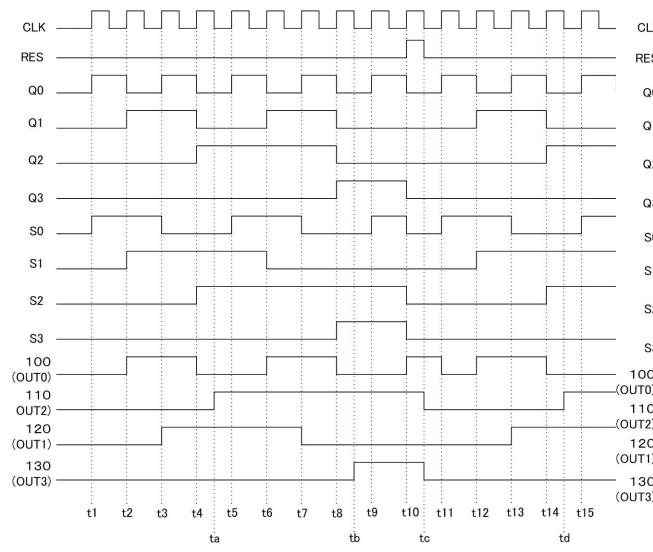

【図2】第1実施形態の動作例を示す図。

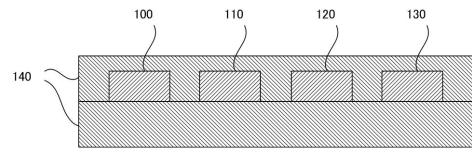

【図3】伝送路を構成する複数の伝送線の配置を例示する図。

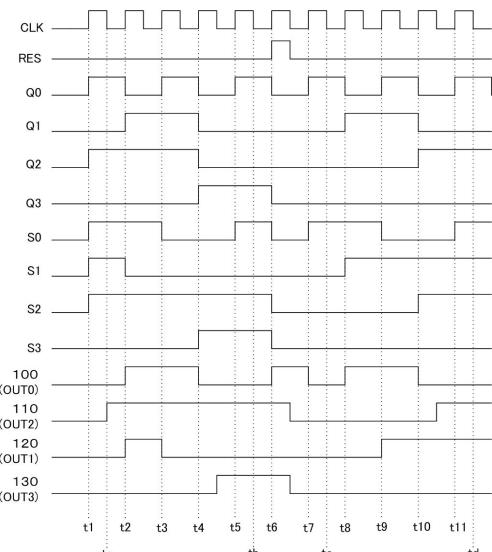

【図4】第2実施形態の電子回路またはカウンタの構成を示す図。

【図5】第2実施形態の動作例を示す図。

【図6】第2実施形態の他の動作例を示す図。

【図7】第2実施形態の更に他の動作例を示す図。 20

【図8】第3実施形態の電子回路または固体撮像装置の構成を示す図。

【図9】第3実施形態の電子回路または固体撮像装置の一部の構成を示す図。

【図10】第3実施形態の電子回路または固体撮像装置の他の一部の構成を示す図。

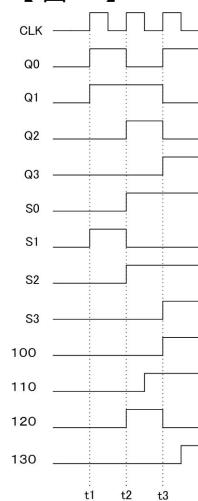

【図11】第3実施形態の電子回路または固体撮像装置の動作例を示す図。

【発明を実施するための形態】

【0009】

以下、添付図面を参照しながら本発明をその例示的な実施形態を通して説明する。

【0010】

図1を参照しながら本発明の第1実施形態の電子回路1について説明する。電子回路1は、第1信号群および第2信号群を生成する生成回路GCと、第1信号群および第2信号群を伝送する伝送路TPとを備える。第1信号群は、基準クロックCLKの立ち上がりエッジおよび立ち下がりエッジの一方である第1エッジにのみ同期した複数の信号OUT0、OUT1で構成される。第2信号群は、基準クロックCLKの立ち上がりエッジおよび立ち下がりエッジの他方である第2エッジにのみ同期した複数の信号OUT2、OUT3で構成される。伝送路TPは、第1信号群を構成する複数の信号OUT0、OUT1を伝送する複数の第1伝送線100、120と、第2信号群を構成する複数の信号OUT2、OUT3を伝送する複数の第2伝送線110、130とを含む。複数の第1伝送線100、120と複数の第2伝送線110、130とは交互に配置されている。換言すると、複数の第1伝送線100、120と複数の第2伝送線110、130とは、第1伝送線100、第2伝送線110、第1伝送線110、第2伝送線130の順で配置されている。 30

【0011】

生成回路GCは、論理回路LCおよびタイミング調整回路TCを含みうる。論理回路LCは、基準クロックCLKに従って動作して、複数ビットの信号Q0、Q1、Q2、Q3を生成する。タイミング調整回路TCは、論理回路LCから出力される複数ビットの信号Q0、Q1、Q2、Q3に従って、複数の第1伝送線100、110に出力される第1信号群、および、複数の第2信号線110、130に出力される第2信号群を生成する。

【0012】

タイミング調整回路TCは、複数の第1フリップフロップ60、70、および、複数の第2フリップフロップ80、90を含みうる。複数の第1フリップフロップ60、70は、基準クロックCLKの立ち上がりエッジおよび立ち下がりエッジの一方である第1エッジ 40

10

20

30

40

50

ジに従って同期化を行うことによって、第1信号群を構成する複数の信号OUT0、OUT1を生成する。複数の第2フリップフロップ80、90は、基準クロックCLKの立ち上がりエッジおよび立ち下がりエッジの他方である第2エッジに従って同期化を行うことによって、第2信号群を構成する複数の信号OUT2、OUT3を生成する。

【0013】

タイミング調整回路TCは、信号線52、54を含みうる。信号線52は、複数の第1フリップフロップ60、70に対して、基準クロックCLKの立ち上がりエッジおよび立ち下がりエッジの一方である第1エッジを提供する。信号線54は、複数の第2フリップフロップ80、90に対して、基準クロックCLKの立ち上がりエッジおよび立ち下がりエッジの他方である第2エッジを提供する。一例において、信号線52は、基準クロックCLKを供給する信号線であり、信号線54は、基準クロックCLKをインバータ50によって反転した反転基準クロックを供給する信号線である。

10

【0014】

信号線52と信号線54とは、互いに交差しないように配置されることが好ましい。これは、信号線52、54を通して伝達される基準クロックCLKおよび反転クロック信号の鈍りを低減するために有利である。図1に示された例では、互いに重ならない第1矩形領域および第2矩形領域を定義し、第1矩形領域の中に複数の第1フリップフロップ60、70が配列され、第2矩形領域の中に複数の第2フリップフロップ80、90が配列されている。このような構成は、信号線52と信号線54とが互いに交差しない配置を提供するために有利である。一方、例えば、複数の第1フリップフロップ60、70と第2フリップフロップ80、90とを交互に配置する構成では、信号線52と信号線54が交差しうる。

20

【0015】

第1実施形態では、論理回路LCは、基準クロックCLKに従ってカウント動作を行うカウンタでありうる。該カウンタによるカウントの形式は、例えば、アップカウントまたはダウンカウントでありうるが、他の形式であってもよい。他の例において、論理回路LCは、例えば、複数ビットの信号Q0、Q1、Q2、Q3の信号としてランダムな値を有する信号を生成する回路、あるいは、入力された信号を処理して得られる値を出力する回路でありうる。

30

【0016】

図1に示された例では、論理回路LCは、複数のフリップフロップ10、20、30、40を直列接続して構成されたカウンタである。複数のフリップフロップ10、20、30、40は、クロック端子CK、データ入力端子D、データ出力端子Q、反転データ出力端子QBおよびリセット端子Rを有する。

【0017】

1段目のフリップフロップ10のクロック端子CKには、基準クロックCLKが供給される。フリップフロップ10の反転データ出力端子QBとフリップフロップ10のデータ入力端子Dとが接続され、フリップフロップ10のデータ出力端子Qから信号Q0が出力される。

40

【0018】

2段目のフリップフロップ20のクロック端子CKには、1段目のフリップフロップ10の反転データ出力端子QBが接続され、1段目のフリップフロップ10の反転データ出力QB0が供給される。フリップフロップ20の反転データ出力端子QBとフリップフロップ20のデータ入力端子Dとが接続され、フリップフロップ20の出力端子Qから信号Q1が出力される。

【0019】

3段目のフリップフロップ30のクロック端子CKには、2段目のフリップフロップ20の反転データ出力端子QBが接続され、2段目のフリップフロップ20の反転データ出力QB1が供給される。フリップフロップ30の反転データ出力端子QBとフリップフロップ30のデータ入力端子Dとが接続され、フリップフロップ30の出力端子Qから信号Q2が出力される。

50

Q 2 が出力される。

【0020】

4段目のフリップフロップ40のクロック端子CKには、3段目のフリップフロップ30の反転データ出力端子QBが接続され、3段目のフリップフロップ30の反転データ出力QB2が供給される。フリップフロップ40の反転データ出力端子QBとフリップフロップ40のデータ入力端子Dとが接続され、フリップフロップ40の出力端子Qから信号Q3が出力される。フリップフロップ10、20、30、40のリセット端子Rには、初期化時にリセット信号RESが供給される。

【0021】

図2には、図1に示された電子回路1の動作が記載されている。初期状態では、リセット信号RESがローレベルにされることによって信号Q0、Q1、Q2、Q3はローレベルにリセットされているものとする。1段目のフリップフロップ10の出力である信号Q0は、基準クロックCLKの1つ目の立ち上がりエッジの時刻t1でローレベルからハイレベルに遷移し、基準クロックCLKの2つ目の立ち上がりエッジの時刻t2でハイレベルからローレベルに遷移する。このように、信号Q0は、基準クロックCLKの立ち上がりエッジに従ってトグルする。

【0022】

2段目のフリップフロップ20は、クロック端子CKに1段目のフリップフロップ10の反転データ出力端子QBが接続されている。このため、2段目のフリップフロップ20は、1段目のフリップフロップ10の反転データ出力QB0がローレベルからハイレベルに遷移したことに応じて、その出力である信号Q1を変化させる。具体的には、2段目のフリップフロップ20は、カウントの開始後に1段目のフリップフロップ10の出力である信号Qが最初にハイレベルからローレベルに遷移する時刻t2において、出力である信号Q1をローレベルからハイレベルに遷移させる。そして、2段目のフリップフロップ20は、信号Q0が2回目にハイレベルからローレベルに遷移する時刻t4において、信号Q1をローレベルからハイレベルに遷移させる。このように、信号Q1は、信号Q0がハイレベルからローレベルに遷移する度に、即ち、信号Q0の立ち下がりエッジ(信号QB0の立ち上がりエッジ)に従ってトグルする。

【0023】

3段目以降のフリップフロップ30、40についても、各クロック端子CKに前段のフリップフロップの反転データ出力端子QBが接続されている。したがって、3段目以降のフリップフロップ30、40の動作は、2段目のフリップフロップ20の動作と同様であり、前段のフリップフロップのデータ出力端子Qの出力がローレベルからハイレベルに遷移する度にトグルする。換言すると、フリップフロップ30、40は、反転データ出力端子QBの出力がハイレベルからローレベルに遷移する度にトグルする。

【0024】

以上のように、フリップフロップ10、20、30、40で構成される論理回路LCとしてのカウンタは、アップカウント動作を行って信号Q0、Q1、Q2、Q3を生成する。信号Q0、Q1、Q2、Q3は、第1フリップフロップ60、70、第2フリップフロップ80、90を含むタイミング調整回路TCを介して信号OUT0、OUT1、OUT2、OUT3として伝送線100、110、120、130に出力される。

【0025】

第1フリップフロップ60、70のクロック端子CKには、信号線52を介して基準クロックCLKが供給され、それぞれのデータ入力端子Dには、信号Q0、Q1が供給される。よって、第1フリップフロップ60、70のデータ出力端子Qからの出力である信号OUT0、OUT1は、信号Q0、Q1をそれぞれ基準クロックCLKの1周期分だけ遅延させた信号となる。一方、第2フリップフロップ80、90のクロック端子CKには、インバータ50および信号線54を介して、基準クロックCLKを反転させた反転基準クロックが供給され、それぞれのデータ入力端子Qには信号Q2、Q3が供給される。よって、第2フリップフロップ80、90のデータ出力端子Qからの出力である信号OUT2

10

20

30

40

50

、OUT3は、信号Q2、Q3をそれぞれ基準クロックCLKの半周期分だけ遅延させた信号となる。つまり、信号OUT2、OUT3は、時刻ta、tb、tcにおいて、基準クロックCLKの立ち下がりエッジに従って遷移する。

【0026】

信号OUT0、OUT1、OUT2、OUT3は、伝送路TPを構成する伝送線100、120、110、130にそれぞれ出力される。ここで、カウント値の第1、第2ビットである信号OUT0、OUT1は、第1伝送線100、120に出力され、カウント値の第3、第4ビットである信号OUT2、OUT3は、第2伝送線110、130に出力される。図1に例示されているように、第1伝送線100、120と第2伝送線110、130とは交互に配置されている。したがって、信号OUT0、OUT1、OUT2、OUT3が10出力される伝送線100、120、110、130において、隣り合う伝送線の信号が同時に遷移することはない。これにより、伝送線100、120、110、130間の寄生容量に起因する信号の遷移の遅延が低減される。また、伝送線100、120、110、130の間隔を小さくするとともに均一化することができる。これは、電子回路1の回路面積の増大を抑制しつつ信号の伝達を高速化するために有利である。

【0027】

図3には、伝送路TPを構成する伝送線100、120、110、130の例が示されている。図3(a)は、伝送線100、120、110、130が同一の層に配置された例であり、図3(b)は、伝送線100、120、110、130が互いに異なる層に配置された例である。伝送線100、120、110、130は、典型的には、層間絶縁膜140によって相互に絶縁されている。伝送線100、120、110、130は、例えば、アルミニウムまたは銅などの導電材料によって構成されうる。図3には示されていないが、伝送線100、120、110、130の寄生容量の均一化のために、伝送線100の隣り(図3(a)では左、図3(b)では上)および伝送線130の隣り(図3(a)では右、図3(b)では下)にダミーの伝送線を配置してもよい。また、伝送線100、120、110、130を長く引き回す場合には、バッファを介在させてもよい。また、信号OUT0、OUT1、OUT2、OUT3を伝送する伝送線100、120、110、130と信号OUT0、OUT1、OUT2、OUT3の伝送先の回路との間に同期化回路を設けてもよい。この同期化回路は、信号OUT0、OUT1、OUT2、OUT3を立ち上りエッジおよび立ち下がりエッジの一方にのみ同期化させる。実施形態3は、このような同期化回路を備える例である。2030

【0028】

図4を参照しながら本発明の第2実施形態の電子回路2について説明する。なお、第2実施形態として言及しない事項は、第1実施形態に従う。第2実施形態では、第1信号群および第2信号群を生成する生成回路GCは、論理回路LCの代わりに論理回路LC2を備えている。論理回路LC2は、グレイコードカウンタである。論理回路LC2は、バイナリカウンタ150と、EXORゲート(排他的論理和ゲート)160、170、180、190とを含む。EXORゲート160、170、180、190は、バイナリカウンタ150から出力されるバイナリコードのカウント値である信号Q0、Q1、Q2、Q3からグレイコードの信号S0、S1、S2、S3を生成する。バイナリカウンタ150は、例えば、第1実施形態における論理回路LCと同様の構成を有しうるが、他の構成を有してもよい。バイナリカウンタ150は、この例では、基準クロックCLKに従ってカウント動作を実行して、バイナリコードのカウント値である信号Q0、Q1、Q2、Q3を生成する。バイナリカウンタ150は、リセット端子RSに供給されるリセット信号RESがアクティブルレベルになることに応じて信号Q0、Q1、Q2、Q3を初期値にリセットする。40

【0029】

図5には、図4に示された電子回路2の動作が記載されている。バイナリカウンタ150から出力される信号Q0、Q1、Q2、Q3は、時刻t10までは、図2と同じようにバイナリコードのカウント値である。時刻t10でバイナリカウンタ150のリセット端50

子 R S に供給されるリセット信号 R E S がアクティブルーレベルになり、信号 Q 0 、 Q 1 、 Q 2 、 Q 3 が全て 0 にリセットされる。ここで、一例において、リセット信号 R E S は、信号 Q 0 、 Q 1 、 Q 2 、 Q 3 が所定値になったことを検知するデコーダ（不図示）によって与えられうる。リセット信号 R E S がアクティブルーレベルとなった後、時刻 t 1 1 ~ 1 5 において、時刻 t 1 ~ t 5 と同じカウント値の信号 Q 0 、 Q 1 、 Q 2 、 Q 3 が出力される。

#### 【 0 0 3 0 】

なお、 Q 0 と Q 1 との EXOR である S 0 、 Q 1 と Q 2 との EXOR である S 1 、 Q 2 と Q 3 との EXOR である S 2 、 Q 3 と GND ( ローレベル ) との EXOR である S 3 は、図 5 に示されようにグレイコードのカウント値である。グレイコードのカウント値である信号 S 0 、 S 1 、 S 2 、 S 3 において、同一タイミングで遷移する信号は基本的には 1 つである。しかし、時刻 t 1 0 においてバイナリカウンタ 150 のカウント値がリセットされるタイミングで、信号 S 0 、 S 2 、 S 3 が同時に遷移する。よって、グレイコードカウンタにおいても、例えば、 0 から 9 までのカウントを繰り返すような場合は、複数の信号が同時に遷移しうる。そこで、タイミング調整回路 S C によって基準クロック C L K の立ち上がり、立ち下がりエッジの一方である第 1 エッジにのみ同期した第 1 信号群と基準クロック C L K の立ち上がり、立ち下がりエッジの他方である第 2 エッジにのみ同期した第 2 信号群とが生成される。そして、第 1 信号群を構成する複数の信号 O U T 0 、 O U T 1 を伝送する複数の第 1 伝送線 100 、 120 と、第 2 信号群を構成する複数の信号 O U T 2 、 O U T 3 を伝送する複数の第 2 伝送線 110 、 130 とは、交互に配置されている。

#### 【 0 0 3 1 】

図 5 に示された例では、カウント値 Q 0 、 Q 1 、 Q 2 、 Q 3 をリセットする機能によってカウント範囲が設定される。これに代えて、または、これに加えて、図 6 に例示されるように、カウント値 Q 0 、 Q 1 、 Q 2 、 Q 3 をセットする機能によってカウント範囲が設定されてもよい。図 6 に示された例では、信号 Q 0 、 Q 1 、 Q 2 、 Q 3 の初期値が 1 、 0 、 1 、 0 に設定され、時刻 t 1 からカウント動作が開始している。この場合も、時刻 t 1 において、信号 S 0 、 S 1 、 S 2 が同時に遷移している。また、図 5 では、信号 Q 0 、 Q 1 、 Q 2 、 Q 3 で示されるカウント値が 1 ずつカウントアップするが、 2 以上の値ずつカウントアップする場合も、グレイコードを構成する複数の信号が同時に遷移しうる。図 7 に示された例では、 Q 0 、 Q 1 、 Q 2 、 Q 3 が 3 ずつカウントアップする。時刻 t 1 以前ではカウント値は 0 、時刻 t 1 ~ t 2 ではカウント値は 3 、時刻 t 2 ~ t 3 ではカウント値は 6 、時刻 t 3 ~ t 4 ではカウント値は 9 となっている。図 7 に示された例において、時刻 t 2 で S 0 、 S 1 、 S 2 が同時に遷移している。

#### 【 0 0 3 2 】

第 2 実施形態においても、第 1 実施形態において説明したようなダミーの伝送線が設けられることが好ましい。

#### 【 0 0 3 3 】

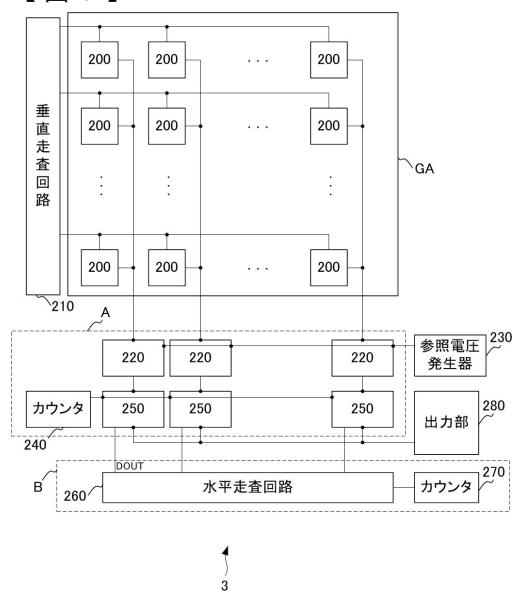

図 8 、 9 を参照しながら本発明の第 3 実施形態の電子回路 3 について説明する。電子回路 3 は、固体撮像装置として構成されている。電子回路 3 は、カウンタ 240 およびカウンタ 270 を備えている。カウンタ 240 は、第 1 実施形態の電子回路 1 としてのカウンタまたは第 2 実施形態の電子回路 2 としてのカウンタで構成されうる。また、カウンタ 240 は、第 1 実施形態の電子回路 1 としてのカウンタまたは第 2 実施形態の電子回路 2 としてのカウンタで構成されうる。一つの好ましい例において、カウンタ 240 は、第 1 実施形態の電子回路 1 としてのカウンタで構成され、カウンタ 240 は、第 2 実施形態の電子回路 2 としてのカウンタで構成されうる。

#### 【 0 0 3 4 】

電子回路 3 は、画素アレイ G A 、垂直走査回路 210 、水平走査回路 260 、 A / D ( アナログ / デジタル ) 変換器 220 、メモリ 250 、参照電圧発生器 230 および出力部 280 を備えうる。画素アレイ G A は、複数の行および複数の列を構成するように配列された複数の画素 200 を含む。各画素 200 は、光電変換素子（例えば、フォトダイオード）を含む。各画素 200 は、光電変換素子で光電変換によって発生した電荷に応じた信

10

20

30

40

50

号を出力する増幅部を含んでもよい。垂直走査回路 210 および水平走査回路 260 の一方あるいは両方は、画素アレイ GA における画素 200 を選択する選択回路である。

【0035】

垂直走査回路 210 は、画素アレイ GA における画素 200 を行単位で選択する。垂直走査回路 210 によって選択された行の画素 200 の信号（アナログ信号）は、A/D 変換器 220 によってデジタル信号に変換される。A/D 変換器 220 は、画素アレイ GA における各列に対して設けられうる。カウンタ 240 は、複数の A/D 変換器 220 に対して共通に設けられ、カウント動作によって  $n$  ビット（ $n$  は自然数）のカウント値を生成する。ただし、複数のカウンタ 240 を備えて、例えば、所定数の A/D 変換器 220 ごとにに対して 1 つのカウンタ 240 を割り当ててもよい。

10

【0036】

A/D 変換器 220 は、例えば、画素 200 の出力信号と参照電圧発生器 230 から出力される参照信号とを比較する比較器を含みうる。参照信号は、時間とともに変化する信号（例えば、ランプ信号）である。比較器は、画素 200 の出力信号と参照信号との大小関係を示す比較結果信号を出力する。画素 200 の出力信号と参照信号との大小関係が反転すると比較結果信号が変化する。メモリ 250 は、比較結果信号の変化をトリガとして、カウンタ 240 から供給されているカウント値を保持する。これにより、画素 200 からの画素信号に応じたデジタル値（カウント値）がメモリ 250 によって保持される。

【0037】

水平走査回路 260 は、カウンタ 270 から供給されるカウント値に従って、画素アレイ GA の複数の行にそれぞれ対応する複数のメモリ 250 を順に選択し、選択されたメモリ 250 の信号を出力部 280 に転送させる。

20

【0038】

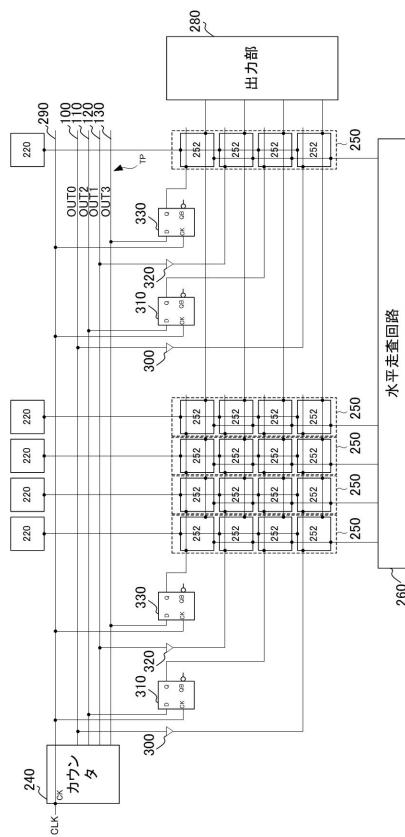

図 9 には、図 8 の領域 A の構成の具体例が示されている。メモリ 250 は、それぞれ 1 ビットの情報を保持する複数のメモリ 252 で構成される。カウンタ 240 は、例えば、第 1 実施形態の電子回路 1 としてのカウンタで構成されうる。カウンタ 240 が発生するカウント値（前述の OUT0、OUT2、OUT1、OUT3 …）は、伝送線 100、110、120、130 を含む伝送路 TP に出力される。ここで、カウント値は、第 1 実施形態として例示された構成では、4 ビットのカウント値であるが、このビット数は自由に決定されうる。伝送路 TP は、カウンタ 240 の構成要素として理解されてもよいし、他のブロックの構成要素として理解されてもよい。基準クロック CLK は、基準クロック線 90 を介してカウンタ 240 に供給される。

30

【0039】

伝送線 100、120、110、130 に出力される信号（カウント値）OUT0、OUT1、OUT2、OUT3 は、同期化回路を介してメモリ 250 に供給される。同期化回路は、信号 OUT0、OUT1、OUT2、OUT3 を基準クロック CLK の全てを基準クロック CLK の立ち上がりエッジおよび立ち下がりエッジの一方のみに同期するよう同期化する。図 9 に示された例では、伝送線 100、120 に出力される信号 OUT0、OUT1 は、基準クロック CLK の立ち上がりエッジに同期した信号であり、バッファ 300、320 を介して、該当するビットの信号を保持するメモリ 250 に供給される。一方、伝送線 110、130 に出力される信号 OUT2、OUT3 は、基準クロック CLK の立ち下がりエッジに同期した信号である。そこで、伝送線 110、130 に出力される信号 OUT2、OUT3 は、基準クロック CLK の立ち上がりエッジに従って動作するフリップフロップ 310、330 によって同期化されて、該当するビットの信号を保持するメモリ 250 に供給される。

40

【0040】

信号 OUT0、OUT1、OUT2、OUT3 を上記のような構成で伝送することにより、上記のように、伝送線 100、120、110、130 の間隔を小さくするとともに均一化することができる。

【0041】

50

これに加えて、第3実施形態によれば、次のような効果も提供されうる。従来の方式では、複数の伝送線における相互の容量結合による影響（信号の遷移速度）は、カウント値（信号が遷移するビットの数）に強く依存する。よって、従来の方式でメモリ250にカウント値を供給した場合、1つのカウント値から他のカウント値に遷移する時間がそれらのカウント値に強く依存し、A/D変換のリニアリティが低下しうる。一方、第3実施形態では、伝送線100、110、120、130における相互の容量結合による影響が低減されるので、1つのカウント値から他のカウント値に遷移する時間が均一化され、これによりA/D変換のリニアリティが向上しうる。

#### 【0042】

バッファ300、320の駆動能力とフリップフロップ310、330の駆動能力は、互いに等しいことが好ましい。また、第3実施形態においても、伝送線100、130の隣にダミーの伝送線を設けることが好ましい。加えて、伝送線290に付随する寄生容量を伝送線100、110、120、130とそろえるように、伝送線290の両側にダミーの伝送線を設けてもよい。これは、フリップフロップ310、330の出力は、伝送線290を伝送された基準クロックCLKに従って遷移するからである。つまり、伝送線290の寄生容量が伝送線100、120の寄生容量と大きく異なると、バッファ300、320の出力の遷移のタイミングとフリップフロップ310、330の出力の遷移のタイミングとがずれてしまう。

#### 【0043】

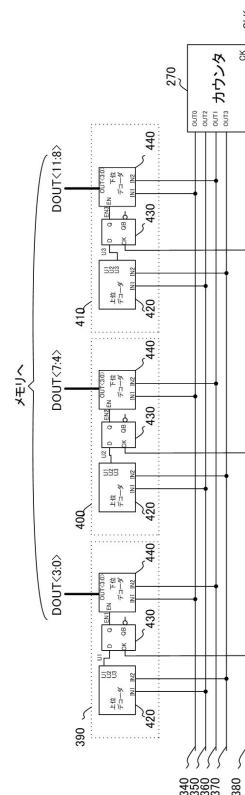

図10には、図8の領域Bの構成の具体例が示されている。カウンタ270は、例えば、第2実施形態の電子回路2としてのカウンタで構成されている。ただし、カウント値としての信号OUT0、OUT2、OUT1、OUT3は、伝送線340、350、360、370に出力される。伝送線340、350、360、370は、伝送線340、350、360、370の順に配置される。

#### 【0044】

水平走査回路260は、複数の単位回路390、400、410によって構成されるデコーダである。基準クロックCLKは、基準クロック線380を介して、カウンタ270、および、水平走査回路260は、複数の単位回路390、400、410に供給される。

#### 【0045】

水平走査回路260を構成する複数の単位回路390、400、410の各々は、上位デコーダ420、フリップフロップ430、下位デコーダ440を含む。上位デコーダ420の入力端子IN1、IN2にはOUT3、OUT4が入力され、上位デコーダ420の出力はフリップフロップ430に供給される。ここで、単位回路390、400、410の構成は、ほぼ同一であるが、上位デコーダ420のどの出力端子をフリップフロップ430のデータ端子Dに接続するかが異なっている。単位回路390においてはU1、単位回路400においてはU2、単位回路410においてはU3が、フリップフロップ430のデータ端子Dに接続されている。フリップフロップ430のクロック端子CKには基準クロックCLKが供給され、出力端子Qは下位デコーダ440のインバブル端子ENに接続されている。下位デコーダ440の入力端子IN1、IN2には、OUT1、OUT2が供給され、デコード結果を出力端子OUT<3:0>に出力する。

#### 【0046】

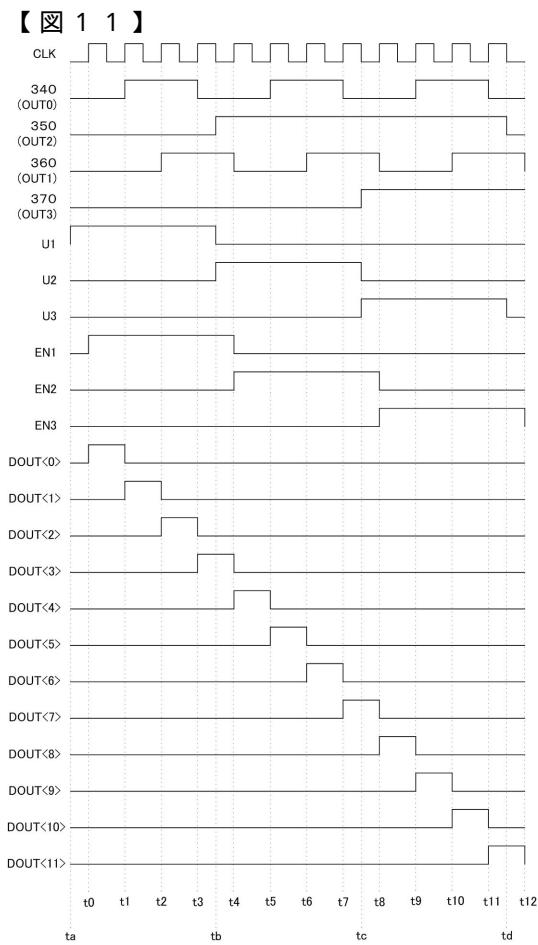

図11には、図10に示された構成のタイミング図が示されている。カウンタ270から出力される信号OUT0、OUT1、OUT2、OUT3は、グレイコードのカウント値を示す信号である。信号OUT0、OUT1は、基準クロックCLKの立ち上がりエッジに同期する信号であり、信号OUT2、OUT3は、基準クロックCLKの立ち下がりエッジに同期する信号である。

#### 【0047】

カウンタ270から出力される信号OUT0、OUT1は、基準クロックCLKの立ち上がりエッジに同期してカウントアップするグレイカウント信号となっている。OUT0

10

20

30

40

50

、 OUT 1 で構成されるカウント値は、時刻  $t_1$  でカウント値が 0 から 1 へ、時刻  $t_2$  でカウント値が 1 から 2 へ、時刻  $t_3$  でカウント値が 2 から 3 へ、時刻  $t_4$  でカウント値が 0 へと変化し、以降は同様な動作を繰り返す。すなわち、OUT 0、OUT 1 で構成されるカウント値は、0 から 3 までのカウントを繰り返す。一方、カウンタ 270 から出力される信号 OUT 2、OUT 3 は、基準クロック CLK の立ち下がりエッジに同期してカウントアップするグレイカウント信号となっている。OUT 2、OUT 3 で構成されるカウント値が 0 から 3 まで変化する周期は、OUT 0、OUT 1 で構成されるカウント値が 0 から 3 まで変化する周期の  $1/4$  である。OUT 2、OUT 3 で構成されるカウント値は、時刻  $t_b$  でカウント値が 0 から 1 へ、時刻  $t_c$  でカウント値が 1 から 2 へ、時刻  $t_d$  でカウント値が 2 から 3 へと変化している。

10

#### 【0048】

上位デコーダ 420 のそれぞれの出力端子 U1、U2、U3 は、入力端子 IN1、IN2 に供給される OUT 0、OUT 1 で構成されるカウント値がそれぞれ 0、1、2 となつた際にハイレベルとなる。よって、単位回路 390 において、フリップフロップ 430 の入力信号となる U1 は、時刻  $t_a$  から  $t_b$  においてハイレベルとなる。また、単位回路 400 において、フリップフロップ 430 の入力信号となる U2 は、時刻  $t_b$  から  $t_c$  においてハイレベルとなる。また、単位回路 410 において、フリップフロップ 430 の入力信号となる U3 は、時刻  $t_c$  から  $t_d$  においてハイレベルとなる。

#### 【0049】

単位回路 390 のフリップフロップ 430 は、U1 の立ち上がりを基準クロック CLK の半周期分だけ遅延させる（つまり、基準クロック CLK の立ち上がりエッジに同期して信号 EN1 をハイレベルにする）。単位回路 400 のフリップフロップ 430 は、U2 の立ち上がりを基準クロック CLK の半周期分だけ遅延させる（つまり、基準クロック CLK の立ち上がりエッジに同期して信号 EN2 をハイレベルにする）。単位回路 410 のフリップフロップ 430 は、U3 の立ち上がりエッジを基準クロック CLK の半周期分だけ遅延させる（つまり、基準クロック CLK の立ち上がりエッジに信号 EN3 をハイレベルにする）。

20

#### 【0050】

各下位デコーダ 440 においては、イネーブル端子 EN $x$ （ $x$  は 1 ~ 3）がローレベルの場合は、出力端子 OUT $<3:0>$  が全てローレベルとなる。一方、イネーブル端子 EN $x$  がハイレベルの場合は、入力端子 IN1、IN2 から入力されるカウント信号のカウント値がそれぞれ 0、1、2、3 となつた際に、出力端子 OUT $<0>$ 、OUT $<1>$ 、OUT $<2>$ 、OUT $<3>$  がそれぞれハイレベルとなる。よって、EN1 がハイとなる時刻  $t_0$  から  $t_4$  において単位回路 390 の下位デコーダ 440 の出力端子 OUT $<3:0>$  が順次にハイレベルとなる。すなわち、DOUT $<0>$ 、 $<1>$ 、 $<2>$ 、 $<3>$  が順次にハイレベルとなる。また、EN2 がハイとなる時刻  $t_4$  から  $t_8$  において単位回路 400 の下位デコーダ 440 の出力端子 OUT $<3:0>$  が順次にハイレベルとなる。すなわち、DOUT $<4>$ 、 $<5>$ 、 $<6>$ 、 $<7>$  が順次にハイレベルとなる。また、EN3 がハイとなる時刻  $t_8$  から  $t_{12}$  において単位回路 410 の下位デコーダ 440 の出力端子 OUT $<3:0>$  が順次にハイレベルとなる。すなわち、DOUT $<8>$ 、 $<9>$ 、 $<10>$ 、 $<11>$  が順次にハイレベルとなる。

30

#### 【0051】

第 3 実施形態によれば、前述の伝送線 100、110、120、130 における相互の容量結合による影響が低減されるのと同様に、伝送線 340、350、360、370 における相互の容量結合による影響が低減される。これにより、伝送線 340、350、360、370 を介して伝送されるカウント値が 1 つのカウント値から他のカウント値に遷移する時間が均一化される。これにより、DOUT $<0>$  ~  $<12>$  のパルス幅をより均一化することができ、メモリ 250 のデータを出力部 280 へ出力する期間を均一化することができる。よって、極端に読み出す時間が短い列が生じることを防止し、より高速な読み出し動作を行うことが可能となる。伝送線 340、350、360、370、380

40

50

に付随する寄生容量はそろえることが好ましい。

【 0 0 5 2 】

なお、上記例では、カウンタ270が水平走査回路260に接続されている構成を示したが、垂直走査回路210にカウンタ270が接続されている構成としてもよい。上記例では、カウンタ240に接続された伝送線100～130とカウンタ270に接続された伝送線340～370との其々において、立ち上がりエッジに同期した信号を伝送する伝送線と立ち下がりエッジに同期した信号を伝送する伝送線とが交互に配置される。これに代えて、カウンタ240に接続された伝送線100、110、120、130において、立ち上がりエッジに同期した信号を伝送する伝送線と、立ち下がりエッジに同期した信号を伝送する伝送線とが交互に配置されるようにしてもよい。あるいは、カウンタ270に接続された伝送線340、350、360、370において、立ち上がりエッジに同期した信号を伝送する伝送線と、立ち下がりエッジに同期した信号を伝送する伝送線とが交互に配置されるようにしてもよい。

〔 0 0 5 3 〕

以下、上記の電子回路としての固体撮像装置の応用例として、該固体撮像装置が組み込まれたカメラについて例示的に説明する。カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置（例えば、パーソナルコンピュータ、携帯端末）も含まれる。カメラは、上記の実施形態として例示された本発明に係る固体撮像装置と、該固体撮像装置から出力される信号を処理する処理部とを含む。該処理部は、例えば、A / D 変換器、および、該 A / D 変換器から出力されるデジタルデータを処理するプロセッサを含みうる。

## 【符号の説明】

〔 0 0 5 4 〕

1 : 電子回路、 G C : 生成回路、 L C : 論理回路、 T C : タイミング調整回路、 1 0 0 : 第 1 伝送線、 1 1 0 : 第 2 伝送線、 1 2 0 : 第 1 伝送線、 1 3 0 : 第 2 伝送線

〔 囮 1 〕

( 2 )

【図3】

(a)

(b)

【図4】

2

【図5】

【図6】

【図7】

【図8】

3

【図9】

【図10】

---

フロントページの続き

(72)発明者 小林 秀央

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 山崎 和男

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 横山 拓己

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 阿部 弘

(56)参考文献 特開平10-170886 (JP, A)

特開平09-006278 (JP, A)

特開平05-343987 (JP, A)

特開平04-219082 (JP, A)

米国特許第05191425 (US, A)

米国特許出願公開第2003/0117301 (US, A1)

特開2013-229708 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |         |

|--------|---------|

| H 04 L | 25 / 02 |

| H 03 K | 21 / 12 |

| H 03 K | 23 / 00 |

| H 04 L | 25 / 40 |

| H 04 N | 5 / 378 |