(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6112940号

(P6112940)

(45) 発行日 平成29年4月12日(2017.4.12)

(24) 登録日 平成29年3月24日(2017.3.24)

(51) Int.Cl.

F 1

|                    |                  |      |       |      |

|--------------------|------------------|------|-------|------|

| <b>H01L 21/338</b> | <b>(2006.01)</b> | H01L | 29/80 | F    |

| <b>H01L 29/812</b> | <b>(2006.01)</b> | H01L | 29/80 | H    |

| <b>H01L 29/778</b> | <b>(2006.01)</b> | H01L | 29/44 | S    |

| <b>H01L 29/41</b>  | <b>(2006.01)</b> | H01L | 21/28 | 301B |

| <b>H01L 21/28</b>  | <b>(2006.01)</b> | H01L | 29/58 | Z    |

請求項の数 7 (全 12 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2013-77408 (P2013-77408)   |

| (22) 出願日     | 平成25年4月3日(2013.4.3)          |

| (65) 公開番号    | 特開2014-29983 (P2014-29983A)  |

| (43) 公開日     | 平成26年2月13日(2014.2.13)        |

| 審査請求日        | 平成27年10月29日(2015.10.29)      |

| (31) 優先権主張番号 | 特願2012-151680 (P2012-151680) |

| (32) 優先日     | 平成24年7月5日(2012.7.5)          |

| (33) 優先権主張国  | 日本国(JP)                      |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000006013<br>三菱電機株式会社<br>東京都千代田区丸の内二丁目7番3号 |

| (74) 代理人  | 100088672<br>弁理士 吉竹 英俊                     |

| (74) 代理人  | 100088845<br>弁理士 有田 貴弘                     |

| (72) 発明者  | 岡崎 拓行<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

| (72) 発明者  | 南條 拓真<br>東京都千代田区丸の内二丁目7番3号 三菱電機株式会社内       |

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

A1GaN層を含むヘテロ接合半導体装置の製造方法であって、

(a) A1GaN層上のゲート電極が配置される領域に、金属から成るダミー電極を形成する工程と、

(b) 異方性のある装置を用いて、前記ダミー電極側面を露出させつつ、前記A1GaN層上に誘電膜を堆積させる工程と、

(c) 前記ダミー電極をウェットエッティング処理によって除去することにより、前記誘電膜に開口を形成する工程と、

(d) 前記開口内からその周辺の前記誘電膜上に延在する前記ゲート電極を形成する工程とを備えることを特徴とする、10

半導体装置の製造方法。

## 【請求項 2】

前記工程(b)が、前記工程(c)において前記ダミー電極よりも除去比率が低い前記誘電膜を堆積させる工程であることを特徴とする、

請求項1に記載の半導体装置の製造方法。

## 【請求項 3】

前記工程(b)が、Cat-CVD法によって前記誘電膜を堆積させる工程であることを特徴とする、

請求項1に記載の半導体装置の製造方法。20

**【請求項 4】**

前記工程（b）が、E C Rスパッタ法によって前記誘電膜を堆積させる工程であることを特徴とする、

請求項1に記載の半導体装置の製造方法。

**【請求項 5】**

前記工程（b）が、前記A1GaN層と接する前記ダミー電極の厚さよりも薄く前記誘電膜を堆積させる工程であることを特徴とする、

請求項1に記載の半導体装置の製造方法。

**【請求項 6】**

前記工程（a）が、T型の形状である前記ダミー電極を形成する工程であることを特徴とする、10

請求項1に記載の半導体装置の製造方法。

**【請求項 7】**

前記工程（a）が、2層以上のダミー材料から前記ダミー電極を形成する工程であり、

前記A1GaN層に接する前記ダミー材料が、他の前記ダミー材料よりも酸またはアルカリ溶液に溶けやすいことを特徴とする、

請求項6に記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体装置の製造方法に関し、特に、A1GaN層を含むヘテロ接合を有する半導体装置のゲート電極の製造方法に関するものである。20

**【背景技術】****【0002】**

半導体装置の一例としての窒化物を含むヘテロ接合電界効果型トランジスタにおいて、高周波化に伴いゲート長を短くするとゲート電極の断面積が減少し、ゲート抵抗が増大する。これを回避するために、ゲート電極上部に傘を開いたような形状（庇状形状。張り出して乗り上げた形）に金属部を増大させ、半導体層と接する実質的ゲート長を短くした状態で、ゲート電極の断面積を大きくしてゲート抵抗を低減する方法がある。

**【0003】**

さらに、窒化物を含む半導体からなるヘテロ接合電界効果型トランジスタにおいて、特徴的な電流コラプスを抑制するために、増大させた金属部と半導体層の間に誘電膜を挿入して、ドレイン電極に高電圧を印加した際にドレイン電極側のゲート電極端に集中する電界を緩和する。例えば、非特許文献1がその代表例として挙げられる。30

**【先行技術文献】****【非特許文献】****【0004】**

【非特許文献1】Yunju Sun, Lester F. Eastman, 「IEEE TRANSACTIONS ON ELECTRON DEVICES Vol. 52」, 2005, p. 168940

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

窒化物を含む半導体からなるヘテロ接合電界効果型トランジスタにおいて、ゲート長をできるだけ短く、かつ、ゲート電極の断面積を大きくするために、傘を開いたような形状（庇状形状。張り出して乗り上げた形）の構造とし、かつ、断面積を増大させる傘と半導体の間に誘電膜を挿入した構造とするためには、ゲート電極を形成する前に半導体上に誘電膜を形成し、その後、ゲート電極を形成する領域の誘電膜をドライエッチング法によって除去し、その後に、除去した領域を覆うようにゲート電極を堆積する必要がある。

**【0006】**

50

しかしながら、このような方法をとった場合、ドライエッチング処理の際に半導体層にダメージが形成され、ゲートリーク電流や電流コラプラス特性が劣化するという問題があった。

#### 【0007】

または、ゲート電極を形成した後に誘電膜を形成すると、傘と半導体の間の領域に誘電膜を挿入することが困難となるという問題があった。

#### 【0008】

また、矩形のゲート電極を形成した後に誘電膜を形成し、さらにゲート電極直上の誘電膜を除去した後にゲート電極を覆うように再度、電極を形成すれば、半導体にドライエッチング処理のダメージを与えることは避けられる。しかしこの場合には、ゲート電極よりも高い解像度でゲート電極上にリソグラフィを行う必要があり、その分だけゲート電極が長くなってしまい、高い周波数特性が得られないという問題があった。10

#### 【0009】

本発明は、上記のような問題を解決するためになされたものであり、ヘテロ接合を有する半導体装置において、ゲート抵抗を低減しつつ高周波特性を実現するゲート電極を容易に形成できる半導体装置の製造方法を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0010】

本発明の一態様に関する半導体装置の製造方法は、AlGaN層を含むヘテロ接合半導体装置の製造方法であって、(a) AlGaN層上のゲート電極が配置される領域に、金属から成るダミー電極を形成する工程と、(b) 異方性のある装置を用いて、前記ダミー電極側面を露出させつつ、前記AlGaN層上に誘電膜を堆積させる工程と、(c) 前記ダミー電極をウェットエッチング処理によって除去することにより、前記誘電膜に開口を形成する工程と、(d) 前記開口内からその周辺の前記誘電膜上に延在する前記ゲート電極を形成する工程とを備えることを特徴とする。20

#### 【発明の効果】

#### 【0011】

本発明の上記態様によれば、AlGaN層を含むヘテロ接合半導体装置の製造方法であって、(a) AlGaN層上のゲート電極が配置される領域に、金属から成るダミー電極を形成する工程と、(b) 異方性のある装置を用いて、前記ダミー電極側面を露出させつつ、前記AlGaN層上に誘電膜を堆積させる工程と、(c) 前記ダミー電極をウェットエッチング処理によって除去することにより、前記誘電膜に開口を形成する工程と、(d) 前記開口内からその周辺の前記誘電膜上に延在する前記ゲート電極を形成する工程とを備えることにより、ヘテロ接合半導体装置において、ゲート抵抗を低減しつつ高周波特性を実現するゲート電極を容易に形成できる。30

#### 【図面の簡単な説明】

#### 【0012】

【図1】本発明の実施形態に関する半導体装置の構造を示す図である。

【図2】本発明の実施形態に関する半導体装置の製造工程を示す図である。40

【図3】本発明の実施形態に関する半導体装置の製造工程を示す図である。

【図4】本発明の実施形態に関する半導体装置の製造工程を示す図である。

【図5】本発明の実施形態に関する半導体装置の製造工程を示す図である。

【図6】本発明の実施形態に関する半導体装置の製造工程を示す図である。

【図7】本発明の実施形態に関する半導体装置の製造工程を示す図である。

【図8】本発明の実施形態に関する半導体装置の製造工程を示す図である。

【図9】本発明の実施形態に関する半導体装置の製造工程を示す図である。

【図10】本発明の実施形態に関する半導体装置の製造工程を示す図である。

#### 【発明を実施するための形態】

#### 【0013】

以下、添付の図面を参照しながら、本発明の実施形態について説明する。

**【0014】**

<実施形態>

<構成>

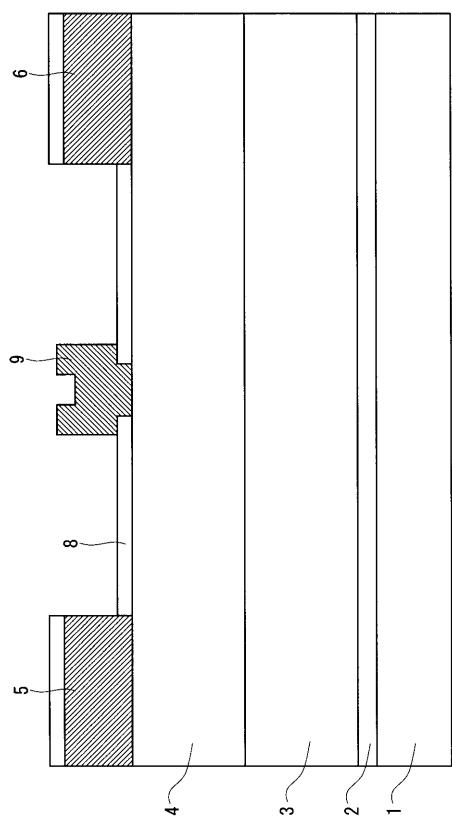

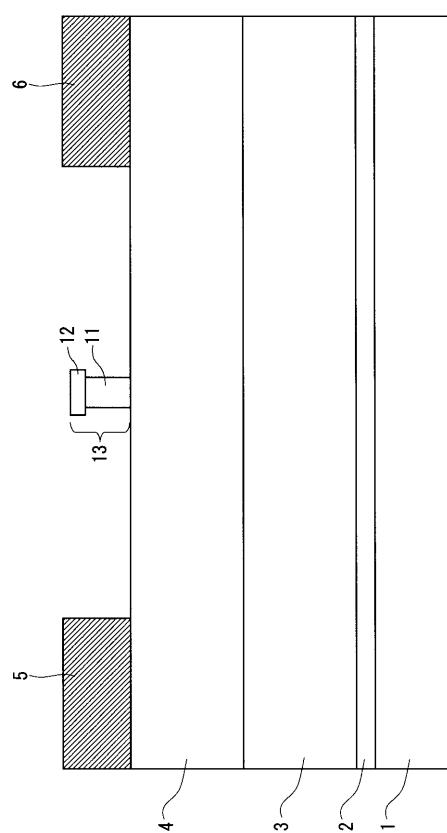

図1は、本発明の実施形態に関するヘテロ接合を有する半導体装置の構造を示す図である。本実施形態では特に、窒化物半導体からなるヘテロ接合電界効果型トランジスタの構造が示されている。

**【0015】**

図1に示されるようにヘテロ接合電界効果型トランジスタは、最下層に形成された窒化物半導体からなる基板1と、基板1上に形成されたバッファ層2と、バッファ層2上に形成された窒化物半導体からなるチャネル層3と、チャネル層3上に形成された、チャネル層3とヘテロ接合を形成する窒化物半導体からなるバリア層4と、バリア層4上に部分的に形成されたソース電極5と、バリア層4上に部分的に形成されたドレイン電極6と、ソース電極5、ドレイン電極6、バリア層4を覆って形成されたSiN<sub>x</sub>からなる誘電膜(表面保護膜)8と、誘電膜8が形成されていないバリア層4上に形成されたゲート電極9とを備える。

**【0016】**

このような構造とすることによって、ゲート電極9は半導体層(バリア層4)と接する実質的ゲート長を短くした状態で、断面積が大きくなるようにゲート電極9上部を傘を開いたような形状(底状形状。張り出して乗り上げた形)にできる。

**【0017】**

さらに、ゲート電極9の増大させた上部の金属部と半導体層(バリア層4)の間に誘電膜8が挿入された構造が可能となり、ゲートリーク電流や電流コラプスを抑制できる。

**【0018】**

なお、窒化物半導体層構造は、必ずしも上記のバッファ層2、チャネル層3、バリア層4の3層から構成される必要はなく、トランジスタとして動作すれば、窒化物半導体、特にAlGaNからなる層が1層でも形成されればよい。

**【0019】**

また、誘電膜8は、必ずしもSiN<sub>x</sub>である必要はなく、誘電膜によってドレイン側のゲート電極9端にかかる電界を緩和できるものであればよい。例えば、SiO<sub>x</sub>、SiO<sub>x</sub>N<sub>y</sub>、Al<sub>x</sub>N<sub>y</sub>、AlO<sub>x</sub>N<sub>y</sub>、SiN<sub>y</sub>、HfO<sub>x</sub>N<sub>y</sub>等でもよい。

**【0020】**

なお、以上では、トランジスタとして動作する必要最小限の要素しか記載していないが、最終的には、配線、バイアホール等の形成された構造においてデバイスとして用いられる。

**【0021】**

<製造方法>

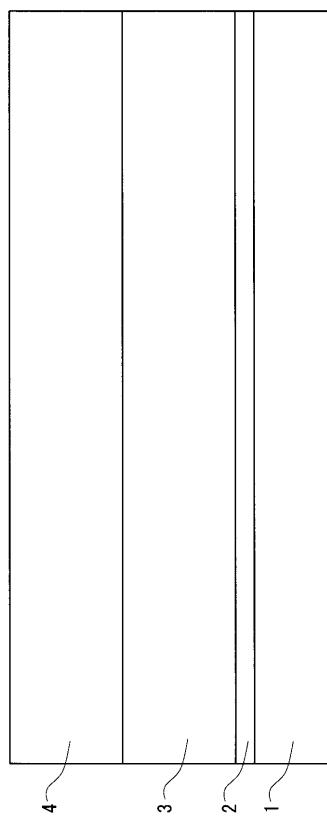

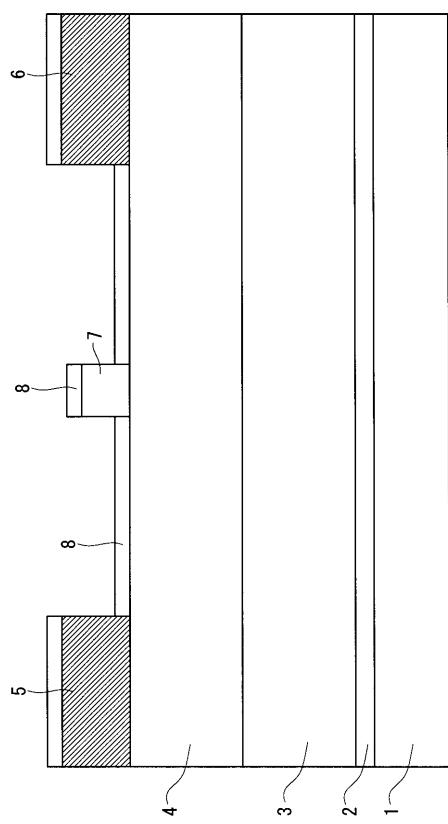

図2～図10に、本発明に関する窒化物半導体からなるヘテロ接合電界効果型トランジスタの製造工程の一例を示す。なお図2～図10は、本発明の実施形態に関する半導体装置の製造工程を示す図である。

**【0022】**

まず図2に示されるように、基板1上にMOCVD法(Metal Organic Chemical Vapor Deposition: 有機金属気相成長法)、MBE法(Molecular Beam Epitaxy: 分子線エピタキシー法)等のエピタキシャル成長法を適用することで、バッファ層2、チャネル層3、バリア層4をそれぞれ下から順にエピタキシャル成長させる。

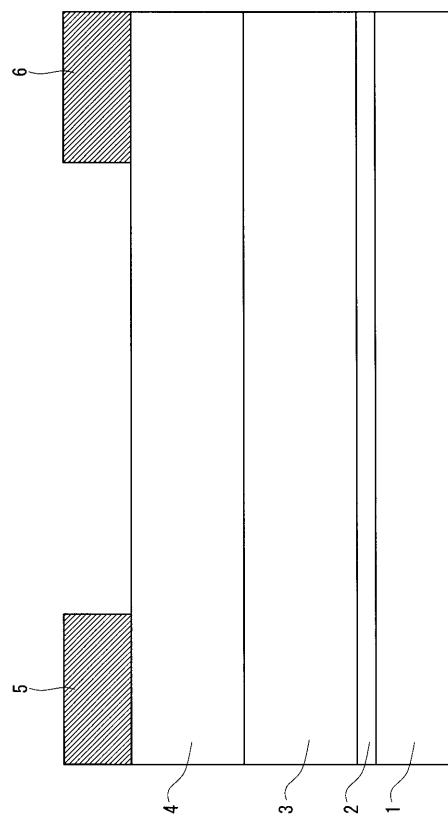

**【0023】**

次に図3に示されるように、例えばTi、Al、Nb、Hf、Zr、Sr、Ni、Ta、Au、Mo、W等の金属、もしくは、これらから構成される多層膜を蒸着法やスパッタ法を用いてリフトオフ法等により堆積した後、RTA(Rapid Thermal A

10

20

30

40

50

n n e a l ) 法等を用いて合金化してオーミック特性となるソース電極 5 およびドレイン電極 6 を形成する。

#### 【 0 0 2 4 】

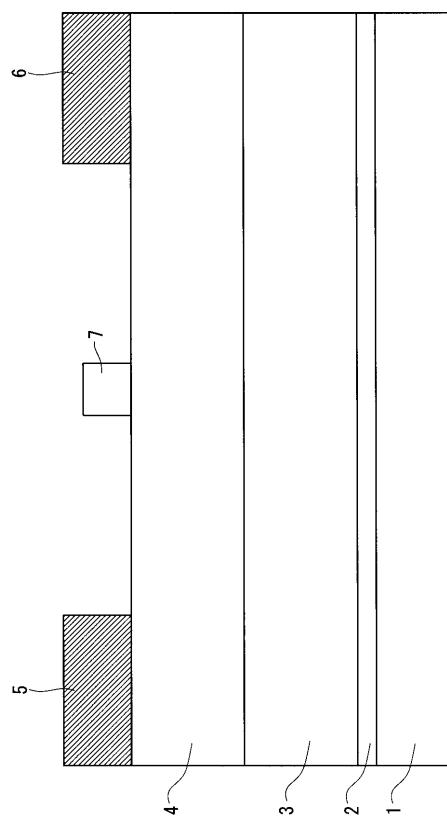

次に図 4 に示されるように、例えば Nb、Ta、Ti、Zr 等の HF に溶けやすい金属、例えば Al、Cr、Fe、Ni 等の HCl に溶けやすい金属、例えば Ag、Hg、Se、Zn 等の HNO<sub>3</sub> に溶けやすい金属、例えば Be、As、Mo、Nb、Re、Sb 等の H<sub>2</sub>SO<sub>4</sub> に溶けやすい金属、例えば Au、Mo、Pd、Pt、W 等の王水 (HNO<sub>3</sub> : HCl = 1 : 3) に溶けやすい金属を、蒸着法やスパッタ法により堆積し、リフトオフ法等によりダミー電極 7 (ゲート部分に相当するダミー材料) を形成する。ダミー電極 7 は、後のゲート電極 9 と半導体層 (バリア層 4) 表面との接地面に対応するため、ゲート長が極力短くなるように (接地面が狭くなるように) 形成する。<sup>10</sup> ダミー電極 7 の材料としては、上記のように、酸等に溶けやすい金属が望ましい。後述する除去工程で誘電膜よりも除去比率が高くなるためである。また例えば、半導体との密着性が悪い金属が挙げられる。これも、後述する除去工程で除去しやすくするためである。なお、本実施形態では、ダミー電極 7 に用いられる材料は金属であるが、後述するダミー材料の除去工程において除去されうる材料であればよく、金属に限られるものではない。

#### 【 0 0 2 5 】

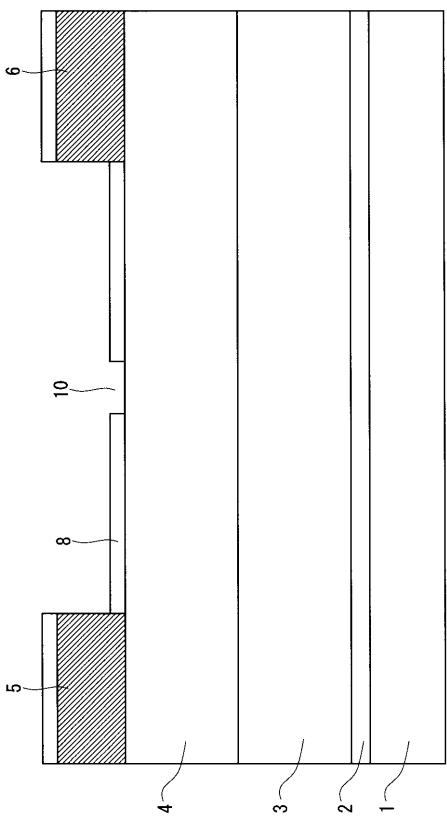

次に図 5 に示されるように、ダミー電極 7 を除去する際、酸の溶液がダミー電極 7 をエッチング処理しやすくするために誘電膜 8 をダミー電極 7 側面に堆積させることのない、例えば Cat - CVD (Catalytic Chemical Vapor Deposition : 触媒化学気相成長法) 法、ECR (Electron Cyclotron Resonance : 電子サイクロトロン共鳴) スパッタ法等の異方性のある手法を用いて、例えば SiN<sub>x</sub>、SiO<sub>x</sub>、SiO<sub>x</sub>N<sub>y</sub> 等からなる誘電膜 8 を半導体層 (バリア層 4) 表面の垂直な方向のみに堆積する。ただし、誘電膜 8 を堆積させる手法は上記の場合に限られるわけではなく、例えば異方性のある他の手法によって堆積させられてもよい。またこの際、ダミー電極 7 の一部側面を確実に露出させるため、ダミー電極 7 に比べ誘電膜 8 の厚さを薄く堆積させる。<sup>20</sup>

#### 【 0 0 2 6 】

次に図 6 に示されるように、例えば HCl、HNO<sub>3</sub>、H<sub>2</sub>SO<sub>4</sub>、HF、王水 (HNO<sub>3</sub> : HCl = 1 : 3) によるウェットエッチング処理等で半導体層 (バリア層 4) 表面や誘電膜 8 にダメージを与えることのないように、ダミー電極 7 を除去する。このようにして、ダミー電極 7 が除去された箇所には、誘電膜 8 の開口 10 が形成される。<sup>30</sup>

#### 【 0 0 2 7 】

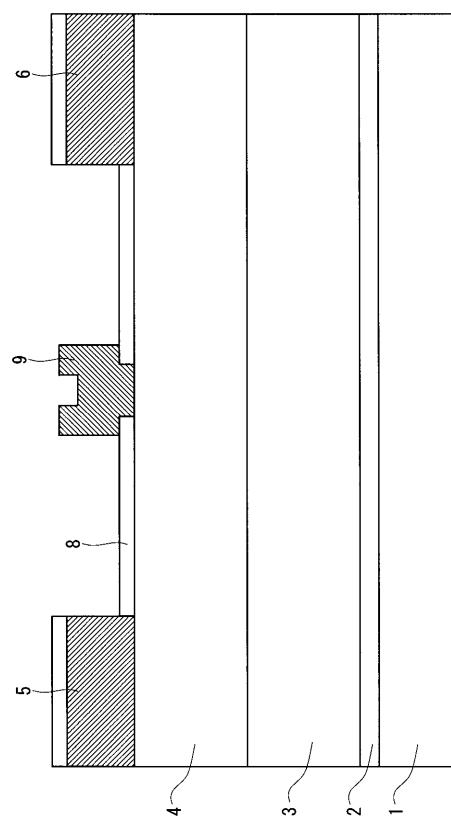

次に図 7 に示されるように、例えば Ti、Al、Nb、Hf、Zr、Sr、Ni、Ta、Au、Mo、W、Pt 等の金属、もしくは、これらから構成される多層膜を、蒸着法やスパッタ法を用いてリフトオフ法等により堆積して、ショットキー特性となるゲート電極 9 を形成する。

#### 【 0 0 2 8 】

この際、ゲート電極 9 の断面積を大きくするために、ダミー電極 7 の除去時に開いた開口 10 よりもゲート長の広い、すなわち、開口 10 内からその周辺の誘電膜 8 上に延在するようにゲート電極 9 を形成することで、ゲート長は短く、かつ、ゲート断面積が大きいゲート電極 9 が形成できる。よって、低抵抗、かつ、電界緩和型の傘を開いたような形状 (底状形状。張り出して乗り上げた形) のゲート構造が形成できる。<sup>40</sup>

#### 【 0 0 2 9 】

以上の方法により、ゲートリーク電流、電流コラプスを抑制した特性を持ち、図 1 に示された構造を持つヘテロ接合電界効果型トランジスタが作製できる。以上では、トランジスタとして動作する必要最小限の要素しか記載していないが、最終的には配線、バイアホール等の形成プロセスを経て、デバイスとして用いられる。

#### 【 0 0 3 0 】

< 変形例 1 >

上記の実施形態では、ウェットエッティング処理によってダミー電極7の除去を行っていたが、超音波洗浄処理によってダミー電極7の除去を行ってもよい。

#### 【0031】

図4に示された工程において、例えば応力が異なる金属膜を複数堆積した構造（例えばNi/Pt/Au等の層構造）等、誘電膜8よりも半導体層との密着性の低い金属を、蒸着法やスパッタ法により堆積することで、その後、図6に示された工程において、例えば超音波洗浄処理等の、従来のドライエッティング処理に比べ、半導体層（バリア層4）表面や誘電膜8に対して低ダメージの処理を行うことによって、十分にダミー電極7の除去を行うことができる。

#### 【0032】

以上の方針により、半導体層（バリア層4）にダメージを与えることなく、ヘテロ接合電界効果型トランジスタが作製することができる。

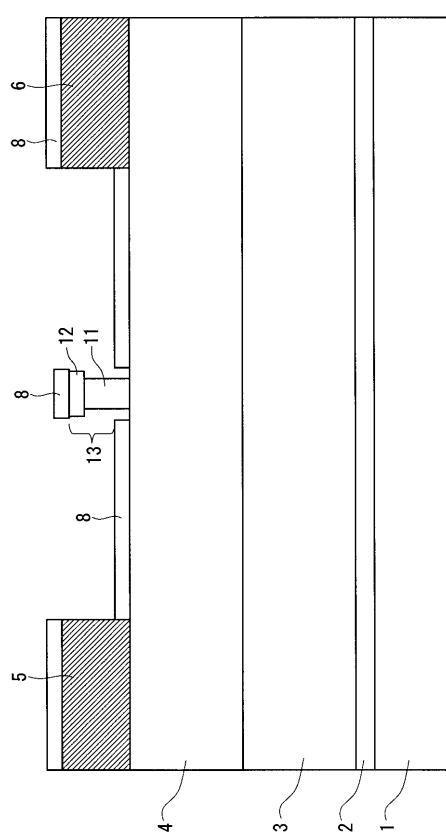

#### 【0033】

##### <変形例2>

上記の実施形態では、ダミー電極を1層の金属層で形成していたが、ダミー電極側面の少なくとも一部を露出させ、後のウェットエッティングでダミー電極除去をしやすくするために、ダミー電極に2層以上の金属層を用いてT型ゲート形状に形成してもよい。

#### 【0034】

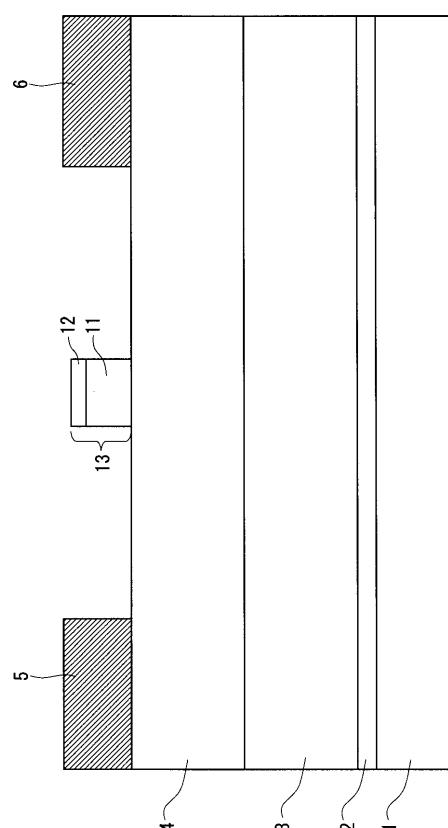

図8に示されるように、例えばダミー電極11とダミー電極12とからなる、2層以上の金属層を用いたダミー電極13を形成してもよい。

#### 【0035】

これら金属層の材料には、例えばNb、Ta、Ti、Zr等のHFに溶けやすい金属、例えばAl、Cr、Fe、Ni等のHClに溶けやすい金属、例えばAg、Hg、Se、Zn等のHNO<sub>3</sub>に溶けやすい金属、例えばBe、As、Mo、Nb、Re、Sb等のH<sub>2</sub>SO<sub>4</sub>に溶けやすい金属、例えばAu、Mo、Pd、Pt、W等の王水（HNO<sub>3</sub> : HCl = 1 : 3）に溶けやすい金属を用いることができる。そしてこれらの材料を蒸着法やスパッタ法により堆積し、さらにリフトオフ法等を用いることによりダミー電極11およびダミー電極12からなるダミー電極13（ゲート部分に相当するダミー材料）を形成する。

#### 【0036】

この際、ダミー電極11はダミー電極12に比べ、例えば上記酸に対するエッチグレートが早い材料を使用することが望ましい。

#### 【0037】

その後、図9で示されるように、形成されたダミー電極13を酸によりエッティングすることで、1層目と2層目のエッティングレートの違いからT型の形状（バリア層4に接する層よりもその上に形成された層の方が広い幅を持つ形状）を持つダミー電極13が形成される。

#### 【0038】

このような形状となることにより、さらに図10で示されるように、ダミー電極13のような構造を形成することで、後の誘電膜8堆積時にダミー電極13の側面が少なくとも一部露出し、ダミー電極13を除去しやすくなる。

#### 【0039】

また、ダミー電極13が形成される位置は、後のゲート電極9と半導体層（バリア層4）表面との接地面に対応する位置であるため、ゲート長が極力短くなるように形成することが望ましい。

#### 【0040】

なお、本実施形態では、ダミー電極11およびダミー電極12に用いられる材料は金属であるが、ダミー材料の除去工程において除去されうる材料であればよく、金属に限られるものではない。

#### 【0041】

10

20

30

40

50

## &lt;効果&gt;

本発明に関する実施形態によれば、半導体装置の製造方法は、ヘテロ接合半導体装置の製造方法であって、(a)半導体層であるバリア層4上のゲート電極9が配置される領域に、ダミー材料からなるダミー電極7を形成する工程と、(b)バリア層4上に、ダミー電極7を覆って、誘電膜8を堆積させる工程と、(c)ダミー電極7を除去することにより、誘電膜8に開口10を形成する工程と、(d)開口10内からその周辺の誘電膜8上面に延在するゲート電極9を形成する工程とを備える。

## 【0042】

このような構成によれば、ヘテロ接合半導体装置において、ゲート抵抗を低減しつつ高周波特性を実現するゲート電極9を容易に形成できる。 10

## 【0043】

ゲート電極9は、端部において誘電膜8が潜り込んだ構造(底状形状。張り出して乗り上げた形)となるため、実質的なゲート長を短くした状態でゲート電極の断面積を大きくして、ゲート抵抗を低減し、電流コラプスを抑制することができる。

## 【0044】

また、本発明に関する実施形態によれば、(c)ダミー電極7を除去することにより、誘電膜8に開口10を形成する工程が、ウェットエッチング処理によってダミー材料としてのダミー電極7を除去する工程である。

## 【0045】

このような構成によれば、半導体層との密着性が低い材料や酸に溶けやすい材料で形成されたダミー材料が、半導体層であるバリア層4に与えるダメージを抑制しつつ除去される。よって、ゲートリーアク電流と電流コラプスを抑制することができる。 20

## 【0046】

また、本発明に関する実施形態によれば、(c)ダミー電極7を除去することにより、誘電膜8に開口10を形成する工程が、超音波洗浄処理によってダミー材料としてのダミー電極7を除去する工程である。

## 【0047】

このような構成によれば、半導体層との密着性が低い材料や酸に溶けやすい材料で形成されたダミー材料が、半導体層であるバリア層4に与えるダメージを抑制しつつ除去される。よって、ゲートリーアク電流と電流コラプスを抑制することができる。 30

## 【0048】

また、本発明に関する実施形態によれば、(a)半導体層であるバリア層4上のゲート電極9が配置される領域に、ダミー材料からなるダミー電極7を形成する工程が、バリア層4上のゲート電極9が配置される領域に、誘電膜8よりもバリア層4との密着性が低い材料からなるダミー電極7を形成する工程である。

## 【0049】

このような構成によれば、超音波洗浄処理やウェットエッチング処理等の半導体層や誘電膜8に対して低ダメージの処理を行うことで十分にダミー電極7を除去することができるため、ゲートリーアク電流と電流コラプスを抑制することができる。

## 【0050】

また、本発明に関する実施形態によれば、(b)バリア層4上に、ダミー電極7を覆って、誘電膜8を堆積させる工程が、(c)ダミー電極7を除去することにより、誘電膜8に開口10を形成する工程においてダミー電極7よりも除去比率が低い誘電膜8を堆積させる工程である。 40

## 【0051】

このような構成によれば、超音波洗浄処理やウェットエッチング処理等の半導体層や誘電膜8に対して低ダメージの処理を行うことで十分にダミー電極7を除去することができるため、ゲートリーアク電流と電流コラプスを抑制することができる。

## 【0052】

また、本発明に関する実施形態によれば、(b)バリア層4上に、ダミー電極7を覆つ 50

て、誘電膜8を堆積させる工程が、Cat-CVD法によって誘電膜8を堆積させる工程である。

**【0053】**

このような構成によれば、異方性のあるCat-CVD法等で誘電膜8を堆積させることにより、ダミー電極7の露出した側面に堆積する誘電膜8を抑制することができ、後の工程でダミー電極7を除去しやすくすることができる。

**【0054】**

また、本発明に関する実施形態によれば、(b)バリア層4上に、ダミー電極7を覆つて、誘電膜8を堆積させる工程が、ECRスパッタ法によって誘電膜8を堆積させる工程である。

10

**【0055】**

このような構成によれば、異方性のあるECRスパッタ法等で誘電膜8を堆積させることにより、ダミー電極7の露出した側面に堆積する誘電膜8を抑制することができ、後の工程でダミー電極7を除去しやすくすることができる。

**【0056】**

本発明の実施形態では、各構成要素の材質、材料、実施の条件等についても記載しているが、これらは例示であって記載したものに限られるものではない。

**【0057】**

ここで、実際に実験を行った際の条件を記しておく。本実施形態で示されたダミー電極7は、360nmのAlを蒸着して形成した。また、表面保護膜8として、cat-CVD装置を用いてSiNを100nm堆積した。その後、塩酸を用いてウェットエッティングを行うことで、本実施形態で示されるようにダミー電極7の除去を行うことができた。

20

**【0058】**

なお本発明は、その発明の範囲内において、本実施形態における任意の構成要素の変形もしくは省略が可能である。

**【0059】**

また、本発明に関する実施形態によれば、(a)半導体層であるバリア層4上のゲート電極9が配置される領域に、ダミー材料からなるダミー電極7を形成する工程が、T型の形状であるダミー電極13を形成する工程である。

30

**【0060】**

このような構成によれば、ダミー電極13を形成するダミー電極11とダミー電極12との間の、酸またはアルカリ溶液に対する溶けやすさ(エッティングレート)の違いを利用してT型の形状のダミー電極13を形成することにより、誘電膜8を堆積させる際、ダミー電極13の一部側面を露出させることができ、後の工程でダミー電極13を除去しやすくすることができる。

**【0061】**

また、本発明に関する実施形態によれば、(b)バリア層4上に、ダミー電極13を覆つて、誘電膜8を堆積させる工程が、AlGaN層(バリア層4)と接するダミー電極11の厚さよりも薄く誘電膜8を堆積させる工程である。

40

**【0062】**

このような構成によれば、ダミー電極11に比べ膜厚の薄い誘電膜8を堆積させることで、ダミー電極13の一部側面を露出させることができ、後の工程でダミー電極13を除去しやすくすることができる。

**【0063】**

この際、誘電膜8は金属層より薄ければよいが、誘電膜8の厚さがダミー電極13の高さの半分以下だと、ダミー電極13の側面が確実に露出するため、より望ましい。

**【符号の説明】**

**【0064】**

1 基板、2 バッファ層、3 チャネル層、4 バリア層、5 ソース電極、6 ド

50

レイン電極、7，11，12，13 ダミー電極、8 誘電膜、9 ゲート電極、10

開口。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 29/423 (2006.01)

(72)発明者 鈴木 洋介

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 今井 章文

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 吹田 宗義

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

(72)発明者 柳生 栄治

東京都千代田区丸の内二丁目 7番 3号 三菱電機株式会社内

審査官 綿引 隆

(56)参考文献 特開昭63-129632 (JP, A)

特開平05-152294 (JP, A)

特開2011-233612 (JP, A)

特開平06-097160 (JP, A)

特開昭60-039875 (JP, A)

特開2010-205837 (JP, A)

特開2004-273752 (JP, A)

特開2004-273655 (JP, A)

特開平01-194475 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/28 - 288

H 01 L 21/335 - 338

H 01 L 29/423

H 01 L 29/778

H 01 L 29/78

H 01 L 29/812