(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6125211号

(P6125211)

(45) 発行日 平成29年5月10日(2017.5.10)

(24) 登録日 平成29年4月14日(2017.4.14)

|               |           |        |       |         |

|---------------|-----------|--------|-------|---------|

| (51) Int.Cl.  | F 1       |        |       |         |

| HO 1 L 21/336 | (2006.01) | HO 1 L | 29/78 | 6 2 7 Z |

| HO 1 L 29/786 | (2006.01) | HO 1 L | 29/78 | 6 1 8 B |

| GO 2 F 1/1368 | (2006.01) | HO 1 L | 29/78 | 6 1 7 V |

| GO 9 F 9/30   | (2006.01) | HO 1 L | 29/78 | 6 2 7 F |

| GO 9 F 9/00   | (2006.01) | HO 1 L | 29/78 | 6 1 7 S |

請求項の数 6 (全 56 頁) 最終頁に続く

|              |                               |           |                                                |

|--------------|-------------------------------|-----------|------------------------------------------------|

| (21) 出願番号    | 特願2012-253870 (P2012-253870)  | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成24年11月20日 (2012.11.20)      | (72) 発明者  | 山出 直人<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号    | 特開2013-140949 (P2013-140949A) | (72) 発明者  | 肥塚 純一<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日     | 平成25年7月18日 (2013.7.18)        | (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査請求日        | 平成27年10月22日 (2015.10.22)      |           |                                                |

| (31) 優先権主張番号 | 特願2011-257793 (P2011-257793)  |           |                                                |

| (32) 優先日     | 平成23年11月25日 (2011.11.25)      |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                                |

| (31) 優先権主張番号 | 特願2011-267307 (P2011-267307)  |           |                                                |

| (32) 優先日     | 平成23年12月6日 (2011.12.6)        |           |                                                |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                                |

審査官 岩本 勉

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート電極層を形成し、

前記ゲート電極層上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上の前記ゲート電極層と重畠する領域に酸化物半導体膜を形成し、

前記酸化物半導体膜上に前記酸化物半導体膜に接して絶縁膜を形成し、

前記絶縁膜に第2の熱処理を行って、前記絶縁膜中の水又は水素を除去し、

前記水又は水素が除去された絶縁膜に第2の酸素プラズマドープ処理を行って、前記絶縁膜に酸素を供給することを特徴とする半導体装置の作製方法。

## 【請求項 2】

ゲート電極層を形成し、

前記ゲート電極層上にゲート絶縁膜を形成し、

前記ゲート絶縁膜上の前記ゲート電極層と重畠する領域に酸化物半導体膜を形成し、

前記酸化物半導体膜上に前記酸化物半導体膜に接して絶縁膜を形成し、

前記絶縁膜に第2の熱処理を行って、前記絶縁膜中の水又は水素を除去し、

前記水又は水素が除去された絶縁膜に第2の酸素ドープ処理を行って、前記絶縁膜に酸素を供給することを特徴とする半導体装置の作製方法。

## 【請求項 3】

ゲート電極層を形成し、

前記ゲート電極層上にゲート絶縁膜を形成し、

10

20

前記ゲート絶縁膜に第1の熱処理を行って、前記ゲート絶縁膜中の水又は水素を除去し、

前記水又は水素が除去されたゲート絶縁膜に第1の酸素ドープ処理を行って、前記ゲート絶縁膜に酸素を供給し、

前記ゲート絶縁膜上の前記ゲート電極層と重畳する領域に酸化物半導体膜を形成し、

前記酸化物半導体膜上に前記酸化物半導体膜に接して絶縁膜を形成し、

前記絶縁膜に第2の熱処理を行って、前記絶縁膜中の水又は水素を除去し、

前記水又は水素が除去された絶縁膜に第2の酸素ドープ処理を行って、前記絶縁膜に酸素を供給することを特徴とする半導体装置の作製方法。

## 【請求項4】

10

請求項3において、前記第1の熱処理前に、前記ゲート絶縁膜に酸素ドープ処理を行うことを特徴とする半導体装置の作製方法。

## 【請求項5】

請求項2乃至請求項4のいずれか一項において、

前記第2の酸素ドープ処理後に、前記ゲート絶縁膜、前記酸化物半導体膜、及び前記絶縁膜を覆う酸化アルミニウム膜を形成し、

前記酸化アルミニウム膜形成後に、熱処理を行うことを特徴とする半導体装置の作製方法。

## 【請求項6】

20

請求項1乃至請求項5のいずれか一項において、前記第2の熱処理前に、前記絶縁膜に酸素ドープ処理を行うことを特徴とする半導体装置の作製方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

半導体装置及び半導体装置の作製方法に関する。

## 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

## 【背景技術】

## 【0003】

30

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタ（薄膜トランジスタ（TFT）ともいう）を構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（表示装置）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

## 【0004】

例えば、基板上にインジウム（In）、ガリウム（Ga）、及び亜鉛（Zn）を含むアモルファス酸化物（In-Ga-Zn-O系アモルファス酸化物）からなる半導体層を用いたトランジスタが開示されている（特許文献1参照）。

## 【先行技術文献】

40

## 【特許文献】

## 【0005】

## 【特許文献1】特開2011-181801号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0006】

ところで、酸化物半導体を用いたトランジスタを有する半導体装置において、高信頼性の達成は、製品化にむけて重要事項である。

## 【0007】

特に、半導体装置の電気特性の変動や低下は信頼性の低下を招く要因である。

50

**【 0 0 0 8 】**

このような問題に鑑み、酸化物半導体を用いたトランジスタを有する信頼性の高い半導体装置を提供することを課題の一とする。

**【課題を解決するための手段】****【 0 0 0 9 】**

酸化物半導体膜を有するボトムゲート構造のトランジスタを有する半導体装置の作製工程において、酸化物半導体膜と接する絶縁膜に、熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行う。

**【 0 0 1 0 】**

酸化物半導体膜と接する絶縁膜は、酸化物半導体膜下に設けられるゲート絶縁膜と、酸化物半導体膜上に設けられる保護絶縁膜（及び層間絶縁膜）として機能する絶縁膜である。本明細書で開示する発明において、ゲート絶縁膜、及び／又は絶縁膜に熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行う。

10

**【 0 0 1 1 】**

熱処理による脱水化又は脱水素化処理を行う前の絶縁膜にも、酸素ドープ処理を行っておいてもよい。絶縁膜に酸素ドープ処理と熱処理とを複数回繰り返し行ってもよい。絶縁膜に対して、熱処理の前に酸素ドープ処理を行うと、絶縁膜の脱水化又は脱水素化処理を効果的に行うことができる。

**【 0 0 1 2 】**

脱水化又は脱水素化処理と酸素ドープ処理を行ったゲート絶縁膜及び／又は絶縁膜と、酸化物半導体膜とを接した状態で、熱処理を行うことが好ましい。該熱処理により、ゲート絶縁膜及び／又は絶縁膜から酸化物半導体膜へ酸素を供給することができる。酸化物半導体膜へ酸素を供給することにより、膜中の酸素欠損を補填することができる。

20

**【 0 0 1 3 】**

本明細書で開示する発明の構成の一形態は、ゲート電極層を形成し、ゲート電極層上にゲート絶縁膜を形成し、ゲート絶縁膜に熱処理を行って、ゲート絶縁膜中の水又は水素を除去し、水又は水素が除去されたゲート絶縁膜に酸素ドープ処理を行って、ゲート絶縁膜に酸素を供給し、ゲート絶縁膜上のゲート電極層と重畳する領域に酸化物半導体膜を形成し、酸化物半導体膜と電気的に接続するソース電極層及びドレイン電極層を形成する半導体装置の作製方法である。

30

**【 0 0 1 4 】**

ゲート絶縁膜に熱処理による脱水化又は脱水素化処理を行う前に、ゲート絶縁膜に酸素ドープ処理を行ってもよい。

**【 0 0 1 5 】**

また、熱処理による脱水化又は脱水素化処理及び酸素ドープ処理を行ったゲート絶縁膜上に酸化物半導体膜を形成した後、該ゲート絶縁膜及び酸化物半導体膜に熱処理を行うことが好ましい。

**【 0 0 1 6 】**

本明細書で開示する発明の構成の他の一形態は、ゲート電極層を形成し、ゲート電極層上にゲート絶縁膜を形成し、ゲート絶縁膜上のゲート電極層と重畳する領域に酸化物半導体膜を形成し、酸化物半導体膜と電気的に接続するソース電極層及びドレイン電極層を形成し、酸化物半導体膜、ソース電極層及びドレイン電極層上に酸化物半導体膜に接して絶縁膜を形成し、絶縁膜に熱処理を行って、絶縁膜中の水又は水素を除去し、水又は水素が除去された絶縁膜に酸素ドープ処理を行って、絶縁膜に酸素を供給する半導体装置の作製方法である。

40

**【 0 0 1 7 】**

絶縁膜に熱処理による脱水化又は脱水素化処理を行う前に、絶縁膜に酸素ドープ処理を行ってもよい。

**【 0 0 1 8 】**

本明細書で開示する発明の構成の他の一形態は、ゲート電極層を形成し、ゲート電極層上

50

にゲート絶縁膜を形成し、ゲート絶縁膜に第1の熱処理を行って、ゲート絶縁膜中の水又は水素を除去し、水又は水素が除去されたゲート絶縁膜に第1の酸素ドープ処理を行って、ゲート絶縁膜に酸素を供給し、ゲート絶縁膜上のゲート電極層と重畳する領域に酸化物半導体膜を形成し、酸化物半導体膜と電気的に接続するソース電極層及びドレイン電極層を形成し、酸化物半導体膜、ソース電極層及びドレイン電極層上に酸化物半導体膜に接して絶縁膜を形成し、絶縁膜に第2の熱処理を行って、絶縁膜中の水又は水素を除去し、水又は水素が除去された絶縁膜に第2の酸素ドープ処理を行って、絶縁膜に酸素を供給する半導体装置の作製方法である。

#### 【0019】

上記構成において、ゲート絶縁膜に第1の熱処理による脱水化又は脱水素化処理を行う前に、ゲート絶縁膜に酸素ドープ処理を行ってもよい。絶縁膜に第2の熱処理による脱水化又は脱水素化処理を行う前に、絶縁膜に酸素ドープ処理を行ってもよい。10

#### 【0020】

また、熱処理による脱水化又は脱水素化処理及び酸素ドープ処理を行ったゲート絶縁膜、及び絶縁膜上に緻密性の高い膜、代表的には酸化アルミニウム膜を形成した後、ゲート絶縁膜、酸化物半導体膜、及び絶縁膜に熱処理を行うことが好ましい。酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を通過させない遮断効果（プロック効果）が高い。従って、酸化アルミニウム膜は、作製工程中及び作製後において、変動要因となる水素、水分などの不純物のゲート絶縁膜、酸化物半導体膜、絶縁膜への混入、及び酸素のゲート絶縁膜、酸化物半導体膜、絶縁膜からの放出を防止することができる20。

#### 【0021】

ゲート絶縁膜、又はノード及び絶縁膜は成膜ガスを用いる成膜方法により形成することができる。例えば、化学気相成長（CVD：Chemical Vapor Deposition）法により形成することができる。

#### 【0022】

なお、上記の「酸素ドープ」とは、酸素（少なくとも、酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン（酸素分子イオン）、及びノード又は酸素クラスタイオンのいずれかを含む）をバルクに添加することを言う。なお、当該「バルク」の用語は、酸素を、薄膜表面のみでなく薄膜内部に添加することを明確にする趣旨で用いている。また、「酸素ドープ」には、プラズマ化した酸素をバルクに添加する「酸素プラズマドープ」が含まれる30。

#### 【0023】

酸素ドープ処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素ドープ処理において、希ガスを用いてもよい。

#### 【0024】

本発明の一形態は、トランジスタ若しくはトランジスタを含んで構成される回路を有する半導体装置に関する。例えば、酸化物半導体でチャネル形成領域が形成される、トランジスタ若しくはトランジスタを含んで構成される回路を有する半導体装置に関する。例えば、LSIや、CPUや、電源回路に搭載されるパワーデバイスや、メモリ、サイリスタ、コンバータ、イメージセンサなどを含む半導体集積回路、液晶表示パネルに代表される電気光学装置や発光素子を有する発光表示装置を部品として搭載した電子機器に関する40。

#### 【発明の効果】

#### 【0025】

酸化物半導体を用いたトランジスタを有する信頼性の高い半導体装置を提供する。

#### 【図面の簡単な説明】

#### 【0026】

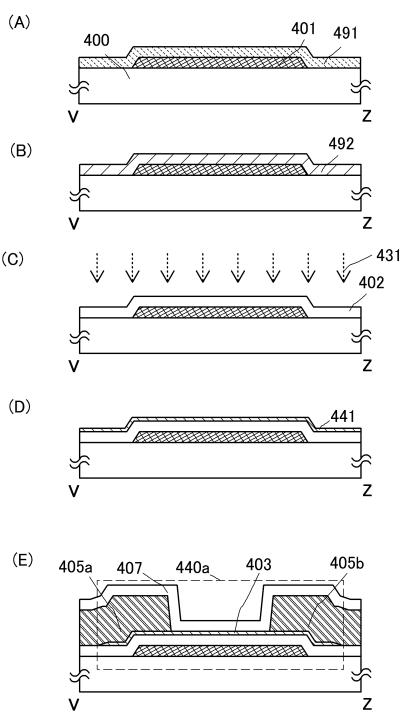

【図1】半導体装置の作製方法の一形態を説明する断面図。

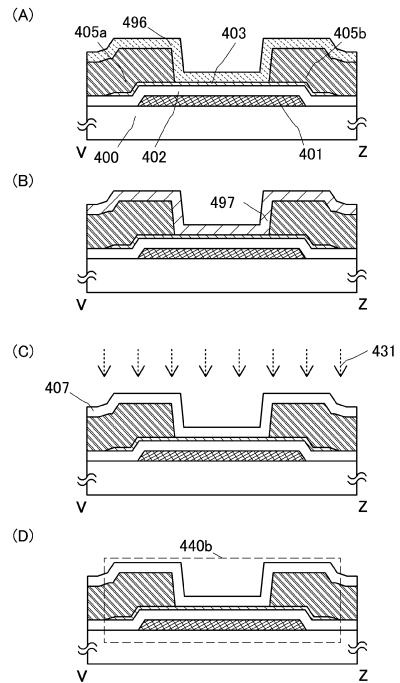

【図2】半導体装置の作製方法の一形態を説明する断面図。

10

20

30

40

50

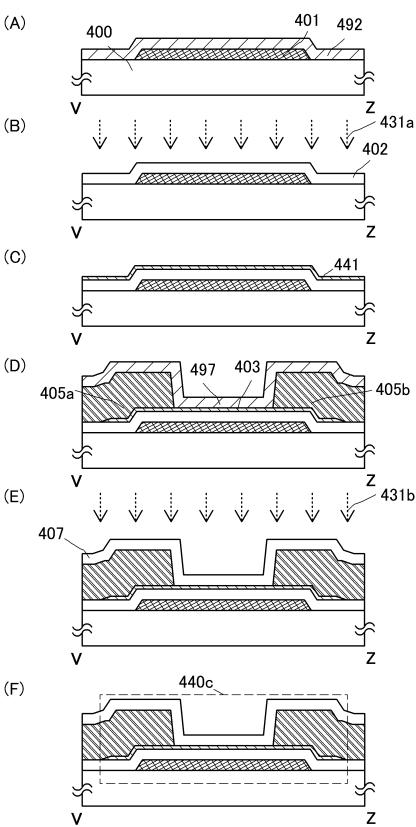

- 【図3】半導体装置の作製方法の一形態を説明する断面図。

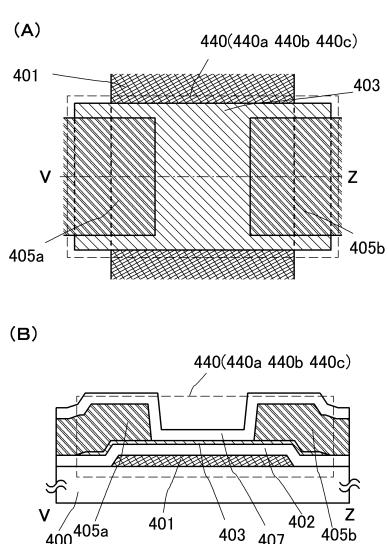

- 【図4】半導体装置の一形態を説明する平面図及び断面図。

- 【図5】半導体装置の一形態を説明する平面図及び断面図。

- 【図6】半導体装置の一形態を説明する平面図及び断面図。

- 【図7】半導体装置の一形態を説明する平面図及び断面図。

- 【図8】半導体装置の一形態を説明する平面図。

- 【図9】半導体装置の一形態を説明する平面図及び断面図。

- 【図10】半導体装置の一態様を示す断面図。

- 【図11】半導体装置の一形態を示す回路図及び断面図。

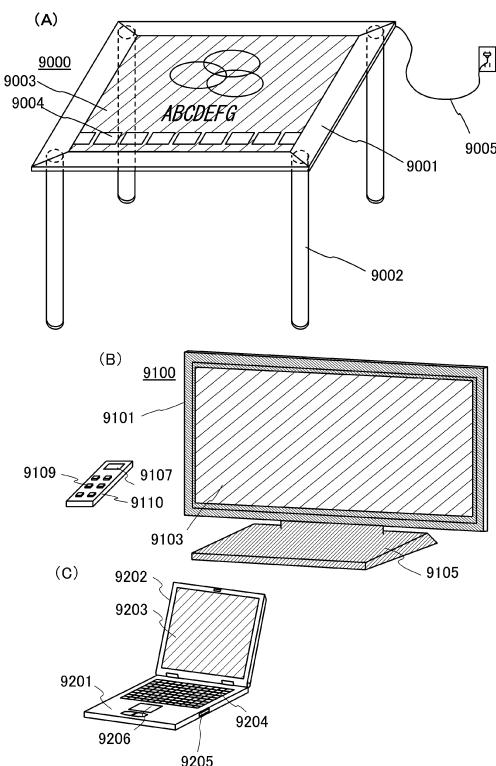

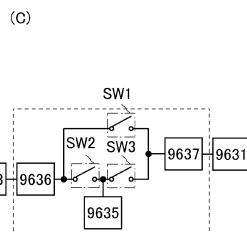

- 【図12】電子機器を示す図。

- 【図13】電子機器を示す図。

- 【図14】C A A C - O S 膜の概念図。

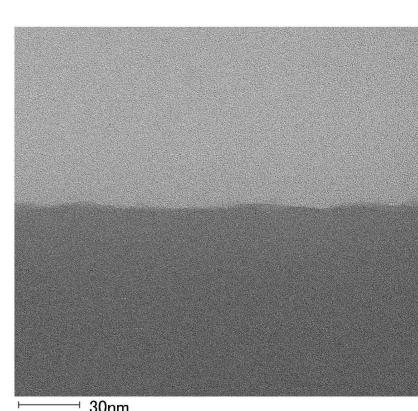

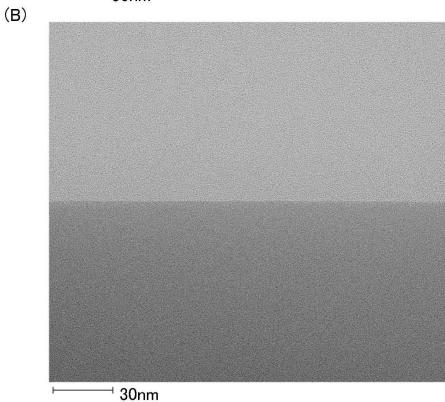

- 【図15】実施例で作製したサンプルAの断面TEM写真。

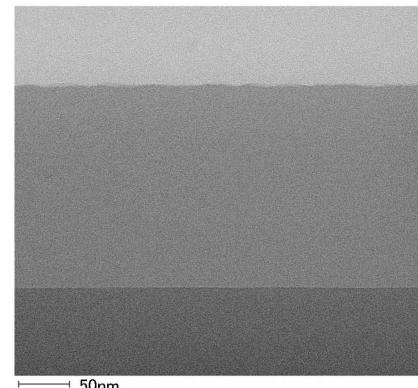

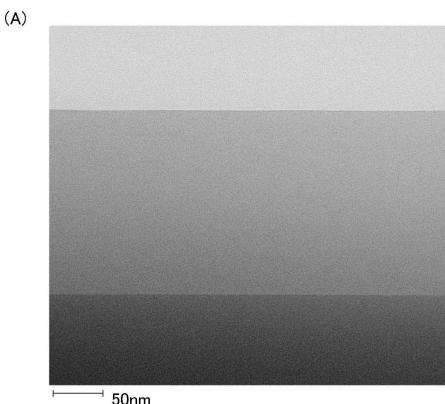

- 【図16】実施例で作製したサンプルBの断面TEM写真。

- 【図17】半導体装置の一態様を説明する断面図。

【発明を実施するための形態】

【0027】

以下では、本明細書に開示する発明の実施の形態について図面を用いて詳細に説明する。ただし、本明細書に開示する発明は以下の説明に限定されず、その形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本明細書に開示する発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、第1、第2として付される序数詞は便宜上用いるものであり、工程順又は積層順を示すものではない。また、本明細書において発明を特定するための事項として固有の名称を示すものではない。

【0028】

(実施の形態1)

本実施の形態では、半導体装置及び半導体装置の作製方法の一形態を、図1を用いて説明する。本実施の形態では、半導体装置の一例として酸化物半導体膜を有するトランジスタを示す。

【0029】

トランジスタはチャネル形成領域が1つ形成されるシングルゲート構造でも、2つ形成されるダブルゲート構造もしくは3つ形成されるトリプルゲート構造であってもよい。また、チャネル形成領域の上下にゲート絶縁膜を介して配置された2つのゲート電極層を有する、デュアルゲート型でもよい。

【0030】

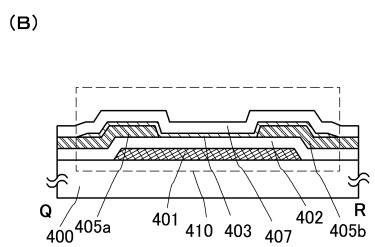

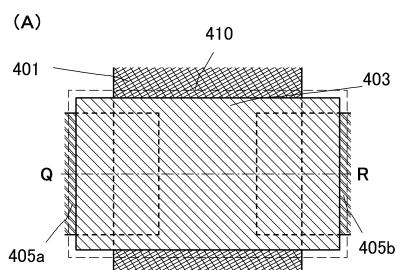

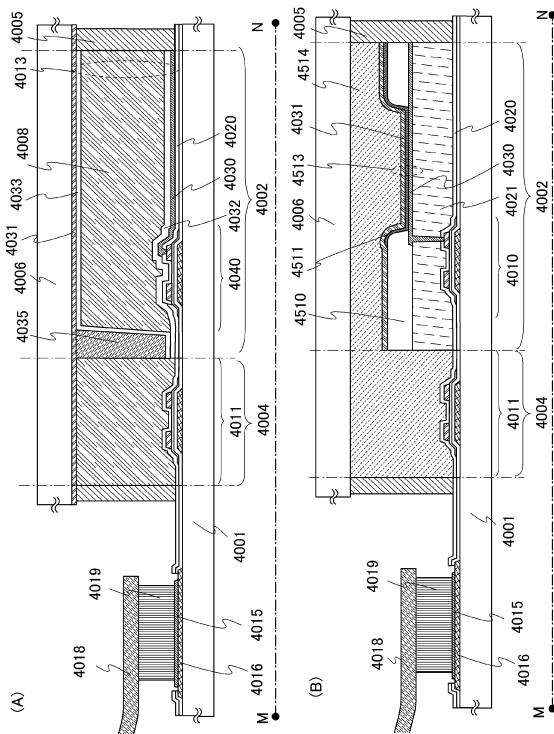

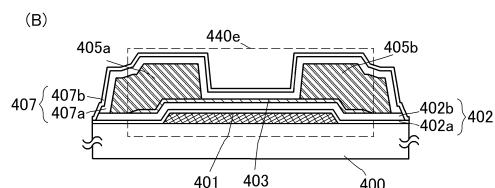

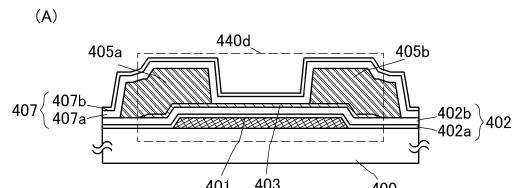

図4に示すトランジスタ440(440a、440b、440c)は、ボトムゲート構造の一つであり逆スタガ型トランジスタともいうトランジスタの一例である。図4(A)は平面図であり、図4(A)中の一点鎖線V-Zで切断した断面が図4(B)に相当する。

【0031】

トランジスタ440(440a、440b、440c)のチャネル長方向の断面図である図4(B)に示すように、トランジスタ440(440a、440b、440c)を含む半導体装置は、基板400上に、ゲート電極層401と、ゲート電極層401上にゲート絶縁膜402、酸化物半導体膜403、ソース電極層405a、及びドレイン電極層405bを有する。また、トランジスタ440を覆う絶縁膜407が設けられている。

【0032】

本明細書に開示するトランジスタ440(440a、440b、440c)は、該作製工程において、酸化物半導体膜403と接する絶縁膜(ゲート絶縁膜402、及び/又は絶縁膜407)に、熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行う。

【0033】

10

20

30

40

50

本実施の形態では、酸化物半導体膜の下層に接して設けられるゲート絶縁膜に熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行い、作製するトランジスタ440aを例として示す。

#### 【0034】

酸化物半導体膜403に用いる酸化物半導体としては、少なくともインジウム(Indium)を含む。特にIndiumと亜鉛(Zinc)を含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Gallium)を有することが好ましい。また、スタビライザーとしてスズ(Silver)を有することが好ましい。また、スタビライザーとしてハフニウム(Hafnium)を有することが好ましい。また、スタビライザーとしてアルミニウム(Aluminum)を有することが好ましい。

また、スタビライザーとしてジルコニウム(Zirconium)を有することが好ましい。

10

#### 【0035】

また、他のスタビライザーとして、ランタノイドである、ランタン(Lanthanum)、セリウム(Cerium)、プラセオジム(Praseodymium)、ネオジム(Neodimium)、サマリウム(Samarium)、ユウロピウム(Yttrium)、ガドリニウム(Gadolinium)、テルビウム(Terbium)、ジスプロシウム(Dysprosium)、ホルミウム(Holmium)、エルビウム(Erbium)、ツリウム(Triplutonium)、イッテルビウム(Ytterbium)、ルテチウム(Lutetium)のいずれか一種あるいは複数種を有してもよい。

#### 【0036】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIndium-Zinc系酸化物、Indium-Magnesium系酸化物、Indium-Gallium系酸化物、三元系金属の酸化物であるIndium-Gallium-Zinc系酸化物(IGZOとも表記する)、Indium-Aluminum-Zinc系酸化物、Indium-Silver-Zinc系酸化物、Indium-Hafnium-Zinc系酸化物、Indium-Lanthanum-Zinc系酸化物、Indium-Cerium-Zinc系酸化物、Indium-Praseodymium-Zinc系酸化物、Indium-Neuropium-Zinc系酸化物、Indium-Samarium-Zinc系酸化物、Indium-Earthium-Zinc系酸化物、Indium-Gadolinium-Zinc系酸化物、Indium-Terbium-Zinc系酸化物、Indium-Dysprosium-Zinc系酸化物、Indium-Holmium-Zinc系酸化物、Indium-Erbium-Zinc系酸化物、Indium-Triplutonium-Zinc系酸化物、Indium-Ytterbium-Zinc系酸化物、Indium-Lutetium-Zinc系酸化物、四元系金属の酸化物であるIndium-Silver-Gallium-Zinc系酸化物、Indium-Hafnium-Gallium-Zinc系酸化物、Indium-Aluminum-Gallium-Zinc系酸化物、Indium-Silver-Aluminum-Zinc系酸化物、Indium-Silver-Hafnium-Zinc系酸化物、Indium-Hafnium-Aluminum-Zinc系酸化物を用いることができる。

20

#### 【0037】

なお、ここで、例えば、Indium-Gallium-Zinc系酸化物とは、IndiumとGalliumとZincを主成分として有する酸化物という意味であり、IndiumとGalliumとZincの比率は問わない。また、IndiumとGalliumとZinc以外の金属元素が入っていてもよい。

#### 【0038】

また、酸化物半導体として、 $IndiumMO_3 (ZnO)_m$ ( $m > 0$ 、且つ、 $m$ は整数でない)で表記される材料を用いてもよい。なお、Mは、Gallium、Ferrous、Manganese及びCobaltから選ばれた一の金属元素又は複数の金属元素を示す。また、酸化物半導体として、 $Indium_2SnO_5 (ZnO)_n$ ( $n > 0$ 、且つ、 $n$ は整数)で表記される材料を用いてもよい。

30

#### 【0039】

例えば、 $Indium : Gallium : Zinc = 1 : 1 : 1$ (=1/3:1/3:1/3)、 $Indium : Gallium : Zinc = 2 : 2 : 1$ (=2/5:2/5:1/5)、あるいは $Indium : Gallium : Zinc = 3 : 1 : 2$ (=1/2:1/6:1/3)の原子数比のIndium-Gallium-Zinc系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、 $Indium : Silver : Zinc = 1 : 1 : 1$ (=1/3:1/3:1/3)、 $Indium : Silver : Zinc = 2 : 1 : 3$ (=1/3:1/6:1/2)あるいは $Indium : Silver : Zinc = 2 : 1 : 5$ (=1/4:1/8:5/8)の原子数比のIndium-Silver-Zinc系酸化物やその組成の近傍の酸化物を用いるとよい。

40

#### 【0040】

しかし、インジウムを含む酸化物半導体は、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要

50

とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【0041】

例えば、In - Sn - Zn系酸化物では比較的容易に高い移動度が得られる。しかしながら、In - Ga - Zn系酸化物でも、バルク内欠陥密度を低くすることにより移動度を上げることができる。

#### 【0042】

なお、例えば、In、Ga、Znの原子数比が $In : Ga : Zn = a : b : c$  ( $a + b + c = 1$ ) である酸化物の組成が、原子数比が $In : Ga : Zn = A : B : C$  ( $A + B + C = 1$ ) の酸化物の組成の近傍であるとは、a、b、cが、 $(a - A)^2 + (b - B)^2 + (c - C)^2 \leq r^2$  を満たすことをいう。rとしては、例えば、0.05とすればよい。他の酸化物でも同様である。

#### 【0043】

酸化物半導体膜403は、単結晶、多結晶(ポリクリスタルともいう。)または非晶質などの状態をとる。

#### 【0044】

好ましくは、酸化物半導体膜は、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜とする。

#### 【0045】

CAAC-OS膜は、完全な単結晶ではなく、完全な非晶質でもない(図14参照)。CAAC-OS膜は、非晶質相に結晶部を有する結晶・非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が100nm未満の立方体内に収まる大きさが多い。また、透過型電子顕微鏡(TEM: Transmission Electron Microscope)による観察像では、CAAC-OS膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEMによってCAAC-OS膜には粒界(グレインバウンダリーともいう。)は確認できない。そのため、CAAC-OS膜は、粒界に起因する電子移動度の低下が抑制される。

#### 【0046】

CAAC-OS膜は、c軸に対しては単結晶化した薄膜であり、a-b面はモザイク状になっており、結晶粒界が不明確である。CAAC-OS膜に含まれる結晶部は、c軸がCAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつa-b面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれa軸およびb軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85°以上95°以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°以上5°以下の範囲も含まれることとする。

#### 【0047】

なお、CAAC-OS膜において、結晶部の分布が一様でなくてもよい。例えば、CAAC-OS膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、CAAC-OS膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

#### 【0048】

CAAC-OS膜に含まれる結晶部のc軸は、CAAC-OS膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、CAAC-OS膜の形状(被形成面の断面形状または表面の断面形状)によっては互いに異なる方向を向くことがある。なお、結晶部のc軸の方向は、CAAC-OS膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に熱処理などの結晶化処理を行うことにより形成される。

#### 【0049】

10

20

30

40

50

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

【 0 0 5 0 】

なお、酸化物半導体膜を構成する酸素の一部は窒素で置換されてもよい。

【 0 0 5 1 】

また、C A A C - O S のように結晶部を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ ( R a ) が 1 n m 以下、好ましくは 0 . 3 n m 以下、より好ましくは 0 . 1 n m 以下の表面上に形成するとよい。

10

【 0 0 5 2 】

なお、 R a とは、 J I S B 0 6 0 1 : 2 0 0 1 ( I S O 4 2 8 7 : 1 9 9 7 ) で定義されている算術平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」で表現でき、以下の式にて定義される。

【 0 0 5 3 】

【 数 1 】

$$R a = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

20

【 0 0 5 4 】

なお、ここで、指定面とは、粗さ計測の対象となる面であり、座標 ( ( x 1 , y 1 , f ( x 1 , y 1 ) ) , ( x 1 , y 2 , f ( x 1 , y 2 ) ) , ( x 2 , y 1 , f ( x 2 , y 1 ) ) , ( x 2 , y 2 , f ( x 2 , y 2 ) ) の 4 点で表される四角形の領域とし、指定面を x y 平面に投影した長方形の面積を S 0 、基準面の高さ（指定面の平均の高さ）を Z 0 とする。 R a は原子間力顕微鏡 ( A F M : A t o m i c F o r c e M i c r o s c o p e ) にて測定可能である。

【 0 0 5 5 】

ただし、トランジスタ 4 4 0 ( 4 4 0 a 、 4 4 0 b 、 4 4 0 c ) は、ボトムゲート型であるため、酸化物半導体膜の下方には基板 4 0 0 とゲート電極層 4 0 1 とゲート絶縁膜 4 0 2 が存在している。従って、上記平坦な表面を得るためにゲート電極層 4 0 1 及びゲート絶縁膜 4 0 2 を形成した後、 C M P 処理などの平坦化処理を行ってもよい。

30

【 0 0 5 6 】

酸化物半導体膜 4 0 3 の膜厚は、 1 n m 以上 3 0 n m 以下（好ましくは 5 n m 以上 1 0 n m 以下）とし、スパッタリング法、 M B E ( M o l e c u l a r B e a m E p i t a x y ) 法、 C V D 法、パルスレーザ堆積法、 A L D ( A t o m i c L a y e r D e p o s i t i o n ) 法等を適宜用いることができる。また、酸化物半導体膜 4 0 3 は、スパッタリングターゲット表面に対し、概略垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて成膜してもよい。

【 0 0 5 7 】

また、酸化物半導体膜 4 0 3 において、銅、アルミニウム、塩素などの不純物がほとんど含まれない高純度化されたものであることが望ましい。トランジスタの製造工程において、これらの不純物が混入または酸化物半導体膜表面に付着する恐れのない工程を適宜選択することが好ましく、酸化物半導体膜表面に付着した場合には、シュウ酸や希フッ酸などに曝す、またはプラズマ処理 ( N 2 O プラズマ処理など) を行うことにより、酸化物半導体膜表面の不純物を除去することが好ましい。具体的には、酸化物半導体膜の銅濃度は 1 × 1 0 1 8 a t o m s / c m 3 以下、好ましくは 1 × 1 0 1 7 a t o m s / c m 3 以下とする。また、酸化物半導体膜のアルミニウム濃度は 1 × 1 0 1 8 a t o m s / c m 3 以下とする。また、酸化物半導体膜の塩素濃度は 2 × 1 0 1 8 a t o m s / c m 3 以下とする。

40

50

**【0058】**

図1(A)乃至(E)にトランジスタ440aを有する半導体装置の作製方法の一例を示す。

**【0059】**

絶縁表面を有する基板400に使用することができる基板に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板などの電子工業用に使われる各種ガラス基板を用いることが出来る。なお、基板としては、熱膨張係数が $25 \times 10^{-7} /$ 以上 $50 \times 10^{-7} /$ 以下(好ましくは、 $30 \times 10^{-7} /$ 以上 $40 \times 10^{-7} /$ 以下)であり、歪み点が650以上750以下(好ましくは、700以上740以下)である基板を用いることが好ましい。10

**【0060】**

第5世代( $1000\text{mm} \times 1200\text{mm}$ または $1300\text{mm} \times 1500\text{mm}$ )、第6世代( $1500\text{mm} \times 1800\text{mm}$ )、第7世代( $1870\text{mm} \times 2200\text{mm}$ )、第8世代( $2200\text{mm} \times 2500\text{mm}$ )、第9世代( $2400\text{mm} \times 2800\text{mm}$ )、第10世代( $2880 \times 3130\text{mm}$ )などの大型ガラス基板を用いる場合、半導体装置の作製工程における加熱処理などで生じる基板の縮みによって、微細な加工が困難になる場合がある。そのため、前述したような大型ガラス基板を基板として用いる場合、縮みの少ないものを用いることが好ましい。例えば、基板として、好ましくは450、好ましくは500の温度で1時間加熱処理を行った後の縮み量が $20\text{ppm}$ 以下、好ましくは $10\text{ppm}$ 以下、さらに好ましくは $5\text{ppm}$ 以下である大型ガラス基板を用いればよい。20

**【0061】**

または、基板400として、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することもできる。これらの基板上に半導体素子が設けられたものを用いてもよい。

**【0062】**

また、基板400として、可撓性基板を用いて半導体装置を作製してもよい。可撓性を有する半導体装置を作製するには、可撓性基板上に酸化物半導体膜403を含むトランジスタ440aを直接作製してもよいし、他の作製基板に酸化物半導体膜403を含むトランジスタ440aを作製し、その後可撓性基板に剥離、転置してもよい。なお、作製基板から可撓性基板に剥離、転置するために、作製基板と酸化物半導体膜を含むトランジスタ440aとの間に剥離層を設けるとよい。30

**【0063】**

基板400上に下地膜として絶縁膜を設けてもよい。絶縁膜としては、プラズマCVD法又はスパッタリング法等により、酸化シリコン、酸化窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、酸化ハフニウム、酸化ガリウムなどの酸化物絶縁膜、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウムなどの窒化物絶縁膜、又はこれらの混合材料を用いて形成することができる。

**【0064】**

基板400(又は基板400及び下地膜)に熱処理を行ってもよい。例えば、高温のガスを用いて熱処理を行うGRTA(Gas Rapid Thermal Anneal)装置により、650、1分~5分間、熱処理を行えばよい。なお、GRTAにおける高温のガスには、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。また、電気炉により、500、30分~1時間、熱処理を行ってもよい。40

**【0065】**

次に基板400上に導電膜を形成し、該導電膜をエッチングして、ゲート電極層401を形成する。導電膜のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。50

## 【 0 0 6 6 】

ゲート電極層 401 の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらを主成分とする合金材料を用いて形成することができる。また、ゲート電極層 401 としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。ゲート電極層 401 は、単層構造としてもよいし、積層構造としてもよい。

## 【 0 0 6 7 】

また、ゲート電極層 401 の材料は、酸化インジウム酸化スズ、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、酸化インジウム酸化亜鉛、酸化ケイ素を添加したインジウム錫酸化物などの導電性材料を適用することもできる。また、上記導電性材料と、上記金属材料の積層構造とすることもできる。

10

## 【 0 0 6 8 】

また、ゲート電極層 401 として、窒素を含む金属酸化物、具体的には、窒素を含む In-Ga-Zn-O 膜や、窒素を含む In-Sn-O 膜や、窒素を含む In-Ga-O 膜や、窒素を含む In-Zn-O 膜や、窒素を含む Sn-O 膜や、窒素を含む In-O 膜や、金属窒化膜 (InN, SnN など) を用いることができる。これらの膜は 5 eV (電子ボルト)、好ましくは 5.5 eV (電子ボルト) 以上の仕事関数を有し、ゲート電極層として用いた場合、トランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。

20

## 【 0 0 6 9 】

本実施の形態では、スパッタリング法により膜厚 100 nm のタングステン膜を形成する。

## 【 0 0 7 0 】

また、ゲート電極層 401 形成後に、基板 400、及びゲート電極層 401 に熱処理を行ってもよい。例えば、GRTA 装置により、650、1 分～5 分間、熱処理を行えばよい。また、電気炉により、500、30 分～1 時間、熱処理を行ってもよい。

## 【 0 0 7 1 】

次いで、ゲート電極層 401 上にゲート絶縁膜 491 を形成する (図 1 (A) 参照)。

30

## 【 0 0 7 2 】

なお、ゲート絶縁膜 491 の被覆性を向上させるために、ゲート電極層 401 表面に平坦化処理を行ってもよい。特にゲート絶縁膜 491 として膜厚の薄い絶縁膜を用いる場合、ゲート電極層 401 表面の平坦性が良好であることが好ましい。

## 【 0 0 7 3 】

ゲート絶縁膜 491 の膜厚は、1 nm 以上 300 nm 以下とし、成膜ガスを用いた CVD 法を用いることができる。CVD 法としては、LPCVD 法、プラズマ CVD 法などを用いることができ、また他の方法としては、塗布膜なども用いることができる。

## 【 0 0 7 4 】

ゲート絶縁膜 491 の材料としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、または窒化酸化シリコン膜を用いて形成することができる。

40

## 【 0 0 7 5 】

また、ゲート絶縁膜 491 の材料として酸化ハフニウム、酸化イットリウム、ハフニウムシリケート ( $HfSi_xO_y$  ( $x > 0, y > 0$ ))、窒素が添加されたハフニウムシリケート ( $HfSiO_xN_y$  ( $x > 0, y > 0$ ))、ハフニウムアルミネート ( $HfAl_xO_y$  ( $x > 0, y > 0$ ))、酸化ランタンなどの hight-k 材料を用いることでゲートリード電流を低減できる。さらに、ゲート絶縁膜 491 は、単層構造としても良いし、積層構造としても良い。

## 【 0 0 7 6 】

50

本実施の形態では、ゲート絶縁膜491として、プラズマCVD法により膜厚200nmの酸化窒化シリコン膜を形成する。ゲート絶縁膜491の成膜条件は、例えば、SiH<sub>4</sub>とN<sub>2</sub>Oのガス流量比をSiH<sub>4</sub>:N<sub>2</sub>O=4sccm:800sccm、圧力40Pa、RF電源電力(電源出力)50W、基板温度350とすればよい。

#### 【0077】

ゲート絶縁膜491に熱処理による脱水化又は脱水素化処理を行う。

#### 【0078】

本実施の形態では、ゲート絶縁膜491の成膜ガスとして、水素を含むガスを用いても、ゲート絶縁膜491に脱水素化処理を行うため、ゲート絶縁膜491中の水素を除去することができる。よって、プラズマCVD法を好適に用いることができる。プラズマCVD法は、成膜時に膜へごみなどが付着、混入しにくい上、比較的速い成膜速度で成膜することができる所以、厚膜化が可能であり、生産性に有利である。10

#### 【0079】

熱処理の温度は、300以上700以下、または基板の歪み点未満とする。熱処理の温度は、ゲート絶縁膜491の成膜温度より高い方が、脱水化または脱水素化の効果が高いため好ましい。例えば、熱処理装置の一つである電気炉に基板を導入し、ゲート絶縁膜491に対して真空下450において1時間の熱処理を行う。

#### 【0080】

なお、熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。20

#### 【0081】

例えば、熱処理として、650~700の高温に加熱した不活性ガス中に基板を入れ、数分間加熱した後、基板を不活性ガス中から出すGRTAを行ってもよい。30

#### 【0082】

熱処理は、減圧(真空)下、窒素雰囲気下、又は希ガス雰囲気下で行えばよい。また、上記窒素、または希ガス等の雰囲気に水、水素などが含まれないことが好ましい。また、熱処理装置に導入する窒素、または希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

#### 【0083】

熱処理によって、ゲート絶縁膜491の脱水化または脱水素化を行うことができ、トランジスタの特性変動を引き起こす水素、又は水などの不純物が排除されたゲート絶縁膜492を形成することができる(図1(B)参照。)。40

#### 【0084】

脱水化又は脱水素化処理を行う熱処理において、ゲート絶縁膜491表面は水素又は水等の放出を妨害するような状態(例えば、水素又は水等を通過させない(ブロックする)膜などを設ける等)とせず、ゲート絶縁膜491は表面を露出した状態とすることが好ましい。

#### 【0085】

また、脱水化又は脱水素化のための熱処理は、複数回行ってもよく、他の熱処理と兼ねてもよい。

#### 【0086】

次に、脱水化または脱水素化されたゲート絶縁膜492に酸素ドープ処理を行い、酸素を過剰に含むゲート絶縁膜402を形成する(図1(C)参照)。ゲート絶縁膜492に酸素ドープ処理を行うことにより、酸素431をゲート絶縁膜492に供給して、ゲート絶縁膜492中、又はゲート絶縁膜492中及び後工程でゲート絶縁膜402上に形成される酸化物半導体膜441との界面近傍に酸素を含有させる。

#### 【0087】

ゲート絶縁膜402は、膜中(バルク中)に少なくとも化学量論比を超える量の酸素が存在することが好ましい。

#### 【0088】

ドープされる酸素(酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン(酸素分子イオン)、及び/又は酸素クラスタイオン)431は、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。また、イオン注入法にはガスクラスタイオンビームを用いてもよい。酸素のドープ処理は、全面を一度に行ってもよいし、線状のイオンビーム等を用いて移動(スキヤン)させ行ってもよい。

10

#### 【0089】

例えば、ドープされる酸素(酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン(酸素分子イオン)、及び/又は酸素クラスタイオン)431は、酸素を含むガスを用いてプラズマ発生装置により供給されてもよいし、又はオゾン発生装置により供給されてもよい。より具体的には、例えば、半導体装置に対してエッティング処理を行うための装置や、レジストマスクに対してアッシングを行うための装置などを用いて酸素431を発生させ、ゲート絶縁膜491を処理してゲート絶縁膜402を形成することができる。

20

#### 【0090】

酸素ドープ処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素ドープ処理において、希ガスを用いてもよい。

#### 【0091】

酸素431のドープ処理は、例えば、イオン注入法で酸素イオンの注入を行う場合、ドーズ量を $1 \times 10^{13}$  ions/cm<sup>2</sup>以上 $5 \times 10^{16}$  ions/cm<sup>2</sup>以下とすればよい。

30

#### 【0092】

また、酸素ドープ処理によって、ゲート絶縁膜402の表面の平坦性を向上させることができる。

#### 【0093】

次に、ゲート絶縁膜402上に膜状の酸化物半導体膜441を形成する(図1(D)参照)。なお、本実施の形態では、酸化物半導体膜441は膜状の酸化物半導体膜であり、完成したトランジスタ440aに含まれる酸化物半導体膜403は島状の酸化物半導体膜である。

#### 【0094】

ゲート絶縁膜402において酸化物半導体膜441が接して形成される領域に、平坦化処理を行ってもよい。平坦化処理としては、特に限定されないが、研磨処理(例えば、化学的機械研磨法(Chemical Mechanical Polishing: CMP))、ドライエッティング処理、プラズマ処理を用いることができる。また、先の酸素ドープ処理を、ゲート絶縁膜402の平坦化処理と兼ねることも可能である。

40

#### 【0095】

プラズマ処理としては、例えば、アルゴンガスを導入してプラズマを発生させる逆スパッタリングを行うことができる。逆スパッタリングとは、アルゴン雰囲気下で基板側にRF電源を用いて電圧を印加して基板近傍にプラズマを形成して表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。逆スパッタリングを行うと、ゲート絶縁膜402の表面に付着している粉状物質(パーティクル、ごみ

50

ともいう)を除去することができる。

**【0096】**

平坦化処理として、研磨処理、ドライエッティング処理、プラズマ処理は複数回行ってもよく、それらを組み合わせて行ってもよい。また、組み合わせて行う場合、工程順も特に限定されず、ゲート絶縁膜402表面の凹凸状態に合わせて適宜設定すればよい。

**【0097】**

なお、酸化物半導体膜441は、成膜時に酸素が多く含まれるような条件(例えば、酸素100%の雰囲気下でスパッタリング法により成膜を行うなど)で成膜して、酸素を多く含む(好ましくは酸化物半導体が結晶状態における化学量論的組成に対し、酸素の含有量が過剰な領域が含まれている)膜とすることが好ましい。

10

**【0098】**

なお、本実施の形態において、酸化物半導体膜441として、AC電源装置を有するスパッタリング装置を用いたスパッタリング法を用い、膜厚35nmのIn-Ga-Zn系酸化物膜(IGZO膜)を成膜する。本実施の形態において、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)の原子比のIn-Ga-Zn系酸化物ターゲットを用いる。なお、成膜条件は、酸素及びアルゴン雰囲気下(酸素流量比率50%)、圧力0.6Pa、電源電力5kW、基板温度170°とする。この成膜条件での成膜速度は、16nm/minである。

**【0099】**

酸化物半導体膜441を、成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

20

**【0100】**

減圧状態に保持された成膜室内に基板を保持する。そして、成膜室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて基板400上に酸化物半導体膜441を成膜する。成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素(水素原子)、水(H<sub>2</sub>O)など水素(水素原子)を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜441に含まれる不純物の濃度を低減できる。

30

**【0101】**

酸化物半導体膜403と接するゲート絶縁膜402は、酸素の供給源となる酸素を多く(過剰に)含むので、該ゲート絶縁膜402から酸化物半導体膜403へ酸素を供給することができる。

**【0102】**

酸化物半導体膜403とゲート絶縁膜402とを接した状態で熱処理を行うことが好ましい。熱処理によってゲート絶縁膜402から酸化物半導体膜403への酸素の供給を効果的に行うことができる。

40

**【0103】**

なお、ゲート絶縁膜402から酸化物半導体膜403への酸素の供給のための熱処理を、酸化物半導体膜441が島状に加工される前に行うと、ゲート絶縁膜402に含まれる酸素が熱処理によって放出されるのを防止することができるため好ましい。

**【0104】**

酸化物半導体膜403へ酸素を供給することにより、酸化物半導体膜403中の酸素欠損を補填することができる。

**【0105】**

酸化物半導体膜441をフォトリソグラフィ工程により加工して、島状の酸化物半導体膜403を形成する。

**【0106】**

50

また、島状の酸化物半導体膜403を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

#### 【0107】

なお、酸化物半導体膜441のエッティングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。例えば、酸化物半導体膜441のウェットエッティングに用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO-07N（関東化学社製）を用いてもよい。また、ICP（Inductive Coupled Plasma：誘導結合型プラズマ）エッティング法によるドライエッティングによってエッティング加工してもよい。

10

#### 【0108】

次いで、ゲート電極層401、ゲート絶縁膜402、及び酸化物半導体膜403上に、ソース電極層及びドレイン電極層（これと同じ層で形成される配線を含む）となる導電膜を形成する。

#### 【0109】

導電膜は後の熱処理に耐えられる材料を用いる。ソース電極層、及びドレイン電極層に用いる導電膜としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンクスステン膜）等を用いることができる。また、Al、Cuなどの金属膜の下側又は上側の一方または双方にTi、Mo、Wなどの高融点金属膜またはそれらの金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンクスステン膜）を積層させた構成としても良い。また、ソース電極層、及びドレイン電極層に用いる導電膜としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ( $In_2O_3 - SnO_2$ )、酸化インジウム酸化亜鉛( $In_2O_3 - ZnO$ )またはこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

20

#### 【0110】

フォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッティングを行ってソース電極層405a、ドレイン電極層405bを形成する。ソース電極層405a、ドレイン電極層405bを形成した後、レジストマスクを除去する。

30

#### 【0111】

レジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いるとい。酸化物半導体膜403上で隣り合うソース電極層405aの下端部とドレイン電極層405bの下端部との間隔幅によって後に形成されるトランジスタ440のチャネル長Lが決定される。なお、チャネル長L = 25nm未満の露光を行う場合には、数nm～数10nmと極めて波長が短い超紫外線（Extreme Ultraviolet）を用いてレジストマスク形成時の露光を行うとい。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成されるトランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化できる。

40

#### 【0112】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッティング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッティングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッティング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減するため、工程の簡略化が可能となる。

#### 【0113】

本実施の形態では、導電膜のエッティングには、塩素を含むガス、例えば、塩素( $Cl_2$ )

50

、三塩化硼素（ $B Cl_3$ ）、四塩化珪素（ $Si Cl_4$ ）、四塩化炭素（ $CCl_4$ ）などを含むガスを用いることができる。また、フッ素を含むガス、例えば、四弗化炭素（ $CF_4$ ）、六弗化硫黄（ $SF_6$ ）、三弗化窒素（ $NF_3$ ）、トリフルオロメタン（ $CHF_3$ ）などを含むガスを用いることができる。また、これらのガスにヘリウム（He）やアルゴン（Ar）などの希ガスを添加したガス、などを用いることができる。

#### 【0114】

エッチング法としては、平行平板型RIE（Reactive Ion Etching）法や、ICP（Inductively Coupled Plasma：誘導結合型プラズマ）エッチング法を用いることができる。所望の加工形状にエッチングできるように、エッチング条件（コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等）を適宜調節する。10

#### 【0115】

本実施の形態では、導電膜としてスパッタリング法により膜厚100nmのチタン膜、膜厚400nmのアルミニウム膜、膜厚100nmのチタン膜の積層を用いる。導電膜のエッチングは、ドライエッチング法により、チタン膜、アルミニウム膜、チタン膜の積層をエッチングして、ソース電極層405a、ドレイン電極層405bを形成する。

#### 【0116】

本実施の形態では、第1のエッチング条件でチタン膜とアルミニウム膜の2層をエッチングした後、第2のエッチング条件で残りのチタン膜単層を除去する。なお、第1のエッチング条件は、エッチングガス（ $BCl_3 : Cl_2 = 750 \text{ sccm} : 150 \text{ sccm}$ ）を用い、バイアス電力を1500Wとし、ICP電源電力を0Wとし、圧力を2.0Paとする。第2のエッチング条件は、エッチングガス（ $BCl_3 : Cl_2 = 700 \text{ sccm} : 100 \text{ sccm}$ ）を用い、バイアス電力を750Wとし、ICP電源電力を0Wとし、圧力を2.0Paとする。20

#### 【0117】

なお、導電膜のエッチング工程の際に、酸化物半導体膜403がエッチングされ、分断することのないようエッチング条件を最適化することが望まれる。しかしながら、導電膜のみをエッチングし、酸化物半導体膜403を全くエッチングしないという条件を得ることは難しく、導電膜のエッチングの際に酸化物半導体膜403は一部のみがエッチングされ、溝部（凹部）を有する酸化物半導体膜となることもある。また、酸化物半導体膜403のうち、ソース電極層405a、ドレイン電極層405bと接する部分の近傍では、その他の部分より導電率が高くなることがある。この場合、ソース電極層405aの近傍の導電率が高い部分をソースと称し、ドレイン電極層405bの近傍の導電率が高い部分をドレインと称してもよい。30

#### 【0118】

以上の工程で、本実施の形態のトランジスタ440aが作製される。

#### 【0119】

本実施の形態では、ソース電極層405a、ドレイン電極層405b上に、酸化物半導体膜403と接して、絶縁膜409を形成する（図1（E）参照）。

#### 【0120】

絶縁膜409としては、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ハフニウム膜、又は酸化ガリウム膜、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などの無機絶縁膜の単層又は積層を用いることができる。40

#### 【0121】

また、さらに絶縁膜409上に緻密性の高い無機絶縁膜を設けてもよい。例えば、絶縁膜409上にスパッタリング法により酸化アルミニウム膜を形成する。酸化アルミニウム膜を高密度（膜密度 $3.2 \text{ g/cm}^3$ 以上、好ましくは $3.6 \text{ g/cm}^3$ 以上）とすることによって、トランジスタ440aに安定な電気特性を付与することができる。膜密度はラザフォード後方散乱法（RBS：Rutherford Backscattering）50

Spectrometry) や、X線反射率測定法(XRR:X-Ray Reflection)によって測定することができる。

【0122】

トランジスタ440a上に設けられる絶縁膜として用いることのできる酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を通過させない遮断効果(ブロック効果)が高い。

【0123】

従って、酸化アルミニウム膜は、作製工程中及び作製後において、変動要因となる水素、水分などの不純物の酸化物半導体膜403への混入、及び酸化物半導体を構成する主成分材料である酸素の酸化物半導体膜403からの放出を防止する保護膜として機能する。

10

【0124】

また、トランジスタ440a起因の表面凹凸を低減するために平坦化絶縁膜を形成してもよい。平坦化絶縁膜としては、ポリイミド、アクリル、ベンゾシクロブテン系樹脂等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(low-k材料)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで、平坦化絶縁膜を形成してもよい。

【0125】

例えば、平坦化絶縁膜として、膜厚1500nmのアクリル樹脂膜を形成すればよい。アクリル樹脂膜は塗布法による塗布後、焼成(例えば窒素雰囲気下250℃で1時間)して形成することができる。

20

【0126】

平坦化絶縁膜を形成後、熱処理を行ってもよい。例えば、窒素雰囲気下250℃で1時間熱処理を行う。

【0127】

このように、トランジスタ440a形成後、熱処理を行ってもよい。また、熱処理は複数回行ってもよい。

【0128】

酸化物半導体膜403に接するゲート絶縁膜402に、熱処理による脱水化又は脱水素化処理を行い、かつ脱水化又は脱水素化処理後に酸素ドープ処理を行って作製されたトランジスタ440aは、電気特性変動が抑制されており、電気的に安定である。

30

【0129】

よって、安定した電気特性を有するトランジスタ440aを作製することができる。

【0130】

また、本発明の一形態は、電気特性が良好で信頼性のよいトランジスタ440aを含む半導体装置を作製することができる。

【0131】

(実施の形態2)

本実施の形態では、半導体装置及び半導体装置の作製方法の他の一形態を、図2を用いて説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

40

【0132】

本実施の形態では、酸化物半導体層上に接して設けられる絶縁膜に熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行い、作製するトランジスタ440bを例として示す。

【0133】

図2(A)乃至(D)にトランジスタ440bを有する半導体装置の作製方法の一例を示す。

【0134】

絶縁表面を有する基板400上に導電膜を形成し、該導電膜をエッチングして、ゲート電

50

極層 401 を形成する。本実施の形態では、スパッタリング法により膜厚 100 nm のタンゲステン膜を形成する。

**【0135】**

次に、ゲート電極層 401 上にゲート絶縁膜 408 を形成する。ゲート絶縁膜 408 の材料又は膜厚等は、実施の形態 1 と同様とすることができる。

**【0136】**

ゲート絶縁膜 408 上に酸化物半導体膜を成膜後、該酸化物半導体膜を島状に加工して酸化物半導体膜 403 を形成する。本実施の形態において、酸化物半導体膜 403 として、A C 電源装置を有するスパッタリング装置を用いたスパッタリング法を用い、膜厚 35 nm の In - Ga - Zn 系酸化物膜 (IGZO 膜) を成膜する。本実施の形態において、In : Ga : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3 ) の原子比の In - Ga - Zn 系酸化物ターゲットを用いる。なお、成膜条件は、酸素及びアルゴン雰囲気下 (酸素流量比率 50 %) 、圧力 0.6 Pa 、電源電力 5 kW 、基板温度 170 °C とする。この成膜条件での成膜速度は、16 nm / min である。

10

**【0137】**

なお、ゲート絶縁膜 408 を大気に解放せずにゲート絶縁膜 408 と酸化物半導体膜を連続的に形成することが好ましい。ゲート絶縁膜 408 を大気に曝露せずにゲート絶縁膜 408 と酸化物半導体膜を連続して形成すると、ゲート絶縁膜 408 表面に水素や水分などの不純物が吸着することを防止することができる。

**【0138】**

酸化物半導体膜 403 に、過剰な水素 (水や水酸基を含む) を除去 (脱水化または脱水素化) するための熱処理を行ってもよい。例えば、熱処理装置の一つである電気炉に基板を導入し、酸化物半導体膜 403 に対して窒素雰囲気下 450 °C において 1 時間、さらに窒素及び酸素雰囲気下 450 °C において 1 時間の熱処理を行えばよい。酸化物半導体膜 403 に脱水化又は脱水素化処理を行った後に、酸素を含む雰囲気下で熱処理を行うことにより、酸化物半導体膜 403 を高純度化することができる。

20

**【0139】**

次いで、ゲート電極層 401 、ゲート絶縁膜 402 、及び酸化物半導体膜 403 上に、ソース電極層及びドレイン電極層となる導電膜を形成する。

**【0140】**

本実施の形態では、導電膜としてスパッタリング法により形成した膜厚 100 nm のチタン膜、膜厚 400 nm のアルミニウム膜、膜厚 100 nm のチタン膜の積層の導電膜を用いる。導電膜のエッチングは、ドライエッチング法により、チタン膜、アルミニウム膜、チタン膜の積層をエッチングして、ソース電極層 405a 、ドレイン電極層 405b を形成する。

30

**【0141】**

本実施の形態では、第 1 のエッチング条件でチタン膜とアルミニウム膜の 2 層をエッチングした後、第 2 のエッチング条件で残りのチタン膜単層を除去する。なお、第 1 のエッチング条件は、エッチングガス (BCl<sub>3</sub> : Cl<sub>2</sub> = 750 sccm : 150 sccm) を用い、バイアス電力を 1500 W とし、ICP 電源電力を 0 W とし、圧力を 2.0 Pa とする。第 2 のエッチング条件は、エッチングガス (BCl<sub>3</sub> : Cl<sub>2</sub> = 700 sccm : 100 sccm) を用い、バイアス電力を 750 W とし、ICP 電源電力を 0 W とし、圧力を 2.0 Pa とする。

40

**【0142】**

ソース電極層 405a 、ドレイン電極層 405b 上に、酸化物半導体膜 403 と接して、絶縁膜 496 を形成する (図 2 (A) 参照)。

**【0143】**

絶縁膜 496 としては、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ハフニウム膜、酸化ガリウム膜、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、又は窒化酸化アルミニウム膜などの無機絶

50

縁膜の単層又は積層を用いることができる。

**【0144】**

絶縁膜496の形成方法としては、成膜ガスを用いたCVD法を用いることができる。CVD法としては、LPCVD法、プラズマCVD法などを用いることができ、また他の方法としては、塗布膜なども用いることができる。

**【0145】**

本実施の形態では、絶縁膜496として、プラズマCVD法により膜厚300nmの酸化窒化シリコン膜を形成する。絶縁膜496の成膜条件は、例えば、SiH<sub>4</sub>とN<sub>2</sub>Oのガス流量比をSiH<sub>4</sub>:N<sub>2</sub>O=4sccm:800sccm、圧力40Pa、RF電源電力(電源出力)50W、基板温度350とすればよい。

10

**【0146】**

絶縁膜496に熱処理による脱水化又は脱水素化処理を行う。

**【0147】**

本実施の形態では、絶縁膜496の成膜ガスとして、水素を含むガスを用いても、絶縁膜496に脱水素化処理を行うため、絶縁膜496中の水素を除去することができる。よって、プラズマCVD法を好適に用いることができる。プラズマCVD法は、成膜時に膜へごみなどが付着、混入しにくい上、比較的速い成膜速度で成膜することができるので、厚膜化が可能であり、生産性に有利である。

**【0148】**

熱処理の温度は、300以上700以下、または基板の歪み点未満とする。熱処理の温度は、絶縁膜496の成膜温度より高い方が、脱水化または脱水素化の効果が高いため好ましい。例えば、熱処理装置の一つである電気炉に基板を導入し、絶縁膜496に対して真空下450において1時間の熱処理を行う。

20

**【0149】**

なお、熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導または熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて熱処理を行う装置である。高温のガスには、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。

30

**【0150】**

例えば、熱処理として、650~700の高温に加熱した不活性ガス中に基板を入れ、数分間加熱した後、基板を不活性ガス中から出すGRTAを行ってもよい。

**【0151】**

熱処理は、減圧下、窒素雰囲気下、又は希ガス雰囲気下で行えばよい。また、上記窒素、または希ガス等の雰囲気に水、水素などが含まれないことが好ましい。また、熱処理装置に導入する窒素、または希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

40

**【0152】**

熱処理によって、絶縁膜496の脱水化または脱水素化を行うことができ、水素、又は水などの不純物が排除された絶縁膜497を形成することができる(図2(B)参照。)。

**【0153】**

脱水化又は脱水素化処理を行う熱処理において、絶縁膜496表面は水素又は水等の放出を妨害するような状態(例えば、水素又は水等を通過させない(ブロックする)膜などを設ける等)とせず、絶縁膜496は表面を露出した状態とすることが好ましい。

50

## 【0154】

また、脱水化又は脱水素化のための熱処理は、複数回行ってもよく、他の熱処理と兼ねてもよい。

## 【0155】

脱水素化又は脱水素化のための熱処理を行うことにより、絶縁膜497に含まれる、水、水素等の不純物を除去し、低減させることができる。絶縁膜497に水素が含まれると、その水素の酸化物半導体膜403への侵入、又は水素による酸化物半導体膜403中の酸素の引き抜きが生じ酸化物半導体膜403のバックチャネルが低抵抗化(N型化)してしまい、寄生チャネルが形成される恐れがある。よって、脱水素化又は脱水素化のための熱処理を行うことにより、絶縁膜497はできるだけ水素を含まない膜とすることで、トランジスタ440bの特性変動を抑制し、安定した電気特性を付与することができる。10

## 【0156】

次に、脱水化または脱水素化された絶縁膜497に酸素ドープ処理を行い、酸素を過剰に含む絶縁膜407を形成する(図2(C)参照)。絶縁膜497に酸素ドープ処理を行うことにより、酸素431を絶縁膜497に供給して、絶縁膜497中、又は絶縁膜497中及び酸化物半導体膜403との界面近傍に酸素を含有させる。

## 【0157】

絶縁膜407は、膜中(バルク中)に少なくとも化学量論比を超える量の酸素が存在することが好ましい。

## 【0158】

ドープされる酸素(酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン(酸素分子イオン)、及び/又は酸素クラスタイオン)431は、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。また、イオン注入法にはガスクラスタイオンビームを用いてよい。酸素のドープ処理は、全面を一度に行ってもよいし、線状のイオンビーム等を用いて移動(スキヤン)させ行ってもよい。20

## 【0159】

例えば、ドープされる酸素(酸素ラジカル、酸素原子、酸素分子、酸素イオン(酸素分子イオン)、及び/又は酸素クラスタイオン)431は、酸素を含むガスを用いてプラズマ発生装置により供給されてもよいし、又はオゾン発生装置により供給されてもよい。より具体的には、例えば、半導体装置に対してエッティング処理を行うための装置や、レジストマスクに対してアッシングを行うための装置などを用いて酸素431を発生させ、絶縁膜497を処理して絶縁膜407を形成することができる。30

## 【0160】

酸素ドープ処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素ドープ処理において、希ガスを用いてもよい。

## 【0161】

酸素431のドープ処理は、例えば、イオン注入法で酸素イオンの注入を行う場合、ドーズ量を $1 \times 10^{13} \text{ ions/cm}^2$ 以上 $5 \times 10^{16} \text{ ions/cm}^2$ 以下とすればよい。40

## 【0162】

絶縁膜407は酸素ドープ処理により、酸素を多く(過剰)含む膜(好ましくは結晶状態における化学量論的組成に対し、酸素の含有量が過剰な領域が含まれている膜)であるので、酸化物半導体膜403に対する酸素の供給源として好適に機能させることができる。

## 【0163】

酸化物半導体膜403に、一部(チャネル形成領域)が絶縁膜407と接した状態で熱処理を行うことが好ましい。熱処理によって絶縁膜407から酸化物半導体膜403への酸素の供給を効果的に行うことができる。

## 【0164】

10

20

30

40

50

本実施の形態において、脱水化又は脱水素化した酸化物半導体膜403に、酸素を導入して膜中に酸素を供給することによって、酸化物半導体膜403を高純度化、及び電気的にI型(真性)化することができる。

#### 【0165】

熱処理の温度は、250以上700以下、または400以上700以下、または基板の歪み点未満とする。例えば、熱処理装置の一つである電気炉に基板を導入し、酸化物半導体膜に対して窒素雰囲気下250において1時間の熱処理を行う。

#### 【0166】

この熱処理は絶縁膜407の脱水化又は脱水素化処理を行う熱処理と同様の加熱方法及び加熱装置を用いることができる。

10

#### 【0167】

熱処理は、減圧下、又は窒素、酸素、超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計を用いて測定した場合の水分量が20ppm(露点換算で-55)以下、好ましくは1ppm以下、好ましくは10ppb以下の空気)、若しくは希ガス(アルゴン、ヘリウムなど)の雰囲気下で行えばよいが、上記窒素、酸素、超乾燥エア、または希ガス等の雰囲気に水、水素などが含まれないことが好ましい。また、熱処理装置に導入する窒素、酸素、または希ガスの純度を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

#### 【0168】

20

酸化物半導体膜403と酸素を過剰に含む絶縁膜407とを接した状態で熱処理を行うため、酸化物半導体膜403を構成する主成分材料の一つである酸素を、酸素を含む絶縁膜407より酸化物半導体膜403へ供給することができる。

#### 【0169】

また、上記熱処理は、絶縁膜407上に緻密性の高い無機絶縁膜を設けた後行うことが好ましい。例えば、絶縁膜407上にスパッタリング法により酸化アルミニウム膜を形成する。

#### 【0170】

絶縁膜407上に設けられる絶縁膜として用いることのできる酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を通過させない遮断効果(ブロック効果)が高い。酸化アルミニウム膜を高密度(膜密度3.2g/cm<sup>3</sup>以上、好ましくは3.6g/cm<sup>3</sup>以上)とすることによって、上記ブロック効果をより高めることができる。

30

#### 【0171】

従って、酸化アルミニウム膜により酸素ドープ処理を行った絶縁膜407を覆い、熱処理を行うことで、絶縁膜407から酸化アルミニウム膜方向への酸素の放出を防止し、絶縁膜407から酸化物半導体膜403への酸素の供給を効果的に行うことができる。さらに、作製工程中及び作製後において、変動要因となる水素、水分などの不純物の酸化物半導体膜403への混入、及び酸化物半導体を構成する主成分材料である酸素の酸化物半導体膜403からの放出を防止する保護膜として機能する。

40

#### 【0172】

以上の工程で、トランジスタ440bを作製する(図2(D)参照)。

#### 【0173】

酸化物半導体膜403に接する絶縁膜407に、熱処理による脱水化又は脱水素化処理を行い、かつ脱水化又は脱水素化処理後に酸素ドープ処理を行って作製されたトランジスタ440bは、電気特性変動が抑制されており、電気的に安定である。

#### 【0174】

よって、安定した電気特性を有するトランジスタ440bを作製することができる。

#### 【0175】

また、本発明の一形態は、電気特性が良好で信頼性のよいトランジスタ440bを含む半

50

導体装置を作製することができる。

**【0176】**

(実施の形態3)

本実施の形態では、半導体装置及び半導体装置の作製方法の他の一形態を、図3を用いて説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

**【0177】**

本実施の形態では、酸化物半導体膜の下層に接して設けられるゲート絶縁膜と、酸化物半導体膜上に接して設けられる絶縁膜との双方に熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行い、作製するトランジスタ440cを例として示す。

10

**【0178】**

図3(A)乃至(F)にトランジスタ440cを有する半導体装置の作製方法の一例を示す。

**【0179】**

基板400上に導電膜を形成し、該導電膜をエッチングして、ゲート電極層401を形成する。

**【0180】**

本実施の形態では、スパッタリング法により膜厚100nmのタンゲステン膜を形成する。

20

**【0181】**

次いで、ゲート電極層401上にゲート絶縁膜を形成する。

**【0182】**

本実施の形態では、ゲート絶縁膜として、プラズマCVD法により膜厚200nmの酸化窒化シリコン膜を形成する。ゲート絶縁膜の成膜条件は、例えば、SiH<sub>4</sub>とN<sub>2</sub>Oのガス流量比をSiH<sub>4</sub>:N<sub>2</sub>O=4sccm:800sccm、圧力40Pa、RF電源電力(電源出力)50W、基板温度350とすればよい。

**【0183】**

ゲート絶縁膜に熱処理による脱水化又は脱水素化処理を行う。

**【0184】**

本実施の形態では、ゲート絶縁膜の成膜ガスとして、水素を含むガスを用いても、ゲート絶縁膜に脱水素化処理を行うため、ゲート絶縁膜中の水素を除去することができる。よって、プラズマCVD法を好適に用いることができる。プラズマCVD法は、成膜時に膜へごみなどが付着、混入しにくい上、比較的速い成膜速度で成膜することができるので、厚膜化が可能であり、生産性に有利である。

30

**【0185】**

熱処理の温度は、300以上700以下、または基板の歪み点未満とする。熱処理の温度は、ゲート絶縁膜の成膜温度より高い方が、脱水化または脱水素化の効果が高いため好ましい。例えば、熱処理装置の一つである電気炉に基板を導入し、ゲート絶縁膜に対して窒素雰囲気下450において1時間の熱処理を行う。

40

**【0186】**

熱処理によって、ゲート絶縁膜の脱水化または脱水素化を行うことができ、トランジスタの特性変動を引き起こす水素、又は水などの不純物が排除されたゲート絶縁膜492を形成することができる(図3(A)参照。)。

**【0187】**

次に、脱水化または脱水素化されたゲート絶縁膜492に酸素ドープ処理を行い、酸素を過剰に含むゲート絶縁膜402を形成する(図3(B)参照)。ゲート絶縁膜492に酸素ドープ処理を行うことにより、酸素431aをゲート絶縁膜492に供給して、ゲート絶縁膜492中、又はゲート絶縁膜492中及び後工程でゲート絶縁膜402上に形成される酸化物半導体膜403との界面近傍に酸素を含有させる。

50

## 【0188】

ゲート絶縁膜402は、膜中(バルク中)に少なくとも化学量論比を超える量の酸素が存在することが好ましい。

## 【0189】

ドープされる酸素(酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン(酸素分子イオン)、及び/又は酸素クラスタイオン)431aは、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。また、イオン注入法にはガスクラスタイオンビームを用いてもよい。酸素のドープ処理は、全面を一度に行ってもよいし、線状のイオンビーム等を用いて移動(スキヤン)させ行ってもよい。10

## 【0190】

例えば、ドープされる酸素(酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン(酸素分子イオン)、及び/又は酸素クラスタイオン)431aは、酸素を含むガスを用いてプラズマ発生装置により供給されてもよいし、又はオゾン発生装置により供給されてもよい。より具体的には、例えば、半導体装置に対してエッチング処理を行うための装置や、レジストマスクに対してアッシングを行うための装置などを用いて酸素431aを発生させ、ゲート絶縁膜491を処理してゲート絶縁膜402を形成することができる。

## 【0191】

酸素ドープ処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素ドープ処理において、希ガスを用いてもよい。20

## 【0192】

なお、酸素ドープ処理によって、ゲート絶縁膜402の表面の平坦性を向上させることができる。

## 【0193】

次に、ゲート絶縁膜402上に酸化物半導体膜441を形成する(図3(C)参照)。

## 【0194】

なお、本実施の形態において、酸化物半導体膜441として、AC電源装置を有するスパッタリング装置を用いたスパッタリング法を用い、膜厚35nmのIn-Ga-Zn系酸化物膜(IGZO膜)を成膜する。本実施の形態において、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)の原子比のIn-Ga-Zn系酸化物ターゲットを用いる。なお、成膜条件は、酸素及びアルゴン雰囲気下(酸素流量比率50%)、圧力0.6Pa、電源電力5kW、基板温度170°とする。この成膜条件での成膜速度は、16nm/minである。30

## 【0195】

酸化物半導体膜403と接するゲート絶縁膜402は、酸素の供給源となる酸素を多く(過剰に)含むので、該ゲート絶縁膜402から酸化物半導体膜403へ酸素を供給することができる。

## 【0196】

酸化物半導体膜403とゲート絶縁膜402とを接した状態で熱処理を行うことが好ましい。熱処理によってゲート絶縁膜402から酸化物半導体膜403への酸素の供給を効果的に行うことができる。40

## 【0197】

なお、ゲート絶縁膜402から酸化物半導体膜403への酸素の供給のための熱処理を、酸化物半導体膜441が島状に加工される前に行うと、ゲート絶縁膜402に含まれる酸素が熱処理によって放出されるのを防止することができるため好ましい。

## 【0198】

酸化物半導体膜403へ酸素を供給することにより、酸化物半導体膜403中の酸素欠損を補填することができる。

## 【0199】

酸素ドープ処理を行ったゲート絶縁膜402から酸化物半導体膜403へ酸素の供給を行うための熱処理は、この後に行われる熱処理と兼ねてもよい。例えば、絶縁膜407の脱水化又は脱水素化のための熱処理、酸素ドープ処理を行った絶縁膜407から酸化物半導体膜403へ酸素の供給を行う熱処理と兼ねることができる。

#### 【0200】

酸化物半導体膜441をフォトリソグラフィ工程により加工して、島状の酸化物半導体膜403を形成する。

#### 【0201】

次いで、ゲート電極層401、ゲート絶縁膜402、及び酸化物半導体膜403上に、ソース電極層及びドレイン電極層となる導電膜を形成する。

10

#### 【0202】

本実施の形態では、導電膜としてスパッタリング法により形成した膜厚100nmのチタン膜、膜厚400nmのアルミニウム膜、膜厚100nmのチタン膜の積層の導電膜を用いる。導電膜のエッチングは、ドライエッチング法により、チタン膜、アルミニウム膜、チタン膜の積層をエッチングして、ソース電極層405a、ドレイン電極層405bを形成する。

#### 【0203】

ソース電極層405a、ドレイン電極層405b上に、酸化物半導体膜403と接して、絶縁膜を形成する。

#### 【0204】

本実施の形態では、絶縁膜として、プラズマCVD法により膜厚300nmの酸化窒化シリコン膜を形成する。絶縁膜の成膜条件は、例えば、SiH<sub>4</sub>とN<sub>2</sub>Oのガス流量比をSiH<sub>4</sub>:N<sub>2</sub>O=4sccm:800sccm、圧力40Pa、RF電源電力(電源出力)50W、基板温度350とすればよい。

20

#### 【0205】

絶縁膜に熱処理による脱水化又は脱水素化処理を行う。

#### 【0206】

本実施の形態では、絶縁膜の成膜ガスとして、水素を含むガスを用いても、ゲート絶縁膜に脱水素化処理を行うため、絶縁膜中の水素を除去することができる。よって、プラズマCVD法を好適に用いることができる。プラズマCVD法は、成膜時に膜へごみなどが付着、混入しにくい上、比較的速い成膜速度で成膜することができるので、厚膜化が可能であり、生産性に有利である。

30

#### 【0207】

熱処理の温度は、300以上700以下、または基板の歪み点未満とする。熱処理の温度は、絶縁膜の成膜温度より高い方が、脱水化または脱水素化の効果が高いため好ましい。例えば、熱処理装置の一つである電気炉に基板を導入し、絶縁膜に対して窒素雰囲気下450において1時間の熱処理を行う。

#### 【0208】

熱処理によって、絶縁膜の脱水化または脱水素化を行うことができ、水素、又は水などの不純物が排除された絶縁膜497を形成することができる(図3(D)参照。)。

40

#### 【0209】

脱水化又は脱水素化処理を行う熱処理において、絶縁膜496表面は水素又は水等の放出を妨害するような状態(例えば、水素又は水等を通過させない(ブロックする)膜などを設ける等)とせず、絶縁膜496は表面を露出した状態とすることが好ましい。

#### 【0210】

また、脱水化又は脱水素化のための熱処理は、複数回行ってもよく、他の熱処理と兼ねてもよい。

#### 【0211】

脱水素化又は脱水素化のための熱処理を行うことにより、絶縁膜497(絶縁膜407)に含まれる、水、水素等の不純物を除去し、低減させることができる。絶縁膜497(絶

50

縁膜 407) に水素が含まれると、その水素の酸化物半導体膜 403への侵入、又は水素による酸化物半導体膜 403中の酸素の引き抜きが生じ酸化物半導体膜 403のバックチャネルが低抵抗化( N型化 )してしまい、寄生チャネルが形成される恐れがある。よって、脱水素化又は脱水素化のための熱処理を行うことにより、絶縁膜 497( 絶縁膜 407 )はできるだけ水素を含まない膜として、トランジスタ 440b の特性変動を抑制し、安定した電気特性を付与することができる。

#### 【 0212 】

次に、脱水化または脱水素化された絶縁膜 497 に酸素ドープ処理を行い、酸素を過剰に含む絶縁膜 407 を形成する( 図 3 ( E ) 参照 )。絶縁膜 497 に酸素ドープ処理を行うことにより、酸素 431b を絶縁膜 497 に供給して、絶縁膜 497 中、又は絶縁膜 497 中及び酸化物半導体膜 403との該界面近傍に酸素を含有させる。

10

#### 【 0213 】

絶縁膜 407 は、膜中( バルク中 )に少なくとも化学量論比を超える量の酸素が存在することが好ましい。

#### 【 0214 】

ドープされる酸素( 酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン( 酸素分子イオン )、及び / 又は酸素クラスタイオン ) 431b は、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。また、イオン注入法にはガスクラスタイオンビームを用いてもよい。酸素のドープ処理は、全面を一度に行ってもよいし、線状のイオンビーム等を用いて移動( スキャン )させ行ってもよい。

20

#### 【 0215 】

例えば、ドープされる酸素( 酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン( 酸素分子イオン )、及び / 又は酸素クラスタイオン ) 431b は、酸素を含むガスを用いてプラズマ発生装置により供給されてもよいし、又はオゾン発生装置により供給されてもよい。より具体的には、例えば、半導体装置に対してエッチング処理を行うための装置や、レジストマスクに対してアッシングを行うための装置などを用いて酸素 431b を発生させ、絶縁膜 497 を処理して絶縁膜 407 を形成することができる。

#### 【 0216 】

酸素ドープ処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。また、酸素ドープ処理において、希ガスを用いてもよい。

30

#### 【 0217 】

絶縁膜 407 は酸素ドープ処理により、酸素を多く( 過剰 ) 含む膜( 好ましくは結晶状態における化学量論的組成に対し、酸素の含有量が過剰な領域が含まれている膜 ) であるので、酸化物半導体膜 403 に対する酸素の供給源として好適に機能させることができる。

#### 【 0218 】

酸化物半導体膜 403 に、一部( チャネル形成領域 ) が絶縁膜 407 と接した状態で熱処理を行うことが好ましい。熱処理によって絶縁膜 407 から酸化物半導体膜 403 への酸素の供給を効果的に行うことができる。

40

#### 【 0219 】

熱処理の温度は、250 以上 700 以下、または 400 以上 700 以下、または基板の歪み点未満とする。例えば、熱処理装置の一つである電気炉に基板を導入し、酸化物半導体膜に対して窒素雰囲気下 250 において 1 時間の熱処理を行う。

#### 【 0220 】

この熱処理は絶縁膜 407 の脱水化又は脱水素化処理を行う熱処理と同様の加熱方法及び加熱装置を用いることができる。

#### 【 0221 】

熱処理は、減圧下、又は窒素、酸素、超乾燥エア( C R D S ( キャビティリングダウンレーザー分光法 ) 方式の露点計を用いて測定した場合の水分量が 20 ppm ( 露点換算で -

50

55 ) 以下、好ましくは 1 ppm 以下、好ましくは 10 ppb 以下の空気)、若しくは希ガス(アルゴン、ヘリウムなど)の雰囲気下で行えばよいが、上記窒素、酸素、超乾燥エア、または希ガス等の雰囲気に水、水素などが含まれないことが好ましい。また、熱処理装置に導入する窒素、酸素、または希ガスの純度を、6N(99.9999%)以上好ましくは 7N(99.99999%)以上(即ち不純物濃度を 1 ppm 以下、好ましくは 0.1 ppm 以下)とすることが好ましい。

#### 【0222】

酸化物半導体膜 403 と酸素を過剰に含む絶縁膜 407 とを接した状態で熱処理を行うため、酸化物半導体膜 403 を構成する主成分材料の一つである酸素を、酸素を含む絶縁膜 407 より酸化物半導体膜 403 へ供給することができる。

10

#### 【0223】

また、上記熱処理は、絶縁膜 407 上に緻密性の高い無機絶縁膜を設けた後行うことが好ましい。例えば、絶縁膜 407 上にスパッタリング法により酸化アルミニウム膜を形成する。

#### 【0224】

絶縁膜 407 上に設けられる絶縁膜として用いることのできる酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を通過させない遮断効果(ブロック効果)が高い。酸化アルミニウム膜を高密度(膜密度 3.2 g/cm<sup>3</sup> 以上、好ましくは 3.6 g/cm<sup>3</sup> 以上)とすることによって、上記ブロック効果をより高めることができる。

20

#### 【0225】

従って、酸化アルミニウム膜により、酸素ドープ処理を行った絶縁膜 407 を覆い、熱処理を行うことで、絶縁膜 407 から酸化アルミニウム膜方向への酸素の放出を防止し、絶縁膜 407 から酸化物半導体膜 403 への酸素の供給を効果的に行うことができる。さらに、作製工程中及び作製後において、変動要因となる水素、水分などの不純物の酸化物半導体膜 403 への混入、及び酸化物半導体を構成する主成分材料である酸素の酸化物半導体膜 403 からの放出を防止する保護膜として機能する。

#### 【0226】

以上の工程で、トランジスタ 440c を作製する(図 3(F) 参照)。

#### 【0227】

酸化物半導体膜 403 に接するゲート絶縁膜 402 及び絶縁膜 407 に、熱処理による脱水化又は脱水素化処理を行い、かつ脱水化又は脱水素化処理後に酸素ドープ処理を行って作製されたトランジスタ 440c は、電気特性変動が抑制されており、電気的に安定である。

30

#### 【0228】

よって、安定した電気特性を有するトランジスタ 440c を作製することができる。

#### 【0229】

また、本発明の一形態は、電気特性が良好で信頼性のよいトランジスタ 440c を含む半導体装置を作製することができる。

#### 【0230】

なお、上述したように、ゲート絶縁膜及び/又は酸化物半導体膜上に接して設けられる絶縁膜は、積層構造してもよい。図 17 に、ゲート絶縁膜 402 及び絶縁膜 407 を積層構造としたトランジスタ 440d 及びトランジスタ 440e を例示する。

40

#### 【0231】

図 17(A) に示すトランジスタ 440e は、ゲート電極層 401 側から順に、ゲート絶縁膜 402a 及びゲート絶縁膜 402b が積層されたゲート絶縁膜 402 と、酸化物半導体膜 403 側から順に、絶縁膜 407a 及び絶縁膜 407b が積層された絶縁膜 407 と、を含む。

#### 【0232】

ゲート絶縁膜 402 に含まれる積層構造のうち、少なくとも酸化物半導体膜 403 と接す

50

るゲート絶縁膜402bは、脱水化又は脱水素化処理によって膜中の水素が低減され、且つ、その後の酸素ドープ処理によって酸素を過剰に含む膜であることが好ましい。同様に、絶縁膜407に含まれる積層構造のうち、少なくとも酸化物半導体膜403と接する絶縁膜407aは、脱水化又は脱水素化処理によって膜中の水素が低減され、且つ、その後の酸素ドープ処理によって酸素を過剰に含む膜であることが好ましい。これにより、酸化物半導体膜403と接する絶縁膜から酸化物半導体膜403に酸素を供給し、酸化物半導体膜403中、又は酸化物半導体膜403とそれに接する絶縁膜との界面における酸素欠損を低減することができる。

#### 【0233】

本実施の形態においては、ゲート絶縁膜402b及び絶縁膜407aとして、窒化酸化シリコン膜を用いるものとする。 10

#### 【0234】

また、絶縁膜407bは、トランジスタ440dの保護膜として機能する絶縁膜である。よって、絶縁膜407bとしては酸化アルミニウム膜を設けることが好ましい。同様に、ゲート絶縁膜402に含まれる積層構造のうち、ゲート電極層401と接する側に位置するゲート絶縁膜402aとして、酸化アルミニウム膜を設けることが好ましい。

#### 【0235】

酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を透過させない遮断（ブロッキング）効果が高い。したがって、ゲート絶縁膜402a及び絶縁膜407bとして酸化アルミニウム膜を用いることで、酸化物半導体膜403、並びにそれに接するゲート絶縁膜402b及び絶縁膜407aからの酸素の脱離を防止するとともに、酸化物半導体膜403への水及び水素の混入を防止することができる。 20

#### 【0236】

なお、酸化アルミニウム膜を高密度（膜密度 $3.2\text{ g/cm}^3$ 以上、好ましくは $3.6\text{ g/cm}^3$ 以上）とすると、トランジスタ440dに安定な電気特性を付与することができるため、より好ましい。

#### 【0237】

なお、ゲート絶縁膜402aは、ゲート絶縁膜402bへの脱水化又は脱水素化処理及びその後の酸素ドープ処理によって、ゲート絶縁膜402bと同様に膜中の水素が低減され、酸素を過剰に含む膜となり得る。又は、ゲート絶縁膜402aの脱水化又は脱水素化処理を目的とした工程を別途設けてもよいし、ゲート絶縁膜402aへの酸素ドープ処理を目的とした工程を別途設けてもよい。 30

#### 【0238】

また、絶縁膜407aへの脱水化又は脱水素化処理、及び／又はその後の酸素ドープ処理は、絶縁膜407bの形成前に行ってもよいし、絶縁膜407bを形成後に行うことも可能である。絶縁膜407bを形成後に、絶縁膜407aへの脱水化又は脱水素化処理と、酸素ドープ処理を行った場合、絶縁膜407bも同様に膜中の水素が低減され、酸素を過剰に含む膜となり得る。又は、絶縁膜407bへの脱水化又脱水素化処理を目的とした工程を別途設けてもよいし、絶縁膜407bへの酸素ドープ処理を目的とした工程を別途設けてもよい。 40

#### 【0239】

トランジスタ440dにおいて、ゲート絶縁膜402bと、絶縁膜407aと、は、ソース電極層405a及びドレイン電極層405bが存在しない領域において接している。つまり、酸化物半導体膜403は、ゲート絶縁膜402b及び絶縁膜407aに囲まれて設けられている。なお、図17（B）に示すトランジスタ440eのように、ゲート絶縁膜402aと、絶縁膜407bと、がソース電極層405a及びドレイン電極層405bが存在しない領域において接する構成としてもよい。

#### 【0240】

酸化物半導体膜403と接して、膜中の水素を低減され、酸素を過剰に含む絶縁膜を設け、その外側にブロッキング効果を有する絶縁膜（本実施の形態では酸化アルミニウム膜） 50

を設けることで、トランジスタの電気的特性をより安定化させることができる。

**【0241】**

(実施の形態4)

本実施の形態では、半導体装置及び半導体装置の作製方法の他の一形態を、図5を用いて説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

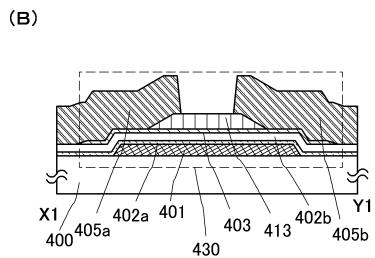

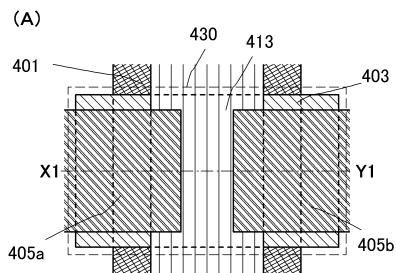

**【0242】**

図5(A)及び図5(B)に示すトランジスタ430は、チャネル保護型(チャネルトップ型ともいう)と呼ばれるボトムゲート構造の一つであり逆スタガ型トランジスタともいうトランジスタの一例である。図5(A)は平面図であり、図5(A)中の一点鎖線X1-Y1で切断した断面が図5(B)に相当する。

10

**【0243】**

トランジスタ430のチャネル長方向の断面図である図5(B)に示すように、トランジスタ430を含む半導体装置は、基板400上に、ゲート電極層401と、ゲート電極層401上にゲート絶縁膜402a、ゲート絶縁膜402b、酸化物半導体膜403、ソース電極層405a、及びドレイン電極層405bを有する。また、酸化物半導体膜403に接する絶縁層413を有する。

**【0244】**

トランジスタ430はゲート絶縁膜として積層構造のゲート絶縁膜402a、ゲート絶縁膜402bを有する例である。

20

**【0245】**

酸化物半導体膜403に接する絶縁層413は、ゲート電極層401と重畠する酸化物半導体膜403のチャネル形成領域上に設けられており、チャネル保護膜として機能する。

**【0246】**

チャネル形成領域上に重なる絶縁層413の断面形状、具体的には端部の断面形状(テープ角や膜厚など)を工夫することにより、ドレイン電極層405bの端部近傍に生じる恐れのある電界集中を緩和し、トランジスタ430のスイッチング特性の劣化を抑えることができる。

**【0247】**

30

具体的には、チャネル形成領域上に重なる絶縁層413の断面形状は、台形または三角形状とし、断面形状の下端部のテープ角を60°以下、好ましくは45°以下、さらに好ましくは30°以下とする。このような角度範囲とすることで、高いゲート電圧がゲート電極層401に印加される場合、ドレイン電極層405bの端部近傍に生じる恐れのある電界集中を緩和することができる。

**【0248】**

また、チャネル形成領域上に重なる絶縁層413の膜厚は、0.3μm以下、好ましくは5nm以上0.1μm以下とする。このような膜厚範囲とすることで、電界強度のピークを小さくできる、或いは電界集中が分散されて電界の集中する箇所が複数となり、結果的にドレイン電極層405bの端部近傍に生じる恐れのある電界集中を緩和することができる。

40

**【0249】**

以下、トランジスタ430を有する半導体装置の作製方法の一例を示す。

**【0250】**

本実施の形態のトランジスタ430は、該作製工程において、酸化物半導体膜403と接する絶縁膜(ゲート絶縁膜402b、及び/又は絶縁層413)に、熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行う。本実施の形態では、ゲート絶縁膜402b、及び絶縁層413に熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行い、作製するトランジスタ430を例として示す。熱処理による脱水化又は脱水素化処理及び酸素ドープ処理は、ゲート絶縁膜402b及び絶縁層413のどちらか

50

一方にのみ行ってもよい。

**【0251】**

絶縁表面を有する基板400上に導電膜を形成し、該導電膜をエッチングして、ゲート電極層401を形成する。本実施の形態では、スパッタリング法により膜厚100nmのタンゲステン膜を形成する。

**【0252】**

次に、ゲート電極層401上にゲート絶縁膜402a、ゲート絶縁膜402bを積層する。本実施の形態では、ゲート絶縁膜402aに窒化物絶縁膜（例えば、膜厚30nm以上50nm以下の窒化シリコン膜、窒化酸化シリコン膜）、ゲート絶縁膜402bに酸化物絶縁膜（例えば、酸化シリコン膜、酸化窒化シリコン膜）を用いる。

10

**【0253】**

本実施の形態ではゲート絶縁膜402aとしてプラズマCVD法を用いて膜厚30nmの窒化シリコン膜を形成し、ゲート絶縁膜402bとしてプラズマCVD法を用いて膜厚200nmの酸化窒化シリコン膜を形成する。

**【0254】**

ゲート絶縁膜402a、402bに熱処理による脱水化又は脱水素化処理を行う。

**【0255】**

本実施の形態では、ゲート絶縁膜402a、402bの成膜ガスとして、水素を含むガスを用いても、ゲート絶縁膜402a、402bに脱水素化処理を行うため、ゲート絶縁膜402a、402b中の水素を除去することができる。よって、プラズマCVD法を好適に用いることができる。プラズマCVD法は、成膜時に膜へごみなどが付着、混入しにくい上、比較的速い成膜速度で成膜することができるので、厚膜化が可能であり、生産性に有利である。

20

**【0256】**

熱処理の温度は、300以上700以下、または基板の歪み点未満とする。熱処理の温度は、ゲート絶縁膜402a、402bの成膜温度より高い方が、脱水化または脱水素化の効果が高いため好ましい。例えば、熱処理装置の一つである電気炉に基板を導入し、ゲート絶縁膜402a、402bに対して窒素雰囲気下450において1時間の熱処理を行う。

**【0257】**

30

熱処理によって、ゲート絶縁膜402a、402bの脱水化または脱水素化を行うことができ、トランジスタ430の特性変動を引き起こす水素、又は水などの不純物が排除されたゲート絶縁膜402a、402bを形成することができる。

**【0258】**

次に、脱水化または脱水素化されたゲート絶縁膜402a、402bに酸素ドープ処理を行い、酸素を過剰に含むゲート絶縁膜402a、402bとする。ゲート絶縁膜402a、402bに酸素ドープ処理を行うことにより、酸素をゲート絶縁膜402a、402bに供給して、ゲート絶縁膜402a、402b中、又はゲート絶縁膜402a、402b中及び該界面近傍に酸素を含有させる。

**【0259】**

40

酸素ドープ処理は、少なくとも酸化物半導体膜403と接するゲート絶縁膜402bに行えばよく、ゲート絶縁膜402aには必ずしも行わなくてもよい。

**【0260】**

ゲート絶縁膜402a、402b上に酸化物半導体膜403を形成する。本実施の形態において、酸化物半導体膜403として、AC電源装置を有するスパッタリング装置を用いたスパッタリング法を用い、膜厚35nmのIn-Ga-Zn系酸化物膜（IGZO膜）を成膜する。本実施の形態において、In:Ga:Zn = 1:1:1 (= 1/3:1/3:1/3) の原子比のIn-Ga-Zn系酸化物ターゲットを用いる。なお、成膜条件は、酸素及びアルゴン雰囲気下（酸素流量比率50%）、圧力0.6Pa、電源電力5kW、基板温度170とする。この成膜条件での成膜速度は、16nm/minである。

50

**【0261】**

酸化物半導体膜403と接するゲート絶縁膜402bは、酸素の供給源となる酸素を多く（過剰に）含むので、該ゲート絶縁膜402bから酸化物半導体膜403へ酸素を供給することができる。

**【0262】**

酸化物半導体膜403とゲート絶縁膜402bとを接した状態で熱処理を行うことが好ましい。熱処理によってゲート絶縁膜402bから酸化物半導体膜403への酸素の供給を効果的に行うことができる。

**【0263】**

酸化物半導体膜403へ酸素を供給することにより、酸化物半導体膜403中の酸素欠損を補填することができる。10

**【0264】**

酸素ドープ処理を行ったゲート絶縁膜402bから酸化物半導体膜403へ酸素の供給を行うための熱処理は、この後に行われる熱処理と兼ねてもよい。例えば、絶縁層413の脱水化又は脱水素化のための熱処理、酸素ドープ処理を行った絶縁層413から酸化物半導体膜403へ酸素の供給を行う熱処理と兼ねることができる。

**【0265】**

次にゲート電極層401と重畳する酸化物半導体膜403のチャネル形成領域上に絶縁層413となる絶縁膜を形成する。20

**【0266】**

絶縁層413となる絶縁膜はプラズマCVD法、スパッタリング法により成膜した絶縁膜をエッチングにより加工して形成することができる。絶縁層413として、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ハフニウム膜、又は酸化ガリウム膜、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜、酸化アルミニウム膜などの無機絶縁膜の単層又は積層を用いることができる。

**【0267】**

本実施の形態では、酸化物半導体膜403上に、酸化物半導体膜403と接して、絶縁膜として、プラズマCVD法により膜厚200nmの酸化窒化シリコン膜を形成する。

**【0268】**

絶縁膜に熱処理による脱水化又は脱水素化処理を行う。30

**【0269】**

本実施の形態では、絶縁膜の成膜ガスとして、水素を含むガスを用いても、絶縁膜に脱水素化処理を行うため、絶縁膜中の水素を除去することができる。よって、プラズマCVD法を好適に用いることができる。プラズマCVD法は、成膜時に膜へごみなどが付着、混入しにくい上、比較的速い成膜速度で成膜することができるので、厚膜化が可能であり、生産性に有利である。

**【0270】**

熱処理の温度は、300以上700以下、または基板の歪み点未満とする。熱処理の温度は、絶縁膜の成膜温度より高い方が、脱水化または脱水素化の効果が高いため好ましい。例えば、熱処理装置の一つである電気炉に基板を導入し、絶縁膜に対して窒素雰囲気下450において1時間の熱処理を行う。40

**【0271】**

熱処理によって、絶縁膜の脱水化または脱水素化を行うことができ、水素、又は水などの不純物が排除された絶縁膜を形成することができる。

**【0272】**

脱水素化又は脱水素化のための熱処理を行うことにより、絶縁膜に含まれる、水、水素等の不純物を除去し、低減させることができる。絶縁膜をできるだけ水素を含まない膜とすることで、トランジスタ430の特性変動を抑制し、安定した電気特性を付与することができる。50

## 【0273】

次に、脱水化または脱水素化された絶縁膜に酸素ドープ処理を行い、酸素を過剰に含む絶縁膜を形成する。

## 【0274】

絶縁膜は酸素ドープ処理により、酸素を多く（過剰）含む膜（好ましくは結晶状態における化学量論的組成に対し、酸素の含有量が過剰な領域が含まれている膜）であるので、酸化物半導体膜403に対する酸素の供給源として好適に機能させることができる。

## 【0275】

酸化物半導体膜403に絶縁膜と接した状態で熱処理を行うことが好ましい。熱処理によって絶縁膜から酸化物半導体膜403への酸素の供給を効果的に行うことができる。本実施の形態では、窒素雰囲気下300°で1時間熱処理を行う。

10

## 【0276】

絶縁膜を選択的にエッチングして、断面形状が台形または三角形状であり、断面形状の下端部のテーパ角が60°以下、好ましくは45°以下、さらに好ましくは30°以下の絶縁層413を形成する。なお、絶縁層413の平面形状は矩形である。なお、本実施の形態では、フォトリソグラフィ工程により酸化窒化シリコン膜上にレジストマスクを形成し、選択的にエッチングを行って絶縁層413の下端部のテーパ角を約30°とする。

## 【0277】

次いで、ゲート電極層401、ゲート絶縁膜402a、402b、酸化物半導体膜403、及び絶縁層413上に、ソース電極層及びドレイン電極層となる導電膜を形成する。

20

## 【0278】

本実施の形態では、導電膜としてスパッタリング法により形成した膜厚100nmのチタン膜、膜厚400nmのアルミニウム膜、膜厚100nmのチタン膜の積層の導電膜を用いる。導電膜のエッチングは、ドライエッチング法により、チタン膜、アルミニウム膜、チタン膜の積層をエッチングして、ソース電極層405a、ドレイン電極層405bを形成する。

## 【0279】

本実施の形態では、第1のエッチング条件でチタン膜とアルミニウム膜の2層をエッチングした後、第2のエッチング条件で残りのチタン膜単層を除去する。なお、第1のエッチング条件は、エッチングガス（BCl<sub>3</sub> : Cl<sub>2</sub> = 750 sccm : 150 sccm）を用い、バイアス電力を1500Wとし、ICP電源電力を0Wとし、圧力を2.0Paとする。第2のエッチング条件は、エッチングガス（BCl<sub>3</sub> : Cl<sub>2</sub> = 700 sccm : 100 sccm）を用い、バイアス電力を750Wとし、ICP電源電力を0Wとし、圧力を2.0Paとする。

30

## 【0280】

以上の工程で、本実施の形態のトランジスタ430が作製される。

## 【0281】

ソース電極層405a、ドレイン電極層405b上に絶縁膜を形成してもよい。

## 【0282】

絶縁膜は、絶縁層413と同様な材料及び方法を用いて形成することができる。例えば、CVD法により形成した酸化窒化シリコン膜を400nm形成する。また、絶縁膜の形成後、熱処理を行ってもよい。例えば、窒素雰囲気下300°で1時間熱処理を行う。

40

## 【0283】

また、トランジスタ430起因の表面凹凸を低減するために平坦化絶縁膜を形成してもよい。

## 【0284】

例えば、絶縁膜上に平坦化絶縁膜として、膜厚1500nmのアクリル樹脂膜を形成すればよい。アクリル樹脂膜は塗布法による塗布後、焼成（例えば窒素雰囲気下250°1時間）して形成することができる。

## 【0285】

50

平坦化絶縁膜を形成後、熱処理を行ってもよい。例えば、窒素雰囲気下 250 で 1 時間熱処理を行う。

【0286】

酸化物半導体膜 403 に接するゲート絶縁膜 402b 及び / 又は絶縁層 413 に、熱処理による脱水化又は脱水素化処理を行い、かつ脱水化又は脱水素化処理後に酸素ドープ処理を行って作製されたトランジスタ 430 は、電気特性変動が抑制されており、電気的に安定である。

【0287】

よって、安定した電気特性を有するトランジスタ 430 を作製することができる。

【0288】

また、本発明の一形態は、電気特性が良好で信頼性のよいトランジスタ 430 を含む半導体装置を作製することができる。

10

【0289】

(実施の形態 5)

本実施の形態では、半導体装置及び半導体装置の作製方法の他の一形態を、図 6 を用いて説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

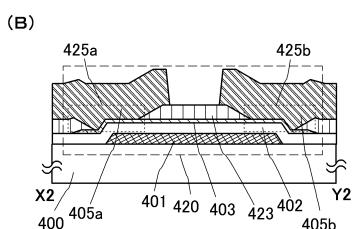

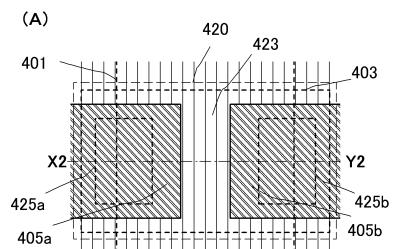

【0290】

図 6 (A) 及び (B) に示すトランジスタ 420 は、チャネル保護型 (チャネルトップ型ともいう) と呼ばれるボトムゲート構造の一つであり逆スタガ型トランジスタともいうトランジスタの一例である。図 6 (A) は平面図であり、図 6 (A) 中の一点鎖線 X2-Y2 で切断した断面が図 6 (B) に相当する。

20

【0291】

チャネル長方向の断面図である図 6 (B) に示すように、トランジスタ 420 を含む半導体装置は、基板 400 上に、ゲート電極層 401 と、ゲート電極層 401 上にゲート絶縁膜 402、酸化物半導体膜 403、絶縁層 423、ソース電極層 405a、ドレイン電極層 405b を有する。

【0292】

絶縁層 423 は、少なくともゲート電極層 401 と重畠する酸化物半導体膜 403 のチャネル形成領域上を含めた酸化物半導体膜 403 上に設けられており、チャネル保護膜として機能する。さらに、絶縁層 423 は、酸化物半導体膜 403 に達し、かつソース電極層 405a 又はドレイン電極層 405b が内壁を覆うように設けられた開口 425a、425b を有している。従って、酸化物半導体膜 403 の周縁部は、絶縁層 423 で覆われてあり、層間絶縁膜としても機能している。ゲート配線とソース配線の交差部において、ゲート絶縁膜 402 だけでなく、絶縁層 423 も層間絶縁膜として配置することで寄生容量を低減できる。

30

【0293】

トランジスタ 420 において、酸化物半導体膜 403 は、絶縁層 423、ソース電極層 405a、及びドレイン電極層 405b に覆われる構成となっている。

40

【0294】

絶縁層 423 はプラズマ CVD 法、スパッタリング法により成膜した絶縁膜をエッチングにより加工して形成することができる。また、絶縁層 423 の開口 425a、425b の内壁は、テーパ形状を有している。

【0295】

絶縁層 423 は、少なくともゲート電極層 401 と重畠する酸化物半導体膜 403 のチャネル形成領域上を含めた酸化物半導体膜 403 上に設けられており、一部がチャネル保護膜として機能する。

【0296】

本実施の形態のトランジスタ 420 は、該作製工程において、酸化物半導体膜 403 と接

50

する絶縁膜（ゲート絶縁膜402、及び／又は絶縁層423）に、熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行う。本実施の形態では、ゲート絶縁膜402及び絶縁層423に熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行い、作製するトランジスタ420を例として示す。熱処理による脱水化又は脱水素化処理及び酸素ドープ処理は、ゲート絶縁膜402及び絶縁層423のどちらか一方にのみ行ってもよい。

#### 【0297】

よって、酸化物半導体膜403には、トランジスタ420の特性変動を引き起こす水素、又は水などの不純物が混入せず、かつ酸素欠損を補填する酸素が供給される。

#### 【0298】

酸化物半導体膜403に接するゲート絶縁膜402及び／又は絶縁層423に、熱処理による脱水化又は脱水素化処理を行い、かつ脱水化又は脱水素化処理後に酸素ドープ処理を行って作製されたトランジスタ420は、電気特性変動が抑制されており、電気的に安定である。

#### 【0299】

よって、安定した電気特性を有するトランジスタ420を作製することができる。

#### 【0300】

また、本発明の一形態は、電気特性が良好で信頼性のよいトランジスタ420を含む半導体装置を作製することができる。

#### 【0301】

##### (実施の形態6)

本実施の形態では、半導体装置及び半導体装置の作製方法の他の一形態を、図7を用いて説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

#### 【0302】

図7(A)及び図7(B)に示すトランジスタ410は、ボトムゲート構造のトランジスタの一例である。図7(A)は平面図であり、図7(A)中の一点鎖線Q-Rで切断した断面が図7(B)に相当する。

#### 【0303】

トランジスタ410のチャネル長方向の断面図である図7(B)に示すように、トランジスタ410を含む半導体装置は、基板400上に、ゲート電極層401と、ゲート電極層401上にゲート絶縁膜402、ソース電極層405a、ドレイン電極層405b、及び酸化物半導体膜403を有する。また、酸化物半導体膜403に接し、トランジスタ410を覆う絶縁膜407を有する。

#### 【0304】

以下、トランジスタ410を有する半導体装置の作製方法の一例を示す。

#### 【0305】

本実施の形態のトランジスタ410は、該作製工程において、酸化物半導体膜403と接する絶縁膜（ゲート絶縁膜402、及び／又は絶縁膜407）に、熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行う。本実施の形態では、ゲート絶縁膜402及び絶縁膜407に熱処理による脱水化又は脱水素化処理を行った後、酸素ドープ処理を行い、作製するトランジスタ410を例として示す。熱処理による脱水化又は脱水素化処理及び酸素ドープ処理は、ゲート絶縁膜402及び絶縁膜407のどちらか一方にのみ行ってもよい。

#### 【0306】

絶縁表面を有する基板400上に導電膜を形成し、該導電膜をエッチングして、ゲート電極層401を形成する。本実施の形態では、スパッタリング法により膜厚100nmのタンゲステン膜を形成する。

#### 【0307】

10

20

30

40

50

次に、ゲート電極層 401 上にゲート絶縁膜 402 を形成する。本実施の形態では、プラズマ CVD 法により膜厚 200 nm の酸化窒化シリコン膜を形成する。

【0308】

ゲート絶縁膜 402 に熱処理による脱水化又は脱水素化処理を行う。

【0309】

本実施の形態では、ゲート絶縁膜 402 の成膜ガスとして、水素を含むガスを用いても、ゲート絶縁膜 402 に脱水素化処理を行うため、ゲート絶縁膜 402 中の水素を除去することができる。よって、プラズマ CVD 法を好適に用いることができる。プラズマ CVD 法は、成膜時に膜へごみなどが付着、混入しにくい上、比較的速い成膜速度で成膜することができるるので、厚膜化が可能であり、生産性に有利である。

10

【0310】

熱処理の温度は、300 以上 700 以下、または基板の歪み点未満とする。熱処理の温度は、ゲート絶縁膜 402 の成膜温度より高い方が、脱水化または脱水素化の効果が高いため好ましい。例えば、熱処理装置の一つである電気炉に基板を導入し、ゲート絶縁膜 402 に対して窒素雰囲気下 450 において 1 時間の熱処理を行う。

【0311】

熱処理によって、ゲート絶縁膜 402 の脱水化または脱水素化を行うことができ、トランジスタ 410 の特性変動を引き起こす水素、又は水などの不純物が排除されたゲート絶縁膜 402 を形成することができる。

【0312】

次に、脱水化または脱水素化されたゲート絶縁膜 402 に酸素ドープ処理を行い、酸素を過剰に含むゲート絶縁膜 402 とする。ゲート絶縁膜 402 に酸素ドープ処理を行うことにより、酸素をゲート絶縁膜 402 に供給して、ゲート絶縁膜 402 中、又はゲート絶縁膜 402 中及び後工程でゲート絶縁膜 402 上に形成される酸化物半導体膜 403 との界面近傍に酸素を含有させる。

20

【0313】

次いで、ゲート電極層 401、ゲート絶縁膜 402 上に、ソース電極層及びドレイン電極層となる導電膜を形成する。

【0314】

本実施の形態では、導電膜としてスパッタリング法により形成した膜厚 100 nm のタンゲステン膜を用いる。ドライエッチング法により導電膜をエッチングして、ソース電極層 405a、及びドレイン電極層 405b を形成する。

30

【0315】

ソース電極層 405a、及びドレイン電極層 405b 上に酸化物半導体膜 403 を形成する。本実施の形態において、酸化物半導体膜 403 として、AC 電源装置を有するスパッタリング装置を用いたスパッタリング法を用い、膜厚 35 nm の In - Ga - Zn 系酸化物膜 (IGZO 膜) を成膜する。本実施の形態において、In : Ga : Zn = 1 : 1 : 1 (= 1 / 3 : 1 / 3 : 1 / 3) の原子比の In - Ga - Zn 系酸化物ターゲットを用いる。なお、成膜条件は、酸素及びアルゴン雰囲気下 (酸素流量比率 50%)、圧力 0.6 Pa、電源電力 5 kW、基板温度 170 とする。この成膜条件での成膜速度は、16 nm / min である。

40

【0316】

酸化物半導体膜 403 と接するゲート絶縁膜 402 は、酸素の供給源となる酸素を多く (過剰に) 含むので、該ゲート絶縁膜 402 から酸化物半導体膜 403 へ酸素を供給することができる。

【0317】

酸化物半導体膜 403 とゲート絶縁膜 402 とを接した状態で熱処理を行うことが好ましい。熱処理によってゲート絶縁膜 402 から酸化物半導体膜 403 への酸素の供給を効果的に行うことができる。

【0318】

50

酸化物半導体膜403へ酸素を供給することにより、酸化物半導体膜403中の酸素欠損を補填することができる。

【0319】

酸素ドープ処理を行ったゲート絶縁膜402から酸化物半導体膜403へ酸素の供給を行うための熱処理は、この後に行われる熱処理と兼ねてもよい。例えば、絶縁膜407の脱水化又は脱水素化のための熱処理、酸素ドープ処理を行った絶縁膜407から酸化物半導体膜403へ酸素の供給を行う熱処理と兼ねることができる。

【0320】

本実施の形態では、酸化物半導体膜403上に、酸化物半導体膜403と接して、絶縁膜407を形成する。

10

【0321】

本実施の形態では、絶縁膜407として、プラズマCVD法により膜厚400nmの酸化窒化シリコン膜を形成する。

【0322】

絶縁膜407に熱処理による脱水化又は脱水素化処理を行う。

【0323】

本実施の形態では、絶縁膜407の成膜ガスとして、水素を含むガスを用いても、絶縁膜407に脱水素化処理を行うため、絶縁膜407中の水素を除去することができる。よって、プラズマCVD法を好適に用いることができる。プラズマCVD法は、成膜時に膜へごみなどが付着、混入しにくい上、比較的速い成膜速度で成膜することができるので、厚膜化が可能であり、生産性に有利である。

20

【0324】

熱処理の温度は、300以上700以下、または基板の歪み点未満とする。熱処理の温度は、絶縁膜407の成膜温度より高い方が、脱水化または脱水素化の効果が高いため好ましい。例えば、熱処理装置の一つである電気炉に基板を導入し、絶縁膜407に対して窒素雰囲気下450において1時間の熱処理を行う。

【0325】

熱処理によって、絶縁膜407の脱水化または脱水素化を行うことができ、水素、又は水などの不純物が排除された絶縁膜を形成することができる。

30

【0326】

脱水素化又は脱水化のための熱処理を行うことにより、絶縁膜407に含まれる、水、水素等の不純物を除去し、低減させることができる。絶縁膜407をできるだけ水素を含まない膜として、トランジスタ410の特性変動を抑制し、安定した電気特性を付与することができる。

【0327】

次に、脱水化または脱水素化された絶縁膜407に酸素ドープ処理を行い、酸素を過剰に含む絶縁膜407を形成する。

【0328】

絶縁膜407は酸素ドープ処理により、酸素を多く（過剰）含む膜（好ましくは結晶状態における化学量論的組成に対し、酸素の含有量が過剰な領域が含まれている膜）であるので、酸化物半導体膜403に対する酸素の供給源として好適に機能させることができる。

40

【0329】

酸化物半導体膜403に絶縁膜407と接した状態で熱処理を行うことが好ましい。熱処理によって絶縁膜407から酸化物半導体膜403への酸素の供給を効果的に行うことができる。本実施の形態では、窒素雰囲気下300で1時間熱処理を行う。

【0330】

また、上記熱処理は、絶縁膜407上に緻密性の高い無機絶縁膜を設けた後行うことが好ましい。例えば、絶縁膜407上にスパッタリング法により酸化アルミニウム膜を形成する。

【0331】

50

以上の工程で、本実施の形態のトランジスタ410が作製される。

【0332】

また、トランジスタ410起因の表面凹凸を低減するために平坦化絶縁膜を形成してもよい。

【0333】

例えば、絶縁膜上に平坦化絶縁膜として、膜厚1500nmのアクリル樹脂膜を形成すればよい。アクリル樹脂膜は塗布法による塗布後、焼成（例えば窒素雰囲気下250℃で1時間）して形成することができる。

【0334】

平坦化絶縁膜を形成後、熱処理を行ってもよい。例えば、窒素雰囲気下250℃で1時間熱処理を行う。

【0335】

酸化物半導体膜403に接するゲート絶縁膜402及び/又は絶縁膜407に、熱処理による脱水化又は脱水素化処理を行い、かつ脱水化又は脱水素化処理後に酸素ドープ処理を行って作製されたトランジスタ410は、電気特性変動が抑制されており、電気的に安定である。

【0336】

よって、安定した電気特性を有するトランジスタ410を作製することができる。

【0337】

また、本発明の一形態は、電気特性が良好で信頼性のよいトランジスタ410を含む半導体装置を作製することができる。

【0338】

(実施の形態7)

本実施の形態では、半導体装置の作製方法の他の一形態を説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0339】

本実施の形態では、熱処理による脱水化又は脱水素化処理を行う前の、酸化物半導体膜と接する絶縁膜にも、酸素ドープ処理を行う例を示す。

【0340】

なお、酸化物半導体膜と接する絶縁膜とは、実施の形態1乃至6においてはゲート絶縁膜402、絶縁膜407、絶縁層413、絶縁層423である。本実施の形態は、実施の形態1乃至6におけるトランジスタ440a、440b、440c、430、420、410に適用することができる。

【0341】

熱処理による脱水化又は脱水素化処理を行う前の絶縁膜にも、酸素ドープ処理を行っておいてもよい。絶縁膜に酸素ドープ処理と熱処理とを複数回繰り返し行ってもよい。絶縁膜に対して、熱処理の前に酸素ドープ処理を行うと、絶縁膜の脱水化又は脱水素化処理を効果的に行うことができる。

【0342】

酸化物半導体膜と接する絶縁膜に酸素をドープすることにより、絶縁膜を構成している元素（例えば金属元素）と水素との間の結合が切断され、後に行われる熱処理により不純物である水素を絶縁膜から脱離させやすくすることができる。さらに、酸素のドープによって膜中にボイド（欠陥）が形成されるため、結合が切断された水素は、該ボイドを通じて容易に膜中から脱離することができる。

【0343】

また、水素の脱離は、絶縁膜に酸素をドープすることにより、絶縁膜を構成している元素（例えば金属元素）と水酸基との間の結合も切断されるため、結合が切断された水素と水酸基が結合し、水として絶縁膜中から脱離する場合もある。

【0344】

10

20

30

40

50

ドープされる酸素（酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン（酸素分子イオン）、及び／又は酸素クラスタイオン）は、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。また、イオン注入法にはガスクラスタイオンビームを用いてもよい。

#### 【0345】

例えば、ドープされる酸素（酸素ラジカル、酸素原子、酸素分子、オゾン、酸素イオン（酸素分子イオン）、及び／又は酸素クラスタイオン）は、酸素を含むガスを用いてプラズマ発生装置により供給されてもよいし、又はオゾン発生装置により供給されてもよい。より具体的には、例えば、半導体装置に対してエッチング処理を行うための装置や、レジストマスクに対してアッシングを行うための装置などを用いて酸素を発生させ、絶縁膜を処理してもよい。10

#### 【0346】

酸素ドープ処理には、酸素を含むガスを用いることができる。酸素を含むガスとしては、酸素、一酸化二窒素、二酸化窒素、二酸化炭素、一酸化炭素などを用いることができる。

#### 【0347】

また、脱水化又は脱水素化処理のための熱処理の前にドープする元素として希ガスを用いてもよい。

#### 【0348】

希ガスは上記酸素を含むガス中に混合して用いてもよいし、希ガスドープ処理と、酸素ドープ処理を両方用いてもよい。20

#### 【0349】

絶縁膜に酸素ドープ処理と脱水化又は脱水素化処理のための熱処理とを複数回繰り返し行ってもよい。絶縁膜に対して、脱水化又は脱水素化処理のための熱処理の前に酸素ドープ処理を行うと、絶縁膜の脱水化又は脱水素化処理を効果的に行うことができる。

#### 【0350】

よって、安定した電気特性を有するトランジスタを作製することができる。

#### 【0351】

また、本発明の一形態は、電気特性が良好で信頼性のよいトランジスタを含む半導体装置を作製することができる。

#### 【0352】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。30

#### 【0353】

##### （実施の形態8）

実施の形態1乃至7のいずれかに示したトランジスタを用いて表示機能を有する半導体装置（表示装置ともいう）を作製することができる。また、トランジスタを含む駆動回路の一部又は全体を、画素部と同じ基板上に一体形成し、システムオンパネルを形成することができる。

#### 【0354】

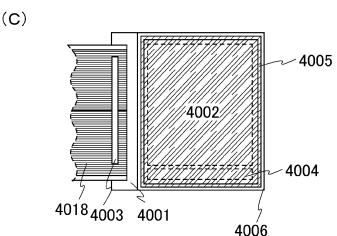

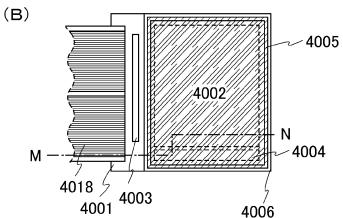

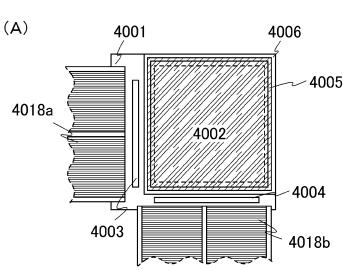

図8(A)において、基板4001上に設けられた画素部4002を囲むようにして、シール材4005が設けられ、基板4006によって封止されている。図8(A)においては、基板4001上のシール材4005によって囲まれている領域とは異なる領域に、ICチップ、又は別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された走査線駆動回路4004、信号線駆動回路4003が実装されている。また別途形成された信号線駆動回路4003と、走査線駆動回路4004又は画素部4002に与えられる各種信号及び電位は、FPC(Flexible printed circuit)4018a、4018bから供給されている。40

#### 【0355】

図8(B)、及び図8(C)において、基板4001上に設けられた画素部4002と、走査線駆動回路4004とを囲むようにして、シール材4005が設けられている。また50

画素部 4002 と、走査線駆動回路 4004 の上に基板 4006 が設けられている。よって画素部 4002 と、走査線駆動回路 4004 とは、基板 4001 とシール材 4005 と基板 4006 とによって、表示素子と共に封止されている。図 8 (B)、及び (C) においては、基板 4001 上のシール材 4005 によって囲まれている領域とは異なる領域に、IC チップ、又は別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路 4003 が実装されている。図 8 (B)、及び 図 8 (C) においては、別途形成された信号線駆動回路 4003 と、走査線駆動回路 4004 又は画素部 4002 に与えられる各種信号及び電位は、FPC 4018 から供給されている。

#### 【0356】

また図 8 (B)、及び図 8 (C) においては、信号線駆動回路 4003 を別途形成し、基板 4001 に実装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して実装してもよいし、信号線駆動回路の一部又は走査線駆動回路の一部のみを別途形成して実装してもよい。10

#### 【0357】

なお、別途形成した駆動回路の接続方法は、特に限定されるものではなく、COG (Chip On Glass) 方法、ワイヤボンディング方法、或いは TAB (Tape Automated Bonding) 方法などを用いることができる。図 8 (A) は、COG 方法により信号線駆動回路 4003、走査線駆動回路 4004 を実装する例であり、図 8 (B) は、COG 方法により信号線駆動回路 4003 を実装する例であり、図 8 (C) は、TAB 方法により信号線駆動回路 4003 を実装する例である。20

#### 【0358】

また、表示装置は、表示素子が封止された状態にあるパネルと、該パネルにコントローラを含む IC 等を実装した状態にあるモジュールとを含む。

#### 【0359】

なお、本明細書中における表示装置とは、画像表示デバイス、表示デバイス、もしくは光源（照明装置含む）を指す。また、コネクター、例えば FPC もしくは TAB テープもしくは TCFP が取り付けられたモジュール、TAB テープや TCFP の先にプリント配線板が設けられたモジュール、又は表示素子に COG 方式により IC（集積回路）が直接実装されたモジュールも全て表示装置に含むものとする。

#### 【0360】

また基板上に設けられた画素部及び走査線駆動回路は、トランジスタを複数有しており、実施の形態 1 乃至 7 のいずれかに示したトランジスタを適用することができる。30

#### 【0361】

表示装置に設けられる表示素子としては液晶素子（液晶表示素子ともいう）、発光素子（発光表示素子ともいう）、を用いることができる。発光素子は、電流又は電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機 EL（Electro Luminescence）、有機 EL 等が含まれる。また、電子インクなど、電気的作用によりコントラストが変化する表示媒体も適用することができる。

#### 【0362】

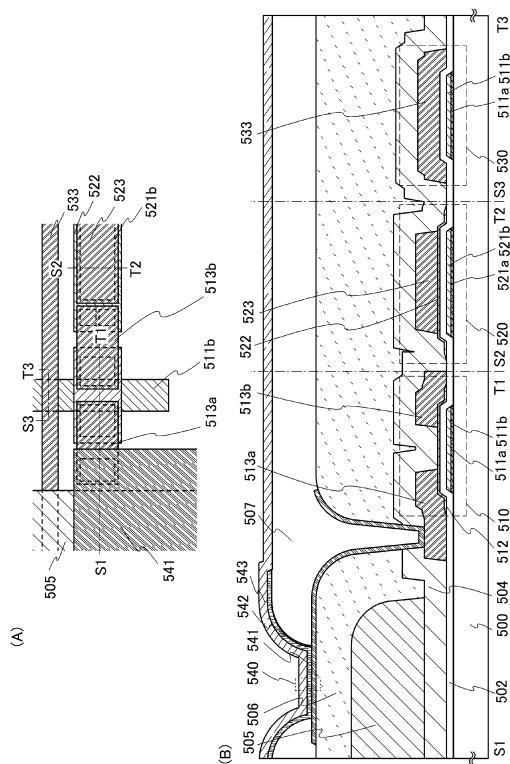

また、半導体装置の一形態について、図 8 乃至 図 10 を用いて説明する。図 10 は、図 8 (B) の M - N における断面図に相当する。40

#### 【0363】

図 8 及び図 10 で示すように、半導体装置は接続端子電極 4015 及び端子電極 4016 を有しており、接続端子電極 4015 及び端子電極 4016 は FPC 4018 (FPC 4018a、4018b) が有する端子と異方性導電膜 4019 を介して、電気的に接続されている。

#### 【0364】

接続端子電極 4015 は、第 1 の電極層 4030 と同じ導電膜から形成され、端子電極 4016 は、トランジスタ 4040、4011 のソース電極層及びドレイン電極層と同じ導電膜で形成されている。50

**【0365】**

また基板4001上に設けられた画素部4002と、走査線駆動回路4004は、トランジスタを複数有しており、図8及び図10では、画素部4002に含まれるトランジスタ4040と、走査線駆動回路4004に含まれるトランジスタ4011とを例示している。図10(A)では、トランジスタ4040、4011上には絶縁膜4020が設けられ、図10(B)では、さらに、絶縁膜4021が設けられている。

**【0366】**

トランジスタ4010、4011としては、実施の形態1乃至7のいずれかに示したトランジスタを適用することができる。本実施の形態では、実施の形態1で示したトランジスタ440と同様な構造を有するトランジスタを適用する例を示す。トランジスタ4010、4011は、ボトムゲート構造のスタガ型トランジスタである。10

**【0367】**

トランジスタ4010、4011は、酸化物半導体膜に接するゲート絶縁膜及び/又は絶縁膜4020に、熱処理による脱水化又は脱水素化処理を行い、かつ脱水化又は脱水素化処理後に酸素ドープ処理を行って作製されたトランジスタである。よって、酸化物半導体膜には、トランジスタ4010、4011の特性変動を引き起こす水素、又は水などの不純物が混入せず、かつ酸素欠損を補填する酸素が供給される。よって、トランジスタ4010、4011は、電気特性変動が抑制されている。

**【0368】**

従って、図8及び図10で示す本実施の形態の酸化物半導体膜を用いた安定した電気特性を有するトランジスタ4010、4011を含む半導体装置として信頼性の高い半導体装置を提供することができる。20

**【0369】**

また、駆動回路用のトランジスタ4011の酸化物半導体膜のチャネル形成領域と重なる位置にさらに導電層を設けてもよい。導電層を酸化物半導体膜のチャネル形成領域と重なる位置に設けることによって、バイアス-熱ストレス試験(BT試験)前後におけるトランジスタ4011のしきい値電圧の変化量をさらに低減することができる。また、導電層は、電位がトランジスタ4011のゲート電極層と同じでもよいし、異なっていても良く、第2のゲート電極層として機能させることもできる。また、導電層の電位がGND、0V、或いはフローティング状態であってもよい。30

**【0370】**

また、該導電層は外部の電場を遮蔽する、すなわち外部の電場が内部(トランジスタを含む回路部)に作用しないようにする機能(特に静電気に対する静電遮蔽機能)も有する。導電層の遮蔽機能により、静電気などの外部の電場の影響によりトランジスタの電気的な特性が変動することを防止することができる。

**【0371】**

画素部4002に設けられたトランジスタ4010は表示素子と電気的に接続し、表示パネルを構成する。表示素子は表示を行うことができれば特に限定されず、様々な表示素子を用いることができる。

**【0372】**

図10(A)に表示素子として液晶素子を用いた液晶表示装置の例を示す。図10(A)において、表示素子である液晶素子4013は、第1の電極層4030、第2の電極層4031、及び液晶層4008を含む。なお、液晶層4008を挟持するように配向膜として機能する絶縁膜4032、4033が設けられている。第2の電極層4031は基板4006側に設けられ、第1の電極層4030と第2の電極層4031とは液晶層4008を介して積層する構成となっている。

**【0373】**

またスペーサ4035は絶縁膜を選択的にエッチングすることで得られる柱状のスペーサであり、液晶層4008の膜厚(セルギャップ)を制御するために設けられている。なお球状のスペーサを用いていてもよい。

1020304050

## 【0374】

表示素子として、液晶素子を用いる場合、サーモトロピック液晶、低分子液晶、高分子液晶、高分子分散型液晶、強誘電性液晶、反強誘電性液晶等を用いることができる。これらの液晶材料（液晶組成物）は、条件により、コレステリック相、スメクチック相、キュービック相、カイラルネマチック相、等方相等を示す。

## 【0375】

また、液晶層4008に、配向膜を用いないブルー相を発現する液晶組成物を用いてもよい。この場合、液晶層4008と、第1の電極層4030及び第2の電極層4031とは接する構造となる。ブルー相は液晶相の一つであり、コレステリック液晶を昇温していくと、コレステリック相から等方相へ転移する直前に発現する相である。ブルー相は、液晶及びカイラル剤を混合させた液晶組成物を用いて発現させることができる。また、ブルー相が発現する温度範囲を広げるために、ブルー相を発現する液晶組成物に重合性モノマー及び重合開始剤などを添加し、高分子安定化させる処理を行って液晶層を形成することもできる。ブルー相を発現する液晶組成物は、応答速度が短く、光学的等方性であるため配向処理が不要であり、視野角依存性が小さい。また配向膜を設けなくてもよいのでラビング処理も不要となるため、ラビング処理によって引き起こされる静電破壊を防止することができ、作製工程中の液晶表示装置の不良や破損を軽減することができる。よって液晶表示装置の生産性を向上させることができるとなる。酸化物半導体膜を用いるトランジスタは、静電気の影響によりトランジスタの電気的な特性が著しく変動して設計範囲を逸脱する恐れがある。よって酸化物半導体膜を用いるトランジスタを有する液晶表示装置にブルー相を発現する液晶組成物を用いることはより効果的である。10

## 【0376】

また、液晶材料の固有抵抗は、 $1 \times 10^9 \text{ } \cdot \text{cm}$ 以上であり、好ましくは $1 \times 10^{11} \text{ } \cdot \text{cm}$ 以上であり、さらに好ましくは $1 \times 10^{12} \text{ } \cdot \text{cm}$ 以上である。なお、本明細書における固有抵抗の値は、20で測定した値とする。20

## 【0377】

液晶表示装置に設けられる保持容量の大きさは、画素部に配置されるトランジスタのリーク電流等を考慮して、所定の期間の間電荷を保持できるように設定される。保持容量の大きさは、トランジスタのオフ電流等を考慮して設定すればよい。本明細書に開示する酸化物半導体膜を有するトランジスタを用いることにより、各画素における液晶容量に対して1/3以下、好ましくは1/5以下の容量の大きさを有する保持容量を設ければ充分である。30

## 【0378】

本明細書に開示する酸化物半導体膜を用いたトランジスタは、オフ状態における電流値（オフ電流値）を低く制御することができる。よって、画像信号等の電気信号の保持時間を長くすることができ、電源オン状態では書き込み間隔も長く設定できる。よって、リフレッシュ動作の頻度を少なくすることができるため、消費電力を抑制する効果を奏する。

## 【0379】

また、本明細書に開示する酸化物半導体膜を用いたトランジスタは、比較的高い電界効果移動度が得られるため、高速駆動が可能である。例えば、このような高速駆動が可能なトランジスタを液晶表示装置に用いることで、画素部のスイッチングトランジスタと、駆動回路部に使用するドライバートランジスタを同一基板上に形成することができる。すなわち、別途駆動回路として、シリコンウェハ等により形成された半導体装置を用いる必要がないため、半導体装置の部品点数を削減することができる。また、画素部においても、高速駆動が可能なトランジスタを用いることで、高画質な画像を提供することができる。40

## 【0380】

液晶表示装置には、TN（Twisted Nematic）モード、IPS（In-Plane-Switching）モード、FFS（Fringe Field Switching）モード、ASM（Axially Symmetric aligned Micro-cell）モード、OCB（Optical Compensated B

i r e f r i n g e n c e) モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モードなどを用いることができる。

#### 【0381】

また、ノーマリーブラック型の液晶表示装置、例えば垂直配向(VA)モードを採用した透過型の液晶表示装置としてもよい。垂直配向モードとしては、いくつか挙げられるが、例えば、MVA(Multi-Domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASV(Advanced Super View)モードなどを用いることができる。また、VA型の液晶表示装置にも適用することができる。VA型の液晶表示装置とは、液晶表示パネルの液晶分子の配列を制御する方式の一種である。VA型の液晶表示装置は、電圧が印加されていないときにパネル面に対して液晶分子が垂直方向を向く方式である。また、画素(ピクセル)をいくつかの領域(サブピクセル)に分け、それぞれ別の方に向に分子を倒すよう工夫されているマルチドメイン化あるいはマルチドメイン設計といわれる方法を用いることができる。

#### 【0382】

また、表示装置において、ブラックマトリクス(遮光層)、偏光部材、位相差部材、反射防止部材などの光学部材(光学基板)などは適宜設ける。例えば、偏光基板及び位相差基板による円偏光を用いてもよい。また、光源としてバックライト、サイドライトなどを用いてもよい。

#### 【0383】

また、画素部における表示方式は、プログレッシブ方式やインターレース方式等を用いることができる。また、カラー表示する際に画素で制御する色要素としては、RGB(Rは赤、Gは緑、Bは青を表す)の三色に限定されない。例えば、RGBW(Wは白を表す)、又はRGBに、イエロー、シアン、マゼンタ等を一色以上追加したものがある。なお、色要素のドット毎にその表示領域の大きさが異なっていてもよい。ただし、開示する発明はカラー表示の表示装置に限定されるものではなく、モノクロ表示の表示装置に適用することもできる。

#### 【0384】

また、表示装置に含まれる表示素子として、エレクトロルミネッセンスを利用する発光素子を適用することができる。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

#### 【0385】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。本実施の形態では、発光素子として有機EL素子を用いる例を示す。

#### 【0386】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー-アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。

#### 【0387】

発光素子は発光を取り出すために少なくとも一対の電極の一方が透光性であればよい。そ

10

20

30

40

50

して、基板上にトランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、どの射出構造の発光素子も適用することができる。

**【0388】**

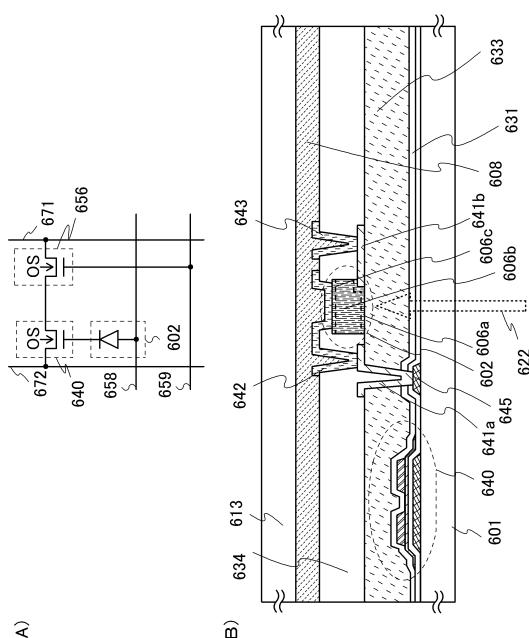

図9(A)(B)及び図10(B)に表示素子として発光素子を用いた発光装置の例を示す。

**【0389】**

図9(A)は発光装置の平面図であり、図9(A)中の一点鎖線S1-T1、S2-T2、及びS3-T3で切断した断面が図9(B)に相当する。なお、図9(A)の平面図においては、電界発光層542及び第2の電極層543は省略してあり図示していない。10

**【0390】**

図9に示す発光装置は、基板500上に、トランジスタ510、容量素子520、配線層交差部530を有しており、トランジスタ510は発光素子540と電気的に接続している。なお、図9は基板500を通過して発光素子540からの光を取り出す、下面射出型構造の発光装置である。

**【0391】**

トランジスタ510としては、実施の形態1乃至7のいずれかで示したトランジスタを適用することができる。本実施の形態では、実施の形態1で示したトランジスタ440と同様な構造を有するトランジスタを適用する例を示す。トランジスタ510は、ボトムゲート構造のスタガ型トランジスタである。20

**【0392】**

トランジスタ510はゲート電極層511a、511b、ゲート絶縁膜502、酸化物半導体膜512、ソース電極層又はドレイン電極層として機能する導電層513a、513bを含む。

**【0393】**

トランジスタ510は、酸化物半導体膜に接するゲート絶縁膜502及び/又は層間絶縁膜504に、熱処理による脱水化又は脱水素化処理を行い、かつ脱水化又は脱水素化処理後に酸素ドープ処理を行って作製されたトランジスタである。よって、酸化物半導体膜には、トランジスタ510の特性変動を引き起こす水素、又は水などの不純物が混入せず、かつ酸素欠損を補填する酸素が供給される。よって、トランジスタ510は、電気特性変動が抑制されている。30

**【0394】**

従って、図9で示す本実施の形態の酸化物半導体膜512を用いた安定した電気特性を有するトランジスタ510を含む半導体装置として信頼性の高い半導体装置を提供することができる。また、そのような信頼性の高い半導体装置を歩留まりよく作製し、高生産化を達成することができる。

**【0395】**

容量素子520は、導電層521a、521b、ゲート絶縁膜502、酸化物半導体膜522、導電層523を含み、導電層521a、521bと導電層523とで、ゲート絶縁膜502及び酸化物半導体膜522を挟む構成とすることで容量を形成する。40

**【0396】**

配線層交差部530は、ゲート電極層511a、511bと、導電層533との交差部であり、ゲート電極層511a、511bと、導電層533とは、間にゲート絶縁膜502を介して交差する。

**【0397】**

本実施の形態においては、ゲート電極層511a及び導電層521aとして膜厚30nmのチタン膜を用い、ゲート電極層511b及び導電層521bとして膜厚200nmの銅薄膜を用いる。よって、ゲート電極層はチタン膜と銅薄膜との積層構造となる。

**【0398】**

酸化物半導体膜 512、522 としては膜厚 25 nm の I G Z O 膜を用いる。

【0399】

トランジスタ 510、容量素子 520、及び配線層交差部 530 上には層間絶縁膜 504 が形成され、層間絶縁膜 504 上において発光素子 540 と重畠する領域にカラーフィルタ層 505 が設けられている。層間絶縁膜 504 及びカラーフィルタ層 505 上には平坦化絶縁膜として機能する絶縁膜 506 が設けられている。

【0400】

絶縁膜 506 上に第 1 の電極層 541、電界発光層 542、第 2 の電極層 543 の順に積層した積層構造を含む発光素子 540 が設けられている。発光素子 540 とトランジスタ 510 とは、導電層 513a に達する絶縁膜 506 及び層間絶縁膜 504 に形成された開口において、第 1 の電極層 541 及び導電層 513a とは接することによって電気的に接続されている。なお、第 1 の電極層 541 の一部及び該開口を覆うように隔壁 507 が設けられている。

10

【0401】

層間絶縁膜 504 には、プラズマ CVD 法による膜厚 200 nm 以上 600 nm 以下の酸化窒化シリコン膜を用いることができる。また、絶縁膜 506 には膜厚 1500 nm の感光性のアクリル膜、隔壁 507 には膜厚 1500 nm の感光性のポリイミド膜を用いることができる。

【0402】

カラーフィルタ層 505 としては、例えば有彩色の透光性樹脂を用いることができる。有彩色の透光性樹脂としては、感光性、非感光性の有機樹脂を用いることができるが、感光性の有機樹脂層を用いるとレジストマスク数を削減することができるため、工程が簡略化し好ましい。

20

【0403】

有彩色は、黒、灰、白などの無彩色を除く色であり、カラーフィルタ層は、着色された有彩色の光のみを透過する材料で形成される。有彩色としては、赤色、緑色、青色などを用いることができる。また、シアン、マゼンダ、イエロー（黄）などを用いてもよい。着色された有彩色の光のみを透過するとは、カラーフィルタ層における透過光は、その有彩色の光の波長にピークを有するということである。カラーフィルタ層は、含ませる着色材料の濃度と光の透過率の関係に考慮して、最適な膜厚を適宜制御するとよい。例えば、カラーフィルタ層 505 の膜厚は 1500 nm 以上 2000 nm 以下とすればよい。

30

【0404】

図 10 (B) に示す発光装置においては、表示素子である発光素子 4513 は、画素部 4002 に設けられたトランジスタ 4010 と電気的に接続している。なお発光素子 4513 の構成は、第 1 の電極層 4030、電界発光層 4511、第 2 の電極層 4031 の積層構造であるが、示した構成に限定されない。発光素子 4513 から取り出す光の方向などに合わせて、発光素子 4513 の構成は適宜変えることができる。

【0405】

隔壁 4510、507 は、有機絶縁材料、又は無機絶縁材料を用いて形成する。特に感光性の樹脂材料を用い、第 1 の電極層 4030、541 上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

40

【0406】

電界発光層 4511、542 は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでもよい。

【0407】

発光素子 4513、540 に酸素、水素、水分、二酸化炭素等が侵入しないように、第 2 の電極層 4031、543 及び隔壁 4510、507 上に保護膜を形成してもよい。保護膜としては、窒化シリコン膜、窒化酸化シリコン膜、DLC 膜等を形成することができる。

【0408】

50

また、発光素子 4513、540 に酸素、水素、水分、二酸化炭素等が侵入しないように、発光素子 4513、540 を覆う有機化合物を含む層を蒸着法により形成してもよい。

#### 【0409】

また、基板 4001、基板 4006、及びシール材 4005 によって封止された空間には充填材 4514 が設けられ密封されている。このように外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム（貼り合わせフィルム、紫外線硬化樹脂フィルム等）やカバー材でパッケージング（封入）することが好ましい。

#### 【0410】

充填材 4514 としては窒素やアルゴンなどの不活性な気体の他に、紫外線硬化樹脂又は熱硬化樹脂を用いることができ、PVC（ポリビニルクロライド）、アクリル、ポリイミド、エポキシ樹脂、シリコーン樹脂、PVB（ポリビニルブチラル）又はEVA（エチレンビニルアセテート）を用いることができる。例えば充填材として窒素を用いればよい。

10

#### 【0411】

また、必要であれば、発光素子の射出面に偏光板、又は円偏光板（橙円偏光板を含む）、位相差板（1/4 板、1/2 板）、カラーフィルタなどの光学フィルムを適宜設けてよい。また、偏光板又は円偏光板に反射防止膜を設けてよい。例えば、表面の凹凸により反射光を拡散し、映り込みを低減できるアンチグレア処理を施すことができる。

#### 【0412】

また、表示装置として、電子インクを駆動させる電子ペーパーを提供することも可能である。電子ペーパーは、電気泳動表示装置（電気泳動ディスプレイ）とも呼ばれており、紙と同じ読みやすさ、他の表示装置に比べ低消費電力、薄くて軽い形状とすることが可能という利点を有している。

20

#### 【0413】

電気泳動表示装置は、様々な形態が考えられ得るが、プラスの電荷を有する第1の粒子と、マイナスの電荷を有する第2の粒子とを含むマイクロカプセルが溶媒又は溶質に複数分散されたものであり、マイクロカプセルに電界を印加することによって、マイクロカプセル中の粒子を互いに反対方向に移動させて一方側に集合した粒子の色のみを表示するものである。なお、第1の粒子又は第2の粒子は染料を含み、電界がない場合において移動しないものである。また、第1の粒子の色と第2の粒子の色は異なるもの（無色を含む）とする。

30

#### 【0414】

このように、電気泳動表示装置は、誘電定数の高い物質が高い電界領域に移動する、いわゆる誘電泳動的効果を利用したディスプレイである。

#### 【0415】

上記マイクロカプセルを溶媒中に分散させたものが電子インクと呼ばれるものであり、この電子インクはガラス、プラスチック、布、紙などの表面に印刷することができる。また、カラーフィルタや色素を有する粒子を用いることによってカラー表示も可能である。

#### 【0416】

なお、マイクロカプセル中の第1の粒子および第2の粒子は、導電体材料、絶縁体材料、半導体材料、磁性材料、液晶材料、強誘電性材料、エレクトロルミネセント材料、エレクトロクロミック材料、磁気泳動材料から選ばれた一種の材料、又はこれらの複合材料を用いればよい。

40

#### 【0417】

また、電子ペーパーとして、ツイストボール表示方式を用いる表示装置も適用することができる。ツイストボール表示方式とは、白と黒に塗り分けられた球形粒子を、表示素子に用いる電極層である第1の電極層及び第2の電極層の間に配置し、第1の電極層及び第2の電極層に電位差を生じさせて球形粒子の向きを制御することにより、表示を行う方法である。

#### 【0418】

なお、図8乃至図10において、基板 4001、500、基板 4006 としては、ガラス

50

基板の他、可撓性を有する基板も用いることができ、例えば透光性を有するプラスチック基板などを用いることができる。プラスチックとしては、F R P (F i b e r g l a s s - R e i n f o r c e d P l a s t i c s ) 板、P V F (ポリビニルフルオライド) フィルム、ポリエステルフィルム又はアクリル樹脂フィルムを用いることができる。また、透光性が必要でなければ、アルミニウムやステンレスなどの金属基板(金属フィルム)を用いてもよい。例えば、アルミニウムホイルをP V F フィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。

#### 【0419】

本実施の形態では、絶縁膜4020としてプラズマCVD法によって形成する酸化窒化シリコン膜を用い、脱水化又は脱水素化のための熱処理及び酸素ドープ処理を行う。

10

#### 【0420】

さらに、脱水化又は脱水素化のための熱処理及び酸素ドープ処理を行った酸化窒化シリコン膜上に酸化アルミニウム膜を形成し、熱処理を行うことが好ましい。

#### 【0421】

酸化アルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を透過させない遮断効果(ロック効果)が高い。

#### 【0422】

従って、酸化アルミニウム膜は、作製工程中及び作製後において、脱水化又は脱水素化のための熱処理及び酸素ドープ処理を行った酸化窒化シリコン膜への変動要因となる水素、水分などの不純物の混入、及び酸素の放出を防止する保護膜として機能する。

20

#### 【0423】

また、平坦化絶縁膜として機能する絶縁膜4021、506は、アクリル、ポリイミド、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料(LOW-k材料)、シロキサン系樹脂、PSG(リンガラス)、BPSG(リンボロンガラス)等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層することで、絶縁膜を形成してもよい。

#### 【0424】

絶縁膜4021、506の形成法は、特に限定されず、その材料に応じて、スパッタリング法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法(インクジェット法等)、印刷法(スクリーン印刷、オフセット印刷等)、ドクターナイフ、ロールコーテー、カーテンコーテー、ナイフコーテー等を用いることができる。

30

#### 【0425】

表示装置は光源又は表示素子からの光を透過させて表示を行う。よって光が透過する画素部に設けられる基板、絶縁膜、導電膜などの薄膜はすべて可視光の波長領域の光に対して透光性とする。

#### 【0426】

表示素子に電圧を印加する第1の電極層及び第2の電極層(画素電極層、共通電極層、対向電極層などともいう)においては、取り出す光の方向、電極層が設けられる場所、及び電極層のパターン構造によって透光性、反射性を選択すればよい。

40

#### 【0427】

第1の電極層4030、541、第2の電極層4031、543は、酸化タンゲスタンを含むインジウム酸化物、酸化タンゲスタンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物、グラフェンなどの透光性を有する導電性材料を用いることができる。

#### 【0428】

また、第1の電極層4030、541、第2の電極層4031、543はタンゲスタン(W)、モリブデン(Mo)、ジルコニア(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、クロム(Cr)、コバルト(Co)、ニッケ

50

ル( Ni )、チタン( Ti )、白金( Pt )、アルミニウム( Al )、銅( Cu )、銀( Ag )等の金属、又はその合金、若しくはその金属窒化物から一つ、又は複数種を用いて形成することができる。

#### 【 0 4 2 9 】

本実施の形態においては、図9に示す発光装置は下面射出型なので、第1の電極層541は透光性、第2の電極層543は反射性を有する。よって、第1の電極層541に金属膜を用いる場合は透光性を保てる程度膜厚を薄く、第2の電極層543に透光性を有する導電膜を用いる場合は、反射性を有する導電膜を積層するとよい。

#### 【 0 4 3 0 】

また、第1の電極層4030、541、第2の電極層4031、543として、導電性高分子(導電性ポリマーともいう)を含む導電性組成物を用いて形成することができる。導電性高分子としては、いわゆる電子共役系導電性高分子が用いることができる。例えば、ポリアニリン又はその誘導体、ポリピロール又はその誘導体、ポリチオフェン又はその誘導体、若しくはアニリン、ピロールおよびチオフェンの2種以上からなる共重合体若しくはその誘導体などがあげられる。

10

#### 【 0 4 3 1 】

また、トランジスタは静電気などにより破壊されやすいため、駆動回路保護用の保護回路を設けることが好ましい。保護回路は、非線形素子を用いて構成することが好ましい。

#### 【 0 4 3 2 】

以上のように実施の形態1乃至7のいずれかで示したトランジスタを適用することで、様々な機能を有する半導体装置を提供することができる。

20

#### 【 0 4 3 3 】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【 0 4 3 4 】

##### ( 実施の形態 9 )

実施の形態1乃至7のいずれかに示したトランジスタを用いて、対象物の情報を読み取るイメージセンサ機能を有する半導体装置を作製することができる。

#### 【 0 4 3 5 】

図11(A)に、イメージセンサ機能を有する半導体装置の一例を示す。図11(A)はフォトセンサの等価回路であり、図11(B)はフォトセンサの一部を示す断面図である。

30

#### 【 0 4 3 6 】

フォトダイオード602は、一方の電極がフォトダイオードリセット信号線658に、他方の電極がトランジスタ640のゲートに電気的に接続されている。トランジスタ640は、ソース又はドレインの一方がフォトセンサ基準信号線672に、ソース又はドレインの他方がトランジスタ656のソース又はドレインの一方に電気的に接続されている。トランジスタ656は、ゲートがゲート信号線659に、ソース又はドレインの他方がフォトセンサ出力信号線671に電気的に接続されている。

#### 【 0 4 3 7 】

40

なお、本明細書における回路図において、酸化物半導体膜を用いるトランジスタと明確に判明できるように、酸化物半導体膜を用いるトランジスタの記号には「OS」と記載している。図11(A)において、トランジスタ640、トランジスタ656は実施の形態1乃至7のいずれかに示したトランジスタが適用でき、酸化物半導体膜を用いるトランジスタである。本実施の形態では、実施の形態1で示したトランジスタ440と同様な構造を有するトランジスタを適用する例を示す。トランジスタ640は、ボトムゲート構造のスタガ型トランジスタである。

#### 【 0 4 3 8 】

図11(B)は、フォトセンサにおけるフォトダイオード602及びトランジスタ640に示す断面図であり、絶縁表面を有する基板601(素子基板)上に、センサとして機能

50

するフォトダイオード 602 及びトランジスタ 640 が設けられている。フォトダイオード 602、トランジスタ 640 の上には接着層 608 を用いて基板 613 が設けられている。

#### 【0439】

トランジスタ 640 上には絶縁膜 631、層間絶縁膜 633、層間絶縁膜 634 が設けられている。フォトダイオード 602 は、層間絶縁膜 633 上に設けられ、層間絶縁膜 633 上に形成した電極層 641a、641b と、層間絶縁膜 634 上に設けられた電極層 642 との間に、層間絶縁膜 633 側から順に第1半導体膜 606a、第2半導体膜 606b、及び第3半導体膜 606c を積層した構造を有している。

#### 【0440】